#### Reliability Aware Computing Platforms Design and Lifetime Management

Cucu Laurenciu, Nicoleta

10.4233/uuid:9c46dcd4-e68e-42de-a7ab-676a3e631f0d

**Publication date**

**Document Version** Final published version

Citation (APA)

Cucu Laurenciu, N. (2017). Reliability Aware Computing Platforms Design and Lifetime Management. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:9c46dcd4-e68e-42dea7ab-676a3e631f0d

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Reliability Aware Computing Platforms Design and Lifetime Management

Cover illustration: Constantin Brancusi's monumental Endless Column in Targu-Jiu, Romania. The column of metal-coated cast-iron modules on a steel spine with a height of 29.33 meters, is part of a sculptural ensemble originally installed in 1937-1938, which includes the travertine Table of Silence and Gate of the Kiss, as well.

# Reliability Aware Computing Platforms Design and Lifetime Management

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op

donderdag 26 januari 2017, om 10:00 uur

door

Nicoleta CUCU LAURENCIU

Master of Science in Computer Engineering Technische Universiteit Delft, Nederland geboren te Brasov, Romania Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. ir. K. L. M. Bertels

Copromotor:

Dr. S. D. Cotofana

#### Samenstelling promotiecommissie:

Rector Magnificus, voorzitter Technische Universiteit Delft

Prof. dr. ir. K. L. M. Bertels

Dr. S. D. Cotofana

Technische Universiteit Delft, promotor

Technische Universiteit Delft, copromotor

#### Onafhankelijke leden:

Prof. dr. ir. G. Leus

Prof. dr. A. Rubio

Universiteit Politècnica de Catalunya, Spain

Dr. C. Anghel

Prof. dr. ir. K. Goossens

Prof. dr. G. Stefan

Prof. dr. ir. P. Van Mieghem

Technische Universiteit Delft, Nederland

Universiteit Delft, Nederland

Universiteit Delft, Nederland

Universiteit Delft, Nederland

Universiteit Eindhoven, Nederland

"Politehnica" University of Bucharest, Romania

Technische Universiteit Delft, reserve lid

#### CIP-DATA KONINKLIJKE BIBLIOTHEEK, DEN HAAG

Nicoleta Cucu Laurenciu

Reliability Aware Computing Platforms Design and Lifetime Management Delft: TU Delft, Faculty of Elektrotechniek, Wiskunde en Informatica - III Thesis Technische Universiteit Delft.

Met samenvatting in het Nederlands.

ISBN 978-94-6186-780-3

Keywords: Reliability, Reliability Aware Computation, Dynamic Lifetime Reliability Management, Reliability Assessment

Copyright © 2016 Nicoleta Cucu Laurenciu

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission of the author.

Printed in Nederland

### **Abstract**

ggressive CMOS technology feature size down-scaling into the deca nanometer regime, while benefiting performance and yield, determined device characteristics variability increase w.r.t. their nominal values, which can lead to large spreads in delay, power, and robustness, and make devices more prone to aging and noise induced failures during in-field usage. Because of transistor's gate dielectric increasing power density and electric field the nanoscale Integrated Circuits (ICs) failure mechanisms accelerating factors have become more severe than ever, which can cause higher failure rate during ICs useful life and early aging onset. As a result, meeting the reliability targets with viable costs in this landscape becomes a significant challenge, requiring to be addressed in an unitary manner from design time to run time. To this end, we propose a holistic reliability aware design and lifetime management framework concerned (i) at design time, with providing a reliability enhanced adaptive architecture fabric, and (ii) at run time, with observing and dynamically managing fabric's wear-out profile such that user defined Qualityof-Service requirements are fulfilled, and with maintaining a full-life reliability log to be utilized as auxiliary information during the next IC generation design. Specifically, we first introduce design time transistor and circuit level aging models, which provide the foundation for a 4-dimensional Design Space Exploration (DSE) meant to identify a reliability optimized circuit realization compliant with area, power, and delay constraints. Subsequently, to enable the creation of a low cost but yet accurate fabric observation infrastructure, we propose a methodology to minimize the number of aging sensors to be deployed in a circuit and identify their location, and introduce a sensor design able to directly capture circuit level amalgamated effects of concomitant degradation mechanisms. Furthermore, to make the information collected from sensors meaningful to the run-time management framework we introduce a circuit level model that can estimate the overall circuit aging and predict its End-of-Life based on imprecise sensors measurements, while taking into account the degradation nonlinearities. Finally, to provide more DSE reliability enhancement options we focus on the realization of reliable data transport and processing with unreliable components, and propose: (i) a codec for reliable energy efficient medium/long range data transport, and (ii) a methodology to obtain Error Correction Codes protected data processing units with an output error rate smaller than the fabrication technology gate error rate.

## Acknowledgments

The past 5 years work whose end result is constituted by this thesis, was enabled by the contribution of several excellent people, to whom I would like to pay my respects chronologically.

I would like to thank my former professors from Transilvania University of Brasov, Romania, for laying the Computer Engineering (CE) knowledge foundations. I would like to thank especially Prof. dr. Gheorghe Toacse, founder of the CE department at Transilvania University of Brasov, one of the Romanian university education titans, who introduced me to the rigors of computer engineering and laid the foundations of structured thinking in this domain. His influence on my knowledge and professional formation was significant. He also facilitated me to begin my studies in Delft, as a terminal year bachelor exchange student, and I am forever grateful.

I thank my former professors from TU Delft, The Netherlands, for consolidating and enriching my knowledge during the M.Sc. studies in Computer Engineering.

Foremost I would like to express my deepest, utmost and sincere gratitude to my Ph.D. supervisor, Dr. Sorin D. Cotofana, for shaping and cultivating the quality of my mind and character, the freedom of thought and for awakening an ardent spirit of inquiry, while instilling at the same time enduring life values. He permanently guided me while allowing me complete freedom of exploration, he taught me the modus operandi of critical thinking and not what to think, and facilitated me to experience knowledge for the sake of knowledge. His passion and inexorable dedication for research and academia earned my profound esteem. Prof. Cotofana incessantly motivated me to keep progressing, and encouraged assiduous and disciplined pursuit of knowledge. His moral stamina and energy were always a source of inspiration. In any situation he was always objective, and with an irreproachable moral stance. My gratitude toward Prof. Cotofana is limitless. It was truly a privilege, a pleasure and an honor to work and interact with him.

I am thankful to Prof. dr. ir. Koen Bertels, the head of the Quantum Computing Department, who brought a welcomed influence, by supporting us in our academic development, encouraging a unified collaboration working atmosphere, and creating a pleasant intellectual environment in the department. He broadened our horizon in other scientific areas via the various topics colloquia regularly held by top field professors

I would like to thank the CE secretary Ms. Lidwina Tromp for guiding me through the

administrative and financial cobweb, multum in parvo for her promptitude, availability and professionalism. I have enjoyed the pleasant conversations with her and greatly benefited from her advice on various matters as well.

I would like to extend my thanks to Dr. ir. Arjan van Genderen for his support, enabling me to be independent to a certain extent, which positively influenced my EDA tools knowledge and simulations.

I am grateful to the technical support team, foremost Erik de Vries, the CE system administrator, for ensuring a fluent and smooth operation of the simulation infrastructure on the HPC clusters, a sine qua non component of research infrastructure.

Within the framework of i-RISC international project, I had the opportunity to collaborate with Dr. Valentin Savin, from CEA-LETI, France. I was impressed by his work conduit and his clear, structured mathematical thinking, and I thank him for the fruitful discussions concerning LDPC codes and their utilization in reliable functional units design.

I would also like to thank the members of the committee for accepting to take part in the defense committee and for reviewing the thesis.

I would like to thank the Ph.D. colleagues, especially the Chinese ones, for the fruitful exchange of ideas.

I also thank my parents, of whom material and moral support I enjoyed throughout my studies.

Nicoleta Cucu Laurenciu

Delft, The Netherlands, January 2017

# Table of Contents

| Tit | le      |                                                    |

|-----|---------|----------------------------------------------------|

| Αb  | stract  | vi                                                 |

| Αc  | know    | ledgments ix                                       |

| Lis | st of T | ables                                              |

| Lis | st of F | igures                                             |

| Lis | st of A | cronyms                                            |

| 1   | Intro   | duction                                            |

|     | 1.1     | ICs Reliability Trends                             |

|     | 1.2     | Research Questions                                 |

|     | 1.3     | Thesis Contributions                               |

|     | 1.4     | Thesis Organization                                |

| 2   | Desi    | gn-Time Transistor-Level Aging Model               |

|     | 2.1     | Introduction                                       |

|     | 2.2     | Signal Slope as Aging Monitor                      |

|     | 2.3     | Transistor Aging Model                             |

|     | 2.4     | Performance Evaluation                             |

|     | 2.5     | Conclusion                                         |

| 3   | Desi    | gn-Time Transistor-Based Circuit-Level Aging Model |

|     | 3.1     | Introduction                                       |

|   | 3.2   | Critical Transistors Kernel Selection                                     | 38 |

|---|-------|---------------------------------------------------------------------------|----|

|   | 3.3   | Regression-Based Circuit-Level Aging Model                                | 40 |

|   | 3.4   | Markovian Circuit-Level Aging Model                                       | 41 |

|   | 3.5   | Performance Evaluation                                                    | 46 |

|   | 3.6   | Conclusion                                                                | 50 |

| 4 | Agin  | g Sensor Design for Dynamic Lifetime Resources Management                 | 53 |

|   | 4.1   | Introduction                                                              | 54 |

|   | 4.2   | Power Supply Current as Aging Monitor                                     | 55 |

|   | 4.3   | <i>I<sub>DD</sub></i> -Based Aging Sensor Circuit Design                  | 59 |

|   |       | 4.3.1 The Current Peak Detector (CPD)                                     | 59 |

|   |       | 4.3.2 The Current-to-Time Converter (C2T)                                 | 62 |

|   | 4.4   | Performance Evaluation                                                    | 63 |

|   | 4.5   | Conclusion                                                                | 66 |

| 5 | End   | Of-Life and Reliability Statistics Estimation From Noisy Sensors          |    |

| J |       | ervations                                                                 | 69 |

|   | 5.1   | Introduction                                                              | 69 |

|   | 5.2   | Degradation Process Formalism                                             | 70 |

|   | 5.3   | Reliability Assessment Framework                                          | 72 |

|   |       | 5.3.1 Reliability evaluation procedure outline                            | 72 |

|   |       | 5.3.2 Gibbs sampler step 1 - draw $x_{1:N} \mid \theta, V$                | 73 |

|   |       | 5.3.3 Gibbs sampler step 2 - draw $\theta \mid x_{1:N} \dots \dots \dots$ | 74 |

|   | 5.4   | Performance Evaluation                                                    | 75 |

|   |       | 5.4.1 Case Study                                                          | 77 |

|   | 5.5   | Conclusion                                                                | 79 |

| 6 | Relia | able Data Transport                                                       | 81 |

|   | 6.1   | Introduction                                                              | 81 |

|   | 6.2   | Haar Codec Modus Operandi                                                 | 83 |

|   |       | 6.2.1 Haar Codec                                                          | 83 |

|   |       | 6.2.2 SECDED                                                              | 85 |

|   | 6.3   | Simulation Results                                                        | 88 |

|     |              | 6.3.1      | Energy & Area                  |  |  |  |

|-----|--------------|------------|--------------------------------|--|--|--|

|     |              | 6.3.2      | Delay                          |  |  |  |

|     | 6.4          | State-of-t | he-Art Comparison              |  |  |  |

|     | 6.5          | Conclusio  | on                             |  |  |  |

| 7   | Relia        | ble Data F | Processing Units               |  |  |  |

|     | 7.1          | Introduct  | ion                            |  |  |  |

|     | 7.2          | General I  | Framework and Simulation Setup |  |  |  |

|     | 7.3          | Design S   | pace Exploration               |  |  |  |

|     |              | 7.3.1      | Gate Criticality               |  |  |  |

|     |              | 7.3.2      | Code Correction Capacity       |  |  |  |

|     |              | 7.3.3      | ECC Type                       |  |  |  |

|     |              | 7.3.4      | Time-Space Redundancy          |  |  |  |

|     |              | 7.3.5      | Non-Ideal Decoding             |  |  |  |

|     |              | 7.3.6      | Modularized ECC                |  |  |  |

|     | 7.4          | Conclusio  | on                             |  |  |  |

| 8   | Conc         | lusions a  | nd Future Work                 |  |  |  |

|     | 8.1          | Summary    | 7                              |  |  |  |

|     | 8.2          | Future Re  | esearch Directions             |  |  |  |

| Bib | oliogra      | phy        |                                |  |  |  |

| Lis | t of Pu      | ıblication | s                              |  |  |  |

| Sa  | Samenvatting |            |                                |  |  |  |

| Pro | positi       | ons        |                                |  |  |  |

| Cu  | rriculu      | m Vitae    |                                |  |  |  |

# List of Tables

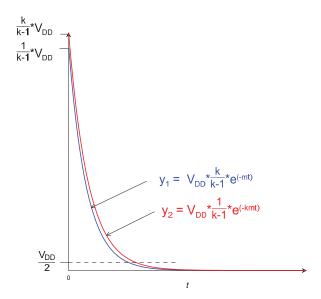

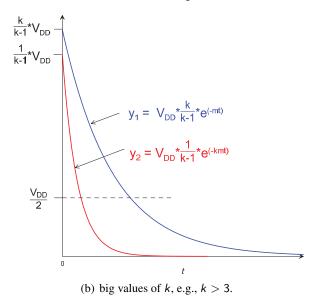

| 2.1 | The Output Voltage Value, $V_{out}$ , Sampled at Two Different Time Instants $(1/m \text{ and } 2/m)$ , for Three Different Multiplicity Factors $k$ (3, 1.5, and 1.1) | 28 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Aging Assessment and Prediction Accuracy Context-Aware vs. Intrinsic.                                                                                                  | 33 |

| 6.1 | One-Bit Error Scenarios for Haar System                                                                                                                                | 80 |

| 6.2 | Haar System Single Error Correction.                                                                                                                                   | 8′ |

# List of Figures

| 1.1 | Lifetime Failure Distribution for Advanced Technology Nodes                                                  | 3  |

|-----|--------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Power Density of Intel Microprocessors                                                                       | 5  |

| 1.3 | Structured View of the Different Types of Parameters Variations                                              | 6  |

| 1.4 | Reliability-Aware Circuit Design Sub-Framework                                                               | 9  |

| 1.5 | Dynamic Lifetime Resources Management Framework                                                              | 14 |

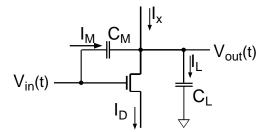

| 2.1 | Transistor Age Assessment Circuit Schematic                                                                  | 24 |

| 2.2 | Graphical Interpretation of the Approximation $	au.$                                                         | 29 |

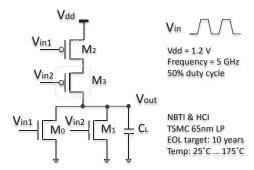

| 2.3 | Test Circuit for Model Validation and Aging Assessment and Prediction Accuracy.                              | 31 |

| 2.4 | Simulated vs. Estimated Output Voltage Slope                                                                 | 32 |

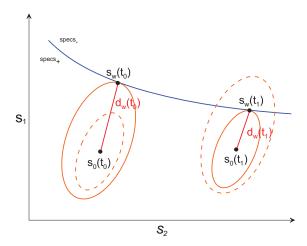

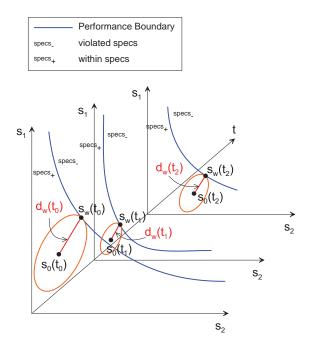

| 3.1 | Lifetime Evolution for Fixed Performance Boundary Graphical Representations.                                 | 43 |

| 3.2 | Lifetime Evolution for Time Varying Performance Boundary Graphical Representations                           | 44 |

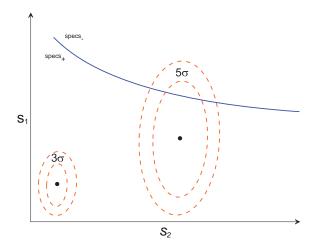

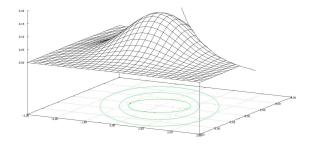

| 3.3 | 2D-PDF Evolution                                                                                             | 45 |

| 3.4 | 2D-PDF Truncated by Performance Boundary                                                                     | 45 |

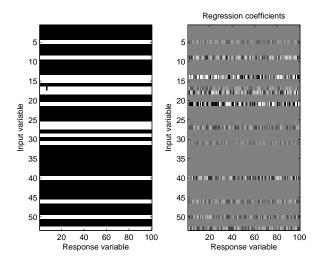

| 3.5 | The Regression Coefficients Determining the Reduced Set of Critical Transistors                              | 47 |

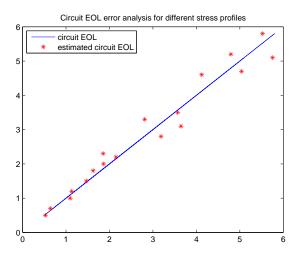

| 3.6 | Error Analysis of Circuit End-Of-Life Estimation Based on the End-Of-Life Values of the Critical Transistors | 48 |

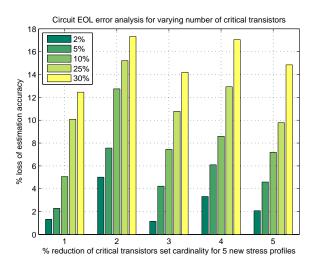

| 3.7  | Error Analysis of Circuit End-Of-Life Estimation Based on the End-Of-Life Values of the Critical Transistors                                                                                                                                                                                                                                      | 49 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

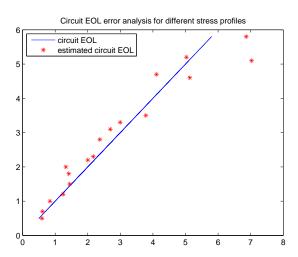

| 3.8  | Error Analysis of Circuit End-Of-Life Estimation, Using the Markovian Statistical Framework on the Set of Critical Aging Transistors                                                                                                                                                                                                              | 50 |

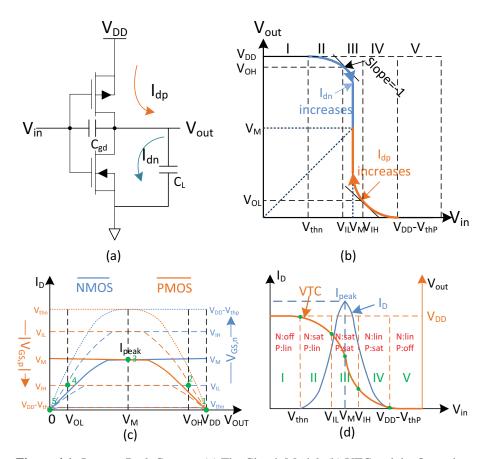

| 4.1  | Inverter Peak Current: (a) The Circuit Model; (b) VTC and the Operating Regions of PMOS, NMOS Transistors; (c) Intersections of the Output Characteristic Curves of PMOS, NMOS Transistors; (d) The Peak Power Supply Current and Transistor Operating Regions                                                                                    | 56 |

| 4.2  | Peak Current of CMOS Logic: (a) A General Illustration of CMOS Network; (b) Equivalent Invert Circuit for the Pull-Up Network                                                                                                                                                                                                                     | 57 |

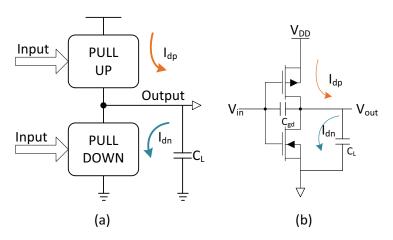

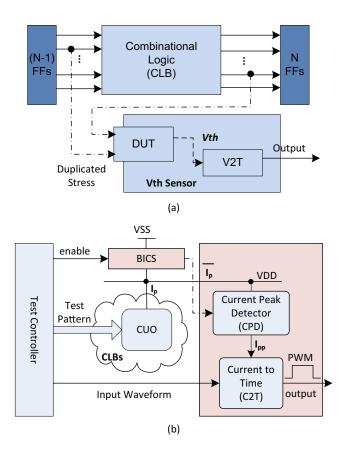

| 4.3  | Two Different Measurement Schemes for Degradation Detection: (a) $V_{th}$ Sensor Scheme; (b) A Direct Measurement Scheme with the Proposed $I_{pp}$ Sensor (in the Shadow Box). The Aging Indicator $I_{pp}$ of the Proposed Sensor Is Taken from the CUO Directly. $V_{th}$ Sensor Takes the Aging Indicator $V_{th}$ from the DUT of the Sensor | 60 |

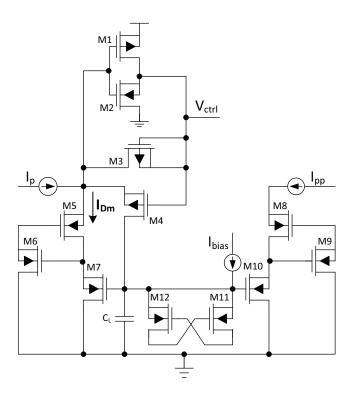

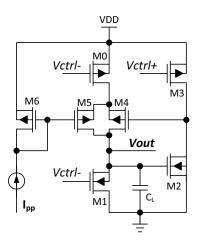

| 4.4  | Circuit Schematic of the Current-Mode Peak Detector                                                                                                                                                                                                                                                                                               | 61 |

| 4.5  | Circuit Schematic of the Current-to-Time Converter                                                                                                                                                                                                                                                                                                | 62 |

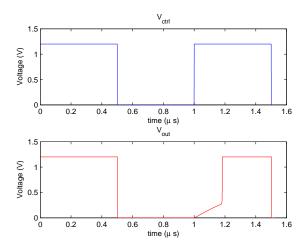

| 4.6  | The Transient Waveform of the Voltage Across Capacitor $C_L$                                                                                                                                                                                                                                                                                      | 63 |

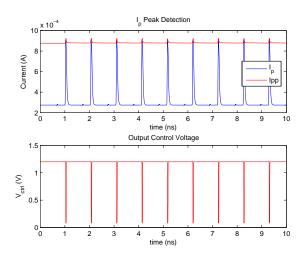

| 4.7  | Peak Current Detection at 1GHZ                                                                                                                                                                                                                                                                                                                    | 64 |

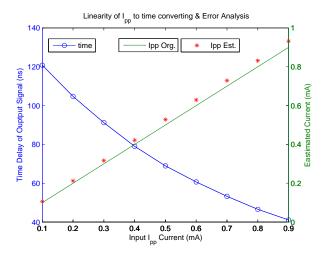

| 4.8  | Linearity of Peak $I_p$ to Time Converting (Left Axis) and Error Analysis of Peak Detection (Right Axis)                                                                                                                                                                                                                                          | 64 |

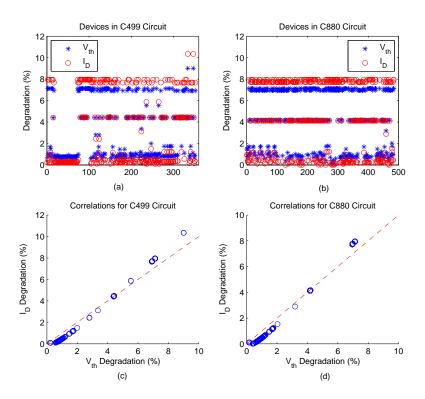

| 4.9  | The Percentage Degradations of $V_{th}$ and $I_D$ for All Devices in the c499 and c880 Circuits - (a) and (b); and the Correlations between the Percentage Degradations of $V_{th}$ and $I_D$ - (c) and (d)                                                                                                                                       | 65 |

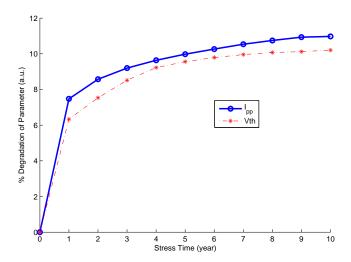

| 4.10 | The Time Evolution of the $V_{th}$ and $I_D$ Degradation for 10-Year Simulation                                                                                                                                                                                                                                                                   | 66 |

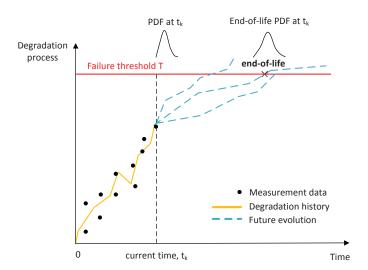

| 5.1  | Illustration of the Reliability Modeling Principle                                                                                                                                                                                                                                                                                                | 71 |

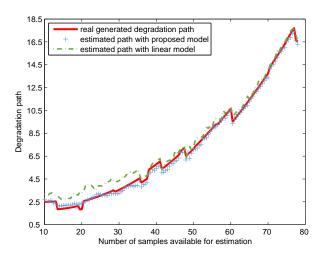

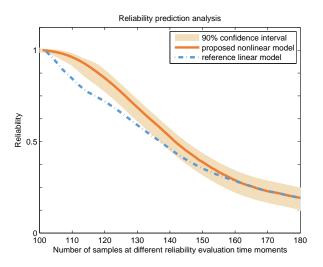

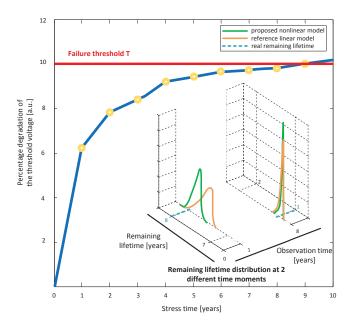

| 5.2  | The Real vs. Estimated Degradation Paths                                                                                                                                                                                                                                                                                                          | 76 |

| 5.3  | The Reliability Assessment/Prediction Error Analysis                                                                                                                                                                                                                                                                                              | 76 |

| 5.4  | Time Evolution of the $V_{th}$ Degradation After 10-year Simulation and Remaining Lifetime Distribution at two Different observation time moments: 1 year and 8 years                                                                                                                                                                             | 78 |

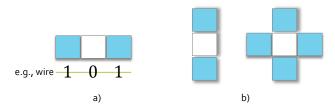

| 6.1 | Switching patterns to be avoided for: a) own transitions along the wire, and b) single/double coupling transitions between adjacent wires. | 84  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

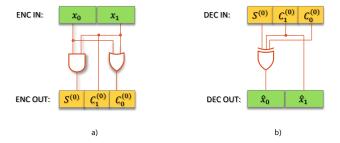

| 6.2 | 2- bit Haar codec: a) encoder, and b) decoder                                                                                              | 84  |

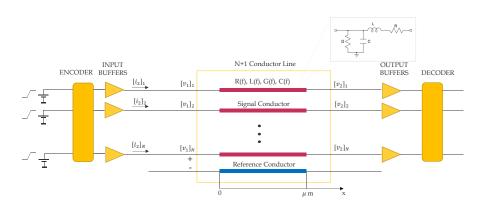

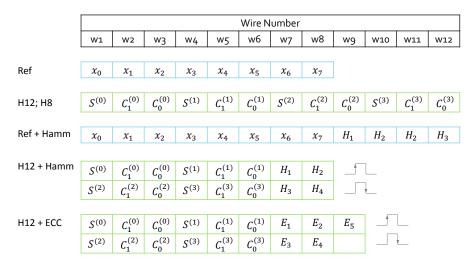

| 6.3 | SPICE simulation setup for the interconnect coding-based systems                                                                           | 87  |

| 6.4 | Bits transmission configuration                                                                                                            | 90  |

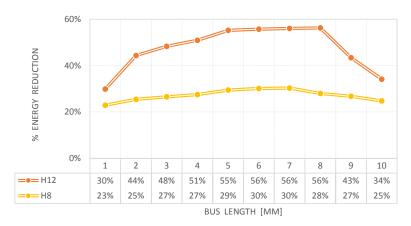

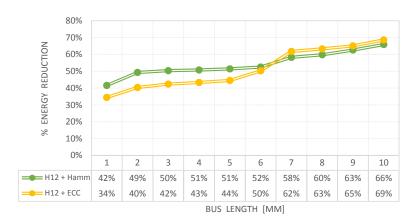

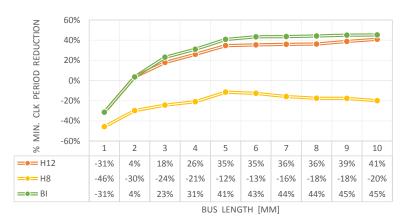

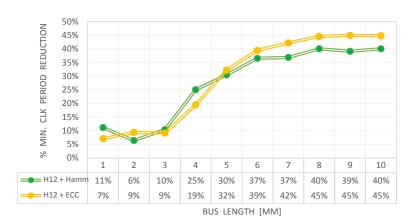

| 6.5 | Energy profile vs. interconnect length                                                                                                     | 91  |

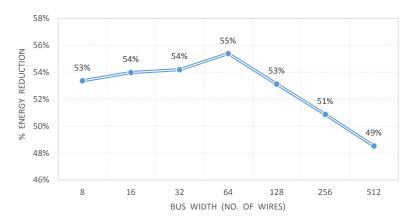

| 6.6 | Energy profile for "H" system for bus length of 5mm vs. bus width                                                                          | 92  |

| 6.7 | Energy profile vs. interconnect length for the ECC protected systems.                                                                      | 92  |

| 6.8 | Minimum clock period vs. interconnect length                                                                                               | 93  |

| 6.9 | Minimum clock period vs. interconnect length for the ECC protected systems.                                                                | 94  |

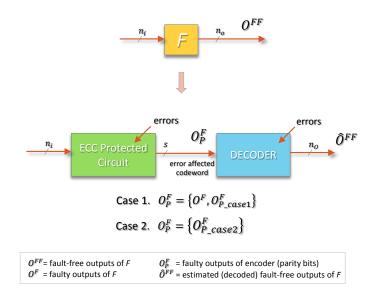

| 7.1 | ECC Protection for Boolean logic <i>F</i>                                                                                                  | 102 |

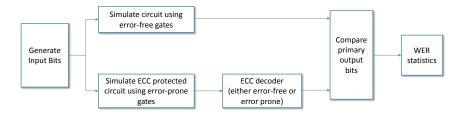

| 7.2 | Reliability Evaluation Framework                                                                                                           | 102 |

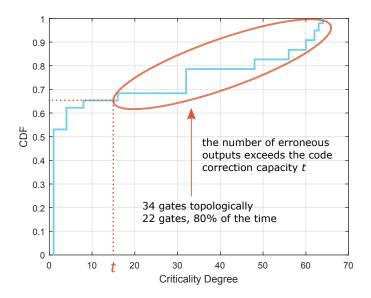

| 7.3 | Gates Criticality Statistics                                                                                                               | 103 |

| 7.4 | WER/Area vs. Gates Criticality                                                                                                             | 105 |

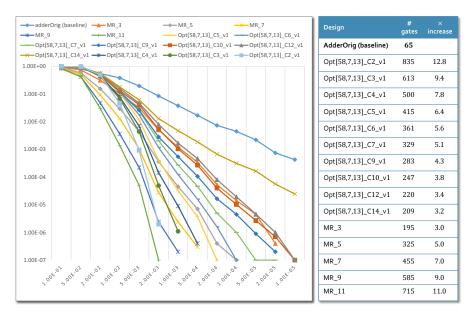

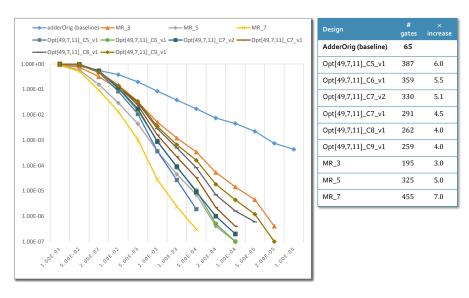

| 7.5 | WER/Area for Code Correction Capacity $t = 11$                                                                                             | 106 |

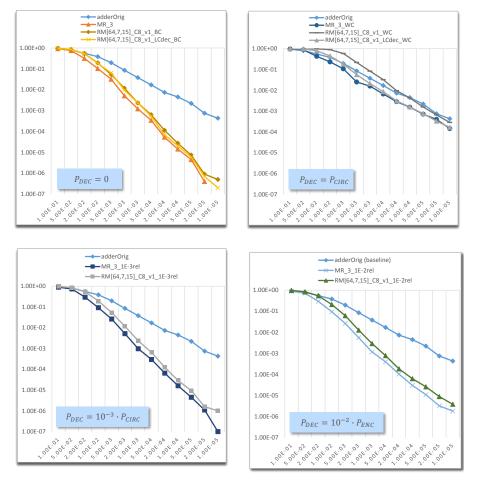

| 7.6 | WER for Non-Ideal Decoding                                                                                                                 | 108 |

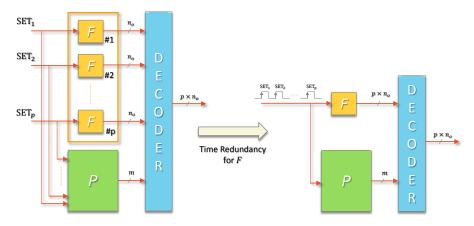

| 7.7 | Time-Space Redundancy.                                                                                                                     | 109 |

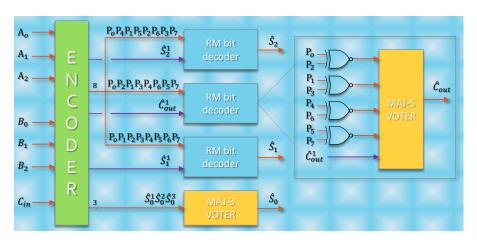

| 7 8 | Reed-Müller Low Complexity Decoder for 3-Bit Adder                                                                                         | 111 |

# List of Acronyms

AIC Akaike Information Criterium **BICS Built-In Current Sensor** Circuit Assisted Design CAD CLMChannel Length Modulation **CMOS** Complementary Metal-Oxide-Semiconductor **CPD** Current-mode Peak Detector C2TCurrent-to-Time Converter CUO Circuit Under Observation DPU **Data Processing Unit** DRM Dynamic Reliability Management DRM Dynamic Reliability Management **ECC** Error Correcting Code **ECL Emmiter-Coupled Logic** Electro-Migration ЕМ **EOL** End-Of-Life **FEOL** Front-End-Of-Line **FET** Field Effect Transistor **GDP** Gross Domestic Product HCI Hot Carrier Injection HDL Hardware Description Language IC Integrated Circuit KLKarhunen Loeve LPLow Power LSB Least Significant Bit MD Mobility Degradation MOS Metal-Oxide-Semiconductor **MOSFET** Metal-Oxide-Semiconductor Field Effect Transistor MR Modular Redundancy Most Significant Bit **MSB** NBTI Negative Bias Temperature Instability NoCNetwork on Chip **NMOS** N-type Metal-Oxide-Semiconductor NWE Narrow Width Effects **PBTI** Positive Bias Temperature Instability **PMOS** P-type Metal-Oxide-Semiconductor PDF **Probability Density Function** PΙ **Primary Input** Primary Output PO PWMPulse Width Modulated

Source-Drain parasitic Resistance

RDS

RM Reed-Müller

SCE Short Channel Effects

SECDED Single Error Correction Double Error Detection

SoC System on Chip

STA Statistical Timing AnalysisSSTA Statistical Static Timing Analysis

TC Thermal Cycling

TDDB Time Dependent Dielectric Breakdown

TTL Transistor-Transistor Logic

VS Velocity Saturation WER Word Error Rate

# Introduction

Integrated Circuits (ICs) brought about a computerization and electronics revolution, which radically changed the preponderant manner of human living and interaction. The silicon ICs age has its roots marked by three salient milestones: (i) the Field Effect Transistor (FET) concept introduction in 1926 by Julius Edgar Lilienfeld [1], and in 1934 by Oskar Heil [2], (ii) the invention of the bipolar transistor at Bell Telephone Laboratories by John Bardeen, Walter Brattain, and William Shockley in 1947 [3], and (iii) the introduction in 1959 of the planar manufacturing process by Jean Hoerni (Fairchild Semiconductor) [4], and of the monolithic approach by Robert Noyce (Fairchild Semiconductor) [5], which revolutionized the semiconductor manufacturing and technology.

One year later, the ICs era started, as the first working monolithic ICs were produced, credited to Jack Kilby (Texas Instruments) and Robert Noyce (Fairchild Semiconductor) [6]. Early 1960's witnessed the low density fabrication process with only a few transistors per chip, known as Small Scale Integration (SSI), which paved the way to the Medium Scale Integration (MSI) at the end of the decade, with a chip transistor count of 100 or more. Military and aerospace computer systems were among the first to benefit from the ICs applications. As more competitors entered the market share race, multiple bipolar IC standard logic families were pioneered, e.g., Emitter-Coupled Logic (ECL) [7], Transistor-Transistor Logic (TTL) [8]. ECL which originated in late 1950's at IBM, was the fastest logic family available (with picoseconds logic gate delays), but suffered from low noise margin and high power dissipation, i.e.,  $3 \times$  to  $10 \times$  higher than that of the TTL logic family. Patented in 1961 by James Buie (Pacific Semiconductor), TTL had the advantage of allowing for higher integration density and of being less power hungry. By the late 1960's, the TTL logic family and its successors established as the logic market share leaders for nearly 2 decades, being the impetus for the semiconductor industries evolution. In the same time, the Metal-Oxide Semiconductor Field Effect Transistor (MOSFET) entered production and in 1964, the first commercial Metal-Oxide Semiconductor (MOS) ICs appeared [6]. As a matter of fact, despite the FET principle being invented in 1926 and 1934, due to material related problems, early attempts to fabricate functioning devices were hindered for nearly 4 decades. Early commercial MOS processes employed pMOS transistors

only, which had the drawbacks of low performance and reliability, while in the 1970's the nMOS-only logic took over due to its higher speed. Intel inaugurated in 1972 the nMOS technology with the first mass-producible microprocessor (the 4-bit 4004, containing 2300 transistors on an area of only 3 by 4 millimetres, which consumed tenths of a Watt, and had a price of  $\approx 200US$ \$) [9]. Programmable intelligence was now attainable with an affordable cost, and Intel 4004 conquered the market within months after its introduction.

In the 1980's, as Very-Large-Scale Integration (VLSI) process enabled ICs to hold hundreds of thousands of transistors, power consumption aroused as a dominant issue. In this context, the MOS family won the hegemony over previous bipolar ECL and TTL logic families (though still in use today in special very high performance demanding situations, e.g., BiCMOS that combines bipolar and MOS transistors in high-speed memories, ECL successors in high frequency digital communications), mainly for the same reasons vacuum tubes were deemed inappropriate and were replaced by bipolar transistors, i.e., the high power dissipation, which imposed a hard limit on the integration density envelope. From the MOS family, the CMOS technology was widely adopted and preferred over nMOS-only and pMOS-only, mainly due to the manufacturing process simplicity and its "zero" static power consumption characteristic, becoming the dominant technology for nearly all logic applications.

Since 1970's MOS ICs integration density and performance underwent a staggering revolution as (i) transistors count per die grew exponentially, doubling roughly each and every 18 months, reaching billions of transistors in today's multi-core processors, and (ii) ICs performance had a similar evolution trend, e.g., the clock frequency of Intel's microprocessors doubled approximately every 3 years. This exponential growth was very much in line with the insightful prediction Gordon Moore (Fairchild Semiconductor) formulated in 1965, which became known as "Moore's law" and prevailed for the past 5 decades [10]. "Moore's law" was adopted as target guideline by the semiconductor companies to maintain their market position w.r.t. competitors. In 1974, Robert Dennard (IBM) formulated a corollary to the "Moore's law" [11], which states that as MOSFET transistors become smaller, they consume less power and are cheaper to manufacture. As the number of transistors per chip increased from hundreds/cm<sup>2</sup> to billions/cm<sup>2</sup>, and the cost per transistor decreased with roughly 29% per year to reach less than 0.05US\$, ICs spread to virtually all economy sectors, from defence industry, aerospace, telecommunications, power, to automotive, health, and food industries, and the semiconductor industry became a strategic driver of the global economy growth, accounting for a large percentage of the total productivity gains (e.g., close to 10% of the world Gross Domestic Product (GDP) [12]).

However, as the CMOS manufacturing process feature size continues to shrink, despite the individual transistors consuming very little power per switching, billions of them switching at very high speed and leaking as well, brought back once more a power wall to further miniaturization. Moreover, with feature size reduction, the manufacturing process becomes less precise as increasingly smaller geometries should be handled, more defects are induced, and transistors become more susceptible to various in-field failures. As a result, transistors no longer operate as expected, their

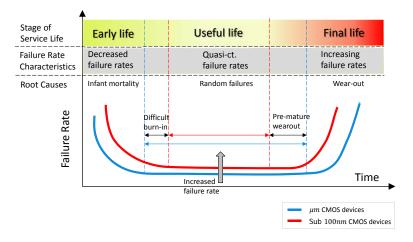

Figure 1.1: Lifetime Failure Distribution for Advanced Technology Nodes.

performance is poorer with respect to the nominal one, or they even fail altogether pre-maturely, i.e., within their intended useful life. The decreasing device reliability poses an increasing concern for current technology nodes, and can potentially become a showstopper to further CMOS scaling.

In view of the reliability wall imminence at the technology horizon, this thesis addressees nano device, circuit, and architecture reliability issues erected by the aggressive technology scaling, as subsequently detailed.

#### 1.1 ICs Reliability Trends

According to IEEE, reliability is defined as the ability of a product, in particular of an IC, to perform as intended (without failures and within intended performance envelopes) for a specified period of time (i.e., during the product lifetime). A product experiences a failure, if the service/performance delivered is not consistent with the expected datasheet service/performance.

During its lifetime, an IC can experience various failures during different life stages. Historically, the IC failure rate during its lifetime, is empirically modeled by the "bathtub" curve [13]. Figure 1.1 illustrates typical "bathtub" curves for a large population of identical and independent ICs, implemented in micro and nano technology generations, and subjected to identical stress conditions. The "bathtub" curve consists of 3 characteristic regions, as follows. During the first stage, i.e., at the beginning of ICs life, the failure rate, which is typically associated with manufacturing defects (e.g., oxide defects) is rapidly decreasing. The ICs suffering from congenital defects that escaped time-zero and yield tests are responsible for the high early life failure rate.

Stress screening (burn-in) proved to be effective in detecting and removing those infant defective ICs such that only the healthy ones, i.e., that passed the burn-in tests, are shipped to customers and enter into the second "bathtub" curve stage, i.e., the useful life, which is characterized by a small and quasi-constant failure rate. During this period, failures are random, and intrinsic to the environmental conditions (e.g., radiation, noise), manifesting themselves mostly as transient (soft) errors. Typically, reducing the in-field stress conditions to which ICs are exposed, and/or increasing the design robustness (e.g., via larger design margins) can minimize the failure rate during the ICs useful life. The third stage, i.e., the final servicing period, is characterized by a rapidly increasing failure rate, caused by accumulated wear-out (aging) of ICs' material/devices. To ensure wear-out occurs past the IC expected lifetime and not pre-maturely, and postpone its on-set as much as possible, preventive and corrective maintenance could be carried out starting from the beginning of the IC servicing life.

In time, as the technology nodes down-scale from micrometer range to nanometer range, devices are becoming less and less reliable, while the IC market demands products with higher reliability (e.g., increased yield, lower infant mortality, lower failure rate during the useful life stage of the "bathtub" curve, increased useful life span). With miniaturization, devices exhibit increasing variability in their characteristics w.r.t. nominal values, which can lead to large spreads in delay, power, and robustness, and make devices become more prone to variability and noise induced failures during their in-field usage, and it is in this landscape of increasing variability, that reliability targets must be met with viable costs.

Specifically, in the micrometer range, devices exhibit a relatively small variability of the critical physical and electrical parameters, which confer them the expected performance envelope. The traditional way for a commercial IC designer to deal with reliability concerns is to introduce higher, more conservative design guard bands (e.g., maximum operating frequency guard band of up to 20%), in order to account for the performance loss caused by in-field variability induced failures [14]. Hence, the commercial IC designer's effort and the associated area and delay overheads required to secure the targeted reliability figures of merit, are relatively small. On the contrary, for reliability critical ICs (with much more restrictive reliability targets), much more effort is involved, fault tolerant techniques being developed and in place since early times [15]. For long life, not maintained systems, dynamic recovery fault-tolerant techniques were being employed as early as the 1960's (e.g., the Self-Testing-And Repairing (STAR) computer developed at NASA for a 10-year space mission [16]). For ultra-dependable, real time applications (e.g., mass transportation, fly-by-wire avionics, nuclear power plants), fault masking via modular and hybrid redundancy (hardware replicas in different technology nodes; software fault tolerance) is commonly employed [17–19]. For systems that required high availability, such as those in telephone switching systems, or transactions processing, self-checking techniques on replicas are typically deployed [20].

As the technology aggressively downscales into the under 100 nanometer regime, as a result of various inaccuracies in the manufacturing line, of the inevitable electrical charge granularity and matter atomic scale (e.g., quantum-mechanical effects such as

**Figure 1.2:** Power Density of Intel Microprocessors.

gate direct tunneling and energy quantization of carriers become visible), etc., devices exhibit increased variability of critical parameters, thus they are not any longer able to systematically deliver their nominal expected behavior. Moreover, as the number of transistors per area unit increases, the gate oxide electric field experiences a significant increase and the power density becomes significantly higher, as illustrated in Figure 1.2, leading to very high chip temperatures. Such high temperatures and electric fields, usually encountered during burn-in screening, are now being experienced by under 100nm commercial high performance ICs (besides the reliability critical ICs) during their useful life stage, and in normal operating conditions. Thus, with each new decananometer technology node, the consequences of scaling are twofold: (i) the IC useful life is reduced, as the on-set of the final servicing life stage (i.e., the wear-out stage) is being accelerated, and (ii) the failure rate during the IC useful life is increased. This trend is graphically illustrated in Figure 1.1, by the sub 100nm red curve.

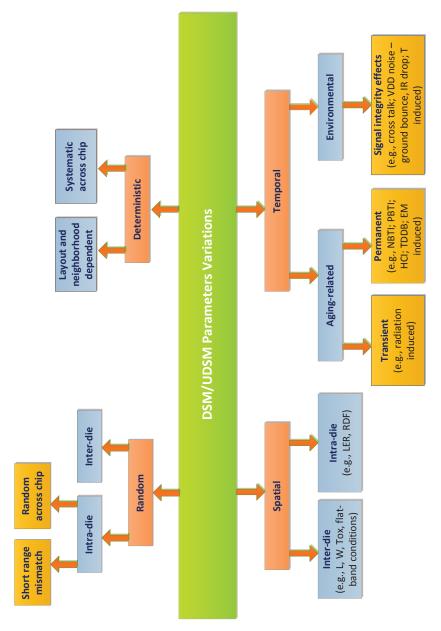

These two consequences descend from several variability sources affecting current nanoscale devices, whose taxonomy is presented in Figure 1.3. Device parameter variations can be broadly segregated into two coarse categories: spatial and temporal (lower half of Figure 1.3). The spatial process fluctuations of a device parameters, caused by manufacturing processes imperfections (manifested at time t=0 of post-Si device lifetime), can be further subdivided into die-to-die variations (e.g., fluctuations of gate width (W), length (L), oxide thickness  $(T_{ox})$ , threshold voltage  $V_{th}$ , etc.) and within-die variations (e.g., random dopant concentration, line edge irregularities), both subcategories resulting in detrimental effects such as increased delay (mean and standard deviation), thermal runaways, and increased power and leakage spread. The temporal variations caused by temperature and voltage fluctuations, as well as wear-out intrinsic mechanisms such as Negative Bias Temperature Instability (NBTI), Hot Carriers Injection (HCI), Time Dependent Dielectric Breakdown (TDDB), Electro-Migration (EM), affect critical transistors parameters (e.g., thresh-

Figure 1.3: Structured View of the Different Types of Parameters Variations.

old voltage  $V_{th}$ , transconductance  $g_m$ , linear and saturation drain current  $I_D$ ), induce abnormal delays and power dissipation, and shorten the device useful life. Another manner of categorizing variability is deterministic versus random, as depicted in the upper half of Figure 1.3. The systematic component has the advantage that is predictable, and once its influence on the transistor performance has been evaluated, it can be provisioned for in the design process, and thus completely eliminated. The random component on the other hand, can have its impact predicted only via a statistical characterization of the transistor/circuit behavior, and it is much more complex and costly to be accounted for.

As these variability sources have a higher impact on deca-nanometer than on micrometer range devices, ICs reliability targets cannot be any longer achieved solely by conservative design margins. On one hand, very large design margins would be required, which would impede attaining the maximal potential offered by the technology node and would significantly hurt performance and cost. On the other hand, due to faster device wear-out design guard bands might not be sufficient to ensure the lifetime reliability expectations. Therefore, for technology nodes < 100nm, a significant threat to attaining the manufacturing yield with a viable cost and maintaining the reliability envelopes without placing a big burden on power and performance, is posed.

Neglecting the reliability concerns at design-time, is no longer a viable approach for a highly competitive semiconductor industry which emphasizes on short timeto-market, reduced Non-Recurring Engineering (NRE) costs associated with mask spins, first-pass success, and long-term reliability goals (e.g., extended useful lifetime). Specifically, reliability ought to be integrated into the design-time flow as an additional objective (besides area, delay, and power), circuit synthesis carried along such a multi-objective optimization setup, and reliability enhancing mechanisms providing the means for reaching the reliability targets during the IC intended lifetime, integrated within the circuit functionality. Moreover, in order to meet given in-filed demands, e.g., maximum failure rate, useful life length, reliability evaluation and mitigation issues should be also dealt with during the IC useful life "bathtub" curve segment. The reliability tasks performed in one phase of the IC lifetime, are often the result of the analysis and trade-offs performed in an earlier phase; thus a robust design constitutes a reliable IC foundation that enables an effective run-time lifetime management. Furthermore, the IC reliability has to be ensured via a closed-loop process, each phase providing feedback to previous phases to enable further reliability improvements (i.e., fewer encountered defects/failures) for the next generation ICs. To this end, the knowledge of the reliability profile/history over the complete IC life cycle, can serve to prevent failure recurrence by fixing its root cause, and not merely its symptom. In consequence, a deca-nanometer dependable IC needs an integrated approach addressing the reliability challenge both up-front, at design-time (pre-Si) and at run-time (post-Si). Most of existing efforts concentrate on dispersed reliability enhancing techniques, i.e., that are suited either solely for design time, or only for run-time, and most often without interfacing compatibility and interaction between design-time and run-time. However, to be effective, the required resiliency techniques for deca-nanometer ICs should transcend multiple levels of abstraction, including device, circuit, micro-architecture, architecture, and system, and envision cross-layer cooperation for optimizing the outcome.

In view of the above discussion we conclude that a framework able to deal with IC reliability aspects in an unitary manner, is crucial for the design and realization of dependable computing platforms and in this thesis, we propose an integrated framework aiming to address the reliability issues in a systematic way, from design to run-time.

#### 1.2 Research Questions

In this section we introduce the basic principles governing the envisaged reliability aware design and life time management framework and formulate the main associated research questions addressed in this thesis. In a nutshell we propose a holistic framework, which systematically builds upon each abstraction level from device to system, and ensures inter-level operability in order to achieve a wear-out aware IC lifetime orchestration in line with user defined reliability targets and performance constraints.

The framework can be regarded as being composed out of two sub-frameworks, which inter-operate as follows: (i) the design-time sub-framework, which provides the reliability-aware adaptive architecture fabric, and (ii) the run-time sub-framework, which (a) dynamically manages the fabric wear-out profile, while fulfilling a set of user defined Quality-of-Service requirements (e.g., power lower than, throughput larger than, keep alive the key live-support components/tasks until, provide warnings if predicted time-to-failure is smaller than) based on information acquired by the fabric's network of sensors, and (b) maintain a full-life reliability log, to be fed-back to the design-time sub-framework in order to identify where most of the failures occurred and obtain hints about how to conduct the reliability aware design of the next IC generation.

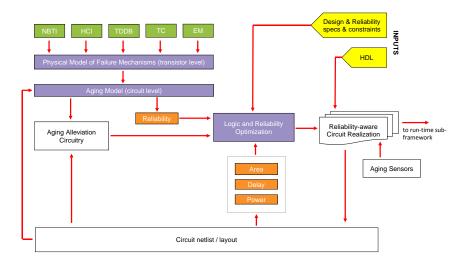

The design-time sub-framework, schematically depicted in Figure 1.4, concerns itself with the reliability optimized and lifetime manageable hardware platform design, laying the infrastructure on which the run-time sub-framework operates. Specifically, its goals are: (i) perform a 4-dimensional Design Space Exploration (DSE), in order to obtain a reliability optimized circuit realization, that is compliant with given delay, area, and power constraints, (ii) pre-characterize the reliability enhanced circuit outputs Word Error Rate (WER) for a wide range of gate error probabilities, and (iii) generate a reliability wrapper containing the hardware means that allow the run-time sub-framework to observe and control the fabric according to the QoS specifications.

The DSE is concerned with the identification of a circuit realization able to perform the targeted computation, with a maximum output Word Error Rate (WER)  $\alpha_C$  compliant with application/user defined reliability specifications, which could be much smaller than the targeted fabrication technology specific gate error rate  $\alpha_G$ , during the circuit intended lifetime. More precisely, it is not an optimum circuit realization that is being sought, but rather a realization that fulfils the reliability constraints, while minimiz-

Figure 1.4: Reliability-Aware Circuit Design Sub-Framework.

ing the other 3 design constraints (i.e., area, delay, and power intent), possibly with different priorities. The design space exploration is performed via an iterative 2-step process: (i) conduct logic synthesis, and (ii) evaluate the performance and reliability of the circuit realization obtained from (i). To evaluate the reliability of a circuit realization, the circuit is subjected to an aggression profile that is likely to be encountered at run-time, and accelerated life simulation is performed (e.g., a device 10-year useful life is shrunk down to a very short period, such that the device reliability can be investigated and dealt with during that period). Aging models are then employed in order to infer the circuit reliability after Y years of operation, and predict its remaining useful life. If the output Word Error Rate (WER) and end-of-life targets are not being met, rewriting the initial circuit function, such that a more reliable circuit realization is obtained [21], and/or designing and employing reliability enhancers, e.g., modular redundancy [22], averaging cell [23] are pursued and the entire cycle repeated until an acceptable realization is identified.

Once the reliability optimized circuit is identified it has to be evaluated for gate error rates into a neighbourhood of  $\alpha_G$ , to asses its output behaviour under various (other than the expected) aggression profiles. To this end a set of Monte Carlo simulations are required to estimate the circuit outputs WER in a 3-dimensional space, as a function of aging, temperature, and radiation, as they constitute the main sources of in-field degradation provisioned by sensors. The obtained WER surface is meant to serve as run-time reference for positioning the instantaneous WER (the WER point corresponding to the (aging, temperature, radiation) values currently sampled by the sensors), and as consequence to pursue the action deemed as the most appropriate for that particular situation.

Given that in-field ICs may have to operate under different (harsher) aggression pro-

file than the one utilized during the DSE process the real wear-out after Y years of operation may be different than the expected one. Due to this, even though the circuit was designed to provide a smaller than  $\alpha_C$  WER for its intended lifetime, it might fail to due so. To handle such situations the circuit has to be augmented with a reliability management wrapper, which creates the premises for lifetime adaptive, reliability-aware circuit management. The wrapper structure and detailed design depends on the circuit it protects but in principle it includes: (i) in-situ sensors (e.g., temperature, aging) for run-time fabric health status monitoring, (ii) mitigation/compensation mechanisms (e.g., Dynamic Frequency Voltage Scaling (DFVS), adaptive body biasing), (iii) adaptation knobs to control fabric operation regime according to the run-time sub-framework decisions, and (iv) a dedicated communication infrastructure to allow for sensor observation and knobs control.

Due to the high complexity of such an endeavour we do not target in this thesis the realization of the entire design-time sub-framework. Instead, we concentrate on its key aspects, i.e., reliability evaluation and reliability wrapper generation, as the viability of the proposed approach very much depends on the answers one can provide to the following related research questions.

In order to be able to assess the reliability of a circuit and guide the 4-dimensional (reliability, area, delay, power) DSE, models have to be devised that can project the degradation mechanisms physics to the transistor and circuit level electrical parameters. Extensive research effort - substantiated per se in the form of device parameters degradation models - was directed on understanding the physics and thermodynamics of the wear-out mechanisms [24–27]. A salient feature of existing device level aging models is that they capture the degradation dynamics of individual wear-out mechanisms [28–31]. In practice however, the devices are affected by multiple degradation mechanisms concomitantly, and their effects on the device parameters most often combine. This is also the case in the context of the proposed framework, thus the following research question arises:

• Can we derive a device-level aging model that is able to capture in an accurate enough manner and with reasonable computational effort, the combined degradation effects of multiple, concomitant aging mechanisms?

Such a model ought to be accurate enough from the aging assessment point of view, but also enable a fast enough computation, as circuits can contain thousands and hundreds of thousands of transistors. A fast reliability assessment benefits the design space exploration time required for reaching a circuit realization solution that is compliant with the circuit given performance and reliability specifications.

The next step is to determine which transistors are to be monitored for degradation, as we cannot monitor all transistors in a circuit, because of their large number. The common sense choice is to monitor only the transistors on the timing critical paths. However, a caveat of this approach is based on the observation that some transistors will degrade more than others, as a function of the input workload and environmental aggression factors they are being exposed to (e.g., temperature and supply voltage

fluctuations). The consequences are twofold: (i) a circuit path can become critical from the timing point of view, even if before it was not, as a result of its comprising transistors aging, and (ii) only a percentage of transistors on each path can significantly contribute to the circuit aging. This imposes a change of paradigm, more specifically, monitor only the transistors that could potentially cause the greatest circuit performance degradation due to their aging. Their numbers should also be as small as possible, as ultimately, the set of transistor chosen to be monitored at design-time determine the number and placement of aging sensors, which measure the amount of degradation at run-time, within the reliability wrapper. Identifying the transistors which influence the most the circuit aging and that ought to be monitored, and limiting their number, are two aspects which should be carefully considered and give shape to the following research question:

# • How to determine for a given circuit, the reduced set of transistors that are critical from the aging point of view and that should be monitored?

Having determined the critical set of transistors in a circuit and their aging status, the next step in the reliability-aware design and computing framework is to determine the overall aging status of the circuit. As was the case also with existing transistor level aging models, most of existing circuit level aging assessment approaches, concentrate either on temporal variations [32, 33] or on process variations [34, 35], disregarding the interaction between them and their corroborated degradation effects on the overall circuit. We also note that previous approaches towards circuit level aging modeling are deterministic. While a deterministic approach is computationally faster, and better suited for larger circuits, a fully probabilistic one would be more accurate and appropriate for design-time, but also more complex. We note that an increased degree of reliability assessment accuracy is desired at design-time for two main reasons: (i) the effectiveness of the entire run-time reliability-aware management depends on the 4-dimensional DSE circuit realization outcome, and on the reliability alleviation mechanisms that are built-in at design-time, and (ii) if the aging assessment accounts for the history of parameters degradation, an inaccurate evaluation an time t could multiply its error magnitude at time t+1. The transistors parameters degradation can be either remnant or only temporary if the circuit was not exposed to stresses for a longer period of time, thus assessing only the instantaneous aging evaluation might be misleading. Regarding aging not only as a function of the instantaneous degradation of certain circuit parameters, but as a function of those parameters degradation evolution in time, ought to yield a more realistic circuit end-of-life prediction during the design-time. In view of the previous argument we propose to investigate the following questions:

- For a given circuit topology, based on comprising transistors aging status, can we infer via fast deterministic means a circuit aging status, and predict its remaining useful life?

- Can we derive via fully probabilistic means a circuit aging status, such that its degradation history is taken into account?

In order to satisfy user defined reliability requirements, for a given fabrication technology and under a certain run-time aggression profiles, thus to achieve reliable computing, the 4-dimensional DSM process may have to make use of reliability enhancing circuit modifications and fault tolerant techniques into the quest for the most appropriate circuit realization. Moreover, additional fault tolerant circuitry can be embedded into the reliability wrapper and only activated when due to extreme environmental aggression profile impede the circuit in delivering a smaller than  $\alpha_C$  WER. Fault tolerant circuitry has to rely on a certain form of information, temporal, or spatial redundancy, (e.g., modular redundancy [22], averaging cell [23]), which while being effective from an error tolerance perspective, generally involves high area and/or performance impairments. Additionally, such techniques do have an Achilles' heel in the voting circuit and do not allow for fine grain tuning of the achieved WER vs. the overhead.

An alternative avenue is to investigate the potential Error Correction Codes (ECC) may have in enabling reliable computation with aged unreliable devices. This proved to be successful in protecting nanoscale memories where ECCs are frequently used to encode the to be stored data, allowing afterwards for the transient bit flips occurrences to be detected and corrected [36, 37]. For digital logic, however, the same line of thought is not directly applicable, as in this case it is not the data - the memory content - that is affected directly by errors, but it is the hardware that generates the data. The logic gates which perform the computation are affected by errors that propagate and cumulate until reaching the circuit primary outputs which are producing the to be protected data, which is raising the following research question:

Given a combinational logic circuit subjected to fault inducing conditions, can we augment the original circuit with an ECC codec able to protect the circuit primary outputs while being itself subjected to errors, such that after decoding, the correct, error-free original circuit outputs can be recovered?

The aggressive technology scaling impacts memory and logic reliability but also the one of interconnects. Moreover, while the transistors performance improves with decreasing feature size, the wires performance does not, as when the feature size shrinks, wires are getting shorter, but also narrower and taller. Their resistance and capacitance per unit length increase, which translates to increased wire propagation delay and higher power consumption. In deca-nanometer technology nodes wire delay, especially global interconnects delay, has become a major limitation of high performance ICs timing characteristics, often being more dominant than the transistors switching delay. Additionally, due to their larger capacitance, interconnects have become the dominant source of power dissipation for contemporary IC designs, surpassing the gate and diffusion capacitances power [38]. Another harmful interconnects scaling consequence is that the capacitive and inductive coupling noise between adjacent wires is becoming more prominent and can severely impact the signals integrity and propagation delay. The technology scaling induced parameters variations, as exemplified in Figure 1.3, affect the reliability of data transport over wires, resulting in erro-

neous data transmission and contributing to a poorer performance of the interconnect and its signalling circuit. In order to deliver against the reliability and performance envelopes when transmitting data across a chip, reliability enhancing circuitry, generated by the design-time framework should be envisaged. To this end, we propose to investigate coding schemes that encode the data prior to its transmission over the wires, able to reduce the switching activity as well as the crosstalk-inducing coupling transitions between adjacent wires. A balance has to be found between codec complexity and the facilitated transmission energy reduction, such that the codec energy consumption does not nullify the transmission energy reduction. In this context, we pose the question:

#### Can we devise energy efficient and reliable data transport via an unreliable medium?

At the crux of the reliability wrapper reside the aging sensors (and their associated communication infrastructure) as their accuracy and operating principle have an essential impact on the lifetime reliability management platform performance and associated overhead. Past approaches towards aging sensor designs [39–43], rely on indirect measurements, i.e., the to be monitored devices are replicated and then exposed to the same stress as the ones that part take into the computations, and typically employ as aging quantifier a low level device parameter, e.g., transistor threshold voltage  $V_{th}$ . These sensors use a performance comparison between stressed and fresh (unaged) devices in order to get the aging information. As a result, existing approaches to sensor designs, while having the advantage of non-intrusiveness (i.e., non-interfering with the circuit operation), rely on an indirect wear-out assessment, which by its very nature is less accurate than a direct one. Additionally, it would be desirable for the aging monitor to be an easier to measure electrical quantity (e.g., device voltage, current). This would decrease the complexity of the previous sensors approaches, which use as aging monitors transistor's internal parameters such as the threshold voltage, or the carriers mobility, which are not easily measurable. A direct measurement is also expected to improve the aging assessment quality, which is very important, as the effectiveness of the run-time reliability aware adopted policy greatly depends on the accuracy of the sensed aging data. The next research question thus formulates as:

### • Can we design cost effective aging sensors that provide a direct measurement of amalgamated wear-out effects?

Thus far, we discussed the design-time sub-framework and the associated research questions we address in this thesis. We note that other design-time sub-framework related open issues exists, e.g., How to efficiently perform the 4-dimensional DSE?, but we concentrated on what we consider as being the enablers for the proposed framework.

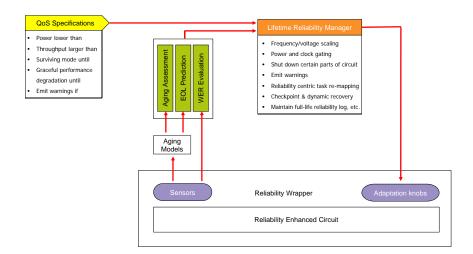

As mentioned in the section opening, the reliability optimized circuit realization and the associated reliability wrapper generated by the design-time sub-framework constitute the foundation on which the run-time sub-framework, schematically depicted

Figure 1.5: Dynamic Lifetime Resources Management Framework.

in Figure 1.5, operates. The run-time sub-framework concerns with two main functions: (i) evaluate circuit outputs WER and based on past and current raw sensors data, assesses the current circuit health and predicts its remaining useful life span, and (ii) reasons about adopting a particular reliability management strategy if the assessed circuit reliability is not compliant with the QoS specifications. We note that, in potential practical implementations the run-time sub-framework goes beyond reliability management only and deals with other QoS specifications, e.g., latency, throughput, power, too. Given that power and performance evaluation is out of this thesis scope we only discuss on the sequel the run-time sub-framework modus operandi solely from the reliability standpoint and note that it can in principle interoperate and potentially (partially) share infrastructure with state of the art performance targeted resource management platforms [44–46].

Specifically, the temperature and aging in-situ sensors that are part of the design-time reliability wrapper infrastructure sample in a quasi-continuous manner the circuit state. The collected raw sensor data are subsequently process by aging models to infer the circuit current aging status and predict its End-of-Life (EOL), based on current and possibly past sensor readings. Moreover, the actual circuit WER is assessed by identifying the circuit operation position, on the design-time pre-characterized WER surface, corresponding to the (aging, temperature, radiation) instantaneous values sampled by sensors. In this way we capture the actual position of the circuit within the reliability "bathtub" framework both in terms of age and failure rate and derive the appropriate reliability management policy. In accordance with circuit reliability status compliance with the user-defined QoS requirements (e.g., WER smaller than, emit warnings if EOL earlier than, surviving mode when, graceful performance degradation when), the operation scenario (i.e., power supply, frequency, mitigation means) best-suited for the current circuit status is determined and put in place by means of

the adaptation knobs. For instance, if the delivered circuit outputs WER is bigger than the QoS specified acceptable error rate  $\alpha_C$ , corrective actions which are changing the circuit operation mode (e.g., less workload, lower frequency, activate additional reliability circuitry) can be undertaken such that QoS acceptable WER figures are reached. On the contrary if WER is too low measures can be taken, e.g., power done reliability enhancers, in order to save energy while still fulfilling the QoS requirements.

If current wear-out is visibly reflected in the circuit behaviour such that (some) QoS constraints are violated, the voltage/frequency can be dynamically adapted in order to lessen the stress on the most affected parts of the circuit, or reliability-centric task re-mapping can be performed, such that less workload is distributed to the components which are most affected by aging. Resources which have pre-maturely aged, or permanently failed, can shift the course of action on surviving mode, i.e., only application life support functionality is provided by solely performing its essential tasks. Graceful performance degradation can come into play when certain circuit resources are either defective of highly faulty, in which case their tasks are relocated to other parts of the circuit which are functional, allowing the overall circuit to perform all expected tasks, but with a lower performance (e.g., slower, lower throughput, higher energy consumption). If the degradation corrective measures are not effective and certain degradation thresholds are being reached, warnings are emitted prompting for user intervention for further actions. Once a line of action has been determined, it is physically enforced via the design-time reliability wrapper knobs that control the circuitry responsible with e.g., voltage/frequency scaling, reliability enhancing circuits, e.g., TMR, and aging mitigation/compensation.

In this thesis, as previously mentioned, we only focus on the run-time framework part dedicated to the transformation of the raw data, acquired from aging and temperature sensors, into meaningful circuit/platform level wear-out information. This step is essential as the runtime reliability management paradigm decisions and actions builds upon its outcome. In order to assess the circuit aging and predict its remaining useful life span, the sensors information has to integrated via an aging model. Sensor measurements are typically noisy, as a result of various measurement imperfections, environmental disturbances, their own aging, etc. Existing literature assumes ideal measurement conditions [41–43] and do not take into account the impreciseness of the sensors measurements, which can lead to either circuit aging status overestimation or underestimation, and further to too restrictive, or less effective reliability mitigation/compensation measures. Thus, different from the design-time aging models, the run-time aging models ought to account for the uncertainty of the sensors measurements when deriving the overall circuit aging status and predict its end-of-life. Thus, the next research question to investigate can be formulated as follows:

How to integrate the noisy aging sensors measurements in a comprehensive manner in order to assess a circuit instantaneous aging status and predict its end-of-life?

In answering the above 8 research questions, this thesis investigates reliability-aware design and dependable computing and data transport techniques in order to deliver

against the reliability envelopes of current technology nodes. Specifically, as presented in the next Section, we investigate, propose, and evaluate technique for (i) the design of reliability enhanced circuits and their enveloping reliability wrappers (sensors, communication infrastructure, and adaptive control mechanisms), and (ii) sensor data based reliability assessment for an effective in-field lifetime reliability management, in compliance with user defined QoS specifications.

#### 1.3 Thesis Contributions

Subsequently, we summarize the contributions we made towards the potential realization of the proposed reliability aware design and life time management framework, as follows:

- We propose a design-time transistor level aging assessment and End-of-Life prediction model that uses the transistor output signal slope as aging quantifier, and can capture the amalgamated effects of the NBTI, HCI, and TDDB aging mechanisms. The model accounts for the intrinsic degradation of transistor's own parameters (e.g.,  $V_{th}$ ), which are ultimately reflected in the transistors's output voltage slope degradation. Moreover, it is also able to take into consideration the influence of the surrounding circuit topology via: (i) the slope degradation of the surrounding environment current contribution, which reflects the impact of the aging of neighbouring transistors connected to the source terminal of the transistor whose aging we assess, and (ii) the slope degradation of the transistor's gate voltage, which reflects the impact of the aging of the driver transistors. We define the transistor age as the time integral of the sum of output voltage slope variations caused by the aging induced drift of its intrinsic/extrinsic parameters. A NOR-2 gate implemented in TSMC 65nm CMOS technology is considered as test vehicle, and exposed to NBTI and HCI stress, for a temperature range of  $25^{\circ}-175^{\circ}$  C. Compared against the Cadence simulation, we obtain a fairly small estimation error of the output voltage slope (mean < 10% and standard deviation < 5%), which confirms the feasibility and potential of the proposed approach. Since PMOS transistors typically suffer more degradation than the NMOS counterparts, we consider the lower PMOS transistor in the NOR-2 gate, and evaluate the amount of degradation induced by: (i) only its intrinsic aging (which is the typical employed method), and (ii) both intrinsic and extrinsic (from the neighbours) aging, as proposed in our model. Simulation results reveal that if only intrinsic degradations are considered the PMOS transistor aging is underestimated by 4%-7%, when compared with the case when both the intrinsic and extrinsic aging are taken into account, which quantitatively proves that our model provides a better insight into the aging assessment issue.

- We introduce a model able to infer circuit aging based on the aging of com-

prising transistors. Specifically, we propose to predict the circuit End-Of-Life (EOL) as a sum of the critical transistors individual EOL values, weighted by circuit topology dependent coefficients that are fixed at design-time via a multi-response regression approach. Given that abstracting the circuit level aging status from the aging of all its component transistors is not an option for non-toy circuits we further propose a methodology to select a reduced set of circuit transistors, i.e., those which are critical from the aging point of view, based on whose degradation circuit aging assessment becomes computationally tractable. To this end, we identify the circuit paths which are critical from the aging point of view, i.e., the paths whose aging induced degraded performance violates their un-aged timing requirements. In view of the fact that from each such aging critical path, only a small percentage of transistors could potentially cause the greatest extent of damage we introduce a method to identify and select those as constituents of an aging critical transistors kernel. The transistors thus selected are the ones to have their aging monitored, and used to infer the aging of the overall circuit via the proposed topology dependent circuit-level model. When applied on the ISCAS-85 c499 circuit implemented in PTM 45nm CMOS technology our approach identified a 15 critical transistors kernel out of a total of 1526 transistors, which greatly benefits from the standpoints of wear-out measurements sites (the number of aging sensors) reduction and circuit aging derivation tractability. When inferring the circuit age with the proposed model based on the 15 identified critical transistors, we obtain a small circuit aging approximation error (mean < 15% and standard deviation < 6%) w.r.t. the reference circuit aging obtained by means of Cadence simulation, which quantitatively confirms the evaluation accuracy of our approach. When reducing the number of sensors by 2/3, i.e., only 5 transistors out of the kernel of 15 are utilized for aging evaluation, the EOL estimation accuracy is diminished with 18% (reported relative to the estimation accuracy achieved by employing the entire kernel of 15 critical transistors), which indicate that trade-offs between area overhead and EOL estimation accuracy are possible, the lifetime prediction being kept within reasonable bounds. The proposed circuit aging assessment approach is deterministic and fast, and requires a minimum number of in-field aging sensors (to monitor the circuit kernel of critical transistors), which makes it a good candidate for run-time aging evaluation.

• We propose a fully probabilistic circuit level aging model which regards age not only as a function of the instantaneous degradation, but also of past degradation. To this end we introduce a probabilistic model that allows the circuit performance (e.g., clock frequency) to vary in time, and has a Markovian character (the age being expressed as a function of the degradation parameters values at the current sampling moment and the ones from the previous sampling moments), as opposed to the traditional deterministic approach, which considers a fixed performance boundary and includes only the current sampling moment degradation values when inferring the age. In this way, we account