### A 1.2mW/channel 100m-Pitch-Matched Transceiver ASIC with Boxcar-Integration-Based RX Micro-Beamformer for High-Resolution 3D Ultrasound Imaging

Guo, Peng; Fool, Fabian; Noothout, Emile; Chang, Zu-Yao; Vos, Hendrik J.; Bosch, Johan G.; Verweij, Martin D.; de Jong, Nico; Pertijs, Michiel

DOI

10.1109/ISSCC42614.2022.9731784

Publication date

2022

**Document Version**Final published version

Published in

2022 IEEE International Solid-State Circuits Conference, ISSCC 2022

Citation (APA)

Guo, P., Fool, F., Noothout, E., Chang, Z.-Y., Vos, H. J., Bosch, J. G., Verweij, M. D., de Jong, N., & Pertijs, M. (2022). A 1.2mW/channel 100m-Pitch-Matched Transceiver ASIC with Boxcar-Integration-Based RX Micro-Beamformer for High-Resolution 3D Ultrasound Imaging. In L. C. Fujino (Ed.), 2022 IEEE International Solid-State Circuits Conference, ISSCC 2022: Digest of technical papers (pp. 496-498). Article 9731784 (Digest of Technical Papers - IEEE International Solid-State Circuits Conference; Vol. 2022-February). IEEE. https://doi.org/10.1109/ISSCC42614.2022.9731784

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

## 32.3 A 1.2mW/channel 100µm-Pitch-Matched Transceiver ASIC with Boxcar-Integration-Based RX Micro-Beamformer for High-Resolution 3D Ultrasound Imaging

Peng Guo¹, Fabian Fool¹, Emile Noothout¹, Zu-Yao Chang¹, Hendrik J. Vos¹², Johan G. Bosch², Martin D. Verweij¹², Nico de Jong¹², Michiel A. P. Pertijs¹

<sup>1</sup>Delft University of Technology, Delft, The Netherlands <sup>2</sup>Erasmus MC, Rotterdam, The Netherlands

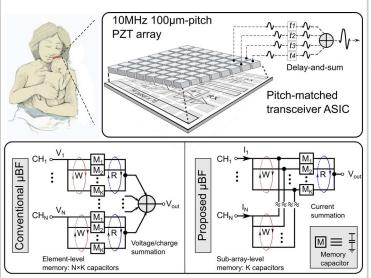

The integration of 2D ultrasonic transducer arrays and pitch-matched ASICs has enabled the realization of various 3D ultrasound imaging devices in recent years [1-3]. As applications such as 3D intravascular ultrasonography, intra-cardiac echocardiography, and trans-fontanelle ultrasonography call for miniaturization and improved spatial resolution, higher-frequency transducers (>5MHz) with a correspondingly smaller array pitch (<150 m) are needed. Such devices generally employ a large number of transducer elements, calling for channel-count reduction in the ASIC while meeting stringent restrictions on per-element power consumption and die area. Micro-beamforming (μBF) is an effective way of reducing channel count by performing a delay-and-sum operation on the echo signals received within a sub-array [1]. However, prior μBF implementations the employ per-element capacitive memory to realize the delay [1,2], making it increasingly difficult to apply μBF in smaller-pitch arrays.

This paper presents a  $\mu$ BF architecture that employs current-mode summation and boxcar integration to realize delay-and-sum on an N-element sub-array using N fewer capacitive memory elements than conventional  $\mu$ BF implementations. This facilitates the use of  $\mu$ BF in smaller-pitch applications, as demonstrated by a prototype transceiver ASIC targeting a wearable ultrasound device that monitors brain perfusion in preterm infants via the fontanel (Fig. 32.3.1). To meet its strict spatial resolution requirements, a 10MHz 100 $\mu$ m-pitch piezoelectric transducer array is employed, leading to a per-element die area >2 $\square$  smaller than prior designs employing  $\mu$ BF [1-3].

Conventional  $\mu$ BF implementations [1,2] sample the echo signals V<sub>1..N</sub> from the sub-array elements and store the last *K* samples for each element, thus requiring *K* capacitive memory cells per element (Fig. 32.3.1). These stored values are then read out after a programmable time delay and added in the voltage- or charge-domain to implement the delay-and-sum operation. The proposed  $\mu$ BF, in contrast, operates on current-mode input signals I<sub>1..N</sub>, and successively connects these to a set of *K* memory cells. These collect charge representing the upcoming *K* output samples, allowing summation to take place in the current domain at their input. The delay associated with an individual input is set by the delay between the connection of that input to a memory cell, and the moment that the memory cell connects to the output. This architecture reduces the number of memory cells by a factor of *N* compared to conventional  $\mu$ BFs [1,2]. In contrast with prior current-mode  $\mu$ BFs, which either employ per-channel delay lines [4] or explicit per-thannel S/H stages [5], the signal currents are directly integrated on the memory capacitors, realizing boxcar integration that provides inherent anti-alias filtering and obviates the need for such filtering in the analog front-end (AFE), thus further reducing die size.

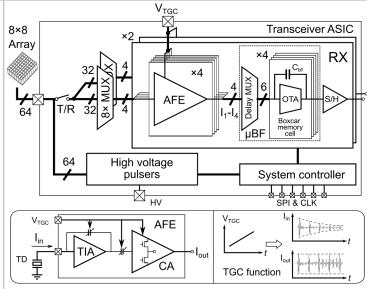

Figure 32.3.2 shows a block diagram of the prototype ASIC interfacing with an  $8\times 8$  transducer array. Element-level high-voltage (HV) pulsers allow all elements to contribute to acoustic pulse transmission (TX), with the ability to define time delays at the row- or column-level to steer the resulting TX beam to different angles. For echo reception (RX), the array is divided into sub-arrays of  $2\times 2$  elements. After TX, HV T/R switches and multiplexers connect two of these sub-arrays to the receive (RX) circuitry. The signal currents from the elements of the selected sub-arrays are amplified by 4 AFEs and then fed, via multiplexers that set the element delays, to 4 memory cells, implemented as active boxcar integrators to improve linearity compared to a passive integrator. Output sample-and-hold (S/H) stages drive the  $\mu BF$  outputs off chip.

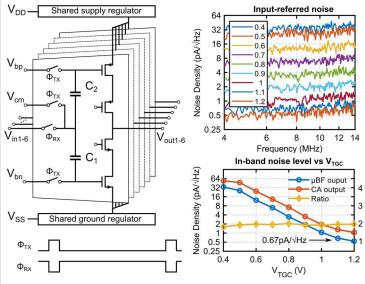

The AFEs are based on the design presented in [6] and consist of a capacitive-feedback transimpedance amplifier (TIA), the output of which is capacitively coupled to the input of a current amplifier (CA). The CA provides a high-Z output to drive the boxcar integrator in the  $\mu$ BF with an amplified version of the transducer's signal current. The AFE's gain can be continuously controlled in a range of 36dB by an external voltage  $V_{TGC}$  to provide time-gain compensation, i.e., to compensate for the stronger attenuation of echoes that arrive later. The AFE provides less than  $\pm 0.4$ dB gain error and has a 1.31pA/ $\sqrt{Hz}$  inputing referred noise density within 6 to 14MHz bandwidth at its maximum gain ( $V_{TGC} = 1.1$ V).

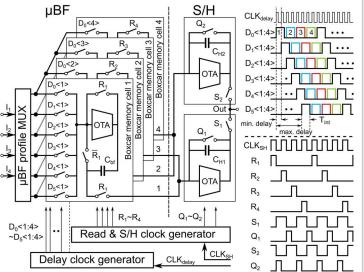

Figure 32.3.3 shows the detailed implementation of the  $\mu$ BF. To set the delay profile, each of the input currents I<sub>1.4</sub> is connected to one of 6 summation nodes, which correspond to 6 possible delay steps. These 6 summation nodes are cyclically connected to the 4 boxcar integrators, orchestrated by an 80MHz delay clock CLK<sub>delay</sub>. The active

boxcar integrators alternate between integration ( $R_i = 0$ ) and readout ( $R_i = 1$ ) phases. During the latter, the accumulated charge is transferred to one of two S/H stages, which operate in a ping-pong fashion and alternately drive the output, controlled by a 40MHz clock  $CLK_{SH}$ . While  $CLK_{delay}$  sets the minimum delay step to 12.5ns and the delay range to 62.5ns,  $CLK_{SH}$ , independently, sets the output sampling period to 25ns. The boxcar integration time is 25ns to provide effective anti-alias filtering.

The OTAs in the boxcar integrators and S/H stages are implemented using inverter-based amplifiers (Fig. 32.3.4) with current-reuse supply- and ground-regulators that suppress interference and are shared at the sub-array level to save area. Two capacitive level shifters  $(C_1/C_2)$  are used to enlarge the dynamic range of the OTAs. These are reset during the TX period  $(\Phi_{TX})$  and hold the DC bias points during the RX period  $(\Phi_{DX})$ .

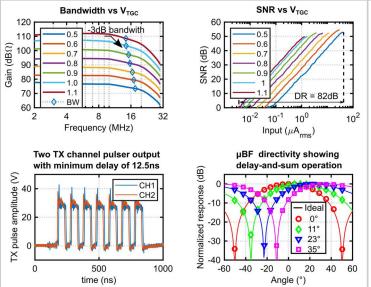

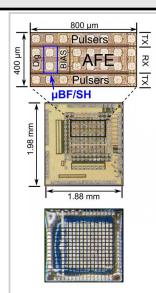

The ASIC has been fabricated in a 180nm BCD process (Fig. 32.3.7) and consumes 1.2mW/channel, of which 0.8mW is consumed by the AFE and 0.33mW by the  $\mu$ BF, while the 30V TX consumes 32 $\mu$ W/channel at a pulse repetition frequency of 10kHz. Figure 32.3.4 shows the input-referred noise at the  $\mu$ BF's output (Fig. 32.3.4) for different TGC control voltages (V<sub>TGC</sub>). At the highest gain, it achieves 0.67pA/\Hz, which is close to half of the input-referred noise (1.31pA/\Hz) of a single-channel AFE measured at CA's output. This factor is in line with the  $\sqrt{N}=2$  noise reduction expected from a  $\mu$ BF without noticeable noise-folding effects and is maintained across the full gain range (Fig. 32.3.4). The gain of the full signal chain at 7 different TGC levels (Fig. 32.3.5) shows a minimum -3dB bandwidth of 14.7MHz at  $V_c=1.1V$ . A measurement of SNR vs. input current shows a peak SNR of 54dB, and an 82dB dynamic range. An accurate delay-and-sum operation is demonstrated by applying time-shifted sinusoidal inputs to the chip, thus emulating acoustic inputs arriving at different angles, and comparing the  $\mu$ BF response with the ideal expected directivity for different  $\mu$ BF delay settings. The HV pulsers successfully produce 30V pulses with a delay resolution of 12.5ns.

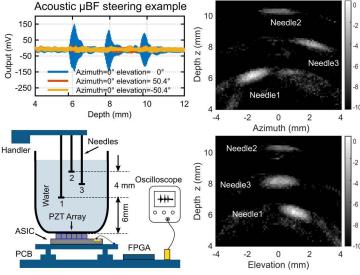

Acoustic characterization is done on a prototype with transducer array built on top as shown in Fig. 32.3.7. A small water tank was mounted on top of the chip, with 3 needle reflectors positioned at about 8mm from the transducer surface (Fig. 32.3.6). For TX, 3-cycle 30V pulses were used. The  $\mu BFs$  were steered to different angles and the amplitude of the received echo signals increases as the  $\mu BF$  steered towards the reflectors. A B-mode image clearly shows the needles positions even with the small aperture size  $(0.8 \times 0.8 mm^2)$ .

A comparison with prior  $\mu$ BF ASIC designs with pitch-matched 2D arrays (Fig. 32.3.7) shows that this work achieves the smallest array pitch, the highest center frequency, and the smallest  $\mu$ BF area per channel, making the  $\mu$ BF architecture a promising solution for channel-count reduction in next-generation small-pitch 3D ultrasound imaging devices.

#### Acknowledgement:

This work is part of the MIFFY project (#15293) funded by the Open Technology Programme of the Dutch Research Council NWO.

#### References:

- [1] C. Chen, et al., "A Pitch-Matched Front-End ASIC With Integrated Subarray Beamforming ADC for Miniature 3-D Ultrasound Probes," *IEEE JSSC*, vol. 53, no. 11, pp. 3050–3064, Nov. 2018.

- [2] Y. Igarashi, et al., "Single-Chip 3072-Element-Channel Transceiver/ 128-Subarray-Channel 2-D Array IC With Analog RX and All-Digital TX Beamformer for Echocardiography," *IEEE JSSC*, vol. 54, no. 9, pp. 2555–2567, Sept. 2019.

- [3] M.-C. Chen, et al., "A Pixel Pitch-Matched Ultrasound Receiver for 3-D Photoacoustic Imaging with Integrated Delta-Sigma Beamformer in 28-nm UTBB FD-SOI," *IEEE JSSC*, vol. 52, no. 11, pp. 2843–2856, Nov. 2017.

- [4] B. Stefanelli, et al., "An Analog Beam-Forming Circuit for Ultrasound Imaging Using Switched-Current Delay Lines," *IEEE JSSC*, vol. 35, no. 2, pp. 202–211, Feb. 2000.

- [5] J.-Y. Um, 'Current-Mode Ultrasound Beamformer with Multiple-Input-Sequential-Output Memory Structure', *IET Electronics Letters*, vol. 54, no. 9, pp. 545–546, May 2018

- [6] P. Guo, et al., "A Pitch-Matched Analog Front-End with Continuous Time-Gain Compensation for High-Density Ultrasound Transducer Arrays," *ESSCIRC*, pp. 163–166, Sept. 2021.

Figure 32.3.1: Overview of the ASIC for trans-fontanelle echography and comparison Figure 32.3.2: ASIC architecture with an inset showing the continuous-time timebetween conventional and proposed micro-beamforming.

Figure 32.3.3: Circuit diagram of the boxcar-integration  $\mu$ -beamformer, the pingpong S/H and their timing details.

TX pulser and  $\mu$ -beamforming directivity.

gain-compensation AFE.

Figure 32.3.4: Inverter-based amplifiers, measured input-referred noise of the  $\mu BF$

Figure 32.3.5: Measured signal-chain bandwidth, signal-to-noise ratio, high-voltage Figure 32.3.6: Acoustic beam-steering example, acoustic measurement setup and B-mode images.

#### **ISSCC 2022 PAPER CONTINUATIONS**

Comparison with state-of-the-art pitch-matched micro-beamformer circuits for 2D arrays

| micro-beamformer circuits for 2D arrays |                         |                        |                      |                        |

|-----------------------------------------|-------------------------|------------------------|----------------------|------------------------|

|                                         | This work               | [1]                    | [2]                  | [3]                    |

| uBF type                                | Boxcar Int.             | Voltage S/H            | Voltage S/H          | ADC+FIFO               |

| Process                                 | 180nm BCD               | 180nm                  | 180nm SOI            | 28nm                   |

| Sub-array size                          | 2 × 2                   | 3 × 3                  | 4 × 6                | 4 × 4                  |

| Transducer type                         | PZT                     | PZT                    | PZT                  | CMUT                   |

| Pitch                                   | 100 µm                  | 150 µm                 | 300 µm               | 250 µm                 |

| Center freq.                            | 10 MHz                  | 5 MHz                  | < 5 MHz              | 5 MHz                  |

| Sampling rate                           | 40 MS/s                 | 30 MS/s                | 40 MS/s              | 20 MS/s                |

| Delay resolution                        | 12.5 ns                 | 33 ns                  | 25 ns                | 8.33 ns                |

| uBF area/ch.                            | 0.005 mm <sup>2</sup> * | 0.011 mm <sup>2†</sup> | 0.03 mm <sup>2</sup> | 0.041 mm <sup>2§</sup> |

| uBF power/ch.                           | 0.33 mW *               | 0.17 mW <sup>†</sup>   | 0.19 mW              | 17.5 mW §              |

| AFE type                                | LNA with TGC            | LNA + PGA              | LNA + PGA            | LNA + PGA              |

| RX area/ch.                             | 0.04 mm <sup>2</sup>    | 0.026 mm <sup>2</sup>  | 0.09 mm <sup>2</sup> | 0.088 mm <sup>2</sup>  |

| RX power/ch.                            | 1.17 mW                 | 0.91 mW <sup>†</sup>   | 0.43 mW              | 33 mW §                |

| Peak SNR                                | 54 dB                   | 51.8 dB                | n/a                  | 59.9 dB                |

| Input DR                                | 82 dB                   | 85 dB                  | 85 dB                | n/a                    |

| Includes TX                             | Υ                       | N                      | Υ                    | N                      |

| TX voltage                              | 30 V                    | *                      | 138 V                | 8                      |

<sup>\*</sup>includes S/H stage; † includes sub-array ADC;

Figure 32.3.7: Micrograph of the ASIC and prototype with transducers on top, and comparison with the state of the art.

<sup>§</sup>includes element-level ADC