# Testing Computation-in-Memory Architectures Based on Emerging Memories

by

## Surya Nagarajan

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Thursday November 28, 2019 at 13:30

Student number:4743385Thesis number:Q&CE-CE-MS-2019-21Project duration:December 1, 2018 – November 28, 2019Thesis committee:Prof. dr. ir. S. HamdiouiTU Delft, supervisorDr. ir. M. Taouil,TU DelftDr. ir. T. G. R. M. van Leuken,TU DelftIr. M. C. R. FiebackTU Delft

An electronic version of this thesis is available at http://repository.tudelft.nl/.

## Abstract

Many alternative computer architectures that use emerging devices are under investigation to address the challenges current architectures and technologies face. Computation-in-memory (CIM) architectures are one among these alternative that tries to solve these challenges by performing computations in the memory structure as opposed to transferring the data to a central processing unit.One class of these CIM architectures employs memristive devices. These are non-volatile devices that store data as a resistance, and are highly compatible with traditional CMOS process. Many research centers and companies are prototyping such architectures. Efficient and high-quality test solutions are required for these architectures, which is the subject of this thesis.

This thesis presents a methodology for testing any CIM architecture, focusing on their memory and computation configurations, and applies this methodology to an existing CIM architecture as an example. The configurations are tested in the mentioned order for maximum fault coverage, while minimizing test development complexity. The testing method is structural rather than functional, thereby maximizing and guaranteeing fault coverage. To create accurate tests, device-aware testing is employed to model these defective devices. As a case study, the methodology is applied to scouting logic, a bit-wise logic CIM architecture that performs operations on data stored in memristors. Defects in the memory array as well as in the peripheral circuitry were injected and simulated to obtain realistic faults. The resultant fault analysis shows that there exist faults that are unique to the computation configuration and are not observed in the memory configuration. This implies that testing a CIM architecture only as a memory will lead to test escapes. Hence, the proposed test solution tests both the memory and computation configuration, and detects all faults.

## Acknowledgements

I would like to thank Prof. Said Hamdioui, my supervising professor for this thesis for his constant monitoring and support. I learnt a good deal about getting presenting topics with clarity and asking the right questions, which would automatically steer the direction of research in any case. Second, I would like to thank my daily supervisor Moritz Fieback who guided me through this thesis. I enjoyed the numerous discussion sessions, which made the learning process quite fruitful. I would also like to thank Mehdi Tahoori and Rajendra Bishnoi for their feedback during the implementation of this work.

Next, I would like to thank my friends who have been with me through thick and thin. They had made my two years in Netherlands memorable, even though they might not have been here in person. In particular, I would like to thank Prajish, Anand and Gautham for being my roommates and making me feel less homesick on a daily basis. I would also like to thank Pradeep, Abhairaj, Manasa and Siddharth for being there at the 9th floor when everything went down. A special thanks to San and Prithvi for their constant support and love. Even though they live far away, M.A.S.S. and PROMICE had provided me constant support and I am grateful for knowing them.

I will always be grateful for my family, for without their constant support and motivation I do not see myself in the position I am.

Last but not least, I would like to thank caffeine, adrenaline, Kanye West and heavy metal music for existing.

Thank you!

Surya Nagarajan Delft, November 2019

## Contents

| Lis | st of I            | Figures                                                        | xi   |

|-----|--------------------|----------------------------------------------------------------|------|

| Lis | st of <sup>-</sup> | Tables                                                         | xiii |

| Lis | st of <i>i</i>     | Abbreviations                                                  | xix  |

| 1   | Intr               | roduction                                                      | 1    |

|     | 1.1                | Motivation                                                     | 1    |

|     | 1.2                | Need for high quality test                                     | 5    |

|     | 1.3                | State of the art in CIM Testing                                | 6    |

|     | 1.4                | Contributions                                                  | 6    |

|     |                    | 1.4.1 Discussion of Test approach for CIM architectures        | 6    |

|     |                    | 1.4.2 Systematic Approach for Testing CIM Architectures        | 6    |

|     |                    | 1.4.3 Application of systemic approach to Scouting Logic       | 7    |

|     |                    | 1.4.4 Simulation Setup for Test Development for Scouting logic | 7    |

|     |                    | 1.4.5 Publications                                             | 7    |

|     | 1.5                | Organization                                                   | 7    |

| 2   | Me                 | mristor based CIM                                              | 9    |

|     | 2.1                | CIM Introduction.                                              | 9    |

|     | 2.2                | Classification of CIM                                          | 11   |

|     | 2.3                | Memristor Cell                                                 | 12   |

|     |                    | 2.3.1 STT-MRAM                                                 | 13   |

|     |                    | 2.3.2 PCRAM                                                    | 13   |

|     |                    | 2.3.3 ReRAM                                                    | 14   |

|     |                    | 2.3.4 Memristor Array Architecture                             | 16   |

|     |                    | 2.3.5 Production of ReRAM Devices                              | 17   |

| 3   | CIM                | / Architecture Testing                                         | 19   |

|     | 3.1                | Introduction                                                   | 19   |

|     | 3.2                | Test Methods                                                   | 20   |

|     |                    | 3.2.1 Functional Testing                                       | 20   |

|     |                    | 3.2.2 Structural testing                                       | 20   |

|   | 3.3  | Memo     | pry Testing                                                  | 21  |

|---|------|----------|--------------------------------------------------------------|-----|

|   |      | 3.3.1    | Defects                                                      | 21  |

|   |      | 3.3.2    | Faults                                                       | 23  |

|   |      | 3.3.3    | Testing                                                      | 27  |

|   | 3.4  | CIM te   | est methodology                                              | 29  |

|   |      | 3.4.1    | Testing in Memory Configuration                              | 29  |

|   |      | 3.4.2    | Testing in Computation Configuration                         | 29  |

|   |      | 3.4.3    | Scouting Logic                                               | 29  |

| 4 | Def  | ect and  | Fault modelling for Scouting Logic based CIM Architectures   | 31  |

|   | 4.1  | Circui   | t Setup                                                      | 31  |

|   | 4.2  | Defect   | t modeling                                                   | 35  |

|   |      | 4.2.1    | Defect modeling for memory configuration                     | 36  |

|   |      | 4.2.2    | Defect modeling in computation configuration                 | 37  |

|   |      | 4.2.3    | Defect Injection.                                            | 37  |

|   |      | 4.2.4    | Experimental Setup                                           | 38  |

|   | 4.3  | Fault I  | Modeling and Analysis                                        | 39  |

|   |      | 4.3.1    | Fault Modeling and Analysis for Memory Configuration         | 39  |

|   |      | 4.3.2    | Fault modeling and Analysis for Computation configuration    | 61  |

| 5 | Test | ts for S | couting Logic                                                | 87  |

|   | 5.1  | Tests i  | n Memory Configuration                                       | 87  |

|   |      | 5.1.1    | Memory array.                                                | 87  |

|   |      | 5.1.2    | Address Decoder                                              | 88  |

|   |      | 5.1.3    | Sense Amplifier                                              | 89  |

|   |      | 5.1.4    | Test Sequences for Memory Configuration                      | 90  |

|   | 5.2  | Tests i  | n Computation configuration                                  | 92  |

|   |      | 5.2.1    | Memory Array.                                                | 92  |

|   |      | 5.2.2    | Address Decoder                                              | 93  |

|   |      | 5.2.3    | Sense Amplifier                                              | 93  |

| 6 | Cor  | nclusio  | ns                                                           | 99  |

|   | 6.1  | Summ     | nary                                                         | 99  |

|   | 6.2  |          | ssions                                                       | 100 |

|   | 6.3  |          | e Research                                                   | 101 |

| А | Test | ting Sco | outing Logic-Based Computation-in-Memory Architectures       | 103 |

| В |      |          | mputation-in-Memory Architectures Based on Emerging Memories | 111 |

| Contents                                                       |     |

|----------------------------------------------------------------|-----|

| C Rebooting Computing: The Challenges for Test and Reliability | 123 |

| Bibliography                                                   | 131 |

## List of Figures

| 1.1  | Reliability Wall                        | 2  |

|------|-----------------------------------------|----|

| 1.2  | Leakage Wall                            | 2  |

| 1.3  | Cost Wall                               | 3  |

| 1.4  | Memory Wall [33]                        | 4  |

| 1.5  | Leakage Wall [68]                       | 4  |

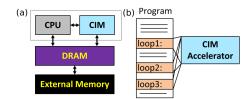

| 2.1  | CIM architecture - overview             | 10 |

| 2.2  | CIM configurations                      | 11 |

| 2.3  | CIM Classification                      | 12 |

| 2.4  | MTJ Cell structure                      | 13 |

| 2.5  | PCM Cell Structure                      | 14 |

| 2.6  | OxRAM and CBRAM                         | 15 |

| 2.7  | I-V Curve for ReRAM                     | 15 |

| 2.8  | Resistance range in Memristors          | 16 |

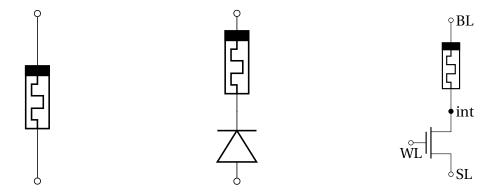

| 2.9  | 1R memristor cell                       | 17 |

| 2.10 | 1S1R memristor cell                     | 17 |

| 2.11 | 1T1R memristor cell                     | 17 |

| 2.12 | ReRAM Production Process                | 17 |

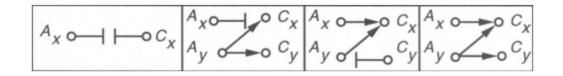

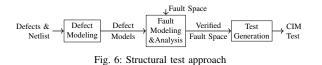

| 3.1  | Structural testing approach             | 21 |

| 3.2  | Device oriented modeling method         | 23 |

| 3.3  | Address Decoder faults                  | 26 |

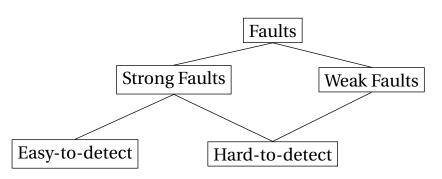

| 3.4  | Fault Classification                    | 27 |

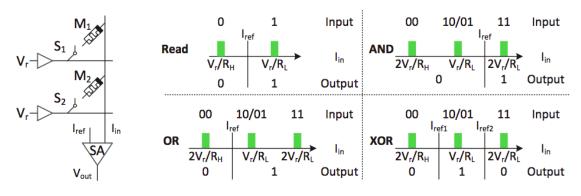

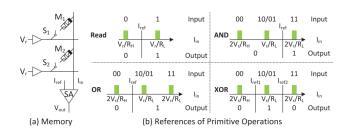

| 3.5  | Memory array setup [80]                 | 30 |

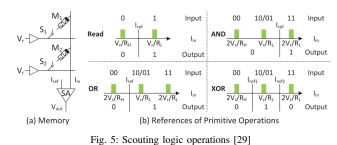

| 3.6  | References of primitive operations [80] | 30 |

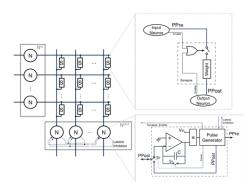

| 4.1  | Structural testing approach             | 31 |

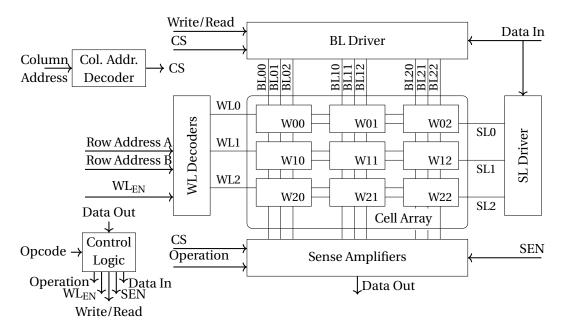

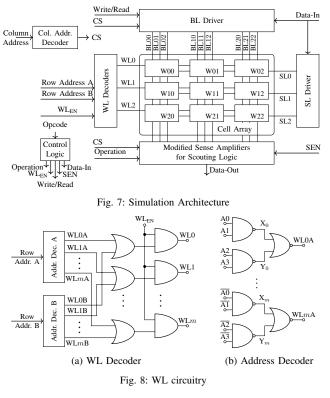

| 4.1  | Simulation Architecture                 |    |

|      |                                         | 32 |

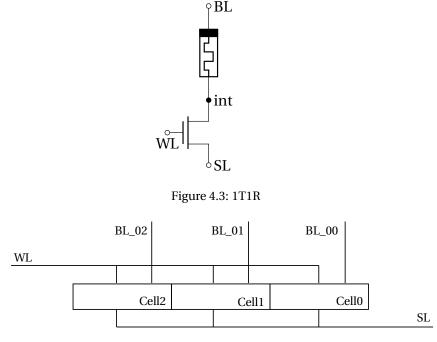

| 4.3  | 1T1R                                    | 32 |

| 4.4  | Word in array                           | 32 |

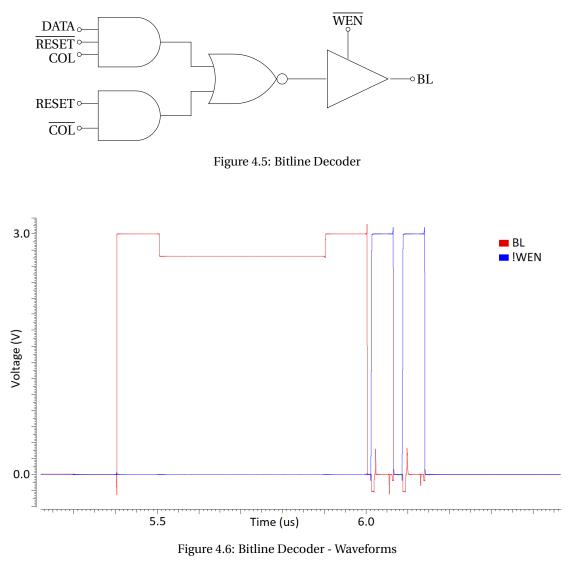

| 4.5  | Bitline Decoder                         | 33 |

| 4.6  | Bitline Decoder - Waveforms             | 33 |

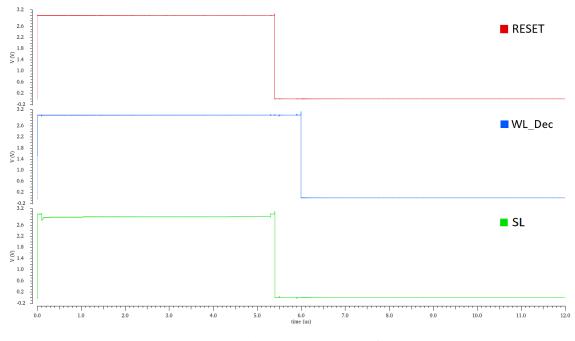

| 4.7  | Select Line Driver                                    | 33 |

|------|-------------------------------------------------------|----|

| 4.8  | Select Line Driver - Waveforms                        | 34 |

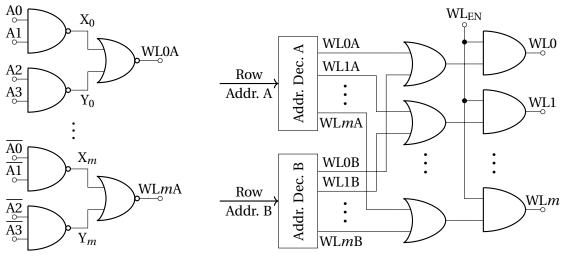

| 4.9  | Address Decoder                                       | 35 |

| 4.10 | WL Decoder                                            | 35 |

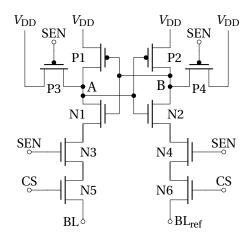

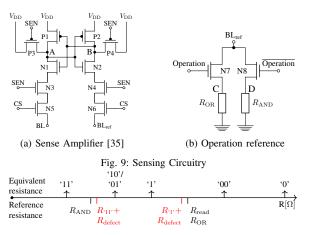

| 4.11 | Sense Amplifier                                       | 36 |

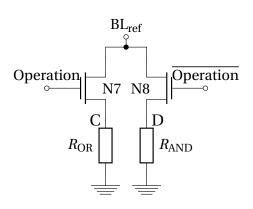

| 4.12 | Operation reference                                   | 36 |

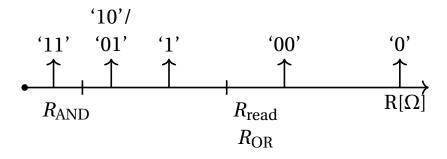

| 4.13 | Scouting logic relative resistance and references     | 36 |

| 4.14 | Sense Amplifier Internal Nodes                        | 37 |

| 4.15 | Model Parameters                                      | 38 |

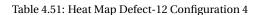

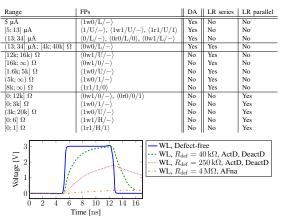

| 4.16 | WL Decoder fault with different defect strengths      | 58 |

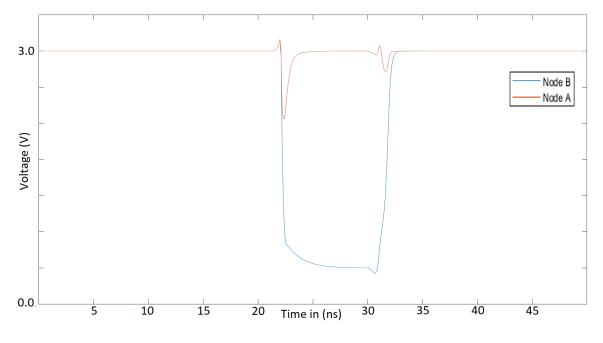

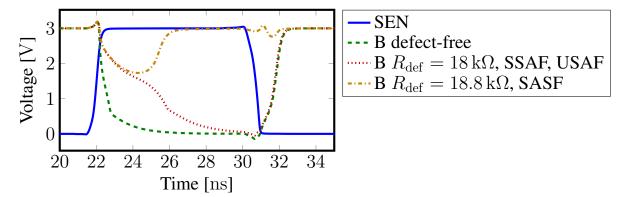

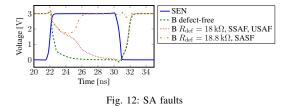

| 4.17 | Sense Amplifier Faults                                | 60 |

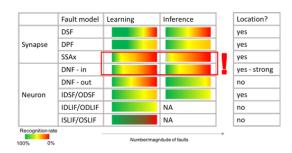

| 4.18 | Fault location in address decoder for two port memory | 84 |

|      |                                                       |    |

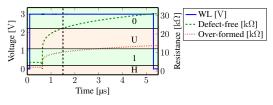

| 5.1  | Defect-free and over-formed cell                      | 88 |

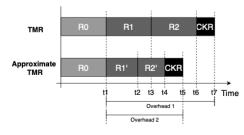

| 5.2  | Test Unique faults in 2 Port Memories                 | 94 |

## List of Tables

| 2.1  | Front-End-of-Line Process                    | 18 |

|------|----------------------------------------------|----|

| 3.1  | Complete single-cell static fault primitives | 26 |

| 3.2  | March test notations                         | 28 |

| 4.1  | Truth Table - Bitline Decoder                | 34 |

| 4.2  | Defect Location in the Memory cell           | 38 |

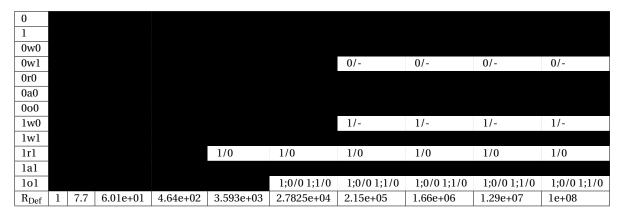

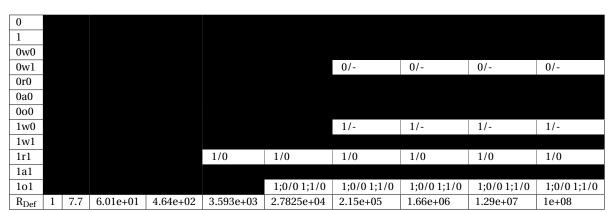

| 4.3  | Heat Map Example                             | 40 |

| 4.4  | Heat Map Defect-1 Configuration 1            | 40 |

| 4.5  | Heat Map Defect-1 Configuration 2            | 40 |

| 4.6  | Heat Map Defect-1 Configuration 3            | 41 |

| 4.7  | Heat Map Defect-1 Configuration 4            | 41 |

| 4.8  | Heat Map Defect-2 Configuration 1            | 41 |

| 4.9  | Heat Map Defect-2 Configuration 2            | 41 |

| 4.10 | Heat Map Defect-2 Configuration 3            | 42 |

| 4.11 | Heat Map Defect-2 Configuration 4            | 42 |

| 4.12 | Heat Map Defect-3 Configuration 1            | 42 |

| 4.13 | Heat Map Defect-3 Configuration 2            | 43 |

| 4.14 | Heat Map Defect-3 Configuration 3            | 43 |

| 4.15 | Heat Map Defect-3 Configuration 4            | 44 |

| 4.16 | Heat Map Defect-4 Configuration 1            | 44 |

| 4.17 | Heat Map Defect-4 Configuration 2            | 44 |

| 4.18 | Heat Map Defect-4 Configuration 3            | 44 |

| 4.19 | Heat Map Defect-4 Configuration 4            | 45 |

| 4.20 | Heat Map Defect-5 Configuration 1            | 45 |

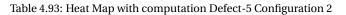

| 4.21 | Heat Map Defect-5 Configuration 2            | 45 |

| 4.22 | Heat Map Defect-5 Configuration 3            | 45 |

| 4.23 | Heat Map Defect-5 Configuration 4            | 46 |

| 4.24 | Heat Map Defect-6 Configuration 1            | 46 |

|      | Heat Map Defect-6 Configuration 2            | 46 |

| 4.26 | Heat Map Defect-6 Configuration 3            | 46 |

|      |                                              |    |

| 4.27 Heat Map Defect-6 Configuration 4  | 47 |

|-----------------------------------------|----|

| 4.28 Heat Map Defect-7 Configuration 1  | 47 |

| 4.29 Heat Map Defect-7 Configuration 2  | 47 |

| 4.30 Heat Map Defect-7 Configuration 3  | 47 |

| 4.31 Heat Map Defect-7 Configuration 4  | 48 |

| 4.32 Heat Map Defect-8 Configuration 1  | 48 |

| 4.33 Heat Map Defect-8 Configuration 2  | 48 |

| 4.34 Heat Map Defect-8 Configuration 3  | 48 |

| 4.35 Heat Map Defect-8 Configuration 4  | 49 |

| 4.36 Heat Map Defect-9 Configuration 1  | 49 |

| 4.37 Heat Map Defect-9 Configuration 2  | 49 |

| 4.38 Heat Map Defect-9 Configuration 3  | 49 |

| 4.39 Heat Map Defect-9 Configuration 4  | 50 |

| 4.40 Heat Map Defect-10 Configuration 1 | 50 |

| 4.41 Heat Map Defect-10 Configuration 2 | 50 |

| 4.42 Heat Map Defect-10 Configuration 3 | 50 |

| 4.43 Heat Map Defect-10 Configuration 4 | 51 |

| 4.44 Heat Map Defect-11 Configuration 1 | 51 |

| 4.45 Heat Map Defect-11 Configuration 2 | 51 |

| 4.46 Heat Map Defect-11 Configuration 3 | 51 |

| 4.47 Heat Map Defect-11 Configuration 4 | 52 |

| 4.48 Heat Map Defect-12 Configuration 1 | 52 |

| 4.49 Heat Map Defect-12 Configuration 2 | 52 |

| 4.50 Heat Map Defect-12 Configuration 3 | 52 |

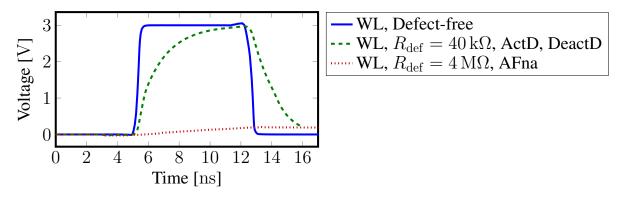

| 4.51 Heat Map Defect-12 Configuration 4 | 53 |

| 4.52 Heat Map Defect-13 Configuration 1 | 53 |

| 4.53 Heat Map Defect-13 Configuration 2 | 53 |

| 4.54 Heat Map Defect-13 Configuration 3 | 53 |

| 4.55 Heat Map Defect-13 Configuration 4 | 54 |

| 4.56 Heat Map Defect-14 Configuration 1 | 54 |

| 4.57 Heat Map Defect-14 Configuration 2 | 54 |

| 4.58 Heat Map Defect-14 Configuration 3 | 54 |

| 4.59 Heat Map Defect-14 Configuration 4 | 55 |

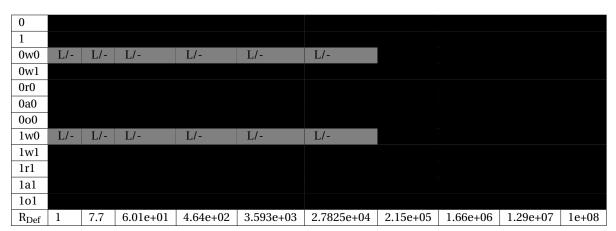

| 4.60 Heat Map Defect-15 Configuration 1 | 55 |

| 4.61 Heat Map Defect-15 Configuration 2 | 55 |

| 4.62 Heat Map Defect-15 Configuration 3                 | 55 |

|---------------------------------------------------------|----|

| 4.63 Heat Map Defect-15 Configuration 4                 | 56 |

| 4.64 Heat Map Defect-16 Configuration 1                 | 56 |

| 4.65 Heat Map Defect-16 Configuration 2                 | 56 |

| 4.66 Heat Map Defect-16 Configuration 3                 | 56 |

| 4.67 Heat Map Defect-16 Configuration 4                 | 57 |

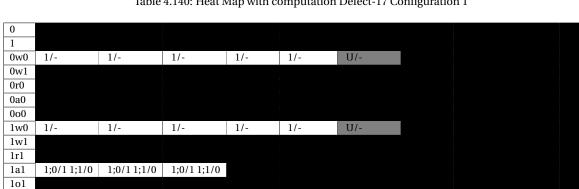

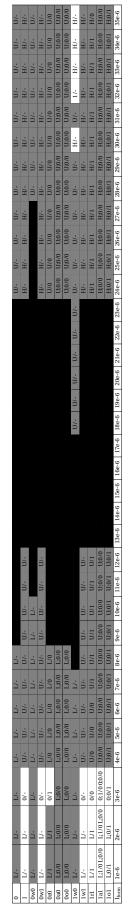

| 4.68 Heat Map Defect-17 Configuration 1                 | 57 |

| 4.69 Heat Map Defect-17 Configuration 2                 | 57 |

| 4.70 Heat Map Defect-17 Configuration 3                 | 57 |

| 4.71 Heat Map Defect-17 Configuration 4                 | 58 |

| 4.72 Heat Map Forming defect Configuration 1            | 59 |

| 4.73 Heat Map Forming defect Configuration 2            | 59 |

| 4.74 Heat Map Forming defect Configuration 3            | 59 |

| 4.75 Heat Map Forming defect Configuration 4            | 59 |

| 4.76 Heat Map with computation Defect-1 Configuration 1 | 62 |

| 4.77 Heat Map with computation Defect-1 Configuration 2 | 62 |

| 4.78 Heat Map with computation Defect-1 Configuration 3 | 62 |

| 4.79 Heat Map with computation Defect-1 Configuration 4 | 63 |

| 4.80 Heat Map with computation Defect-2 Configuration 1 | 63 |

| 4.81 Heat Map with computation Defect-2 Configuration 2 | 63 |

| 4.82 Heat Map with computation Defect-2 Configuration 3 | 64 |

| 4.83 Heat Map with computation Defect-2 Configuration 4 | 64 |

| 4.84 Heat Map with computation Defect-3 Configuration 1 | 64 |

| 4.85 Heat Map with computation Defect-3 Configuration 2 | 64 |

| 4.86 Heat Map with computation Defect-3 Configuration 3 | 65 |

| 4.87 Heat Map with computation Defect-3 Configuration 4 | 65 |

| 4.88 Heat Map with computation Defect-4 Configuration 1 | 65 |

| 4.89 Heat Map with computation Defect-4 Configuration 2 | 66 |

| 4.90 Heat Map with computation Defect-4 Configuration 3 | 66 |

| 4.91 Heat Map with computation Defect-4 Configuration 4 | 66 |

| 4.92 Heat Map with computation Defect-5 Configuration 1 | 67 |

| 4.93 Heat Map with computation Defect-5 Configuration 2 | 67 |

| 4.94 Heat Map with computation Defect-5 Configuration 3 | 67 |

| 4.95 Heat Map with computation Defect-5 Configuration 4 | 67 |

| 4.96 Heat Map with computation Defect-6 Configuration 1 | 68 |

| 4.97 Heat Map with computation Defect-6 Configuration 2   | 68 |

|-----------------------------------------------------------|----|

| 4.98 Heat Map with computation Defect-6 Configuration 3   | 68 |

| 4.99 Heat Map with computation Defect-6 Configuration 4   | 69 |

| 4.100Heat Map with computation Defect-7 Configuration 1   | 69 |

| 4.101Heat Map with computation Defect-7 Configuration 2   | 69 |

| 4.102Heat Map with computation Defect-7 Configuration 3   | 70 |

| 4.103Heat Map with computation Defect-7 Configuration 4   | 70 |

| 4.104Heat Map with computation Defect-8 Configuration 1   | 70 |

| 4.105Heat Map with computation Defect-8 Configuration 2   | 71 |

| 4.106Heat Map with computation Defect-8 Configuration 3   | 71 |

| 4.107Heat Map with computation Defect-8 Configuration 4   | 71 |

| 4.108Heat Map with computations Defect-9 Configuration 1  | 71 |

| 4.109Heat Map with computations Defect-9 Configuration 2  | 72 |

| 4.110Heat Map with computations Defect-9 Configuration 3  | 72 |

| 4.111Heat Map with computations Defect-9 Configuration 4  | 72 |

| 4.112Heat Map with computations Defect-10 Configuration 1 | 73 |

| 4.113Heat Map with computations Defect-10 Configuration 2 | 73 |

| 4.114Heat Map with computations Defect-10 Configuration 3 | 73 |

| 4.115Heat Map with computations Defect-10 Configuration 4 | 74 |

| 4.116Heat Map with computation Defect-11 Configuration 1  | 74 |

| 4.117/Heat Map with computation Defect-11 Configuration 2 | 74 |

| 4.118Heat Map with computation Defect-11 Configuration 3  | 75 |

| 4.119Heat Map with computation Defect-11 Configuration 4  | 75 |

| 4.120Heat Map with computation Defect-12 Configuration 1  | 75 |

| 4.121Heat Map with computation Defect-12 Configuration 2  | 76 |

| 4.122Heat Map with computation Defect-12 Configuration 3  | 76 |

| 4.123Heat Map with computation Defect-12 Configuration 4  | 76 |

| 4.124Heat Map with computation Defect-13 Configuration 1  | 77 |

| 4.125Heat Map with computation Defect-13 Configuration 2  | 77 |

| 4.126Heat Map with computation Defect-13 Configuration 3  | 77 |

| 4.127Heat Map with computation Defect-13 Configuration 4  | 77 |

| 4.128Heat Map with computation Defect-14 Configuration 1  | 78 |

| 4.129Heat Map with computation Defect-14 Configuration 2  | 78 |

| 4.130Heat Map with computation Defect-14 Configuration 3  | 78 |

| 4.131Heat Map with computation Defect-14 Configuration 4  | 79 |

| 4.132Heat Map with computation Defect-15 Configuration 1                               | 79 |

|----------------------------------------------------------------------------------------|----|

| 4.133 Heat Map with computation Defect-15 Configuration 2                              | 79 |

| 4.134Heat Map with computation Defect-15 Configuration 3                               | 80 |

| 4.135Heat Map with computation Defect-15 Configuration 4                               | 80 |

| 4.136Heat Map with computation Defect-16 Configuration 1                               | 80 |

| 4.137Heat Map with computation Defect-16 Configuration 2                               | 80 |

| 4.138Heat Map with computation Defect-16 Configuration 3                               | 81 |

| 4.139Heat Map with computation Defect-16 Configuration 4                               | 81 |

| 4.140Heat Map with computation Defect-17 Configuration 1                               | 81 |

| 4.141Heat Map with computation Defect-17 Configuration 2                               | 82 |

| 4.142Heat Map with computation Defect-17 Configuration 3                               | 82 |

| 4.143Heat Map with computation Defect-17 Configuration 4                               | 82 |

| 4.144Heat Map with computation Forming defect Configuration 1                          | 83 |

| 4.145Heat Map with computation Forming defect Configuration 2                          | 83 |

| 4.146Heat Map with computation Forming defect Configuration 3                          | 83 |

| 4.147Heat Map with computation Forming defect Configuration 4                          | 83 |

| 4.148Unique defects in two port memory Address decoders                                | 84 |

| 5.1 Sensitized FP with Maximum Coverage - ETD                                          | 91 |

| 5.2 Defect Coverage in ETD test sequence - Memory configuration                        | 91 |

| 5.3 Sensitized FP with Maximum Coverage - HTD                                          | 92 |

| 5.4 Defect Coverage in HTD test sequence - Memory configuration                        | 93 |

| 5.5 Sensitized FP with Maximum Coverage for Computation Configuration - ETD $\ldots$ . | 95 |

| 5.6 Defect Coverage in ETD test sequence - Computation Configuration                   | 96 |

| 5.7 Sensitized FP with Maximum Coverage for Computation Configuration - HTD            | 96 |

| 5.8 Defect Coverage in HTD test sequence - Computation Configuration                   | 97 |

## List of Abbreviations

**BE** Bottom Electrode **BEOL** Back-End-of-Line **CBRAM** Conductive Bridge random access memory **CIM** Computation-in-memory CMOS complementary metal-oxide-semiconductor DRAM Dynamic Random Access Memory **DUT** Device under Test ETD Easy to Detect FEOL Front-End-of-Line **FP** Fault Primitive **HRS** High Resistance state HTD Hard to Detect ILP Instruction level parallelism LRS Low Resistance state MOSFET Metal-oxide-semiconductor field-effect transistor **OxRAM** Oxide random access memory **PCM** Phase chage memory **ReRAM** Resistive Random Access Memory SRAM Static Random Access Memory STT-MRAM Spin-transfer-torque magnetic random access memory TE Top Electrode **V**<sub>DD</sub> Operation Voltage VLSI Very large scale integration

## Introduction

This chapter introduces the thesis. First the motivation of the thesis is discussed. Then, the state of the art in CIM architecture testing is discussed. This is followed by the contributions of the thesis. Finally the organisation of this thesis is briefed.

#### 1.1. Motivation

Modern computing systems are a collection of different sub-systems that make up the system as a whole. These sub-systems are arranged in different layers of abstraction [40]. The abstractions range from the device-level components, such as metal–oxide–semiconductor field-effect transistors (MOSFET) which form the basic logic-gates (such as the NAND and NOR logic gates) to operating systems that the users interact with [40]. MOSFET technology has paved the way for the development of complementary metal-oxide-semiconductor (CMOS) fabrication process. This enabled the development of integrated circuits which have more than a million transistors in them, all while having low static power consumption and high noise immunity [63]. In all layers of abstraction, there has been constant research and development to create the most efficient computing system in terms of power, area and performance [33]. However, with the recent development in the fields of medical imaging, meteorological sciences and DNA sequencing, there has risen a need for high performance computers that are able to solve large problems with minimum effort possible [24] [18].

While the aforementioned problems can be solved with existing computing technologies, there are several shortcomings of present day computers and their architectures. These serve as hindrances for improving the computing performance to keep up with the ever growing demand for computation and data analysis [33]. These hindrances are commonly known as "performance limiting walls" in different performance aspects. These walls exist for both the underlying CMOS technology and the computer architecture that make up the computing system [26] [4]. CMOS technology faces the following walls:

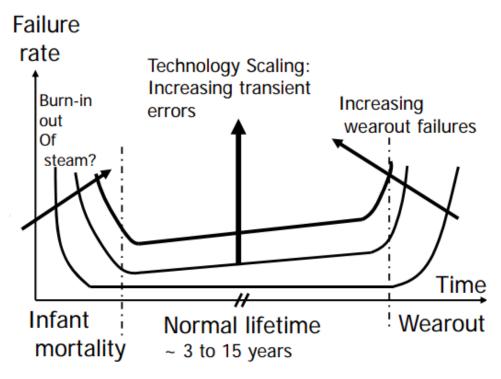

- 1. **Reliability Wall** As traditional CMOS based devices are scaled down to smaller nanoscale dimensions, the resulting production variations, operational variations, and defects cause higher failure rates and tend to reduces the lifetime of computing systems. This can be visualised in the bathtub diagram shown in Figure 1.1 where there is an increase in failure rate as the sizes of the devices are scaled down [4].

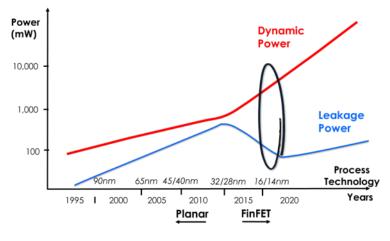

- 2. Leakage Wall To keep in check the power density of the devices, it was necessary to reduce

Figure 1.1: Reliability Wall [4]

the operating voltages of the devices. This enabled the integration of more and more devices in a small space. Unfortunately, reducing the operating voltage ( $V_{DD}$ ) reduces the threshold voltage of the CMOS inverter as well. This has in-turn led to an increase in sub-threshold leakage in these devices [34]. This means that for smaller devices, the leakage power is larger than the active power in some cases. Figure 1.2 [1] shows the leakage power and the active power consumed as the technology size is reduced [34].

Figure 1.2: Leakage Wall [3]

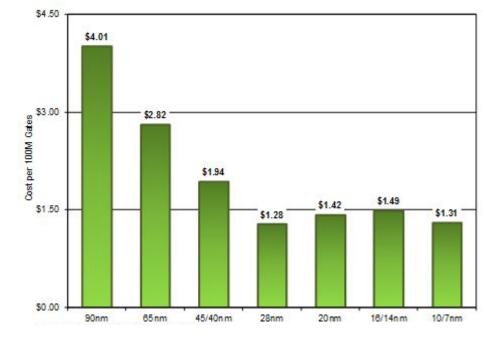

3. **Cost Wall** - There is a clear increase in the production costs over the years for the CMOS devices as their geometric size is reduced to nanoscale [78], while there the cost per gate has been decreasing [2]. However, the decrease in cost per device more than compensated from 90nm technology that there was an overall decrease in the prices. There is however a considerable amount of increase in yield loss as a large number of transistors are integrated into a

single chip, which contributes to the increase in the overall cost of the device for smaller devices [55]. This has lead to the plateauing of the cost of production for smaller devices [36]. The cost trend with time is shown in the Figure 1.3 [36].

Figure 1.3: Cost Wall [36]

In addition to these limitations in the CMOS devices, there are also the following walls for the Von-Neumann architecture itself. These type of computer systems have distinct control unit, processing unit and memory that stores data and instructions. These kind of architectures are used predominantly in all computing systems nowadays [62][26].

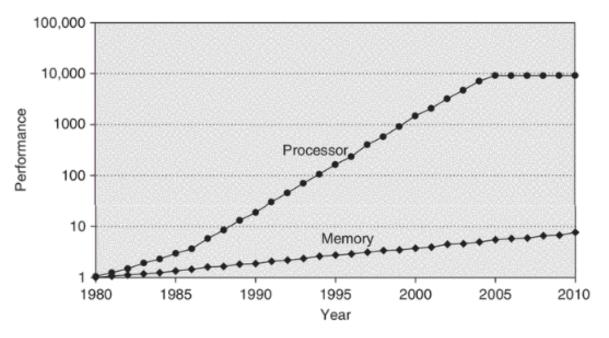

- 1. **Memory Wall** Some applications might require a large amount of data to be transferred between the memory and the processing unit in the Von-Neumann architecture. But the memory bandwidth has not increased as much as the processor throughput over the years, as shown in the Figure 1.4. Although cache memory mechanisms have been introduced to reduce the data access time, they are limited in size [33] [41]. This serves as a bottleneck for applications where there is a large amount of data transfer, which takes more time than computations. Hence overall throughput of the system has not increased [61].

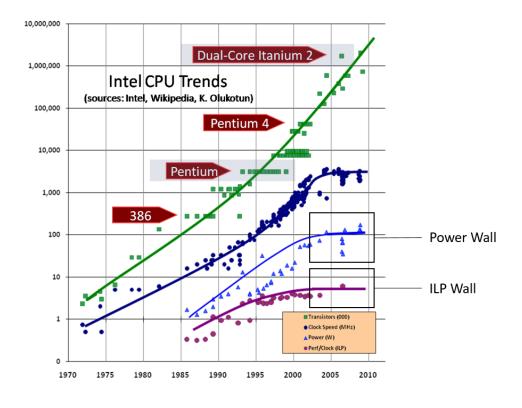

- 2. **Power Wall** While the performance of the processing unit has seen a significant increase over the years thanks to the increase in the frequency, the power consumption has also increased. This leads to overheating in the system [33]. The trend for the speed of the processor and the power consumed over the years is shown in Figure 1.5. The operation frequency of computing systems have reached a limit because of the available power.

- 3. **Instruction level parallelism (ILP) Wall** While there is parallelism shown in the CPU level with the help of pipelining, and processor level with multi-threading and multi-core systems, the problems that need to be solved are not solvable with parallelism. This increases the power consumption of the computing system to solve the problems [33]. This stagnation can be seen in the Figure 1.5, where the instruction level parallelism has flat-lined.

Figure 1.4: Memory Wall [33]

Figure 1.5: Leakage Wall [68]

The combination of these walls in modern computing systems has urged researchers to look towards novel methods of optimization, including modified architectures. Computation in memory (CIM) architectures have been developed as alternatives to traditional architectural solutions. These CIM architectures work around the memory wall by performing logic operations in the memory, thus reducing memory transfers and thereby improving performance. With CIM architectures, massive parallelism is achieved because of the repeated structure possible with the memory cells that are present in these architectures. CIM architectures have been realised with DRAM [48] and SRAM [70] memory cells as well as employing emerging memory technology, as described next.

The walls in CMOS technology have also increased the interest in device level alternatives that have lower static leakage and lower cost. The realization of memristors devices on silicon has paved the way for development of new logic and architecture designs that have minimal static power dissipation, because of their non-volatile nature. Memristive devices are the physical implementations of memristors. Memristors were first conceptualized by Chua in 1971 as a missing two-terminal circuit element, along the lines of the resistor, inductor and capacitor [14]. The Memristor is characterized by the relation between the charge and the magnetic flux [14]. As the name suggests, one of the unique property of memristors is that they behave like a non-linear resistor with memory. The first practical memristor in modern times was developed by the research group of Stanley Williams at the Hewlett-Packard labs in 2008 [66]. It was realised as a metal/oxide/metal cross-point device with  $TiO_2$  making up the oxide layer. Since then, there has been significant amount of research dedicated towards improvement of the devices. These include experimenting with different metal oxides, fine tuning physical properties for better yield and towards development of the circuits and architectures using these memristors that could solve real world problems. Many different kinds of memristive devices have been identified and produced, namely resistive RAM (ReRAM) [77], phase change memory (PCM) [76] and spin-transfer-torque magnetic RAM (STT-MRAM) [86].

These memristors, by virtue of their non-volatile nature, can be employed in creating alternative computer architectures which can be used to reduce, if not eliminate, the need for data movement between the memory and the computation unit. In our research, we concentrate on the CIM architectures based on memristive technologies because of the multiple advantages gained including low power consumption, non-volatility of the data in the memristor among others [26]. Since individual memristor devices are used for the computation of logic, massive amounts of parallelism can be achieved in the system, leading to improved efficiency.

#### 1.2. Need for high quality test

The memristive devices themselves are not with their downside. Since research is still at a nascent stage with respect to the development of the memristor technology, many issues such as variations, faults etc., exist, that need to be tackled. The growth in popularity of memristor based CIM architectures has lead to huge developments in the area, such as improvement in reliability and faster operation timings because of selecting appropriate materials for producing memristive devices [83]. Memristive devices have a different production process as opposed to traditional CMOS devices, which makes them susceptible to defects that have not been studied yet. Studying, testing and detecting these defects and faults that arise in memristor-based system is essential in order to make sure that the end product can be considered consumer grade.

A characteristic feature of the CIM architectures based on memristive devices is their reliance of CMOS technology to control the operations of memristive devices. This includes operations such as driving the necessary voltages, writing logical values on the memristors, computing logic values based on the values in the memristors etc. There is also the added possibility of new defect that can occur in the memristor devices because of the interactions between the CMOS devices and memristors. These need to be accounted for during the testing of a memristor based circuit.

All these factors contribute towards potential failure of devices that are based on CIM architectures. This creates the need for high quality tests for these devices. These tests determine if the CIM architecture based circuits are devoid of any known defects and if they are fit for consumer operation. In order to detect these defects, complete analysis of these architectures have to be made. Since these CIM architectures act as a memory *and* computing unit, tests have to be developed for these different modes of operations as well. Therefore, a structural test approach is needed for these devices. This forms the basis of this thesis, where we explore these architectures and device and create tests for the faults that might occur in them.

#### 1.3. State of the art in CIM Testing

In the literature, there only exist limited works which revolves around the testing CIM architecture [15, 69]. In Tsai et al.s work, 8T cell SRAM based CIM structures are tested. However, it does not address the peripherals of the CIM architecture in the test sequences created, and it does not address tests for different CIM architectures based on other emerging memory devices [69]. While Emara et al.s work [15] tests for Memristor Ratioed Logic [44], it fails to expand on the same for other logic types. There are also works which test only the emerging memory technologies, based on which CIM architectures are developed. These works test ReRAM [31, 32] and STT-MRAM [56], thermally assisted switching MRAM (TAS-MRAM) [6] but only as standalone devices. The tests from these publications focus only on the defects and faults in a singular device and provide solutions for them. However, these test cannot, for example, take into account the interaction between two cells when performing a computing operation.

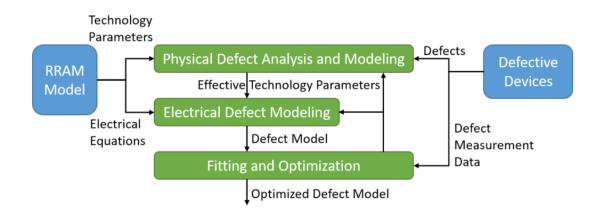

These publications have also been found to not take into account the physical behaviour of the defective devices while simulations, and use linear resistors as the defect model. This goes against the definition of these memristive device showing non-linear resistive characteristics. This leads to inaccurate fault models from the defect injections, which in turn lead to inaccurate tests [17]. A novel approach named the Device aware test approach models the physics of the defective device and is employed in this thesis to get accurate fault models and thereby better tests[16].

Through this thesis, the following goals are achieved: A methodology for CIM architectures testing is created that make use of emerging devices (RRAM, STT-MRAM, etc.) as well as traditional memory cells (DRAM, SRAM) in their core. The method of testing of these devices must make use of device aware testing to ensure the right modelling of the devices used. The method takes all operations, *both memory and computation*, into account, as well as the peripheral circuits when defining a test.

#### 1.4. Contributions

The following contributions are made in this thesis:

#### 1.4.1. Discussion of Test approach for CIM architectures

For testing of VLSI systems, there are two kinds of test approaches that are generally followed. These are *Functional* testing and *Structural* testing. This work systematically discusses the feasibility of applying these approaches to CIM architectures and concludes that structural testing is the more suitable method for testing CIM architectures.

#### 1.4.2. Systematic Approach for Testing CIM Architectures

The functional operations in the CIM architectures are identified and the architecture itself is divided into two configurations based on the type of operation that is performed on the memristor devices:

- *Memory configuration* where one or more memory device is accessed for either reading the data stored in them or writing data into them.

- *Computation configuration* where the data in one or more memory devices are accessed and some logic or arithmetic operation is performed on them.

These configurations are studied and a systematic approach for testing all CIM architectures is proposed in this work.

#### 1.4.3. Application of systemic approach to Scouting Logic

The test approach is verified on Scouting logic [80], a CIM architecture that is able to perform bitwise logic OR, AND and XOR operations on the data present in the memristor devices. The defects and the fault models in both memory and computation configuration in scouting logic are discussed. Tests are developed for faults observed in simulating the circuit after injecting defects.

#### 1.4.4. Simulation Setup for Test Development for Scouting logic

In order to develop the tests for both configurations of scouting logic, the following steps were taken: Fault primitive modelling for both memory and computation configurations, setting up netlists in the Cadence Spectre language and injecting defects in them for simulations, automation of the simulation in a cluster using Mathworks MATLAB and bash scripting, extraction of the simulated data and identifying the tests to be performed.

#### 1.4.5. Publications

Parts of this thesis have been used in the following publications, which have been included in the appendices:

- A. Bosio, I. O'Connor, G. S. Rodrigues, F. K. Lima, E. I. Vatajelu, G. Di Natale, L. Anghel, S. Nagarajan, M. C. R. Fieback, S. Hamdioui "Rebooting Computing: The Challenges for Test and Reliability," 2019 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), Noordwijk, Netherlands, 2019, pp. 8138-8143.

- 2. S. Hamdioui, M. C. R. Fieback, *S. Nagarajan*, M. Taouil "Testing Computation-in-Memory Architectures Based on Emerging Memories", in 2019 *International Test Conference*, Washington D.C, U.S.A, 2019.

- 3. M. Fieback, S. Nagarajan, R. Bishnoi, M. Tahoori, M. Taouil, S. Hamdioui "Testing Scouting Logic-Based Computation-in-Memory Architectures", submitted for *European Test Symposium, Tallinn, Estonia, 2020.*

#### 1.5. Organization

The rest of this work is organized into the following chapters.

Chapter 2 introduces and discusses memristive device based CIM architectures in detail. After this, the CIM architectures are classified based on the location of where computations reside. This is then followed by a detailed explanation of ReRAM cells.

Chapter 3 gives an introduction to testing electronics. Then, the different test methods employed in testing electronic devices are introduced. This is followed by detailed explanation of the memory testing. Then it proposes the systematic approach that can be used to test CIM architectures.

Chapter 4 details the fault analysis of Scouting logic, describing the experimental setup and faults in each component.

Chapter 5 gives the tests that were developed for scouting logic, both in memory and computation configurations.

Chapter 6 concludes the work by summarizing each of the chapters, followed by discussions and suggestions for possible future work.

# 2

### Memristor based CIM

This chapter introduces the memristor based CIM architectures and their classifications, and explains in detail the memristor cell. A general introduction to CIM architectures is presented in Section 2.1. Then, the classification of the CIM architectures is introduced in Section 2.2. Section 2.3 presents the memristor cell, which forms the building block of these CIM architectures.

#### 2.1. CIM Introduction

As described earlier, traditional Von-Neumann architectures have to transfer data from the memory to the central processing unit (CPU). This is an overhead to the overall time taken for the computation of data. In addition, it also accounts for high energy consumption and naturally creates an upper limit to the amount of data that can be transferred. In order to reduce or at best eliminate this overhead, Computation-in-Memory (CIM) architectures were developed. A CIM architecture is one that actively tries to eliminate the cost of data transfer between the memory and computation unit and has the potential to perform computations with massive parallelization by processing the data in the memory. CIM architectures have been realised with DRAM and SRAM memories in the past [81] [48] [5] [70]. However with the commercial production of the memristor devices, architectures that make use of these devices have seen a rise in popularity [26].

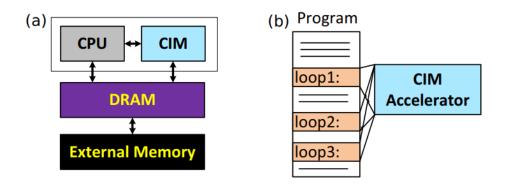

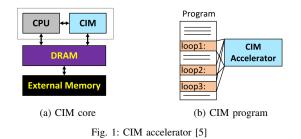

How these CIM architectures can be part of the computing system is still under discussion [46]. The ideal case for the implementation would be to completely get rid of traditional computer architecture based sub-units such as an adder or multiplier and replace them with CIM architectures. But this cannot be achieved with the available technology because of the relatively low amount of development in the CIM architectures which can perform these complex tasks. One proposed way of integrating CIM architectures is to use them as accelerators with existing computing cores and memories as shown in Figure 2.1-a. The CIM accelerator accesses the data from the main memory and is controlled by the control units in the main CPU. Reduced memory access time between the CIM die and the memory would mean high amount of data traffic and hence higher rate of calculations in the CPU. The use case for these accelerators is easily illustrated when there is a need for repeated calculations or a loop in the program, that can be off-loaded to the accelerator. For example, a loop in a program that repeatedly reduces an equation based on simple calculations on a data stored in a fixed memory location. CIM architectures enable parallelism in the system, i.e. if there can be a part of the program that needs iterative computations, it can be processed in the CIM accelerator and the other parts of the program can be executed in the conventional CPU in the system, as shown in Figure 2.1-b. This can be achieved by modifying the instruction set to accommodate macro-instructions in the system, which can be generated at the compiler level. This instruction can be sent from the CPU to the CIM core, where the instruction is executed. The instruction would point to the cell where an operation needs to take place and instruct which operation has to be performed on them. The final results are then returned to the main CPU to complete the program. The data produced in the intermediate steps of these iterations can be stored in the crossbar-array itself or in dedicated registers. While storing the intermediate results in the cross-bar can be resource efficient, they can also make the CIM accelerator to run at less than optimum speeds because of the overhead from the write operations used to store of data. We will now focus further on the internal architecture of the CIM accelerator.

Figure 2.1: CIM architecture - overview [27]

CIM architectures using emerging memories tend to resemble an SRAM memory device in term of their architecture. In the core of the architecture, There is a very dense crossbar array, which is made of these memristor devices. In place of the SRAM cells in a regular SRAM architecture, memristive devices are present in CIM architectures. Owing to this similarity, we shall henceforth refer to the memristor devices in an array as being part of a memristor cells. The memristor cells are accessed with the help of peripheral circuits which include address decoders to identify the group of cells where operations are performed and the bit-line drivers which provide voltages to the cells to set the value of data in the memory and to enable computations in them. These structures would vary for each type of logic that is implemented in the CIM architecture. In addition to the drivers and decoders, there would also exist communication interfaces that would help with the commands to be sent to the CIM unit.

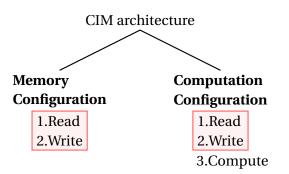

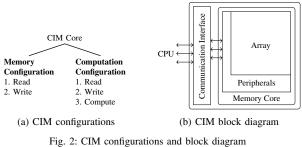

Due to the dual functionalities of the architecture, there would be changes in the circuits that build up the architecture in order to enable both memory operations and computation operations. The CIM architectures operate in two *configurations*:

- *Memory configuration* where one or more memory cells is accessed only for either reading the data that is stored in them or to write new values into these devices.

- *Computation configuration* where some logic or arithmetic operation is performed on the memory units separately or in combination with another memory cell. In these configurations, some architectures need changes in the driving circuits, the address decoders and the sensing circuits to facilitate the operations.

The Figure 2.2 shows these configurations and their operations. If we consider these memory and computation configurations as sets of operations, it can be seen that the memory configuration is a subset of the computation configuration. The results produced by computation operations are

Figure 2.2: CIM configurations

either stored in the memory cells themselves or are available via peripherals as direct outputs in the form of electrical signals. This means that there needs to be a write operation in the former case and a read operation in the latter. Thus, it can be concluded that the computation configuration is a super-set of the memory configuration. This relation would play a role in the decision making for the test methodology explained in Chapter 3.

#### 2.2. Classification of CIM

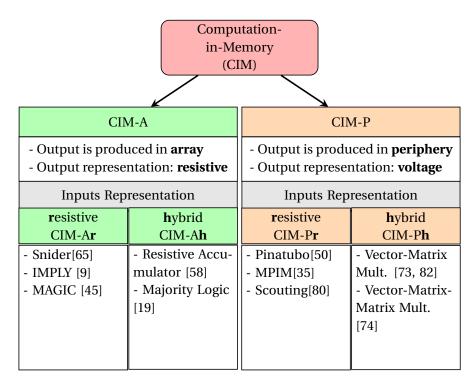

This section classifies the CIM architectures based on where the inputs for computation are obtained from and where data is stored post calculation. The CIM unit can store computation results in one of only two places (i) the crossbar array itself or (ii) the peripherals of the CIM crossbar array. From this the CIM architectures can be split in the following manner [46]:

- *CIM-Array (CIM-A)*: In CIM-A, the computation result is stored in the array after their production. The examples of such architectures include Snider [65], IMPLY [9], MAGIC [45] etc. These CIM-A architecture based cores may have significant changes in the memory array as opposed to regular memory structure in the crossbar. This is because some logic types such as MAGIC demand an array structure different from that of an SRAM.

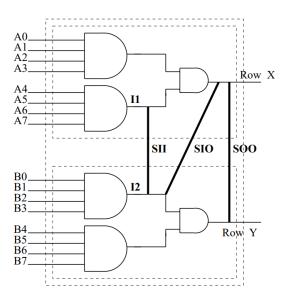

- *CIM-Peripheral (CIM-P)*: in CIM-P, the computation result is produced within the peripheral based on electrical properties of one or more memory cells. For example the amount of current that passes through the device after an operation. These architectures thus have special circuits in their periphery that can perform logical operations. Example of these kinds of architectures include Pinatubo [50] and Scouting logic [80]. The memory cells still play a huge role in these architectures as they are involved in the generation of a base electrical value, which the peripherals use to perform the operation. For some logic types this would mean that a series of operations have to be performed in one or more of these memory cells in order to obtain a logic value.

While this distinction is made with the location of results, there exists a sub-division that can be made by studying where the inputs for these logical operations are stored. Logical and arithmetic operations generally operate on two input operands. This means that there has to be minimum one operand in the crossbar array. The second operand can be obtained from either the memory itself or in the form of a external voltage depending on the architecture. The former method has *resistive* inputs in the system and the latter input method has a *hybrid* set of inputs as it has both resistive and voltage inputs. This results in the classification of the CIM architecture mentioned above to have four sub-classes: CIM-Ar and CIM-Ah for architectures that store the results of the computation

Figure 2.3: CIM Classification

in the array and have resistive and hybrid inputs respectively, and CIM-Pr and CIM-Ph where the results are obtained in the peripherals and have their inputs taking the resistive and hybrid forms respectively. The Figure 2.3 shows the various CIM logic architectures classified with the four subclasses. This classification aids in the analysis of these architectures for test development, which will be discussed later in Section 3.

#### 2.3. Memristor Cell

It is important to understand the operation of a memristive device before we can venture further into the test development. Here we discuss the three different types of memristive devices that have been fabricated and that can be used in the CIM architecture.

The three major non-volatile memoristor devices are STT-MRAM, PCRAM and ReRAM. All these memristor devices have common features: These are two terminal devices that act as non-volatile memories and they can be in one of many 'resistance states'. The states are determined by the resistance provided by these devices in the circuit. The resistance state boundary where there is minimal resistance to current in the circuit is the low resistance state (LRS) of the cell, also known as the 'On state'. Similarly, the state boundary where there is a large resistance is the high resistance state (HRS) and is known as the 'Off state'. LRS and HRS are dependent on the material of the device, process variations, noise factors and ambient conditions. The operation that switches the state of the cell from the HRS to the LRS is called as the "Set" operation, and the switching of the states in the opposite way is called as the "Reset" operation. The switching between these states is achieved with the help of some form of electrical stimulus, but the mechanism that is behind these operation varies between each of the different type of devices. We shall now look at the working principles behind each of these devices.

#### 2.3.1. STT-MRAM

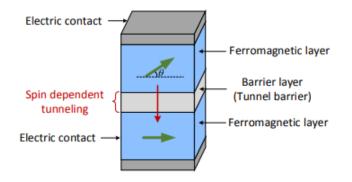

The spin-transfer-torque magnetic device is based on the magnetic torque switching that occurs in an atom because of electron spin under the influence of an electric field [8]. A STT-MRAM device consists of two dielectric materials, one with a magnetic moment of free polarity and other with a fixed polarity. These layers are separated by a thin tunneling insulation layer as shown in Figure 2.4. When a current of sufficient amplitude is applied to the device, a change in the angular momentum of the device occurs, that in turn changes the magnetisation of the free layer in the device. If the magnetisation of the free layer is in the same direction of the device, a high amount of current passes through the bulk, which is seen as a Low resistance state (LRS). If the direction is the opposite, then it is in the High resistance state (HRS).

STT-MRAM has high endurance, high scalability and high retention rate than other memristive devices [83]. However, STT-MRAM Devices have very low on resistance to off resistance ratio, which can make it difficult for state identification in some cases, where the on and off resistances are in the range  $10 - 100\Omega$ . Because of their large size, their package density is often lower than other forms of memristors [8]. The production of these devices have poor process compatibility with that of mainstream silicon CMOS devices, which creates a cost barrier due to the extra investment.

Figure 2.4: MTJ Cell structure [8]

#### 2.3.2. PCRAM

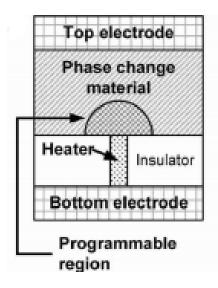

Phase change devices is primarily made up of chalcogenide glass-based elements such as GeSbTe,  $Sb_2Ti_3$  and AgInSbTe. An example of SbTe based phase change device is shown in the Figure 2.5 [76]. These materials have the property of changing their phase from crystalline, which represents low resistance state, to an amorphous form, which is the high resistance state. This phase change occurs with Joule heating, applied in the form of electric field or voltage. The transformation from LRS to HRS occurs when the material is heated above its melting point and then rapidly cooled down to room temperature. The "Set" operation is achieved by heating the material at a specific temperature between its critical point and melting point. The heating of the device is performed using a heating filament through which the current is passed [76].

PCRAM has a very large on resistance to off resistance ratio. This could mean that they could be used for multi-bit operations [83]. But the key challenges in PCRAM are large melt currents required to trigger the phase change, and the time it takes for the crystallization of the PCRAM material which can be more than 50 ns.

Figure 2.5: PCM Cell Structure [76]

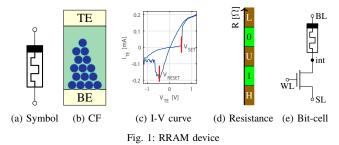

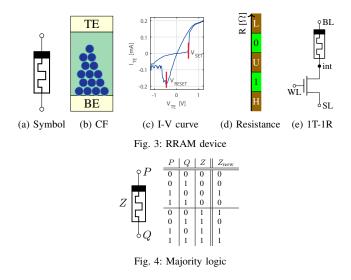

#### 2.3.3. ReRAM

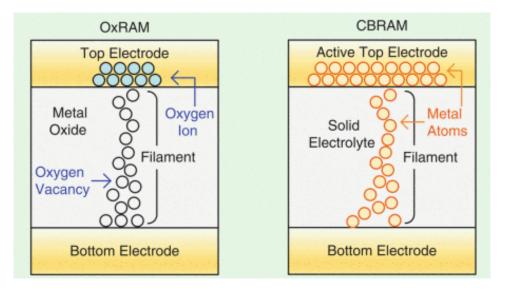

The family of Resistive RAM consists of two different types of physical devices exhibiting different underlying physics. But, these devices operate in a similar fashion, have many common characteristics and a similar structure [12, 77, 83]. All ReRAM cells are made up of a metal top electrode and a metal bottom electrode which sandwich a switching medium where a *Conductive Filament* is formed. The two different types of ReRAM cells are explained as follows:

- **OxRAM**: The Oxide RAM consists of a top and bottom electrode with the bulk of the device made up of one of TiO<sub>2</sub> [75], ZnO [59], HfO<sub>2</sub>[60], which act as the switching material. When there is certain amount of voltage applied across the device, a conductive filament made up of oxygen valencies is formed in the bulk that connects the top electrode and the bottom electrode.

- **CBRAM**: In the conductive bridge RAM, the conductive filament is made up of metal atoms which are formed by fast-diffusive Ag or Cu ions migrating into the solid-electrolyte [83]. These conductive filaments provide a path for current to flow, driving the device to a low resistance phase.

The Figure 2.6 shows the two types of ReRAM. The only difference between these cells in terms of the characteristics is that the ratio between the resistances at the on and off state which is higher in CBRAM devices. The endurance of OxRAM devices, however, are higher than that of CBRAM devices. For all comparison purposes with other types of memristor devices these two devices are grouped together as ReRAM.

The ReRAM devices have high compatibility with the CMOS process, low write time compared to other memristor devices, and low voltage requirement for read and write operations. While the ratio between on and off resistances are quite high, they also show intermediate resistance values with high precision, making them the perfect candidate for CIM architectures that have computations in the analog domain [47]. Because of these factors and the availability of well established models

Figure 2.6: OxRAM and CBRAM [83]

for these ReRAMs we use these devices in the CIM architectures in our simulations. The operations and characteristics of the ReRAM devices are discussed below.

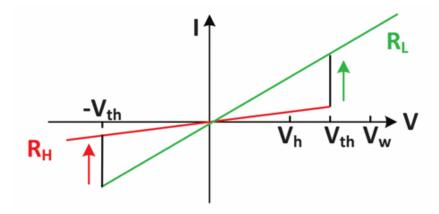

Figure 2.7: I-V Curve for ReRAM [79]

The I-V curve for ReRAM devices is shown in Figure 2.7. Here, it can be seen that when a positive voltage  $V_W$  is applied to the ReRAM device, the current increases slightly at first. At a threshold voltage ( $V_{th}$ ), there is a sudden increase in the current that flows through the device. Here, there is enough energy in the switching material to break the bonds between the metal and oxygen ions, in the case of an OxRAM device. The free oxygen ions are attracted to the positively charged electrodes and start to form the conductive filament (CF). The CF is formed all the way from the positive electrode to the bottom electrode. This chain of ions facilitate the flow of the electrons through the device and hence the resistance of the device decreases, pushing it to the LRS. When the applied voltage is removed from the cell, the conductive filament stays intact, making the device *non-volatile*. The voltage at which the transformation takes place is called the set threshold voltage ( $V_{\text{RESET}}$ ). Similarly, when a negative voltage is applied to the device that is more negative than the reset threshold voltage ( $V_{\text{RESET}}$ ), some ions in the conductive filament move back into the oxide. this reduces the size of the CF and breaks the chain of ions that connect the electrodes together, thus reverting back to the HRS. At the moment of fabrication of the device, there is no free oxide that can create the link through which the current can flow. Hence a process step where this CF is formed is required. This step in the production of the device is called *CF Forming*. In this step, a voltage much larger  $V_{SET}$  is applied to the memristor device. This voltage, called the forming voltage ( $V_{form}$ ) is dependant on the thickness of the switching material in the device. The forming of the cell happens along the grain boundaries that form in the poly-crystalline switching material [64].

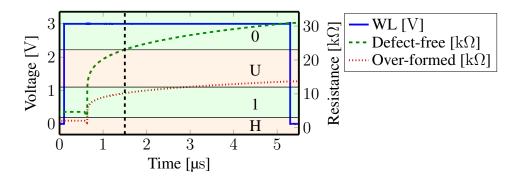

Figure 2.8: Resistance range in Memristors

The logical states in the ReRAM devices are shown in the Figure 2.8. The states are derived from the resistance of the device after a set or reset operation. As the resistance of the device is in a continuous range and varies with the write cycle, separate states for the logical values whose resistances do not lie within the exact limits of the HRS and LRS are defined. The state that corresponds to the HRS is the logical '0' and the state that corresponds to the LRS is the logical '1'. The state of the device when the resistance is less than that of the logical '1' is called as 'H'. Similarly, the state of the cell where the resistance is higher than that of the logical '0' is called as 'L'. The state that is between the LRS and HRS resistance range is the undefined state, denoted by 'U'. These states have been seen in defective ReRAMs, whose detection is an important part of the test development.

#### 2.3.4. Memristor Array Architecture

The CIM architectures have the memristive devices in the crossbar. These devices can be arranged in different architectures. These are briefed as below:

- **1R configuration**: In the 1R configuration (Figure 2.9), each memristor cell has only the memristive device. It translates to the devices being connected end to end in the array.

- **1S1R**: Here (Figure 2.10)the cells consist of a selector that is connected to the bottom electrode. These selectors can include tunneling diodes,PT diodes etc.

- **1T1R**: In this configuration (Figure 2.11), the memristor device is connected on one end with a three terminal MOSFET device that can effectively control the current passing through the cell.

1T1R architecture is the preferred option because of the following reasons: the 1R configuration is susceptible to sneak path currents, which are caused in the array. Sneak paths are undesirable paths for the current which runs parallel to the intended path of the current in the array [87]. These sneak paths exist in the 1R configuration because of the lack of gating in the cells. There could be a path in the array that can have a lesser resistance that the intended access path in the array and can cause wrong addressing. This effect can be reduced with the usage of the 1S1R architecture for the array. This makes use of a rectifying diode or a bidirectional selector connected to the memristor device. But there are issues with maintaining stability with the cells, as there could be unstable oscillatory behaviour caused by the switching of the device or the selector. This is alleviated by the use of 1T1R architecture, which uses a transistor that is connected in series with the memristive device. This makes it a requirement to have three bit line addressing for the memory cells. Although this increases the addressing complexity and the area of the cell itself, there is a pay-off in having cells whose current can be controlled.

Figure 2.9: 1R memristor cell

Figure 2.10: 1S1R memristor cell Figure 2.11: 1

Figure 2.11: 1T1R memristor cell

The Figure 2.11 is a representation of a typical 1T1R cell. Here BL, WL and SL represent the bit line, word line and select line which enable the accessing and operations to be performed in the cell. When a positive voltage is applied to the WL, the NMOS gate opens, which allows current to pass from the BL through the device to the internal node (int in Figure 2.11) to the select line.

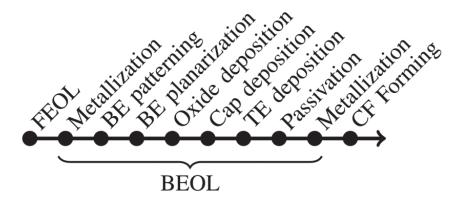

### 2.3.5. Production of ReRAM Devices

The production process of the ReRAM device in the 1T1R cell configuration is shown in Figure 2.12 and described here in detail. There are three steps that form the production process of the ReRAM device: Front-End-of-Line (FEOL), Back-End-of-Line (BEOL) and CF formation. The FEOL is the formation of the MOSFET device in the 1T1R cell structure, while the BEOL is the formation of the memristor itself. The final step is the forming of the CF, which is dependent on the oxide layer thickness at the end of the BEOL. We now look at each of these steps in detail.

Figure 2.12: ReRAM Production Process

#### FEOL:

The standard production process that is taken up for the FEOL is called as "Gate first" process. the steps in the FEOL is given in the Table 2.1. These processes are preceded by the selection of the wafer to be used, Chemical-mechanical planarization and the cleaning of the wafer using plasma, dry-physical or super-critical fluid methods [39]. Details of these processes are out of scope and readers are encouraged to refer to [63]. After these processes, the ReRAM cell is fabricated in the BEOL processes which are explained in the next subsection.

| S.No | Process steps                                     |

|------|---------------------------------------------------|

| 1    | Shallow trench isolation (STI)                    |

| 2    | High-k gate deposition                            |

| 3    | Dual metal-gate deposition                        |

| 4    | Poly-silicon gate deposition                      |

| 5    | Poly-silicon/metal etch                           |

| 6    | Source/Drain formation                            |

| 7    | Salicide/contact etch stop deposition             |

| 8    | First interlayer dielectric (ILD) film deposition |

| 9    | Polishing                                         |

| 10   | Contact formation                                 |

#### **BEOL:**

After the FEOL process, the lower metal layers of the BEOL are manufactured. These are extended up to where the memristors are fabricated. First the BE has to be constructed. The BE is patterned and etched, followed by its planarization with chemical mechanical polishing. On top of the smoothed BE, the switching material is deposited uniformly, using atomic layer deposition to ensure uniformity [38]. Coating the oxygen layer is performed with care, as the larger number of grain boundaries that form between the poly-crystalline switching material, the wider the range of the resistance of the cell. Next the oxide is deposited with a capping layer made of TiN metal. This layer is inserted to deplete the O atoms in the switching material to act as an oxygen reservoir [77]. After this the TE is deposited and etched to remove excess depositions. With the ReRAM device built, it is isolated (passivation) and connected to the metal layers (metallization).

#### **CF Forming**

As mentioned, the grain boundaries between the poly crystalline material create the path for the CF to be formed. Thus the BEOL step plays an important role in this step of the production process, as the lesser grain boundaries in the switching layer, the higher the resistance in the device. The forming step can be seen as a dielectric soft breakdown [77]. After the CF forming process, the cell is in logical state '1' and can be used as a memory and logical unit. During the forming process, the forming current,  $I_{\text{form}}$  should be kept constant throughout the operation. In order to reduce the variability of the device after forming, different schemes are followed. These apply a sequence of pulses with varying pulse width and voltage [52]. The best way to form was found to employ trape-zoidal waveforms that had their voltage cutoff when the expected switching behaviour is achieved [22].

These manufacturing processes are points where defects arise in the cell and in the peripherals. These defects cause the failure of CIM devices. The defects are discussed in Section 3.3.

# 3

# **CIM Architecture Testing**

Chapter 2 gave an introduction to CIM architectures and memristor cells used in them. This chapter provides background on electronic testing. The first section gives an introduction to testing, followed by definitions of basic terms in electronics testing. Section 3.2 gives a brief about the different test methods available for electronics testing. The last section deals solely with testing of CIM based architectures.

# 3.1. Introduction

There are billions of transistors that are packed in a modern electronic design. This level of compactness can cause a lot of faulty devices if precision is not followed. They can sometimes fail even when care is taken to produce well fabricated devices. This is where the testing of the electronic devices comes into picture. The testing of these products after their production not only detects failed devices, after which diagnosis can identify the cause of the failure. It is of utmost importance to test components that would be used in critical applications such as military and automotive industry. Testing of these devices also plays a vital role in consumer goods as well, as they provides market advantages and overall customer satisfaction.

The general procedure followed in the testing of products is as follows: the manufactured goods are put under a test program, where devices are tested as pass or fail. The failed devices are diagnosed to find where the failure has occurred. When the failure is found, it would be used to fix either the design of the circuit or tweak the production method.

According to Micheal L. Bushnell, there are several roles taken up by testing process in electronic circuits[54]. these are listed as follows:

- **Detection**: The tests are used to detect the devices that do not work or are not up to the standards set by the company.

- **Diagnosis**: The devices that have failed are studied to identify the specific cause of the problem which resulted in the failure.

- **Device characterization**: It is imperative to understand the device operation and correct errors in the design and come up with a test procedure, which is performed during testing.

- Failure mode analysis (FMA): Through the use of different test and instruments such as optical and electron microscopes, the cause of failure is detected and the process of production is rectified[54].

Before we look in detail the process of finding defective devices, a few definitions from [54] have to be introduced:

- Device under test (DUT): The circuit system that needs to be verified to be fault free.

- **Defect**: A defect in an electronic system is the unintended difference between the implemented hardware and its intended design. These could include process defects, material defects, age defects and package defects.

- Error: A wrong output signal produced by a defective system is called an error. A defect causes an error.

- Fault: A representation of a defect at the abstracted function level is called a fault.

In order to create tests that would be able to detect the faults that are found in the devices, the internal circuits have to be studied beforehand and suitable tests for the devices have to be generated. Care has to be taken with these tests as the potential 'escape' of a fault can cause faulty devices to pass the test. These tests have to consider all possible defects, including parametric faults and if their functionality is as required by the end user. There are other concepts that are related to testing of components, but we concentrate on the testing methodologies for memories because CIM architectures are essentially memories which can do computations in them. For more information on testing electronic devices Micheal L. Bushnell's book [54] is recommended. In this thesis, the test developed is for the purpose of detection, to verify is the system developed matches the requirements set by the designer. The tests confirm the presence of a defect in the memory architecture.

# 3.2. Test Methods

This section deals with the different types of testing procedures that are taken up in order to verify the DUT for correctness.

# 3.2.1. Functional Testing

Functional testing makes use of functional tests that would check all possible inputs to the DUT to find if they produce the correct results. This means that for a circuit with n inputs a total of  $2^n$  inputs are possible. This is a very costly operation, which would be impractical for high values of n. There is also the added disadvantage of not knowing where there actual defect is in the circuit, which makes the diagnosis process highly resource consuming. On top of all of this, there is no guarantee that these functional tests cover most of the faults that can be present in the DUT.

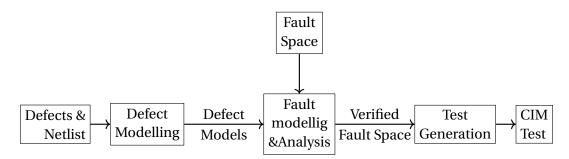

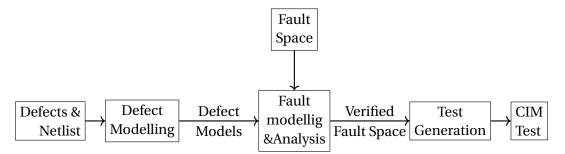

# 3.2.2. Structural testing

In Structural testing, the initial assumption is that the DUT has been manufactured according to specification. This means that unless there are defects that have come up during the manufacturing, the device would have no errors and would function properly. These tests are called structural because they rely on the specific structure of the circuits. With structural testing, it is possible to create algorithms that can test the devices for the specific faults are found to be in the system.

The Structural testing process can be streamlined into the following steps:

1. The netlist of the DUT is obtained and studied to identify potential defects. These defects are understood and adequately modelled.

Figure 3.1: Structural testing approach

- 2. A set of possible faults that in the system based on individual components in the circuit is defined. This set is called the *Fault space*.

- 3. Defect models are then injected into to the netlist to observe the faulty behaviour caused by these defects.

- 4. All faulty behaviour observed is then combined to form fault models.

- 5. These fault models are verified against the fault space to identify missing faults, by injecting all possible defects in the system. This step is called as *fault analysis*.

- 6. Tests are generated for the realistic set of faults that occur in DUT.

The above process is shown in Figure 3.1. There might be cases where structural testing does not provide as much fault coverage as required by specification. In those cases, functional tests can be employed to improve the fault coverage[11]. In the next section, we deal with the special case of memory testing with memristive devices.

# 3.3. Memory Testing

As mentioned, the CIM architectures that use memristor cells of 1T1R architecture resemble an SRAM array architecture. It consists of peripheral that allow accessing of the cells to read and write data and also compute logic. Thus it is only natural that we discuss about the testing methodology for ReRAM devices and for the peripheral units that are made up of MOSFET technology devices. The Subsection 3.3.1 discusses about the failures that can occur in the memory unit, followed by Subsection 3.3.2 which discusses the faults that occur in the memory unit because of these defects. Then the tests for these fault types that are available are introduced.

# 3.3.1. Defects

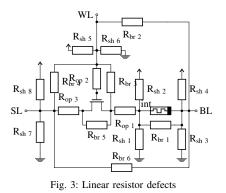

Despite efforts to manufacture devices with high precision, there are always defects in the process. These can be in the form of parametric variations or physical irregularities that hinder the operation of the cell. Defects in the memory cell can occur in both the transistor component, memristor component and the metal interconnects between them. With the peripherals, it can occur in the transistors or the interconnects. In this section, the defects that occur in these locations are discussed.

# **Defects in MOSFET components (FEOL)**

The study of defects that occur in the MOSFET transistors is a well established research field. The variation sources which cause defects were classified by Kuhn et al. as historical and emerging [42].

Historical sources are those which have been studied for a long time. These include patterning proximity effects, line roughness, polish variations and gate variations (in dielectric thickness, charge variation, traps etc.). Emerging sources are those which were seen to have lesser impact in the past, but have become of high significance lately. These include random dopant fluctuations, strain related variations etc. Long-term variation management is required to understand and keep these variation sources in check.

#### **Defects in Memristor Device**

Defects in the memristor device include those that occur in the FEOL, BEOL and CF forming. FEOL defects are similar to those discussed in Section 3.3.1. The Defects in each step discussed in the BEOL production phase described in Section 2.3.5 are discussed here:

- While the metal layer is extended to the layer where the memristor is to be constructed, standard defects that occur in CMOS production can be present. These were discussed in Section 3.3.1. These include wire opens or shorts, change in wire resistances due to line-width roughness.

- Next, in the construction of the BE, there can be variations with the area of the device due to line edge roughness. This causes lowering of the resistance of the device, which can lead to wrong logical states being stored. Smaller devices also have difficulties with the forming of CF [64].

- During the chemical-mechanical polishing of the device, there can be defects that are caused in the device due to the roughness of the BE. This can lead to variations in the device which results in faulty behaviour.

- In the switching material, the CF is formed along the grain boundaries of the poly-crystal. Since the distribution of the grain-boundaries varies with every device, the resistance range of the device varies as well.