# Optimizing generator protection by developing an islanding tripping scheme with Siemens SIPROTEC 5 IED's for DOW Industrial network

by Mihaela Petcu

to obtain the degree of Master of Science at Delft University of Technology, to be defended publicly on 8th of September, 2025

Student number: 5843758

Thesis committee: Prof. dr. ir. M. Popov, TU Delft, supervisor

Dr. ir. M. G. Niasar, TU Delft

Ir. S. de Clippelaar, DOW Energy System Technology Center (ESTC)

Dr. ir. K. Polat, Siemens PTI

## **Abstract**

Dow Terneuzen, the second-largest site of Dow Chemical, relies on the ELSTA cogeneration plant to supply electricity and steam to its production facilities while contributing to the Dutch national grid. Ensuring stable operation is critical for safety and reliability. While internal disturbances are managed by existing protections, external grid faults pose challenges for detection and for enabling a controlled transition to islanded operation.

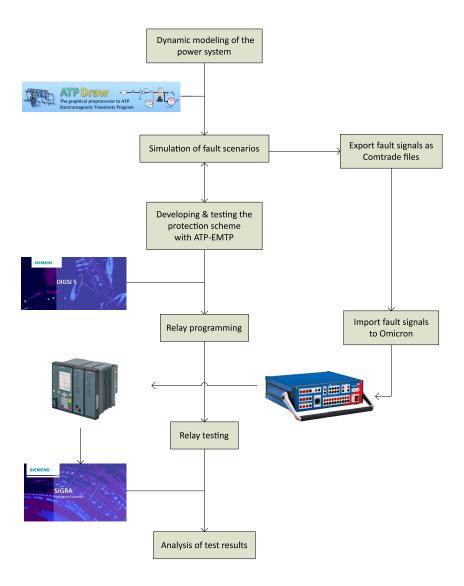

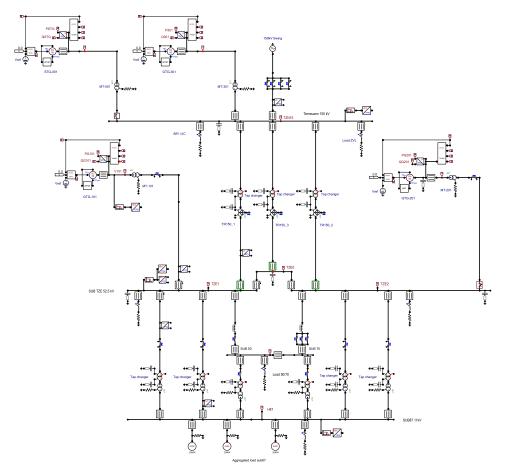

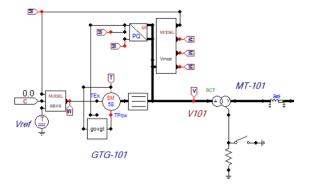

This thesis develops and validates an islanding tripping scheme for Dow Terneuzen. The objectives are to design a protection logic based on frequency and undervoltage detection, establish a load shedding strategy to maintain generator stability during islanding and validate the protection logic using online simulations and hardware testing. A dynamic model of the power system was created in ATP-EMTP, including synchronous machines with governors and excitation systems, transformers, and dynamic loads. Fault scenarios were simulated to assess stability, determine critical clearing times, and validate the protection logic. The protection logic was then programmed into a Siemens 7UM85 relay using DIGSI5 and tested with an Omicron CMC 356+, where COMTRADE signals from simulations were replayed into the relay. Relay responses were analyzed using the Fault Record tool SIGRA and compared with the online simulation results.

The results show how generator dynamics affect stability, confirm the need for rapid load shedding, and highlight challenges in designing a reliable islanding tripping scheme. The comparison between ATP-EMTP simulations and relay tests demonstrates the effectiveness of the proposed scheme and provides practical guidance for implementing reliable islanding protection at Dow Terneuzen.

# Contents

| ΑI | bstract                                                                                                                                                                                                                                                                    | i                                                                   |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| A  | cknowledgement                                                                                                                                                                                                                                                             | vii                                                                 |

| 1  | Introduction  1.1 Problem definition and objectives                                                                                                                                                                                                                        | 1<br>1<br>2<br>2<br>4<br>5                                          |

|    | 2.1 Classification of Islanding Detection Methods 2.1.1 Local-Area Measurement-Based Schemes 2.1.2 Wide-Area Measurement-Based Schemes 2.2 Current Research Gaps and Future Directions 2.3 Conclusion                                                                      | 5<br>5<br>6<br>7<br>7                                               |

| 3  | <ul><li>3.5 Fault Modeling and Simulation Scenarios</li><li>3.6 Measurement and Monitoring Systems</li></ul>                                                                                                                                                               | 8<br>10<br>11<br>12<br>13<br>14<br>16<br>17<br>19<br>20<br>20<br>21 |

| 4  | 4.1 Test Scenarios and Simulation Parameters 4.1.1 Fault locations  4.2 Determining the Critical Clearing Time (CCT) 4.2.1 Three-phase fault (3LG) 4.2.2 Two-phase fault (2LG) 4.2.3 Single-phase fault (1LG) 4.2.4 Conclusions  4.3 Machine Dynamics and Control Response | 22<br>22<br>23<br>24<br>24<br>27<br>28<br>29<br>30<br>32<br>34      |

| 5  | 5.1 Dutch NetCode Requirements  5.2 Protection Settings                                                                                                                                                                                                                    | 35<br>35<br>37<br>37<br>38<br>39                                    |

Contents

| ^  | Sou                | rce Code                                                              | 67                    |

|----|--------------------|-----------------------------------------------------------------------|-----------------------|

| Re | ferer              | nces                                                                  | 66                    |

| 7  | <b>Con</b> 7.1 7.2 | Conclusion  Conclusion  Recommendations for future work               | <b>64</b><br>64<br>65 |

|    | 6.6                | Discussion                                                            | 63                    |

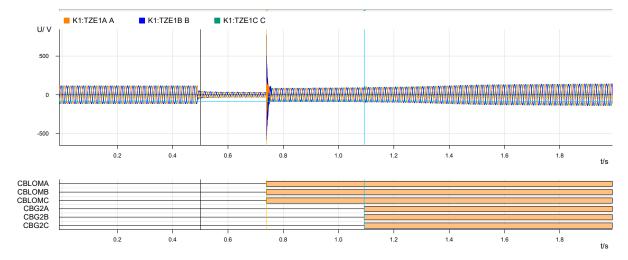

|    | 6.5                | Results comparison                                                    | 62                    |

|    | 6.4                | Results 7UM85                                                         | 62                    |

|    |                    | 6.3.6 Test Case F8                                                    | 61                    |

|    |                    | 6.3.5 Test Cases F6-7                                                 | 61                    |

|    |                    | 6.3.3 Test Case F3-F4                                                 | 59<br>60              |

|    |                    | 6.3.2 Test Case F2                                                    | 58                    |

|    |                    | 6.3.1 Test Case F1                                                    | 58                    |

|    | 6.3                | Omicron Testing                                                       | 57                    |

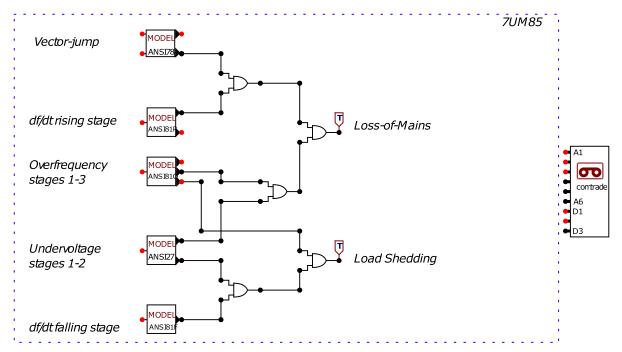

|    |                    | 6.2.4 Protection Logic                                                | 56                    |

|    |                    | 6.2.3 Overcurrent blocking                                            | 55                    |

|    |                    | 6.2.2 Protection Settings                                             | 55                    |

|    | 6.2                | Protection Device Configuration                                       | 54<br>54              |

| -  | 6.1                | Test Overview & Setup                                                 | 53                    |

| 6  | Hard               | dware Testing                                                         | 53                    |

|    | 5.6                | Conclusions                                                           | 52                    |

|    | 5.5                | Results ATP-EMTP                                                      | 51                    |

|    |                    | 5.4.4 Test Cases F6-7                                                 | 50<br>51              |

|    |                    | 5.4.3 Test Case F5                                                    | 49                    |

|    |                    | 5.4.2 Test Cases F2-4                                                 | 48                    |

|    |                    | 5.4.1 Test Case F1                                                    | 46                    |

|    | 5.4                | Protection Scheme Testing and Validation                              | 46                    |

|    |                    | <ul><li>5.3.4 Thresholds and Settings</li></ul>                       | 44<br>45              |

|    |                    | 5.3.3 Signal Processing Models                                        | 43<br>44              |

|    |                    | 5.3.2 Logic Architecture                                              | 42                    |

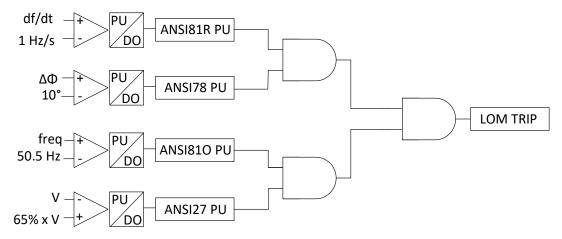

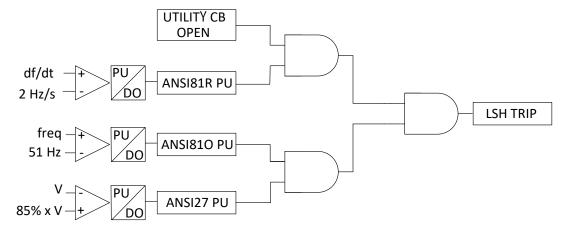

|    |                    | 5.3.1 Measured Values                                                 | 42                    |

|    | 5.3                | Protection Logic Development with ATP-EMTP                            | 42                    |

|    |                    | 5.2.4 Undervoltage Protection with Positive Sequence Voltage (ANSI27) | 40                    |

# List of Figures

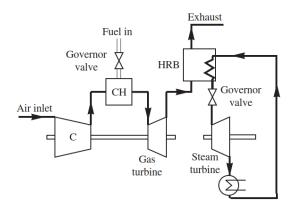

| 3.1 Example of a Combined-Cycle Gas Turbine [12] 3.2 Single line diagram of Dow's Industrial Network 3.3 Synchronous machine & control systems 3.4 Rotating Machine model 3.5 Simplified Excitation System (SEXS) block diagram 3.6 Exitation System & AVR MODEL in ATP-EMTP 3.7 AVR & Excitation System 3.8 GAST MODEL [10] 3.9 Governor Model with TACS 3.10 Governor Working Principle 3.11 MT-101 unit transformer BCTRAN model 3.12 Transformer Models 3.13 Static Load Model 3.14 Dynamic Load Model 3.15 Line Model 3.16 Line Model 3.17 Utility Grid 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault locations F2-F4: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms 4.3 Fault locations F2-F4: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=580 4.4 Scenario 1 - Fault location F1: CCT = 320 ms 4.5 Scenario 1 - Fault location F1: CCT = 600 ms 4.6 Scenario 2 - Fault location F1: CCT = 600 ms 4.8 Scenario 3 - Fault location F1: CCT = 600 ms 4.9 Fault location F2-F4: CCT-S1 = 580 ms, CCT-S2 = 4200 ms, CCT-S3 = 4200 ms 4.10 Fault location F2-F4: CCT = 550 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 3 - Fault location F1: CCT = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.12 Scenario 1 - Fault location F1: CCT = 440 ms, F2-4: CCT = 520 ms 4.13 Scenario 3 - Fault location F1: CCT = 880 ms, F2-4: CCT = 520 ms 4.10 Fault location F2-F4: CCT = 580 ms, F2-4: CCT = 520 ms 4.12 Scenario 1 - Fault location F1: CCT = 4200 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 1-3 - Fault location F1: CCT = 1500 ms, CT-S2 = 720 ms, CCT-S3 = 1400 ms 4.15 Scenario 1-3 - Fault location F1: CCT = 10 s 4.16 Scenario 1-3 - Fault location F1: CCT = 10 s 4.17 Scenario 1-3 - Fault location F1: CCT = 10 s 4.18 Scenario 1-3 - Fault location F1: CCT = 10 s 4.19 Sover-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.24 Currents measured at non-faulted fee | 1.1  | Processes used to fulfill the thesis objectives                           | 2  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------|----|

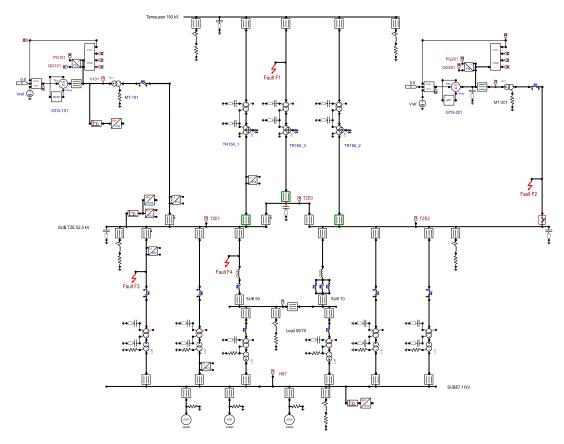

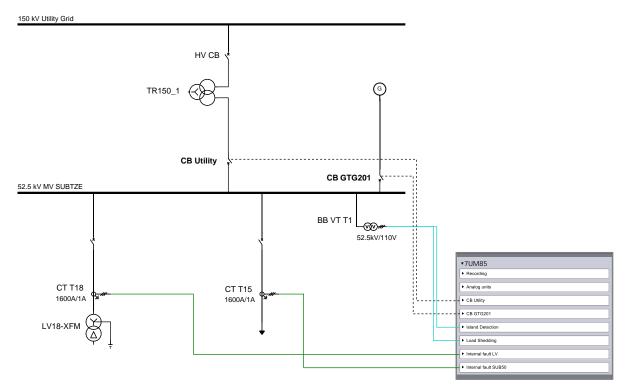

| 3.2 Single line diagram of Dow's Industrial Network 3.3 Synchronous machine & control systems 3.4 Rotating Machine model 3.5 Simplified Excitation System (SEXS) block diagram 3.6 Exitation System & AVR MODEL in ATP-EMTP 3.7 AVR & Excitation System 3.8 GAST MODEL [10] 3.9 Governor Model with TACS 3.10 Governor Working Principle 3.11 MT-101 unit transformer BCTRAN model 3.12 Transformer Models 3.13 Static Load Model 3.14 Dynamic Load Model 3.15 Line Model 3.16 Branch Models 3.17 Utility Grid 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault location F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=580 4.4 Scenario 1 - Fault location F2-F4: CCT = 320 ms 4.5 Scenario 1 - Fault location F2-F4: CCT = 300 ms 4.6 Scenario 2 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 400 ms 4.7 Scenario 3 - Fault location F1: CCT = 580 ms 4.8 Scenario 3 - Fault location F1: CCT = 580 ms 4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 1400 ms 4.10 Fault location F1: CCT = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.12 Scenario 3 - Fault location F1: CCT = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.13 Scenario 3 - Fault location F1: CCT = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.14 Scenario 3 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.15 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.16 Scenario 3 - Fault location F1: CCT = 800 ms 4.17 Scenario 1 - Fault location F1: CCT = 1400 ms 4.18 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 720 ms 4.19 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 720 ms 4.19 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 720 ms 4.19 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 720 ms 4.19 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 720 ms 4.19 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 720 ms 4.19 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 720 ms 4.19 | 3.1  | Example of a Combined-Cycle Gas Turbine [12]                              | 8  |

| 3.3 Synchronous machine & control systems 3.4 Rotating Machine model 3.5 Simplified Excitation System (SEXS) block diagram 3.6 Exitation System & AVR MODEL in ATP-EMTP 3.7 AVR & Excitation System 3.8 GAST MODEL [10] 3.9 Governor Model with TACS 3.10 Governor Working Principle 3.11 MT-101 unit transformer BCTRAN model 3.12 Transformer Models 3.13 Static Load Model 3.14 Dynamic Load Model 3.15 Line Model 3.16 Branch Models 3.17 Utility Grid 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault locations F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms 4.3 Fault locations F2-F4: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=580 4.5 Scenario 1 - Fault location F1: CCT = 320 ms 4.5 Scenario 1 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 440 ms, Fault location F2-F4: CCT = 580 ms 4.7 Scenario 3 - Fault location F1: CCT = 580 ms 4.8 Scenario 3 - Fault location F2-F4: CCT = 580 ms 4.9 Fault locations F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 4200 ms 4.10 Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.12 Scenario 3 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.13 Scenario 3 - Fault location F1: CCT = 580 ms, F2-4: CCT = 720 ms 4.14 Scenario 3 - Fault location F1: CCT = 580 ms, F2-4: CCT = 720 ms 4.15 Scenario 3 - Fault location F1: CCT = 580 ms, F2-4: CCT = 720 ms 4.16 Scenario 3 - Fault location F1: CCT = 10 s 4.17 Scenario 1 - Fault location F1: CCT = 10 s 4.18 Scenario 3 - Fault location F1: CCT = 10 s 4.19 Scenario 3 - Fault location F1: CCT = 10 s 4.19 Scenario 3 - Fault location F1: CCT = 10 s 4.10 Scenario 1 - Fault location F1: CCT = 10 s 4.11 Scenario 1 - Fault location F1: CCT = 10 s 4.12 Scenario 1 - Fault location F1: CCT = 10 s 4.13 Scenario 3 - Fault location F1: CCT = 10 s 4.14 Scenario 1 - Fault location F1: CCT = 10 s 4.15 Scenario 1 - Fault location F1: CCT = 10 s 4.16 Scenario 1 - Fault location F1: CCT = 10 s 4.17 Scenario 1 - Fault location F1: CCT = 10 s 4.18 Scenario 1 - Fault locat | 3.2  |                                                                           | 11 |

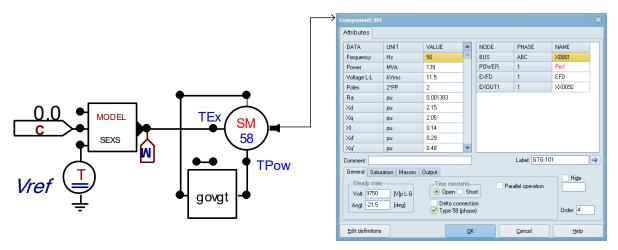

| 3.4 Rotating Machine model 3.5 Simplified Excitation System (SEXS) block diagram 3.6 Exitation System & AVR MODEL in ATP-EMTP 3.7 AVR & Excitation System 3.8 GAST MODEL [10] 3.9 Governor Model with TACS 3.10 Governor Working Principle 3.11 MT-101 unit transformer BCTRAN model 3.12 Transformer Models 3.13 Static Load Model 3.14 Dynamic Load Model 3.15 Line Model 3.15 Line Model 3.16 Branch Models 3.17 Utility Grid 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault location F1: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=660ms 4.3 Fault location F1: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=580 4.4 Scenario 1 - Fault location F1: CCT = 320 ms 4.5 Scenario 1 - Fault location F1: CCT = 300 ms 4.6 Scenario 2 - Fault location F1: CCT = 400 ms 4.7 Scenario 3 - Fault location F1: CCT = 600 ms 4.8 Scenario 3 - Fault location F1: CCT = 580 ms, CCT-S2 = 800 ms, CCT-S3 = 4200 ms 4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.10 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 80 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 400 ms 4.12 Scenario 3 - Fault location F1: CCT = 4200 ms 4.13 Scenario 1 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F1: CCT = 4200 ms 4.15 Scenario 1 - Fault location F1: CCT = 4200 ms 4.16 Scenario 1 - Fault location F1: CCT = 4200 ms 4.17 Scenario 3 - Fault location F1: CCT = 4200 ms 4.18 Scenario 1 - Fault location F1: CCT = 4200 ms 4.19 Scenario 1 - Fault location F1: CCT = 4200 ms 4.10 Scenario 1 - Fault location F1: CCT = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 4200 ms 4.12 Scenario 3 - Fault location F1: CCT = 1400 ms 4.13 Scenario 1 - Fault location F1: CCT = 1400 ms 4.14 Scenario 1 - Fault location F1: CCT = 1400 ms 4.15 Scenario 1 - Fault location F1: CCT = 1400 ms 4.16 Scenario 1 - Fault location F1: CCT = 1400 ms 4.17 Scenario 1 - Fault location F1: CCT = 1400 ms 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.20 Excitation System Response 4.21 Frequency Stab | 3.3  |                                                                           | 12 |

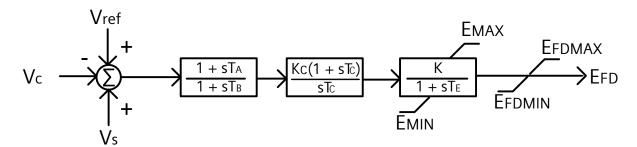

| 3.5 Simplified Excitation System (SEXS) block diagram 3.6 Exitation System & AVR MODEL in ATP-EMTP 3.7 AVR & Excitation System 3.8 GAST MODEL [10] 3.9 Governor Model with TACS 3.10 Governor Working Principle 3.11 MT-101 unit transformer BCTRAN model 3.12 Transformer Models 3.13 Static Load Model 3.14 Dynamic Load Model 3.15 Line Model 3.16 Branch Models 3.17 Utility Grid 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault locations F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms 4.3 Fault locations F2-F4: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=580 4.4 Scenario 1 - Fault location F1: CCT = 320 ms 4.5 Scenario 1 - Fault location F1: CCT = 420 ms 4.6 Scenario 2 - Fault location F1: CCT = 600 ms 4.7 Scenario 3 - Fault location F1: CCT = 600 ms 4.8 Scenario 3 - Fault location F1: CCT = 580 ms 4.9 Fault locations F2-F4: CCT-S1 = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.10 Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.10 Fault locations F2-F4: CCT = 580 ms, F2-4: CCT = 520 ms 4.11 Scenario 3 - Fault location F1: CCT = 800 ms 4.12 Scenario 3 - Fault location F1: CCT = 800 ms 4.13 Scenario 3 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.14 Scenario 3 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.15 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.16 Scenario 3 - Fault location F1: CCT = 580 ms, F2-4: CCT = 720 ms 4.17 Scenario 3 - Fault location F1: CCT = 4200 ms 4.18 Scenario 3 - Fault location F1: CCT = 1400 ms 4.19 Scenario 1-3 - Fault location F1: CCT = 1400 ms 4.10 Scenario 1-3 - Fault location F1: CCT = 1400 ms 4.11 Scenario 1-3 - Fault location F1: CCT = 1400 ms 4.12 Scenario 1-3 - Fault location F1: CCT = 1400 ms 4.13 Scenario 1-3 - Fault location F1: CCT = 1400 ms 4.14 Scenario 3 - Fault location F1: CCT = 1400 ms 4.15 Scenario 1-3 - Fault location F1: CCT = 1400 ms 4.16 Scenario 1-3 - Fault location F1: CCT = 1400 ms 4.17 Scenario 1-3 - Fault location F1: CCT = 1400 ms 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation S |      |                                                                           | 12 |

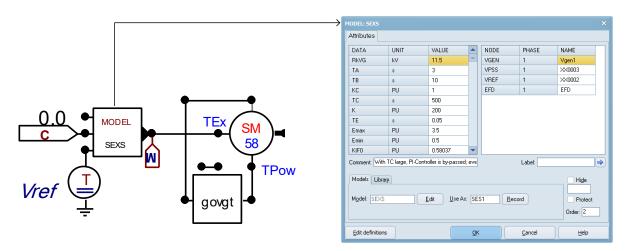

| 3.6 Exitation System & AVR MODEL in ATP-EMTP 3.7 AVR & Excitation System 3.8 GAST MODEL [10] 3.9 Governor Working Principle 3.10 Governor Working Principle 3.11 MT-101 unit transformer BCTRAN model 3.12 Transformer Models 3.13 Static Load Model 3.14 Dynamic Load Model 3.15 Line Model 3.16 Branch Models 3.17 Utility Grid 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault locations F2-F4: CCT-S1=300ms, CCT-S2=440ms, CCT-S3=660ms 4.3 Fault locations F2-F4: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=580 4.4 Scenario 1 - Fault location F1: CCT = 320 ms 4.5 Scenario 1 - Fault location F2-F4: CCT = 300 ms 4.6 Scenario 2 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 400 ms 4.7 Scenario 3 - Fault location F1: CCT = 600 ms 4.8 Scenario 3 - Fault location F2-F4: CCT = 580 ms 4.9 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.12 Scenario 2 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.13 Scenario 3 - Fault location F1: CCT = 580 ms, F2-4: CCT = 720 ms 4.14 Scenario 1 - Fault location F1: CCT = 4200 ms 4.15 Scenario 1 - Fault location F1: CCT = 1400 ms 4.16 Scenario 1 - Fault location F2-4: CCT = 1400 ms 4.17 Scenario 1 - Fault location F2-4: CCT = 10 s 4.18 Scenario 1 - Fault location F1-4: CCT > 10 s 4.19 Governor System Response 4.20 Excitation System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at non-faulted feeders for an internal fault 5.1 Basic Principle of Vector Jump protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip                                                                                                                                                       |      | Simplified Excitation System (SEXS) block diagram                         | 13 |

| 3.7 AVR & Excitation System 3.8 GAST MODEL [10] 3.9 Governor Model with TACS 3.10 Governor Working Principle 3.11 MT-101 unit transformer BCTRAN model 3.12 Transformer Models 3.13 Static Load Model 3.14 Dynamic Load Model 3.15 Line Model 3.16 Branch Models 3.17 Utility Grid 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault locations F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms 4.3 Fault locations F2-F4: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=580 4.4 Scenario 1 - Fault location F1: CCT = 320 ms 4.5 Scenario 1 - Fault location F1: CCT = 320 ms 4.5 Scenario 2 - Fault location F1: CCT = 600 ms 4.6 Scenario 3 - Fault location F1: CCT = 600 ms 4.7 Scenario 3 - Fault location F1: CCT = 600 ms 4.8 Scenario 3 - Fault location F2-F4: CCT = 580 ms 4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 4200 ms 4.10 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.12 Scenario 3 - Fault location F1: CCT = 800 ms, F2-4: CCT = 520 ms 4.13 Scenario 3 - Fault location F1: CCT = 800 ms, F2-4: CCT = 520 ms 4.14 Scenario 3 - Fault location F1: CCT = 800 ms, F2-4: CCT = 720 ms 4.15 Scenario 3 - Fault location F1: CCT = 120 ms 4.16 Scenario 1-3 - Fault location F1: CCT = 1400 ms 4.17 Scenario 1-3 - Fault location F1: CCT > 10 s 4.18 Scenario 1-3 - Fault location F1: CCT > 10 s 4.19 Governor System Response 4.20 Excitation System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.24 Currents measured at the outgoing feeders during a 3LG fault 4.24 Currents measured at non-faulted feeders for an internal fault 5.1 Basic Principle of Vector Jump protection Trip 5.1 Logic Diagram for Load Shedding Protection Trip 5.2 Logic Diagram for Load Shedding Protection Trip                                                                                                                   |      |                                                                           | 14 |

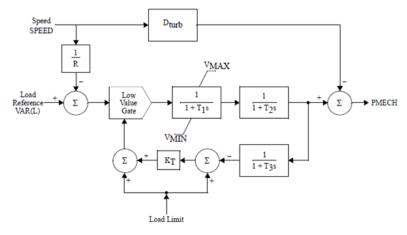

| 3.8 GAST MODEL [10] 3.9 Governor Model with TACS 3.10 Governor Working Principle 3.11 MT-101 unit transformer BCTRAN model 3.12 Transformer Models 3.13 Static Load Model 3.14 Dynamic Load Model 3.15 Line Model 3.16 Branch Models 3.17 Utility Grid 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault location F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms 4.3 Fault location F2: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=580 4.4 Scenario 1 - Fault location F1: CCT = 320 ms 4.5 Scenario 1 - Fault location F2: CCT = 300 ms 4.6 Scenario 1 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 400 ms 4.7 Scenario 3 - Fault location F1: CCT = 600 ms 4.8 Scenario 3 - Fault location F2: F4: CCT = 580 ms 4.9 Fault locations F2: F4: CCT-S1 = 580 ms, CCT-S2 = 80 ms, CCT-S3 = 4200 ms 4.10 Fault location F1: CCT = 1 580 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.12 Scenario 2 - Fault location F1: CCT = 4200 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F1: CCT = 4200 ms 4.15 Scenario 1-3 - Fault location F1: CCT = 1400 ms 4.16 Scenario 1-3 - Fault location F1: CCT = 100 ms 4.17 Scenario 1-3 - Fault location F1: CCT = 100 ms 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the MV busbar during a 3LG fault 4.24 Currents measured at non-faulted feeders for an internal fault 5.1 Basic Principle of Vector Jump protection Trip 5.1 Logic Diagram for Losa-of-Mains Protection Trip 5.2 Logic Diagram for Losa-of-Mains Protection Trip 5.3 Logic Diagram for Losa-of-Mains Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip                                                                                                                                                                                                                                       |      |                                                                           | 14 |

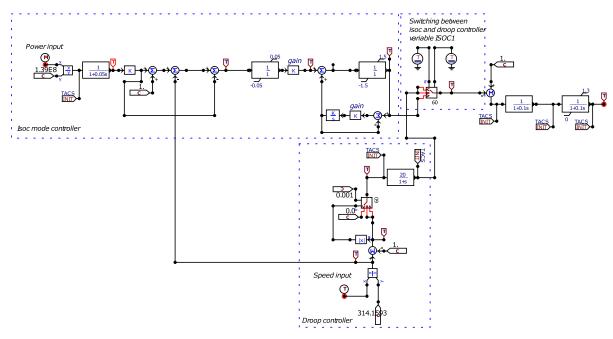

| 3.9 Governor Model with TACS 3.10 Governor Working Principle 3.11 MT-101 unit transformer BCTRAN model 3.12 Transformer Models 3.13 Static Load Model 3.14 Dynamic Load Model 3.15 Line Model 3.16 Branch Models 3.17 Utility Grid 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault location F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms 4.3 Fault location F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=580 4.4 Scenario 1 - Fault location F1: CCT = 320 ms 4.5 Scenario 1 - Fault location F1: CCT = 300 ms 4.6 Scenario 1 - Fault location F2-F4: CCT = 300 ms 4.7 Scenario 3 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 400 ms 4.8 Scenario 3 - Fault location F1: CCT = 580 ms 4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 4200 ms 4.10 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 4200 ms 4.10 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 880 ms, F2-4: CCT = 520 ms 4.12 Scenario 2 - Fault location F1: CCT = 4200 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F1: CCT = 4200 ms 4.15 Scenario 1-3 - Fault location F1: CCT = 1400 ms 4.16 Scenario 1-3 - Fault location F1: CCT = 1400 ms 4.17 Scenario 1-3 - Fault location F1: CCT > 10 s 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the MV busbar during a 3LG fault 4.24 Currents measured at non-faulted feeders for an internal fault 5.1 Basic Principle of Vector Jump protection Trip 5.1 Logic Diagram for Load Shedding Protection Trip 5.2 Logic Diagram for Load Shedding Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip                                                                                                                                                                                     |      | GAST MODEL [10]                                                           | 15 |

| 3.10 Governor Working Principle 3.11 MT-101 unit transformer BCTRAN model 3.12 Transformer Models 3.13 Static Load Model 3.14 Dynamic Load Model 3.15 Line Model 3.16 Branch Models 3.17 Utility Grid 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.3 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.4 Fault locations sa per ATP-EMTP SLD of DOW industrial network 4.5 Fault locations F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms 4.6 Scenario 1 - Fault location F1: CCT = 320 ms 4.7 Scenario 1 - Fault location F1: CCT = 320 ms 4.8 Scenario 2 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 400 ms 4.8 Scenario 3 - Fault location F1: CCT = 600 ms 4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 4200 ms 4.10 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.10 Fault location F2-F4: CCT = 580 ms, F2-4: CCT = 520 ms 4.11 Scenario 1 - Fault location F1: CCT = 880 ms, F2-4: CCT = 520 ms 4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F1: CCT = 4200 ms 4.15 Scenario 1-3 - Fault location F1: CCT = 4200 ms 4.16 Scenario 1-3 - Fault location F1-4: CCT > 10 s 4.17 Scenario 1-3 - Fault location F1-4: CCT > 10 s 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the outgoing feeders during a 3LG fault 4.24 Currents measured at the outgoing feeders during a 3LG fault 5.1 Basic Principle of Vector Jump protection [1] 5.1 Logic Diagram for Loas-of-Mains Protection Trip 5.2 Logic Diagram for Loas Shedding Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip                                                                                                                                                                        |      |                                                                           | 15 |

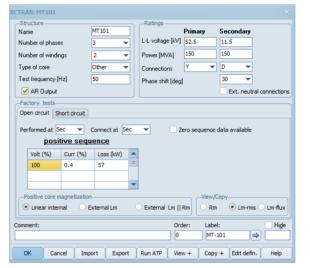

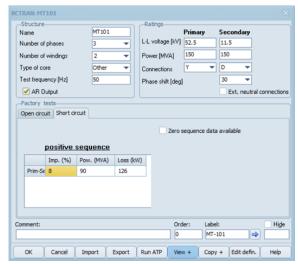

| 3.11 MT-101 unit transformer BCTRAN model 3.12 Transformer Models 3.13 Static Load Model 3.14 Dynamic Load Model 3.15 Line Model 3.16 Branch Models 3.17 Utility Grid 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault location F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms 4.3 Fault location F2: F4: CCT-S1=300ms, CCT-S2=440ms, CCT-S3=580 4.4 Scenario 1 - Fault location F1: CCT = 320 ms 4.5 Scenario 1 - Fault location F1: CCT = 320 ms 4.6 Scenario 1 - Fault location F2: F4: CCT = 300 ms 4.7 Scenario 3 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 400 ms 4.8 Scenario 3 - Fault location F1: CCT = 580 ms 4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 4200 ms 4.10 Fault location F1: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.12 Scenario 2 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.13 Scenario 3 - Fault location F1: CCT = 480 ms, F2-4: CCT = 720 ms 4.14 Scenario 3 - Fault location F1: CCT = 4400 ms 4.15 Scenario 3 - Fault location F1: CCT = 4400 ms 4.16 Scenario 1-3 - Fault location F1: CCT > 10 s 4.17 Scenario 1-3 - Fault location F1: CCT > 10 s 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the outgoing feeders during a 3LG fault 4.24 Currents measured at the outgoing feeders during a 3LG fault 5.1 Basic Principle of Vector Jump protection [1] 5.2 Logic Diagram for Loas-of-Mains Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip                                                                                                                                                                                                                                                                                                                                       |      |                                                                           | 16 |

| 3.12 Transformer Models 3.13 Static Load Model 3.14 Dynamic Load Model 3.15 Line Model 3.16 Branch Models 3.17 Utility Grid 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault location F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms 4.3 Fault locations F2-F4: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=580 4.4 Scenario 1 - Fault location F1: CCT = 320 ms 4.5 Scenario 1 - Fault location F1: CCT = 420 ms 4.6 Scenario 2 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 440 ms 4.7 Scenario 3 - Fault location F1: CCT = 680 ms 4.8 Scenario 3 - Fault location F1: CCT = 580 ms 4.9 Fault locations F2-F4: CCT-S1 = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 520 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F1: CCT = 4200 ms 4.15 Scenario 1-3 - Fault location F1: CCT = 4200 ms 4.16 Scenario 1-3 - Fault location F2-4: CCT = 1400 ms 4.17 Scenario 1-3 - Fault location F1: CCT > 10 s 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the outgoing feeders during a 3LG fault 4.24 Currents measured at the outgoing feeders during a 3LG fault 4.25 Logic Diagram for Loss-of-Mains Protection [1] 5.1 Basic Principle of Vector Jump protection [1] 5.2 Logic Diagram for Load Shedding Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip                                                                                                                                                                                                                                                                                                                                     |      |                                                                           | 16 |

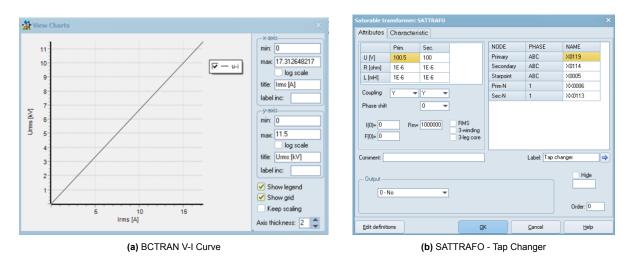

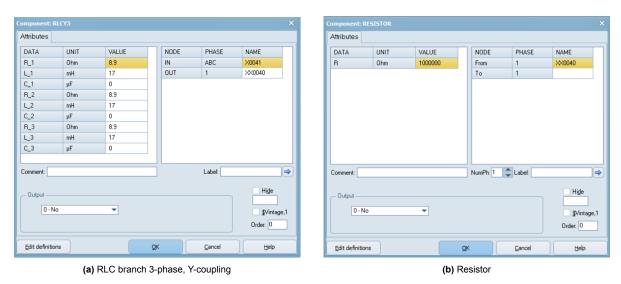

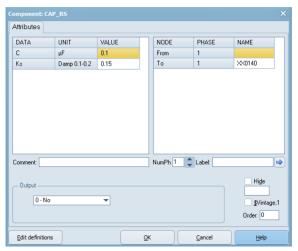

| 3.13 Static Load Model 3.14 Dynamic Load Model 3.15 Line Model 3.16 Branch Models 3.17 Utility Grid 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault location F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms 4.3 Fault locations F2-F4: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=580 4.4 Scenario 1 - Fault location F1: CCT = 320 ms 4.5 Scenario 1 - Fault location F1: CCT = 320 ms 4.6 Scenario 1 - Fault location F1: CCT = 400 ms 4.7 Scenario 3 - Fault location F1: CCT = 600 ms 4.8 Scenario 3 - Fault location F1: CCT = 600 ms 4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 80 ms, CCT-S3 = 4200 ms 4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 520 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F1: CCT = 4200 ms 4.15 Scenario 3 - Fault location F1: CCT = 4200 ms 4.16 Scenario 1-3 - Fault location F1: CCT > 10 s 4.17 Scenario 1-3 - Fault location F1: CCT > 10 s 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the outgoing feeders during a 3LG fault 4.24 Currents measured at non-faulted feeders for an internal fault 5.1 Basic Principle of Vector Jump protection [1] 5.1 Logic Diagram for Load Shedding Protection Trip 5.2 Logic Diagram for Load Shedding Protection Trip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |                                                                           |    |

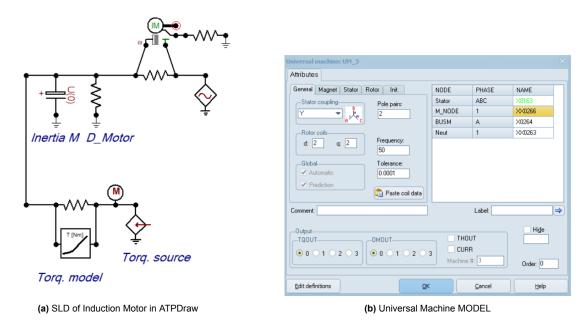

| 3.14 Dynamic Load Model 3.15 Line Model 3.16 Branch Models 3.17 Utility Grid 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault location F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms 4.3 Fault locations F2-F4: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=580 4.4 Scenario 1 - Fault location F1: CCT = 320 ms 4.5 Scenario 1 - Fault location F1: CCT = 320 ms 4.6 Scenario 2 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 440 ms 4.7 Scenario 3 - Fault location F1: CCT = 600 ms 4.8 Scenario 3 - Fault location F1: CCT = 600 ms 4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 4200 ms 4.10 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.12 Scenario 2 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F1: CCT = 4200 ms 4.15 Scenario 1-3 - Fault location F1: CCT = 1400 ms 4.16 Scenario 1-3 - Fault location F1: CCT > 10 s 4.17 Scenario 1-3 - Fault location F1: CCT > 10 s 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the MV busbar during a 3LG fault 4.24 Currents measured at non-faulted feeders for an internal fault 5.1 Basic Principle of Vector Jump protection [1] 5.2 Logic Diagram for Loss-of-Mains Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |                                                                           | 17 |

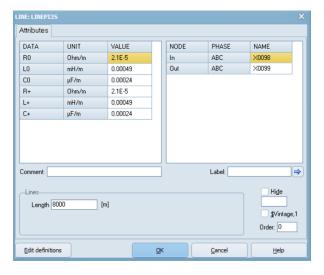

| 3.15 Line Model 3.16 Branch Models 3.17 Utility Grid 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault location F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms 4.3 Fault locations F2-F4: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=580 4.4 Scenario 1 - Fault location F1: CCT = 320 ms 4.5 Scenario 1 - Fault location F2-F4: CCT = 300 ms 4.6 Scenario 2 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 400 ms 4.7 Scenario 3 - Fault location F1: CCT = 600 ms 4.8 Scenario 3 - Fault location F2-F4: CCT = 580 ms 4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 880 ms, F2-4: CCT = 520 ms 4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F1: CCT = 1400 ms 4.15 Scenario 1-3 - Fault location F1: CCT = 1400 ms 4.16 Scenario 1-3 - Fault location F1: CCT > 10 s 4.17 Scenario 1-3 - Fault location F1: CCT > 10 s 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the outgoing feeders during a 3LG fault 4.24 Currents measured at non-faulted feeders for an internal fault 5.1 Basic Principle of Vector Jump protection [1] 5.2 Logic Diagram for Loss-of-Mains Protection Trip 5.3 Logic Diagram for Losd Shedding Protection Trip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |                                                                           | 17 |

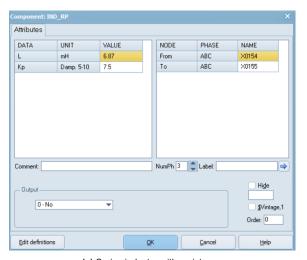

| 3.16 Branch Models 3.17 Utility Grid 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault location F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms 4.3 Fault locations F2-F4: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=580 4.4 Scenario 1 - Fault location F1: CCT = 320 ms 4.5 Scenario 1 - Fault location F2-F4: CCT = 300 ms 4.6 Scenario 2 - Fault location F2-F4: CCT = 300 ms 4.7 Scenario 3 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 400 ms 4.8 Scenario 3 - Fault location F1: CCT = 600 ms 4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 4200 ms 4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.12 Scenario 2 - Fault location F1: CCT = 480 ms, F2-4: CCT = 720 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F1: CCT = 4200 ms 4.15 Scenario 1-3 - Fault location F1: CCT > 10 s 4.16 Scenario 1-3 - Fault location F1: CCT > 10 s 4.17 Scenario 1-3 - Fault location F1: CCT > 10 s 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the outgoing feeders during a 3LG fault 4.24 Currents measured at non-faulted feeders for an internal fault 5.1 Basic Principle of Vector Jump protection [1] 5.2 Logic Diagram for Loss-of-Mains Protection Trip 5.3 Logic Diagram for Losd Shedding Protection Trip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                                                                           | 18 |

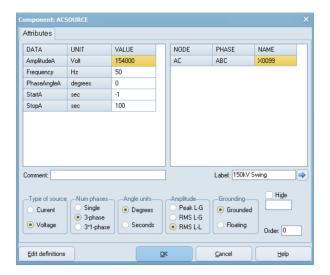

| <ul> <li>3.17 Utility Grid</li> <li>4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network</li> <li>4.2 Fault location F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms</li> <li>4.3 Fault locations F2-F4: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=580</li> <li>4.4 Scenario 1 - Fault location F1: CCT = 320 ms</li> <li>4.5 Scenario 1 - Fault location F2-F4: CCT = 300 ms</li> <li>4.6 Scenario 2 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 400 ms</li> <li>4.7 Scenario 3 - Fault location F1: CCT = 600 ms</li> <li>4.8 Scenario 3 - Fault location F2-F4: CCT = 580 ms</li> <li>4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 4200 ms</li> <li>4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms</li> <li>4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms</li> <li>4.12 Scenario 1 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms</li> <li>4.13 Scenario 3 - Fault location F1: CCT = 4200 ms</li> <li>4.14 Scenario 3 - Fault location F1: CCT = 400 ms</li> <li>4.15 Scenario 1-3 - Fault location F1: CCT &gt; 10 s</li> <li>4.16 Scenario 1-3 - Fault location F1: CCT &gt; 10 s</li> <li>4.17 Scenario 1-3 - Fault location F1-4: CCT &gt; 10 s</li> <li>4.18 Power-Angle Relationship</li> <li>4.19 Governor System Response</li> <li>4.20 Excitation System Response</li> <li>4.21 Frequency Stability</li> <li>4.22 Voltage measured at the MV busbar during a 3LG fault</li> <li>4.23 Currents measured at the outgoing feeders during a 3LG fault</li> <li>4.24 Currents measured at non-faulted feeders for an internal fault</li> <li>5.1 Basic Principle of Vector Jump protection [1]</li> <li>5.2 Logic Diagram for Loss-of-Mains Protection Trip</li> <li>5.3 Logic Diagram for Load Shedding Protection Trip</li> </ul>                                                                                                                                                                                                                                                                          |      |                                                                           | 19 |

| 4.1 Fault locations as per ATP-EMTP SLD of DOW industrial network 4.2 Fault location F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms 4.3 Fault locations F2-F4: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=580 4.4 Scenario 1 - Fault location F1: CCT = 320 ms 4.5 Scenario 1 - Fault location F2-F4: CCT = 300 ms 4.6 Scenario 2 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 400 ms 4.7 Scenario 3 - Fault location F1: CCT = 600 ms 4.8 Scenario 3 - Fault location F2-F4: CCT = 580 ms 4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 4200 ms 4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F1: CCT = 4200 ms 4.15 Scenario 1-3 - Fault location F1: CCT > 10 s 4.16 Scenario 1-3 - Fault location F1: CCT > 10 s 4.17 Scenario 1-3 - Fault location F1-4: CCT > 10 s 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the outgoing feeders during a 3LG fault 4.24 Currents measured at non-faulted feeders for an internal fault 5.1 Basic Principle of Vector Jump protection [1] 5.2 Logic Diagram for Load Shedding Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                                                           | 19 |

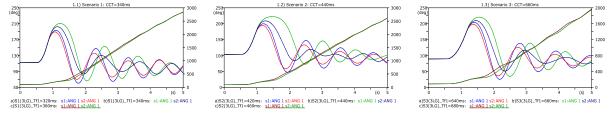

| <ul> <li>4.2 Fault location F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms</li> <li>4.3 Fault locations F2-F4: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=580</li> <li>4.4 Scenario 1 - Fault location F1: CCT = 320 ms</li> <li>4.5 Scenario 1 - Fault location F2-F4: CCT = 300 ms</li> <li>4.6 Scenario 2 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 400 ms</li> <li>4.7 Scenario 3 - Fault location F1: CCT = 600 ms</li> <li>4.8 Scenario 3 - Fault location F2-F4: CCT = 580 ms</li> <li>4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 4200 ms</li> <li>4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms</li> <li>4.11 Scenario 1 - Fault location F1: CCT = 880 ms, F2-4: CCT = 520 ms</li> <li>4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms</li> <li>4.13 Scenario 3 - Fault location F1: CCT = 4200 ms</li> <li>4.14 Scenario 3 - Fault location F1: CCT = 1400 ms</li> <li>4.15 Scenario 1-3 - Fault location F1: CCT &gt; 10 s</li> <li>4.16 Scenario 1-3 - Fault location F1-4: CCT &gt; 10 s</li> <li>4.17 Scenario 1-3 - Fault location F1-4: CCT &gt; 10 s</li> <li>4.18 Power-Angle Relationship</li> <li>4.19 Governor System Response</li> <li>4.20 Excitation System Response</li> <li>4.21 Frequency Stability</li> <li>4.22 Voltage measured at the MV busbar during a 3LG fault</li> <li>4.23 Currents measured at the outgoing feeders during a 3LG fault</li> <li>4.24 Currents measured at non-faulted feeders for an internal fault</li> <li>5.1 Basic Principle of Vector Jump protection [1]</li> <li>5.2 Logic Diagram for Loas Shedding Protection Trip</li> <li>5.3 Logic Diagram for Load Shedding Protection Trip</li> </ul>                                                                                                                                                                                                                                                                                                                                                                             | 3.17 | Utility Grid                                                              | 20 |

| <ul> <li>4.2 Fault location F1: CCT-S1=340ms, CCT-S2=440ms, CCT-S3=660ms</li> <li>4.3 Fault locations F2-F4: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=580</li> <li>4.4 Scenario 1 - Fault location F1: CCT = 320 ms</li> <li>4.5 Scenario 1 - Fault location F2-F4: CCT = 300 ms</li> <li>4.6 Scenario 2 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 400 ms</li> <li>4.7 Scenario 3 - Fault location F1: CCT = 600 ms</li> <li>4.8 Scenario 3 - Fault location F2-F4: CCT = 580 ms</li> <li>4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 4200 ms</li> <li>4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms</li> <li>4.11 Scenario 1 - Fault location F1: CCT = 880 ms, F2-4: CCT = 520 ms</li> <li>4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms</li> <li>4.13 Scenario 3 - Fault location F1: CCT = 4200 ms</li> <li>4.14 Scenario 3 - Fault location F1: CCT = 1400 ms</li> <li>4.15 Scenario 1-3 - Fault location F1: CCT &gt; 10 s</li> <li>4.16 Scenario 1-3 - Fault location F1-4: CCT &gt; 10 s</li> <li>4.17 Scenario 1-3 - Fault location F1-4: CCT &gt; 10 s</li> <li>4.18 Power-Angle Relationship</li> <li>4.19 Governor System Response</li> <li>4.20 Excitation System Response</li> <li>4.21 Frequency Stability</li> <li>4.22 Voltage measured at the MV busbar during a 3LG fault</li> <li>4.23 Currents measured at the outgoing feeders during a 3LG fault</li> <li>4.24 Currents measured at non-faulted feeders for an internal fault</li> <li>5.1 Basic Principle of Vector Jump protection [1]</li> <li>5.2 Logic Diagram for Loas Shedding Protection Trip</li> <li>5.3 Logic Diagram for Load Shedding Protection Trip</li> </ul>                                                                                                                                                                                                                                                                                                                                                                             |      | E III II ATD ENTROLD (DOWN I I'I I I                                      | 00 |

| <ul> <li>4.3 Fault locations F2-F4: CCT-S1=300ms, CCT-S2=400ms, CCT-S3=580</li> <li>4.4 Scenario 1 - Fault location F1: CCT = 320 ms</li> <li>4.5 Scenario 1 - Fault location F2-F4: CCT = 300 ms</li> <li>4.6 Scenario 2 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 400 ms</li> <li>4.7 Scenario 3 - Fault location F1: CCT = 600 ms</li> <li>4.8 Scenario 3 - Fault location F2-F4: CCT = 580 ms</li> <li>4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 4200 ms</li> <li>4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms</li> <li>4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms</li> <li>4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms</li> <li>4.13 Scenario 3 - Fault location F1: CCT = 4200 ms</li> <li>4.14 Scenario 3 - Fault location F1: CCT = 1400 ms</li> <li>4.15 Scenario 1-3 - Fault location F1: CCT &gt; 10 s</li> <li>4.16 Scenario 1-3 - Fault location F1-4: CCT &gt; 10 s</li> <li>4.17 Scenario 1-3 - Fault location F1-4: CCT &gt; 10 s</li> <li>4.18 Power-Angle Relationship</li> <li>4.19 Governor System Response</li> <li>4.20 Excitation System Response</li> <li>4.21 Frequency Stability</li> <li>4.22 Voltage measured at the MV busbar during a 3LG fault</li> <li>4.23 Currents measured at the outgoing feeders during a 3LG fault</li> <li>4.24 Currents measured at non-faulted feeders for an internal fault</li> <li>5.1 Basic Principle of Vector Jump protection [1]</li> <li>5.2 Logic Diagram for Loss-of-Mains Protection Trip</li> <li>5.3 Logic Diagram for Load Shedding Protection Trip</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |                                                                           |    |

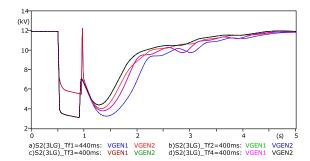

| <ul> <li>4.4 Scenario 1 - Fault location F1: CCT = 320 ms</li> <li>4.5 Scenario 1 - Fault location F2-F4: CCT = 300 ms</li> <li>4.6 Scenario 2 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 400 ms</li> <li>4.7 Scenario 3 - Fault location F1: CCT = 600 ms</li> <li>4.8 Scenario 3 - Fault location F2-F4: CCT = 580 ms</li> <li>4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 4200 ms</li> <li>4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms</li> <li>4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms</li> <li>4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms</li> <li>4.13 Scenario 3 - Fault location F1: CCT = 4200 ms</li> <li>4.14 Scenario 3 - Fault location F2-4: CCT = 1400 ms</li> <li>4.15 Scenario 1-3 - Fault location F2-4: CCT &gt; 10 s</li> <li>4.16 Scenario 1-3 - Fault location F2-4: CCT &gt; 10 s</li> <li>4.17 Scenario 1-3 - Fault location F1-4: CCT &gt; 10 s</li> <li>4.18 Power-Angle Relationship</li> <li>4.19 Governor System Response</li> <li>4.20 Excitation System Response</li> <li>4.21 Frequency Stability</li> <li>4.22 Voltage measured at the MV busbar during a 3LG fault</li> <li>4.23 Currents measured at the outgoing feeders during a 3LG fault</li> <li>4.24 Currents measured at non-faulted feeders for an internal fault</li> <li>5.1 Basic Principle of Vector Jump protection [1]</li> <li>5.2 Logic Diagram for Load Shedding Protection Trip</li> <li>5.3 Logic Diagram for Load Shedding Protection Trip</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                                                                           |    |

| <ul> <li>4.5 Scenario 1 - Fault location F2-F4: CCT = 300 ms</li> <li>4.6 Scenario 2 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 400 ms</li> <li>4.7 Scenario 3 - Fault location F1: CCT = 600 ms</li> <li>4.8 Scenario 3 - Fault location F2-F4: CCT = 580 ms</li> <li>4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 4200 ms</li> <li>4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms</li> <li>4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms</li> <li>4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms</li> <li>4.13 Scenario 3 - Fault location F1: CCT = 4200 ms</li> <li>4.14 Scenario 3 - Fault location F2-4: CCT = 1400 ms</li> <li>4.15 Scenario 1-3 - Fault location F1: CCT &gt; 10 s</li> <li>4.16 Scenario 1-3 - Fault location F1-4: CCT &gt; 10 s</li> <li>4.17 Scenario 1-3 - Fault location F1-4: CCT &gt; 10 s</li> <li>4.18 Power-Angle Relationship</li> <li>4.19 Governor System Response</li> <li>4.20 Excitation System Response</li> <li>4.21 Frequency Stability</li> <li>4.22 Voltage measured at the MV busbar during a 3LG fault</li> <li>4.23 Currents measured at the outgoing feeders during a 3LG fault</li> <li>4.24 Currents measured at non-faulted feeders for an internal fault</li> <li>5.1 Basic Principle of Vector Jump protection [1]</li> <li>5.2 Logic Diagram for Loss-of-Mains Protection Trip</li> <li>5.3 Logic Diagram for Load Shedding Protection Trip</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | , , , , , , , , , , , , , , , , , , ,                                     |    |

| <ul> <li>4.6 Scenario 2 - Fault location F1: CCT = 440 ms, Fault location F2-F4: CCT = 400 ms</li> <li>4.7 Scenario 3 - Fault location F1: CCT = 600 ms</li> <li>4.8 Scenario 3 - Fault location F2-F4: CCT = 580 ms</li> <li>4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 4200 ms</li> <li>4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms</li> <li>4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms</li> <li>4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms</li> <li>4.13 Scenario 3 - Fault location F1: CCT = 4200 ms</li> <li>4.14 Scenario 3 - Fault location F2-4: CCT = 1400 ms</li> <li>4.15 Scenario 1-3 - Fault location F1: CCT &gt; 10 s</li> <li>4.16 Scenario 1-3 - Fault location F1-4: CCT &gt; 10 s</li> <li>4.17 Scenario 1-3 - Fault location F1-4: CCT &gt; 10 s</li> <li>4.18 Power-Angle Relationship</li> <li>4.19 Governor System Response</li> <li>4.20 Excitation System Response</li> <li>4.21 Frequency Stability</li> <li>4.22 Voltage measured at the MV busbar during a 3LG fault</li> <li>4.23 Currents measured at the outgoing feeders during a 3LG fault</li> <li>4.24 Currents measured at non-faulted feeders for an internal fault</li> <li>5.1 Basic Principle of Vector Jump protection [1]</li> <li>5.2 Logic Diagram for Loss-of-Mains Protection Trip</li> <li>5.3 Logic Diagram for Load Shedding Protection Trip</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |                                                                           |    |

| 4.7 Scenario 3 - Fault location F1: CCT = 600 ms 4.8 Scenario 3 - Fault location F2-F4: CCT = 580 ms 4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 4200 ms 4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F2-4: CCT = 1400 ms 4.15 Scenario 1-3 - Fault location F1: CCT > 10 s 4.16 Scenario 1-3 - Fault location F2-4: CCT > 10 s 4.17 Scenario 1-3 - Fault location F1-4: CCT > 10 s 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the outgoing feeders during a 3LG fault 4.24 Currents measured at non-faulted feeders for an internal fault 5.1 Basic Principle of Vector Jump protection [1] 5.2 Logic Diagram for Loas Shedding Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.5  |                                                                           |    |

| 4.8 Scenario 3 - Fault location F2-F4: CCT = 580 ms 4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 4200 ms 4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F2-4: CCT = 1400 ms 4.15 Scenario 1-3 - Fault location F2-4: CCT > 10 s 4.16 Scenario 1-3 - Fault location F2-4: CCT > 10 s 4.17 Scenario 1-3 - Fault location F1-4: CCT > 10 s 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the outgoing feeders during a 3LG fault 4.24 Currents measured at non-faulted feeders for an internal fault 5.1 Basic Principle of Vector Jump protection [1] 5.2 Logic Diagram for Loss-of-Mains Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.6  |                                                                           |    |

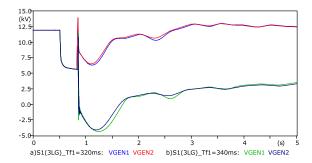

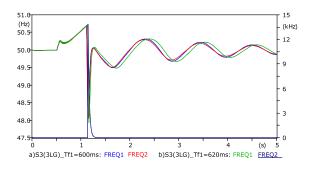

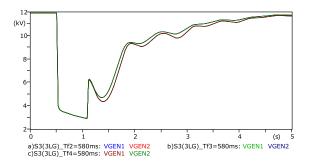

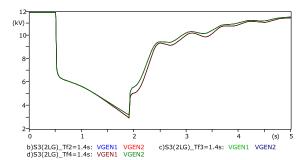

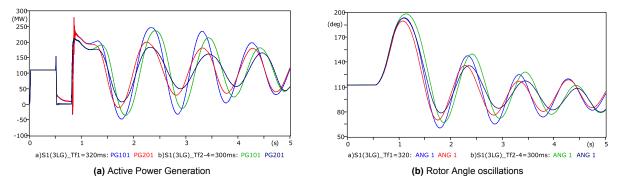

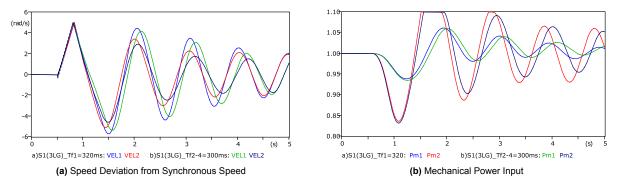

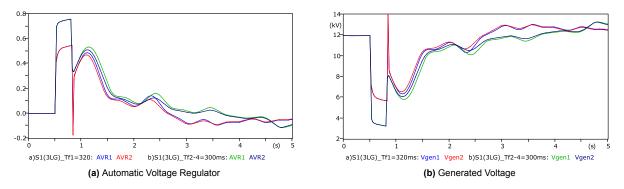

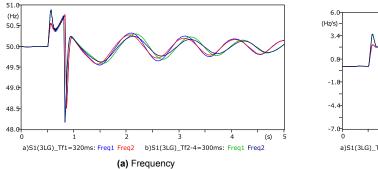

| 4.9 Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 4200 ms 4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F2-4: CCT = 1400 ms 4.15 Scenario 1-3 - Fault location F1: CCT > 10 s 4.16 Scenario 1-3 - Fault location F2-4: CCT > 10 s 4.17 Scenario 1-3 - Fault location F1-4: CCT > 10 s 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the outgoing feeders during a 3LG fault 4.24 Currents measured at non-faulted feeders for an internal fault 5.1 Basic Principle of Vector Jump protection [1] 5.2 Logic Diagram for Loss-of-Mains Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.7  | Scenario 3 - Fault location F1: CCT = 600 ms                              | 25 |

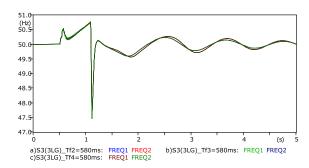

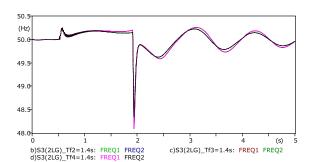

| 4.10 Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms 4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F2-4: CCT = 1400 ms 4.15 Scenario 1-3 - Fault location F1: CCT > 10 s 4.16 Scenario 1-3 - Fault location F2-4: CCT > 10 s 4.17 Scenario 1-3 - Fault location F1-4: CCT > 10 s 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the outgoing feeders during a 3LG fault 4.24 Currents measured at non-faulted feeders for an internal fault 5.1 Basic Principle of Vector Jump protection [1] 5.2 Logic Diagram for Load Shedding Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.8  | Scenario 3 - Fault location F2-F4: CCT = 580 ms                           | 26 |

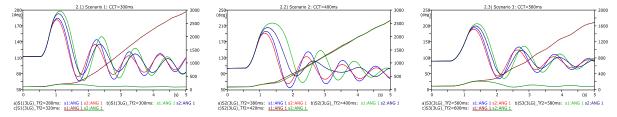

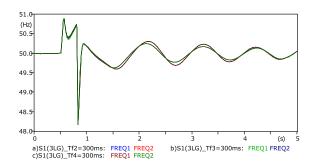

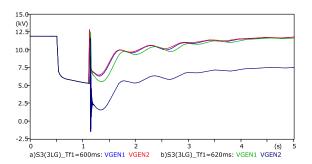

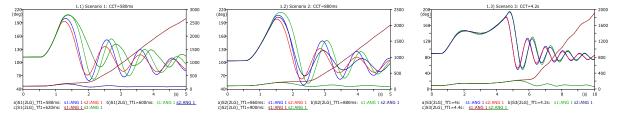

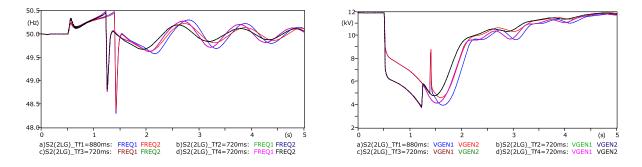

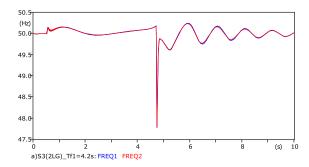

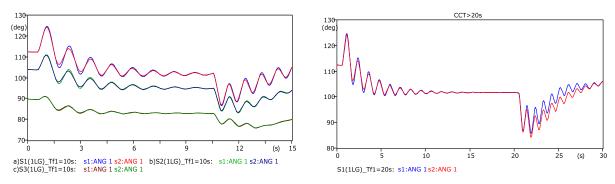

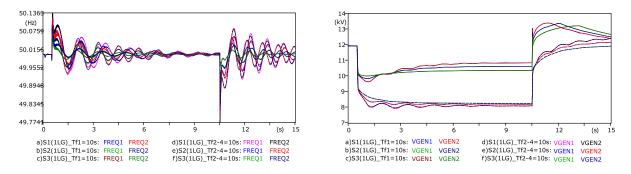

| 4.11 Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms 4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F2-4: CCT = 1400 ms 4.15 Scenario 1-3 - Fault location F1: CCT > 10 s 4.16 Scenario 1-3 - Fault location F2-4: CCT > 10 s 4.17 Scenario 1-3 - Fault location F1-4: CCT > 10 s 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the outgoing feeders during a 3LG fault 4.24 Currents measured at non-faulted feeders for an internal fault 5.1 Basic Principle of Vector Jump protection [1] 5.2 Logic Diagram for Loss-of-Mains Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4.9  | Fault location F1: CCT-S1 = 580 ms, CCT-S2 = 880 ms, CCT-S3 = 4200 ms     | 27 |

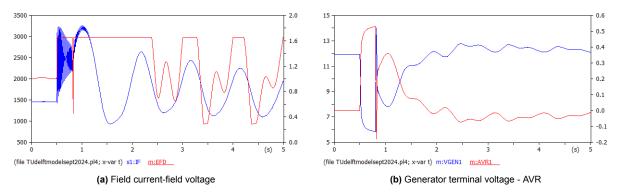

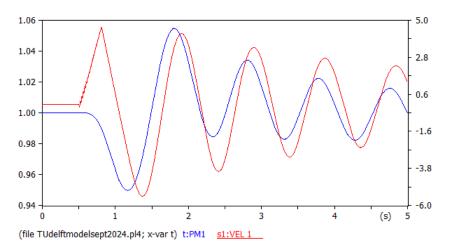

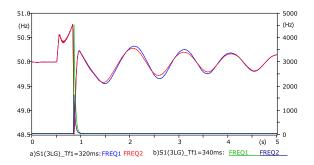

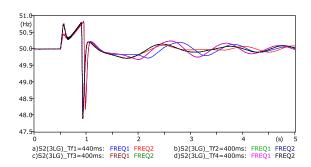

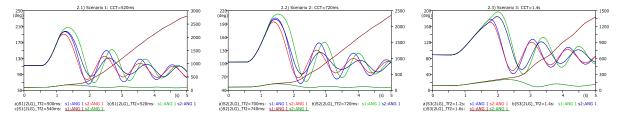

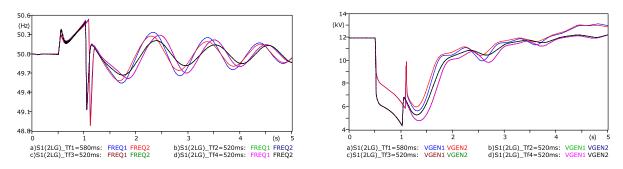

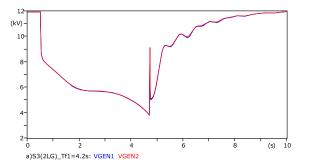

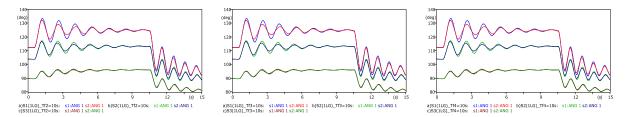

| 4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F2-4: CCT = 1400 ms 4.15 Scenario 1-3 - Fault location F1: CCT > 10 s 4.16 Scenario 1-3 - Fault location F2-4: CCT > 10 s 4.17 Scenario 1-3 - Fault location F1-4: CCT > 10 s 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the outgoing feeders during a 3LG fault 4.24 Currents measured at non-faulted feeders for an internal fault 5.1 Basic Principle of Vector Jump protection [1] 5.2 Logic Diagram for Loss-of-Mains Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.10 | Fault locations F2-F4: CCT-S1 = 520 ms, CCT-S2 = 720 ms, CCT-S3 = 1400 ms | 27 |

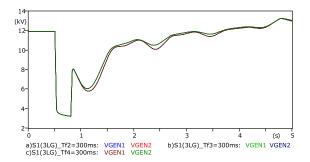

| 4.12 Scenario 2 - Fault location F1: CCT = 880 ms, F2-4: CCT = 720 ms 4.13 Scenario 3 - Fault location F1: CCT = 4200 ms 4.14 Scenario 3 - Fault location F2-4: CCT = 1400 ms 4.15 Scenario 1-3 - Fault location F1: CCT > 10 s 4.16 Scenario 1-3 - Fault location F2-4: CCT > 10 s 4.17 Scenario 1-3 - Fault location F1-4: CCT > 10 s 4.18 Power-Angle Relationship 4.19 Governor System Response 4.20 Excitation System Response 4.21 Frequency Stability 4.22 Voltage measured at the MV busbar during a 3LG fault 4.23 Currents measured at the outgoing feeders during a 3LG fault 4.24 Currents measured at non-faulted feeders for an internal fault 5.1 Basic Principle of Vector Jump protection [1] 5.2 Logic Diagram for Loss-of-Mains Protection Trip 5.3 Logic Diagram for Load Shedding Protection Trip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.11 | Scenario 1 - Fault location F1: CCT = 580 ms, F2-4: CCT = 520 ms          | 27 |