# **Electrothermal Filters for No-Trim Temperature Sensors**

### [Daguang Liu]

Thesis submitted in partial fulfillment of

the requirements for the requirements for the degree of

MASTER OF SCIENCE

IN

**ELECTRICAL ENGINEERING**

Author: BSc.D.Liu

Student ID: 4739760

Supervisor: Prof. Kofi A.A. Makinwa

Ir. Sining Pan

[2019 Oct 12th]

# **Abstract**

This thesis describes the design and characterization of thermistor-based electrothermal filters (ETFs) intended for use in high-accuracy CMOS temperature sensors. ETFs have been previously realized by placing an onchip heater in close proximity to an on-chip thermopile, which then picks up the thermally-delayed signals generated by the heater. This delay is a well-defined function of absolute temperature and can be used as the basis for highly accurate temperature sensors. In this work, the thermopiles are replaced by a thermistor, resulting in greater sensitivity and higher resolution. Measurements show that the new ETFs can achieve  $3.6 \text{m}^{\circ}\text{C}$  resolution in a conversion time of 1s and  $0.2^{\circ}\text{C}(3\sigma)$  untrimmed inaccuracy from  $30^{\circ}\text{C}$  to  $60^{\circ}\text{C}$ .

### **Contents**

| Abstract                                             | iii |

|------------------------------------------------------|-----|

| 1 – Introduction                                     | 1   |

| 1 1 – Motivation and objective                       | 1   |

| 1 2 – Literature review                              | 2   |

| 1.2.1 – BJT based temperature sensor                 | 2   |

| 1.2.2 – MOSFET based temperature sensor              | 4   |

| 1.2.3 – Resistor based temperature sensor            | 5   |

| 1.2.4 – Thermal diffusivity based temperature sensor | 6   |

| 1 3 – Organization of the thesis                     | 7   |

| 2 – TD Temperature Sensor                            | 8   |

| 2.1 – Principles of TD sensor                        | 8   |

| 2.2 – ETF Design in CMOS                             | 11  |

| 2.2.1 – Bar ETF                                      | 13  |

| 2.2.2 – Phase contour ETF                            | 13  |

| 2.2.3 – Polygon ETF                                  | 14  |

| 2.3 – ETF Accuracy                                   | 15  |

| 2.3.1 – Lithography                                  | 15  |

| 2.3.2 – Self-heating effect                          | 16  |

| 2.4 – ETF resolution                                 | 16  |

| 2.5 – Summary                                        | 18  |

| 3 – Ring ETF                                         | 19  |

| 3.1 – Principles                                     | 19  |

| 3.2 – Different structures                           | 20  |

| 3.3 – Choice of thermistor                           | 21  |

| 3.4 – Resolution analysis                            | 21  |

| 3.5 – Ring ETF design in CMOS                        | 23  |

| 3.5.1 – Layout                                       | 23  |

| 3.5.2 – Pros and Cons                                | 24  |

| 3 6 – Readout System                                 | 24  |

|   | 3.7 – Error source analysis                  | .25  |

|---|----------------------------------------------|------|

|   | 3.7.1 – Lithography                          | . 25 |

|   | 3.7.2 – Self-heating effect                  | . 25 |

|   | 3.7.3 – RC error                             | .26  |

|   | 3.7.4 – Delay of on-chip logic               | .26  |

|   | 3.7.5 – Frequency reference                  | .26  |

|   | 3.7 –Summary                                 | . 27 |

| 4 | - Test chip 1                                | .28  |

|   | 4.1 –Chip details                            | .28  |

|   | 4.1.1 – ETF details                          | .28  |

|   | 4.1.2 – Circuit diagrams                     | . 29 |

|   | 4.1.3 – Layout                               | .30  |

|   | 4.2 –Measurement set-up                      | .31  |

|   | 4.2.1 – System diagrams                      | .31  |

|   | 4.2.2 – PCB design                           | .31  |

|   | 4.2.3 – Temperature stability control        | .32  |

|   | 4.2.4 – Set-up evolvements                   | .33  |

|   | 4.3 –Measurement results                     | .33  |

|   | 4.3.1 – Phase characteristics                | .33  |

|   | 4.3.2 – Resolution optimization              | . 35 |

|   | 4.3.3 – Untrimmed accuracy                   | .37  |

|   | 4.3.3.1 – Power regulation and extrapolation | .37  |

|   | 4.3.3.2 – FIB circuit edit                   | .38  |

|   | 4.4 –Summary table                           | .38  |

|   | 4.5 –Summary                                 | . 39 |

| 5 | - Test chip 2                                | .40  |

|   | 5.1 –Chip details and improvements           | .40  |

|   | 5.1.1 – ETF details                          | .40  |

| 5   | .1.2 – Chip improvements             | 41 |

|-----|--------------------------------------|----|

| 5   | .1.3 – Circuit diagrams              | 42 |

|     | 5.1.3.1 – Phase autozeroing          | 42 |

|     | 5.1.3.2 – Circuit implementation     | 43 |

| 5   | .1.4 – Layout                        | 44 |

| 5.2 | –Measurement set-up                  | 44 |

| 5   | .2.1 – PCB design                    | 45 |

| 5   | .2.2 – Set-up evolvements            | 45 |

|     | 5.2.2.1 – New set-up                 | 45 |

|     | 5.2.2.2 – PCB modification           | 46 |

| 5.3 | –Measurement results                 | 46 |

| 5   | .3.1 – Phase characteristics         | 46 |

|     | 5.3.1.1 – Phase normalization        | 46 |

|     | 5.3.1.2 – Thermopile ETF model       | 47 |

| 5   | .3.2 – Resolution optimization       | 49 |

| 5   | .3.3 – Untrimmed Accuracy            | 49 |

|     | 5.3.3.1 – Polynomial fit experiments | 49 |

|     | 5.3.3.2 – ETFs accuracy              | 50 |

|     | 5.3.3.3 – Wafer-to-wafer spread      | 53 |

|     | 5.3.3.4 – Batch-to-batch spread      | 54 |

|     | 5.3.3.5 – Mechanical stress          | 55 |

| 5.4 | –Summary table and analysis          | 56 |

|     | 5.4.1 –Summary table                 | 56 |

|     | 5.4.2 –Other error sources analysis  | 57 |

|     | 5.4.2.1 – RC error                   | 57 |

|     | 5.4.2.2 – Self-heating effect        | 57 |

| 5 5 | Summary                              | 50 |

| 6 - Conclusion and Future work | 59 |

|--------------------------------|----|

| 6.1 –Conclusion                | 59 |

| 6.2 –Future work               | 59 |

| Acknowledgements               | 61 |

| Reference                      | 62 |

# 1 - Introduction

# 11 - Motivation and objective

Temperature is an important environmental quantity. It plays a significant role in most physical, chemical and biomedical processes [1]. This makes temperature measurement critical for the monitoring and control of such processes. Thanks to the development of integrated circuit technology, extremely small temperature sensors can be realized based on BJTs [2] [3], MOSFETs [4], resistors [5] [6] and electro-thermal filters [7] [8].

Accuracy is one of the most important specifications of a temperature sensor. Since the inherent accuracy of integrated temperature sensors is limited by process spread, their accuracy is typically improved by trimming on the basis of information acquired by calibration [9] [10]. Traditionally, this requires a temperature-controlled environment, an external reference sensor and a certain amount of time, during which the device-undertest (DUT) reaches thermal equilibrium with the reference sensor. However, this is time-consuming and thus costly. Recently, voltage-based calibration [12] and heater-assisted calibration [11] have been proposed to address this problem. However, these techniques have been developed specifically for BJT-based temperature sensors.

Temperature calibration could be improved if the reference sensor could be realized on the same piece of silicon. Since silicon is a good conductor, the thermal equilibrium between the DUT and the reference sensor can be reached in a very short time (<<1s), enabling a significant reduction in calibration speed and cost. The design of such a reference sensor is the goal of this thesis.

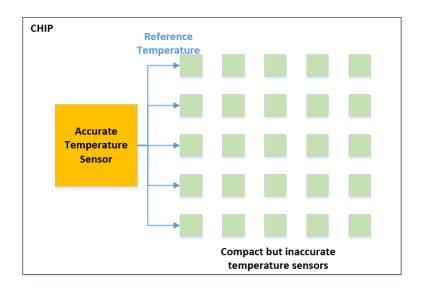

Fig.1.1 shows an application of this idea for the thermal monitoring of a large silicon chip. In modern system-on-chips (SoCs), a large number of small but fast temperature sensors are needed to monitor hot-spots whose intensity and location rapidly changes. Given a highly accurate reference sensor, all the other sensors can be rapidly trimmed without the need for a temperature-controlled environment.

Figure 1.1 Temperature sensor as an on-chip calibration reference

It should be noted that although the reference sensor should be more accurate than the DUT (error < 0.05°C), it does not need to cover a wide temperature range. This is because trimming is usually done in a fairly stable environment (less than 10°C variation) To leave some margin, a temperature range of 30°C is set as one of the targets. Also, the reference sensor's conversion time needs to be short (<1s) to avoid increasing the time-related cost.

The target specifications of a reference sensor are summarized in Table 1.1.

Specification Target

Temperature accuracy <0.05°C

Conversion time <1s

Temperature range 30°C to 60°C

Table 1 Specifications of a reference sensor

### 12 - Literature review

# 1.2.1 - BJT based temperature sensor

In CMOS technology, both PNPs and NPNs can be used to sense temperature. Vertical PNPs are usually preferred due to their lower sensitivity to packaging stress. NPNs typically have more current gain, but typically require extra process options (twin wells or deep n-wells). Regardless of what type of BJT is used, their use as temperature sensors relies on the temperature-dependency of a BJT's base-to-emitter voltage  $V_{BE}$ , which can be expressed as:

$$V_{BE} = \frac{kT}{q} \ln(\frac{I_C}{I_S}) \tag{1.1}$$

In this equation,  $I_C$  is the collector current,  $I_S$  is the saturation current, k is the Boltzmann constant, q is the electron charge, and T is the temperature. Because of the temperature dependence of  $I_S$ ,  $V_{BE}$  decreases over temperature with a 2 mV/K slope, which is complementary to absolute temperature (CTAT) [12].

For a pair of BJTs biased at different current densities, the difference of their base-emitter voltages exhibits another characteristic, which is given by:

$$\Delta V_{BE} = \frac{kT}{q} \ln(p) \tag{1.2}$$

where p is the ratio between their current densities This equation shows that  $\Delta V_{BE}$  is proportional to absolute temperature (PTAT), which is inherently independent of process and supply voltage.

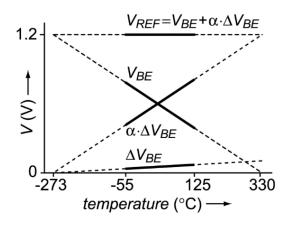

The CTAT  $V_{BE}$  and PTAT  $\Delta V_{BE}$  can be linearly combined to get the well-known temperature-independent band-gap voltage  $V_{REF}$ , given by[13]:

$$V_{REF} = \alpha \Delta V_{BE} + V_{BE} \tag{1.3}$$

Where  $\Delta V_{BE}$  is scaled by a factor of  $\alpha$ . This principle is shown in Figure 1.2.

Figure 1.2 Bandgap voltage of BJT based temperature sensor [10]

The reference voltage can then be used to digitize the PTAT  $\Delta V_{BE}$  and to sense temperature since the ratio of them is a function of absolute temperature:

$$\mu = \frac{V_{PTAT}}{V_{REF}} = \frac{\alpha \Delta V_{BE}}{\alpha \Delta V_{BE} + V_{BE}} \tag{1.4}$$

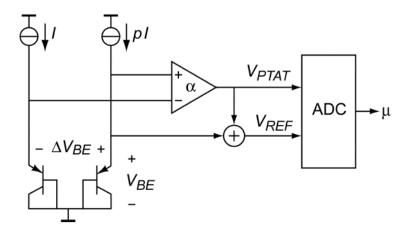

Figure 1.3 shows how the combination is realized in real circuits.

Figure 1.3 Block diagram of a BJT-based temperature sensor [10]

After a single-point trim, BJT-based sensors can achieve 0.1°C inaccuracy over the military temperature range (-55°C to 125°C) [3]. However, due to process spread, the saturation current changes from batch to batch, resulting in an untrimmed inaccuracy of a few °C [14]. Also, the fact that V<sub>BE</sub> is approximately 0.7V sets a lower limit on the supply voltage, restricting the use of such sensors in advanced technologies in which supply voltages are typically less than 1V.

### 1.2.2 – MOSFET based temperature sensor

There are also various types of MOSFET-based temperature sensors, since many MOS device parameters (Trans-conductance, threshold voltage, etc.) are heavily temperature-dependent.

For a MOSFET, there is an exponential relationship between the drain current  $I_{DS}$  in the weak inversion region and the overdrive voltage  $V_{GS}$  -  $V_{\rm TH}$  given by:

$$V_{GS} - V_{TH} = \left(\frac{\eta kT}{q}\right) \ln\left(\frac{I_{DS}}{I_0}\right)$$

(1.5)

where  $\eta$  is the sub-threshold slope factor and  $I_0$  is a process-dependent parameter. Dynamic-Threshold based temperature sensor, in which the BJTs in a bipolar core are replaced with DTMOST(Dynamic-Threshold MOSFET) [15]. Basically, it is a MOSFET

whose body, drain and gate terminals are tied together, a diode-connected DTMOST exhibits a near-ideal exponential replationship between  $I_D$  and  $V_{GS}$  [28]. As the  $V_{TH}$  of DTMOST sensors is well-defined, they can be used in the same way as BJTs to achieve decent accuracy.

Compared to BJT sensors, however, DTMOST sensors have one more variable that can spread over process: the sub-threshold slope factor  $\eta$ . With a single-point trim, the state-of-the-art accuracy is 0.4 °C(3 $\sigma$ ) over the military temperature range [4].

There are also other types of MOSFET-based temperature sensors. E.g., [3] is built by comparing the difference in the propagation delay of differently types of inverters. This type of sensor can be quite compact (< 0.01mm²) and is compatible with a sub-1V supply. However, since the delay is a complicated function of the transconductance and threshold voltage of many transistors, many error sources contribute to the final spread, making these kinds of sensors rather inaccurate, even after 2-point trimming.

### 1.2.3 – Resistor based temperature sensor

On-chip resistors can have stable temperature coefficients as large as 0.3%/°C, which provides another temperature sensing mechanism. The basic idea is to compare the resistance change of a temperature-dependent resistor with a fixed reference resistor that is temperature insensitive.

The front end of a resistor-based sensor could either be a Wheatstone bridge [6] or a Wien-bridge filter [16]. For a Wheatstone bridge, the reference is another on-chip resistor. For a Wien bridge, the resistors are combined with capacitors, to create a temperature-dependent time constant (phase shift). Temperature information can then be extracted by measuring the phase shift output of the Wien bridge.

The biggest advantage of these types of sensors is that they can be designed for low noise and extremely high resolution (sub-mK) [6]. In addition, resistor-based temperature sensors do not have a fundamental limit on voltage headroom.

Unfortunately, the untrimmed inaccuracy of resistor based sensors is quite poor, since variations in geometry and doping concentration cause large resistance spread. This spread can be ±20%, which corresponds to temperature errors of tens of °C.

### 1.2.4 – Thermal diffusivity based temperature sensor

In addition to the three aforementioned types of temperature sensors, thermal diffusivity based sensors are another option [7]. The thermal diffusivity of silicon,  $D_{si}$  describes the time it takes for heat signals to diffuse through a volume of silicon. Its temperature sensitivity comes from the temperature-dependent phonon scattering of crystalline semiconductors. Since silicon is a highly homogeneous and pure material, the temperature sensitivity of  $D_{si}$  is a well-defined function of absolute temperature, and can be approximated by [17]:

$$D_{si} \propto T^{-1.8} \tag{1.6}$$

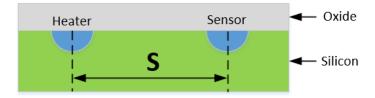

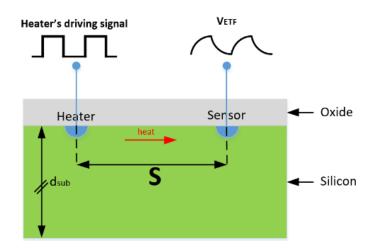

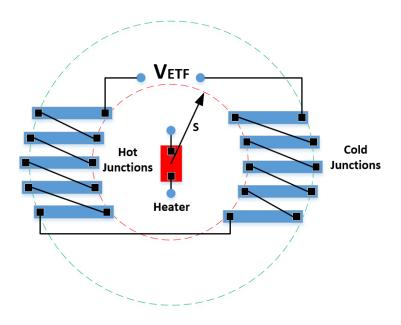

As shown in Fig.1.4, heat signals diffuse from a heater to the surrounding silicon substrate, and a sensor is placed at a distance 'S' to pick up the delayed heat signal. Since thermal diffusivity defines the speed of the diffusion process, the thermal delay between heater and sensor will also be temperature-dependent. Such a structure is known as an Electrothermal Filter, or ETF [18].

Figure.1.4 A basic electro-thermal filter (ETF)

As the distance 'S' is defined by lithography, it is also a well-defined variable: so in principle, the sensor can be quite accurate even without trimming.

Table 1.2 provides an overview of the best accuracy (untrimmed or 1 point trimmed) achieved by different types of temperature sensors so far. Compared to the other types, thermal diffusivity based temperature sensors achieve the best untrimmed inaccuracy of  $0.2 \, ^{\circ}\text{C}(3\sigma)$  [8], making them the most promising candidate for the targeted application.

Table 1.2-Overview of the most accurate temperature sensors

| State of the art       | Accuracy °C(3σ)    | Temperature Range | Reference |

|------------------------|--------------------|-------------------|-----------|

| BJT-based              | 0.3 (untrimmed)    | -55°C to 125°C    | [3]       |

| MOSFET-based           | 0.4 (1 point trim) | -55°Cto 125°C     | [19]      |

| Resistor-based         | 0.3 (1 point trim) | -40°C to 85°C     | [20]      |

| Thermal diffusivity-   | 0.2 (untrimmed)    | -55°C to 125°C    | [8]       |

| Targeted specification | 0.05 (untrimmed)   | 30°C to 60°C      |           |

# 13 - Organization of the thesis

The rest of this thesis is organized as follows. First, the principles, prior art and major accuracy limitations of TD sensors are analyzed in Chapter 2. In Chapter 3, a new type of ETF is proposed, and its advantages and disadvantages compared with traditional ETFs is discussed. In order to characterize the performance of this new type of ETF, two batches of test chips have been taped out. They are presented in Chapter 4 and Chapter 5, including the chip details, measurement setups and characterization results. The thesis concludes in Chapter 6. Possible future work is presented in the same chapter.

# 2 - TD Temperature Sensor

This chapter discusses how the thermal diffusivity of silicon  $D_{si}$  can be measured by using an electro-thermal filter (ETF). First, the thermal properties of Si and SiO<sub>2</sub> are discussed. Second, an electro-thermal model is developed and used to estimate ETF performance. Then the performance of previous TD sensors based on ETFs realized in CMOS technology is presented. Last but not least, the accuracy and resolution of traditional ETFs are discussed and compared to the targeted specification, which suggests the need for a new type of ETF.

# 2.1 - Principles of TD sensor

Thermal diffusivity D defines the speed at which heat diffuses through a material. It is the ratio of k and  $C_{\nu}$ , given by [21]:

$$D = \frac{k}{C_{v}} = \frac{1}{3} v_{s} \lambda_{ph} \tag{2.1}$$

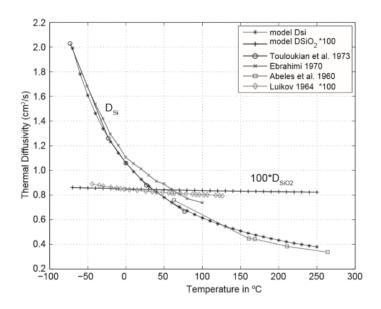

in which k is the thermal conductivity in W/m/K,  $C_v$  is the volumetric heat capacity in J/cm³/K,  $v_s$  is the mean photon velocity and  $\lambda_{ph}$  is the mean free path. As shown in Fig. 2.1,  $D_{si}$  and  $D_{sio_2}$  can be obtained from the previous equation and from literature [17]. Note that  $D_{sio_2}$  is multiplied by a factor of 100 to fit on the same scale as  $D_{si}$ .

Figure.2.1 Historical data and simulated values of  $D_{si}$  and  $D_{so}$  [21]

Two observations can be made from the equation and plot above:

- 1.  $D_{si}$  is strongly temperature-dependent, while  $D_{siO_2}$  is much less sensitive to temperature variations. For  $D_{si}$ , a  $1/T^{1.8}$  power-law proportionality holds well over a wide temperature range (-55°C to 125°C) [14].

- 2. As  $v_s$  is fairly constant and  $\lambda_{ph}$  is only weakly sensitive to doping variations,  $D_{si}$  is only technology-dependent and the thermal constants are very well-defined.

Since  $D_{si}$  is a thermal characteristic rather than an electrical one, a thermal detection system, in this case, an Electro-thermal filter (ETF) [14] is needed to sense it. An ETF consists of a heater, a thermal medium (silicon in this case) and a relative temperature sensor.

Fig 2.2 shows the cross-section of a conceptual ETF which consists of a point heater and a point temperature sensor on the surface of silicon bulk. In general, the value of their spacing 'S' is much smaller than the thickness of the silicon substrate (~300μm). Furthermore, the SiO<sub>2</sub> layer can be considered to be a thermal insulator due to its much lower thermal diffusivity.

Figure 2.2 The cross-section of a basic ETF that measures  $D_{si}$

When the heater is driven by a harmonic signal at a fixed frequency, heat diffuses into silicon in a semi-spherical manner. The associated temperature profile is given by solving [22]:

$$\frac{d^2(rT(r))}{dr^2} - q^2rT(r) = 0 {(2.2)}$$

in which  ${\cal F}$  s the distance to the point heater, T(r) is the temperature profile along the diffusion path, and  $q^2=j\omega/D$ . The solution of Eq.(2.2) defines the thermal impedance[22], which is related to the temperature profile  $T(\omega,r)$  and heater's power  $P_{heater}(\omega)$ :

$$Z_{th}(\omega, r) = \frac{T(\omega, r)}{P_{heater}(\omega)} = \frac{1}{2\pi k_{si} r} \exp(-r\sqrt{\frac{\omega}{2D_{si}}}) \exp(-jr\sqrt{\frac{\omega}{2D_{si}}})$$

(2.3)

The magnitude and phase components can be computed as follows:

$$\left|Z_{th}(\omega,r)\right| = \frac{1}{2\pi k_{si}r} \exp\left(-r\sqrt{\frac{\omega}{2D_{si}}}\right) \tag{2.4}$$

$$\phi(\omega, r) = -r \sqrt{\frac{\omega}{2D_{si}}}$$

(2.5)

These equations indicate that the thermal impedance  $|Z_{th}(\omega,r)|$  is a function of  $k_{si}$  and  $D_{si}$ . As the drive frequency goes up, the magnitude of the phase shift will increase, just as in an electrical low-pass filter. Assuming this ETF has a sensitivity  $S_t$ , then the amplitude of ETF's output is given by:

$$V_{ETF}(\omega, r) = \frac{P_{heater} S_t}{2\pi k_{si} r} \exp(-r \sqrt{\frac{\omega}{2D_{si}}})$$

(2.6)

And the phase output can be rewritten as:

$$\phi_{ETF} = -s \sqrt{\pi f_{drive}} / D_{si} \propto -s \sqrt{\pi f_{drive}} T^{1.8}$$

(2.7)

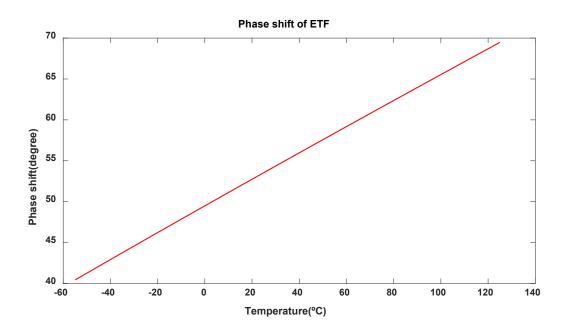

This shows that the ETF phase  $\phi_{ETF}$  has a near-linear  $T^{0.9}$  dependency, which is only dependent on heater distance 'S', driving frequency  $f_{drive}$  and  $D_{si}$ . Fig. 2.3 shows the simulated  $|\phi_{ETF}|$  for S=24µm and  $f_{drive}$ =42kHZ.

Figure.2.3 Simulated  $\phi_{ETF}$  as a function of temperature

Compared to the ETF phase  $\phi_{ETF}$ ,  $V_{ETF}$  has more degrees of freedom. For instance, the heater power  $P_{heater}$ , will depend both on its resistance and on the supply voltage, which can easily vary by over 10%. On the contrary,  $\phi_{ETF}$  is a well-defined function over temperature, and can serve as an accurate temperature reference.

# 2.2 - ETF Design in CMOS

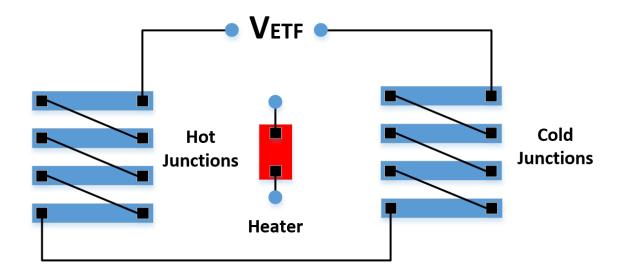

As shown in the Fig.2.2, there are 2 necessary elements for an ETF: a heater and a temperature sensor. In prior art, the heaters were simply realized as small on-chip resistors, while the temperature sensors were realized as thermopiles [23] [8].

A typical thermopile is shown in Fig.2.4; it consists of series-connected p+ diffusion resistors and aluminum strips. Due to the Seebeck effect, a voltage that is proportional to the temperature difference between the hot/cold junctions ( $\sim$ 0.5mV/K) is created. Being passive sensors, thermopiles are intrinsically offset-free. However, thermopile ETFs suffer from significant thermal noise, due to the finite resistance (140  $\Omega$ /square) of diffusion resistors.

Figure.2.4 A thermopile based ETF

As mentioned earlier, there are two metallurgical junctions in thermopile ETFs, called the hot junction and the cold junction, respectively. The hot junction is closest to the heater and can detect the phase information from the delayed heating signal, while the cold junction is placed far away from the heater so that it is ideally at ambient temperature. In reality, however, it will still pick up a weak signal and reduce the voltage output of the ETF. For this reason, the cold junction should be placed as far away as possible in order to get a strong ETF signal. However, long thermopiles will exhibit significant thermal noise. From [14], the optimum SNR is achieved when the length of the thermopile is roughly equal to 'S'.

The distance between the heater and hot junctions is critical for accuracy. In a CMOS process, the distance 'S' is defined by the mask dimensions and lithography. Lithography misalignment will result in a variation in the effective 'S', and this variation will lead to a temperature (phase) error, which is given by [14]:

$$\frac{\partial s}{s} = \frac{\partial \phi_{ETF}}{\phi_{ETF}} = 0.9 \frac{\partial T}{T}$$

(2.8)

Therefore, an ETF's accuracy can be improved by increasing 'S'. But this will be at the expense of resolution, since the signal amplitude drops as 'S' increases (Eq. 2.6).

The parasitic junction capacitance of thermocouples is another source of error, since this will add extra phase-shift to the ETF signal and degrade phase accuracy. The junction

capacitance is caused by the P+ diffusion resistors and the substrate and is proportional to the thermocouple area.

Various ETF geometries have been proposed and implemented in the literature in order to achieve optimal performance.

#### 2.2.1 - Bar ETF

The simplest ETF geometry is the bar ETF, whose layout is shown in Figure 2.4. In this type of ETF, a bar-shaped heater is surrounded by a number of thin, long thermocouples that are perpendicular to the heater. The bar ETF is simple, but is not optimal for SNR [24], since the phase of the heatwave is not the same for each hot junction and the temperature information picked up by each thermocouple does not sum up coherently. Therefore, heat generated at the edges of the heater is wasted.

#### 2.2.2 - Phase contour ETF

X. Sha et al. proposed a new type of ETF [24], in which the hot junctions are placed on a constant phase shift contour around the heater, shown in Fig. 2.5. The resulting SNR was 50% better than a Bar ETF with approximately the same delay. In this ETF, the heater was miniaturized, so that it approximates a point-source. All of the heat generated by the heater can then be detected by the hot junctions in a coherent fashion. Both hot and cold junctions are placed on a circular pattern around the heater and the radial distance 'S' defines a specific phase shift.

Phase contour ETFs have been used in integrated temperature sensors, which have achieved excellent accuracy  $(0.2^{\circ}C(3\sigma))$  [8]. However, since the hot junctions did not completely surround the heater, some of its thermal output is lost, resulting in a suboptimal SNR.

Figure.2.5 A phase contour ETF

### 2.2.3 - Polygon ETF

In order to improve the SNR of phase contour ETF, U. Sönmez et al. proposed a polygon ETF [15], as shown in Figure 2.6, in which the thermocouples have been expanded to fully cover the area between hot and cold phase contours. In this way, the resistance (or thermal noise) of thermocouples is reduced, which boosts the ETF's SNR. One drawback of this ETF is a somewhat larger parasitic junction capacitance since it covers a much larger silicon area. This, in turn, means that (the spread) in its RC phase shift will contribute more error.

Figure.2.6 A polygon ETF

# 2.3 - ETF Accuracy

As mentioned earlier, accuracy is one of the most important specifications of a temperature sensor. Two dominant limitations on the accuracy of ETFs will be discussed in this section.

### 2.3.1 - Lithography

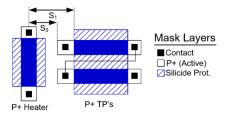

From equation 2.8, lithographic misalignment will cause 'S' of ETF to spread, which will result in a phase shift spread and temperature error. The spread of 'S' can be estimated from the accuracy of the process masks used to build the ETF.

As shown in Fig.2.7, in the case of a thermopile ETF implemented in a modern CMOS process, two masks define 'S': the active (p+) and the silicide protection masks. The distance S0 and S1 in the figure indicate the closest and farthest end of the hot junction from the mid-point of the heater. Then the effective 'S' can be approximated as (S0+S1)/2. The distance S0 is determined only by the p+ active mask, while S1 is defined by both P+ active and silicide protection masks. Therefore, the misalignment of these masks defines the spread in 'S' [23].

Figure.2.7 The layout of a simple bar ETF, showing the three masks involved [23]

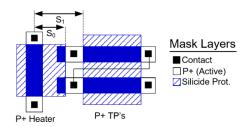

As shown in Fig. 2.8, the accuracy can be improved by extending the silicide protection mask of the heater resistor so that S0 and S1 are only determined by the silicide protection mask [23].

Figure.2.8 The improved layout of a BAR ETF, in which only the silicide protection mask defines the critical distance 'S' [23]

## 2.3.2 - Self-heating effect

Apart from a dynamic heat signal, the DC component of  $P_{\textit{heater}}$  will result in a static temperature gradient across the thermopile [14]. For heat diffusing from a point heater to a point sensor in a semi-sphere of silicon, the static temperature increase at a radius 'S' is given by:

$$T_{DC}(s) = \frac{P_{heater}}{2\pi k_{si} s} \tag{2.9}$$

From Eq.2.2, variations of the heater resistance or the supply voltage will both result in temperature errors. Apart from this static temperature offset, the finite thermal impedance of the package also leads to temperature spread. For example, a typical ceramic package has a thermal impedance of 50°C/W [25], which will also spread depending on how the package is mounted on a PCB. Hence, the total error due to the self-heating effect can be approximated as:

$$T_{selfi-heating}(s) = \frac{P_{heater}}{2\pi k_{si}s} + P_{heater} \times Z_{package}$$

(2.10)

Assuming a thermopile with S =  $24\mu m$ ,  $Z_{package}$  =  $50^{\circ}$ C/W, and a 5% spread in  $P_{heater}$  = 10mW, the total error due to the self-heating effect would be  $0.05^{\circ}$ C. This error can be reduced by precisely controlling the ETF's heating power, at the cost of more complex readout circuits.

### 2.4 - ETF resolution

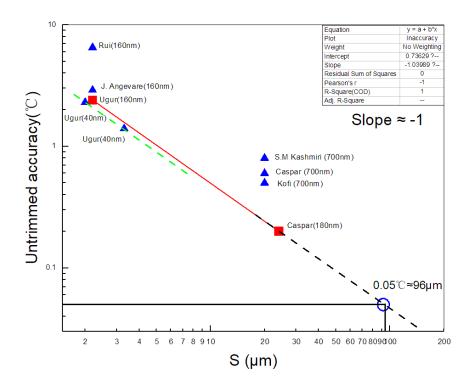

As shown in Figure 2.11, the performance of previous TD sensors shows that accuracy improves with a larger 'S' and with better process technology. In a 180nm process, 'S' should be increased to 96 $\mu$ m to achieve a 0.05°C (3 $\sigma$ ) accuracy. Then in order not to add significant error after a single measurement, the resolution of the ETF should be below 0.01°C(3 $\sigma$ ).

Self-heating effect is another limiting factor. As shown above, for an S24 thermopile ETF, the maximum allowed  $P_{heater}$  under the 0.05 °C accuracy constraint is 10mW.

Figure 2.11 ETF accuracy as a function of 'S'

Table 2.1 shows how the resolution is estimated for a phase contour ETF with S=96  $\mu$ m. Comparing to [8], 'S' is quadrupled, which means that the ETF's output signal becomes 4x weaker, while a thermopile with optimal length (96 $\mu$ m) would exhibit 4x more thermal noise power. The number of thermopiles can be enlarged to 96 to improve the signal amplitude by 2x. Taking these factors into account, the estimated resolution is 150m°Crms.

If a polygon ETF is used, the resistance of the ETF will drop by 2.9x so its resolution will be improved by 70% [23] compared to the optimized phase contour ETF. Thus the best resolution possible with an S96 thermopile based ETF is 30m°Crms, which is still 3x worse than the targeted value. Hence, a new type of ETF with much better resolution is required.

Figure 2 Resolution estimation of Phase contour ETF (\$96)

|                              | 'S'   | Pheater | Conversion | Number | Length | Resolution |

|------------------------------|-------|---------|------------|--------|--------|------------|

|                              |       |         | rate       | of TP  | of TP  |            |

|                              |       |         | (Sample/s) |        |        |            |

| Caspar's Work                | 24 µm | 2.5mW   | 0.16       | 24     | 24 µm  | 20m °Crms  |

| Phase contour<br>ETF(S96)    | 96 µm | 10mW    | 1          | 96     | 96 µm  | 50m °Crms  |

| Scaled factor for resolution | 4 x   | 0.25 x  | 2.5 x      | 0.5 x  | 2x     | 2.5 x      |

# **2.5 – Summary**

Design considerations and accuracy limitations of thermopile ETFs have been described in this chapter. Based on a point-heater point-sensor ETF, a thermal-electrical model has been built which offers useful insights into the thermal diffusivity based temperature sensors. Different limiting factors (lithography, self-heating and resolution) of the ETFs have been analyzed, which show that in a 180nm CMOS process, the traditional thermopile ETF cannot meet the targeted requirements. Hence, a new type of ETF with better accuracy/resolution needs to be designed.

# 3 - Ring ETF

In this chapter, a new type of resistor-based ETF, known as a ring ETF, is presented, which has a much higher resolution than previous thermopile-based ETFs. Its pros and cons, working principle, design considerations will be discussed in detail.

# 3.1 - Principles

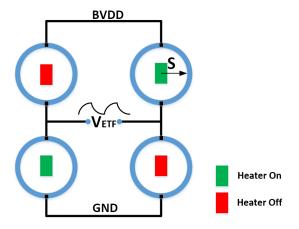

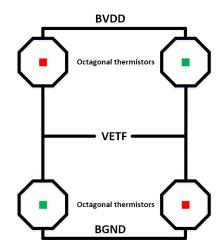

In a ring ETF, the signals generated by the heater are detected by a ring-shaped thermistor rather than by a thermopile. As shown in Fig. 3.1, four heaters are placed in the center of four ring-shaped thermistors, which are configured as a Wheatstone bridge. The heaters are driven in anti-phase so that two of them are heating up while the other two are cooling down. The distance 'S' can be defined as the average radius of the rings.

Figure.3.1 A basic Ring ETF in one phase

During operation, the heaters are switched on or off alternately at a fixed driving frequency. In one phase, the bottom left and top right heaters are turned on, while the other heaters are off. The resistance  $R_{\rm ring}$  of the corresponding thermistors will increase to  $R_{\rm ring} \times (1 + \Delta T * T_{\rm C})$ , where Tc is its temperature coefficient, and  $\Delta T$  is the raised temperature. In the meantime, the other two thermistors will be cooling down, and their resistance will be decreasing. In the next phase, their resistance will start increasing as the bottom right and top left heaters are turned on. Given a fixed supply voltage and driving frequency, the bridge will output an AC signal whose phase is proportional to the ETF's thermal delay.

Using Eq. 2.6, the amplitude of the output of a ring ETF is given by:

$$V_{Ring\_ETF}(\omega, r) = \frac{BVDD}{2} \times \frac{P_{heater}T_c}{2\pi k_{si}r} \exp(-r\sqrt{\frac{\omega}{2D_{si}}})$$

(3.1)

where BV<sub>DD</sub> is the Wheatstone bridge's supply voltage.

Using Eq. 2.7, the phase of the output of a Ring ETF is given by:

$$\phi_{Ring\_ETF} = -s \sqrt{\pi f_{drive} / D_{si}} \propto -s \sqrt{\pi f_{drive}} T^{1.8}$$

(3.2)

Like that of a thermopile ETF,  $\phi_{Ring-ETF}$  is a well-defined function of temperature.

### 3.2 - Different structures

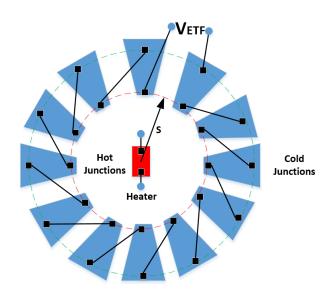

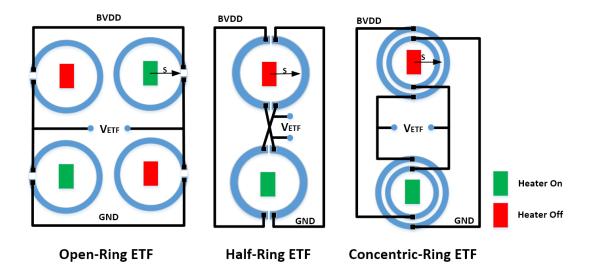

Apart from the basic Ring ETF shown in Fig 3.1, other Ring ETF configurations are possible, as shown in Fig. 3.2. The main differences are in the shape of the thermistors (full-ring, half-ring, concentric-ring or open-ring) and the number of heaters (two or four).

Figure.3.2 Other three types of Ring ETFs: Open-Ring ETF / Half-Ring ETF / Concentric-Ring ETF

The resistance of the thermistors of an open-ring ETF is 4x higher than the resistance of those in a basic ring ETF, which means that it dissipates less power, and can be interfaced more easily with current-based readout circuits. The half-ring and concentric ring ETFs only employ two heaters, so that their heater power is reduced by half. This improves their power-efficiency and reduces errors due to self-heating. To experimentally compare their resolution, accuracy and power efficiency, various ring ETFs with different values of "s" and different configurations have been implemented in two test chips.

### 3.3 - Choice of thermistor

In order to achieve a good resolution, the temperature coefficient (T<sub>C</sub>) of the Ring resistor should be high, while its resistance (R<sub>ring</sub>) should be low to minimize its thermal noise. Also, it should not be a poly resistor, since the oxide layer beneath such resistors is a good thermal insulator.

According to Cadence models of the chosen 180nm process, n-well resistors have the largest TC (0.356%/°C), but they also have a large sheet resistance (440  $\Omega$ /square). Compared to N+ diffusion resistors without silicide (0.1383%/°C, 61.6  $\Omega$ /square), the N+ diffusion resistor with silicide has ~2x larger TC (0.335%/°C), and ~10x smaller sheet resistance (6.82  $\Omega$ /square). Therefore, N+ diffusion resistors with silicide are preferred for us in ring ETFs.

Resistor width is another critical parameter because it affects the resistance and area. A wider resistor will lead to lower thermal noise and better SNR, but also to more parasitic capacitance, which can degrade accuracy. It also leads to more power dissipation, and thus self-heating.

# 3.4 – Resolution analysis

In the case of a Ring ETF, its phase-shifted output can be demodulated with the help of a fixed phase reference  $\phi_{d \in mod}$ . Assuming a square-wave reference signal as in [14], the DC component of the demodulator output  $V_{DC}$  can be expressed as:

$$V_{DC} = \frac{8}{\pi^2} \times V_{Ring\_ETF} \times \cos(\phi_{Ring\_ETF} - \phi_{de \, \text{mod}})$$

(3.3)

The sensitivity of  $V_{DC}$  to temperature is given by its derivative to T, which can be estimated by substituting the temperature dependencies of  $k_{si}$  ( $k_{si} \propto T^{-1.3}$ ) and  $D_{si}$  ( $D_{si} \propto T^{-1.8}$ ) in Eq. 3.3. To eliminate the supply sensitivity, V<sub>DC</sub> is usually not read out directly. Instead,  $\phi_{de\,\mathrm{mod}}$  is adjusted such that V<sub>DC</sub> can be made zero. Thus, the cosine term in Eq.3.3 becomes  $\cos(\pi/2)$  [14].

The sensitivity of  $V_{DC}$  to temperature variations can be investigated by taking the derivative of Eq.3.3, which can be simplified as:

$$\frac{\partial V_{DC}}{\partial T} \propto \frac{8}{\pi^2} \times \frac{BVDD}{2} \times \frac{P_{heater} T_c}{2\pi r} \exp(-r\sqrt{\pi f_{drive}} T^{1.8}) \times (1.3T^{0.3} - 0.9r\sqrt{\pi f_{drive}} \times T^{1.2})$$

(3.4)

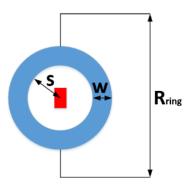

For Ring ETFs, the thermal noise from the bridge is the main noise source. Fig.3.3 illustrates a single ring-shaped thermistor whose resistance is given by:

$$R_{ring} = \frac{R_{sq}\pi}{2} (\frac{1}{2} + \frac{S}{W})$$

(3.5)

Figure 3.3 A single ring-shaped thermistor

Assuming that the input-referred noise of the phase detector is dominated by Johnson noise (white noise) with a PSD of 4KTR<sub>ring</sub> and the bandwidth is limited to B by the low-pass filter at the output, the ETF's temperature sensing resolution can be calculated as:

$$res \approx \frac{\sqrt{4kTR_{ring}B}}{\frac{8}{\pi^2} \times \frac{BVDD}{2} \times \frac{P_{heater}T_c}{2\pi r} \exp(-r\sqrt{\pi f_{drive}}T^{1.8}) \times (1.3T^{0.3} - 0.9r\sqrt{\pi f_{drive}} \times T^{1.2})}$$

(3.6)

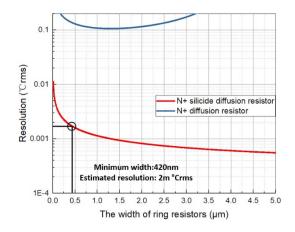

Assuming S=24 $\mu$ m,  $P_{heater}$  = 4mW, B=0.5Hz, T=27°C and Fdrive=42kHz, the resolution of a Ring ETF with a minimum width (0.42  $\mu$ m) resistor can be derived from Eq.3.6, which is commensurate with the target accuracy (0.05°C(3 $\sigma$ )), as shown in Fig.3.4. Hence, the minimum width was selected for constructing the Ring ETFs.

Figure 3.4 Resolution versus with thermistor width: N+ diffusion resistor with or without silicide

# 3.5 - Ring ETF design in CMOS

### 3.5.1 – Layout

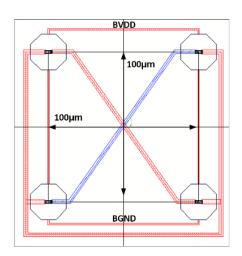

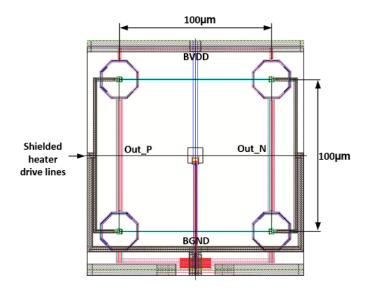

Due to the design rule constraints in Cadence, implementing ring-shaped thermistors is quite difficult. As shown in Fig.3.5, they have been replaced by octagonal thermistors, which are much easier to draw. The only consequence of this is that it will change the effective value of "S" to something between half the width of the octagon and half the width of its diagonal. Since they are driven in anti-phase, there will be no temperature variations at points equidistant to the two heaters. So to maximize their output signal, the octagons should not be too close together. In the test chips the distance between them is set to 100µm in the test chips, which is much larger than the largest implemented value of "S," which was 24µm.

Figure.3.5 Octagonal thermistors-based Ring ETF

#### 3.5.2 - Pros and Cons

Theoretically, Ring ETFs have several advantages compared to thermopile ETFs:

- 1. The structure of a Ring ETF is quite simple. Both layout and readout circuits can be implemented and scaled easily in the CMOS design.

- 2. The thermistors surround the heaters, which maximizes their output.

- 3. The effective 'S' is determined by a complete ring, rather than by a finite number of junction contacts as in a thermopile ETF. Thus, for the same 'S', the lithography-related error should be smaller.

- 4. For thermopile ETFs, the residual signal at cold junctions will result in a weaker output signal and a worse resolution [14]. Ring ETFs do not have cold junctions, so this issue does not arise.

However, the main drawback of Ring ETFs is larger power consumption. Apart from the heater, the bridge itself also dissipates power. The resulting self-heating may be a significant error source. Bridge offset is another disadvantage, since thermopile ETFs are intrinsically offset-free. However, this is not a major problem, since the signal of interest is an AC phase shift.

## 3.6 - Readout System

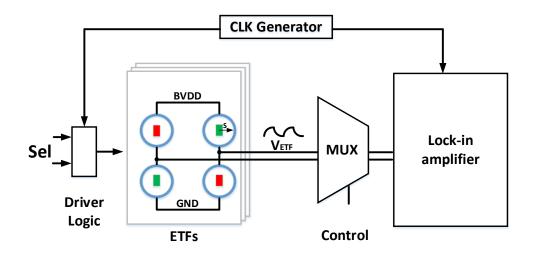

Since the ring ETF is a new type of ETF, it was decided to evaluate its performance by realizing a test chip with the bare minimum of readout circuitry.

The phase of an ETF can be read out by a standard lock-in amplifier (LIA). Fig.3.6 presents the corresponding block diagram. The LIA provides a reference signal that drives the on-chip heaters, and the output phase signal of one of the Ring ETF is selected by multiplexers and sent to the LIA. The phase difference between this signal and the LIA's reference signal is a representation of temperature.

Figure.3.6 Readout system for Ring ETFs

# 3.7 - Error source analysis

### 3.7.1 - Lithography

Similar to the thermopile ETF, lithography misalignment will cause 'S' of ring ETF to spread, resulting in a phase shift spread and then a temperature error. In previous work [8] [15] [26], lithography error is suspected to be the dominant error source. It is hard to estimate this with standard simulation tools. Thus, a practical way of investigating the lithography error is by building several Ring ETFs with different 'S' and then analyzing the correlation between 'S' and temperature error.

# 3.7.2 - Self-heating effect

As mentioned in section 2.3.2, the variations of heater resistance, supply voltage or thermal resistance of the package all result in different levels of self-heating and thus temperature errors. In order to achieve 0.05°C accuracy, the power consumption of a single chip should not exceed 10mW.

In addition, as temperature sensors, other heat sources on the die or PCB may potentially interfere with the temperature variations detected by ETF. When multiple ETFs are built in the same die, they should be placed far away (100µm) from each other to eliminate the interference. In addition, the heat generated by other components on the PCB (buffers and digital isolators) will affect the temperature distribution around the chips, thus resulting in significant errors as well, especially when many test chips are to be measured simultaneously on the same PCB.

#### 3.7.3 - RC error

Any extra phase-shift that occurs in the signal path between the ETFs and the LIA will be a source of error. For example, there will be an RC error associated with the finite delay between the Ring ETF and the LIA. At the chip's output, the bridge resistance and the parasitic capacitance (pad and PCB) forms an RC low-pass filter. This adds a nominal phase offset as well as potential phase spread to  $\phi_{Ring\_ETF}$ . Assuming the phase spread is 10% and the ETFs have a phase sensitivity of 5°C/°, the temperature error could be estimated as follows:

$$T_{error\_RC} = \arctan(\frac{f_{drive}}{f_{-3dB}}) \times 10\% \times 5^{\circ} C / ^{\circ}$$

(3.7)

To guarantee 0.05°C accuracy, this error should be at a 0.01°C level. Hence, the phase offset should be below 20m° at a typical F<sub>drive</sub>=42kHz (this choice will be discussed later), which corresponds to a -3dB-bandwidth of 120MHz.

### 3.7.4 - Delay of on-chip logic

Apart from the phase shift due to the thermal filtering of ETF, the delay (phase shift) of on-chip also will be measured by the LIA. Obviously, the spread of this delay will result in error as well. Assuming the delay spread is 10% and the ETFs have a phase sensitivity of 5°C/°, this temperature error is given by:

$$T_{error\ Delay} = Delay \times 10\% \times f_{drive} \times 360 \times 5^{\circ} C /^{\circ}$$

(3.8)

From Eq.3.8, the delay of on-chip logic should be below1.3ns to ensure this error lower than 0.01°C at F<sub>drive</sub>=42kHz.

# 3.7.5 - Frequency reference

Another error source would be the accuracy of the frequency reference. From Eq.3.2, the phase shift of ETF is a linear function of  $\sqrt{f_{drive}}$ , the spread of  $f_{drive}$  will result in phase and temperature as well. This temperature error can be estimated as follows:

$$T_{error\_fdrive} = 0.5 \times S \times \sqrt{\frac{1}{D_{si}}} \times f_{drive}^{-0.5} \times \frac{180}{\pi} \times \Delta f_{drive} \times 5^{\circ} C / ^{\circ}$$

(3.9)

Assuming S=24 $\mu$ m, F<sub>drive</sub>=42kHz, and the typical value of Dsi at room temperature is 0.7cm<sup>2</sup>/s, the frequency accuracy should better than 120 ppm to make this error lower than 0.01°C.

# 3.7 -Summary

In this chapter, the Ring ETF has been presented. Its principles, resolution, structures, design considerations, advantages or disadvantages and error sources have been discussed. To characterize this new type of ETFs quickly, a simple readout system based on a lock-in-amplifier has been proposed.

# 4 - Test chip 1

A first prototype with Ring ETFs was fabricated in a TSMC180nm CMOS process. In this chapter, design details, measurement set-up and characterization results of this test chip will be discussed.

# 4.1 -Chip details

#### 4.1.1 - ETF details

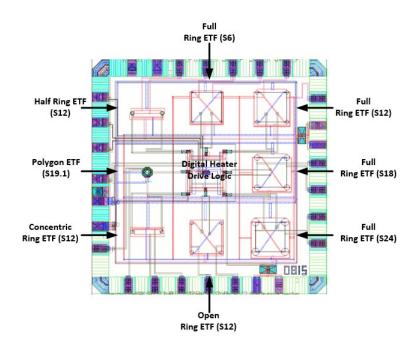

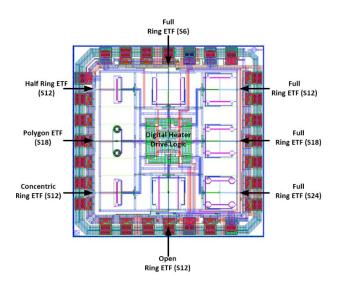

The top-level layout of this test chip is shown in Fig.4.1. It contains 8 ETFs, including 7 Ring ETFs and 1 Polygon ETF (as a reference). Table 4.1 summarizes their parameters, like their names, ETF type, 'S' and bridge resistance.

Figure.4.1 The top-level layout of this test chip 1

For the heaters, bar-shaped n+ diffusion resistors without silicide (Length: 7.2 $\mu$ m, Width:2.5 $\mu$ m, Resistance:194 $\Omega$ ) are used. The width of the heaters is limited by the maximum current density (800 $\mu$ A/ $\mu$ m) specified in Cadence models. This low resistance allows for a maximum heater power of 8mW which provides a large enough signal to characterize the ring ETFs.

Table-4.1 ETF details of test chip 1

| No. | Name    | ETF Type        | Distance 'S'(µm) | Rbridge( $\Omega$ ) |  |

|-----|---------|-----------------|------------------|---------------------|--|

| 1   | Q4S6    | Full Ring       | 6                | 136                 |  |

| 2   | Q4S12   | Full Ring       | 12               | 320                 |  |

| 3   | Q4S18   | Full Ring       | 18               | 432                 |  |

| 4   | Q4S24   | Full Ring       | 24               | 580                 |  |

| 5   | HalfS12 | Half Ring       | 12               | 458                 |  |

| 6   | OpenS12 | Open Ring       | 12               | 1005                |  |

| 7   | Q2S12   | Concentric Ring | 12               | 319                 |  |

| 8   | TP      | Polygon         | 19.1             | 494                 |  |

## 4.1.2 - Circuit diagrams

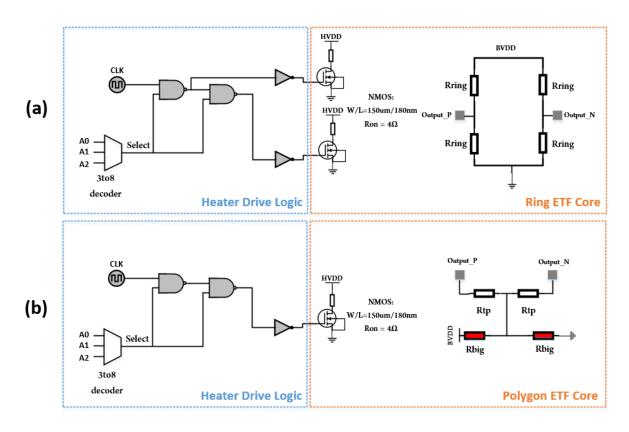

As shown in Fig.4.2, the circuit diagram of a single ETF includes a heater drive circuit and a ETF core. The heater drive circuit is used to switch on/off the heater periodically after selecting by a 3-to-8 decoder. In the ETF core, the outputs are taken directly to the pads.

Figure 4.2 The circuit diagram of the ring ETFs (a) and the polygon ETF (b) in test chip 1

As shown in Fig.4.2, a square wave heat signal is achieved by driving an NMOS switch placed in series with the heater. For the size of driving NMOS, there is a design trade-off:

- 1. The on-resistance should be small enough to ensure less spread and less power wasted in the switch. In this sense, a wide NMOS switch is preferred.

- 2. The error due to CLK delay spread over corners should be minimized. A narrow NMOS switch is favorable because of its small gate capacitance.

Take these considerations into account, the optimal width of NMOS is around 150 $\mu$ m with the minimum length (0.18 $\mu$ m). The simulated CLK delay is 300ps. Given F<sub>drive</sub>=42kHz, 20% spread of this CLK delay would result in a 5m°C error, which is sufficiently low for the targeted accuracy. Given a 1.8V supply, the heater's power spreads by 0.4mW over corners in the simulation. Assuming S=24 $\mu$ m, Z<sub>package</sub>=50°C/W, the error due to the power variation would be 0.04°C. However, in this design, the fatal flaw is the huge power consumption of bridges (81mW), since they are not multiplexed properly. As will be shown later, it introduces more than 0.5°C error, which degrades the accuracy of the various ETFs significantly.

### 4.1.3 – Layout

Fig.4.3 illustrates the layout of the Q4S24 ETF in this test chip, including the bar-shaped heaters and 4 octagonal thermistors.

Figure 4.3 The layout of Q4S24 ETF in test chip 1

## 4.2 -Measurement set-up

### 4.2.1 - System diagrams

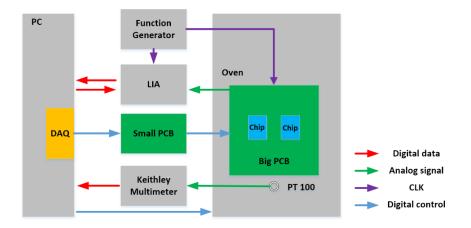

In all the measurements, samples were characterized in a Votsch VT 7004 oven in which temperature can be well controlled. A Pt-100 temperature sensor was used as the temperature reference, which had been calibrated to better than 10mK (from -75°C to 145°C). Its resistance was measured by a Keithley 2002 multimeter. The resolution of the multimeter is 26 bits with a measured period of 1 power line cycle, which corresponds to  $3\mu\Omega$  in a  $200\Omega$  range and a temperature resolution of  $7.7\mu$ K. The Pt-100 sensor was placed inside a large aluminium block, and chips were mounted on the block [27].

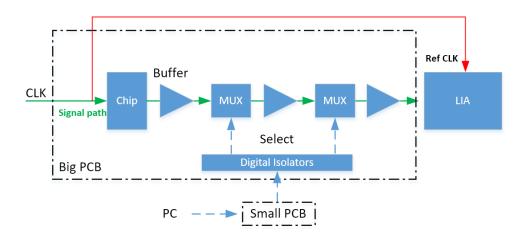

The diagram of measurement setup is shown in Fig.4.4. A PC was used to send all the control commands and record the data. The lock-in amplifier (LIA) was used to demodulate the outputs of ETFs and read out the phase information directly. The type of the Lock-in amplifier is SR865A. The phase noise of this amplifier (<1m° with 100ms time constant and 12dB/oct slope) can be translated to less than 5mK temperature resolution, which is sufficiently low for the target accuracy. The frequency accuracy of the LIA is 25ppm, which will result in less than 2mK temperature error (from Eq.3.9). The PCBs' design will be discussed in the next section.

Figure.4.4 Measurement system diagram

## 4.2.2 - PCB design

As shown in Fig.4.5, there are 2 PCBs in the whole measurement setup. All the digital control signals are controlled by a PC and transmitted to the chips via a small PCB. the small PCB is an adaptor between a VHDCl header (PC) and a flat cable header (big PCB). In the big PCB, digital isolators are used in conjunction with isolated power supplies

to prevent noise currents on the data buses. The primary purpose of the big PCB is selecting the ETF outputs from different sensors and sending it to the lock-in amplifier.

The spread of delay (phase shift) on the readout chain can introduce significant temperature error during measurements. In order to minimize this error, the output signal is firstly buffered by a high-speed buffer (500MHz -3dB-bandwidth), and then multiplexed using reed relays (<1 $\Omega$  on-resistance) before it was sent to the lock-in amplifier via coaxial cables. For the Q4S24 ETF, the large bridge resistance (580 $\Omega$ ) together with the total parasitic capacitance (8pF) of the pad and the PCB, limits the bandwidth of the entire readout chain to 34MHz. According to Eq.3.7, the estimated RC error is 35mK then about given F<sub>drive</sub>=42kHz. Therefore, a resistor (500  $\Omega$ ) and a dummy buffer in a reference CLK path are used to mimic the RC delay to provide a first order compensation.

Figure 4.5 PCB diagram of this test chip 1

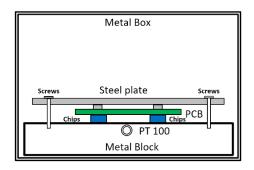

## 4.2.3 – Temperature stability control

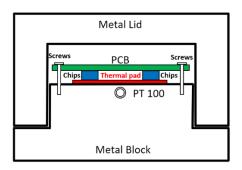

The key accurate temperature measurements is creating a thermal equilibrium between the Pt-100 reference and the sensors so that the measurement error can be minimized. As shown in Fig.4.6, in order to achieve this, the lead of chips was touched with a thermal pad of excellent thermal conductivity (5W/mK) and screws were used to press the chips against a large block tightly. The metal block acted as a low-pass thermal filter with an extremely low corner frequency (<1mHz), keeping the sensor's temperature stable during the measurements. A metal lid was used to avoid temperature fluctuations due to airflow inside the oven. The Pt-100 temperature sensor was inserted into a hole on the block near the chips.

Figure.4.6 Measurement set-up for test chip 1, cross-sectional view

By recording the resistance of the PT-100 sensor with a Keithley multimeter at  $30^{\circ}$ C, the temperature stability with the metal block was measured to be 1.5mK ( $3\sigma$ ) with a 0.1Hz sampling rate. In the accuracy measurements, the difference between two successive readouts of the Pt-100 temperature reference (about 30s per readout) was measured to be less than 1mK, this results held for 300 successive readouts without any exception. Therefore, the Pt-100 and the chips could then be considered to be in thermal equilibrium, and thus the LIA could start to capture the signals. For a single temperature point, the oven takes about 4 hours to settle.

### 4.2.4 - Set-up evolvements

To speed up the measurements, initially, two sockets were placed on the big PCB so that two chips could be measured in the same oven run. However, the phase spread between two sockets was measured to be 15m°, leading to around 1°C temperature error. In order to eliminate the socket dependency, we finally decided to use only one socket to measure the chips, at a cost of 2x more measurement time.

### 4.3 -Measurement results

#### 4.3.1 – Phase characteristics

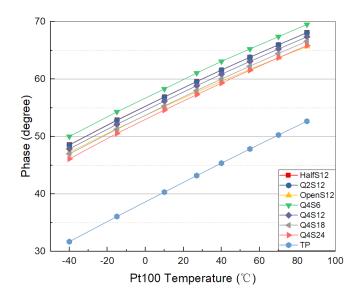

The initial measurements (Fig.4.7) show that  $\phi_{Ring\_ETF}$  is a near-linear function of temperature as expected from Eq.3.2. This validates the Ring ETF's temperature sensing potential.

Figure.4.7 Phase versus temperature at a constant driving frequency

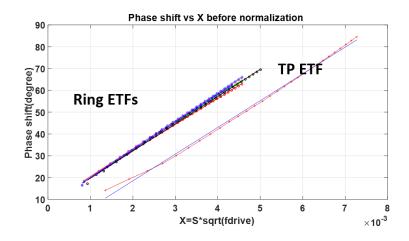

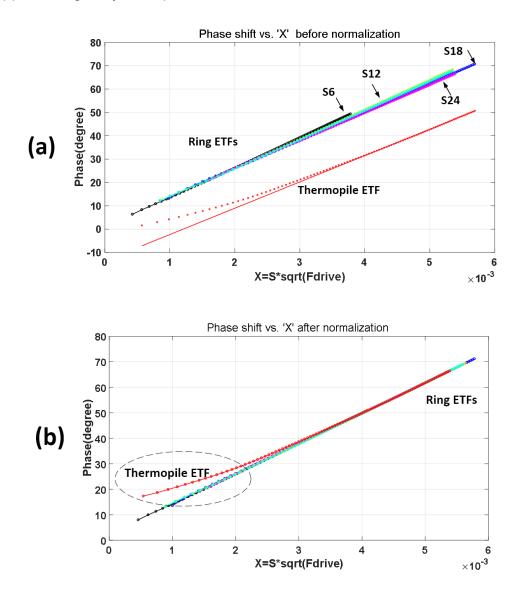

To investigate whether the phase shifts are as expected, we can define a normalization factor 'X' given by:  $X=S\times \sqrt{f_{drive}}$ . As suggested by Eq.3.2, at a certain temperature, this 'X' should be proportional to the ETF's output phase with a slope of  $\sqrt{\frac{\pi}{D_{si}}}$ . As shown in

Fig.4.8, at a fixed temperature (27°C), all Ring ETFs exhibited this feature, which is similar to the thermopile ETF.

However, the bar heater was not an ideal point source in our design, so the effective 'S' is layout dependent. Assuming  $D_{si}$  is constant, we can use the results from a reference ETF (S24) to compute the effective 'S' and the thermal diffusivity  $D_{si}$  of the substrate from the measured slopes:

$$S_{\text{effective}} = \frac{Slope_{\text{ref}}}{Slope_{measured}} \times S_{\text{nominal}}$$

(4.1)

The effective 'S' of 8 ETFs and estimated  $D_{si}$  are summarized in Table 4.2 as well. The effective value of thermal diffusivity 'Dsi' (0.7cm²/s) matches well with the results in [26]. By replacing the nominal 'S' with the effective 'S' and adjusting normalization factor 'X', all the curves we found to overlap as shown in Fig.4.9.

Figure.4.8 Phase vs. 'X', before normalization

Figure 4.9 Phase vs. 'X', after normalization

## 4.3.2 - Resolution optimization

Maximizing the temperature-sensing resolution of ETFs is an important way of preventing noise from degrading the measurement accuracy. Hence, it is important to find the optimal driving frequency for ETFs and maximize the resolution. From Eq.3.6, theoretical analysis of the resolution is too complex obviously, so an experimental approach is used.

Considering a point heater ETF driven by a sine wave, whose phase shift  $\phi_{ETF}$  is read out by a phase detector in the lock-in amplifier. The filtered output will be a DC component given by:

$$V_{DC} = A_{ETF} \times \text{Sin}(\phi_{ETF} - \phi_{demo})$$

(4.2)

where  $A_{ETF}$  is the amplitude of the ETF output and  $\phi_{demo}$  is the reference phase for demodulation. After using a lock-in amplifier to measure  $A_{ETF}$  and  $\phi_{ETF}$  at two close temperatures, e.g. T1 (27°C) and T2 (30°C), the sensitivity  $\frac{\partial V_{DC}}{\partial T}$  of ETF could be calculated as follows:

$$\frac{\partial V_{DC}}{\partial T} = \frac{A_{ETF,T_2} \times \text{Sin}(\phi_{ETF,T_2} - \phi_{demo}) - A_{ETF,T_1} \times \text{Sin}(\phi_{ETF,T_1} - \phi_{demo})}{T_2 - T_1}$$

(4.3)

Since  $A_{ETF}$  changes much slowly with temperature,  $A_{ETF,T_2}$  is approximately equal to  $A_{ETF,T_1}$ , then the sensitivity  $\frac{\partial V_{DC}}{\partial T}$  of ETF is approximately:

$$\frac{\partial V_{DC}}{\partial T} \approx \frac{A_{ETF,T_2} \times \left[ Sin(\phi_{ETF,T_2} - \phi_{demo}) - Sin(\phi_{ETF,T_1} - \phi_{demo}) \right]}{T_2 - T_1}$$

$$\approx 2 \times A_{ETF,T_2} \times \frac{Sin(\frac{\phi_{ETF,T_2} - \phi_{ETF,T_1}}{2})}{\left(T_2 - T_1\right)} \times Cos(\frac{\phi_{ETF,T_2} + \phi_{ETF,T_1}}{2} - \phi_{demo})$$

(4.4)

$\phi_{de mod}$  is adjusted such that V<sub>DC</sub> can be made zero. Thus, the cosine term in Eq.4.4 becomes  $\cos(\pi/2)$  [14]. And the phase difference  $\left(\phi_{ETF,T_2} - \phi_{ETF,T_1}\right)$  is close to zero. Then the sensitivity of V<sub>DC</sub> to temperature variations can be simplified further as follows:

$$\frac{\partial V_{DC}}{\partial T} \approx A_{ETF, T_2} \times \frac{\operatorname{Sin}(\phi_{ETF, T_2} - \phi_{ETF, T_1})}{(T_2 - T_1)}$$

(4.5)

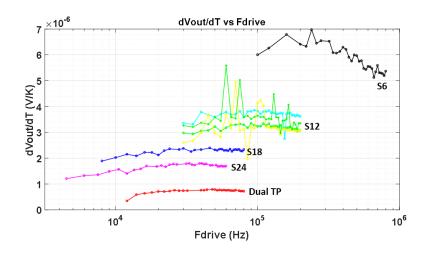

After sweeping the driving frequency, we would be able to find out the optimal  $F_{drive}$  to maximize the sensitivity  $\frac{\partial V_{DC}}{\partial T}$ . The measured  $\frac{\partial V_{DC}}{\partial T}$  is shown in Fig.4.10, which increases at first and then decreases with the driving frequency.

Figure 4.10 Fdrive optimization for 8 ETFs

Given the optimal driving frequency, the temperature sensing resolution of a ETF can be calculated as follows:

$$res = \frac{\sqrt{4kTR_{bridge}B}}{\left(\frac{\partial V_{DC}}{\partial T}\right)} \tag{4.6}$$

The optimal frequencies and calculated resolutions are listed in Table 4.2. The resolutions of all ring ETFs are lower than 2m °Crms in a bandwidth of 0.5Hz.

## 4.3.3 – Untrimmed accuracy

To reduce the significant error due to the huge power of bridges and evaluate the real spread of ETF, two approaches are proposed: power regulation & extrapolation, and FIB circuit edit.

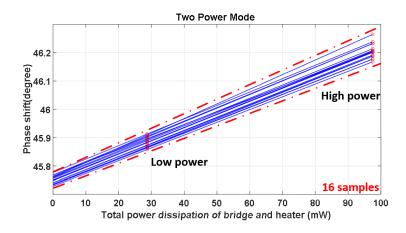

### 4.3.3.1 – Power regulation and extrapolation

The first approach is to regulate the total power dissipation  $P_{total}$  of chips at two power modes by first adjusting the power supplies of bridges and heaters, then plotting the phase versus  $P_{total}$ , and finally doing the extrapolation to find the expected phase output when  $P_{total}$  =0. After the extrapolation, the Q4S18 ETF has the best accuracy among all the ETFs. As shown in Fig.4.11, its  $3\sigma$  spread (16 samples) of phase at 0 power dissipation is about  $\pm 0.04^{\circ}$  at room temperature. With the measured phase-sensitivity of  $7^{\circ}$ C/°p, the untrimmed inaccuracy is  $\pm 0.3^{\circ}$ C ( $3\sigma$ ). By implementing this approach, the measured temperature spread of various ETFs is summarized in Table 4.2.

Figure 4.11 Power regulation and extrapolation to reduce the self-heating effect

#### 4.3.3.2 - FIB circuit edit

A costly way is to use FIB to modify the on-chip circuits. Thanks to the help of ADI, 7 out of 8 bridges were disabled by disconnecting them from the bridge's power supply, and only the Q4S18 ETF remained operational. As a result, the total power consumption of the entire chip dropped by 7x roughly. 5 devices were measured at  $27^{\circ}$ C, the phase spread was  $400\text{m}^{\circ}$ , which corresponds to  $0.28^{\circ}$ C ( $3\sigma$ ) temperature error.

## 4.4 -Summary table

Table-4.2 Measurement result summary for test chip 1

| No. | ETF Type   | 'S'  | Effective<br>'S' | Estimated<br>'Dsi'   | Optimal<br>'Fdrive' | Resolution | Untrimmed<br>accuracy at 27°C |

|-----|------------|------|------------------|----------------------|---------------------|------------|-------------------------------|

|     |            | (µm) | (µm)             | (cm <sup>2</sup> /s) | (kHz)               | (m°Crms)   | $(^{\circ}C(3\sigma))$        |

| 1   | Full Ring  | 6    | 6.2              | 0.76                 | 300                 | 0.15       | 1.05                          |

| 2   | Full Ring  | 12   | 11.9             | 0.70                 | 100                 | 0.50       | 0.47                          |

| 3   | Full Ring  | 18   | 17.8             | 0.69                 | 46                  | 0.79       | 0.30 (*1)<br>0.28 (*2)        |

| 4   | Full Ring  | 24   | 24 (ref)         | 0.7                  | 35                  | 1.22       | 0.51                          |

| 5   | Half Ring  | 12   | 11.9             | 0.69                 | 100                 | 0.51       | 0.41                          |

| 6   | Open Ring  | 12   | 12.3             | 0.75                 | 100                 | 0.91       | 0.54                          |

| 7   | Concentric | 12   | 11.8             | 0.68                 | 100                 | 0.44       | 0.64                          |

|     | Ring       |      |                  |                      |                     |            |                               |

| 8   | Polygon    | 19.1 | 19.7             | 0.75                 | 46                  | 2.58       | 0.44                          |

<sup>\*1:</sup> The estimated untrimmed accuracy with power regulation and extrapolation (16 samples)

<sup>\*2:</sup> The estimated untrimmed accuracy with FIB circuit edit (5 samples)

## 4.5 -Summary

In this chapter, the design details, measurement set-up and characterization results of test chip 1 have been discussed. Similar to thermopile ETFs, the phase shift of ring ETF has a near-linear  $T^{0.9}$  temperature dependency. Given the same measurement set-up, ring ETFs exhibit high enough resolution (<2m °Crms) and good untrimmed inaccuracy (Q4S18:  $0.3^{\circ}C(3\sigma)$ ). In conclusion, they have the potential to be used as electrothermal filters for no-trim temperature sensors.

However, both the self-heating effect and RC error degraded the performance of ring ETFs too much. To investigate them further, an improved version of test chip will be discussed in the next chapter.

# 5 - Test chip 2

The second prototype chip of ring ETFs was fabricated in the ADI180nm CMOS process. The first prototype chip was transferred to ADI, where it was modified and improved mainly by a small team, including Jed Hurwitz, Declan McDonagh, Chris Brown, Caspar Van Vroonhoven and Jeo Spalding. In this chapter, the chip details, measurement set-up and characterization results will be discussed.

## 5.1 -Chip details and improvements

### 5.1.1 - ETF details

The top-level layout of this test chip 2 is shown in the figure below. This test chip also contains 8 ETFs, including 7 Ring ETFs and 1 Dual-Polygon ETF (as a reference). Table 5.1 shows their parameters.

Figure.5.1 The top-level layout of test chip 2

Table-5.1 ETF details of test chip 2

| No. | Name    | ETF Type        | Distance 'S'(μm) | Rbridge( $\Omega$ ) |  |

|-----|---------|-----------------|------------------|---------------------|--|

| 1   | Q4S6    | Full Ring       | 6                | 175                 |  |

| 2   | Q4S12   | Full Ring 12    |                  | 236                 |  |

| 3   | Q4S18   | Full Ring       | 18               | 349                 |  |

| 4   | Q4S24   | Full Ring       | 24               | 464                 |  |

| 5   | HalfS12 | Half Ring       | 12               | 456                 |  |

| 6   | OpenS12 | Open Ring       | 12               | 918                 |  |

| 7   | Q2S12   | Concentric Ring | 12               | 243                 |  |

| 8   | Dual-TP | Polygon         | 18               | 630                 |  |

### 5.1.2 - Chip improvements

Five main changes were made in the new chip to improve its performance:

- 1. The bridges were multiplexed so that the chip dissipated ~5x less power, leading to much less temperature error due to self-heating effects.

- 2. The phase shift due to the RC filtering and the delay of the on-chip logic circuits, can be measured and compensated. This will be discussed in section 5.1.3.

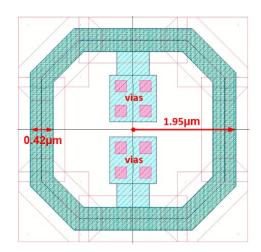

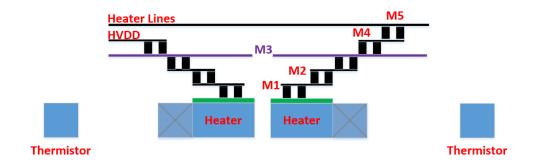

- 3. Instead of using the bar heater, a compact octagonal heater was implemented. As shown in Fig 5.2, the contact vias were placed inside the ring, making the radius of the whole heater smaller than 2 $\mu$ m. Thus, it behaves more like an ideal point source compared to the bar heater (7.2 $\mu$ m x 2.5 $\mu$ m). The resistance of new heater is about 560 $\Omega$ , so each heater would consume 3mW power when driven by a square wave with a 1.8Vpp amplitude.

Figure.5.2 The octagonal heater in test chip 2

4. To minimize the crosstalk between heater/clock lines and signal lines, shielding layers were used. As Fig 5.3 shows, the heaters were shielded by a wall of M1 and M2, then capped by M3, while the connections to heaters were brought up to M4 and M5. The thermistors were shielded as well. For the S24 ETF, the extra parasitic capacitance associated with the shields was estimated to be in the magnitude of fF, which is negligible.

Figure 5.3 Shielding layers are used to avoid crosstalk

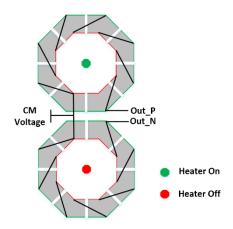

5. The single thermopile ETF was replaced by a dual thermopile ETF to provide a balanced output and improve the signal level by 2x thus  $\sqrt{2}x$  better resolution. However, this comes at the expense of doubling the heater power. Figure 5.4 shows the structure of the dual-thermopile ETF.

Figure 5.4 The structure of the dual-thermopile ETF

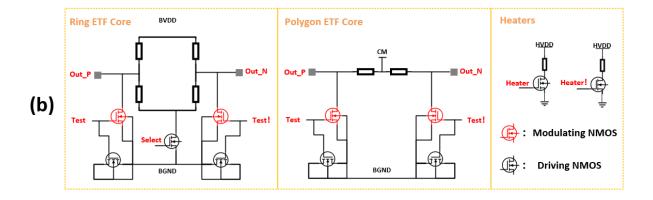

## 5.1.3 - Circuit diagrams

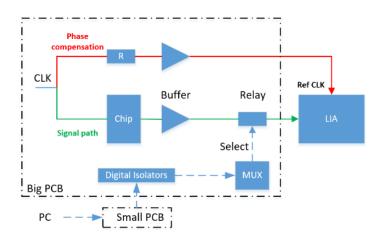

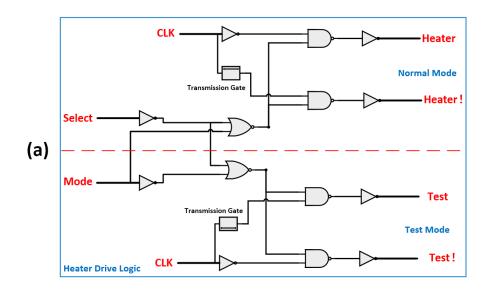

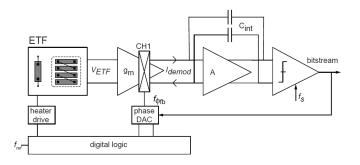

#### 5.1.3.1 - Phase autozeroing

The ETFs can be operated in two different modes: the normal mode and the test mode. In the normal mode, the heaters are driven by a square-wave and the ETFs behave as typical TD sensors. The phase shift is  $\phi_{\text{normal}}$ . In the test mode, all heaters are switched off and two long modulating NMOS beside the bridge are turned on/off at the same driving frequency as shown in Fig.5.5 (b). Thus, a small differential square-wave voltage is generated at the ETF outputs. The phase shift of this voltage  $\phi_{\text{test}}$  should be identical to the additional phase shift due to RC filtering and on-chip logic in the normal mode. Hence,

the exact phase shift due to the thermal diffusion process of ETF can be computed as follows:

$$\phi_{ETF} = \phi_{\text{normal}} - \phi_{\text{test}} \tag{5.1}$$

With this approach, the spread of on-chip logic delay and RC delay is expected to be reduced dramatically.

#### 5.1.3.2 - Circuit implementation

Like test chip 1, the heater is driven by a single NMOS switch. Apart from the CLK and 3-bit address, another pair of control signals (Test/Test!) are added to switch between two modes. As shown in Fig 5.5, a transmission gate is used to compensate for the delay of the first inverter. This ensures that the edges of Heater and Heater! are well synchronized. An NMOS is placed in series with the bridge to disable it when select ='0'.

For phase autozeroing, the on-resistance of the modulating NMOS is about  $10k\Omega$ . To obtain similar amplitude outputs for the different ETFs, the associated NMOS switches are designed to have different on-resistances.

In addition, the gates of the modulating NMOS are loaded with MOS caps of the same size as the heater drive NMOS, which makes the delay difference between two modes negligible (<10ps).

Figure 5.5 The circuit diagram of ring ETF and polygon ETF in test chip 2, including heater drive circuits (a) and ETF cores (b)

### 5.1.4 - Layout

Fig.5.6 illustrates the layout of Q4S24 ETF in this test chip, including the octagonal heaters and 4 octagonal thermistors.

Figure 5.6 The layout of Q4S24 ETF in test chip 2

# 5.2 -Measurement set-up

Since the measurement system of test chip 2 is quite similar to that of test chip 1, this section will only focus on the PCB design and set-up evolvements.

### 5.2.1 - PCB design

To speed up the measurements, a larger PCB was designed so that 8 chips (64ETFs) can be characterized in a single oven run. As mentioned early, the introduction of test mode should make the RC errors insignificant, which relaxes the PCB design. However, we expect that the phase compensation would perform better when the bandwidth of the entire readout chain is higher.

Fig.5.7 presents the system diagram of PCBs. The outputs are multiplexed by 2 levels of 8-to-1 MUX's together with 3 levels of high-speed buffer (500MHz -3dB bandwidth). The RC delay is dominated by the bridge and the parasitic capacitors of pad, traces, and buffers (~8pF). Assuming S =24 $\mu$ m, optimal F<sub>drive</sub>= 35kHz, Rbridge=464 $\Omega$ , phase sensitivity= 7°C/°p, the -3dB bandwidth is around 43MHz. The phase shift is 47m°,10% spread of it would causea temperature error of about 0.03°C before compensation.

For each chip, 16 1st-level buffers are placed close to the pins to reduce the parasitic capacitance of traces. To save power, only one group of buffers are turned on when the chip is selected. Totally, the big PCB employees 146 buffers (1st-level: 128, 2nd-level: 16,3rd-level: 2) and 18 8-to-1 MUXes (1st-level: 16, 2nd-level: 2).

Figure 5.7 PCB system diagram of test chip 2

### 5.2.2 - Set-up evolvements

#### 5.2.2.1 - New set-up

Since this PCB cannot fit with the previous aluminum block, a new set-up is needed. Fig.5.8 shows the new set-up, in which a steel plate was used to press the chips against the block for better thermal contact. A metal box was used to avoid temperature

fluctuations due to the airflow in the oven. Instead of using the thermal pad, chips were covered by the thermal paste and attached to the block directly, which is helpful to achieve better thermal equilibrium between chips and the block.

Figure 5.8 New set-up for test chip 2, cross-sectional view

#### 5.2.2.2 - PCB modification

As discussed in section 3.6.2, any heat generated by the components on the PCB will destroy the temperature equilibrium between the chips and block, therefore resulting in a significant error. During the measurements, 34 buffers (1st-level: 16, 2nd-level:16, 3rd-level: 2) are switched on concurrently and consume 680mW power. This resulted in ~0.5°C temperature offsets between sockets, makeing it impossible to measure the real spread of the ETFs. Thus, in the latest version of PCB, the 1st and 2nd level buffers were removed and replaced by direct connections. However, the -3dB bandwidth of the entire readout chain is reduced to 8.6MHz because of the large value of the total on-capacitance of the 1st and 2nd level MUX (40 pF). For Q4S24 ETF, the phase shift is 230m° given Fdrive=35kHz, 10% spread of it will introduce temperature error of about 0.2°C before compensation.

In addition, to avoid picking up interference from outside, the lids of ceramic package chips are shorted to ground with wires. Without this, it was observed that the dual thermopile ETF suffers from significant heater/output crosstalk.

#### 5.3 –Measurement results

#### 5.3.1 - Phase characteristics

#### 5.3.1.1 - Phase normalization

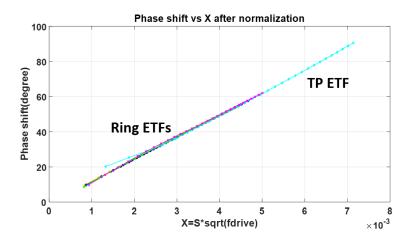

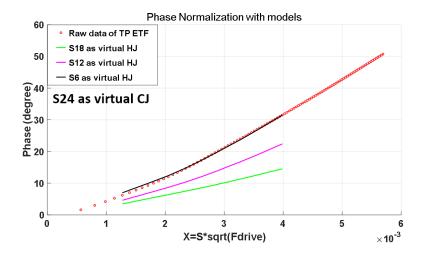

Phase normalization also was performed for 8 ETFs in test chip2 as shown in Fig 5.9. The phase shift of Ring ETF follows the Eq.3.2 very well over a wide frequency range.

The dual thermopile ETF has much less phase shift and exhibits non-linearity at low frequencies, this will be explained in the next section.

The effective 'S' and estimated 'Dsi' are listed in Table 5.2. Since the octagonal heater behaves more like an ideal point source as 'S' increases, the ratio between 'Seffective' and 'S' is approaching unity as expected.

Figure 5.9 Phase normalization for test chip 2, before (a) and after (b) normalization

#### 5.3.1.2 - Thermopile ETF model

In Fig.5.9, the normalized phase of the dual thermopile ETF exhibits some non-linearity at low frequencies, i.e. it no longer like a simple point source /point sensor ETF. This is because of the finite distance between the hot junctions and the cold junctions. To

understand this better, the phase response of each of the two junctions ( $S_{hot}=18\mu m$ ,  $S_{cold}=26\mu m$ ) was be modeled with ring ETF.

For example, the behaviour of cold junction is imitated by a S24 ring ETF, while the hot one is imitated by S18/S12/S6 ring ETFs. The thermal impedance of different junctions (hot/cold) in a thermopile ETF can be writtenas:

$$Zth_{hj} = \frac{Vsig_{hj} \times \exp(-i * phase_{hj})}{(BVDD/2) \times Tc \times P_{heater\_ring}}$$

(5.2)

$$Zth_{cj} = \frac{Vsig_{cj} \times \exp(-i * phase_{cj})}{(BVDD/2) \times Tc \times P_{heater\ ring}}$$

(5.3)

where  $V_{Sig_{cj}}(V_{Sig_{hj}})$  and  $phase_{cj}(phase_{hj})$  are the measured signal amplitude and the phase shift of S24 (S18/S12/S6) ring ETFs, respectively, Tc is the temperature coefficient of N+ diffusion resistor with silicide,  $P_{heater\_ring}$  is the heater power of Q4S24 or Q4S18 ETF. The thermal impedance of the artificial thermopile ETF can be computed as follows:

$$Zth_{T_{D \mod le}} = Zth_{hi} - Zth_{ci}$$

(5.4)

Thus, the phase of the thermopile ETF can be calculated and plotted as shown in Fig.5.10. The S18/S24 combination matches well with the measurement results.

Figure 5.10 Use the output response of ring ETFs to model TP ETF

From Eq.2.6, combining with  $Zth_{T_{p_{-}mod}le}$ , the Seebeck coefficient of the thermopile can also be estimated as follows:

$$S_{tc} = \frac{V_{sig\_TP}}{\left| Zth_{TP\_modle} \right| \times P_{heater\_TP} \times N}$$

(5.5)

where  $V_{sig\_TP}$  is the measured signal amplitude of dual thermopile ETF,  $P_{heater\_TP}$  is the heater power, N is the number of thermocouples (16 in this case). The calculated Seebeck coefficient of the thermopile is 0.42mV/K, which matched well with the reported value (0.5mV/K) in [14].

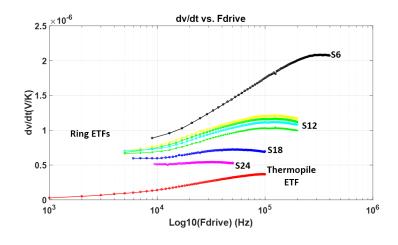

### 5.3.2 – Resolution optimization

The resolution optimization was done for 8 ETFs in test chip2. Experiments were conducted at two temperature points: T1 (27°C) and T2 (35°C). The sensitivities are plotted in Fig. 5.11. Comparing to Fig. 4.13, a bigger temperature gap provides a more clear estimation of the optimal F<sub>drive</sub>. An overview of the optimal driving frequencies and estimated resolutions in a bandwidth of 0.5Hz of 8 ETFs are provided in Table 5.2.

Figure.5.11 Fdrive optimization for 8 ETFs for test chip 2

## 5.3.3 – Untrimmed Accuracy

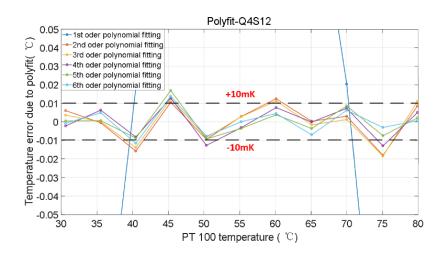

### 5.3.3.1 - Polynomial fit experiments

In this project, a phase output is provided by the LIA, and a polynomial curve fitting is needed to transfer this phase into temperature. In order to limit the impact of the fitting error on the system accuracy (targeted at 0.05°C), the fitting error should be sufficiently

low (~10mK). Higher-order fitting would lead to less error, but longer measurement time and complicated digital circuits are required. Therefore, a minimum polynomial order that meets the accuracy limit is preferred.

To investigate the minimum polynomial order, 5 devices were measured from 5°C to 85 °C with a step of 5°C. Fig.5.12 shows that a 6<sup>th</sup> order polynomial fitting can guarantee a fitting error of 10mK. As a consequence, for the following accuracy measurements, all the ETFs were characterized at 7 temperature points.

Figure 5.12 Polynomial curve fitting for Q4S12

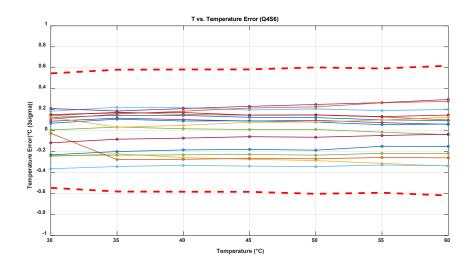

#### 5.3.3.2 - ETFs accuracy

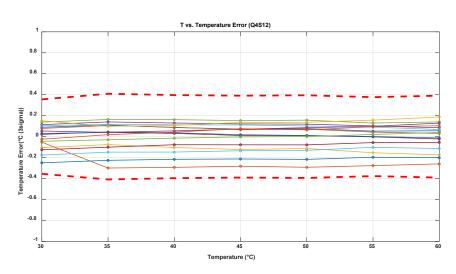

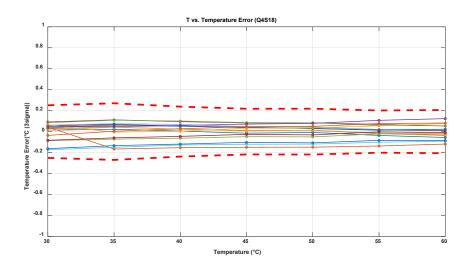

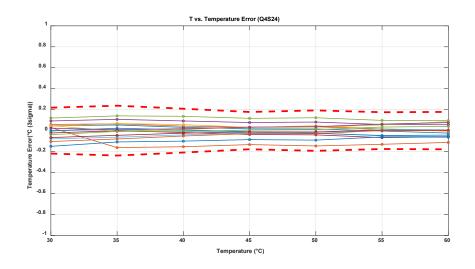

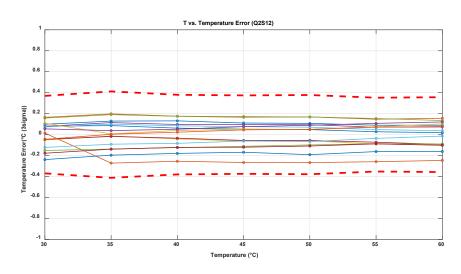

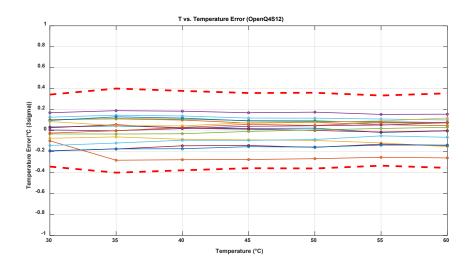

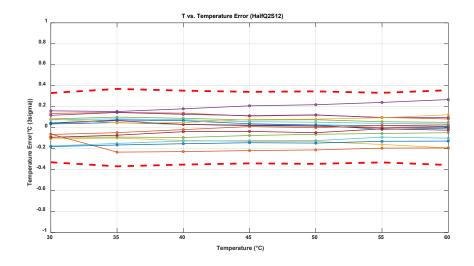

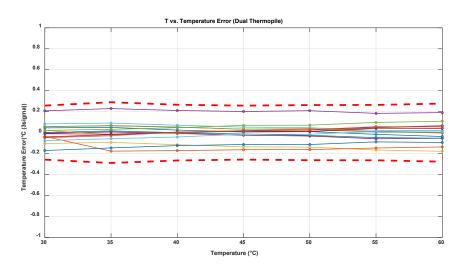

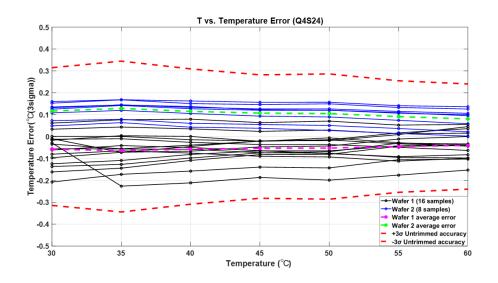

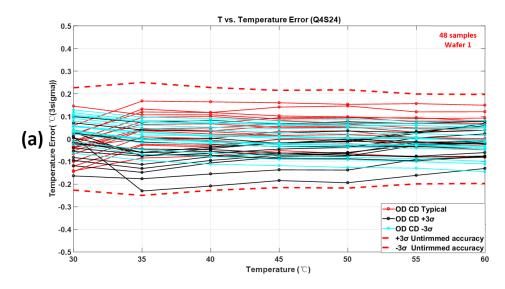

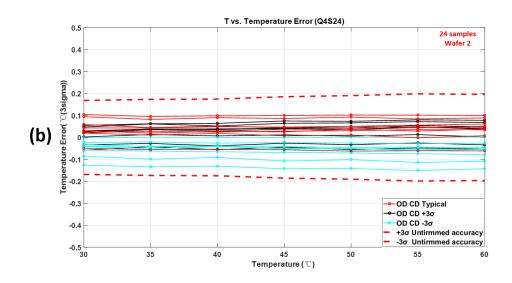

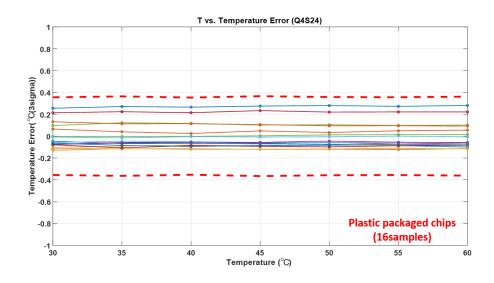

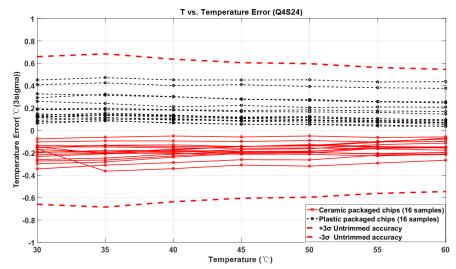

An essential step of these experiments is measuring the untrimmed device-to-device spread of 8 ETFs from 30°C to 60°C with a temperature step of 5°C. For all the ETFs, 16 devices with ceramic packages were measured in the same set-up. After polynomial fitting in MATLAB, the spread plots of 8 types of ETFs from a single batch are shown below, with red dash lines indicating the estimated  $\pm 3\sigma$  limits.

### (a) Q4S6 ETF

## (b) Q4S12 ETF

## (c) Q4S18 ETF

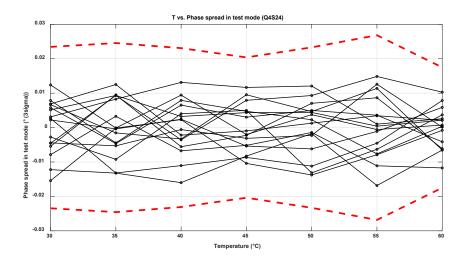

### (d) Q4S24 ETF

### (e) Q2S12 ETF

(f) OpenS12 ETF

(h) HalfS12 ETF

(i) Dual thermopile S18 ETF

The results show that lithography is indeed the main error source of temperature in ring ETFs. The accuracy can be improved if 'S' increases. The Q4S24 ETF has the best accuracy of  $\pm 0.2^{\circ}\text{C}(3\sigma)$  over  $30^{\circ}\text{C}$  to  $60^{\circ}\text{C}$  range, and the dual thermopile S18 ETF exhibits the same accuracy ( $\pm 0.3^{\circ}\text{C}(3\sigma)$ ) as Q4S18 ETF.

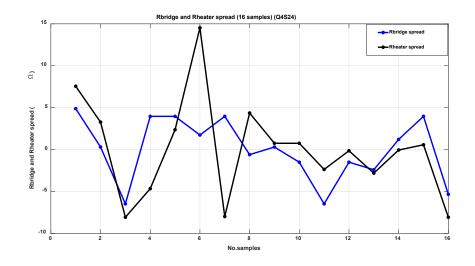

S12 ETFs have almost the same untrimmed accuracies, indicating that the structures have no effect on the accuracy. However, for the sake of power efficiency, half-ring ETF and concentric-ring ETF are favorable in the future design.