## High Voltage Wireless Power Transfer

Design and Prototyping of a DC Power Supply Based on Inductive Power Transfer

ET4300: Master Thesis (5472482)

Suraj Jagannath Manur

#### Design and Prototyping of a DC Power Supply Based on Inductive Power Transfer

by

#### Suraj Jagannath Manur

to obtain the degree of Master of Science in Electrical Engineering at the Delft University of Technology, to be defended publicly on Aug 4, 2023 at 15:00.

Student number: 5472482

Project duration: November 2022 – August 2023

Project Supervisor: Dr. ir. Mohamad Ghaffarian Niasar TU Delft

PhD Supervisor: Ir. Reza Mirzadarani TU Delft

Thesis committee: Dr. ir. Mohamad Ghaffarian Niasar TU Delft

Prof. ir. Peter Vaessen TU Delft

TU Delft

Prof. ir. Peter Vaessen TU Delft Dr. ir. Zian Qin TU Delft

An electronic version of this thesis is available at http://repository.tudelft.nl/.

This thesis is confidential and cannot be made public until July 31, 2025.

No man should escape our universities without knowing how little he knows.

J. Robert Oppenheimer

### Acknowledgements

The journey of learning never stops, the two years at Delft have been an amazing ride, to say the least. The Master's course and the Master's thesis have been an enriching experience from every perspective. This journey has only been possible due to the support, love and patience of a lot of people. I am humbly grateful to all of them.

Firstly, my parents and sister for bearing my idiosyncrasies and supporting me through everything life has thrown. I am glad to be a part of a family which places trust, honesty and hardwork at the forefront. I hope *Subi* and I make you both proud one day.

To the ever-inquisitive Professor *Mohamad*, whose ideas, queries and insights kept me motivated and curious during these two years. Your dedication and passion towards how things work is something I wish to acquire in my career.

To Professor *Peter*, who introduced me to the field of High Voltage at Delft. Your process of breaking down complex processes into much palatable explanations is something I admire.

To Professor *Zian*, for agreeing to spend some time on my thesis and being the external supervisor for my thesis.

To *Reza*, whose curiosity to know more has no bounds. Thank you for enhancing my knowledge of resonant converters, power electronics, high voltage and everything in between.

To *Imke*, *Wim*, *Paul* and *Luis*, for providing me with everything I need for the thesis, and much more. Every aspect of my thesis from the coils, variable capacitors to testing safety has had invaluable insight from you.

To *Dhanashree, Franseca, Sohrab, Weichuan, Gautam* and *Anand,* for clearing my queries by having thought-provoking discussions and providing clarity on the inverter, wireless power transfer and life.

Finally to *Appu, Arpi, Naman, Archith, Shirish, Rishabh, Karun,* the wing bois of Surathkal and my friends at Delft who have been by me through the journey of life.

Suraj Jagannath Manur Delft, August 2023

#### **Abstract**

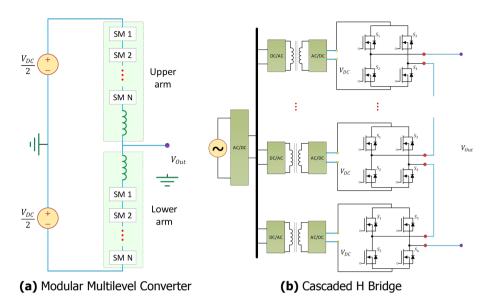

The integration of renewable energy systems into the grid brings new and unique propositions involving the integration of power electronic inverter based solutions into the High Voltage (HV) grid. Thus a need arises to test the HV components with unconventional waveforms which can be satisfied by the Arbitrary Waveshape Generator (AWG). Two such topologies have been shortlisted for the AWG, ie: Modular Multilevel Converter (MMC) & Cascaded H Bridge (CHB). The MMC requires a single insulated DC source while the CHB requires multiple insulated DC sources with isolation.

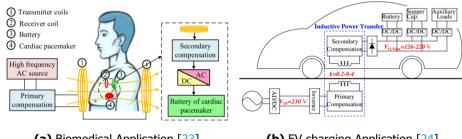

Developing insulated DC sources using traditional transformers requires oil, epoxy or other complex insulation materials. The insulation requirements are further exacerbated when HV > 5 kV is required at power levels greater than 1 kW. For this reason, Wireless Power Transfer (WPT) methods are studied in this thesis to develop a DC Power Supply based on Inductive Power Transfer (IPT). The developed supply is capable of conducting DC breakdown tests and high frequency (>100 kHz) AC discharge tests on dielectrics.

The key requirements for developing such a system are Load Invariant Voltage, High Voltage Gain and Soft Switching. Considering these requirements the Series Parallel (S-P) topology is chosen to deliver 1.5 kW at a DC voltage of 5 kV from a 350 V input, with a diode rectifier. Using the Greinacher rectifier, 10 kV DC output is obtained. Different parameters of the developed resonant converter such as coupling coefficient, switching frequency, deadtime and overcurrent protection are analysed to find a suitable configuration for the DC Power Supply. An efficiency of 88% at rated load and load regulation of 18% is achieved for the developed power supply.

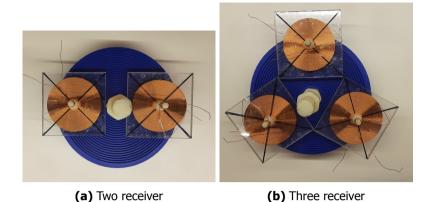

For the CHB, a multi-receiver IPT system is desirable to provide multiple isolated DC outputs. A 2-receiver and a 3-receiver IPT system is constructed and their coupling behaviour is studied. A conclusion is drawn that an "n" receiver system has a coupling coefficient  $k_n = \sqrt{n}k_1$  and accordingly a S-P IPT system can be developed to obtain multiple (n) isolated DC voltage sources.

Suraj Jagannath Manur Delft, August 2023

## Contents

| A  | kno   | wledgements                                        | iii  |

|----|-------|----------------------------------------------------|------|

| Αl | stra  | ct                                                 | v    |

| Li | st of | Figures                                            | ix   |

| Li | st of | Tables                                             | xiii |

| Li | st of | Abbreviations                                      | хv   |

| 1  | Intr  | oduction                                           | 1    |

|    | 1.1   | Test Sources for a Power Electronic Dominated Grid | . 1  |

|    | 1.2   | Wireless Power Transfer                            | . 3  |

|    | 1.3   | Inductive Power Transfer                           | . 3  |

|    |       | An HV-based IPT system                             |      |

|    |       | Thesis Goals & Objectives                          |      |

|    | 1.6   | Thesis Outline                                     | 6    |

| 2  | Top   | ology Analysis                                     | 7    |

|    | 2.1   | Parameters Evaluation                              | . 8  |

|    | 2.2   | One component compensation                         | . 11 |

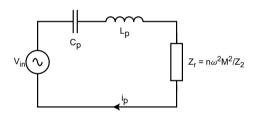

|    |       | 2.2.1 Primary Parallel Compensation                | 13   |

|    |       | 2.2.2 Primary Series Compensation (S-S) & (S-P)    |      |

|    | 2.3   | Multiple component compensation                    |      |

|    |       | 2.3.1 LC Compensation                              |      |

|    |       | 2.3.2 LCC Compensation                             |      |

|    |       | 2.3.3 S-SP Compensation                            |      |

|    |       | Productive drag verage mare production             |      |

|    | 2.5   | Suitable Topology                                  | 25   |

| 3  |       | ies - Parallel Topology                            | 27   |

|    |       | Introduction                                       |      |

|    |       | Load Invariant Voltage                             |      |

|    |       | Mathematical Model                                 |      |

|    |       | Simulation                                         |      |

|    |       | ZVS Operation                                      |      |

|    | 3.6   | Diode Rectifier                                    |      |

|    | 3.7   | Voltage Multiplier                                 |      |

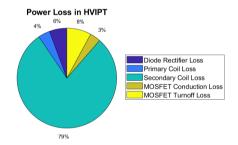

|    | 3.8   | Efficiency Analysis                                |      |

|    | .5 4  | Parametric evaluation                              | 4()  |

viii Contents

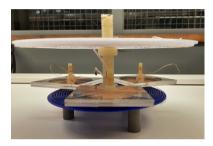

| 4 | Prototype Setup 4.1 Coils                                                            |          |

|---|--------------------------------------------------------------------------------------|----------|

|   | <ul><li>4.2 Compensation Capacitors</li></ul>                                        | 53       |

|   | <ul><li>4.4 Typhoon HIL &amp; Providing Pulses</li><li>4.5 Diode Rectifier</li></ul> |          |

|   | 4.6 Voltage Multiplier                                                               | 57       |

|   | 4.7 Source, Load & Measuring HV                                                      |          |

| 3 | Testing 5.1 Introduction                                                             | 61       |

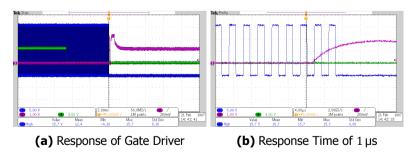

|   | 5.2.2 Overcurrent Test                                                               | 64       |

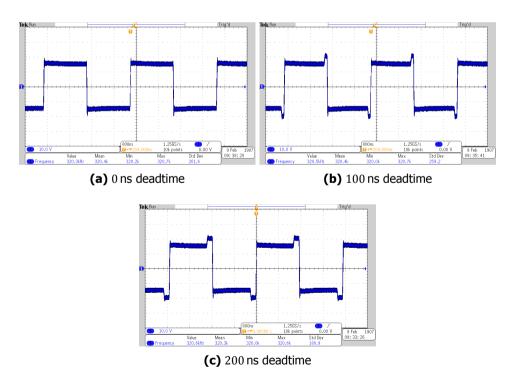

|   | 5.2.5 Deadtime tests                                                                 | 66<br>67 |

|   | 5.2.8 Final test results at 15 V input                                               | 70<br>71 |

|   | <ul> <li>5.5 Efficiency analysis</li></ul>                                           | 73<br>74 |

| 6 | Multiple Output                                                                      | 77       |

| 7 | Conclusion & Recommendations 7.1 Conclusion                                          |          |

| A | MATLAB Code                                                                          | 95       |

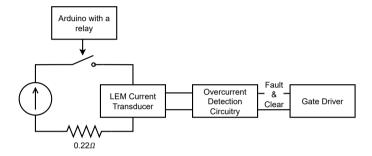

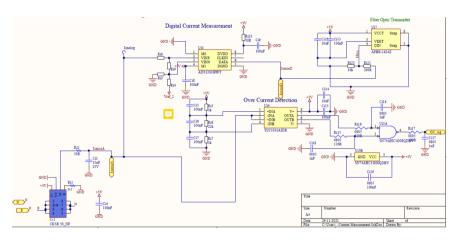

| В | Over Current Protection                                                              | 97       |

## List of Figures

| 1.1<br>1.2<br>1.3                    | Applications of IPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2<br>4<br>5                                                   |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

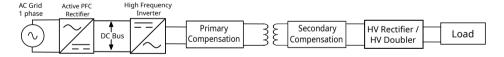

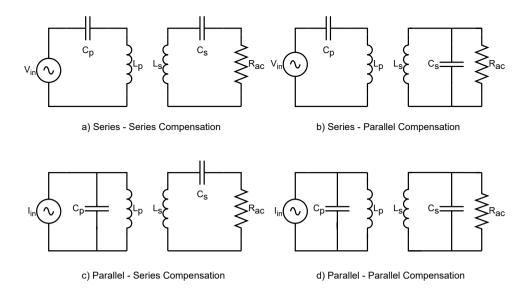

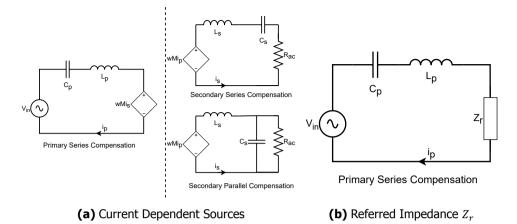

|                                      | HVPS Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7<br>12<br>14<br>15<br>18<br>19<br>21<br>22<br>24<br>24<br>24 |

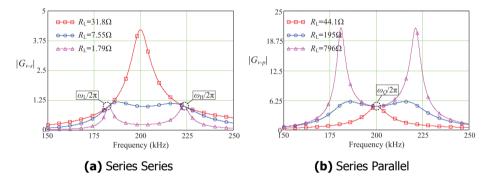

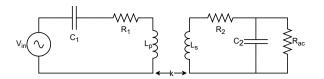

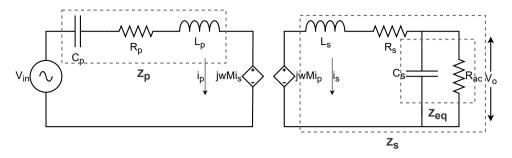

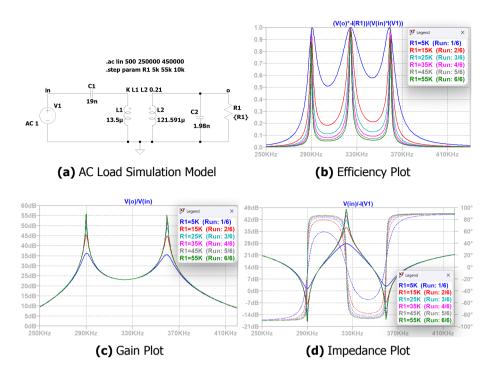

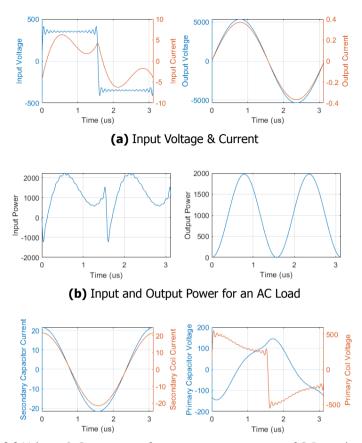

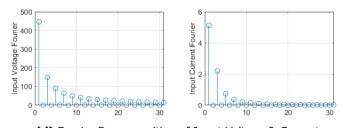

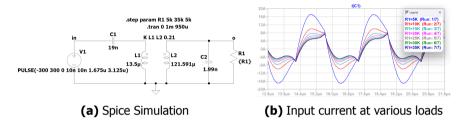

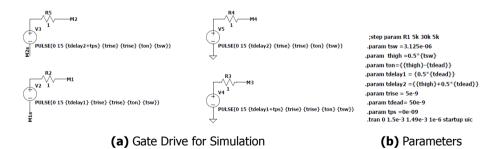

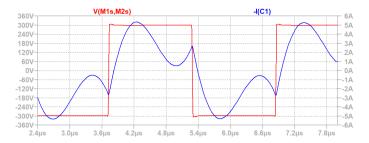

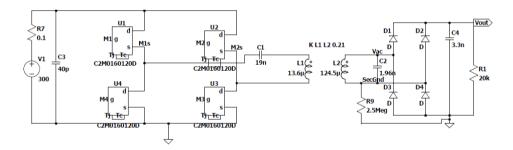

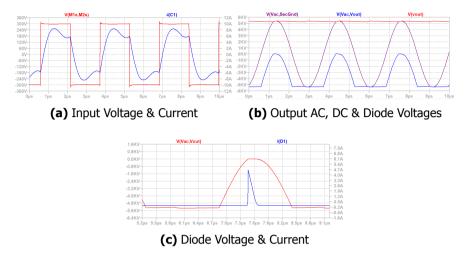

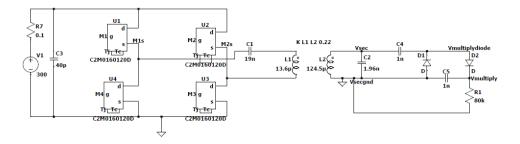

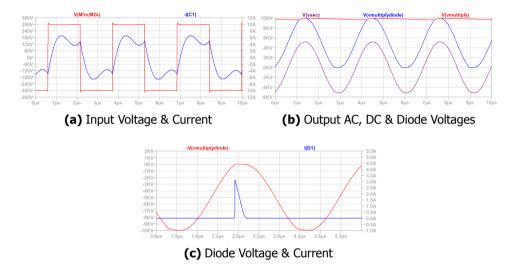

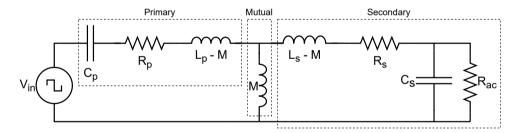

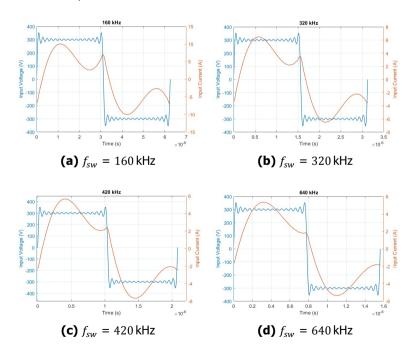

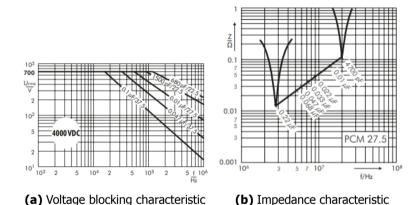

| 3.11<br>3.12<br>3.13<br>3.14<br>3.15 | T Model  M Model  S-P with current controlled voltage sources  Frequency sweep of S-P topology with a variable AC load  Results of the Mathematical Model  Load sweep of the S-P IPT  Driving conditions for SPICE simulation  SPICE Model to analyse ZVS  ZVS analysis from lagging input current  SPICE model of Diode Rectifier  Simulated waveforms of Diode Rectifier  SPICE Model of a One stage Multiplier  SPICE Model of Topical Stage Multiplier  Mutual Inductance Model  Input behaviour of the High Voltage Inductive Power Transfer (HVIPT) based on switching frequency (fsw)  WIMA PCM 27.5 capacitor behaviour across frequencies [63] |                                                               |

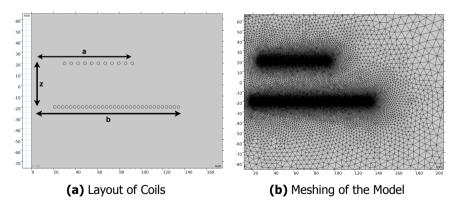

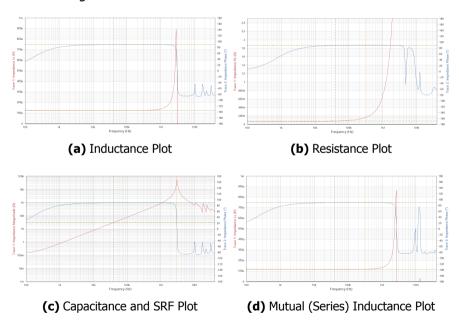

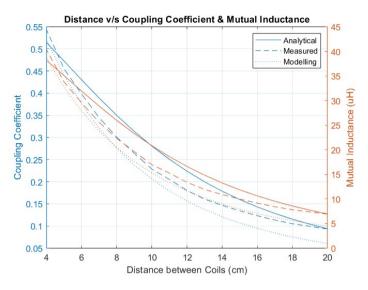

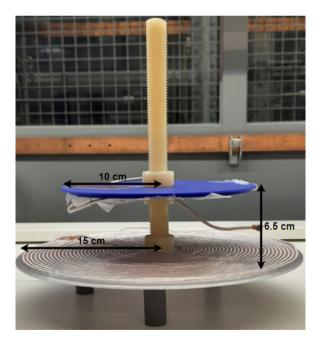

| 4.1<br>4.2<br>4.3<br>4.4             | Designed Coils for HVIPT [Table 4.1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46<br>47<br>48                                                |

x List of Figures

| Litzwire subbundle                                                            | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Primary & Secondary Inductors                                                 | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

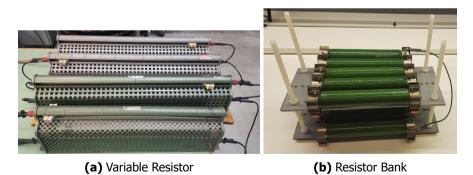

| Variable Capacitor Banks                                                      | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                               | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                               | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

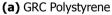

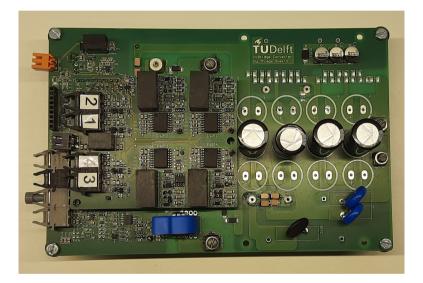

| Two hoards of the Inverter                                                    | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Kelvin Source and Power Source in the SiC MOSFFT                              | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                               | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                               | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

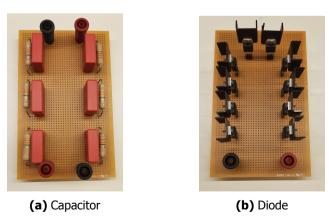

| Multiple Diodes for the rectifier [70]                                        | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

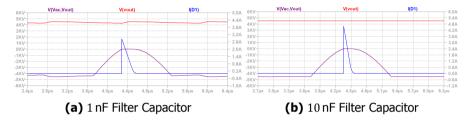

| Diode neak current and Output ripple voltage - Diode Rectifier                | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

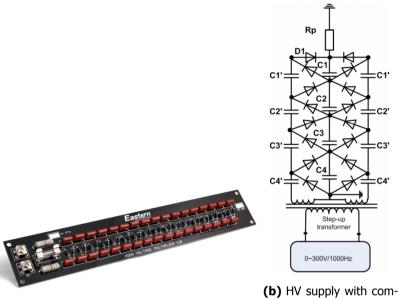

|                                                                               | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

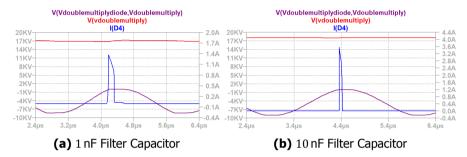

| Diada pank current and Output Dipple voltage Voltage Multiplier               | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Available Leads at LIVLab                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                               | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                               | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                               | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                               | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

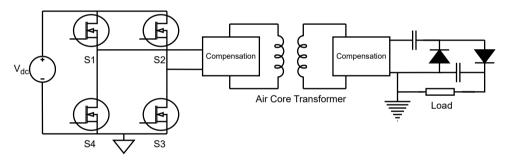

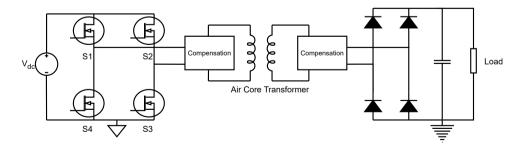

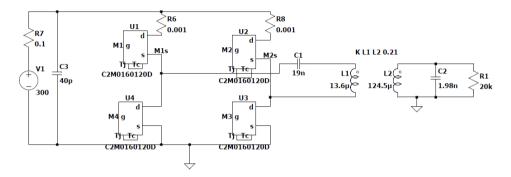

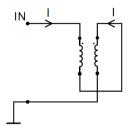

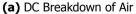

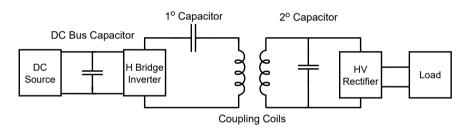

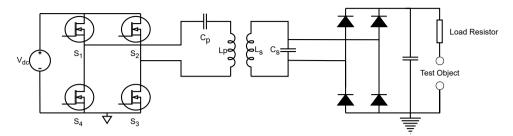

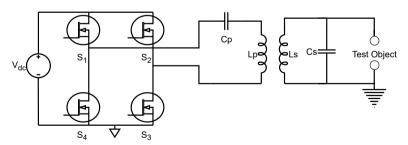

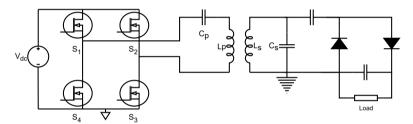

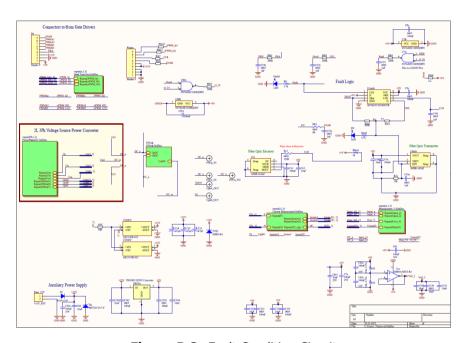

| Circuit Diagram of the HVIPT Prototype                                        | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| No load test of the inverter                                                  | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

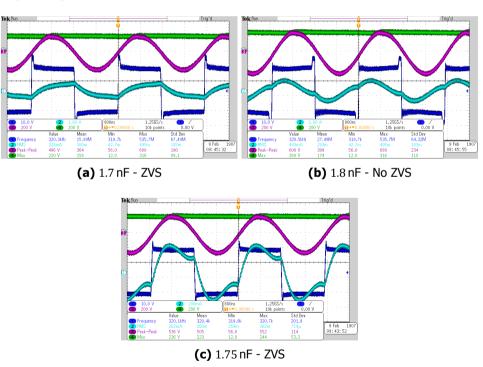

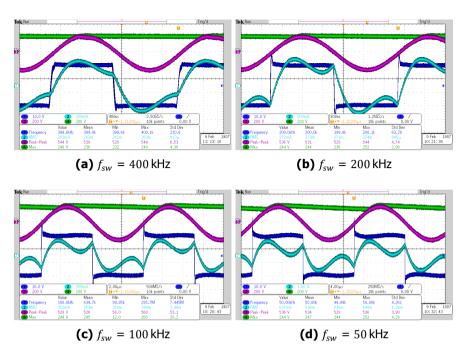

|                                                                               | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                               | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                               | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

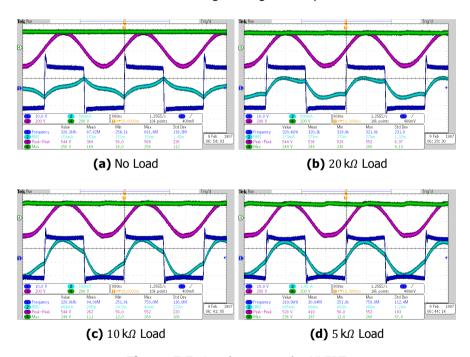

| Load tests on the HVIPT                                                       | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                               | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

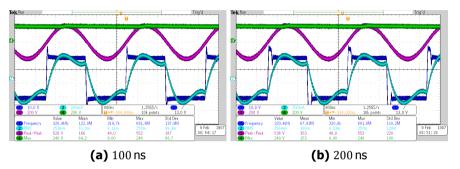

|                                                                               | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                               | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

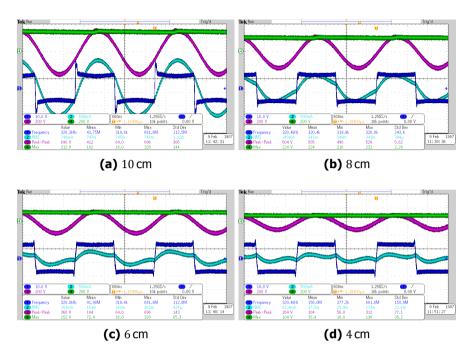

|                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

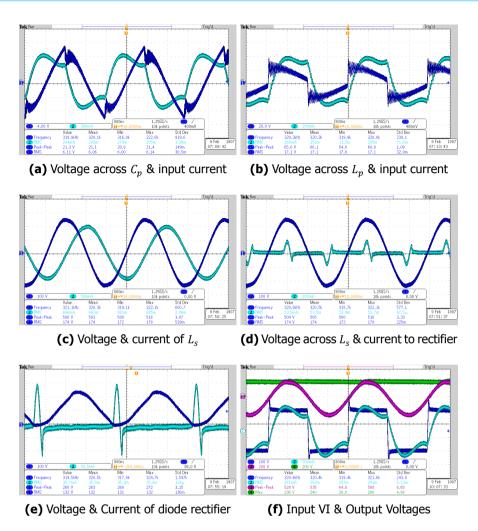

| Final LV tests                                                                | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

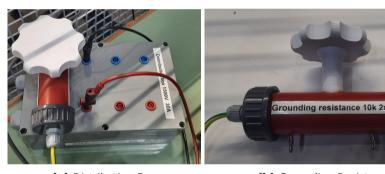

| Safety setup for the SM 1500-CP-30                                            | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

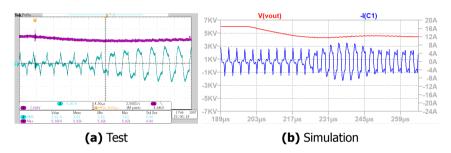

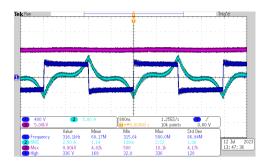

| HVIP1 test at 350 V input                                                     | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                               | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

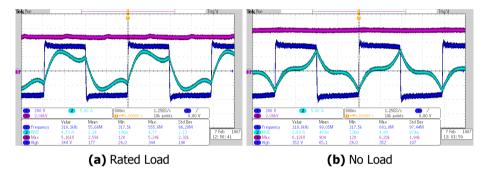

|                                                                               | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                               | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

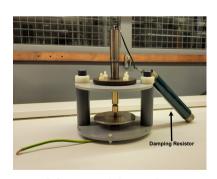

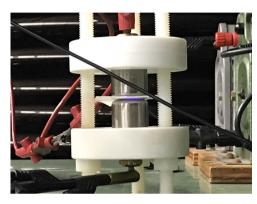

| Breakdown test                                                                | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Circuit Diagram for Surface Discharges                                        | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Surface Discharges on Teflon                                                  | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

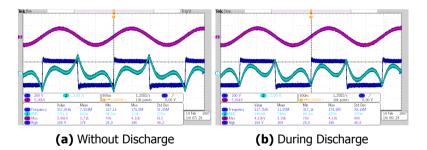

| AC Discharges Waveform                                                        | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HVIPT Test with the Greinacher multiplier                                     | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                               | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

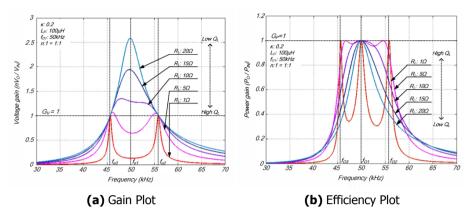

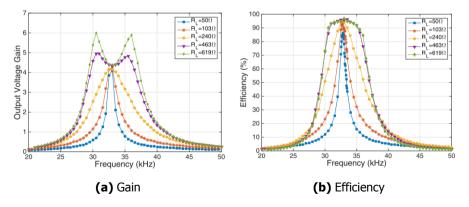

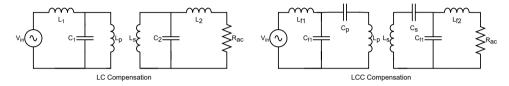

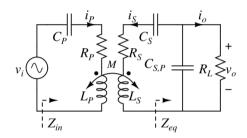

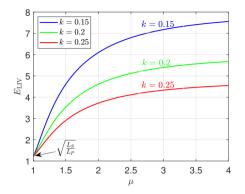

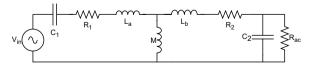

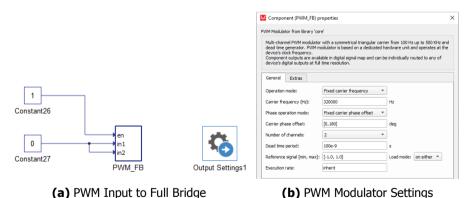

|                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |