### Revitalizing polymer packaging for single-chip implants

Nanbakhsh, K.

10.4233/uuid:2b5d65af-a2dd-4c00-b17b-e4925ca152ee

**Publication date**

**Document Version** Final published version

Citation (APA)

Nanbakhsh, K. (2025). Revitalizing polymer packaging for single-chip implants. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:2b5d65af-a2dd-4c00-b17b-e4925ca152ee

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# REVITALIZING POLYMER PACKAGING FOR SINGLE-CHIP IMPLANTS

### REVITALIZING POLYMER PACKAGING FOR SINGLE-CHIP IMPLANTS

### Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology by the authority of the Rector Magnificus Prof. Dr. Ir. T.H.J.J. van der Hagen, Chair of the Board for Doctorates to be defended publicly on Monday 27 January at 15:00 o'clock

by

### Kambiz Nanbakhsh

Master of Science in Electrical Engineering - Electronics - System & Circuit

University of Tehran, Iran

Born in Orumieh, Iran.

This dissertation has been approved by the promoters.

### Composition of the doctoral committee:

Rector Magnificus Chairperson

Prof. dr. ir. W.A. Serdijn Delft University of Technology, promoter Dr. V. Giagka Delft University of Technology, promoter

### Independent members:

Prof. dr. G. Malliaras

Prof. dr. ir. M. op de Beeck

Prof. dr. E. Cantatore

University of Cambridge

Gent University

Eindhoven University of Technology

Prof. dr. E. Cantatore Eindhoven University of Technolog

Prof. dr. ir. W. van Driel Delft University of Technology

Dr. M. Mastrangeli Delft University of Technology

*Keywords*: integrated circuit, implantable electronics, polymer encapsulation

Printed by: Ipskamp printing

Front & Back: Beautiful cover art that captures the entire content of this thesis in a

single illustration.

Copyright © 2025 by K. Nanbakhsh

ISBN 978-94-6473-699-1

An electronic version of this dissertation is available at

http://repository.tudelft.nl/.

### **CONTENTS**

| Su | ımm  | ary                                                                              | vii      |

|----|------|----------------------------------------------------------------------------------|----------|

| Sa | men  | vatting                                                                          | ix       |

| 1  | Intr | Poduction Packaging of next-generation implantable electronics                   | 1<br>1   |

|    | 1.2  | Outline of thesis                                                                | 2        |

|    | 1.3  | List of original publications                                                    | 3        |

| 2  | Stat | e-of-the-art packaging solutions for miniaturized implantable electron-          |          |

|    | ics  |                                                                                  | 7        |

|    | 2.1  | Packaging of implantable electronics: how did we get here?                       | 7        |

|    | 2.2  | Next-generation implantable electronics                                          | 11       |

|    | 2.3  | The human body: an inhospitable environment for implantable electron-            | 10       |

|    |      | ics                                                                              | 12       |

|    | 2.4  | Miniaturized packaging solutions for implantable ICs                             | 14       |

|    | 2.5  | Conformal (void-free) packaging                                                  | 14<br>14 |

|    |      | <ul><li>2.5.1 Polymer encapsulation.</li><li>2.5.2 Thin-film coatings.</li></ul> | 15       |

|    | 2.6  | Challenges in conformal packaging of implantable ICs                             | 19       |

|    | 2.0  | 2.6.1 Void and defect-free packaging                                             | 19       |

|    |      | 2.6.2 Adhesion                                                                   | 20       |

|    |      | 2.6.3 Moisture-resistance of underlying electronic components                    | 21       |

|    | 2.7  | Evaluation of coating performance and longevity estimation                       | 21       |

|    |      | 2.7.1 Interdigitated capacitor structures                                        | 22       |

|    |      | 2.7.2 Accelerated testing with electrical biasing                                | 23       |

|    |      | 2.7.3 Material evaluation techniques                                             | 24       |

|    |      | 2.7.4 Longevity estimation                                                       | 26       |

|    | 2.8  | Research objectives of thesis                                                    | 26       |

| 3  | On-  | chip CMOS tools for integrity monitoring                                         | 39       |

|    | 3.1  | A Chip Integrity Monitor for Evaluating Long-term Encapsulation Perfor-          |          |

|    |      | mance                                                                            | 39       |

|    |      | 3.1.1 Introduction                                                               | 39       |

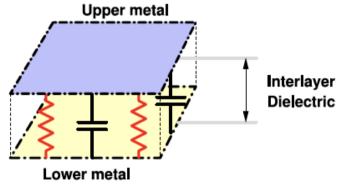

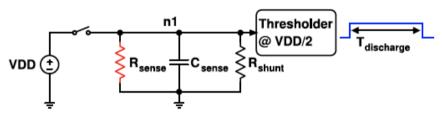

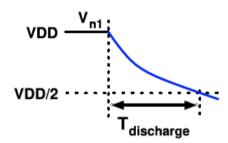

|    |      | 3.1.2 ILD Resistance Measurement                                                 | 41       |

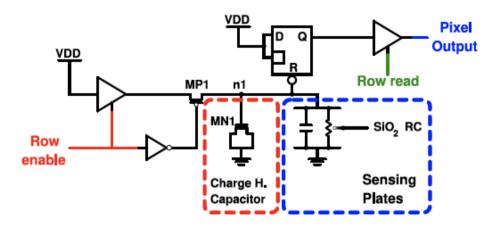

|    |      | 3.1.3 Sensor Pixel Circuit Design.                                               | 44       |

|    |      | 3.1.4 Chip Implementation and Test Setup                                         |          |

|    |      | 3.1.5 Test Setup                                                                 |          |

|    |      | 3.1.6 Measurement results                                                        |          |

|    |      | U.1.1 1/10UUUUUUI                                                                | JJ       |

vi Contents

|    | 3.2        | <b>3.1.8</b> Conclusion                                                            | 58                   |

|----|------------|------------------------------------------------------------------------------------|----------------------|

|    |            | Millimeter Sized Implants3.2.1 Introduction3.2.2 Experimental details3.2.3 Results | 59<br>59<br>60<br>61 |

|    |            | 3.2.4 Discussion                                                                   | 64<br>66             |

| 4  |            | the longevity and hermeticity of silicon-ICs: Evaluation of Bare-Die and           |                      |

|    |            | MS-Coated ICs After Accelerated Aging and Implantation Studies                     | <b>7</b> 3           |

|    |            | Introduction                                                                       | 74                   |

|    | 4.2        | Results                                                                            | 77                   |

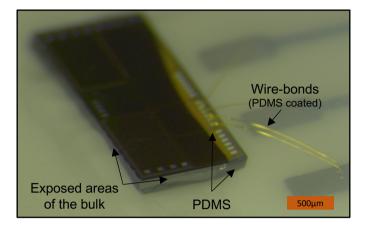

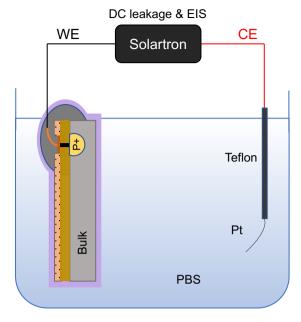

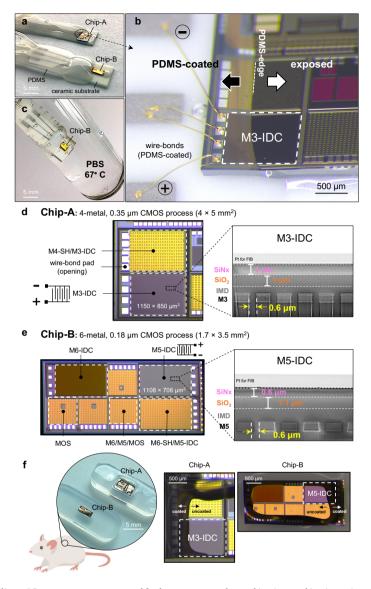

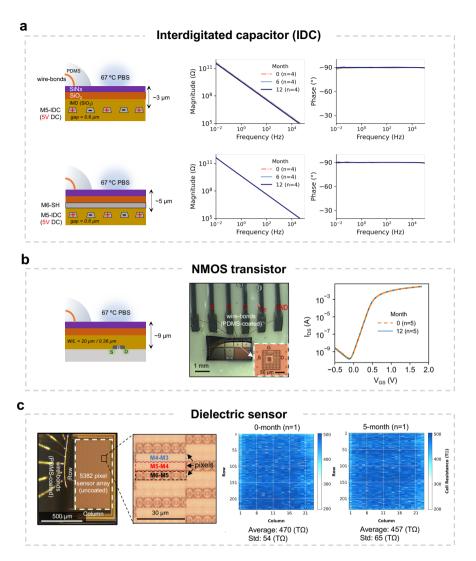

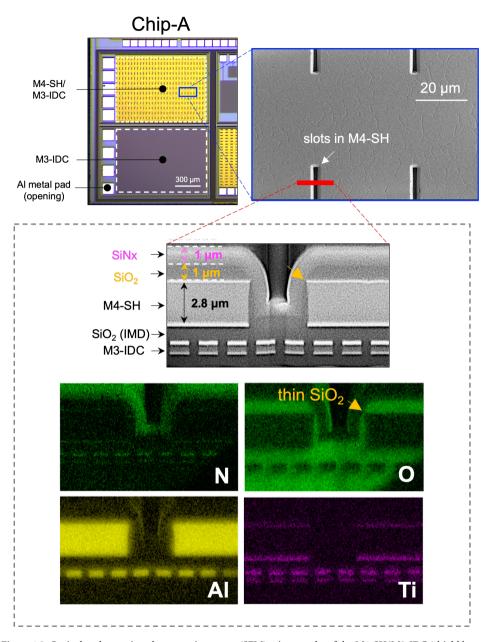

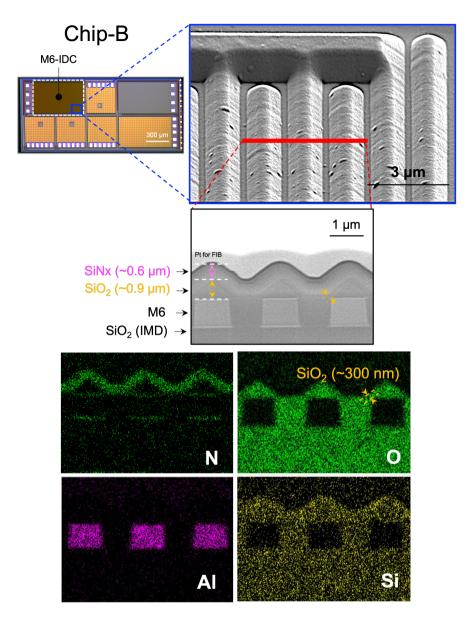

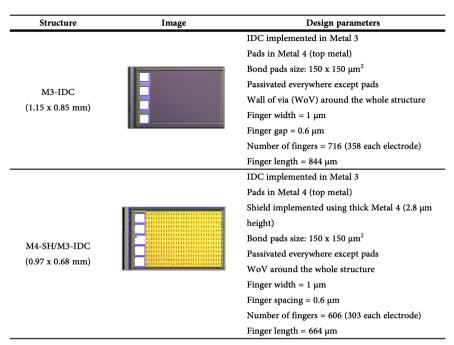

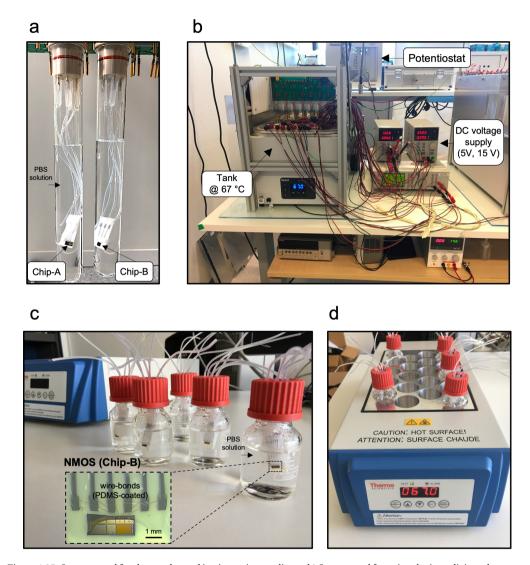

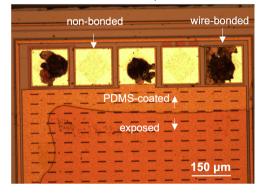

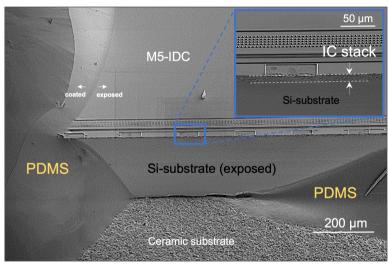

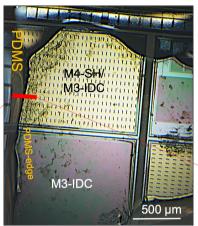

|    |            | 4.2.1 IC design, fabrication, and PDMS coating                                     | 77                   |

|    |            | 4.2.2 Electrical performance in PBS solution at 67 °C                              | 79                   |

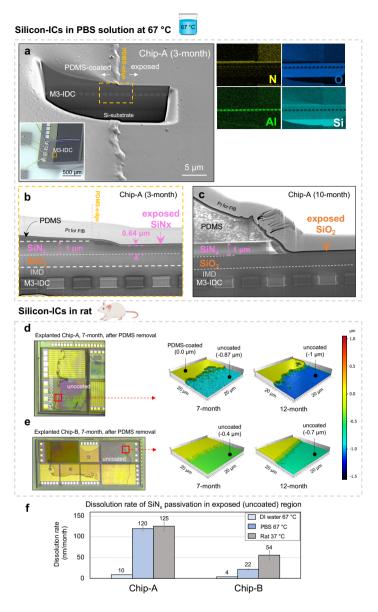

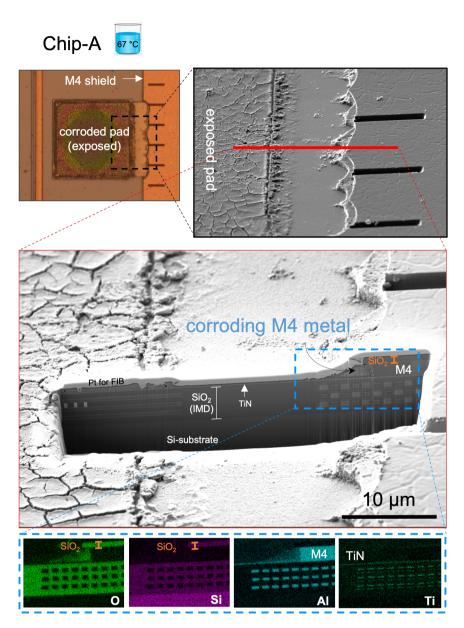

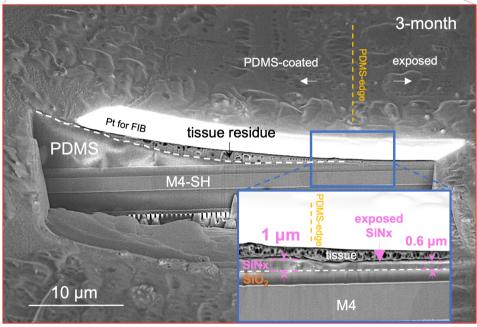

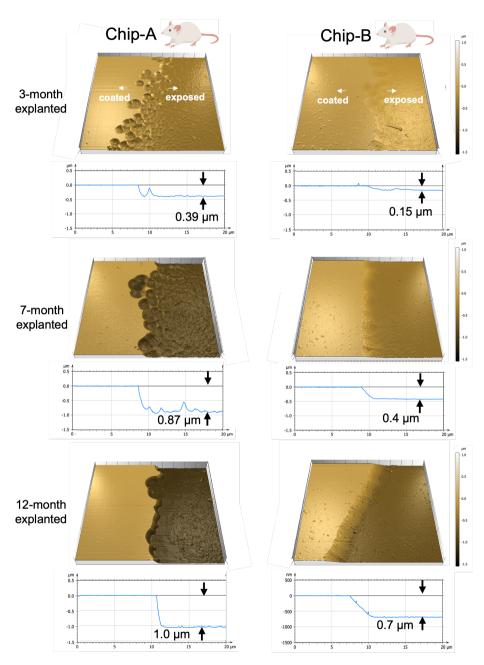

|    | 4.0        | 4.2.3 Material performance: exposed vs. PDMS-coated                                | 81                   |

|    | 4.3        | Discussion and guidelines for longevity                                            | 92                   |

|    | 4.4<br>4.5 | Conclusion                                                                         | 95<br>96             |

|    | 4.5        | Experimental Section                                                               | 99                   |

|    |            |                                                                                    | 99                   |

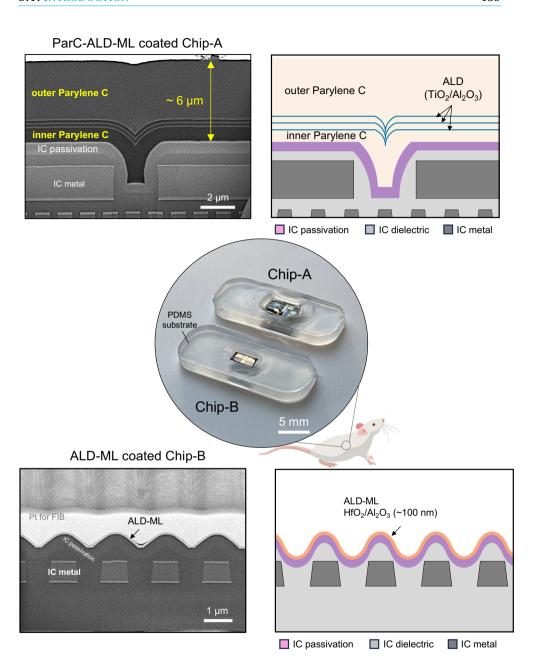

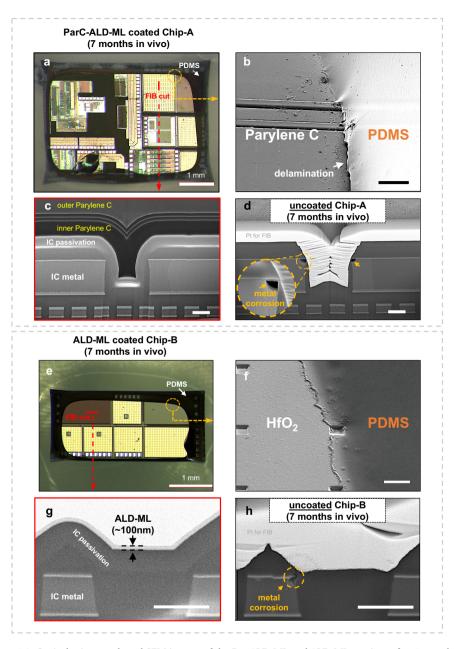

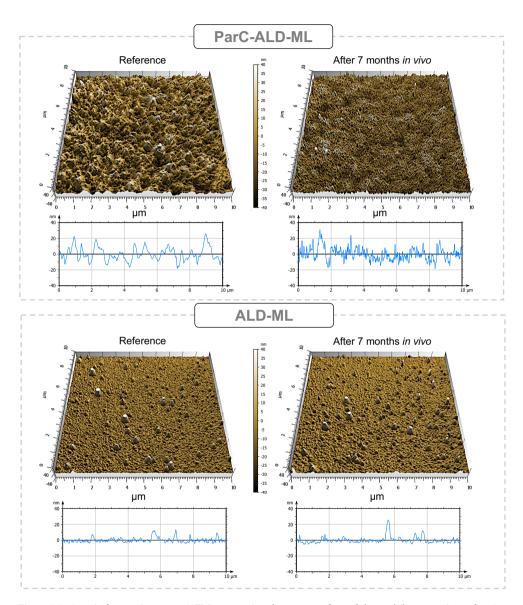

| 5  |            | ivo Biostability of ALD and Parylene-ALD Multilayers as Micro-Packaging            |                      |

|    |            |                                                                                    | 137                  |

|    | 5.1<br>5.2 | Introduction                                                                       |                      |

|    | 5.2        | Results                                                                            |                      |

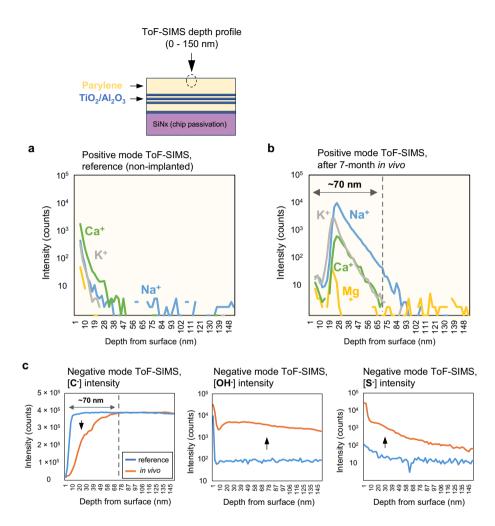

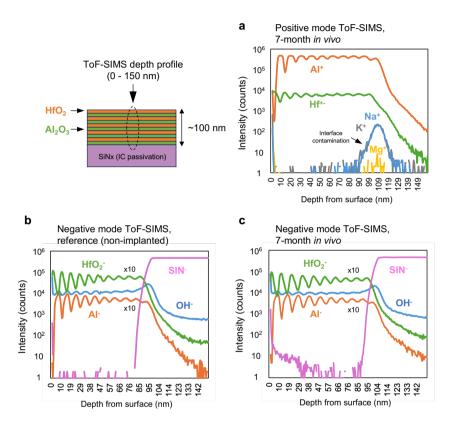

|    |            | 5.2.2 In vivo chemical stability of multilayer coatings                            |                      |

|    | 5.3        | Discussion and Conclusions                                                         |                      |

|    | 5.4        | Experimental Section                                                               |                      |

|    | 5.5        | Supplementary notes                                                                |                      |

| 6  | Con        | nclusion and future work                                                           | 157                  |

|    | 6.1        | Conclusion                                                                         | 157                  |

|    |            | Future work                                                                        |                      |

| Ac | knov       | wledgements                                                                        | 163                  |

### **SUMMARY**

For over five decades, electronic implants have significantly improved the quality of life for millions of patients. With their great potential, substantial advancements have been made in developing new therapeutic devices, particularly in the fields of bioelectronic medicine and brain-machine interfaces. However, these emerging devices require novel approaches to packaging, as traditional hermetic enclosures no longer meet the physical and dimensional demands of modern systems. Polymer packaging offers a promising alternative, enabling device miniaturization and facilitating minimally invasive procedures. Polymer packaging was in fact one of the earliest methods used to protect electronics (implemented with discrete components) in the body. However, due to the inability of polymers to fully block moisture ingress, it soon became evident that the body's wet and corrosive environment could negatively impact device longevity. As electronic implants evolved from using discrete components to complex integrated circuits (ICs), the challenge of protecting these devices became even more critical. In this thesis, I aimed to tackle the challenge of ensuring the safe and reliable operation of polymerpackaged ICs for long-term implantable applications. To address this challenge, I pursued three key objectives: 1) I developed on-chip sensor platforms to carefully monitor the integrity of the IC structure. These tools provide critical data on the condition and performance of the chips, ensuring their expected functionality in clinical settings. 2) I investigated the electrical and material stability of IC structures by directly exposing them as bare die (uncoated) to physiological environments, assessing their durability in the body's corrosive conditions. By identifying potential degradation pathways, I proposed IC design guidelines that can potentially enhance the longevity of polymerpackaged devices. 3) I investigated if silicone rubber, as a polymer packaging material, could prevent or slow down the degradations seen in uncoated ICs. Separately, I also evaluated two thin-film packaging layers for their effectiveness in IC protection. Results demonstrated that IC structures can be inherently hermetic, enabling polymers, such as silicone, to serve as standalone packaging materials despite their moisture permeability. Furthermore, silicone was found to effectively prevent the degradations observed in bare-die ICs. Using advanced material analysis techniques, I derived degradation rates, showing that silicone-encapsulated ICs could last over 10 years in the body. These findings enable the development of long-lasting miniature implants, reducing the need for repeated surgeries and improving patients' quality of life.

### SAMENVATTING

Al meer dan vijf decennia hebben elektronische implantaten de levenskwaliteit van miljoenen patiënten aanzienlijk verbeterd. Met hun enorme potentieel zijn er substantiële vooruitgangen geboekt in de ontwikkeling van nieuwe therapeutische apparaten, met name op het gebied van bio-elektronische geneeskunde en brain-machine interfaces. Echter, deze opkomende apparaten vereisen nieuwe benaderingen op het gebied van encapsulatie, aangezien traditionele hermetische omhulsels niet langer voldoen aan de fysieke en dimensionele eisen van moderne systemen. Polymeer-encapsulatie biedt een veelbelovend alternatief, dat miniaturisatie van elektronische implantaten mogelijk maakt en minimaal invasieve procedures vergemakkelijkt. Polymeer-encapsulatie was in feite één van de vroegste methoden die werden gebruikt om elektronica (met discrete componenten) in het lichaam te beschermen. Echter, vanwege de vochtpermeabiliteit van polymeren werd duidelijk dat de corrosieve omgeving van het lichaam de levensduur van het implantaat negatief kon beïnvloeden. Naarmate elektronische implantaten evolueerden van het gebruik van discrete componenten naar complexe geïntegreerde schakelingen (IC's), werd de uitdaging om deze apparaten te beschermen nog kritieker. In dit proefschrift bestudeer ik de veilige en betrouwbare werking van IC's in polymeer-encapsulatie voor langdurige implanteerbare toepassingen. Hiervoor stelde ik drie belangrijke doelen: 1) Ik ontwikkelde sensorplatformen op de chip om zorgvuldig de integriteit van de IC-structuur te monitoren. Deze sensoren leveren cruciale gegevens over de toestand en prestaties van de chips, waardoor hun betrouwbaarheid in klinische omgevingen wordt gewaarborgd. 2) Ik onderzocht de elektrische en materiaalstabiliteit van IC-structuren door ze onbedekt (niet ge-encapsuleerd) bloot te stellen aan fysiologische omgevingen, waarbij hun betrouwbaarheid in de corrosieve omstandigheden van het lichaam werd beoordeeld. Door mogelijke degradatiepaden te identificeren, stelde ik richtlijnen voor IC-ontwerp voor die de levensduur van implantaten met polymeerencapsulatie mogelijk kunnen verbeteren. 3) Ik onderzocht of siliconenrubber, een polymeer encapsulatiemateriaal, de degradatie die bij onbedekte IC's wordt waargenomen, kan voorkomen of vertragen. Daarnaast evalueerde ik ook twee dunne-film encapsulatielagen op hun effectiviteit bij de bescherming van IC's. De resultaten toonden aan dat IC-structuren van nature hermetisch kunnen zijn, waardoor polymeren, zoals siliconen, ondanks hun vochtpermeabiliteit als op zichzelf staande verpakkingsmaterialen kunnen dienen. Bovendien bleek dat siliconen degradaties, die bij bare-die IC's worden waargenomen, effectief kunnen voorkomen. Door gebruik te maken van geavanceerde materiaalanalysetechnieken, heb ik degradatiesnelheden afgeleid waaruit blijkt dat IC's met een silicone-encapsulatie mogelijk meer dan 10 jaar in het lichaam kunnen meegaan.

1

### INTRODUCTION

## 1.1. PACKAGING OF NEXT-GENERATION IMPLANTABLE ELECTRONICS

For more than 50 years, electronic implants have provided substantial therapeutic benefits, greatly enhancing the quality of life for millions of patients. In the last two decades, there has been a surge of research in two pioneering fields: bioelectronic medicine and brain-machine interfaces (BMI). Bioelectronic medicine offers a neuromodulation alternative to traditional pharmaceuticals by using tiny electrical pulses to stimulate neurons. [1, 2]. Deep brain stimulation (DBS) is perhaps one of the most successful applications of bioelectronic medicine [3]. Approved by the Food and Drug Association (FDA) in 2002, DBS has improved the lives of hundreds of thousands of patients suffering from Parkinson's disease and essential tremor. Besides DBS, there are numerous other potential applications of bioelectronic medicine. For example, occipital nerve stimulation (OSP) is currently being investigated as a potential neuromodulation solution for millions of patients suffering from drug-refractory migraine [4].

Brain-machine interfaces represent another emerging medical field with potentially transformative applications, bridging the gap between neural activity and external devices [2]. By recording and interpreting neural signals, these electronic implants can restore motor function in individuals with severe paralysis, enabling them to control prosthetic limbs and exoskeletons [5, 6]. This technology holds the promise of returning lost mobility, significantly improving the quality of life for patients suffering from spinal cord injuries or pharmaceutically untreatable neurodegenerative diseases [7].

Interacting with the body's nervous system, however, requires dedicated electronics that should be uniquely packaged to ensure biocompatibility, minimize the body's immune responses, and maintain long-term functionality and stability within the biological environment [8].

For electronics, without a doubt, the body is an inhospitable and extremely harsh environment. Therefore, packaging and protecting the electronics within the corrosive body environment has been a key challenge since the first electronic device was implanted for cardiac pacing [9, 10]. Driven by the demands for increased miniaturization and functionality, integrated circuits (IC) are becoming a necessity for these emerging implantable devices [11, 7]. The compact and highly integrated nature of the IC structure, however, demands even more attention against possible moisture and ion ingress [12]. Fortunately, the traditional metal hermetic (gas-tight) enclosures can guarantee such a dry and ion-free environment for >20 years in the body [13].

For future implantable devices, however, traditional hermetic enclosures, fall short of meeting the physical requirements: smaller millimeter-sized and lightweight packages (weighing only a few grams) that allow for minimally invasive procedures, minimizing the tissue response with reduced risk of device migration [14, 15, 5]. Polymer packaging is another solution with many favorable physical attributes such as flexibility, reduced weight, and the potential to miniaturize the device to sub-millimeter scales. The primary challenge, however, is to prevent performance loss or malfunction due to moisture or ion ingress over the functional lifetime of the implant [16].

This thesis tackles the challenge of ensuring the safe and reliable operation of polymer-packaged IC structures for long-term implantable applications. To achieve this, the electrical and material stability of bare-die (uncoated) ICs are evaluated after prolonged exposure to physiological environments, studying their performance over time to assess their durability within the body's corrosive environment. By identifying the potential degradation pathways of these bare structures, IC design guidelines are proposed along with sub-millimeter packaging solutions that can enhance the longevity of polymer-packaged ICs in the body.

Furthermore, this thesis proposes the development of new on-chip monitoring tools for assessing the long-term integrity of implantable ICs. These tools will provide real-time data on the chip's condition and performance, ensuring its reliability in implantable applications.

Successfully achieving these objectives will pave the way for engineering long-lasting low-profile devices, reducing the need for multiple invasive surgeries and significantly improving patients' quality of life.

### **1.2.** OUTLINE OF THESIS

The thesis is structured as follows:

**Chapter 1: Introduction**. This chapter provided a preface to the packaging requirements of next-generation neural implants and gave the motivation for this thesis.

Chapter 2: State-of-the-art miniaturized packaging for implantable ICs. In this chapter, an overview of the latest advancements in miniaturizing the packaging for implantable ICs is provided. Two types of packaging solutions are discussed: void-free polymer packaging (e.g. silicone encapsulation) and thin-film conformal micro-packaging using polymers or ceramics (e.g. atomic layer deposition(ALD) coatings). A detailed review of recent scientific literature on both solutions is given, along with an analysis of their associated challenges. Based on the gaps identified in the literature, the research objectives of this thesis are defined and outlined.

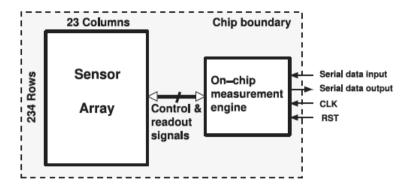

**Chapter 3: On-chip CMOS tools for integrity monitoring.** Silicon-ICs will be an integral component for miniaturized implantable devices. The lack of a hermeticity test for polymer or thin-film packaged ICs demands new solutions to evaluate their integrity,

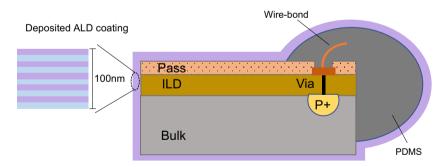

both before and during implantation. In this chapter, two novel on-chip monitors are proposed to evaluate the integrity of the chip structure or the applied thin coating. The first part of the chapter will be dedicated to the design and implementation of an on-chip moisture/ion integrity monitor for early detection of impurity ingress. The second part of the chapter introduces the concept of using the IC's silicon bulk to evaluate the integrity of the coatings that are applied for thin-film packaging.

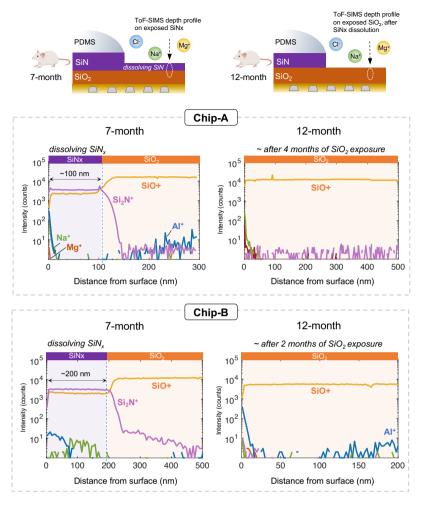

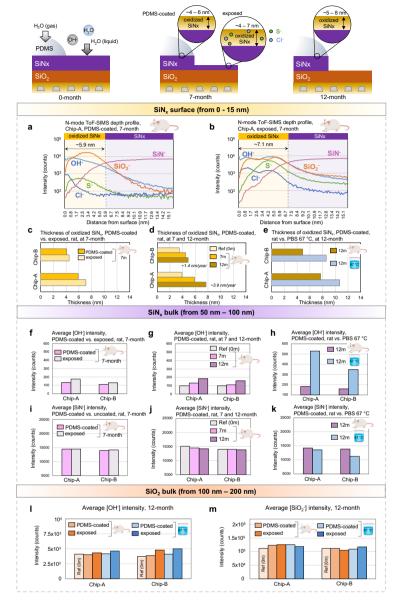

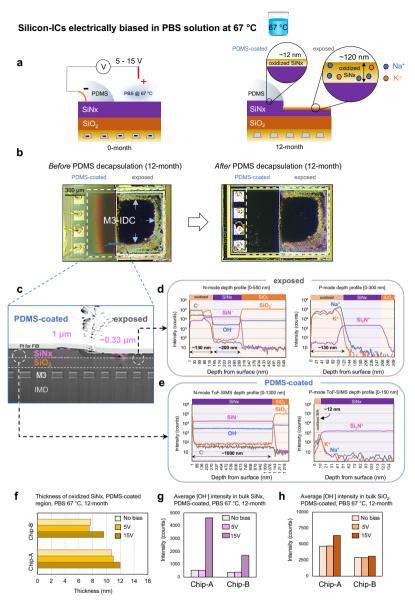

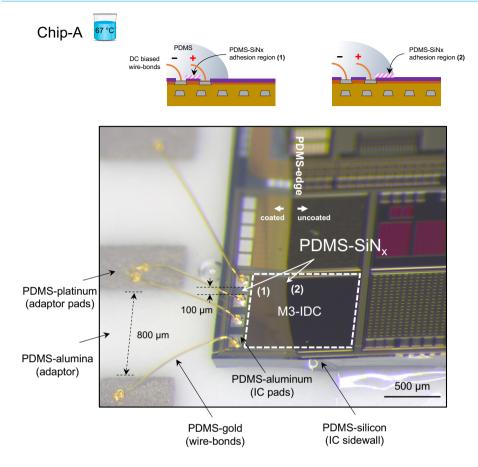

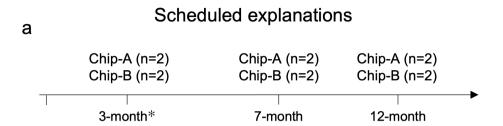

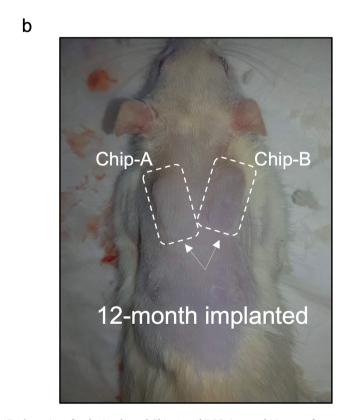

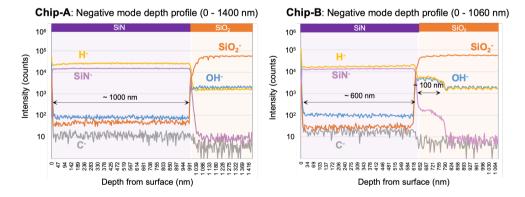

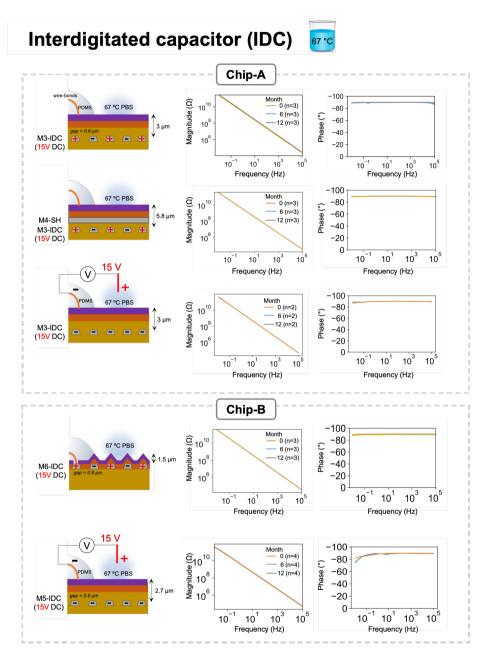

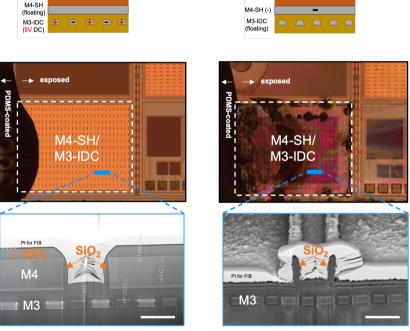

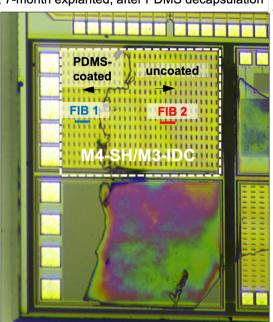

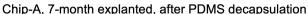

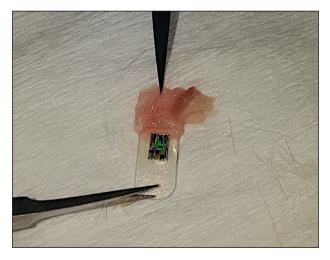

Chapter 4: On the hermeticity and longevity of Silicon-ICs, bare-die and PDMS-coated. In this chapter, the hermeticity of IC structures is investigated by directly exposing them as bare die to accelerated in vitro and in vivo aging conditions over a 12-month period. Various factors, including the effects of different metallization layers and electric fields on IC longevity, are explored. Next, by identifying the potential degradation pathways of bare ICs, it is examined if polydimethylsiloxane (PDMS), used as a soft polymer package, could prevent or delay the identified degradation pathways and thus extend the longevity of the IC. Advanced material analysis techniques were employed to quantify the rates of observed degradations, which will help estimate the longevity of both bare-die and PDMS-coated ICs.

Chapter 5: In vivo biostability of ALD and Parylene-ALD multilayers as thin-film micro-packaging solutions for implantable ICs. Thin-film coating is an attractive solution for IC micro-packaging. The long-term in vivo stability and performance of these films, however, has always been a concern. In this chapter, the long-term biostability of two thin-film coatings over a 7-month in vivo animal study is investigated: a hafnia-based ALD multilayer, and an ALD/parylene-C hybrid multilayer.

**Chapter 6: Conclusion and future work.** In this chapter, the main contents are summarized, highlighting the key original contributions of the thesis. Finally, the remaining challenges and future directions are discussed that, if solved, could help further increase the reliability of polymer-packaged single-chip implants.

### **1.3.** LIST OF ORIGINAL PUBLICATIONS

### **JOURNAL ARTICLES**

- **Kambiz Nanbakhsh**, et al. "On the Longevity and Inherent Hermeticity of Silicon-ICs: Evaluation of Bare-Die and PDMS-Coated ICs After Accelerated Aging and Implantation Studies." Nat. Commun. In press.

- Kambiz Nanbakhsh, et al. "An in vivo Biostability Evaluation of ALD and Parylene-ALD Multilayers as Micro-packaging Solutions for Implantable ICs." in revision.

- Omer Can Akgun, Kambiz Nanbakhsh, Vasiliki Giagka, and Wouter A. Serdijn. "A chip integrity monitor for evaluating moisture/ion ingress in mm-sized single-chip implants." IEEE Transactions on Biomedical Circuits and Systems 14, no. 4 (2020): 658-670.

- Anna Pak, Kambiz Nanbakhsh, Ole Hölck, Riina Ritasalo, Maria Sousa, Matthias Van Gompel, Barbara Pahl, Joshua Wilson, Christine Kallmayer, and Vasiliki Giagka. "Thin film encapsulation for LCP-based flexible bioelectronic implants: comparison of different coating materials using test methodologies for life-time estimation." Micromachines 13, no. 4 (2022): 544.

4 1. Introduction

• Callum Lamont, Timea Grego, **Kambiz Nanbakhsh**, A. Shah Idil, Vasiliki Giagka, Anne Vanhoestenberghe, Stuart Cogan, and Nick Donaldson. "Silicone encapsulation of thin-film  $SiO_X$ ,  $SiO_XN_Y$  and SiC for modern electronic medical implants: a comparative long-term ageing study." Journal of Neural Engineering 18, no. 5 (2021): 055003.

#### **CONFERENCE CONTRIBUTIONS**

- Kambiz Nanbakhsh, Marta Kluba, Barbara Pahl, Florian Bourgeois, Ronald Dekker, Wouter Serdijn, and Vasiliki Giagka. "Effect of signals on the encapsulation performance of parylene coated platinum tracks for active medical implants." In 2019 41st Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBC), pp. 3840-3844. IEEE, 2019.

- **Kambiz Nanbakhsh**, Riina Ritasalo, Wouter A. Serdijn, and Vasiliki Giagka. "Longterm encapsulation of platinum metallization using a HfO<sub>2</sub> ALD-PDMS bilayer for non-hermetic active implants." In 2020 IEEE 70th Electronic Components and Technology Conference (ECTC), pp. 467-472. IEEE, 2020.

- Rodrigues G, Neca M, Silva J, Brito D, Rabuske T, Fernandes J, Mohrlok R, Jeschke C, Meents J, Nanbakhsh K, Giagka V. Towards a wireless system that can monitor the encapsulation of mm-sized active implants in vivo for bioelectronic medicine. In 2021 10th International IEEE/EMBS Conference on Neural Engineering (NER) 2021 May 4 (pp. 981-984). IEEE.

- Kambiz Nanbakhsh, Riina Ritasalo, Wouter A. Serdijn, and Vasiliki Giagka. "Towards CMOS Bulk Sensing for In-Situ Evaluation of ALD Coatings for Millimeter Sized Implants." In 2020 42nd Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBC), pp. 3436-3439. IEEE, 2020.

- Omer Can Akgun, Kambiz Nanbakhsh, Vasiliki Giagka, and Wouter A. Serdijn. "A

chip integrity monitor for evaluating long-term encapsulation performance within

active flexible implants." In 2019 IEEE Biomedical Circuits and Systems Conference (BioCAS), pp. 1-4. IEEE, 2019.

1

### **BIBLIOGRAPHY**

- [1] Karen Birmingham et al. *Bioelectronic medicines: A research roadmap.* 2014. DOI: 10.1038/nrd4351.

- [2] Claude Clément. "The Human Body: A Special Environment". In: *Brain-Computer Interface Technologies*. 2019. DOI: 10.1007/978-3-030-27852-6{\\_}4.

- [3] Laurie Pycroft, John Stein, and Tipu Aziz. "Deep brain stimulation: An overview of history, methods, and future developments". In: *Brain and Neuroscience Advances* 2 (2018). ISSN: 2398-2128. DOI: 10.1177/2398212818816017.

- [4] T. J. Schwedt et al. "Occipital nerve stimulation for chronic headache Long-term safety and efficacy". In: *Cephalalgia* 27.2 (2007). ISSN: 03331024. DOI: 10.1111/j.1468-2982.2007.01272.x.

- [5] Adrien B. Rapeaux and Timothy G. Constandinou. *Implantable brain machine interfaces: first-in-human studies, technology challenges and trends.* 2021. DOI: 10.1016/j.copbio.2021.10.001.

- [6] Elon Musk. "An integrated brain-machine interface platform with thousands of channels". In: *Journal of Medical Internet Research* 21.10 (2019). ISSN: 14388871. DOI: 10.2196/16194.

- [7] Claude Clément. "The Human Body: A Special Environment". In: *Brain-Computer Interface Technologies*. 2019. DOI: 10.1007/978-3-030-27852-6{\\_}4.

- [8] Kenneth W. Horch. *Neuroprosthetics: Theory and practice: Second edition.* 2017. DOI: 10.1142/10368.

- [9] Moo Sung Chae, Zhi Yang, and Wentai Liu. Implantable Neural Prostheses 2. 2010.

- [10] W. F. DeForge. "Cardiac pacemakers: a basic review of the history and current technology". In: *Journal of Veterinary Cardiology* 22 (2019). ISSN: 18750834. DOI: 10.1016/j.jvc.2019.01.001.

- [11] Yan Liu et al. "Bidirectional Bioelectronic Interfaces: System Design and Circuit Implications". In: *IEEE Solid-State Circuits Magazine* 12.2 (2020). ISSN: 19430590. DOI: 10.1109/MSSC.2020.2987506.

- [12] Marius Bâzu and Titu Băjenescu. Failure Analysis: A Practical Guide for Manufacturers of Electronic Components and Systems. 2011. DOI: 10.1002/9781119990093.

- [13] Haleh Ardebili and Michael G. Pecht. *Encapsulation technologies for electronic applications*. 2018. DOI: 10.1016/C2016-0-01829-6.

- [14] Vasiliki Giagka and Wouter A. Serdijn. *Realizing flexible bioelectronic medicines* for accessing the peripheral nerves technology considerations. Dec. 2018. DOI: 10.1186/s42234-018-0010-y.

6 BIBLIOGRAPHY

1

[15] Nikita Obidin, Farita Tasnim, and Canan Dagdeviren. *The Future of Neuroim- plantable Devices: A Materials Science and Regulatory Perspective*. Apr. 2020. DOI: 10.1002/adma.201901482.

[16] James J. Licari. Coating Materials for Electronic Applications: Polymers, Processing, Reliability, Testing. 2003.

### STATE-OF-THE-ART PACKAGING SOLUTIONS FOR MINIATURIZED IMPLANTABLE ELECTRONICS

Packaging has been a major engineering challenge for implantable electronics intended to function reliably for years within the body. In this chapter, I provide an overview of state-of-the-art packaging solutions for next-generation miniaturized implants and detail the associated challenges. I begin with a brief introduction to the first packaging used for electronic implants and discuss in detail the issue of moisture and fluid ingress, which was a primary failure mechanism in these early packages. Next, I describe hermetic enclosures which are the current industrial standard for addressing the issue of moisture ingress. Then I review the latest advancements in implantable electronics, highlighting cutting-edge miniaturized packaging solutions and summarizing the requirements for future millimeter-sized devices. Finally, by examining existing literature, I identify the necessary key gaps for achieving long-term reliability in miniaturized packages. Based on these identified gaps, I conclude the chapter with a definition of the research objectives of the thesis.

## **2.1.** PACKAGING OF IMPLANTABLE ELECTRONICS: HOW DID WE GET HERE?

Since the first pacemaker in 1958, implantable electronics (also known as "active medical implantable devices") have been successfully used to improve the quality of life for millions of patients [1]. Examples of these devices include cardiac pacemakers [2] (for controlling heart rhythm), spinal cord stimulators [3] (for chronic pain management), deep brain stimulators (for controlling symptoms of conditions, such as Parkinson's disease [4], essential tremor, epilepsy, and depression), cochlear implants (for hearing loss) and, more recently, occipital (ONS) and supraorbital nerve stimulation (SONS) (for pain

alleviation for drug-refractory headache disorders) [5]. Similar to any device incorporating electronics, dedicated packaging is required to guarantee the reliable operation of these implantable devices over their intended lifespan. The in vivo environment, however, dictates very stringent requirements for the choice of materials and fabrication methods. Specifically for the packaging, besides protecting the electronics from the body, it should also protect the biological environment from any exposure to toxic or non-biocompatible materials that are part of the active implant, such as metals (copper traces, aluminum, nickel) [3], [6].

Some of the first implanted electronic devices were not hermetically sealed; meaning that within the device's lifespan, the underlying electronics could be exposed and saturated with moisture [7]. These early devices were used for cardiac pacing and employed polymer encapsulation (epoxy) to package the electronics [2]. The first implantable pacemaker developed by Elmqvist consisted of two transistors and was over-molded in an empty shoe polish tin (see first image in Fig.2.1) [8]. As polymers have a higher permeability to gases (including moisture), all the electronics and interfaces could be saturated with moisture [9, 10]. At the time of the manufacturing of these devices, the electronics were based on discreet components: transistors, resistors, and capacitors, all assembled at a reasonable distance (a few millimeters) from each other. Reports on the failures of these early devices showed signs of cracking or delamination of the epoxy from wires and components, allowing the penetrated or diffused moisture to create corrosion and shunt leakage paths [8]. These failures were the first signs that the body's wet corrosive environment requires dedicated packaging that can guarantee a dry environment for the electronics in the body.

By increasing the functionality of implants, the electronics became more advanced, requiring integrated circuits (ICs) in addition to discrete components for their functionality [6, 11]. For such devices, it was believed that simple polymer encapsulation was not sufficient to provide the long-term reliability expected from a medical implant [8].

When it comes to long-term reliable electronic packaging, the aerospace and automotive industries tend to be the 'trendsetter'. Adopted from the high-reliability aerospace industry, hermetic enclosures were introduced into the active implantable industry [6]. Hermeticity was achieved using a metal or ceramic enclosure to house the electronics. The most common material currently used for making hermetic enclosures for implantable applications is titanium (Fig.2.1) [12]. This is largely due to 1) excellent corrosion resistivity, 2) biocompatibility, and 3) the reliable laser seam welding which has proven to be a reliable process for long-term applications [6]. In addition to the laser weld, hermetic feed-throughs are critical components to guarantee the hermeticity of the enclosure [13]. Without hermetic feedthroughs, the enclosure cannot be considered hermetic even if the enclosure material is made of metal, ceramic, or glass [14].

Hermetic housings have remained the industry standard for packaging life-critical battery-powered active implantable medical devices (AIMD). Since the appearance of the first hermetically sealed pacemaker, this packaging has enabled long lifespans (>20 years) [6]. It results, however, in a costly and bulky device which due to its size usually needs to be placed in a location far from the therapy delivery site, necessitating complicated invasive interventions for implantation [17].

An important advantage of hermetic enclosures is their testability based on the he-

Figure 2.1: Evolution of packaging for implantable electronics [11, 15, 16]

lium (He) fine leak test [6]. This test models water molecule ingress and is used to verify the hermeticity of the seal for each device before its use. It is noteworthy to mention that the helium leak test does not guarantee the long-term hermeticity of the enclosure [18]. This is done by selecting appropriate materials for the packaging (metal or ceramic) and carefully designed feedthroughs. By reducing the size of implantable medical devices, the amount of water necessary to increase the humidity to corrosive levels in the interfacial environment becomes exceedingly small [19]. Also, it takes a shorter time for moisture or ions to go through a narrower sealing wall or an interfacial pathway. For this reason, higher-quality bulk materials and void-free interfacial sealing are essential to achieve the same degree of hermiticity for smaller hermetic packages than bigger ones [20].

Despite the observed failures for epoxy-encapsulated cardiac pacemakers, one of the successful applications of polymer encapsulation is the Finetech-Brindley sacral anterior root stimulator (Fig.2.2) [21, 22]. This device used silicone rubber to package the electronics. The wirelessly powered device consisted of a receiver circuitry and a stimulator that was implemented using discrete components. In a follow-up study on the Finetech-Brindley stimulator, a mean time to failure of 19.6 years was reported for the device [23].

Based on the reported longevity, it can be understood that for this device the penetrated moisture through the silicone encapsulation was not so critical. This suggests that the selected components and interfaces were inherently moisture-resistant with longlasting adhesion to the polymer, preventing any corrosion or shunt leakage paths [25]. These encouraging results show that polymeric encapsulation can be a viable solution for protecting implanted electronics for decades on the caveat that all the components underneath are carefully selected. The circuits used for the Finetech-Brindley are quite simple compared to modern ICs. Silicon-ICs incorporate thin-film ceramics and metals which may exhibit chemical degradation upon moisture exposure [26, 27]. A reduction in feature sizes compared to discrete-level electronics also results in higher electric fields

- Packaging: silicone elastomer

- Power source: battery-free/wirelessly powered

- Number of channels: 3

- Reported longevity: ≈ 20 years

- Electronics: discrete transistors and passive components

- Estimated usage/day: a few hours

Figure 2.2: Image of the Finetech-Brindley three-channel neurostimulator (courtesy of Callum Lamont [24])

which may impact the material stability when saturated with moisture [22].

Despite the longevity of silicone-packaged Finetech-Brindley stimulators, hermetic enclosures remain the golden standard for packaging electronic implants, especially for life-sustaining devices such as defibrillators and pacemakers. Driven by miniaturization, great engineering work has been targeted to shrink the size and weight of these devices while maintaining their high reliability. The latest example is the Micra  $^{TM}$  pacemaker (from Medtronic) which is only 2.0 g in weight and 0.8 cm $^3$  in volume (92% smaller than conventional pacemakers which weigh 20-50 g) (Fig.2.1).

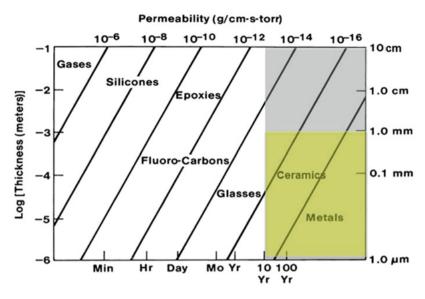

As shown in Fig.2.3, most materials, if given enough time, will eventually allow moisture ingress [10]. Therefore, in addition to the permeability rate of the material and its thickness, the timescale is also a contributing factor in defining a package hermetic (gas tights). For better clarification, two examples are provided although being unrealistic. Example 1: if an implant were to have a lifetime of 1 second, a sub-mm thick silicone package would ensure that the relative humidity within the package would remain unchanged. In other words, a silicone package could be considered hermetic 'enough' for 1 second. Example 2: if an implant were to last >500 years, the currently used titanium enclosure with the thickness employed may not ensure a hermetic environment for such long timescales. Nevertheless, the current norm in defining a package hermetic is by assuming that the implant will have a lifetime of > 20 years [28]. For such lifetimes, and with the thickness and dimensions that are viable for an implant, only metals, ceramics and glass can guarantee a hermetic environment [29, 10].

Recently, cavity packages made from polymers such as liquid crystal polymer (LCP) or Polytetrafluoroethylene (PTFE) are known in the industry as "near-hermetic" or "substantially hermetic" [30, 31]. Despite being more resistant to moisture ingress compared to other polymers like polyurethane, epoxy, or silicone, they cannot guarantee a hermetic enclosure for decades-long lifespans [32].

The success of the Finetech neurostimulator demonstrated that silicone encapsulation could be a viable solution for devices requiring >10 years of lifetime. Compared to the three-channel Finetech stimulator, however, future implantable devices require

Figure 2.3: Material-dependent moisture permeability over time. The graph also provides information regarding permeability as a function of material thickness. [33]

ICs to satisfy their complex functionalities, small footprint, and tight power budget [34, 35]. One key question arises: can silicone-encapsulated ICs also reach  $\approx 5-10$  years of functional lifetime in the body?

### 2.2. NEXT-GENERATION IMPLANTABLE ELECTRONICS

In recent years, a new generation of non-life-sustaining implantable devices has emerged as exploratory tools for interacting with the nervous system. The two main applications currently in focus are 1) brain-machine interfaces (BMI), and 2) bioelectronics medicine. For BMI, the implanted electronics are intended to record neural signals from the human brain (or central nervous system) to control a computer or a prosthetic limb [36]. Bioelectronic medicine is another emerging application with the ultimate goal of replacing chemical drugs with neuromodulation [37]. Perhaps the best example of bioelectronic medicine that is currently in clinical practice is the deep brain stimulation (DBS) device. The DBS system has been in use for >10 years and has helped over 200 thousand patients suffering from life-debilitating diseases such as Parkinson's and essential tremors [38]. This example has demonstrated how neuromodulation can help assist patients where conventional chemical drugs fall short. In the last years, new applications of bioelectronic medicine have been investigated. Rheumatoid arthritis (RA), migraine, and chronic cluster headache are a few conditions that are currently being investigated for bioelectronic medicine [5, 35].

As explained in the previous section, hermetic enclosures are the golden standard, and will most likely remain to be, for packaging battery-powered life-sustaining devices. However, for the newly explored conditions which are non-life-sustaining, battery-free

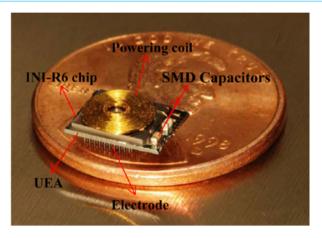

Figure 2.4: A battery-free wireless device with an IC connected to the Utah electrode array [40].

devices with wireless power delivery could be a viable powering solution. Moving away from the battery can help in the miniaturization process of the device but also open new possibilities for alternative packaging solutions, such as polymer packaging, that can further help in shrinking the overall size of the device. As a result of the miniaturization, such devices could be positioned in a minimally invasiveness manner, reducing the risks of surgery [35]. Given the non-life-sustaining application and minimal invasiveness, one could even argue that such implants may require shorter functional lifetimes ( $\approx 5-10$  years), further justifying an alternative packaging solution such as polymer packaging.

The next generation of implantable devices is expected to have more channel counts and embed more functionally compared to the simple 3-channel Finetech-Brindley stimulator. These devices will rely on ICs for their functionality. As an example, Fig.2.4 depicts a wireless device implemented using the Utah electrode array having 100 electrodes. The discrete components on the devices (capacitor and coil) together with the INI-R6 IC were packaged using a thin-film coating that resulted in a millimeter-sized implant [39].

## **2.3.** THE HUMAN BODY: AN INHOSPITABLE ENVIRONMENT FOR IMPLANTABLE ELECTRONICS

The human body is an inhospitable environment for foreign materials. Electronic implants, designed to restore or enhance physiological functions, face relentless challenges from the body's biochemical and mechanical forces. Far from being a passive host, the body actively interacts with implant materials, often leading to their degradation over time. Studies of explanted devices have consistently demonstrated the detrimental effects of this environment on both metals [12] (e.g., titanium and stainless steel) and polymers [41, 42] (e.g., polyurethane and Parylene C). This degradation not only compromises device performance but can also alter the surrounding biological milieu, potentially undermining the biocompatibility of the device [43, 44]. The implantation

site plays a crucial role in determining the types and severity of stress factors that an implantable device experiences. These stress factors are broadly categorized into two groups:

**Chemical Stress**: Chemical stress in the body primarily comprises of the body's inherent properties and defense mechanisms. Moisture and body fluids are omnipresent in the biological environment, exposing electronic devices to a constant risk of corrosion and ionic infiltration. Additionally, inflammatory responses and foreign body reactions can exacerbate chemical stress by creating oxidative environments and enzymatic attacks [45]. The severity of this chemical stress depends on several factors, including the materials used in the device, its size and shape, and the degree of tissue trauma induced during implantation [46]. For example, larger or more rigid devices may cause greater tissue damage, amplifying inflammatory responses and increasing the exposure of the device to aggressive biochemical agents [47].

**Mechanical Stress**: The exerted mechanical stresses on implanted devices can be grouped into two categories: stress applied to the device during implantation and handling, and stress experienced during its lifetime use in the body. For the latter case, the extent of stress depends heavily on the size, shape, and flexibility of the device, as well as its implantation site. Implantation in more dynamic regions, such as near muscles, joints, or the cardiovascular system, would likely subject the devices to significantly greater mechanical forces, including compression, stretching, bending, or shear. Such forces can compromise the mechanical integrity of the device's encapsulation, potentially leading to microcracks, delamination, or structural failure [46, 48]. Mechanical stress also varies over time. For instance, scar tissue formation during the healing process can exert compressive forces on the device, while ongoing physiological movements subject it to cyclic loading [47]. In more extreme cases, mechanical stress could disrupt the electrode connections or fracture the encapsulation materials, allowing body fluids to infiltrate and compromise the device's functionality.

Combined Effects of Chemical and Mechanical Stress: The interplay between chemical and mechanical stressors further complicates the challenge of designing reliable packaging for implantable electronics [49]. Mechanical damage, such as cracks or delamination, can create entry points for body fluids, intensifying the chemical attack on the underlying materials. Similarly, chemical degradation of encapsulation materials can weaken their mechanical properties, making them more susceptible to stress-induced failure. These aspects highlight the need for a holistic approach to encapsulation design. Miniaturizing the implant can significantly reduce both chemical and mechanical stress by decreasing the surface area exposed to tissue and minimizing the mechanical forces exerted on the device [46, 43]. Implants targeting different locations in the human body, or designed for specific applications, whether battery-powered, life-sustaining, or non-life-sustaining, require specifically designed packaging solutions. The final packaging must be engineered to account for these factors, ensuring optimal performance and reliability while targeting the intended application and environment.

## **2.4.** MINIATURIZED PACKAGING SOLUTIONS FOR IMPLANTABLE ICS

IC packaging is necessary to protect both the microelectronics within the die and the external interconnects from any environmental factors that could jeopardize their intended reliability. The IC packaging industry has undoubtedly been driven by the requirements in the automotive industry [50]. The high-reliability requirements in the automotive industry have pushed the packaging industry to increase the functional reliability of the chips while being subjected to harsh environments. In the automotive industry, harsh environments can be described as temperature fluctuations, vibration, and to a lesser degree, moisture ingress [51]. As temperature fluctuations are the primary reliability concern for ICs, packages have been engineered and optimized to withstand the stresses induced during these fluctuations experienced under the hood of the car. This has been done by minimizing the coefficients of thermal expansion (CTE) between the IC and the peripheral materials touching the die (polymer package, underfill, and printed circuit board) [51, 50]. For moisture stability, the automotive industry has also rigorous conditions. The current standardized tests for testing moisture robustness are various accelerated tests such as the 85 °C/85% relative humidity (RH) or the highly accelerated stress testing (HAST) [52]. These tests expose the packaged IC to for example 85 °C/85% RH or 120 °C/100% RH for HAST for 1000 and 90 hours, respectively. This test has been sufficient to ensure the moisture robustness of the chip throughout the used lifetimes in automobiles. In comparison to the auto field, for medical implants, temperature is not a concern given the body's constant temperature at 37 °C. Moisture ingress, on the other hand, is a concern as the implant will be exposed to corrosive liquids throughout its intended use in the body [29]. In addition to ionic ingress, the packaging must maintain its biocompatibility and biostability throughout its intended functional lifetime. This requirement severely narrows down the choice of materials and processes that could be used for packaging ICs for implantable applications [53].

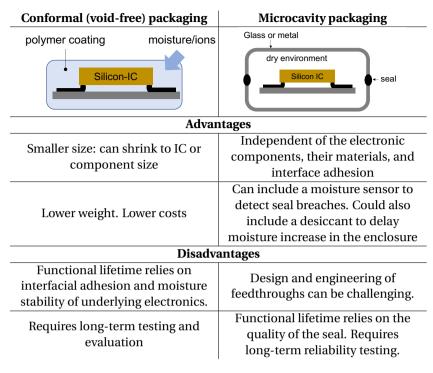

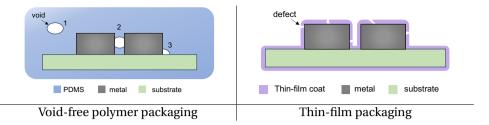

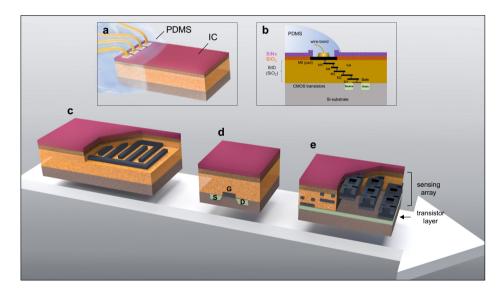

Adopted from the automotive field, two methods are currently investigated for miniaturizing the packaging of implantable ICs: conformal (void-free) packaging and microcavity packaging ((Fig.2.5)). This thesis will focus on conformal packaging with the following sections providing an overview of the latest developments and associated challenges with this packaging solution. For micro-cavity packaging, the reader is referred to [54, 51].

### 2.5. CONFORMAL (VOID-FREE) PACKAGING

### **2.5.1.** POLYMER ENCAPSULATION

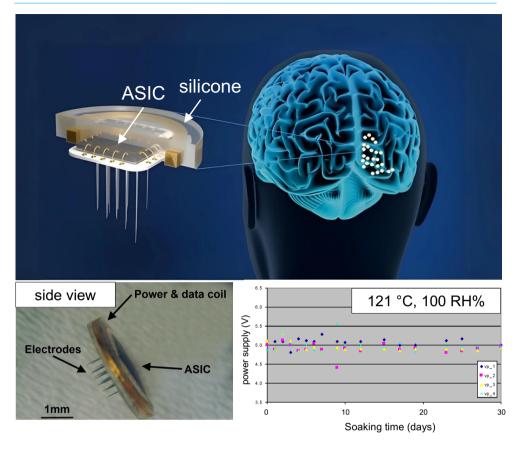

As explained in the previous section, polymer packaging can be considered as an easy and low-cost method for conformal packaging of ICs. In this case, the die and the metal interconnects (wire-bonds or ball grid arrays) are all covered with a sub-mm thick polymer layer. In [55], a neurostimulator/recorder IC was encapsulated with silicone rubber (Dow 96-083 PDMS) (Fig.2.6). To test the reliability of their silicone packaging, a highly accelerated pressure cooker test was used exposing the packaged ICs to 121 °C and 100% RH for 120 hours. During the test, the ICs were electrically biased. During the stress testing, to monitor the functionality of the ICs reverse telemetry was used to record the

Figure 2.5: A comparison of conformal (void-free) vs. microcavity packaging.

internal IC power supply. Stress test results showed stability over the 30 days of testing for four (n=4) of their devices. These results, strengthen the potential of silicone encapsulation as an IC packaging solution for long-term applications.

Besides epoxy and silicone, polyimide is also used extensively in the chip packaging industry [51].

For medical applications, among the several types of polyimide, the BPDA/PPD type is the most commonly used [56]. This type, however, has not been reported to be long-term biocompatible [57]. Encapsulation using polyimide is based on spin coating on the substrate followed by curing at  $\approx 400$  °C [20]. Due to its excellent thermal and chemical stability, polyimide is compatible with most of the processes used in microelectromechanical systems. Similar to silicone, however, the moisture permeability of polyimide is a concern when implanting for long-term applications and considerations should be taken regarding the moisture-resistivity of the underlying interfaces and materials.

### 2.5.2. THIN-FILM COATINGS

In the last years, various thin-film coatings materials have been engineered and incorporated in the packaging for implantable ICs [59, 60]. These films have been engineered with one main goal in mind: to increase the moisture barrier properties of the packaging material and delay moisture/ion ingress. Thin-film coatings can be divided into two groups: organic and inorganic (ceramic).

Figure 2.6: A silicone rubber (PDMS) encapsulated neurostimulator/recorder IC [58]. The left bottom image shows the functionality of the device over a 30-day stress test.

**Organic thin-films:** Parylene-C has been commonly investigated in the implantable medical field due to its demonstrated biocompatibility and protective properties [31]. It is perhaps the most commonly used polymer in the academic field mainly due to its ease of processing but perhaps also due to the wrong notion of its hermeticity. Parylene-C might have lower water vapor transmission rates (WVTR) compared to other polymers, but for the lifetimes intended for medical implants (> 12 months), a 1-5  $\mu$ m Parylene layer is still permeable to moisture [61, 62]. Similar to epoxy and silicone encapsulation, conformal polymer packaging can be used to achieve a low form factor chip-scale micropackage for implantable ICs. Parylene-C films are applied using the chemical vapor deposition (CVD) process and can be done at room temperature [63]. The low-temperature deposition process makes it very attractive to coat materials and devices that require a low thermal budget. Due to the molecular level deposition process, a uniform and conformal film can be formed over substrate surfaces having complex micro-topography, including sharp edges and crevices providing a conformal, pinhole-free coating. Moreover,

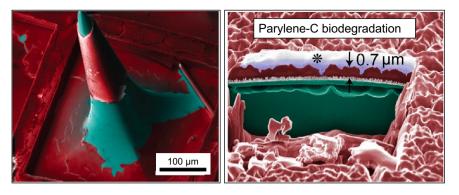

Figure 2.7: Scanning electrode microscope (SEM) images showing biodegradation of Parylene-C after 3.25 years in vivo seen as thinning (3  $\mu$ m original in comparison to 0.7  $\mu$ m after in vivo aging) [66].

its high dielectric strength makes it a suitable insulator in electronic packaging within the body. The typical thickness of Parylene-C can range from 1-10  $\mu$ m.

Parylene-C has been reported to have low adhesion to various metals and siliconbased ceramics. The current industry standard for improving adhesion is the use of a silane-based adhesion promoter (A174) prior to layer deposition [64]. Nevertheless, as will be explained in the next section, weak adhesion can allow condensation of the permeated moisture, resulting in shunt current leakage paths between conductive metals.

Another drawback of Parylene-C is the reported in vivo degradation observed during long-term animal studies Fig.2.7. Degradation has been shown to be in the form of film thinning, cracking, and possible flacking of the material [65]. For packaged ICs employing Parylene-C, such degradation may act as an easy ingress point for body fluids, leading to chip failure.

**Inorganic ceramic thin-films**: adapted from the semiconductor industry, various thin inorganic ceramic coatings have been explored as barrier layers for implantable electronics. Various silicon-based and metal oxide ceramics such as  $SiN_X$ ,  $SiO_2$ , SiC,  $Al_2O_3$ ,  $HfO_2$ ,  $TiO_2$  are a few examples of such inorganic films [67]. Besides having lower WVTR rates compared to organic thin films like Parylene-C, these thin-film ceramics have also shown good biocompatibility [68, 69].

Thin-film ceramic films can be deposited using different processes requiring different temperatures. The best quality films are usually deposited using a low pressure chemical vapor deposition (LPCVD) technique, which is performed at above 800°C [70]. These films can have the highest densities and barrier properties. LPCVD films of silicon nitride, in conjunction with silicon dioxide, have been used to encapsulate conductors and have been shown to be stable in saline, under mechanical and electrical stress, for more than two years [63]. Within the semiconductor industry, the process and temperature usually used for depositing silicon nitride (SiN $_X$ ) is plasma enhanced chemical vapor deposition, done typically at  $\approx$  400 °C. The main challenge in using these barrier materials is that they typically require a high temperature to achieve a reasonable deposition rate and density. In some instances, these films are not quite as conformal as required by some applications. For higher conformality, atomic layer deposition (ALD)

Figure 2.8: A neurostimulator/recorder ASIC coated with a thin-film ceramic ALD layer [74].

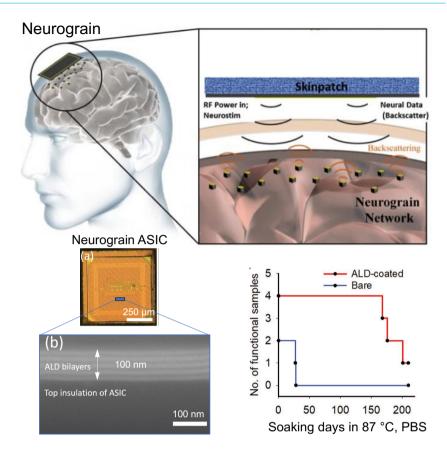

is well-suited for depositing high-density thin films with precise thickness [71]. ALD is usually used for applications that require high purity, precise film properties, and excellent control over film thickness (typically  $1-100\,\mathrm{nm}$ ). ALD equipment can be relatively complex and expensive due to the need for precise control over precursor delivery and reaction conditions. Fig.2.8 shows an ALD-coated neurostimulator IC also known as the 'Neurograin' [72]. To evaluate the longevity of the coating, stress testing in phosphate-buffered saline (PBS) solution at 87 °C on both coated and uncoated chips was done which showed an x5 increase in the functional lifetime of coated ICs compared to uncoated bare dice [73]. Failure was recorded as a shift in the backscattering frequency. The authors of the paper, however, do not explain the reasons for failure, of their uncoated and coated chips. Scanning electron microscope (SEM) cross-sectional investigations on the failed ALD-coated ICs demonstrated the presence of the ALD stack remaining intact throughout the stress-soaking.

One of the main issues with thin ceramic barrier layers is the presence of pinholes or defects which can negatively impact their barrier properties [75]. To mitigate this

Figure 2.9: A neurostimulator ASIC coated with a hybrid polyimide/ALD thin-film layer [78].

issue, brittle ceramic films can be encapsulated with a final biocompatible polymer. The brittleness of these inorganic layers is also an issue that sets some requirements for the thermal budget and the polymer that is applied as the final coat. In [76], the use of a soft silicone final encapsulation on ALD was suggested. Given the low Young's modulus of silicone ( $\approx$ 1 MPa for silicone vs. 3 GPa for Parylene-C) it can be used as a mechanical buffer on top of the ALD while minimizing the stresses on the ceramic during silicone processing (expansion and shrinkage during curing) or the lifetime aging in the body (moisture-induced expansion of silicone).

**Hybrid ceramic-polymer coatings**: As discussed earlier, the presence of defects and pinholes together with brittleness are two major issues for inorganic ceramic films. To mitigate these drawbacks, another technique has been combining ceramic films with thin polymer layers with more flexible characteristics. A few examples of this combination are [75] and [77] where they combined ALD-deposited films with Parylene-C or polyimide.

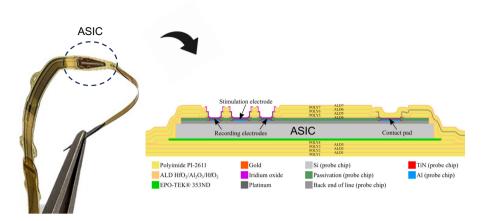

As an example, Fig. 2.9 shows an implantable device using a multilayer ALD/polyimide coating for packaging the IC.

## **2.6.** CHALLENGES IN CONFORMAL PACKAGING OF IMPLANTABLE ICS

### 2.6.1. VOID AND DEFECT-FREE PACKAGING

One of the main challenges when packaging electronics with polymers like silicone or epoxy is to create a void-free environment within the package, specially around the sensitive components [63]. Voids in the polymer can be saturated with moisture when the device is implanted in the body [79]. If the voids are situated in a critical spot of the device, e.g. between two conducting metal lines, it can result in shunt electrical paths, altering the impedance between the two metal lines (Fig.2.10). Depending on the circuitry, the altered impedance can result in electrical malfunction, power drainage, or

Figure 2.10: Schematics depicting voids and defects for polymer and thin-film coating applied on metallization structures. For void-free polymer packages, three types of voids could be present: 1) in the polymer away from critical devices, 2) in between critical metal traces, and 3) on substrate materials (metal or components) but not in between critical metallization.

total failure of the device. Other factors such as biasing between the metal lines and contamination can increase the condensation rate within the void [80]. As a result, the shunt impedance will have a lower resistance causing further power draining or functionality loss.

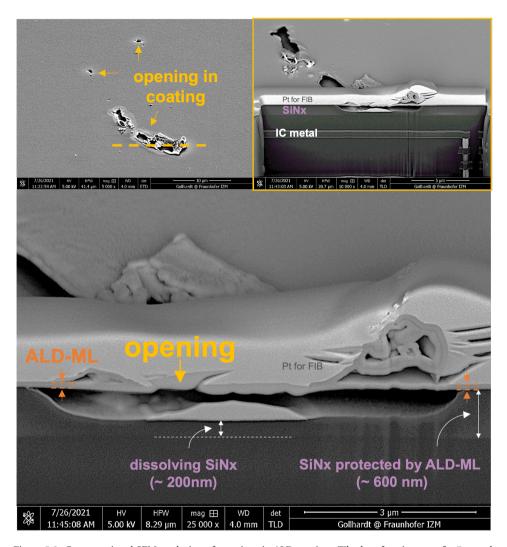

For thin-film coated electronics, any imperfection or openings in the coating will allow the ingress of ionic fluids. Similar to voids in a polymer, openings can interrupt the electrical performance when touching critical metal lines but also result in electrical open circuits by gradually degrading/corroding the metals [81].

With the miniaturization of the next generation of devices, ensuring a void-free packaging is even becoming more critical. In addition, these emerging applications will have neural sensing functionality with signals in the  $\mu V$  range where even tiny amounts of shunt leakage path can result in signal loss.

### **2.6.2.** ADHESION

Adhesion between the coating and all the substrate materials is critical for the longevity of the implants [9, 82]. Adhesion is critical for both polymer-encapsulated and thin-film-coated devices. For thin-film barriers with low WVTR, film delamination can weaken the structural integrity of these barrier films and result in failure [75, 83].

Similar to voids, interfacial adhesion loss can result in gaps between the encapsulant and the underlying materials. Unlike visible voids, however, adhesion losses are undetectable right after coating and typically occur gradually over time as the device is stressed in the aging media (human body).

Adhesion depends not only on the coating materials but on the interfacial interaction that is made between the coating and the encapsulant [84, 83, 79]. Therefore, for proper design and selection of the packaging, a good understanding of all the substrate materials and electronic devices is necessary. Below, a few material examples typically used for implantable application are given which have demonstrated poor and good adhesion to silicone.

#### POOR ADHESION: PLATINUM AND GOLD

Platinum and gold are noble metals with excellent long-term biocompatibility and biostability with high corrosion resistance [29]. Due to these favorable properties, they have

been frequently used in the implantable medical device industry. However, their poor adhesion with polymers can limit their use in critical areas where strong long-lasting adhesion is needed [80, 85].

#### STRONG ADHESION: SILICON-BASED CERAMICS AND METAL OXIDES

Various ceramic materials such as alumina [9], silicon-based ceramics [86], and some metal-based oxides (such as  $HfO_2$ )[87] have been shown to have long-lasting underwater adhesion with silicone.

Besides strong adhesion, the cleanliness of the substrate materials is also critical in ensuring a successful and reliable encapsulation/coating. Contamination on the surface not only will prevent the formation of the desired chemical bond but will also accelerate the condensation of the permeated moisture on the substrate surface. The condensed moisture in combination with the surface contamination will result in more aggressive shunt leakage paths [82]. Therefore, the cleanliness aspect cannot be emphasized enough.

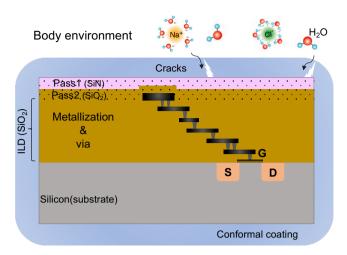

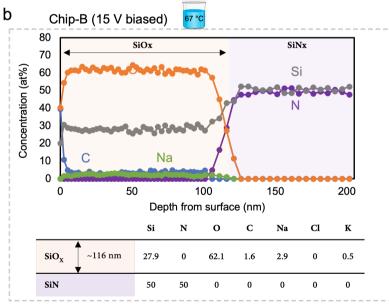

### 2.6.3. MOISTURE-RESISTANCE OF UNDERLYING ELECTRONIC COMPONENTS

As explained previously, all polymers, including Parylene-C and LCP, will allow moisture ingress over periods of 7 - 30 days at a 37 °C ambient (varying based on the thickness of the polymer) [32, 83]. This drawback for polymer packaging creates a key requirement for the underlying electronics: all materials and interfaces that are used in the electronic device should be moisture-robust [88]. This requirement further limits the choice of materials and processes that could be used for the fabrication of the electronics. For example, in [86] interdigitated aluminum metallizations were coated with a thin  $SiO_X$ ceramic and a final silicone overmold. Long-term Impedance measurements showed a gradual change in the spectra when the device was submerged in PBS solution at 67 °C. Optical microscopy did not show any material delamination, dissolution, or metal corrosion which could explain the change in the impedance spectra. However, when using detailed material analysis (X-ray photoelectron spectroscopy and SEM cross-sectional analysis) it was found that the SiO<sub>X</sub> ceramic showed signs of chemical modification and hydration, which could alter the dielectric and insulation properties of the layer. Another example in the same literature was the corrosion of the Au-Al wire-bonds. The siliconeencapsulated Au-Al interface resulted in a galvanic reaction triggered by moisture [81]. Over time, the galvanic reactions resulted in the corrosion of the least noble metal, in this case, Al.

Overall, for silicon-ICs, if the materials used by commercial foundries are found to be unstable when exposed to moisture (100% RH), this would make the packaging a daunting task and limit their chronic application.

## **2.7.** EVALUATION OF COATING PERFORMANCE AND LONGEVITY ESTIMATION

As explained in the previous section, one of the main advantages of hermetic enclosures is the standardized helium leak test. As this test is done on each individual device, the hermeticity of each implant can be verified prior to implantation. For the next genera-

tion of active medical implants employing void-free conformal packaging, there is no standardized test for determining functional longevity. As these packaging solutions could be a viable option for future implants, new techniques are required to evaluate and verify their reliability and targeted longevity. The current practice to evaluate the reliability of polymer-packaged electronics is to submerge the device in a physiological environment such as PBS which has a similar osmotic molarity and pH to body fluid [89]. Some studies have also proposed the use of adding hydrogen peroxide to the PBS solution to better mimic the radical oxygen species present during the first week to months of the implantation [65]. Nevertheless, all these in vitro environments are a simplified model of the complex chemical environment of the body. Therefore, one should validate the in vitro aging studies by performing a comparison with in vivo aging. As devices are getting smaller and more compact, observing and understanding potential reliability issues is much more challenging compared to larger devices [90]. Special tools must be applied to visualize defects or other issues throughout the development, manufacturing, and prior release of the device. Additionally, once the device is implanted, understanding the failure mechanisms and the effect of various stressors (chemical, mechanical, and electrical) can significantly help in increasing the reliability. This section will give a brief overview of the techniques that can be used for evaluating the performance of polymeric packages or thin-film coatings. Similarly, techniques that can be employed for evaluating the integrity of IC structures will be discussed.

#### 2.7.1. Interdigitated capacitor structures

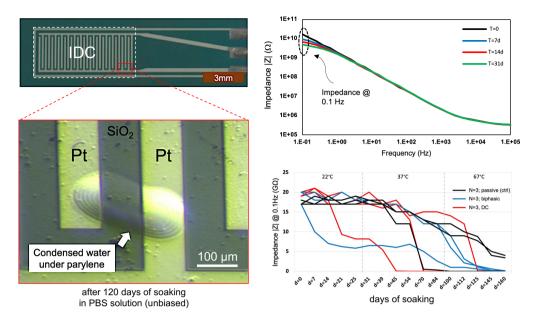

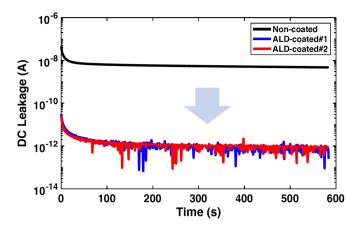

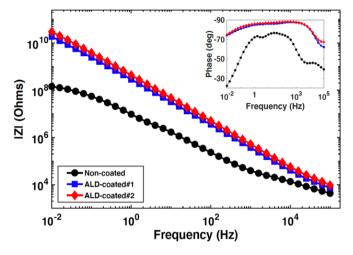

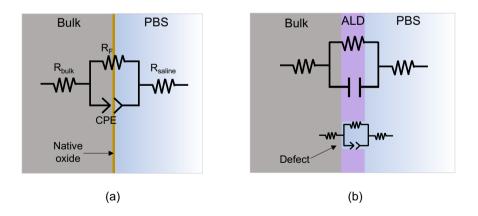

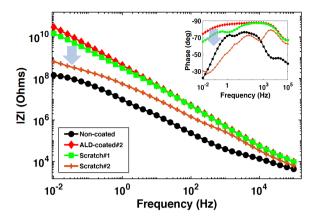

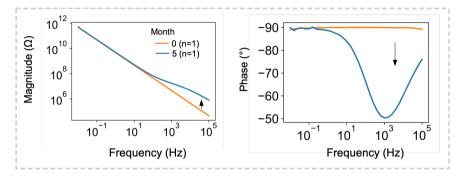

Interdigitated capacitors (IDC) are useful test vehicles for evaluating encapsulation and adhesion performance. Using IDC structures various studies have evaluated the longterm performance of silicone, polyimide, Parylene-C, epoxy, and LCP [80, 83, 91]. These structures are also valuable for evaluating the barrier properties of thin ceramic coatings [86]. The main advantages of IDC structures compared to other encapsulation performance techniques are, 1) the capability of using sensitive electrical characterization techniques to measure insulation performance: DC current leakage, and electrochemical impedance spectroscopy (EIS), 2) the ability to evaluate the effect of various electrical signals (DC or AC) on the long-term aging of materials [80]. Fig.2.11, for example, shows an IDC structure that was used for evaluating the Parylene-C coating on platinum IDC metallization and SiO<sub>2</sub> (used as substrate). EIS measurements performed over the duration of aging can reveal various chemical and mechanical phenomena occurring on the materials and interfaces. For example, as shown in [92] changes in the EIS magnitude at lower frequencies (<10 Hz) can be used to demonstrate shunt current leakage paths developing between the comb structures (bottom left microscope image in Fig.2.11). The effect of continuous electrical biasing on the shunt leakage growth and/or material degradation can also be picked up using EIS measurements (Fig.2.11 right bottom).

The drawback of IDC structures is the detailed set-up development, cabling and interconnection required to ensure that the set-up is more reliable and robust throughout the aging than the test structure itself. In [91], the authors describe an apparatus that is carefully designed for such long-term material aging studies.

Figure 2.11: IDC test structures used for evaluating coating performance and the long-term effect of electric signals [93, 76].

### 2.7.2. ACCELERATED TESTING WITH ELECTRICAL BIASING

For medical devices intended for 5-10 years of functional lifetime, performing real-time aging (at 37 °C) is almost impractical. For this purpose, accelerated aging of the materials and the packaging can be used [91, 94]. The current method for accelerating the degradation of polymers and interfaces is by increasing the testing temperature [63, 20, 95]. In addition to aging the polymer, temperature will also play a role in accelerating moisture permeation within the polymer [63]. For interfaces and coatings, differences in the coefficient thermal expansion (CTE) can also result in stresses, accelerating delamination [90].

Electrical biasing can also play a role in aging electronics and accelerating device failure, especially when the device is exposed to high moisture levels. In [96] it was shown that unbiased devices had a  $\approx$  x13 longer lifetime compared to biased devices. The tested device was a wirelessly powered ASIC comprised of a neural recording chip, and a few passive components (capacitors and a coil). The authors did not report the reason for the failure. Therefore, an in-depth understanding of the effects of biasing on failure(s) is lacking. In [97], to better understand the effect of biasing on failure, IDC structures were coated with a thin Parylene-C layer and subjected to three different stress signals: unbiased, DC-stress, and AC-stress. Results showed how different electrical signals can affect the insulation between the interdigitated metallization and lead to different failure mechanisms.

Similarly, in [76], the effect of DC electrical biasing on ALD-coated IDC structure was investigated. Without biasing, the ALD coating maintained a relatively stable electrical

Figure 2.12: Various material characterization techniques used for capturing overview (mm-level) and surface level (nm-level) info from the coating and materials used for IC packaging.

impedance for over 400 days when submerged in PBS solution. However, after one day of electrical biasing, all the ALD coating on the biased metals cracked (WE and CE), exposing the metals to PBS solution.

These findings highlight the importance of investigating the effect of electrical biasing when evaluating the functional lifetime of implantable electronics.

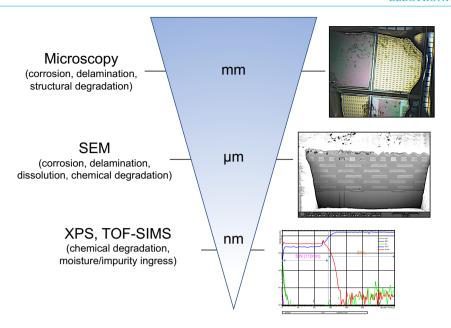

### **2.7.3.** MATERIAL EVALUATION TECHNIQUES

Complementary to the electrical measurements, material analytical techniques can be valuable tools for evaluating coating performance. For example, for silicon-IC, various material analytical techniques are used for failure analysis [98]. Below a few of these techniques will be briefly described. As shown in Fig.2.12, these techniques provide information on the materials at different scales.

#### **MICROSCOPY**

During microscopy, the exterior of the package can be evaluated in detail. Depending on the transparency of the polymer, various failures can be identified: cracking of the polymer, delamination of polymer from the substrate materials (usually seen as Newton rings or bulging and blisters), and polymer degradation (seen as color change). Microscopy can be used from low magnification (x4) for acquiring overviews of the device, to higher magnifications (x200) to observe film defects, cracks, or blisters in both polymers and ceramics.

For silicon ICs, microscopy can be a quick and useful technique for chip inspection

and acquiring an overview of the entire chip: pads and wire-bonds, top metallization, IC passivation (final top dielectric), and all four side walls of the structure. It is also useful in identifying the possible location of failure(s), helping further steps in the root cause analysis process. Microscopy is also a practical tool for corrosion inspection on the pads and wire-bonds. Early film delamination within the IC's material stack could be picked up with microscopy.

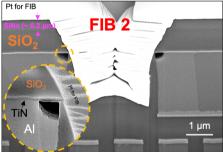

### SEM CROSS-SECTIONAL ANALYSIS

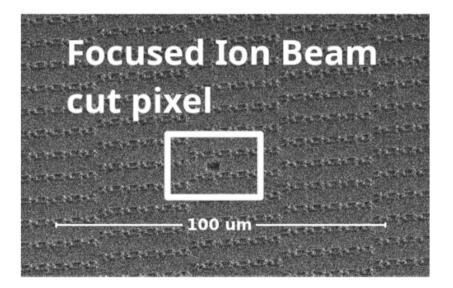

Scanning electrode microscopy can be used for higher magnification (x100K) for a closer inspection of the failure. SEM surface analysis at high magnification is extremely valuable for identifying cracks or defects in the film. For analyzing cross sections of the material stack, focused ion beam (FIB) can employed in the SEM machine. SEM inspections on the FIB cuts can provide valuable insights on layer losses (due to dissolution), film delamination or chemical modification [86, 90].

#### CHEMICAL CHARACTERIZATION

Understanding the chemical stability and ionic/moisture barrier properties of the materials post long-term aging (in vitro or in vivo) is key in engineering long-lasting devices. Time-of-flight secondary ion mass spectrometry (TOF-SIMS) is perhaps one of the most sensitive analytical techniques that is frequently used within the semiconductor industry. During IC fabrication, owing to its high sensitivity, ToF-SIMS is used to detect trace levels of impurities that could arise due to contamination or diffusion. Another key advantage of ToF-SIMS is the ability to generate detailed molecular and elemental maps with high spatial resolution. In the depth profiling mode, ToF-SIMS can provide information, with parts-per-billion-level (ppb) detection limits, from the surface of the material all the way into the micrometer depths of the layer.

The main drawback of ToF-SIMS, however, is the lack of quantitative data due to the matrix effect. The matrix effect makes it difficult to perform quantitative analysis because the signal intensity for a given element or molecule can vary depending on the surrounding matrix, leading to inaccurate concentration measurements [99]. To resolve these drawbacks, ToF-SIMS can be complemented with X-ray photoelectron spectroscopy (XPS) analysis. XPS is a surface-sensitive analytical technique that detects the elemental composition and chemical states of materials. In comparison to ToF-SIMS, it has lower sensitivity, capable of detecting elements in concentrations as low as 0.1 atomic percent. However, one of its main advantages is the ability to provide detailed chemical state information (for example capable of identifying how silicon is bonded to oxygen in a SiO<sub>2</sub> network). Similar to ToF-SIMS, XPS operates under ultra-high vacuum conditions, typically around  $10^{-9}$  to  $10^{-10}$  torr, to prevent contamination and ensure accurate measurements. XPS cannot detect hydrogen (H) and helium (He) because these elements lack core-level electrons that can be ionized by the X-ray source. It also has lower sensitivity for light elements like lithium (Li), beryllium (Be), and boron (B), making accurate detection more challenging. ToF-SIMS is generally used for these elements [98].

#### **ON-CHIP MONITORS**

26

For automotive ICs, cracking of the die passivation layers has always been a major reliability concern [51, 100, 101]. Various investigations have shown passivation cracking to be induced by the expansion of the polymer packaging which is generally an epoxy composite with high Young's modulus [50, 98, 102]. Variations in the thermal expansion coefficient between the packaging polymer and the die passivation can result in interfacial shear stresses causing cracks in the brittle passivation. For this purpose, various on-chip complementary metal-oxide semiconductor (CMOS) crack sensors have been proposed that can monitor and map possible stresses on the die surface [103, 104, 105]. Moisture-induced expansion of the epoxy or any other polymer package could also result in stresses at the interfaces [100]. For an IC exposed to 100 % RH, a cracked die passivation can pose an even greater risk as it provides an easy entry point for moisture and ions. [106].

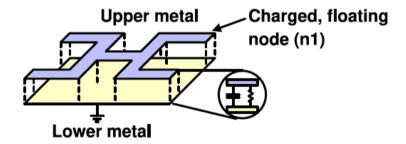

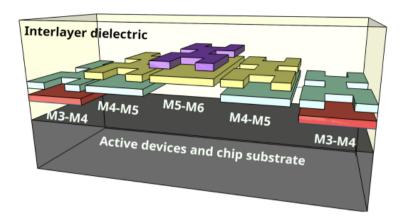

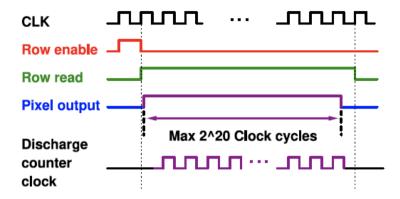

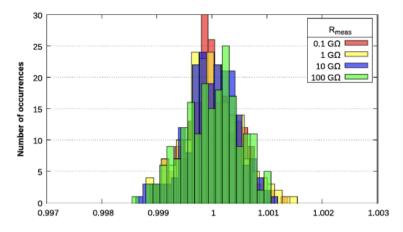

Similar to the top passivation, the sidewalls of the chip can be a point of impurity ingress. Especially during die singulation, stresses can be exerted on the IC's material stack, causing cracking [90]. For sidewall protection, both as an impurity barrier and a crack stop, the IC industry has been using die seal rings [107]. Die seal rings, as the name suggests, are metal rings around the die made of different metal stacks and vias present in the IC process. In [108], the authors incorporated a sensor within the seal rings to monitor the potential penetration of impurities from the sidewalls.

As ICs will be integral components for future miniaturized electronic implants, monitoring their integrity is essential for ensuring a reliable operation. I believe such an on-chip monitor will be an essential component for polymer-packaged implantable ICs.

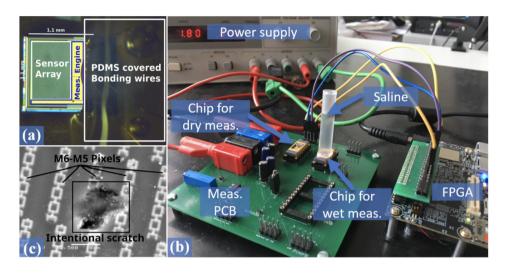

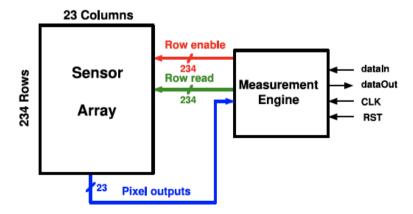

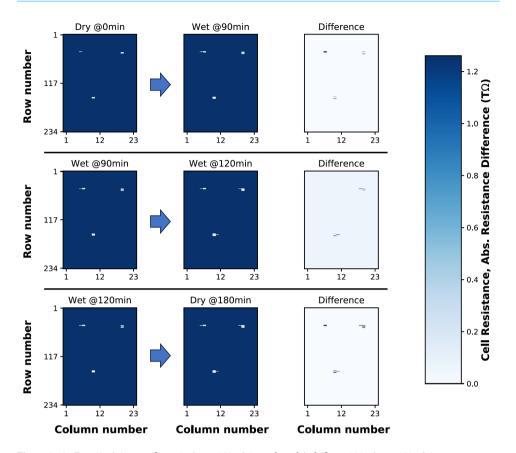

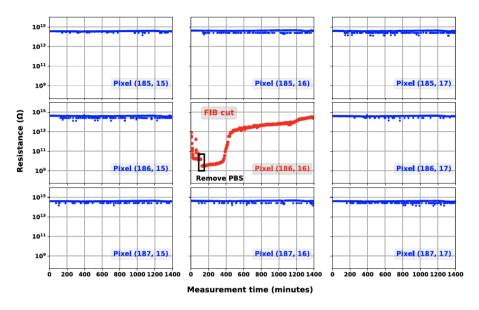

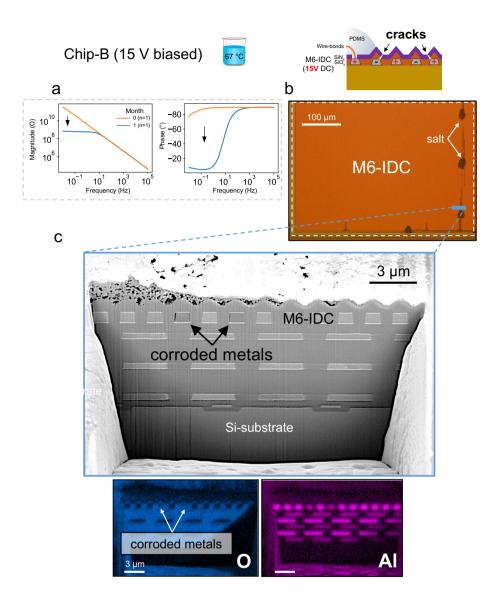

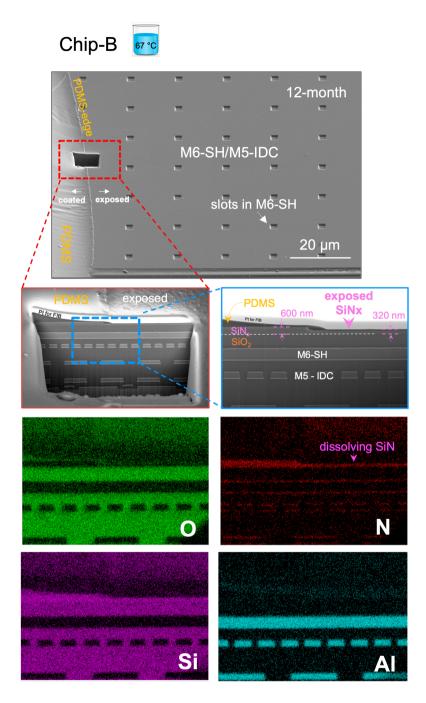

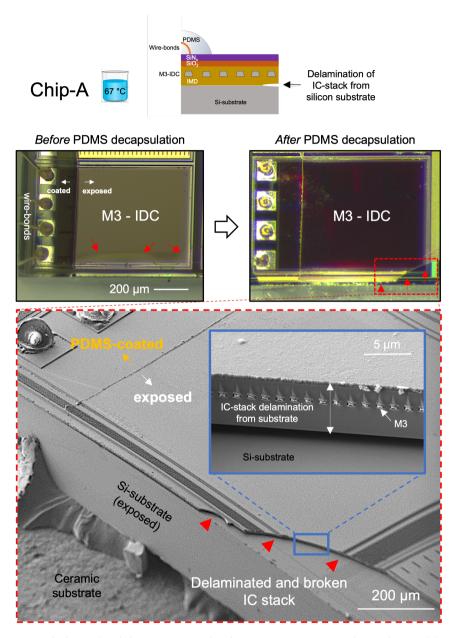

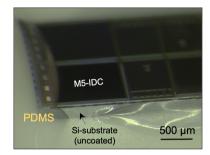

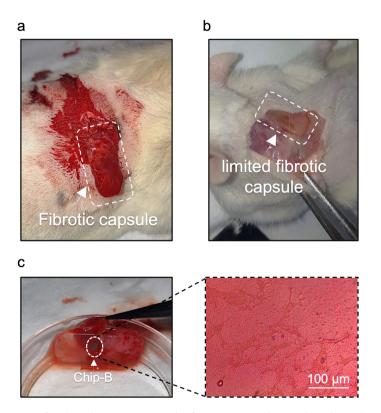

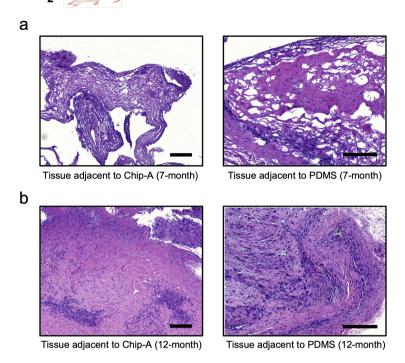

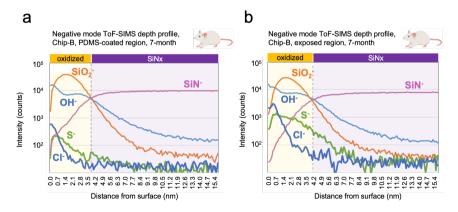

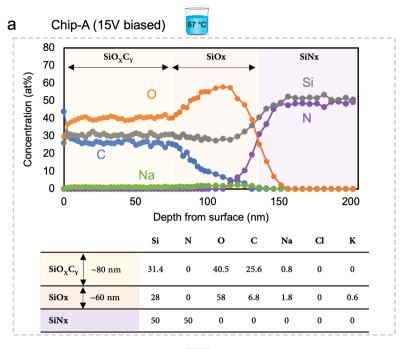

#### 2.7.4. LONGEVITY ESTIMATION