**Delft University of Technology**

#### **Quasi-vertical Gallium Nitride Diodes for Microwave Power Applications**

Sun, Y.

DOI 10.4233/uuid:e6e7ddf2-96cf-4d43-aa94-243c52acc4e1

**Publication date** 2022

**Document Version** Final published version

Citation (APA) Sun, Y. (2022). *Quasi-vertical Gallium Nitride Diodes for Microwave Power Applications*. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:e6e7ddf2-96cf-4d43-aa94-243c52acc4e1

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# Quasi-vertical Gallium Nitride Diodes for Microwave Power Applications

## Quasi-vertical Gallium Nitride Diodes for Microwave Power Applications

### Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology by the authority of the Rector Magnificus Prof.dr.ir. T.H.J.J. van der Hagen chair of the Board for Doctorates to be defended publicly on Monday 27 June 2022 at 10:00 o'clock

by

### Yue Sun

Master of Engineering in Mechanical Engineering, Guilin University of Electronic Technology, China born in Hebei, China This dissertation has been approved by the promotors.

Composition of the doctoral committee:

Rector Magnificus Prof.dr. G.Q. Zhang Prof.dr.ir. W.D. van Driel

Independent members: Prof.dr. U. Mishra Prof.dr. V. Veliadis Prof.dr. P.R. Wilson Prof.dr. B. Shen Dr. Q.W. Fan

*Reserve member:* Prof.dr.ir. P.M. Sarro chairman Delft University of Technology, promotor Delft University of Technology, promotor

University of California, Santa Barbara, USA North Carolina State University, USA University of Bath, UK Peking University, China Delft University of Technology

Delft University of Technology

*Keywords:* quasi-vertical; Gallium Nitride (GaN); Schottky Barrier Diodes (SBD); inductively coupled plasma (ICP) etching; trench etching profile; leakage suppression; edge terminations; microwave power limiter; microwave power detector.

*Printed by:* Ipskamp Printing

*Cover by:* Yue Sun

Copyright © 2022 by Yue Sun

ISBN 978-94-6421-787-2

An electronic version of this dissertation is available at http://repository.tudelft.nl/.

To all those who have helped and supported me.  $\label{eq:support} \mbox{Yue Sun}$

# Contents

| Su | ımm  | ary                                                        | ix |

|----|------|------------------------------------------------------------|----|

| Sa | men  | vatting                                                    | xi |

| 1  | Intr | oduction                                                   | 1  |

|    | 1.1  | Background                                                 | 2  |

|    | 1.2  | GaN-based RF devices                                       | 3  |

|    | 1.3  | Quasi-vertical GaN Schottky diodes                         | 4  |

|    | 1.4  | Problems and challenges                                    | 5  |

|    |      | Aim and scope                                              | 6  |

|    | 1.6  | Thesis outline                                             | 7  |

|    | Refe | rences                                                     | 8  |

| 2  | Ver  | ical GaN Schottky diodes and state of the art              | 13 |

|    | 2.1  | Basic principles of vertical Schottky diodes               | 14 |

|    |      | 2.1.1 Forward conduction and reverse blocking              | 14 |

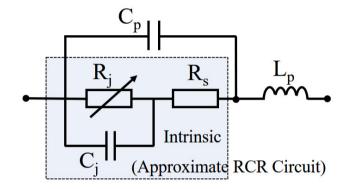

|    |      | 2.1.2 RF equivalent circuit.                               | 18 |

|    | 2.2  | Review of the GaN-based vertical SBDs                      | 19 |

|    |      | 2.2.1 Selection of different substrates                    | 19 |

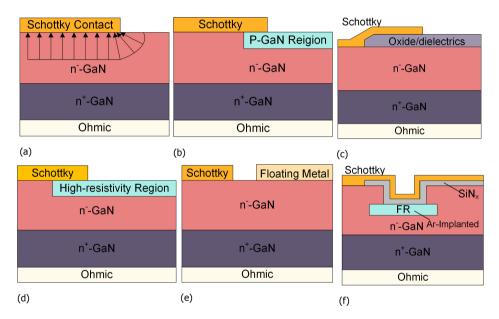

|    |      | 2.2.2 Edge termination techniques                          | 22 |

|    |      | Summary                                                    |    |

|    | Refe | rences                                                     | 27 |

| 3  | Dee  | p and high aspect ratios of GaN trench etching techniques  | 33 |

|    | 3.1  | Common GaN deep etching issues                             | 34 |

|    | 3.2  | Experimental characterization of GaN etching               | 37 |

|    |      | 3.2.1 Method and equipment                                 | 37 |

|    |      | 3.2.2 Flow of soft mask (photoresist)                      | 39 |

|    |      | 3.2.3 Flow of hard mask (silicon dioxide)                  | 42 |

|    | 3.3  | The influence of etching parameters on micro-trench issues | 44 |

|    |      | 3.3.1 Effect of etch time, ICP power and RF power          |    |

|    |      | 3.3.2 Role of $BCl_3$ concentration on GaN etching profile |    |

|    |      | 3.3.3 TMAH wet treatment                                   | 50 |

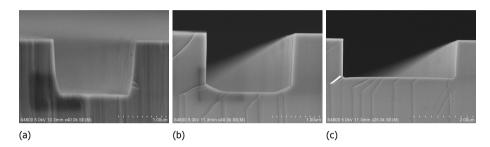

|    | 3.4  | Optimal GaN etching results                                | 52 |

|    |      | 3.4.1 Mesa structure                                       | 52 |

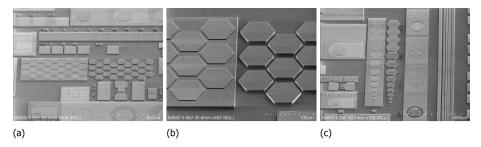

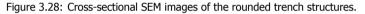

|    |      | 3.4.2 GaN microstructures                                  |    |

|    | 3.5  | Summary                                                    | 56 |

|    | Refe | rences                                                     | 56 |

| 4  | Des   | ign, fabrication and characterization of quasi-vertical GaN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|    | SBI   | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 61    |

|    |       | Device design and layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

|    | 4.2   | Fabrication of vertical GaN diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

|    |       | 4.2.1 Fully-vertical GaN diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

|    |       | 4.2.2 Quasi-vertical GaN diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

|    | 4.3   | Device modeling and optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

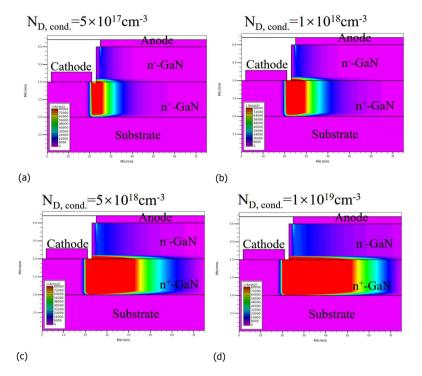

|    |       | 4.3.1 Current crowding effect (CCE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

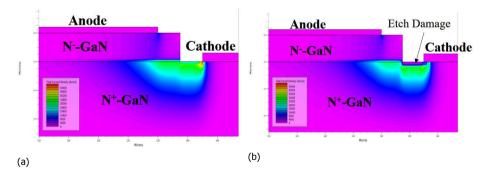

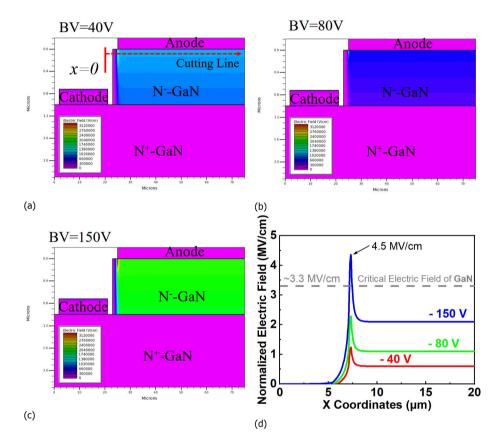

|    |       | 4.3.2 Peak electric field.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

|    | 4.4   | Support of the second |       |

|    |       | 4.4.1 Mesa etching optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

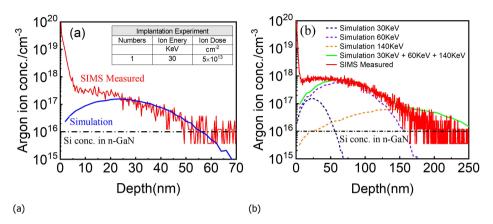

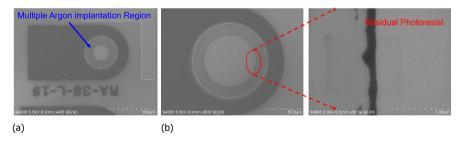

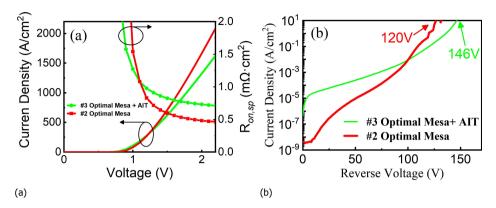

|    |       | 4.4.2 Argon-implanted termination (AIT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

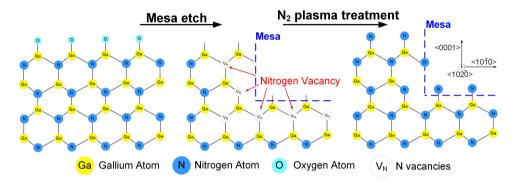

|    | 4 5   | 4.4.3 $N_2$ plasma treatment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

|    |       | Performance benchmark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|    |       | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

|    | Reie  | erences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 80  |

| 5  | App   | lications of quasi-vertical GaN SBD in microwave circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 91    |

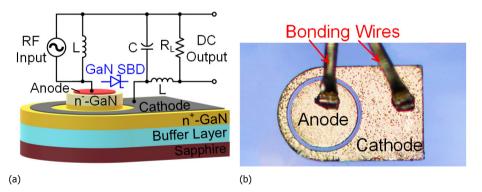

|    | 5.1   | First demonstration of high-power microwave limiters based                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

|    |       | on quasi-vertical GaN SBD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 92  |

|    |       | 5.1.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

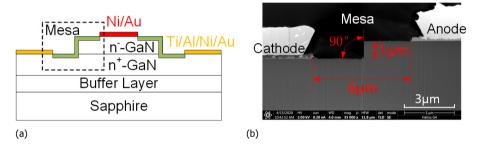

|    |       | 5.1.2 Design and fabrication of GaN SBD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

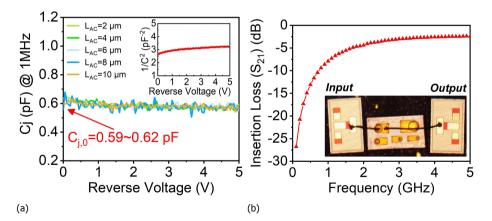

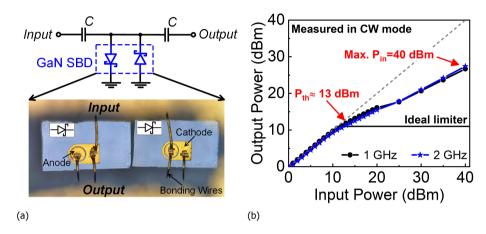

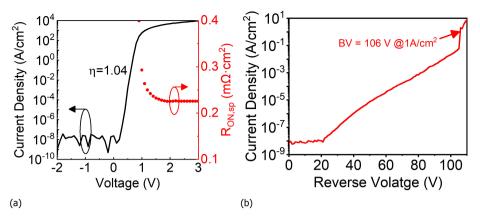

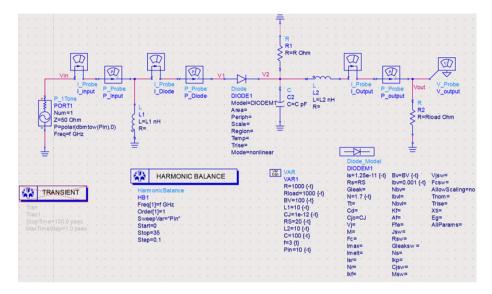

|    |       | 5.1.3 Results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

|    |       | 5.1.4 Outlook                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

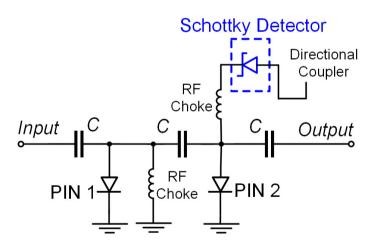

|    | 5.2   | Microwave power detector based on quasi-vertical GaN SBD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

|    |       | 5.2.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

|    |       | 5.2.2 Design and fabrication of GaN SBD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

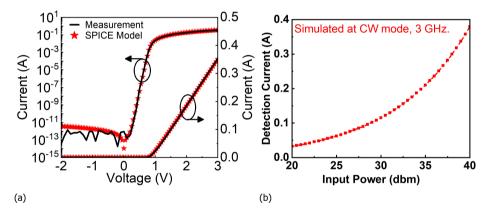

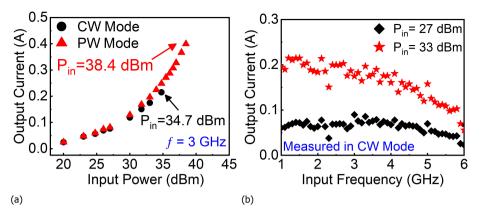

|    | - 0   | 5.2.3 Results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

|    |       | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

|    | Reie  | erences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 107 |

| 6  |       | clusions and recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 111   |

|    |       | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|    | 6.2   | Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 113 |

| A  | App   | endix A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 115   |

| Ac | ckno  | wledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 119   |

| Cι | ırric | ulum Vitæ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 121   |

| Li | st of | Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 123   |

# Summary

The deployment of fifth-generation (5G) networks requires more closely spaced wireless infrastructures with a high output power to deal with high-frequency signal attenuation issues. Microwave power limiters have been widely used in the RF front-end in various wireless communication systems. A diode limiter circuit prevents the damage of sensitive receiver components by allowing RF signals below a certain threshold to pass through, while larger signals exceeding the threshold are attenuated. Many studies have been carried out on Si-based diode limiters in recent years; however, they have shown scant room for further improvement as silicon reaches its theoretical limitations. From this perspective, there is a need for new semiconductor materials to satisfy the requirements of devices. Wide-bandgap materials (e.g., gallium nitride) have recently attracted a great deal of interest due to their superior material properties such as wide band-gap, high electron saturation velocity, and high critical electric field.

Although lateral-structure GaN devices are staying ahead of the pace of industrialization, they still face several constraints and do not reach the GaN material limit due to requiring a high epitaxial layer quality and precise processing. A vertical structure is a convenient solution in Si- or SiC-based devices, which are also attractive alternatives to GaN devices. Quasi-vertical GaN devices have the freedom to select substrates (such as silicon, sapphire, and SiC) by using hetero-epitaxial growth technology. A planar structure design is easy to integrate with other RF components. This dissertation aimed to develop a quasi-vertical GaN diode for highpower RF and microwave applications which could operate in a wide frequency band and at high input power levels, with easy integration and low cost. The scope of this dissertation involved three aspects: design and fabrication of a quasi-vertical GaN device with mesa etching optimization; suppression of reverse leakage with an enhanced breakdown voltage; demonstration of microwave power applications (limiters and detectors) based on developed GaN diodes.

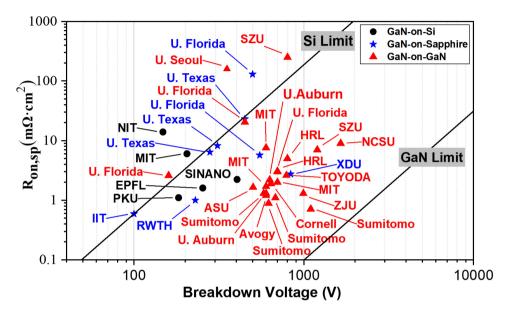

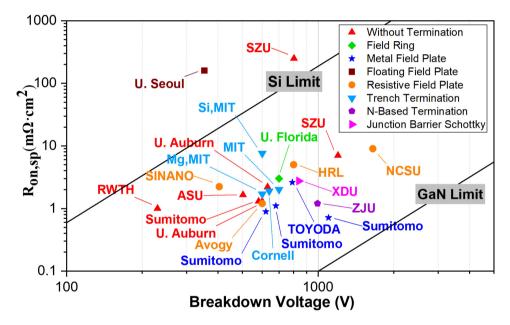

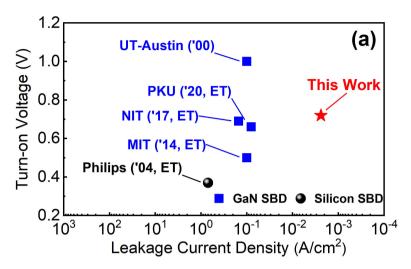

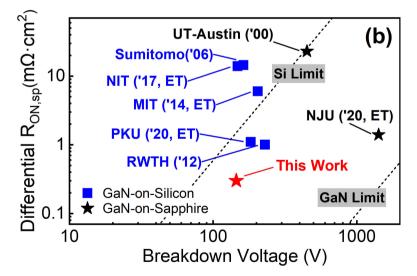

First, a literature summary of the state-of-the-art vertical GaN SBDs is presented in Chapter 2. A trade-off between the  $R_{on,sp}$  and BV of a diode is analyzed to characterize the performance of diodes. We discuss the benchmark of  $R_{on,sp}$  and BV for vertical GaN SBDs with different substrates (Si, sapphire, and GaN) and various edge terminal techniques. The equivalent circuit model of a diode for studying the high-frequency properties is introduced.

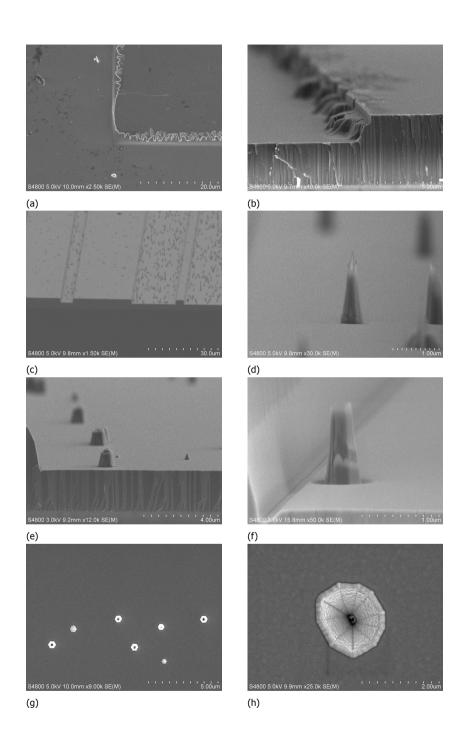

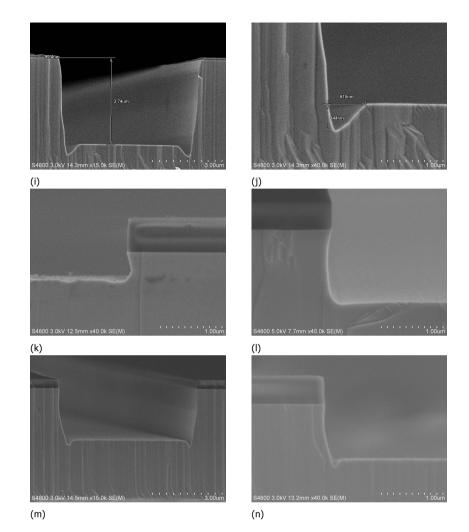

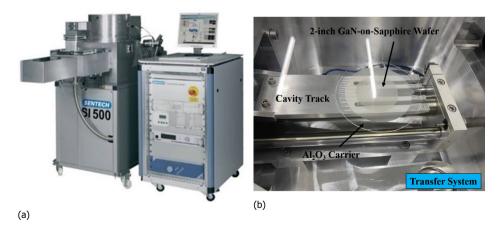

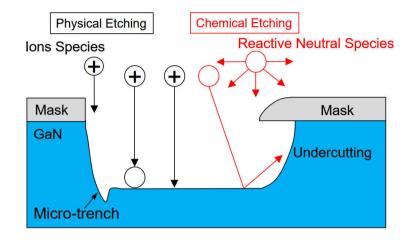

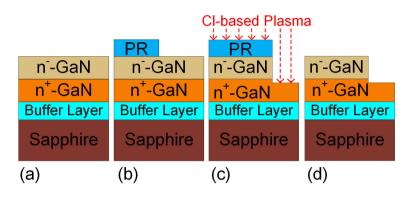

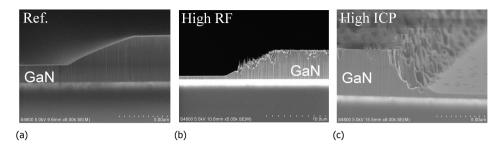

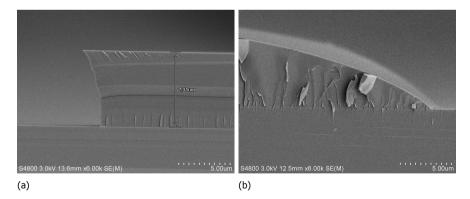

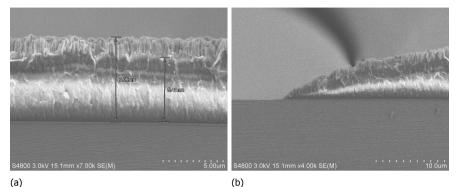

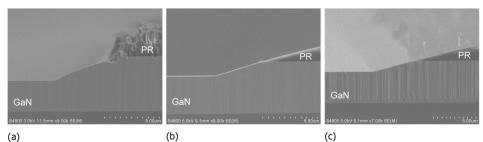

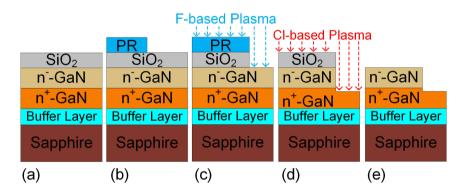

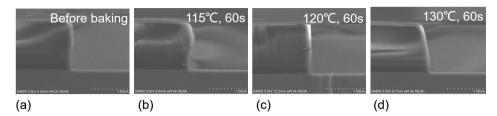

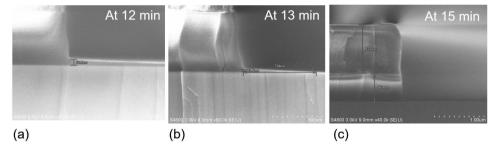

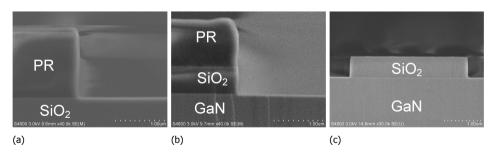

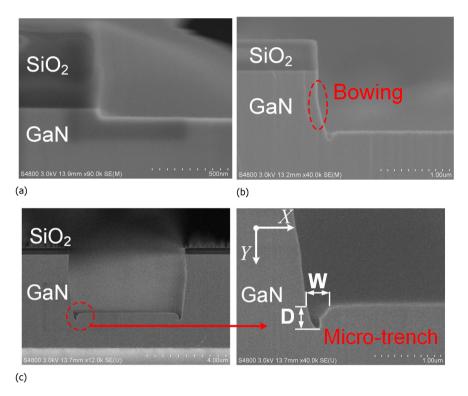

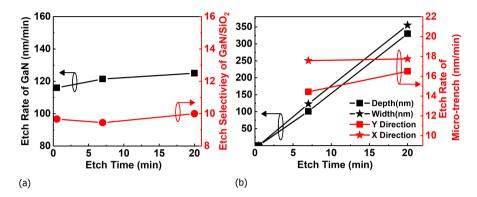

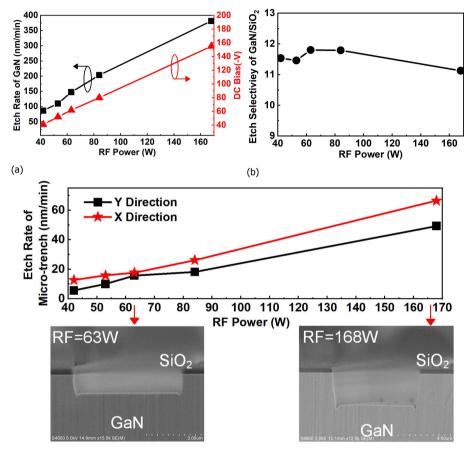

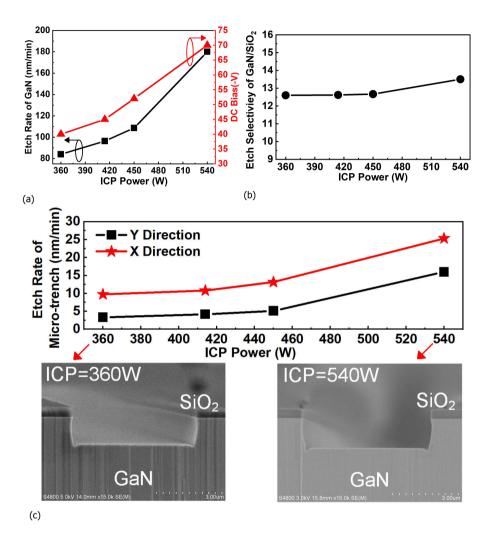

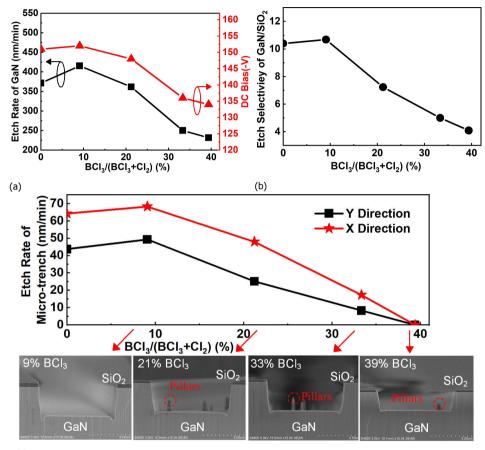

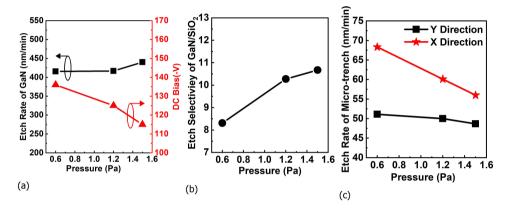

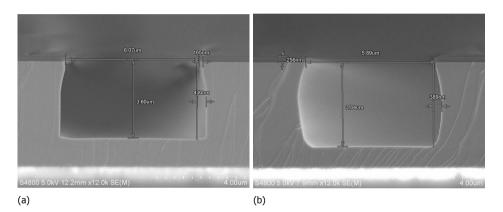

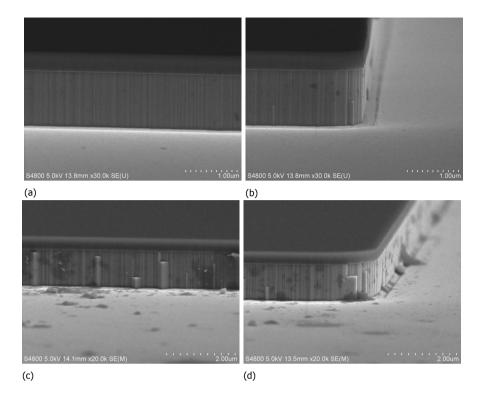

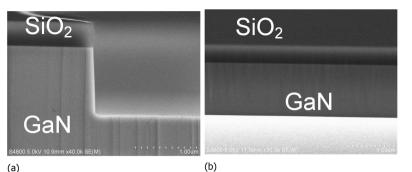

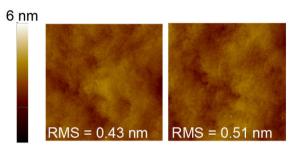

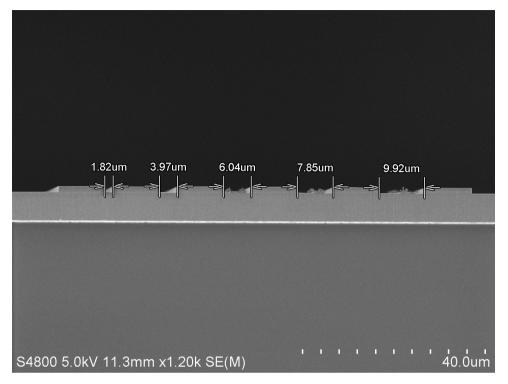

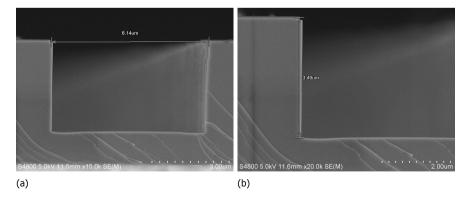

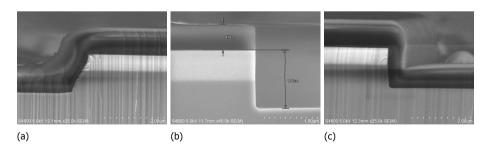

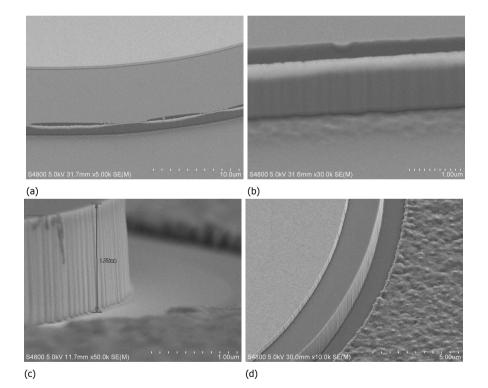

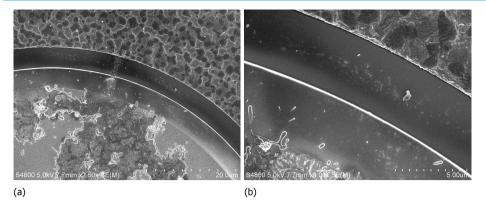

Second, the optimization of mesa etching for a quasi-vertical GaN SBD by inductively coupled plasma (ICP) etching is comprehensively investigated in this chapter. In particular, the microtrench at the bottom corner of the mesa is eliminated by optimizing etch recipes. For the photoresist (PR) masked GaN samples, high source power is the cause of deteriorated mesa sidewall morphology. Although high-temperature (>140 °C) hard baking prior to etching can produce a smooth sidewall, the drawbacks are significant and include oblique sidewall profile formation and hard striping. For the  $SiO_2$ -masked GaN samples, the micro-trench problem at the bottom corner of the mesa can be reduced or eliminated by reducing the source power or by adding  $BCl_3$  into the  $Cl_2$  plasma. After ICP etching, the use of a TMAH wet treatment for samples can obtain a near-90° steep mesa sidewall that is microtrench-free and has a smooth surface. The proposed etching technique can be extended to other GaN nanostructures, such as hexagonal pyramids and nanowire arrays, which is promising for sensors, vertical transistors, optoelectronics, and photovoltaics.

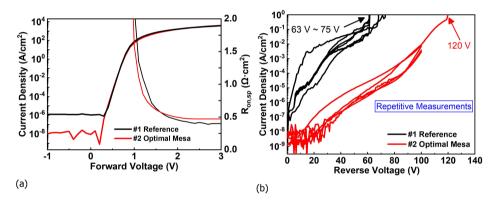

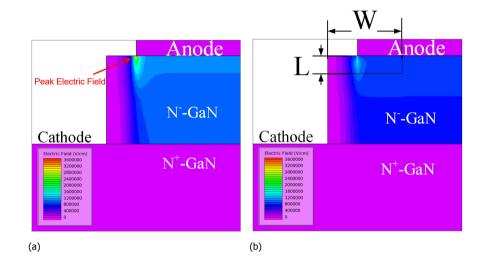

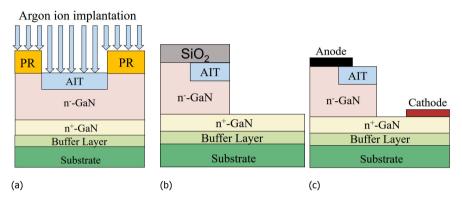

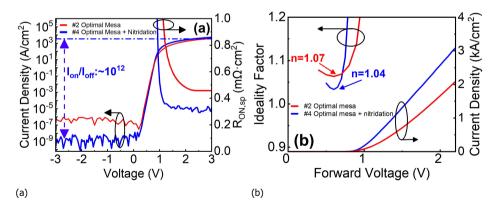

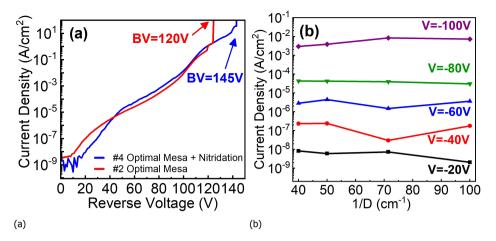

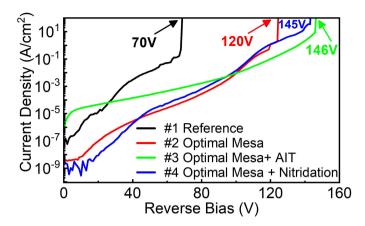

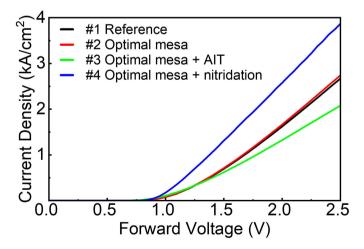

Third, a quasi-vertical GaN SBD is developed from the perspective of epilayer design, device layout, device modeling, fabrication, and leakage suppression. The design flow and fabrication process of quasi-vertical GaN diodes for microwave power applications are presented. Three solutions are developed to suppress the leakage current, namely, mesa optimization, argon ion terminations, and post-mesa nitridation. The experiment results show that our diode has the lowest leakage current density at 80% of the BV among the reported vertical GaN SBDs for a BV between 120 and 250 V. Combining mesa optimization and post-mesa nitridation technology effectively enhances the breakdown voltage and achieves excellent conduction characteristics.

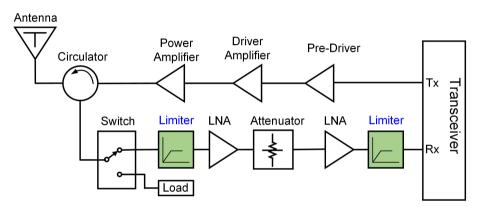

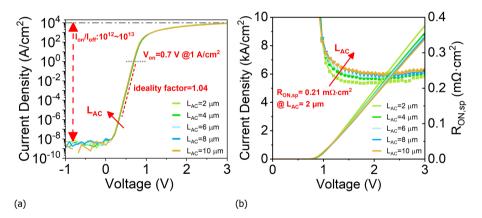

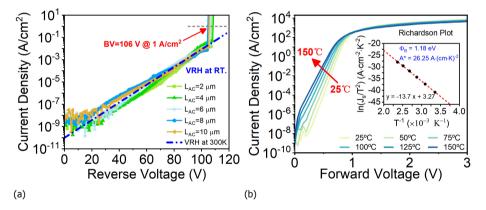

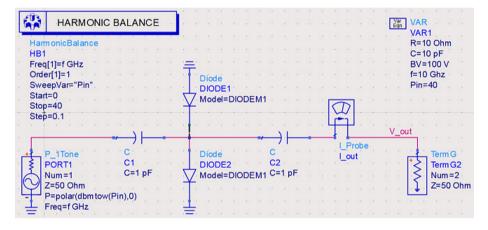

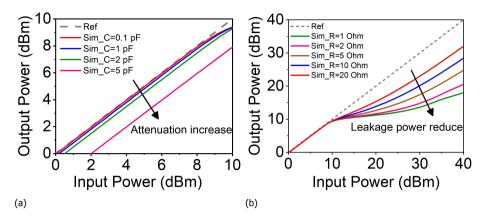

Fourth, a high-performance quasi-vertical GaN Schottky diode on a sapphire substrate and its application for high-power microwave circuits are investigated. We experimentally demonstrate the use of a vertical GaN SBD for L-band microwave power limiters for the first time ever. The GaN SBD limiter can handle at least 40 dBm of CW input power at 2 GHz without failure, which is comparable to a commercial Si-based diode limiter. Then, we experimentally demonstrate a quasi-vertical GaN SBD with post-mesa nitridation for high-power and broadband microwave detection. The fabricated quasi-vertical GaN diode reaches a high forward current density of 9.19  $kA/cm^2$  at 3 V, and BV of 106 V. An extremely high output current of 400 mA is obtained when the detected power reaches 38.4 dBm at 3 GHz in pulsed-wave mode.

Finally, all of the research content mentioned in this thesis is summarized, and the problems needing to be further investigated with lucubrate direction are indicated.

# Samenvatting

De uitrol van de vijfde generatie (5G) communicatie technologie van de vijfde generatievereist dichter bij elkaar geplaatste draadloze infrastructuren met een hoog uitgangsvermogen om de problemen met de hoogfrequente signaalverzwakking aan te pakken. Microgolfvermogensbegrenzers zijn veel gebruikt in de RF-front-end in verschillende draadloze communicatiesystemen. Een diodebegrenzercircuit voorkomt de schade aan gevoelige ontvangercomponenten door RF-signalen onder een bepaalde drempel door te laten, maar grotere signalen die de drempel overschrijden, worden gedempt. Er zijn de afgelopen jaren veel studies uitgevoerd naar op Si gebaseerde diodebegrenzers, maar ze toonden weinig ruimte voor verdere verbetering naarmate het silicium zijn theoretische beperkingen bereikte. Tegen deze achtergrond is er behoefte aan nieuwe halfgeleidermaterialen om aan de apparaatvereisten te voldoen. Wide band-gap materialen (bijv. Gallium Nitride) hebben onlangs veel belangstelling getrokken, toegeschreven aan hun superieure materiaaleigenschappen zoals brede band-gap, hoge elektronenverzadigingssnelheid en hoog kritisch elektrisch veld.

Hoewel gan-apparaten met laterale structuur de industrialisatie blijven voorblijven, worden ze nog steeds geconfronteerd met verschillende beperkingen en bereiken ze de GaN-materiaallimiet niet vanwege de vereiste hoge epitaxiale laagkwaliteit en nauwkeurige verwerking. De verticale structuur is een handige oplossing in Si-gebaseerde of SiC-gebaseerde apparaten, wat ook een aantrekkelijk alternatief is voor GaN-apparaten. Quasi-verticale GaN-apparaten hebben de vrijheid om substraten (zoals silicium, saffier en SiC) te selecteren met behulp van hetero-epitaxiale groeitechnologie. Het ontwerp van de vlakke structuur is eenvoudig te integreren met andere RF-componenten. Dit proefschrift heeft tot doel een auasi-verticale GaN-diode te ontwikkelen voor rf- en microgolftoepassingen met een hoog vermogen, die kan werken in een brede frequentieband en hoge ingangsvermogensniveaus met eenvoudige integratie en lage kosten. De reikwijdte van dit proefschrift omvat drie aspecten: Ontwerp en fabricage van guasi-verticaal GaNapparaat met mesa-etsoptimalisatie; Onderdrukking van omgekeerde lekkage met een verbeterde doorslagspanning; Demonstratie van microwave power toepassingen (limiters en detectoren) op basis van ontwikkelde GaN diodes.

Ten eerste werd de literatuursamenvatting voor de state-of-the-art verticale GaN SBD's gepresenteerd in hoofdstuk 2. Een afweging tussen  $R_{on,sp}$  en BV van een diode werd geanalyseerd om de prestaties van diodes te karakteriseren. We bespraken de benchmark van  $R_{on,sp}$  en BV voor verticale GaN SBD's met verschillende substraten (Si, saffier en GaN) en verschillende edge terminal technieken. Onmiddellijk werd het equivalente circuitmodel van een diode voor het bestuderen van de hoogfrequente eigenschappen geïntroduceerd.

Ten derde is de quasi-verticale GaN SBD ontwikkeld vanuit het perspectief van

epi-laagontwerp, apparaatlay-out, apparaatmodellering, fabricage en lekonderdrukking. Het ontwerpstroom- en fabricageproces van quasi-verticale GaN-diodes voor voedingsmagnetrontoepassingen werd gepresenteerd. Er werden drie oplossingen ontwikkeld om de lekstroom te onderdrukken, waaronder mesa-optimalisatie, Argon-ionafsluitingen en post-mesanitrering. De experimentresultaten tonen aan dat onze diode de laagste lekstroomdichtheid heeft bij 80% van de BV onder de gerapporteerde verticale GaN SBD's voor de BV tussen 120 V en 250 V. De combinatie van mesa-optimalisatie en post-mesa nitridatietechnologie verbetert effectief de doorslagspanning en bereikt uitstekende geleidingseigenschappen.

Ten vierde werden een krachtige quasi-verticale GaN Schottky-diode op Sapphiresubstraat en de toepassing ervan voor krachtige microgolfcircuits uitgevoerd. We hebben voor het eerst ter wereld experimenteel een verticale GaN SBD voor L-band microgolfvermogensbegrenzers gedemonstreerd. De GaN SBD-begrenzer kan zonder storing ten minste 40 dBm CW-ingangsvermogen bij 2 GHz aan, wat vergelijkbaar is met de commerciële Si-gebaseerde diodebegrenzer. Vervolgens hebben we experimenteel een quasi-verticale GaN SBD aangetoond met post-mesanitratie voor detectie van hoge vermogens en breedbandmagnetrons. De gefabriceerde quasi-verticale GaN-diode bereikte een hoge voorwaartse stroomdichtheid van 9.19  $kA/cm^2$  bij 3 V en BV van 106 V. Een extreem hoge uitgangsstroom van 400 mA wordt verkregen wanneer het gedetecteerde vermogen 38.4 dBm bereikte bij 3 GHz in gepulseerde golfmodus.

Ten slotte worden alle onderzoeksinhouden die in dit proefschrift worden genoemd samengevat en worden de problemen aangegeven die verder moeten worden opgelost met lucubrate richting.

# 1

# Introduction

With the introduction of 5G, the modern RF (radio frequency) frontend module requires a high-performance device (transistor or diode), which can operate in a wide bandwidth and a high input power with easy integration and low cost. Today silicon devices have reached their physical limits either in terms of scaling down or in terms of their physical properties. Gallium nitride (GaN) has attracted increased attention because of superior material properties, such as high electron saturation velocity and high electrical field strength. Quasi-vertical GaN diodes have the advantages of withstanding a high reverse voltage without enlarging the device area, a high current density, reliable, and low cost, promising for high-power microwave applications. However, several issues limit the possibility of further improvement, including deep mesa etch, and reverse leakage suppression. Making efforts in device design and fabrication is essential to help quasi-vertical GaN diode reach an excellent performance in power microwave applications.

Parts of this chapter have been published in Electronics 324, 575 (2019) [1].

#### **1.1.** Background

W ith the popularity of fifth-generation (5G) mobile communication technology, the enhanced data transmission rate throughout the network delivers a much better experience with customers on the Internet. Fifth-generation base stations consume more power than 4G base stations, thus inevitably increasing the telcos energy costs. The data show that powering cellular base stations worldwide used nearly 1% of all global electricity in 2012 [2]. By 2020, the telecom industry even consumes 2% to 3% of total global energy. Consequently, improving the energy efficiency in 5G communication has become a hot topic in recent years.

In wireless networks, much of the energy is wasted by grossly inefficient electronic components and modules such as power amplifiers and rectifiers. In recent decades, wireless infrastructure systems have mainly employed Si devices such as a laterally diffused metal oxide semiconductor (LDMOS), which showed scant room for further improvement, as the silicon reached its theoretical limitations. The deployment of 5G requires more closely spaced wireless infrastructures with high-output power to deal with high-frequency signal attenuation issues [3]. Thus, with the introduction of 5G, the modern RF (radio frequency) frontend module requires a high-performance device (transistor or diode), which can operate in a wide bandwidth and a high input power with easy integration and low cost.

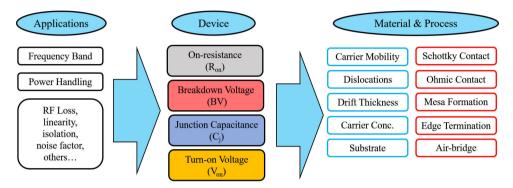

Microwave power limiters have been widely used in the RF frontend in a variety of wireless communication systems [4], such as cellular infrastructure (including 5G) and microwave radio communications [5]. A diode limiter circuit prevents the damage of sensitive receiver components by allowing RF signals below a certain threshold to pass through, but larger signals exceeding the threshold are attenuated [6]. This means that to develop a high-performance limiter, there are two goals: A very low conduction loss and a very high block voltage. Thus, the target for a limiter diode is to reach a low R<sub>on</sub>, a low capacitance, and a high BV toward meeting the above goals. Many studies have been carried out on Si-based diode limiters in recent years [7–9]; however, they showed scant room for further improvement as the silicon reached its theoretical limitations. they showed scant room for further improvement, as the silicon reached its theoretical limitations. Today, silicon devices have reached their physical limits either in terms of scaling down or in terms of their physical properties [10]. In this background, there is a need for new semiconductor materials to be satisfying the device requirements. From this perspective, there is a need for new semiconductor materials to satisfy the device requirements. Wide band-gap materials (e.g., gallium nitride) have recently attracted much interest, attributed to their superior material properties such as wide band-gap, high electron saturation velocity, and high critical electric field.

Table 1.1 shows the primary properties of GaN and Si. The critical electric field of GaN is 11 times higher than Si, which enables GaN RF devices to handle a higher reverse voltage. Both electric field and electron velocity are essential material properties for the requirements of a high-frequency power transistor. In 1991, Johnson derived a figure of merit JFOM, which characterizes the power frequency performance of transistors based on materials [11]. A higher JFOM means that GaN is more suitable for high-frequency power transistor applications and requirements

1

2

| Materials | $E_g$<br>(eV) | $\mu_n$ $(cm^2/V \cdot s)$ | E <sub>c</sub><br>(MV/cm) | V <sub>sat</sub><br>(10 <sup>7</sup> cm/s) | К<br>(W/m·K) | JFOM |

|-----------|---------------|----------------------------|---------------------------|--------------------------------------------|--------------|------|

| Si        | 1.12          | 1350                       | 0.3                       | 1                                          | 145          | 1    |

| GaN       | 3.44          | 1090 (bulk)<br>2000 (2DEG) | 3.3                       | 2.5                                        | 253          | 27.5 |

Table 1.1: Physical properties of Si and GaN

$E_g$ , energy band-gap;  $\mu_n$ , electron mobility;  $E_c$ , critical electric field;  $V_{sat}$ , electron saturation velocity; K, thermal conductivity;  $JFOM = (E_c * V_{sat})/(2\pi)$

than Si. Meanwhile, GaN has the superior material properties of high electron saturation velocity, high electrical field strength, and high operating temperature [12, 13], which is well suited for high-power microwave applications.

#### 1.2. GaN-based RF devices

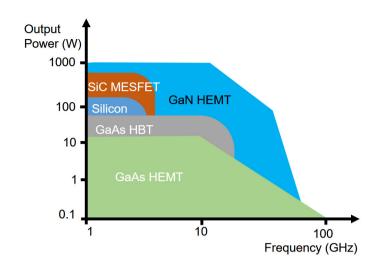

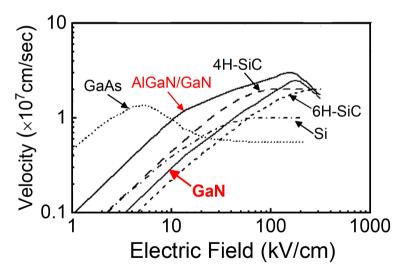

A RF power amplifier (PA) is an integral part of various wireless transmitters, which is located in the final active stage that drives the transmitting antenna. Figure1.1 compares the semiconductor technologies for RF devices in PA applications [14]. GaAs-based RF high-electron mobility transistor (HEMT) and heterojunction bipolar transistor (HBT) devices consistently dominate the RF PA market, especially in highfrequency applications. Si-based RF devices are competitive against GaAs devices in the low-frequency range due to the advantages of low-cost and large-sized silicon wafers. As GaN technologies ramp up, commercial GaN HEMT discrete power transistors can deliver very high-power density and are more suitable for deploying low-frequency RF PA applications. GaN-based MMICs are of more interest at higher frequencies, as they enable matching, system size reduction, and, eventually, cost efficiency.

A GaN-based lateral structure utilizes an AlGaN/GaN hetero-junction to form a two-dimensional electron gas (2DEG) conduction channel with the good features of a high carrier concentration (>  $10^{13}cm^{-3}$ ) and high carrier mobility ( $2000cm^2/V \cdot s$ ). This highlights a GaN HEMT as a most attractive lateral device and has been commercialized in power and RF electronic applications over the past few years. Moreover, lateral AlGaN/GaN SBD with extremely low turn-on voltage and low on-resistance is considered a rectifier, used in microwave power transmission applications [15–17].

The charge trapping effects induced by the interface states from the surface or GaN buffer layer are still the primary challenge in GaN heterojunction devices that will cause a significant drop in RF output power [18–23]. Many solutions have been presented to solve these problems, such as a passivation layer[24], field plate [25, 26], and tri-gate [27] structure. In spite of these efforts for making some progress in improving lateral GaN device performance, they are not reaching the GaN material limit as a result of requiring a high epitaxial layer quality and precise

1

4

Figure 1.1: Power-frequency diagram of application space for several semiconductor materials.

processing[28].

A vertical structure is a convenient solution in Si- or SiC-based devices, which are also an attractive alternative for GaN devices. Recent progress in vertical GaN transistors has mainly involved current-aperture vertical electron transistors (CAVETs)[29], trench MOSFETs[30], fin-channel MOSFETs[31], and fin-JFET [32]. A vertical diode has drawn more attention to the early exploratory research of GaNbased devices because of the more implementable device structure than vertical transistors. One of the advanced features of a vertical GaN device is withstanding a high reverse voltage without enlarging the device area. Thus, in previous research, most of the vertical GaN diode has been dedicated to high-voltage and high-power applications. Researchers are rarely concerned about vertical GaN devices for RF applications due to the lower carrier mobility of bulk GaN than the AlGaN/GaN 2DEG channel. However, with the rapid development of bulk GaN epilaver growth technology, the mobility of bulk GaN has increased to 1090  $cm^2/V \cdot s$  at room-temperature with a carrier concentration of  $\sim 2 \times 10^{16} \, cm^{-3}$  for n-GaN on an Si substrate [33], enabling a lower  $R_{on}$  and higher current density of vertical GaN devices than before. In addition, electrothermal simulation results indicate that using a vertical device structure effectively improves the peak operating temperature of GaN transistors to 150 °C with enhanced thermal performance [34]. Therefore, it is really worthwhile exploring vertical GaN devices that further expand the potential of GaN material in a high-power RF application.

#### **1.3.** Quasi-vertical GaN Schottky diodes

S ince the year 2000, GaN-based rectifiers (including Schottky barrier diodes (SBDs) and PN junction diodes) have attracted considerable interest from researchers.

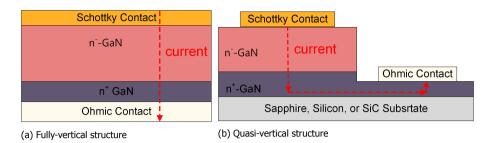

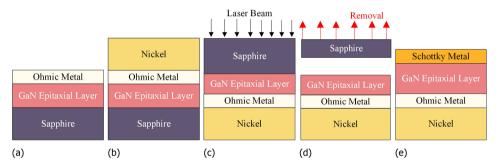

Figure 1.2: Gallium Nitride-based Schottky barrier diode (GaN SBD) structures and current flowing directions.

With the absence of minority carrier accumulation and low barrier height, SBDs can operate at higher frequencies with a lower turn-on voltage ( $V_{on}$ ) than PN junction diodes. Yoshimoto et al.[35] demonstrated the operation of a GaN SBD at a high frequency with a low power loss in the power converter, comparing it with a commercial Si fast recovery diode (FRD) and an SiC SBD via a typical E resonant rectifier tested at a frequency of 30 MHz.

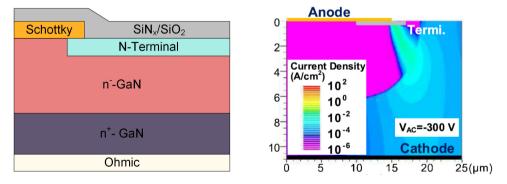

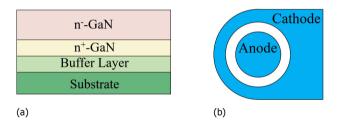

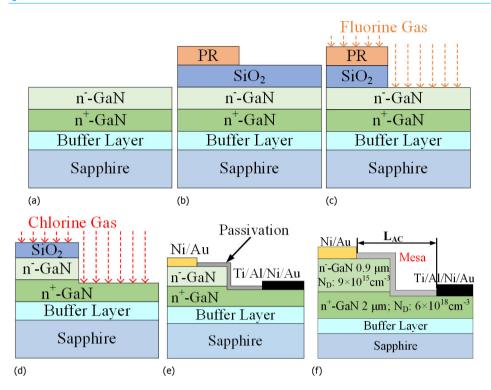

The schematic of a typical vertical GaN Schottky diode is shown in Figure1.2, including its quasi-vertical and fully vertical structure[1]. For the fully vertical structure, the electrodes are located on the two sides of the wafer separately, with current flowing from anode to cathode through the drift layer in a vertical direction, as shown in Figure1.2a. The fully vertical device has the advantages of an effective device size and good thermal performance by cooling from both sides of the wafer. However, the development of fully vertical GaN devices is limited by the expensive and small-sized homogeneous GaN substrate[36].

For the quasi-vertical structure, a mesa is processed and both the anode and cathode are located on the same side of the wafer, as shown in Figure1.2b. The first quasi-vertical GaN diodes were demonstrated on a sapphire substrate in 2000 [37] and on a silicon substrate in 2014 [38], separately. Quasi-vertical GaN devices have the freedom to select substrates (such as silicon, sapphire, or SiC) by using hetero-epitaxial growth technology. The planar structure design is easy to integrate with other RF components. Another advantage is compatible with the mature semiconductor manufacturing lines if grown on an Si substrate. Therefore, quasi-vertical structures are more promising than fully vertical structures for future GaN-based vertical devices.

## **1.4.** Problems and challenges

T o develop a quasi-vertical GaN-based Schottky diode for microwave power applications, we face several problems, split into the following three aspects:

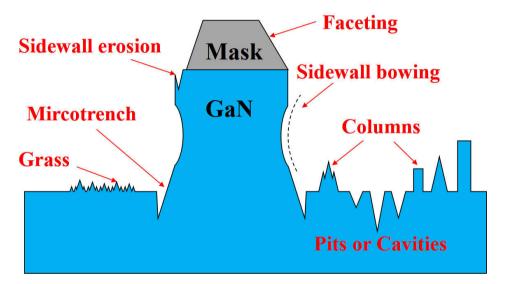

First, the formation of a GaN trench or mesa requires a deep etching technique with a highly anisotropic profile, possibly creating defects on the sidewall and etched surface. These etch defects mainly consist of sidewall erosion, grass on the surface, columns, pits or cavities, and microtrenches. The complicated GaN etching

process makes removing these defects difficult. Different to shallow etching in lateral GaN HEMT devices, deep trench etching technology is not mature and needs further development in vertical GaN devices. Although much effort has been made on GaN etching, some of the critical issues have not yet been solved. A mircotrench on the corner of etched mesa is the most critical defect in these unsolved issues, resulting in a significant leakage current and hiding an enormous risk for the reliability of high-power GaN diodes. A few works on SiC or Si etching have provided some thoughts for eliminating GaN microtrenches. However, due to the diversity of etching reaction mechanisms among semiconductors, it is challenging to effectively solve the microtrench problem in GaN mesa etching.

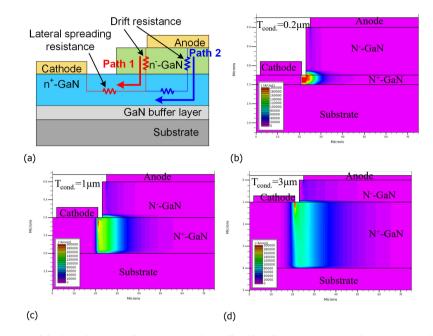

Second, the power handling of microwave diodes corresponds to the capability of conducting a maximum current and withstanding a peak reverse voltage. A higher  $R_{an}$  in a diode brings higher power consumption, thus generating more heat to burn out the device. The peak voltage of an RF signal is not allowed to exceed the BV of a diode, otherwise it will permanently destroy said diode. Therefore, diodes simultaneously require a low  $R_{on}$  and a high BV to reach high-power handling. However, a large reverse leakage current of the diode can cause pre-breakdown and reliability problems. Some works suggest that the leakage can be inhibited by using edge terminations[39], reducing the dislocation density of the drift layer[40], passivating the etched mesa [41], or reducing the interface defect density at the Schottky contact interface [42]. In general, the microwave GaN diode requires a small device area and a thin drift layer, which is sensitive to the damage or traps induced by etching or the plasma treatment processes. Therefore, it is essential to find an effective solution and analyze the mechanism of leakage suppression in a microwave power GaN diode more clearly. In addition, current-crowding effects (CCEs) strongly influence the forward characteristic of a guasi-vertical diode, which needs to be further optimized by a certain device structure design [43-45].

Third, silicon-based<sup>1</sup> and GaAs-based<sup>2</sup> microwave diodes have been demonstrated with a high frequency but limited with the input power by the low BV [46]. These diodes show scant room for further improvement, as the semiconductor material reached its theoretical limitations. GaN has a much higher electron velocity in the high electric field, leading to a higher BV and a higher current density of GaN diodes, achieving a high microwave power level. However, due to the limitations of high-quality GaN materials and obstacles of the heterojunction AlGaN/GaN structure, GaN-based high-power microwave diodes are still a gap in the market. The challenge is to design, fabricate, and characterize a vertical GaN Schottky diode for microwave applications with high power and a wide frequency band.

## 1.5. Aim and scope

T his dissertation aimed to develop a quasi-vertical GaN diode for high-power RF and microwave applications, which can operate in a wide frequency band and at high input power levels with easy integration and a low cost. The scope of this

6

<sup>&</sup>lt;sup>1</sup>BAT63-02V supplied by Infineon Technologies

<sup>&</sup>lt;sup>2</sup>MA4E1317 supplied by MACOM

dissertation involves three aspects:

- Design and fabrication of a quasi-vertical GaN device with mesa etching optimization;

- 2. Suppression of reverse leakage with an enhanced breakdown voltage;

- 3. Demonstration of microwave power applications (limiters and detectors) based on developed GaN diodes.

### **1.6.** Thesis outline

This thesis aimed to address the challenges listed above by developing a deep GaN trench etching technology and exploring the potential of quasi-vertical GaN diodes for high-power microwave applications. This research covered the device design and fabrication technology to circuit applications based on the simulation and experimental results. The rest of this thesis is organized into six chapters:

- In Chapter 2, we present the basic structure of the typical vertical Schottky diode and discuss the basic principles under both forward and reverse bias. A trade-off between *R*<sub>on,sp</sub> and BV is analyzed to characterize the performance of diodes. At once, the equivalent circuit model of a diode for studying the high-frequency properties is introduced. Then, we provide a literature summary for state-of-the-art vertical GaN SBDs. Finally, the benchmark for vertical GaN SBDs with different substrates (Si, sapphire, and GaN) and various edge terminal techniques are presented and discussed.

- In Chapter 3, the optimization of mesa etching for a quasi-vertical GaN SBD by inductively coupled plasma (ICP) etching is comprehensively investigated, including the selection of the etching mask, ICP power, radio frequency (RF) power, a ratio of mixed gas, flow rate, and chamber pressure. In particular, the microtrench on the bottom corner of the mesa sidewall was eliminated by optimizing the etch recipes. Finally, the mesa structure achieved a highly anisotropic profile by combining ICP dry etching and a tetramethylammonium hydroxide (TMAH) wet treatment. In addition, the proposed etching technique was not confined to fabricating a GaN mesa structure for quasi-vertical devices, also extended to other structures, such as hexagonal pyramids and nanowire arrays, promising for sensors, vertical transistors, optoelectronics, and photovoltaics.

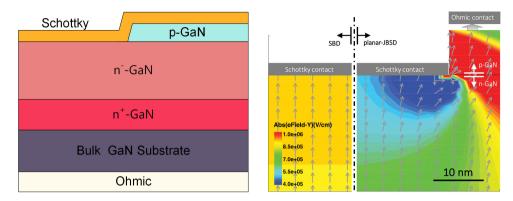

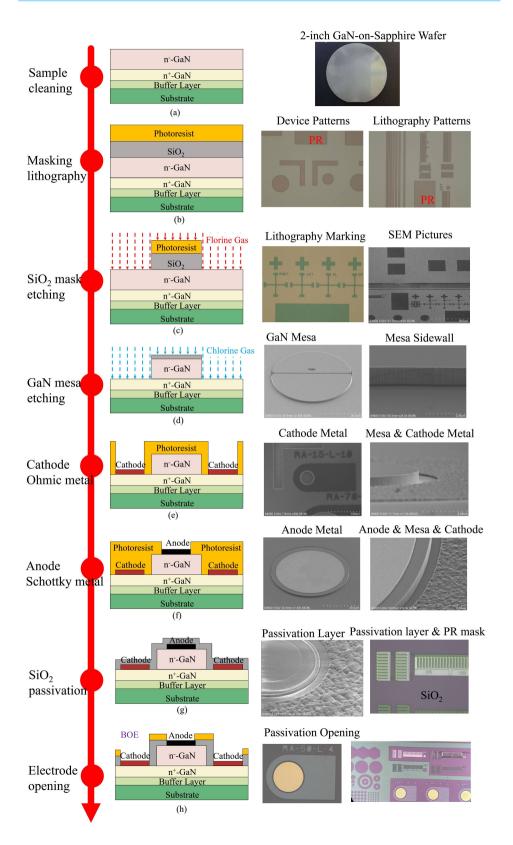

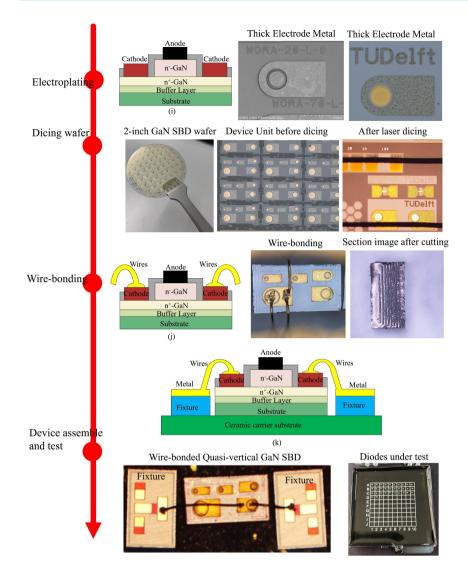

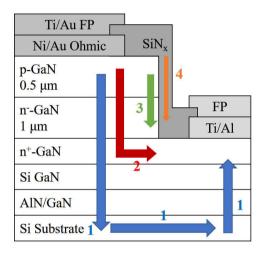

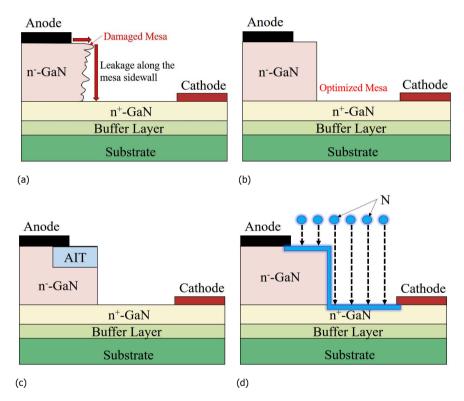

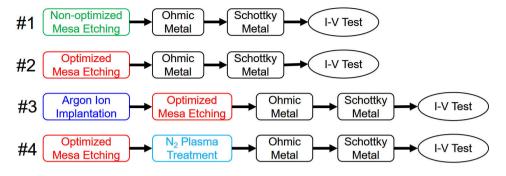

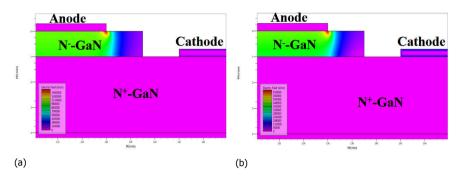

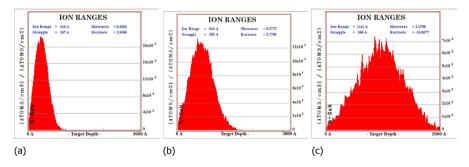

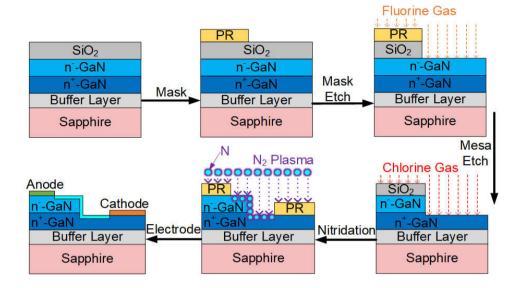

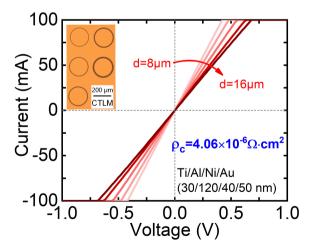

- In Chapter 4, the quasi-vertical GaN SBD is developed from the perspective of an epilayer structure design, device layout, device modeling, fabrication, and leakage suppression solutions. First, the design flow of quasi-vertical GaN diodes for microwave power applications is presented, including the device performance indicators, substrate selection, and device layout. Then, the quasi-vertical GaN SBD fabrication process is elaborated in schematic diagrams and real pictures. Finally, three solutions were developed to suppress the leakage current, including mesa optimization, argon ion terminations, and post-mesa nitridation.

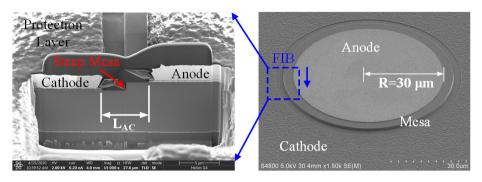

- In Chapter 5, we report the high-performance quasi-vertical GaN Schottky diode on a sapphire substrate and its application for high-power microwave

1

7

circuits. First, we report the first demonstration of an L-band high-power limiter based on our quasi-vertical GaN SBD in a real-life setting. By using steep-mesa technology, the spacing between the anode and cathode can be reduced to 2  $\mu m$ , leading to a further reduction in the on-resistance of the SBD. Second, we experimentally demonstrate a quasi-vertical GaN SBD with post-mesa nitridation for high-power and broadband microwave detection. The simulation of the designed circuit and the experimental results can be well corroborated in the circuit applications.

• Chapter 6 concludes the dissertation, summarizes the contributions, and discusses recommendations derived from the results for future research.

#### References

- Y. Sun, X. Kang, Y. Zheng, J. Lu, X. Tian, K. Wei, H. Wu, W. Wang, X. Liu, and G. Zhang, *Review of the recent progress on gan-based vertical power schottky barrier diodes (sbds)*, Electronics 8, 575 (2019).

- [2] Energy Efficiency: An Overview, Tech. Rep. (GSMA Future Networks, 2019).

- [3] M. Walker, *Operators facing power cost crunch*, Tech. Rep. (MTN Consulting, 2020).

- [4] J. F. White, *Microwave semiconductor engineering* (Springer Science & Business Media, 2012).

- [5] A. Sardi, F. Ö. Alkurt, V. Özkaner, M. Karaaslan, E. Ünal, and T. Mohamed, Investigation of microwave power limiter for industrial scientific medical band (ism) applications, International Journal of RF and Microwave Computer-Aided Engineering **30**, e22180 (2020).

- [6] G. Q. Fan, H. Y. Xing, and H. Q. Hu, K-ka band schottky diode limiter, in 2013 IEEE International Conference on Applied Superconductivity and Electromagnetic Devices (IEEE, 2013) pp. 160–162.

- [7] S.-S. Yang, T.-Y. Kim, D.-K. Kong, S.-S. Kim, and K.-W. Yeom, A novel analysis of a ku-band planar pin diode limiter, IEEE transactions on microwave theory and techniques 57, 1447 (2009).

- [8] H. Wang, H. Zou, Y. Zhou, and H. Li, *Electro-thermal coupled modeling of pin diode limiter used in high-power microwave effects simulation*, Journal of Electromagnetic Waves and Applications **29**, 615 (2015).

- [9] *Limiter Diodes*, Tech. Rep. (Skyworks, 2011).

- [10] G. Q. Zhang and A. Van Roosmalen, *More than Moore: creating high value micro/nanoelectronics systems* (Springer Science & Business Media, 2010).

- [11] E. O. Johnson, *Physical limitations on frequency and power parameters of transistors,* in *Semiconductor Devices: Pioneering Papers* (World Scientific, 1991) pp. 295–302.

- [12] U. K. Mishra, L. Shen, T. E. Kazior, and Y.-F. Wu, Gan-based rf power devices and amplifiers, Proceedings of the IEEE 96, 287 (2008).

- [13] S. Deng, C. Gao, S. Chen, J. Sun, and K. Wu, *Research on linearity improvement of silicon-based pin diode limiters*, IEEE Microwave and Wireless Components Letters **30**, 62 (2019).

- [14] S. Oliver, *Optimize a Power Scheme for these Transient Times*, Tech. Rep. (2014).

- [15] S. D. Joseph, S. S. H. Hsu, A. Alieldin, C. Song, Y. Liu, and Y. Huang, *High power wire bonded gan rectifier for wireless power transmission*, IEEE Access 8, 82035 (2020).

- [16] K. Dang, J. Zhang, H. Zhou, S. Huang, T. Zhang, Z. Bian, Y. Zhang, X. Wang, S. Zhao, K. Wei, and Y. Hao, A 5.8-ghz high-power and high-efficiency rectifier circuit with lateral gan schottky diode for wireless power transfer, IEEE Transactions on Power Electronics 35, 2247 (2020).

- [17] K. Dang, J. Zhang, H. Zhou, S. Yin, T. Zhang, J. Ning, Y. Zhang, Z. Bian, J. Chen, X. Duan, S. Zhao, and Y. Hao, *Lateral gan schottky barrier diode for wireless high-power transfer application with high rf/dc conversion efficiency: From circuit construction and device technologies to system demonstration*, IEEE Transactions on Industrial Electronics **67**, 6597 (2020).

- [18] Y. Zhang, A. Zubair, Z. Liu, M. Xiao, J. A. Perozek, Y. Ma, and T. Palacios, *Gan finfets and trigate devices for power and rf applications: review and perspective,* Semiconductor Science and Technology (2021), 10.1088/1361-6641/abde17.

- [19] W. Song, Z. Zheng, T. Chen, J. Wei, L. Yuan, and K. J. Chen, *Rf linearity enhancement of gan-on-si hemts with a closely coupled double-channel structure*, IEEE Electron Device Letters **42**, 1116 (2021).

- [20] D. S. Lee, Z. Liu, and T. Palacios, *Gan high electron mobility transistors for submillimeter wave applications*, Japanese Journal of Applied Physics **53**, 100212 (2014).

- [21] J. Liu, Y. Zhou, R. Chu, Y. Cai, K. J. Chen, and K. M. Lau, *Highly linear al/sub* 0.3/ga/sub 0.7/n-al/sub 0.05/ga/sub 0.95/n-gan composite-channel hemts, IEEE electron device letters 26, 145 (2005).

- [22] S. C. Binari, K. Ikossi, J. A. Roussos, W. Kruppa, D. Park, H. B. Dietrich, D. D. Koleske, A. E. Wickenden, and R. L. Henry, *Trapping effects and microwave power performance in algan/gan hemts*, IEEE Transactions on Electron Devices **48**, 465 (2001).

- [23] G. Meneghesso, G. Verzellesi, F. Danesin, F. Rampazzo, F. Zanon, A. Tazzoli, M. Meneghini, and E. Zanoni, *Reliability of gan high-electron-mobility transistors: State of the art and perspectives*, IEEE Transactions on Device and Materials Reliability **8**, 332 (2008).

9

- [24] S. Joglekar, M. Azize, E. J. Jones, D. Piedra, S. Gradečak, and T. Palacios, Impact of al2o3 passivation on algan/gan nanoribbon high-electron-mobility transistors, IEEE Transactions on Electron Devices 63, 318 (2015).

- [25] U. K. Mishra, L. Shen, T. E. Kazior, and W. Yi-Feng, Gan-based rf power devices and amplifiers, Proceedings of the IEEE 96, 287 (2008).

- [26] Y. F. Wu, A. Saxler, M. Moore, R. P. Smith, S. Sheppard, P. M. Chavarkar, T. Wisleder, U. K. Mishra, and P. Parikh, *30-w/mm gan hemts by field plate optimization*, IEEE Electron Device Letters **25**, 117 (2004).

- [27] Y. Ma, M. Xiao, Z. Du, X. Yan, K. Cheng, M. Clavel, M. K. Hudait, I. Kravchenko, H. Wang, and Y. Zhang, *Tri-gate gan junction hemt*, Applied Physics Letters **117**, 143506 (2020).

- [28] Y. Li, T.-F. Pu, X.-B. Li, Y.-R. Zhong, L.-A. Yang, S. Fujiwara, H. Kitahata, and J.-P. Ao, Gan schottky barrier diode-based wideband and medium-power microwave rectifier for wireless power transmission, IEEE Transactions on Electron Devices 67, 4123 (2020).

- [29] H. Nie, Q. Diduck, B. Alvarez, A. P. Edwards, B. M. Kayes, M. Zhang, G. Ye, T. Prunty, D. Bour, and I. C. Kizilyalli, *1.5-kv and 2.2-mΩ-cm2 vertical* gan transistors on bulk-gan substrates, IEEE Electron Device Letters **35**, 939 (2014).

- [30] T. Oka, T. Ina, Y. Ueno, and J. Nishii, Over 10a operation with switching characteristics of 1.2 kv-class vertical gan trench mosfets on a bulk gan substrate, in 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD) (IEEE, 2016) pp. 459–462.

- [31] Y. Zhang, M. Sun, D. Piedra, J. Hu, Z. Liu, Y. Lin, X. Gao, K. Shepard, and T. Palacios, 1200 v gan vertical fin power field-effect transistors, in 2017 IEEE International Electron Devices Meeting (IEDM) (IEEE, 2017) pp. 9–2.

- [32] J. Liu, M. Xiao, R. Zhang, S. Pidaparthi, H. Cui, A. Edwards, M. Craven, L. Baubutr, C. Drowley, and Y. Zhang, 1.2-kv vertical gan fin-jfets: Hightemperature characteristics and avalanche capability, IEEE Transactions on Electron Devices, 1 (2021).

- [33] J. Shen, X. Yang, H. Huang, D. Liu, Z. Cai, Z. Chen, C. Ma, F. Xu, L. Sang, X. Wang, et al., High-mobility n–gan drift layer grown on si substrates, Applied Physics Letters **118**, 222106 (2021).

- [34] Y. H. Zhang, M. Sun, Z. H. Liu, D. Piedra, H. S. Lee, F. Gao, T. Fujishima, and T. Palacios, *Electrothermal simulation and thermal performance study of gan vertical and lateral power transistors,* Ieee Transactions on Electron Devices 60, 2224 (2013).

- [35] M. Ueno, S. Yoshimoto, K. Ishihara, M. Okada, K. Sumiyoshi, H. Hirano, F. Mitsuhashi, Y. Yoshizumi, T. Ishizuka, and M. Kiyama, *Fast recovery performance* of vertical gan schottky barrier diodes on low-dislocation-density gan substrates, in 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC's (ISPSD) (IEEE, 2014) pp. 309–312.

- [36] J. Hu, Y. Zhang, M. Sun, D. Piedra, N. Chowdhury, and T. Palacios, *Materials and processing issues in vertical gan power electronics*, Materials Science in Semiconductor Processing **78**, 75 (2018).

- [37] G. T. Dang, A. P. Zhang, F. Ren, X. A. Cao, S. J. Pearton, H. Cho, J. Han, J. Chyi, C. Lee, C. Chuo, S. N. G. Chu, and R. G. Wilson, *High voltage gan schottky rectifiers*, IEEE Transactions on Electron Devices **47**, 692 (2000).