### Computer Engineering

Mekelweg 4, 2628 CD Delft The Netherlands http://ce.et.tudelft.nl/

# MSc THESIS

# Hardware Acceleration of BWA-MEM Genome Mapping Application

Phani Kiran

#### Abstract

CE-MS-2014

Next Generation Sequencing technologies have had a tremendous impact on our understanding of DNA and its role in living organisms. The cost of DNA sequencing has decreased drastically over the past decade, leading the way for personalised genomics. Sequencers provide millions of fragments of DNA (termed short reads), which have to be aligned aginst a reference genome to reconstruct the full information of the DNA molecule under study. Processing short reads requires large computational resources, with many specialised computing platforms now being used to accelerate software aligners. We take up the challenge of accelerating a well know sequence alignment tool called Burrows Wheeler aligner on the Convey Hybrid Computing platform, which has FPGAs as co-processors. The focus of the research is to accelerate the BWA-MEM algorithm of the Burrows Wheeler aligner on the Convey HC-2 platform. The implementation was carried out using the Vivado HLS tool. The architectures proposed are targeted to overcome the memory bottleneck of the application. Two architectures are proposed, the Base architecture and the Batch architecture meant to address the memory bottleneck. Simulations were performed for the intended platform and it was found that, the Batch architecture is 18% faster than the Base

architecture for reads with similar run time characteristics. The architectures provide possibilities of further pipelining and implementation of more cores, which is expected to provide better performance than the current implementation.

# Hardware Acceleration of BWA-MEM Genome Mapping Application

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

COMPUTER ENGINEERING

by

Phani Kiran born in Mysore, India

Computer Engineering

Department of Electrical Engineering

Faculty of Electrical Engineering, Mathematics and Computer Science

Delft University of Technology

# Hardware Acceleration of BWA-MEM Genome Mapping Application

#### by Phani Kiran

#### Abstract

Next Generation Sequencing technologies have had a tremendous impact on our understanding of DNA and its role in living organisms. The cost of DNA sequencing has decreased drastically over the past decade, leading the way for personalised genomics. Sequencers provide millions of fragments of DNA (termed short reads), which have to be aligned against a reference genome to reconstruct the full information of the DNA molecule under study. Processing short reads requires large computational resources, with many specialised computing platforms now being used to accelerate software aligners. We take up the challenge of accelerating a well know sequence alignment tool called Burrows Wheeler aligner on the Convey Hybrid Computing platform, which has FPGAs as co-processors. The focus of the research is to accelerate the BWA-MEM algorithm of the Burrows Wheeler aligner on the Convey HC-2 platform. The implementation was carried out using the Vivado HLS tool. The architectures proposed are targeted to overcome the memory bottleneck of the application. Two architectures are proposed, the Base architecture and the Batch architecture meant to address the memory bottleneck. Simulations were performed for the intended platform and it was found that, the Batch architecture is 18% faster than the Base architecture for reads with similar run time characteristics. The architectures provide possibilities of further pipelining and implementation of more cores, which is expected to provide better performance than the current implementation.

**Laboratory** : Computer Engineering

Codenumber : CE-MS-2014

Committee Members :

Advisor: Zaid Al-Ars, CE, TU Delft

Chairperson: Koen Bertels, CE, TU Delft

Member: Rene Van Leuken, CAS, TU Delft

Member: Vlad Mihai Sima, BlueBee, TU Delft

Dedicated to my grandmother

# Contents

| 1   Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\mathbf{Li}$ | st of | Figure  | es                                    | vii  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|---------|---------------------------------------|------|

| 1 Introduction         1.1 Thesis Objective         1.2 Thesis Organisation         2 Background         2.1 Next Generation Sequencing         2.2 Sequence Alignment         2.2.1 Exact Matching         2.2.2 Inexact Matching         2.3 Existing Aligners         2.3.1 Hash Table Index Aligners         2.3.2 BWT Index Aligners         2.4 Burrows Wheeler Aligner Tool         2.4.1 Burrows Wheeler Transform         2.4.2 FM index         2.4.3 FMD index         2.4.4 BWA-MEM         3 Related Work and Platform         3.1 Hardware Acceleration of BWA       1         3.2 Platform       1         3.2.1 Coprocessor       1         3.2.2 Memory Subsystem and Crossbar       1         3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2                                               | $\mathbf{Li}$ | st of | Tables  | S                                     | ix   |

| 1.1 Thesis Objective       1.2 Thesis Organisation         2 Background       2.1 Next Generation Sequencing         2.2 Sequence Alignment       2.2.1 Exact Matching         2.2.2 Inexact Matching       2.3.2 Existing Aligners         2.3 Existing Aligners       2.3.1 Hash Table Index Aligners         2.3.2 BWT Index Aligners       2.4.2 Burrows Wheeler Aligner Tool         2.4.1 Burrows Wheeler Transform       2.4.2 FM index         2.4.2 FM index       1         2.4.3 FMD index       1         2.4.4 BWA-MEM       1         3 Related Work and Platform       1         3.1 Hardware Acceleration of BWA       1         3.2 Platform       1         3.2.2 Memory Subsystem and Crossbar       1         3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2   | A             | cknov | wledge  | ements                                | xi   |

| 1.2 Background         2.1 Next Generation Sequencing         2.2 Sequence Alignment         2.2.1 Exact Matching         2.2.2 Inexact Matching         2.3 Existing Aligners         2.3.1 Hash Table Index Aligners         2.3.2 BWT Index Aligners         2.4 Burrows Wheeler Aligner Tool         2.4.1 Burrows Wheeler Transform         2.4.2 FM index         2.4.3 FMD index       1         2.4.4 BWA-MEM       1         3 Related Work and Platform       1         3.2 Platform       1         3.2.1 Coprocessor       1         3.2.2 Memory Subsystem and Crossbar       1         3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2                                                                                                                                | 1             | Intr  |         |                                       | 1    |

| 2.1 Next Generation Sequencing       2.2 Sequence Alignment         2.2.1 Exact Matching       2.2.1 Exact Matching         2.2.2 Inexact Matching       2.3 Existing Aligners         2.3 Existing Aligners       2.3.1 Hash Table Index Aligners         2.3.2 BWT Index Aligners       2.3.2 BWT Index Aligners         2.4 Burrows Wheeler Aligner Tool       2.4.1 Burrows Wheeler Transform         2.4.2 FM index       2.4.2 FM index         2.4.3 FMD index       1         2.4.4 BWA-MEM       1         3 Related Work and Platform       1         3.1 Hardware Acceleration of BWA       1         3.2 Platform       1         3.2.1 Coprocessor       1         3.2.2 Memory Subsystem and Crossbar       1         3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2 |               |       |         | <u>v</u>                              |      |

| 2.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2             | Bac   | kgroui  | nd                                    | 3    |

| 2.2.1       Exact Matching         2.2.2       Inexact Matching         2.3       Existing Aligners         2.3.1       Hash Table Index Aligners         2.3.2       BWT Index Aligners         2.4.2       Burrows Wheeler Aligner Tool         2.4.1       Burrows Wheeler Transform         2.4.2       FM index         2.4.3       FMD index         2.4.4       BWA-MEM         3       Related Work and Platform         3.1       Hardware Acceleration of BWA         3.2       Platform         3.2.1       Coprocessor         3.2.2       Memory Subsystem and Crossbar         3.2.3       Application Engines         3.2.4       Hybrid-core Globally Shared Memory         2         4       Tools, Application analysis and Methodology         4.1       Tools                                                                                                                                      |               | 2.1   | Next (  | Generation Sequencing                 | . 3  |

| 2.2.2 Inexact Matching         2.3 Existing Aligners         2.3.1 Hash Table Index Aligners         2.3.2 BWT Index Aligners         2.4 Burrows Wheeler Aligner Tool         2.4.1 Burrows Wheeler Transform         2.4.2 FM index         2.4.3 FMD index       1         2.4.4 BWA-MEM       1         3 Related Work and Platform       1         3.1 Hardware Acceleration of BWA       1         3.2 Platform       1         3.2.1 Coprocessor       1         3.2.2 Memory Subsystem and Crossbar       1         3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2                                                                                                                                                                                                         |               | 2.2   | Seque   | nce Alignment                         | . 4  |

| 2.3       Existing Aligners         2.3.1       Hash Table Index Aligners         2.3.2       BWT Index Aligners         2.4       Burrows Wheeler Aligner Tool         2.4.1       Burrows Wheeler Transform         2.4.2       FM index         2.4.3       FMD index         2.4.4       BWA-MEM         3       Related Work and Platform         3.1       Hardware Acceleration of BWA         3.2       Platform         3.2.1       Coprocessor         3.2.2       Memory Subsystem and Crossbar         3.2.3       Application Engines         3.2.4       Hybrid-core Globally Shared Memory         2         4       Tools, Application analysis and Methodology         4.1       Tools                                                                                                                                                                                                                |               |       | 2.2.1   | Exact Matching                        | . 4  |

| 2.3.1 Hash Table Index Aligners         2.3.2 BWT Index Aligners         2.4 Burrows Wheeler Aligner Tool         2.4.1 Burrows Wheeler Transform         2.4.2 FM index         2.4.3 FMD index       1         2.4.4 BWA-MEM       1         3 Related Work and Platform       1         3.1 Hardware Acceleration of BWA       1         3.2 Platform       1         3.2.1 Coprocessor       1         3.2.2 Memory Subsystem and Crossbar       1         3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2                                                                                                                                                                                                                                                                      |               |       | 2.2.2   | Inexact Matching                      | . 5  |

| 2.3.2 BWT Index Aligners         2.4 Burrows Wheeler Aligner Tool         2.4.1 Burrows Wheeler Transform         2.4.2 FM index         2.4.3 FMD index       1         2.4.4 BWA-MEM       1         3 Related Work and Platform       1         3.1 Hardware Acceleration of BWA       1         3.2 Platform       1         3.2.1 Coprocessor       1         3.2.2 Memory Subsystem and Crossbar       1         3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2                                                                                                                                                                                                                                                                                                              |               | 2.3   | Existin | ng Aligners                           | . 6  |

| 2.3.2 BWT Index Aligners         2.4 Burrows Wheeler Aligner Tool         2.4.1 Burrows Wheeler Transform         2.4.2 FM index         2.4.3 FMD index       1         2.4.4 BWA-MEM       1         3 Related Work and Platform       1         3.1 Hardware Acceleration of BWA       1         3.2 Platform       1         3.2.1 Coprocessor       1         3.2.2 Memory Subsystem and Crossbar       1         3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2                                                                                                                                                                                                                                                                                                              |               |       |         |                                       |      |

| 2.4       Burrows Wheeler Aligner Tool         2.4.1       Burrows Wheeler Transform         2.4.2       FM index         2.4.3       FMD index         2.4.4       BWA-MEM         3       Related Work and Platform         3.1       Hardware Acceleration of BWA         3.2       Platform         3.2.1       Coprocessor         3.2.2       Memory Subsystem and Crossbar         3.2.3       Application Engines         3.2.4       Hybrid-core Globally Shared Memory         2         4       Tools, Application analysis and Methodology         4.1       Tools                                                                                                                                                                                                                                                                                                                                         |               |       | 2.3.2   | 9                                     |      |

| 2.4.1       Burrows Wheeler Transform         2.4.2       FM index         2.4.3       FMD index         2.4.4       BWA-MEM         3       Related Work and Platform         3.1       Hardware Acceleration of BWA         3.2       Platform         3.2.1       Coprocessor         3.2.2       Memory Subsystem and Crossbar         3.2.3       Application Engines         3.2.4       Hybrid-core Globally Shared Memory         2         4       Tools, Application analysis and Methodology         4.1       Tools                                                                                                                                                                                                                                                                                                                                                                                        |               | 2.4   | Burro   | 9                                     |      |

| 2.4.2 FM index       1         2.4.3 FMD index       1         2.4.4 BWA-MEM       1         3 Related Work and Platform       1         3.1 Hardware Acceleration of BWA       1         3.2 Platform       1         3.2.1 Coprocessor       1         3.2.2 Memory Subsystem and Crossbar       1         3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2                                                                                                                                                                                                                                                                                                                                                                                                                        |               |       |         |                                       |      |

| 2.4.4 BWA-MEM       1         3 Related Work and Platform       1         3.1 Hardware Acceleration of BWA       1         3.2 Platform       1         3.2.1 Coprocessor       1         3.2.2 Memory Subsystem and Crossbar       1         3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |       | 2.4.2   |                                       |      |

| 2.4.4 BWA-MEM       1         3 Related Work and Platform       1         3.1 Hardware Acceleration of BWA       1         3.2 Platform       1         3.2.1 Coprocessor       1         3.2.2 Memory Subsystem and Crossbar       1         3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |       | 2.4.3   |                                       |      |

| 3.1 Hardware Acceleration of BWA       1         3.2 Platform       1         3.2.1 Coprocessor       1         3.2.2 Memory Subsystem and Crossbar       1         3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |       | _       |                                       |      |

| 3.2 Platform       1         3.2.1 Coprocessor       1         3.2.2 Memory Subsystem and Crossbar       1         3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3             | Rela  | ated W  | Vork and Platform                     | 17   |

| 3.2.1 Coprocessor       1         3.2.2 Memory Subsystem and Crossbar       1         3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               | 3.1   | Hardw   | ware Acceleration of BWA              | . 17 |

| 3.2.1 Coprocessor       1         3.2.2 Memory Subsystem and Crossbar       1         3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               | 3.2   | Platfo  | rm                                    | . 18 |

| 3.2.2 Memory Subsystem and Crossbar       1         3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |       |         |                                       |      |

| 3.2.3 Application Engines       1         3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |       | 3.2.2   |                                       |      |

| 3.2.4 Hybrid-core Globally Shared Memory       2         4 Tools, Application analysis and Methodology       2         4.1 Tools       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |       |         |                                       |      |

| 4.1 Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |       |         | ••                                    |      |

| 4.1 Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4             | Too   | ls, Ap  | plication analysis and Methodology    | 21   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |       |         | - 9                                   | . 21 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |       | 4.1.1   | Vivado HLS                            | . 21 |

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |       |         |                                       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |       |         |                                       |      |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |       |         | •                                     |      |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               | 4.2   |         | -                                     |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |       |         | · · · · · · · · · · · · · · · · · · · |      |

|    |       | 4.2.2 Code Instrumentation Results | 28         |

|----|-------|------------------------------------|------------|

|    | 4.3   | Methodology                        | 28         |

| 5  | Arc   | hitecture and Implementation       | 31         |

|    | 5.1   | Design Motivation                  | 31         |

|    | 5.2   | Porting to Vivado HLS              |            |

|    | 5.3   | Base Architecture                  |            |

|    |       | 5.3.1 Synthesis Results            |            |

|    | 5.4   | Batch Architecture                 |            |

|    |       | 5.4.1 Synthesis Results            |            |

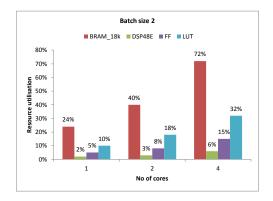

|    |       | 5.4.2 Scalability                  |            |

| 6  | Res   | ults                               | 41         |

|    | 6.1   | Methodology                        | 41         |

|    | 6.2   | Base Architecture Performance      |            |

|    | 6.3   | Batch Architecture Performance     |            |

|    | 6.4   | Pipelining                         |            |

| 7  | Con   | aclusions and Recommendations      | 47         |

|    | 7.1   | Conclusions                        | 47         |

|    | 7.2   | Recommendations for Future Work    | 48         |

| Bi | bliog | graphy                             | <b>5</b> 3 |

# List of Figures

| 2.1 | Comparison of computation costs against sequencing costs [1]            | 4  |

|-----|-------------------------------------------------------------------------|----|

| 2.2 | Alignment of query with reference without differences                   | 5  |

| 2.3 | Alignment of query with reference with mismatch                         | 5  |

| 2.4 | Alignment of query with reference with insertion                        | 6  |

| 2.5 | BWT transformation process                                              | 9  |

| 2.6 | FM index components                                                     | 10 |

| 2.7 | BWA-MEM algorithm [2]                                                   | 16 |

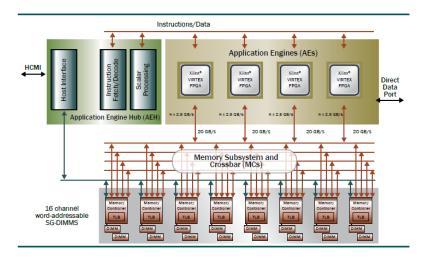

| 3.1 | Convey system architecture [3]                                          | 19 |

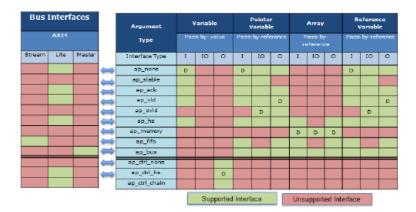

| 4.1 | Supported interfaces by Vivado HLS [4]                                  | 22 |

| 4.2 | BWA-MEM callgraph                                                       | 26 |

| 4.3 | BWT memory layout [5]                                                   | 27 |

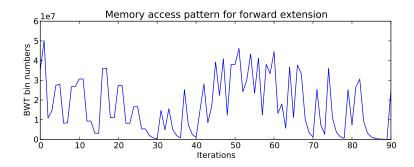

| 4.4 | Memory access pattern for finding a MEM                                 | 27 |

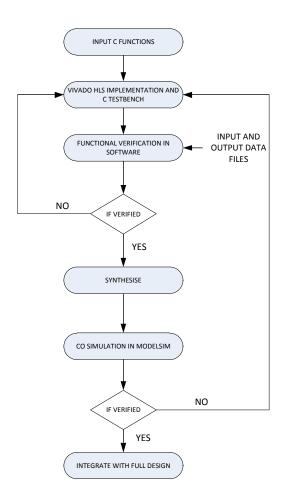

| 4.5 | Vivado HLS implementation methodology                                   | 29 |

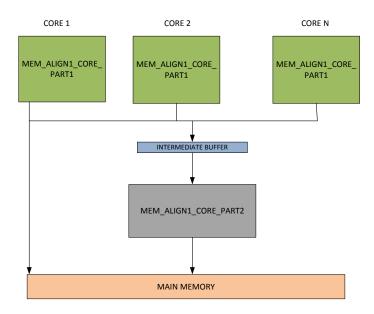

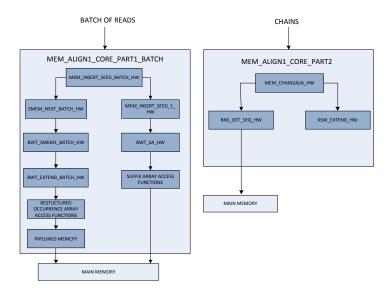

| 5.1 | Top level Base architecture                                             | 33 |

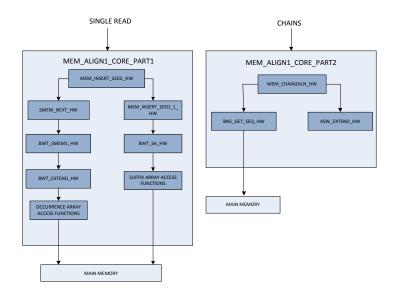

| 5.2 | Sub modules of Base architecture                                        | 34 |

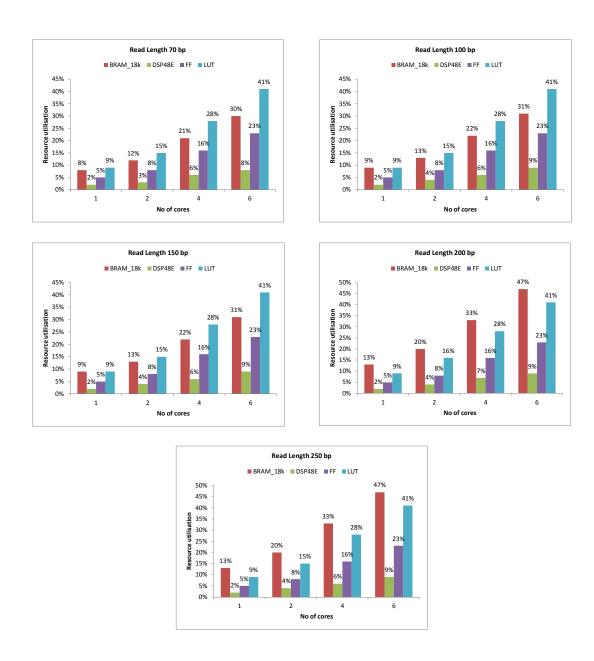

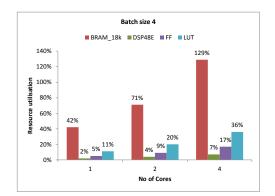

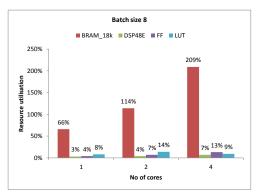

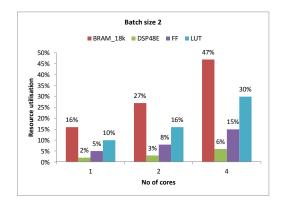

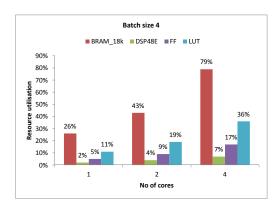

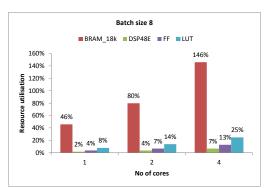

| 5.3 | Synthesis results for Batch architecture                                | 36 |

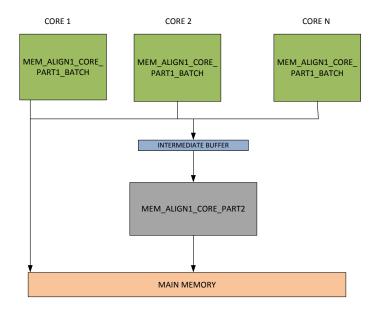

| 5.4 | Top level Batch architecture                                            | 37 |

| 5.5 | Sub modules of Batch architecture                                       | 37 |

| 5.6 | Synthesis results for Batch architecture at read coverage of $99.99\%$  | 39 |

| 5.7 | Synthesis results for Batch architecture at read coverage of $98.99\%$  | 40 |

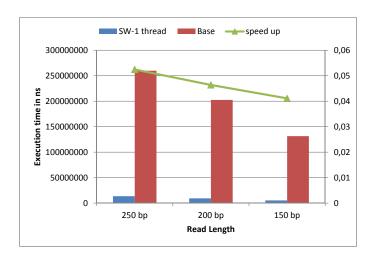

| 6.1 | Performance results of Base architecture                                | 42 |

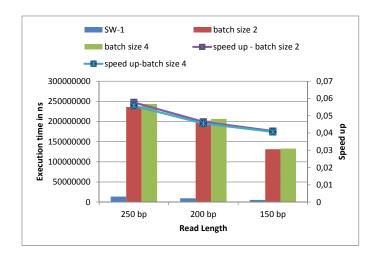

| 6.2 | Performance results of Batch architecture                               | 43 |

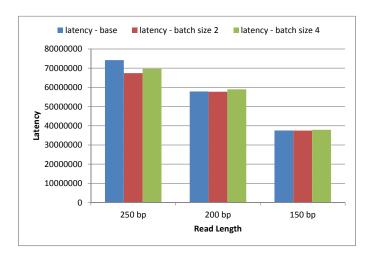

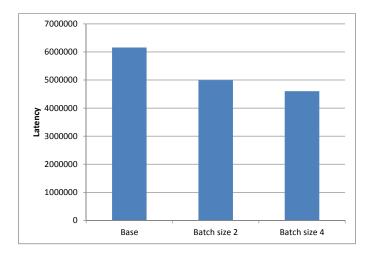

| 6.3 | Latency comparison of different batch sizes for Batch architecture      | 44 |

| 6.4 | Latency comparison of different batch sizes for Batch architecture with |    |

|     | the same read                                                           | 44 |

# List of Tables

| 3.1        | Comparison of different architectures proposed for BWA hardware acceleration         | 18 |

|------------|--------------------------------------------------------------------------------------|----|

| 4.1        | Profile results from aligning the synthetic reads against a fragment of human genome | 26 |

| 4.2        | Profile results from aligning the synthetic reads against the full human             |    |

| 4.3        | genome                                                                               |    |

| 5.1        | Resource utilisation on Virtex-6 LX760 FPGA for Convey modules                       | 35 |

| 6.1<br>6.2 | Hardware profile results for Base architecture                                       |    |

# Acknowledgements

Masters at TU Delft has been a humbling experience, where I have really had to reform my ways of going about learning. Now, when I am at the final step of my masters studies, I realise that this would not mean the end of my studies but rather, the beginning of the rest of my life as a student. Thanks to TU Delft and CE lab, for I have become a better student.

I would like to convey my gratitude to Dr Koen Bertels, for having provided me with the opportunity to work at BlueBee Multicore Technologies and making me feel part of the BlueBee family. I would also like to thank Dr Zaid Al-Ars, who has been my guide at every step through this experience. I would also like to thank him for providing valuable inputs in writing this document. Special thanks to Dr Vlad Mihai Sima and Giacomo Marchiori, for being my mentors and helping me throughout my thesis. Their ability and work ethic is certainly something I will continue to strive towards. I would also like to thank all the members of the BlueBee team for their support.

I would like to especially thank Adithya Pulli, who has been my friend and mentor, through my masters studies. I would also like to thank Sriram Adiga, for his continued support. Last but not the least, I would like to thank each and everyone of my friends here in Delft, who have been a necessary distraction away from studies. Finally, I would like to thank my family for having the faith in me to pursue studies away from home.

Phani Kiran Delft, The Netherlands October 8, 2014

Introduction

Understanding the structure of DNA molecule has been hailed by many, as the most important discovery of the past century. This has paved way towards treating hazardous diseases, as well as identification of genes that trigger major diseases. Advancement in genomic studies has had a tremendous impact on the medical research. This advancement has been largely been accredited towards sequencing technologies. DNA sequencing is used to determine the order of the nucleic acid molecules in the DNA fragment. The initial advancements in sequencing were made in the 1970s with Sanger sequencing dominating the domain, till much of the early 2000s.

In the past decade or so, there has been a tremendous improvement in sequencing technologies, with the cost of sequencing a base halving every five months, while the throughput per machine has increased 500,000 fold and the number of reads per genome increased about 100 fold [6]. This has put tremendous computational pressure on the next stage of DNA processing, which is sequence assembly. The millions of reads which are produced after sequencing, need to be assembled together to make sense out of such quantities of data. The process of assembly has hence proved to be a computational challenge, where millions of reads needs to be processed. Generally, a reference genome is used to map the reads generated from sequencers, which is termed short read alignment.

Many software aligner tools have been developed to address short read alignment problem. The computational complexity and the sheer amount of data that needs to be processed, makes sequence alignment, an interesting challenge in the high performance computing domain. Different platforms such as GPUs and FPGAs have been investigated by many researchers, to speed up the process of short read alignment. In this thesis, we take up such a challenge of investigating the the performance of BWA aligner tool on the Convey hybrid super computing system.

# 1.1 Thesis Objective

The BWA aligner tool, is a well known tool in the bioinformatics research community. BWA recently introduced an algorithm called BWA-MEM, which the authors claim to be better than their previous algorithms, at least for long read alignment [7]. The thesis aims for hardware acceleration of the application, on the CPU-FPGA hybrid Convey computing platform. The thesis aims to perform detailed analysis of the algorithm, identify the performance bottlenecks and aims to come up with solutions, to overcome those bottlenecks. The thesis also adopts Xilinx Vivado High Level Synthesis tool for the hardware implementation of the design, with an objective of increased productivity.

## 1.2 Thesis Organisation

The thesis has been organised into several chapters explaining the intrinsics of the application, identifying opportunities for acceleration, the tools and methodology used during the development process, the solutions and the results obtained from the implementation of those solutions.

In Chapter 2, the background of sequence alignment problem and existing software aligners are mentioned. Also the BWA-MEM application is explained in detail, with the intrinsics of the algorithms used.

In Chapter 3, work related to hardware acceleration of BWA tool by other researchers are described along with the introduction of the Convey computing platform.

In Chapter 4, the application performance is analysed on the target platform, bottlenecks and possible acceleration opportunities are identified. Also the various tools which were developed and used during the course of implementation are described, along with the development methodology followed.

In Chapter 5, the architecture and implementation of the designs are discussed in detail.

In Chapter 6, the results obtained are presented and discussed, with a view of further improvements.

Background

This chapter describes the impact of Next Generation Sequencing technologies in bioinformatics. Section 2.2 introduces the basic sequence alignment problem. We then describe the existing software aligners in section 2.3. Section 2.4 introduces the Burrows Wheeler aligner tool, also providing a detailed explanation of the BWA-MEM algorithm along with specialised data structures used such as FM index and FMD index.

### 2.1 Next Generation Sequencing

DNA sequencing, constitutes of generating data pertaining to the specific order of Adenine, Cytosine, Thymine and Guanine nucleic acid molecules in the strand of DNA. With the growth of sequencing technology, the information about DNA sequences is becoming indispensable to different aspects of biological research such as evolutionary biology, clinical biology, pathology and many more. Early efforts towards sequencing nucleic acids began around 1970s with Gilbert and Maxam [8], coming up with wandering spot analysis technique. In the mid 1970s, a more efficient and sophisticated technique was put forth by Sanger, considered ground breaking enough to be awarded a Nobel prize in Chemistry, 1980 [9].

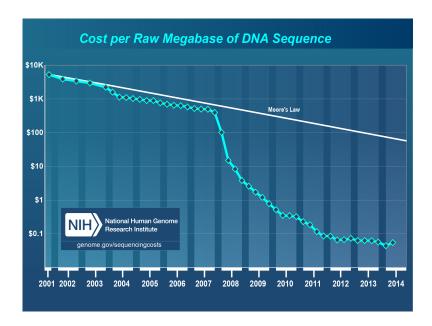

There has been a significant shift in the past decade, where the bioinformatics community has moved on from the traditional Sanger sequencing to what is now known as Next Generation Sequencing (NGS) or massively parallel sequencing [10]. The impact of NGS technologies has been rightly compared with the impact of personal computers on computing industry. The success of sequencing technology in the recent years, mirrors or even exceeds, that of the well known Moore's law in the computing industry. Figure 2.1 shows the decline of sequencing costs in the past decade against the computing costs predicted by Moore's law [1].

The impetus given by NGS technologies, led to a sanction of large number of ambitious projects such as The 1000 genomes project and, the more recently, \$1000 genome project. The \$1000 Genome project has now alleged to have achieved its objective with Illumina recently announcing to provide that service with its latest release of HiSeq X Ten sequencers [11]. The impact of NGS is touted to be immense on genomics and the trend now leading towards personalised genomics. The emergence of NGS has also brought about a fresh set of computational challenges. To meet these challenges, a new caveat of computational tools are being developed, more specifically towards sequence assembly and reconstruction of genomes. NGS technologies produce shorter reads(fragments of DNA) than Sanger sequencing, but generate a copious amount of data. A single run can produce upto 6 billion reads with the read length varying from 50-150 base pairs, compared to 30 million reads of length 500 bp by Sanger sequencing [12]. The primary requirement for these tools, is being able to map these large number of reads onto a high

Figure 2.1: Comparison of computation costs against sequencing costs [1].

quality reference genome.

### 2.2 Sequence Alignment

This section gives a brief description of sequence alignment and its various aspects which are relevant towards this thesis. The process of *mapping* the reads obtained, to their correct position on the reference genome is termed as sequence alignment. Genome assemblers are generally classified into two categories.

- De Novo Assembly: Assembles reads to create full length sequences by comparing each read against every other read obtained. As such, the naive complexity of the process is  $O(n^2)$  and requires a lot of memory and computation.

- Reference based Assembly: Assembles the reads obtained by comparing against a reference sequence and finding out the reads' approximate position on the reference. The complexity of the reference based assembly remains linear with O(n), since each read is compared against the constant reference.

To understand the process of mapping, few properties of the DNA sequence along with some features of the sequencing process itself need to be highlighted.

#### 2.2.1 Exact Matching

The problem of sequence mapping is a string matching problem, where we have millions of reads being matched against a reference sequence. Consider a reference sequence termed R, and a query sequence Q, as illustrated in Figure 2.2. The mapping of the query

sequence, Q, against R would be to find out the exact positions where the query would fit into the reference. The query Q is located at position 2 in the reference sequence. In this case, aligning the sequence Q against R is relatively simple, since we find a unique exact match of the sequence in the reference.

POSITION : 0 1 2 3 4 5 6 7

REFERENCE R : A G T G C C A C

QUERY Q : T G C

Figure 2.2: Alignment of query with reference without differences.

#### 2.2.2 Inexact Matching

However, there are a few problems introduced when we consider the practicalities of sequencing. Sequencing is error prone and sequence errors may be present in the process, which may cause some erroneous bases being introduced into the read. Also, mutations could be present in the DNA strand which is being sequenced and hence may be inherently different from the reference. These are the differences which we are interested in finding out, since they reveal the fundamental anomalies in the genetic make-up of the individual. These factors need to be considered when mapping the read to a reference strand.

Consider the original query sequence Q with the base pair 'G' being changed to 'A', either by process error or mutation, as shown in Figure 2.3. The mapping tool should still be able to point to the correct position on the reference strand. The term *mismatch* is used to denote such an occurrence. Hence, the mapping should allow mismatches to occur, to detect such conditions and still operate accurately. Such an alignment is termed *inexact matching* where mismatches are allowed for alignment.

POSITION : 0 1 2 3 4 5 6 7

REFERENCE R : A G T G C C A C

QUERY Q : T A C

MISMATCH : ↑

Figure 2.3: Alignment of query with reference with mismatch.

There is a possibility of one more such case, where inexact matching should be considered. The sequence Q, as shown in Figure 2.4 has an extra base being inserted during sequencing. If the mapping allows only one difference, the process would not be able to find the correct mapping. The extra base pair 'A' is actually considered an insertion to the read with respect to reference or a deletion from the reference in relation

to the read. The two terms are inter exchangeable and are commonly referred to as indels or gaps.

POSITION : 0 1 2 3 4 5 6 7

REFERENCE R : A G T G C C A C

QUERY Q : T G A C

INSERTION : ↑

Figure 2.4: Alignment of query with reference with insertion.

The quality of an alignment, therefore, is calculated based on a scoring system where mismatches, gaps and indels are penalised while matches are rewarded. For a given position a score is computed and the read with the best score is considered to be correct.

There are other constrictions on the problem as well, brought upon by the nature of the DNA sequence. These challenges posed by sequence mapping can be summarised as shown.

- The reference sequences are generally large and they themselves pose a huge burden on the computational resources available.

- Many short reads have to be aligned to the reference.

- The reads themselves have variations due to sequencing errors or mutations, which causes additional computational complexity.

- The DNA sequences themselves are very repetitive in nature. Nearly half of the human genome is found to be repetitive [12]. This creates ambiguities during the mapping process, and although it does not affect the mapping itself, it may lead to misinterpretation of results.

# 2.3 Existing Aligners

For simplicity, we consider in this section only the current software aligners which dont use any special execution platforms for their execution. Hatem et al provides a very comprehensive overview and comparison of the existing DNA short sequence aligners [13]. He broadly classifies the aligners based on the technique they use for index construction of the reference sequence. Index construction is the process of representing the reference sequence in a convenient way, for the benefit of the algorithm either in terms of speed or size. Before proceeding further, we describe here a set of features or terms, which are synonymous with alignment tools and these terms will be used henceforth in this thesis colloquially.

Seeding: Seeds are the first few base pairs of the reads, which are expected to contain less errors.

- Base quality scores: These scores give an indication towards the quality of base pair characters in the read. The quality score is -10\*log e where 'e' is the probability that the base is wrong [13].

- Paired end reads: These are reads which are produced from sequencing from both ends of the DNA strands. They are generally used to provide some degree of confidence in the mapping process since we can estimate the distance between 2 bases across the ends of the reads.

- SNP: Single Nucleotide Polymorphisms are the variations of single nucleotide between members of the same species and are not considered as mismatches during the mapping process.

Mapping tools are usually based on constructing an index for the reference sequence and using the index to map the short reads onto the reference. Based on the methodology used to construct the index, the tools has been broadly classified into two categories.

#### 2.3.1 Hash Table Index Aligners

These aligners construct hash tables either for the reads or the genome and use them to index the reference sequence in an efficient manner. The key of each entry of the table is a read or a subsequence of genome and the value is a list of positions where the reads/subsequences match. Tools based on hash table construction are described briefly below.

- **GSNAP** [14]: The hash tables are constructed for the genome and each read is divided further into subsequences. These are used to find the matching positions on the reference using the hashing technique. Finally all the positions for the subsequences are compiled together to find a final alignment.

- **Novoalign**: Novoalign is similar to GSNAP where the genome is hashed by overlapping oligomers and the reads are mapped to the reference using the hash tables.

- **FANGS** [15]: is also another genome hashing based mapping tool where it was specifically designed to handle long reads generated by 454 sequencer.

- MAQ [16]: is a read indexing tool where multiple hash tables are generated from the reads and the reference genome is matched against the multiple hash tables. It is different from the previously mentioned tools in that the reads are hashed as opposed to the reference genome.

#### 2.3.2 BWT Index Aligners

The following tools described use the Burrows Wheeler transform for index construction.

• **BWA**: Burrows Wheeler aligner is a siftware sequencer developed by Heng Li, which utilises BWT based index construction for reference sequences. Specialised data structures such as FM index and FMD index are used for efficient indexing of

reference. The latest algorithm employed by the tool called BWA-MEM is chosen for acceleration in this thesis.

- Bowtie [17]: The reference genome is transformed to FM index and the short reads are mapped against the FM index using the modified FM index searching algorithm proposed by Ferragina and Manzini [18]. There are two versions of the tool available Bowtie and Bowtie2, with the second version designed to handle longer reads.

- **SOAP2** [19]: is a unique tool in the sense it uses both BWT and hash tables to speed up the searches for mapping locations on the reference. It also utilises a split-read strategy to find the inexact searches on the genome.

### 2.4 Burrows Wheeler Aligner Tool

Burrows Wheeler Aligner Tool or BWA, is a software aligner designed to align low variant reads against reference genomes. Three algorithms are employed by BWA, namely, BWA-backtrack, BWA-SW and BWA-MEM. The first algorithm was exclusively designed for aligning short reads upto 100bp, while the latter two can handle read lengths upto mega bases. The author recommends the use of the BWA-MEM algorithm for the availability of latest features and performance enhancements compared to the former ones. The thesis, hence, concentrates on BWA-MEM algorithm and this section attempts to provide a detailed description of the fundamental concepts related to the BWA-MEM algorithm.

BWA, fundamentally, is a BWT index based aligner tool, which makes use of a special data structure called *FM index*, for improved accuracy and performance. BWA-MEM specifically uses an extension of the FM index termed FMD index. We proceed to describe briefly the BWT transform, FM index components and the newly introduced FMD index. We then explain the BWA-MEM algorithm and its components.

#### 2.4.1 Burrows Wheeler Transform

Burrows wheeler transform was first proposed in 1994, by M. Burrows and D.J. Wheeler, as a block sorting lossless data compression algorithm [20]. BWT rearranges the string into runs of similar characters and produces a transformation which is *reversible*. The reversibility of the transformation is a key property, which ensures, the data can be retrieved without any additional data being stored. The transformation is performed by producing all possible rotations of the string and sorting them in a lexicographical order.

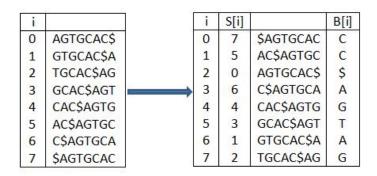

Consider the alphabet set  $\Sigma = \{\text{'A', 'C', 'G', 'T'}\}$ , which forms the base pairs of DNA. A special character termed '\$' is used to indicate the end of a string and also is lexicographically smaller than all the letters of the alphabet set. Consider a sample string G = "AGTGCAC". The special character '\$' is first inserted to produce the string "AGTGCAC\$". For the transformation, all rotations of the string are performed and placed in an array. Now the array has all possible suffixes of the string. Figure 2.5 shows the array with all possible suffixes on the right side table.

The array is then sorted in a lexicographical order to produce a sorted suffix array of the original string. The transformation now takes the last column of the sorted array, to

Figure 2.5: BWT transformation process.

generate the BWT string termed B. B is the Burrows Wheeler transform of the original string G.

#### 2.4.2 FM index

To search for a substring R = "GTG", we lookup the sorted suffix array for the character 'G' and by visual inspection, arrive at the interval [5,6] of the sorted suffix array table. We then proceed to the second character 'T' which narrows the interval to [6,6] which is where the substring lies. One more character 'G' is also considered, which results in the same interval. The suffix array value for the corresponding interval is found to be 1, which is the position of the substring being considered in the example.

Formally, the suffix array S, is a permutation of integers between 0 and |G|-1, where S[i] gives the position of the  $i^{th}$  smallest suffix of G. For a given string P, the suffix array interval or the SA interval, denoted as  $[I^l(P), I^u(P)]$ , gives the lower and upper bounds in the suffix array, within which bounds, P is found to be the suffix of G. The BWT string is computed as B[i] = G[S[i] - 1] for S[i] > 0 and B[i] = \$ otherwise.

This procedure is nothing but traversing through a suffix tree, where the tree is being represented by the sorted suffix array. The disadvantage of using a suffix tree is the memory footprint of the tree. For genomes the tree uses 15 bytes per base pair which results in more than 50GB of data [21]. Based on the BWT transformation, Ferragina and Manzini [18] proposed an algorithm to search the compressed string without completely decompressing it [21] using some additional data.

FM index of a reference string G, consists of the following components.

- **S**: the sorted suffix array

- **B**: the BWT array of the string, obtained as shown in section 2.4.1.

- **O**: the occurrence array, O[a,i], which is obtained by calculating the occurrence of character a in  $\Sigma$  upto  $i^{th}$  position of B, which is shown in Figure 2.6.

- C: the count array where C[a] denotes the number of characters in G which lexicographically smaller than a.

|             |      |      | O[a,i] |       |   |   |

|-------------|------|------|--------|-------|---|---|

| i           | S[i] | B[i] | Α      | С     | G | Т |

| 0           | 7    | С    | 0      | 1     | 0 | 0 |

| 1           | 5    | C    | 0      | 2     | 0 | 0 |

| 2 3         | 0    | \$   | 0      | 2     | 0 | 0 |

| 3           | 6    | Α    | 1      | 2     | 0 | 0 |

| 4           | 4    | G    | 1      | 2     | 1 | 0 |

| 4<br>5<br>6 | 3    | Т    | 1      | 2 2 2 | 1 | 1 |

| 6           | 1    | Α    | 2      | 2     | 1 | 1 |

| 7           | 2    | G    | 2      | 2     | 2 | 1 |

| C[a]        |      | 0    | 2      | 4     | 6 |   |

Figure 2.6: FM index components.

#### 2.4.2.1 Exact Matching using FM index

Using the components of the FM index, an exact match of a substring can be obtained in minimal time, by utilising a key property of FM index.

$$I^{l}[aP] = C[a] + O[a, I^{l}[P] - 1]$$

(2.1)

$$I^{u}[aP] = C[a] + O[a, I^{u}[P]] - 1$$

(2.2)

$$I^{s}[P] = I^{u}[P] - I^{l}[P] + 1$$

(2.3)

The equations 2.1 and 2.2 can be used iteratively, to provide for backward search of a substring on a reference string. The equations are applied until  $I^{I}[P] < I^{u}[P]$ , which represents a valid interval in the suffix array.

Algorithm 1: Exact matching using FM index [21]

### Function EXACTMATCH(R, C, O) begin

```

\begin{split} i &\leftarrow |R| - 1 \\ k &\leftarrow 0 \\ l &\leftarrow |G| - 1; \\ \mathbf{while} \ k \leq l \cap i \geq 0 \ \mathbf{do} \\ \sigma &\leftarrow R[i] \\ k &\leftarrow C[\sigma] + O[\sigma, k - 1] + 1; \\ l &\leftarrow C[\sigma] + O[\sigma, l]; \\ i &\leftarrow i - 1; \end{split}

```

```

egin{aligned} & \mathbf{end} \ \mathbf{while} \ & \mathbf{if} \ k \leq l \ \mathbf{then} \ & \mathbf{return} \ k, l \ & \mathbf{else} \ & \mathbf{return} \ \phi \ & \mathbf{end} \ \mathbf{if} \ & \mathbf{end} \ \mathbf{function} \end{aligned}

```

The algorithm shown above, provides the details for the backward search procedure. The algorithm makes use of the equations above to back extend the string, with the last character of the string being considered first. The interval is first initialised to [0, |G|-1], and above equations are applied iteratively, by performing one back extension at a time. The procedure is continued until there is a valid interval present for each extension or when the entire string is covered by back extension. One useful property of the algorithm is that, it has a linear time complexity dependent on the length of the read. It does not depend on the size of the reference sequence, which is extremely advantageous for sequence alignment.

#### 2.4.2.2 Memory Optimisation

The memory footprint of FM index is still a concern since, the occurrence array alone can occupy upto GBs of size when stored as 32-bit data format [21]. Li and Durbin [22] managed to devise methods to reduce the memory footprints of the data structures drastically, without the need for further compressing the structures. Li and Durbin proposed to store only part of the Suffix and Occurrence arrays in memory, and calculate the rest on the fly. The occurrence array, O[a,i], is stored in the memory only for i being a factor of 128. To calculate the actual occurrence value for particular character and index, the number of occurrences of the character in the BWT string B, from the previously stored 128 factor boundary, is counted upto the current index.

A similar technique, proposed by Grossi and Vitter [23], is used to reduce the footprint of the Suffix array in memory. An inverse compressed suffix array is used, along with Occurrence array and B, to calculate the suffix array. The actual relation is however out of scope for the thesis. S[i], for i being a factor of 32, will be stored in memory in this case. These optimisations result in a significant reduction in memory usage, with approximately n bytes used for a genome of size n, when genomes are less than 4Gb.

#### 2.4.3 FMD index

When the DNA molecule is sequenced, the read can be taken from either the forward or the reverse strand. With FM index, the matching of reads has to be performed multiple times, to check whether the read actually belongs to the forward or the reverse strand and also to verify if the complemented read can map onto the reverse complemented strand. Initially, BWA performed the complemented read search on FM index and hence reverse reference also had to be included. Li et al [24] proposed to incorporate few modifications to the FM index structure to ease the matching of complemented reads and the use of

reverse reference strands. The new data structure is termed FMD index and is used in BWA-MEM, the application under consideration for this thesis.

FMD index is calculated by concatenating the reference sequence by its reverse complement and calculating the FM index for the combined sequence. For example, considering our previous example of G = "AGTGCAC", the reverse complement of the sequence would be G' = "GTGCACT". G and G' are concatenated to obtain one single sequence, G'' = "AGTGCACGTGCACT", and FM index is now calculated on the new sequence. This provides the possibility of matching the read against the forward and reverse strands in a more effective way. FMD index exhibits the useful property of symmetry and bi-directionality.

#### 2.4.3.1 Exact matching using FMD index

The exact search makes use of the symmetry of FMD index. Bi-interval of a substring P, is used instead of the suffix array interval of FM index. The Bi-interval of a string P is denoted as  $[I^l(P), I^l(\bar{P}), I^s(P)]$ , the meaning of which will be explained shortly.  $I^l(P)$ , holds the same meaning as it did with FM index, and provides the lower boundary of P to be the suffix of G in the suffix array. The relation for  $I^s(P)$  is shown in equation 2.3.  $I^l(P)$  and  $I^s(P)$ , essentially provide the same functionality as the SA interval of FM index.  $I^l(\bar{P})$ ,however, is simply the lower boundary of the complemented read in the suffix array. When dealing with  $\bar{P}$ , we note that  $\bar{a}P = \bar{P} \not o \bar{a}$ , where  $o o o o contains and due to this symmetry, <math>I^s(P) = I^s(\bar{P})$ . This allows for  $I^l(\bar{P})$  and  $I^s(P)$ , together, to provide the SA interval for the complemented read in the suffix array.

#### **Algorithm 2**: Backward extension [24]

```

Output: Bi-interval of string aP

Function Backward Ext([k, l, s],a) begin

for b \leftarrow 0 to 5 do

k_b \leftarrow C(b) + O(b, k - 1)

s_b \leftarrow O(b, k + s - 1) - O(b, k - 1)

l_0 \leftarrow l;

l_4 \leftarrow l_0 + s_0;

for b \leftarrow 3 to 1 do

l_b \leftarrow l_{b+1} + s_{b+1}

l_5 \leftarrow l_1 + s_1;

return [k_a, l_a, s_a]

```

**Input**: Bi-interval [k, l, s] of string P and a symbol a

The authors propose that backward extension of P would result in forward extension of  $\bar{P}$  and forward extension of P, would mean backward extending  $\bar{P}$ . Just like the algorithm for exact matching with FM index which uses backward extension, the algorithms shown below provides for the backward and forward extension for calculating bi-intervals and exact matches.

#### **Algorithm 3**: Forward extension [24]

```

Input: Bi-interval [k, l, s] of string W and a symbol a

Output: Bi-interval of string Wa

Function FORWARDEXT([k, l, s],a) begin

[l', k', s'] \leftarrow \text{BACKWARDEXT}([l, k, s], \bar{a});

return [k', l', s']

```

#### 2.4.4 BWA-MEM

BWA-MEM [7] is the latest algorithm released by the authors of BWA alignment tool. As NGS technologies grow, the reads are not short any more, and especially for 100bp or more it becomes necessary for the algorithm to remain robust to sequencing errors. Many short read alignment tools are not very suited for these kind of reads. BWA-MEM is designed for efficient long read alignment, with the length of the reads ranging from 70bp to few megabases. The section describes BWA-MEM algorithm components in detail.

#### 2.4.4.1 Super Maximal Exact Matches

Maximal Exact Match (MEM) is an exact match that cannot be extended in either forward or backward direction. Super Maximal Exact Matches (SMEM) are the MEMs which are not found in other MEMs. BWA-MEM requires that, at any query position, the longest exact match covering the position must be a SMEM. SMEMs are found very quickly using the FMD index and the related backward-forward extension algorithms. The algorithm for finding out the SMEMs present in the query is shown below.

#### Algorithm 5: Finding SMEMs [24]

```

Input: String P and start position i_0; P[-1] = 0

Output: Set of bi-intervals of SMEMs overlapping i_0

Function SuperMEM1(P, i_0) begin

Initialize Curr, Prev and Match as empty arrays;

[k, l, s] \leftarrow [C(P[i_0]), C(\overline{P[i_0]}), C(P[i_0] + 1) - C(P[i_0])];

for i \leftarrow i_0 + 1 to |P| do

if i = |P| then

Append [k, l, s] to Curr

else

[k', l', s'] \leftarrow \text{Forwardext}([k, l, s], P[i]);

if s' \neq s then

Append [k, l, s] to Curr

if s' = 0 then

break;

```

```

[k,l,s] \leftarrow [k',l',s']

Swap array Curr and Prev;

i' \leftarrow |P|;

for i \leftarrow i_0 - 1 to -1 do

Reset Curr to empty;

s'' \leftarrow -1:

for [k, l, s] in Prev do

[k', l', s'] \leftarrow \text{BACKWARDEXT}([k, l, s], P[i]);

if s' = 0 or i = -1 then

if Curr is empty and i+1 < i'+1 then

i' \leftarrow i;

Append [k, l, s] to Match

if s' \neq 0 and s' \neq s'' then

s'' \leftarrow s':

Append [k, l, s] to Curr

if Curr is empty then

break

Swap Curr and Prev;

return Match

```

BWA-MEM uses the traditional seed-and-extend paradigm and SMEMs, found from the above algorithm, are used to seed an alignment. Seeds are parts of the reads used initially, to evaluate an alignment. Sometimes, SMEMs are not present in true alignments. To reduce the mismappings caused by this, re-seeding is performed, where, suppose we have an SMEM of length l with k occurrences in the reference. If l is too large, re-seeding is performed with longest exact matches covering the middle base of the SMEM, with at least k+1 occurrences. Such seeds can be found with minor modification to the SMEM finding algorithm.

#### 2.4.4.2 Chaining and chain filtering

The seeds obtained from the above procedure are than sent through a procedure of *chaining*. Groups of seeds which are close to each other and co-linear are termed *chains*. The chains are then filtered out based on the chain lengths, the shorter chains being removed, and whether they are contained in any of the other longer chains. Chain filtering proves to reduce unsuccessful seed extensions later on.

#### 2.4.4.3 Seed extension

Extension with banded dynamic programming (DP) is performed against a ranked list of seeds. Prior to extension, the seeds are first ranked based on the chain length and then by the seed length. Each seed, from best ranked to the worst, is checked if it is present in another alignment and if not, is extended with banded dynamic programming. Banded dynamic programming is implemented as a SSE2 based Smith-Waterman algorithm proposed by Farrar[25]. A couple of heuristics are applied during the extension phase of the algorithm.

- Banded DP may align through bad intermediate regions if the flanking alignment scores are high. Z-dropoff heuristic is employed to overcome this, where the alignment is stopped if the score drops below certain threshold from the best score. The Z-dropoff is similar to X-dropoff, except when it comes to long gaps, where the Z-dropoff does not penalise long gaps present in reference or query.

- BWA-MEM keeps record of the best alignment score reaching the end of query. If the difference between the end alignment score and local alignment score is below a certain threshold, the local alignment is dropped even if it has the higher score, there by giving a bonus to the extension reaching the end.

The BWA-MEM algorithm can be summarised as shown in Figure 2.7.

This section was mainly concerned with the algorithmic aspects of the application. BWA-MEM presents an interesting opportunity for acceleration, since the sheer amount of data involved is large and the application does not fit into any straight forward acceleration paradigm. We perform further analysis on the practical implementation of BWA-MEM, profile the application and deduce relevant information required, for any kind of acceleration opportunities which can be exploited.

Figure 2.7: BWA-MEM algorithm [2].

Related Work and Platform

Previous chapter introduced the sequence alignment problem and BWA-MEM algorithm. We proceed to study the research works from several authors related to acceleration of sequence alignment algorithm. To satisfy the ever growing demands from the application, wide variety of platforms have been used to obtain performance gains from multi cores, GPUs to FPGAs. Of all these parallel platforms, FPGAs provide the maximum flexibility in design space. Hence we restrict ourselves specifically to implementations of alignment tools on FPGA platforms.

#### 3.1 Hardware Acceleration of BWA

The works, described in this section, address different algorithms of the BWA tool as well as different aspects of those algorithms. The first implementation of BWT based string matching on FPGA was proposed in [26]. The paper discusses, BWT generation as well as exact matching of string patterns on FPGA. It also proposes an architecture for exact matching using FM-index, with the FM-index components stored on FPGA itself. This increases the resource utilisation, with majority of resources allocated for FM-index storage. For a pattern length of range 36 to 108, speedup of upto 196 is reported, when compared with Bowtie software tool.

Xin et al [27], proposes a complete solution including exact and inexact matching for FM-index on hardware. Although, Fernandez et al [26], developed a simple and effective architecture, it does not cover the inexact matching paradigm. Computational complexity and resource utilisation increases exponentially for inexact matching when compared to exact matching. [27] was able to develop architectures for the exact matching algorithm, shown in section 2.4.2.1, as well as the inexact matching algorithm of [22]. For the case of inexact matching, it proposes the use of hierarchical tables instead of prefix tries. The architecture proposed is quite complex with a fair amount of resource usage. Another key factor of their design is that, they only concentrate on SA interval calculation rather than the entire alignment process. With read lengths of around 70 bp, the performance was comparable with CPU platforms with speedups in the range of 1-2.