# Low-Power Receive-Electronics for a Miniature 3D Ultrasound Probe

# Low-Power Receive-Electronics for a Miniature 3D Ultrasound Probe

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor

aan de Technische Universiteit Delft,

op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben

voorzitter van het College voor Promoties,

in het openbaar te verdedigen

op maandag 2 april 2012 om 12:30 uur

door

#### Zili YU

Master of Science in Electrical Engineering geboren te Hangzhou, Zhejiang Province, P.R. China

Dit proefschrift is goedgekeurd door de promotoren:

Prof. dr. ir. G.C.M. Meijer

Prof. dr. ir. N. de Jong

#### Copromotor

Dr. ir. M.A.P. Pertijs

#### Samenstelling promotiecommissie:

Rector Magnificus voorzitter

Prof. dr. ir. G.C.M. Meijer Technische Universiteit Delft, promotor

Prof. dr. ir. N. de Jong Erasmus Universiteit Rotterdam, promotor

Dr. ir. M.A.P. Pertijs Technische Universiteit Delft, copromotor

Prof. dr. E. Charbon Technische Universiteit Delft

Prof. dr. ir. R. Dekker Technische Universiteit Delft

Prof. dr. L.K. Nanver Technische Universiteit Delft

Dr. C.T. Lancée Erasmus Universiteit Rotterdam/CTLTC

Prof. dr. K.A.A. Makinwa Technische Universiteit Delft, reservelid

Printed by Ipskamp Drukkers B.V., Enschede, The Netherlands.

ISBN: 978-94-6191-213-8

Financial support for the printing of this thesis was kindly provided by:

- TU Delft

- Oldelft Ultrasound B.V.

This thesis work is supported by Oldelft Ultrasound B.V., and Dutch Ministry of Economic Affairs in the framework of the program PIEKEN in de Delta, aanloopjaar 2006, project (name): "Het Hart in Drie Dimensies".

Copyright © 2012 by Zili YU

Cover design: Shubin Zheng

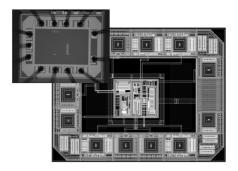

Cover chip photo: Zu-yao Chang

All rights reserved. No part of this publication may be reproduced or distributed in any form or by any other means, or stored in a database or retrieval system, without the prior written permission of the author.

To my parents and Shubin

In memory of my grandparents

# **Table of Contents**

| T | able o | f Contents                                                     | I  |

|---|--------|----------------------------------------------------------------|----|

| 1 | Int    | roduction                                                      | 1  |

|   | 1.1    | Trans-Esophageal Echocardiography (TEE) Basics                 | 2  |

|   | 1.2    | Design Challenges and Choices in 3D TEE                        | 8  |

|   | 1.3    | Objective and Chosen Approaches                                | 11 |

|   | 1.4    | Thesis Organization                                            | 12 |

|   | 1.5    | References                                                     | 14 |

| 2 | Ult    | rasound Transducers                                            | 17 |

|   | 2.1    | A Short Introduction to Piezoelectric Ultrasound Transducers . | 18 |

|   | 2.1    | 1 Piezoelectric Effect                                         | 18 |

|   | 2.1    | 2 Device Structure                                             | 19 |

|   | 2.1    | 3 Electrical Impedance Model                                   | 20 |

|   | 2.1    | 4 Transducer Arrays and Beamforming                            | 22 |

|   | 2.1    | 5 Transducer Resolution                                        | 23 |

|   | 2.2    | Characteristics of Ultrasound Signals                          | 25 |

|   | 2.2    | 1 Reflection and the Time-of-Flight (ToF) Principle            | 25 |

|   | 2.2    | 2 Propagation Attenuation                                      | 26 |

|   | 2.2    | 3 Dynamic Range of the Received Signal                         | 27 |

|   | 2.2    | 4 Signal Distortion and Harmonic Generation                    | 28 |

|   | 2.3    | Matrix Transducer for 3D TEE                                   | 29 |

|   | 2.3    | 1 Transducer Configuration for 3D TEE                          | 29 |

|   | 2.3    | 2 Characteristics of the Rx Transducer                         | 31 |

|   | 2.3    | Requirements for Interconnection and Rx Electronics            | 37 |

|   | 2.4    | Conclusions                                                    | 39 |

|   | 2.5 | Referen   | ces                                                | 39  |

|---|-----|-----------|----------------------------------------------------|-----|

| 3 | F   | ront-End  | Receive-Signal Processing for 3D TEE               | 43  |

|   | 3.1 | Archited  | cture of the Receive-Signal Processing             | 44  |

|   | 3.2 | Simplifi  | cations in the Front-End Signal Processing Scheme  | 47  |

|   | 3.  | 2.1       | Time-Gain-Compensation Scheme                      | 47  |

|   | 3.  | 2.2       | Micro-Beamforming Scheme                           | 49  |

|   |     | 3.2.2.1   | Principle                                          | 49  |

|   |     | 3.2.2.2   | Performance Evaluation by Acoustic Simulation      | 50  |

|   |     | 3.2.2.3   | Requirements for Delay Ranges                      | 54  |

|   | 3.3 | Front-E   | nd Receive ASIC Design Overview                    | 57  |

|   | 3.4 | Conclus   | ions                                               | 58  |

|   | 3.5 | Referen   | ces                                                | 59  |

| 4 | L   | NA and    | ΓGC Amplifier Designs                              | 61  |

|   | 4.1 | Design 1  | Requirements and Choices                           | 61  |

|   | 4.2 | Design    | of the Low-Noise Amplifier (LNA)                   | 64  |

|   | 4.  | 2.1       | Target Specifications of the LNA                   | 64  |

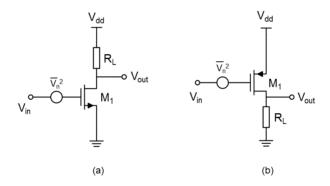

|   | 4.  | 2.2       | Topology Chosen for the LNA                        | 65  |

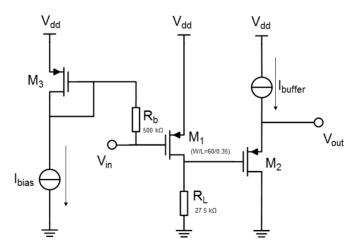

|   | 4.  | 2.3       | LNA Prototype Design                               | 66  |

|   | 4.3 | Design    | of the Time-Gain-Compensation (TGC) Amplifier      | 72  |

|   | 4.  | 3.1       | Target Specifications of the TGC Amplifier         | 72  |

|   | 4.  | 3.2       | Topology Chosen for the TGC Amplifier              | 72  |

|   | 4.  | 3.3       | TGC Amplifier Prototype Design                     | 78  |

|   | 4.4 | Conclus   | ions                                               | 80  |

|   | 4.5 | Referen   | ces                                                | 81  |

| 5 | M   | Iicro-Bea | mformer Design                                     | 83  |

|   | 5.1 | Design    | Choice: Digital Beamforming vs. Analog Beamforming | g84 |

|                                     | 5.2                                                                       | Analog l                                                       | Delay Line Architectures                                                                    | 85                                      |

|-------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------|

|                                     | 5.2.1<br>5.2.2                                                            |                                                                | Possible Approaches                                                                         | 85                                      |

|                                     |                                                                           |                                                                | Chosen Approach: Pipeline-Operated S/H Delay Li                                             | ne86                                    |

|                                     | 5.3                                                                       | A Brief                                                        | Overview of Signal Summation Methods                                                        | 88                                      |

|                                     | 5.4                                                                       | Prototyp                                                       | e Designs                                                                                   | 89                                      |

|                                     | 5.4                                                                       | .1                                                             | General Design Requirements and Goals                                                       | 89                                      |

|                                     | 5.4<br>De                                                                 |                                                                | Precision Considerations of the Pipeline-Operate                                            |                                         |

| 5.4.3 Prototype I: A Micro-Beamforn |                                                                           |                                                                | Prototype I: A Micro-Beamforming Cell with a Pig<br>H Delay Line and a V/I Converter        | -                                       |

|                                     | 5.4.4 Prototype II:                                                       |                                                                | Prototype II: A 9-Channel Analog Micro-Beam e-Operated S/H Stages and Charge-Mode Summation |                                         |

|                                     | 5.4                                                                       | .5                                                             | Performance Comparison                                                                      | 110                                     |

|                                     | ٥.١                                                                       |                                                                |                                                                                             |                                         |

|                                     | 5.5                                                                       | Conclus                                                        | ions                                                                                        | 111                                     |

|                                     |                                                                           |                                                                | ces                                                                                         |                                         |

| 6                                   | 5.5<br>5.6                                                                | Reference                                                      |                                                                                             | 111                                     |

| 6                                   | 5.5<br>5.6                                                                | Reference<br>trasounce                                         | ces                                                                                         | 111<br><b> 115</b>                      |

| 6                                   | 5.5<br>5.6<br>Ult                                                         | Reference<br>trasounce<br>PCB Imp                              | l Receiver Realizations                                                                     | 111<br><b> 115</b><br>116               |

| 6                                   | 5.5<br>5.6<br><b>Ul</b> i<br>6.1                                          | Reference<br>trasounce<br>PCB Imp                              | I Receiver Realizations  plementation of a 3-Channel Ultrasound Receiver                    | 111<br><b> 115</b><br>116<br>116        |

| 6                                   | 5.5<br>5.6<br><b>Ul</b> :<br>6.1                                          | Reference<br>trasound<br>PCB Imp<br>.1<br>.2                   | Plementation of a 3-Channel Ultrasound Receiver  System Description                         | 111 115 116 116 118                     |

| 6                                   | 5.5<br>5.6<br>Uli<br>6.1<br>6.1                                           | Reference trasounce PCB Imp .1 .2 An Integ                     | Plementation of a 3-Channel Ultrasound Receiver  System Description                         | 111 115 116 116 118                     |

| 6                                   | 5.5<br>5.6<br>Uli<br>6.1<br>6.1<br>6.2                                    | Reference trasounce PCB Imp .1 .2 An Integ                     | Plementation of a 3-Channel Ultrasound Receiver  System Description                         | 111 115 116 116 118 121                 |

| 6                                   | 5.5<br>5.6<br>Uli<br>6.1<br>6.1<br>6.2<br>6.2                             | Reference trasounce PCB Imp .1 .2 An Integ .1 .2               | Plementation of a 3-Channel Ultrasound Receiver  System Description                         | 111 115 116 116 118 121 121             |

| 6                                   | 5.5<br>5.6<br>Uli<br>6.1<br>6.1<br>6.2<br>6.2<br>6.2                      | Reference trasounce PCB Imp .1 .2 An Integ .1 .2 .3            | Plementation of a 3-Channel Ultrasound Receiver  System Description                         | 111 115 116 116 118 121 121 122         |

| 6                                   | 5.5<br>5.6<br>Uli<br>6.1<br>6.1<br>6.2<br>6.2<br>6.2<br>6.2               | Reference trasounce PCB Imp .1 .2 An Integ .1 .2 .3 Conclusion | Plementation of a 3-Channel Ultrasound Receiver  System Description                         | 111 115 116 116 118 121 121 122 130     |

| 7                                   | 5.5<br>5.6<br>Uli<br>6.1<br>6.1<br>6.2<br>6.2<br>6.2<br>6.2<br>6.3<br>6.4 | Reference trasounce PCB Imp .1 .2 An Integ .1 .2 .3 Conclusive | Plementation of a 3-Channel Ultrasound Receiver  System Description                         | 111 115 116 116 118 121 121 125 130 131 |

| 7.2     | Evaluation of Prior Art                                                           | 135 |

|---------|-----------------------------------------------------------------------------------|-----|

| 7.3     | Proposed Interconnection Method                                                   | 137 |

| 7.4     | Prototype Design                                                                  | 139 |

| 7.5     | Conclusions                                                                       | 141 |

| 7.6     | References                                                                        | 141 |

| 8 C     | onclusions                                                                        | 143 |

| 8.1     | General Conclusions                                                               | 143 |

| 8.2     | Main Contributions                                                                | 145 |

| 8.3     | Future Research Directions                                                        | 147 |

| 8.4     | References                                                                        | 150 |

| Summ    | ary                                                                               | 151 |

| Samen   | vatting                                                                           | 155 |

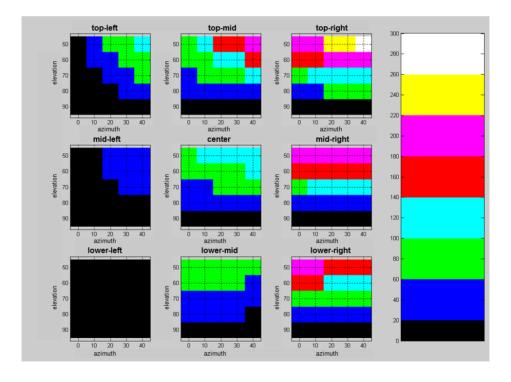

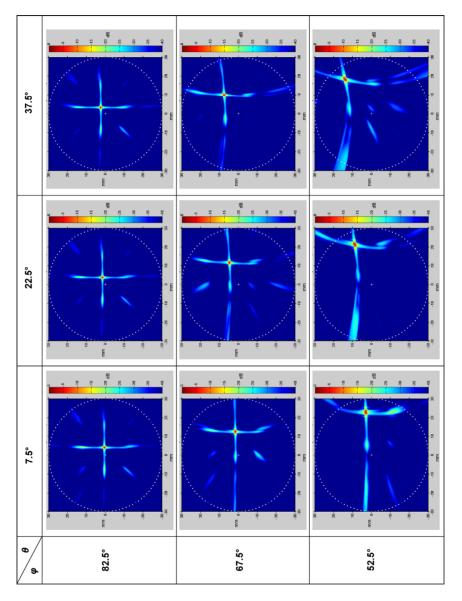

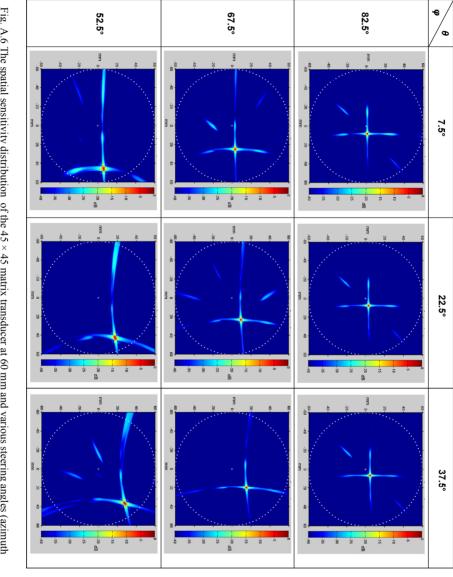

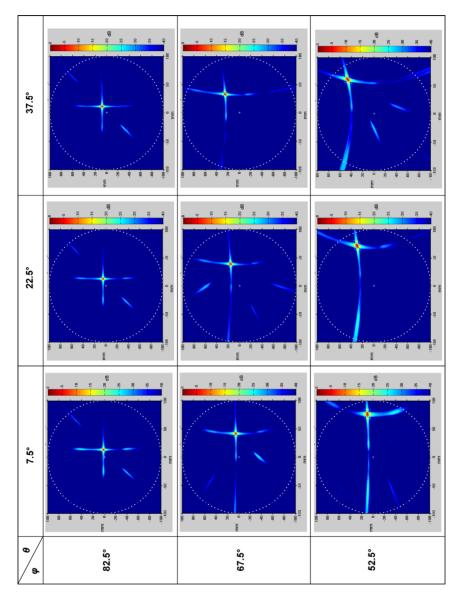

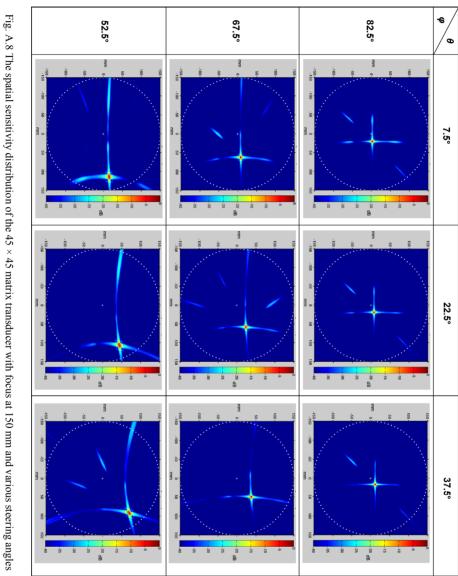

|         | dix A: Simulated Spatial Sensitivity of ducer with Pre-steering and Discrete Dela |     |

| List of | Publications                                                                      | 169 |

| Ackno   | wledgements                                                                       | 171 |

| About   | the Author                                                                        | 173 |

# Introduction

There is a clear clinical need for creating three-dimensional (3D) images of the heart. These images can give more authentic information on the 3D anatomy and function of the heart, such as the cardiac chamber volumes and the movements of the valves [1.1]. Normal imaging is done precordially. However, to obtain a more detailed view, imaging can also be performed from the esophagus. In this case, an ultrasound transound transducer is mounted in the tip of a gastroscopic tube and inserted into the esophagus to make images from the backside of the heart. This is called Trans-Esophageal Echocardiography (TEE). Now the challenge is to enable 3D TEE. We — a team consisting of Oldelft Ultrasound B.V., ErasmusMC and TU Delft is developing a miniature ultrasound probe containing a matrix piezoelectric transducer with more than 2000 elements. Since a gastroscopic tube cannot accommodate the cables needed to connect all transducer elements directly to an imaging system and so far there is no any imaging system exists with more than 256 input connections, a major challenge is to locally reduce the number of channels, while maintaining a sufficient signal-to-noise ratio (SNR). This can be achieved by using a front-end application-specific integrated circuit (ASIC) connected to the transducer that provides appropriate signal conditioning in the tip of the probe. The main goal of this

1

thesis work is to design such an ASIC using simple, low-power circuits, while still maintaining good image quality and to investigate the scientific problems related to this design. In addition to the electronics design, a second goal is to realize the interconnection between the matrix transducer and the ASIC.

In this introductory chapter, the basic knowledge of TEE is given. This is followed by a short discussion of the challenges and choices in designing a 3D TEE probe. It is shown that in order to reduce the channel count and enhance signal quality from the output of an ultrasound matrix transducer, smart signal processing by means of an ASIC in the tip of the probe is necessary. Meanwhile the circuits must be designed in such a way that they are compact and efficient enough to meet the stringent power and space requirements. Moreover, a new methodology is required to tackle the challenge of electrically connecting the transducer to the ASIC. Based on these challenges, the objectives and chosen design approaches are given. Finally, the thesis organization is described.

# 1.1 Trans-Esophageal Echocardiography (TEE) Basics

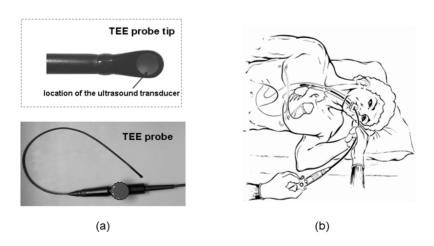

Fig. 1.1 Transesophgeal Echocardiography: (a) A TEE probe of the type 171Z- [1.5] (courtesy of Oldelft Ultrasound B.V.), (b) Use of the esophagus as a window during TEE imaging.

According to statistics from the World Health Organization (WHO) in 2011. cardiovascular diseases (CVDs) are the number-one cause of death globally [1.2]. CVDs are a group of disorders of the heart and blood vessels. In 2008, an estimated 17.3 million people died from CVDs [1.2], representing 30% of all global deaths. In order to save patients' lives, accurate diagnosis is of vital importance. For this purpose, many imaging techniques have been developed to visualize the inner structures of the heart, such as magneticresonance imaging (MRI), computed tomography (CT), positron emission tomography (PET), and echocardiography. Among them, echocardiography is the most popular technique, because of its low cost, non-invasive [1.3]. characteristic and image quality Transesophageal good echocardiography (TEE) is a cardiac imaging modality that uses the esophagus as the imaging window to the heart. Since the heart is directly adjacent to the wall of the esophagus, cardiac images can be obtained without strong attenuation from the ribs or the lungs, which is the case in transthoracic echocardiography (TTE) [1.4]. To enable TEE imaging, a TEE probe is indispensable (Fig. 1.1a). This probe consists of an ultrasound transducer, located in the tip of the probe, which is connected to an imaging system via a flexible gastroscopic tube. The probe is swallowed by a patient into his/her esophagus to obtain images (Fig. 1.1b).

#### Piezoelectric Ultrasound Transducers

To make ultrasound images, signal transductions between the acoustic domain and the electrical domain are needed. In the 20th century, many physical phenomena, such as electromagnetism, electrostatic phenomenon, electric-spark, and the piezoelectric effect, have found application in ultrasound transduction [1.6]. Among them the piezoelectric effect has had a major impact on the successful development of ultrasound transducers. Many crystalline materials exhibit the piezoelectric effect, such as quartz, Rochelle salt, and the man-made lead-zirconate-titanate (PZT) ceramic. Among them, PZT is the most widely used material for ultrasound transducers [1.7].

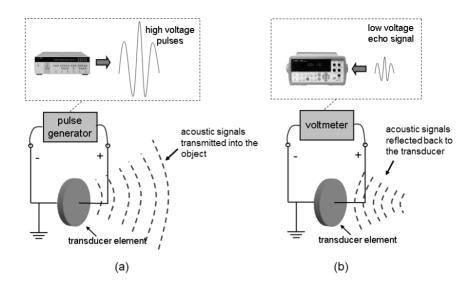

Fig. 1.2 Working mechanism of a piezoelectric ultrasound transducer: (a) transmit mode, (b) receive mode.

As shown in Fig. 1.2a, the piezoelectric ultrasound transducer is a device capable of converting energy between the electrical domain and the acoustic domain. When voltage pulses are applied across the two electrodes of the transducer, the device will oscillate at very high frequencies, thus producing sound waves in the ultrasonic range. Inversely, when an ultrasound echo signal arrives on the surface of the transducer in the form of acoustic pressure, displacements of electrical charges in the transducer occur, which leads to potential differences generated across the transducer. A piezoelectric transducer can thus play the roles of both transmitter and receiver, which is the case in many conventional ultrasound imaging systems. Piezoelectric ultrasound transducers are capable of operating at various frequencies, ranging from kHz to MHz. For medical imaging application, the transducers normally work in the frequency range of 1~40 MHz [1.8].

#### TEE Imaging Systems

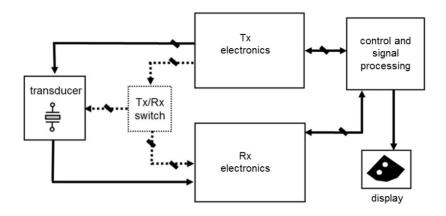

Fig. 1.3 A TEE imaging system

A typical TEE imaging system is based on the pulse-echo principle. It mainly consists of one or more ultrasound transducers with multiple elements arranged in arrays, transmit (Tx) electronics, receive (Rx) electronics, a control and signal processing module, and a display module (Fig. 1.3). Firstly, the transducer elements are excited by high-voltage pulses generated by the Tx electronics. The transducer elements convert the electrical energy into mechanical vibration. When the TEE probe is coupled to the esophageal wall against the heart, the vibration is transmitted into the heart as an acoustic wave. Depending on the acoustic impedance along the path of transmission, a certain percentage of the acoustic signals is reflected back and will hit the surfaces of transducer elements. Next, those so-called "echo" signals are picked up by the transducer elements and are converted into the electrical domain. Typical voltage levels of the echo signals in the TEE application range from several microvolts to hundreds of millivolts. These signals are further processed by Rx electronics. This processing includes amplification, time-gain-compensation (TGC) beamforming among multiple receive channels [1.6]. Based on the signal strength and timing, the inner structure of the heart can be determined. Finally, an image is rendered by the display module.

If a single transducer array is used as both the transmitter and receiver, a Tx/Rx switch must be inserted between the Tx/Rx electronics (dashed line in Fig. 1.3). A protection circuit is typically also included inside the Tx/Rx switches to prevent the low-voltage Rx electronics from being damaged by the high voltage pulses. The transducer is always located in the tip of the TEE probe. In conventional TEE imaging systems, the Tx/Rx electronics and the Tx/Rx switches are located outside the probe tip. However, a new trend for 3D TEE imaging is to move these circuits (at least partially) into the probe tip [1.10].

#### From 2D to 3D

In conventional echocardiography, a one-dimensional (1D) ultrasound array is manually repositioned at several positions and angles to obtain a number of two-dimensional (2D) ultrasound images of different cross-sections of the heart. The physician mentally combines these images to form an impression of the real three-dimensional (3D) anatomy. Therefore, this method is highly subjective and depends on the skill and experience of the physician [1.11]. This issue is addressed by 3D ultrasonic imaging techniques, which have several advantages compared to conventional 2D techniques. Cardiac chamber volumes can be evaluated with more accuracy, without making assumptions on the shape of the volume [1.1]. Furthermore, cross-sectional planes and "en face" views can be reconstructed for any orientation, giving better understanding of the morphology of the various heart cavities, of defects, and of diseased valves [1.12].

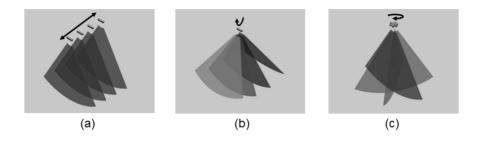

A 3D dataset can be constructed from a series of 2D image planes, provided that the position and orientation of the subsequent planes are known. These image planes can be obtained by using a 1D transducer array with a mechanical scanning approach, such as stepwise translating, tilting or rotating (Fig. 1.4). Various 3D imaging techniques using 1D arrays are described in [1.13]. For TEE applications, the most common techniques use a 1D array that is rotated around its axis. A drawback of this method is that it

increases the scanning time. The acquired 3D image is not real-time, but reconstructed from data acquired at different moments in time. Moreover, the images are sensitive to imaging artifacts due to the movement of the heart [1.14].

Fig. 1.4 Different methods of acquiring a 3D dataset using a 1D array: (a) translating, (b) tilting, and (c) rotating.

With a 2D transducer array (a matrix array), ultrasound beams can be emitted in any direction in a pyramidal volume. Thus, a 3D dataset can be acquired directly without the need for mechanical repositioning of the array (Fig. 1.5). At this moment, a matrix transducer for real-time 3D TEE is already commercially available (xMATRIX, Philips [1.15]). As reported in [1.16], by using an iE33 ultrasound system (Philips Medical Systems) which was equipped with a fully-sampled matrix TEE transducer of approximately 3000 elements, real-time 3D images of the mitral valve, interatrial septum, left atrium and left ventricle have been obtained with excellent image quality. However, the system is not able to scan a large volume in a single heartbeat. Instead it acquires 4~7 narrow wedges over 4~7 heartbeats to form the total volume.

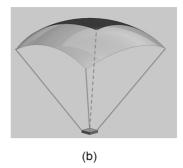

Fig. 1.5 Volumetric dataset acquired using a matrix transducer: (a) front-view of a matrix transducer (courtesy of Oldelft Ultrasound B.V.), (b) a volume can be imaged by a matrix transducer.

## 1.2 Design Challenges and Choices in 3D TEE

In our project, we are designing a TEE probe for real-time 3D imaging using matrix ultrasound transducers. Since the TEE probe will be inserted into the esophagus of a patient, the esophageal cavity puts a size constraint on the transducer as well as on the gastroscopic tube. To obtain 3D images with sufficient resolution, the pitch of the transducer elements should be small and the total aperture should be as large as possible. Therefore, a matrix transducer consisting of several thousands of elements is required [1.17] (more than 2000 elements in this thesis work). One of the major challenges of manufacturing a TEE probe with a matrix transducer is connecting its large number of elements to an external imaging system. Connecting each element with a separate cable is not possible because the number of cables cannot be accommodated in the shaft of the gastroscope and the tube should remain flexible: there is no imaging systems available which can handle 2000 connections. Therefore, smart signal processing is required in the tip of the probe to reduce the number of channels to the external imaging system. This can be achieved using an application-specific integrated circuit (ASIC) bonded to the matrix transducer

In conventional ultrasound imaging systems, the same transducer works as both transmitter and receiver. As discussed in the previous section, high voltage pulses are needed to excite transducer elements during the transmission period. To isolate the sensitive receive circuitry from these high voltage pulses and to prevent the small echo signal from being attenuated by the transmit circuitry, a Tx/Rx switch with protection circuit is mandatory. However, a typical protection circuit consists of large diodes connected back-to-back, which are usually bulky [1.6] and challenging to implement for a matrix transducer with more than 2000 elements in a limited space. Moreover, the need for high-voltage circuitry will limit the options for selecting a proper technology to implement the receiver electronics, which could be a serious drawback when keeping up with today's developments in technology.

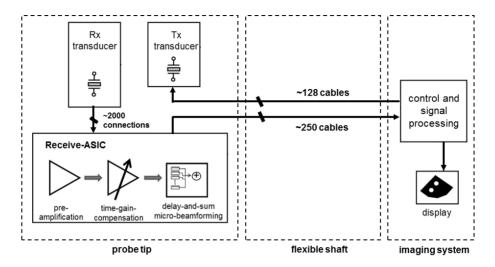

In our design, the problem of protection is circumvented by physically separating the transducer into a transmit sub-array (Tx array) with ~128 elements and a receive sub-array (Rx array) with ~2000 elements. Two sub-arrays are placed side-by-side. The Tx array can be directly connected to the external imaging system via cables. A front-end receive ASIC is needed to interface the Rx array only. An additional advantage is that tissue harmonic imaging [1.6] (see Section 2.2.4) is possible without the need for broadband transducer elements. Furthermore, both Tx and Rx arrays can be optimized for their specific role [1.17]. The proposed block diagram of the TEE imaging system is depicted in Fig. 1.6.

Fig. 1.6 Block diagram of the proposed TEE imaging system.

This thesis mainly focuses on the design of the receive-ASIC, which achieves channel-count reduction by applying appropriate delays to Rx-array outputs locally and coherently summing the signals from several elements. This local delay-and-sum operation is called "micro-beamforming". The ASIC should also provide proper signal pre-amplification and time-gain-compensation (TGC) to each transducer element.

For the receive-ASIC in the tip of the TEE probe, several constraints apply. One limiting factor is the space in the probe tip, which has a size of about 2 cm × 1 cm × 1 cm (length × width × height). Thus, compact circuit design and efficient use of the small space are required. To avoid overheating of the tissue, the maximum power consumption of the front-end electronics is a very critical specification as well. In a conventional TEE probe, a thermistor is employed to monitor the temperature. The system shuts down when a certain threshold temperature (42°C to 44°C) is reached [1.18]. For continuous monitoring of the heart, shut-down is undesirable. Therefore, the self-heating of the probe tip should be limited. The temperature rise in the probe tip depends on many factors, such as the power dissipation of the transducers and the electronics, and the heat-sinking capability of the wires. To obtain an estimate of the power-dissipation levels that are acceptable, the

power consumption of commercially available TEE probes in transmit mode, which is approximately 1 W to 2 W, is used as a reference. To prevent a significant increase in self-heating, we set the power budget for the receive electronics to be in the same order, and preferably not more than 1 W.

In addition to the electronics design, finding a way to connect the ASIC to the matrix ultrasound transducer is another great challenge. The major design constraints are the limited space in the probe tip, the large number of channel counts, and the processing temperature<sup>1</sup>. These constraints make conventional technologies, such as wire bonding technology and flip-chip technology [1.19], challenging to implement. The main research task is to develop an interconnection solution that delivers a compact structure, good electrical connectivity, etc. Moreover, the interconnection solution must fulfill the temperature requirement and be compatible with the transducer manufacturing process.

# 1.3 Objective and Chosen Approaches

The main objective of this thesis work is to tackle design challenges associated with the readout and connectivity of the receive (Rx) transducer in a TEE probe for 3D imaging. Two major design questions are:

- (1) How to apply front-end signal processing using an ASIC under stringent power and space constraints?

- (2) How to solve the transducer-to-ASIC interconnection issue?

The above questions are answered by the following means:

- New system approaches (Chapter 3):

- Instead of using a conventional continuous time-gain compensation (TGC) scheme, we have chosen for a four-step discrete-gain implementation, which highly simplifies the circuit design.

ne processing temperature must be well below the Curie temper

<sup>&</sup>lt;sup>1</sup> The processing temperature must be well below the Curie temperature of the piezoelectric material to avoid depolarization.

- A new micro-beamforming methodology is employed to reduce the circuit-design complexity without causing significant degradation of the image quality.

- New circuit solutions (Chapters 4 & 5):

- A low-power time-gain-compensation (TGC) amplifier has been realized by using an open-loop topology. Circuit techniques such as trans-conductance boosting using a cascaded-flipped voltage follower and Kelvin connections, are employed to improve the accuracy.

- Analog delay lines have been designed using the pipeline-operated S/H delay architecture. This circuit topology is simple, flexible and accurate in terms of gain and timing.

- O Two micro-beamformers with different signal-summation methods have been designed. The first one employs a voltage-to-current converter and sums the signals from several channels in the current domain. The other circuit uses an elegant charge-averaging structure, which significantly reduces the power consumption.

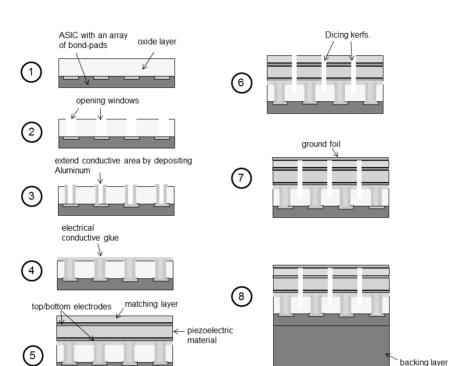

- A new interconnection technology (Chapter 7):

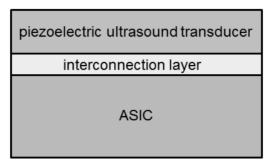

- The use of electrical conductive glue as the intermediate conductor enables an ultrasound matrix transducer to be built directly on top of an ASIC.

## 1.4 Thesis Organization

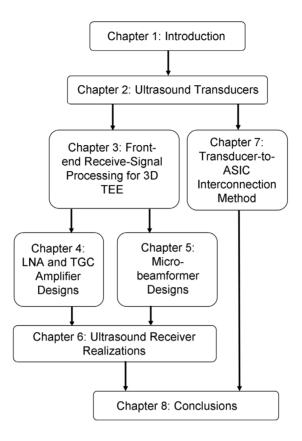

The remainder of this thesis consists of seven chapters. The thesis structure and the relationship between these chapters are shown in the flowchart below (Fig. 1.7).

Fig. 1.7 Flowchart of the thesis organization.

Chapter 2 is an introduction to ultrasound transducers. The basic principles of operating ultrasound transducers are described. The major focus of this chapter is on the receive (Rx) transducer used for 3D TEE. Practical issues associated with this transducer such as its geometry, its electrical model, and the requirements of the associated readout-electronics design, are examined.

In Chapter 3, the system architecture of the front-end signal processing chain is given. Simplifications made to time-gain compensation (TGC) and microbeamforming are described. The design requirements for the front-end electronics are also proposed.

In Chapters 4 and 5, designs of a low-noise amplifier, a TGC amplifier, and micro-beamforming circuits are presented. Various circuit topologies and techniques are compared, improved and optimized.

In Chapter 6, two ultrasound receivers are presented. They combine the circuit building blocks presented in Chapter 4 and Chapter 5 into complete front-end signal-processing chains. Both receivers demonstrate the effectiveness of the design approaches and deliver proofs of concepts.

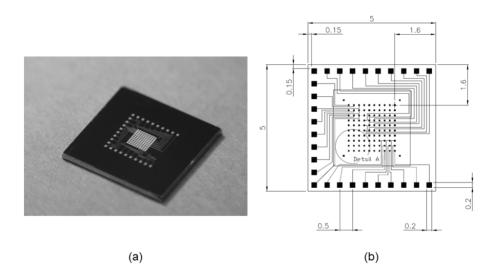

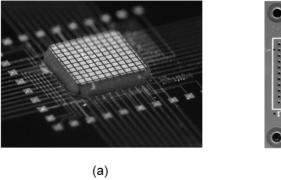

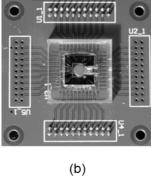

In Chapter 7, a new method of electrically connecting an ultrasound matrix transducer to an ASIC is proposed and experimental results are presented.

Finally, in Chapter 8, conclusions are drawn and the main contributions of this work are summarized. Some recommendations for future research are also presented.

#### 1.5 References

- [1.1] R.M. Lang, V. Mor-Avi, L. Sugeng, P.S. Nieman, D.J. Sahn, "Three-dimensional echocardiography: the benefits of the additional dimension", *Journal of the American College of Cardiology*, vol. 48, no. 10, pp. 2053-2069, Nov. 2006.

- [1.2] http://www.who.int/mediacentre/factsheets/fs317/en/ (2011).

- [1.3] K.Y.E. Leung, *Automated Analysis of 3D Stress Echocardiography*, PhD thesis: Department of Biomedical Engineering, Erasmus University, 2009.

- [1.4] E.A. Fisher, J.A. Stahl, J.H. Budd, M.E. Goldman, "Transesophageal echocardiography: procedures and clinical application", *Journal of the American College of Cardiology*, vol. 18, issue 5, pp. 1333-1348, Nov. 1991.

- [1.5] Oldelft Ultrasound, "Oldelft MicroMulti TE Probe Type number 171Z-", *User Manual*, February 2010.

http://www.oldelft.nl/upload/documenten/gebruiksaanwijzingen/250m065-00a-manual-micromulti.pdf.

- [1.6] R. S. C. Cobbold, *Foundations of Biomedical Ultrasound*, Oxford University Press, 2007.

- [1.7] A. Arnau, *Piezoelectric Transducers and Application*, Berlin: Springer, 2008.

- [1.8] M. Postema, O.H. Gilja, "Contrast-enhanced and targeted ultrasound", *World Journal of Gastroenterology*, vol. 17, no.1, pp. 28-41, 2011.

- [1.9] K. Iniewski, *Medical Imaging, Principles, Detectors and Electronics*, New Jersey: John Wiley & Sons, 2009.

- [1.10] V. Mor-Avi, L. Sugen, R.M. Lang, "Real-time 3-dimensional echocardiography: an integral component of the routine echocardiographic examination in adult patients", *Circulation*, vol. 119: pp. 314-29, 2009.

- [1.11] A. Fenster, D. B. Downey, H. N. Cardinal, "Three-dimensional ultrasound imaging", *Physics in Medicine and Biology*, vol. 46, pp. 67-99, 2001.

- [1.12] J. Roelandt, "Three-dimensional echocardiography", *Echocardiography*, part 7, pp. 603-618, London: Springer, 2009.

- [1.13] B.J. Krenning, M.M. Voormolen and J.R. Roelandt, "Assessment of left venricular function by three-dimensional echocardiography", *Cardiovascular Ultrasound*, vol.1, No.12, Sept. 2003.

- [1.14] A. Salustri, J. Roelandt, "Three dimensional reconstruction of the heart with rotational acquisition: methods and clinical applications", *British Heart Journal*, vol. 73, supplement 2, pp. 10-15, 1995.

- [1.15] F. Taddei, L. Franceshetti, M. Signorelli, F. Prefumo, N. Fratelli, T. Frusca, C. Groli, "xMATRIX Array Transducer in Fetal Echocardiography", http://www.healthcare.philips.com/pwc\_hc/main/shared/Assets/Documents/ Ultrasound/Products/Campaigns/Pushing%20the%20Boundaries/xMATRIX \_fetal\_echo\_by\_Franceshetti\_et\_al.pdf, 2011.

- [1.16] L. Sugeng, S. K. Shernan, I. S. Salgo, L. Weinert, D. Shook, J. Raman,V. Jeevanandam, F. Dupont, S. Settlemier, B. Savord, J. Fox, V. Mor-Avi, R.M. Lang, "Live 3-dimensional transesophageal echocardiography: initial

experience using the fully-sampled matrix array probe," *Journal of the American College of Cardiology*, vol. 52, no. 6, pp. 446-449, 2008.

[1.17] P. L. M. J. van Neer, *Ultrasonic Superharmonic Imaging*, PhD thesis: Department of Biomedical Engineering, Erasmus University, 2010.

[1.18] J.N. Hilberath, D.A. Oakes, S.K. Shernan, B.E. Bulwer, M.N. D'Ambra, H.K. Eltzschig, "Safety of Transesophageal Echocardiography", http://www.asecho.org/files/JASE2010Nov.pdf, 2010.

[1.19] J. H. Lau, Low Cost Flip Chip Technology for DCA, WLCSP, and PBGA Assemblies, New York: McGraw-Hill, 2000.

# Ultrasound Transducers

Ultrasound transducers are devices that are capable of converting energy between the mechanical domain and the electrical domain. They are indispensable elements in ultrasound imaging systems. Before we dive into the system design, an in-depth understanding of ultrasound transducers is essential. Therefore, this chapter begins with a brief introduction to ultrasound transducers. Although there are different types of transducers, we will restrict ourselves to the study of piezoelectric transducers, which are the most widely used in medical ultrasound imaging. Afterwards, several important characteristics associated with ultrasound signals will be discussed. such as the reflection at tissue boundaries, the attenuation of the ultrasound wave during propagation, signal dynamic range, and harmonics generation. These are the foundations for ultrasound signal processing. The final part of this chapter is devoted to the analysis of the transducers that are used in this thesis work. As described in Chapter 1, the major tasks of this thesis work are to design an interface ASIC for the receive (Rx) transducer and to develop a technology for the transducer-to-chip interconnection. Therefore, in this chapter great emphasis is placed on the study of the Rx transducer. Based on the characteristics of this transducer, considerations on interconnection electronics and designs will be given.

17

# 2.1 A Short Introduction to Piezoelectric Ultrasound Transducers

#### 2.1.1 Piezoelectric Effect

The fundamental working principle of a piezoelectric ultrasound transducer is based on the piezoelectric effect. When a mechanical force in the form of an ultrasound wave is applied to a transducer, along with geometric deformation, polarization of the electrical dipoles in the transducer dielectric occurs. Thus, a net dipole moment is created, which forms an electric field across the two electrodes of the transducer [2.1]. The polarization is proportional to the mechanical force, and changes sign depending on the sign of the pressure wave [2.2]. Inversely, if an ultrasound transducer is excited with alternating electric fields, it will compress and expand, and thereby generating sound waves in the ultrasonic range.

Many crystalline materials can be used to build piezoelectric ultrasound transducers, which can be categorized as natural crystals (e.g. quartz, Rochelle salt) or man-made ceramics (e.g. barium-titanate ceramics, lead-zirconate-titanate ceramics). Among them, the lead-zirconate-titanate ceramic, known as PZT, is the most widely used material [2.3]. It is also the building material for transducers used in this thesis project. It is worth noting that the piezoelectric property of a PZT ultrasound transducer will be lost if the temperature of the crystal rises above its Curie temperature. The temperature requirement puts constraints on the transducer-to-chip interconnection technology. Therefore, we should keep the processing temperature well below the Curie temperature of the selected PZT ceramic.

#### 2.1.2 Device Structure

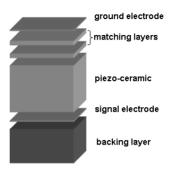

Fig. 2.1 Structure of a typical piezoelectric transducer (exploded view).

A typical piezoelectric ultrasound transducer is a layered device consisting of two electrodes, a piece of piezo-ceramic, a backing layer and one or more matching layers (Fig. 2.1). The electrodes should be sufficiently thin so that their influence on wave propagation is negligible [2.2]. The piezo-ceramic is the actual ultrasound generator and detector, which is sandwiched between the signal electrode and the ground electrode. The size and shape of the piezo-ceramic determine the resonance frequency of the transducer, at which the energy-conversion efficiency of the transducer reaches its highest value [2.4]. The frequency response of a piezoelectric ultrasound transducer has a band-pass shape. The bandwidth determines the range of frequencies over which the transducer can operate with relatively high energy conversion efficiency.

Since the acoustic impedances between the piezo-ceramic and the tissue being imaged differ greatly (e.g. the acoustic impedance of PZT ceramic is about 20-30 times higher than that of soft tissue [2.5]), connecting the piezo-ceramic directly to the tissue would cause strong reflection at the boundary. In this case, in the transmit mode, only a small percentage of the acoustic energy would then be transmitted into the tissue. The reflected waves would cause unwanted ringing of the piezo-ceramic, which would degrade the axial resolution (discussed in Section 2.1.5) of the image due to very long pulse

duration. Moreover, in the receive mode, large reflection would result in a low sensitivity.

To improve the energy transfer efficiency at the transduce-tissue boundary and enhance the sensitivity, one or more matching layers are employed. Matching layers have acoustic impedance levels between those of the piezoceramic and the tissue. The use of matching layers allows the sound waves to reflect back and forth repeatedly inside the matching layers, producing waves that are in phase to each other. Hence, waves are constructively added up to form a reinforced wave that propagates across the boundary. In this way, the sensitivity of the transducer is improved. In addition to the aforementioned advantage, as described in [2.5], by using several matching layers to gradually bridge the gap of acoustic impedances between the tissue and the piezo-ceramic, the bandwidth of the transducer can be tuned. In the meantime, to overcome the ringing problem, a backing layer (Fig. 2.1) is attached underneath the piezo-ceramic, so that during transmission, most of the energy reflected back into the piezo-ceramic can be absorbed and turned into heat. The backing layer also provides damping to the received echo signals. The durations of the echoes are as well shortened for better axial resolution.

## 2.1.3 Electrical Impedance Model

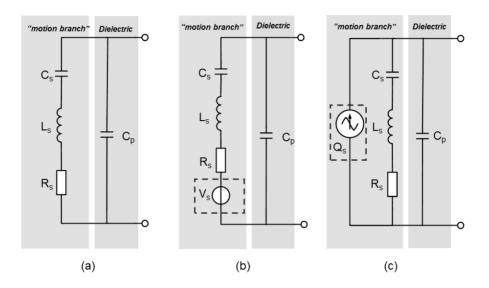

The electrical impedance looking into the two electrodes of a transducer can be modeled using a lumped-element model. Once the transducer design is completed, the electrical impedance model can be obtained by firstly measuring the device using an impedance analyzer and then applying curve fitting to find the values of the model parameters. Figure 2.2a shows a typical electrical impedance model. It consists of a series RCL resonance tank ( $L_s$ ,  $C_s$ ,  $R_s$ ) and a shunting capacitor  $C_p$ . The series connection of  $L_s$ ,  $C_s$  and  $R_s$  creates the so-called "motion branch", which is devoted to the description of the mechanical part of the transducer [2.6]. The inductance  $L_s$  represents the inertial effect of the piezoelectric material in vibration. The capacitance  $C_s$  represents the elastic stiffness and  $R_s$  relates to the energy

dissipation and mechanical loading. The shunting capacitor  $C_p$  represents the dielectric property of the piezoelectric material.

Fig. 2.2 Electrical model of a piezoelectric transducer: (a) typical impedance model, (b) electrical model in the receive mode (expanded model with a voltage source presented) and (c) electrical model in the receive mode (expanded model with a charge source presented).

The impedance model is useful for analyzing the transducer frequency response. Besides, during the front-end electronics design, the impedance model can be plugged into the circuit simulator for co-simulation. In the transmit mode, the transducer acts as a load. By including the impedance model into simulation, the required drive current, ring-down effects and power transfer can be calculated [2.7]. In the receive mode, the transducer acts as a sensor and senses dynamic mechanical excitations, i.e., changing forces. As indicated in [2.6], using an electromechanical analogy, the dynamic mechanical excitation is introduced in the form of a voltage source that is coupled to the "motion branch". To obtain an electrical model in the receive mode, the impedance model can be expanded to include a voltage source  $V_s$  in series with the "motion branch" (Fig. 2.2b). This voltage source mimics the transduction between the mechanical domain and the electrical domain, which has a voltage directly proportional to the force and can have

an arbitrary frequency determined by the excitation source. The output voltage measured across the two output terminals of the transducer model can be understood as the voltage  $V_s$  passes through a filter network [2.8]. It is worth noting that, using circuit theory, the voltage source shown in Fig. 2.2b can be transformed into a charge source (Fig. 2.2c), which represents the displacement of the piezoelectric transducer. The charge source model is convenient when displacement is a measurand and a charge amplifier can be used to interface the transducer. Moreover, one difference between the voltage source and the charge source is that the charge source is frequency-dependent.

### 2.1.4 Transducer Arrays and Beamforming

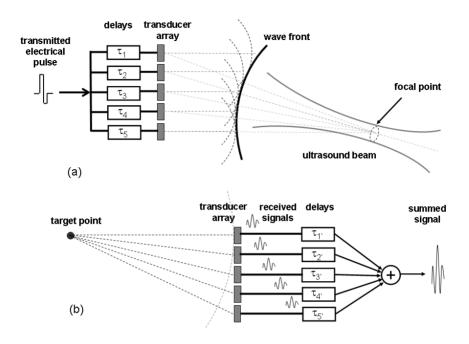

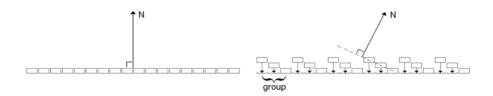

Most ultrasound transducers that are used for medical imaging are arrays. An array transducer is constructed with many transducer elements that arranged in a line, in a ring or in a 2D matrix pattern. By using a so-called "beamforming" technique [2.2], an array transducer allows the steering and focusing of ultrasound beams at various angles and at different depths, without physically moving the transducer. An array transducer also provides the flexibility to adjust the active aperture size to meet the requirements for lateral resolution and beam shape. The beamforming function is realized by a beamformer circuit, which determines the shape, size and position of the beams. An illustration is shown in Fig. 2.3. In the transmit mode, a transmit beamformer generates signals with relative delays to drive the individual transducer element in an array, so that beams can be steered to scan various angles and be focused at different depths (Fig. 2.3a). In the receive mode, a receive beamformer provides appropriate electrical delays to the echo signals received by the individual transducer elements and coherently sum them up to form a stronger electrical signal (Fig. 2.3b).

Fig. 2.3 Illustration of beamforming function: (a) transmit mode, (b) receive mode.

#### 2.1.5 Transducer Resolution

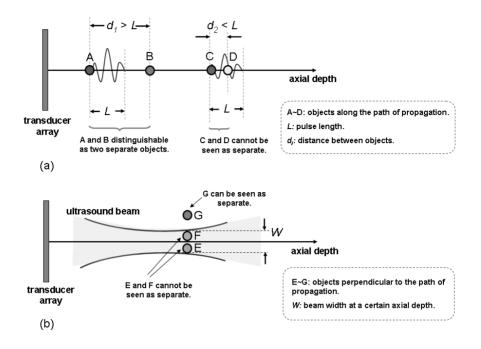

Transducer resolution is defined as the smallest distance between two targets that can still be distinguished and displayed separately. It can be categorized into the axial resolution (parallel to the path of sound propagation) and the lateral resolution (perpendicular to the path of sound propagation).

Axial resolution is strongly dependent on the lengths of the transmitted acoustic pulses. An example is given in Fig. 2.4a. Assume the transmitted pulse has a length of L and points A, B, C and D are the objects along the axis of the ultrasound beam. Since the distance between two objects A and B is larger than L, they reflect pulses one after another. Therefore, they can be distinguished as two separate points. However, targets C and D have a distance smaller than L. The reflected pulses are no longer separate. It can be concluded from the above illustration that a shorter pulse length leads to a better axial resolution. To obtain a short pulse length, a well-designed transducer (matching layer at the front and backing layers) is required to

effectively dampen the vibration of the piezo-ceramic. Moreover, the shape of the electric excitation pulse will also affect the acoustic pulse length [2.9][2.10]. For a given transducer, the excitation pulse shape can be optimized to achieve the best axial resolution.

Lateral resolution refers to the ability to resolve two targets side by side perpendicular to the sound propagation direction. A narrower ultrasound beam width provides a better lateral resolution. Figure 2.4b shows an example. Assume the ultrasound beam at a certain axial depth has a width of W, and points E, F and G are targets perpendicular to the sound beam. Targets E and F are located within the beam width and they will appear as one point on the display. Target G is located separatelyt from targets E and F, thus, it can be displayed as a separate point. The beam width depends on the transducer aperture size, focal distance and wave length. A larger aperture size, higher frequency and a shorter focal length result in a narrower beam width and thus better lateral resolution [2.5].

Fig. 2.4 Illustration of transducer resolution: (a) axial resolution, (b) lateral resolution.

# 2.2 Characteristics of Ultrasound Signals

# 2.2.1 Reflection and the Time-of-Flight (ToF) Principle

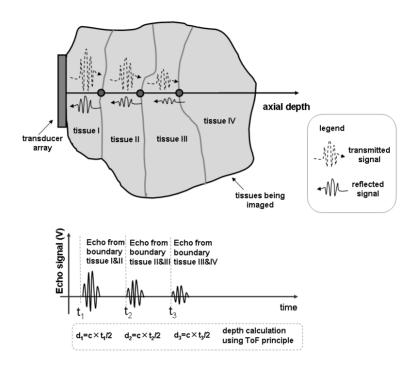

Conventional ultrasound imaging systems are based on the pulse-echo principle. As shown in Fig. 2.5, when ultrasound pulses generated by a transducer are propagating through inhomogeneous tissues, reflections occur at tissue boundaries due to differences in acoustic impedances. Then echo signals received by the transducer are sequences of reflected pulses over time. The axial depths that correspond to echoes can be calculated by tracking the time-of-flight (ToF). Since the values for the speed of sound in human soft tissues are rather similar, an average value of 1540 m/s can be used as the nominal value without introducing significant errors to the image [2.5]. Thus, once we know the arrival time of the reflected pulses, by multiplying the arrival time with the sound speed, the axial depths at which reflections occurred can be derived.

Fig. 2.5 Reflection phenomenon at tissue boundaries and the time-of-flight (ToF) principle.

# 2.2.2 Propagation Attenuation

When ultrasound waves are traveling in tissue, they experience energy loss. Two effects play a major role in this energy loss: absorption and scattering [2.2]. Absorption refers to the process whereby ultrasound energy is converted into heat. Scattering means the redirection of ultrasound waves. Those waves will deviate from the desired propagation path and will not be detected by the transducer. Comparing these two effects, absorption causes more attenuation than scattering [2.2].

A measure of energy loss along the ultrasound propagation path is the attenuation coefficient, which is expressed in dB/cm. For most tissues, the attenuation coefficient increases approximately linear with frequency [2.5]. Therefore, for ease of calculation, the attenuation is usually measured in dB/cm/MHz. For example, if a tissue attenuates by 0.5 dB/cm/MHz, then for a 5 MHz ultrasound signal that travels into the tissue, the attenuation at a

depth of 10 cm is approximately:  $(0.5 \text{ dB/cm/MHz}) \times 5 \text{ MHz} \times 10 \text{ cm} = 25 \text{ dB}$ .

## 2.2.3 Dynamic Range of the Received Signal

The electrical signal produced by an ultrasound transducer in the receive mode has a certain intrinsic dynamic range. The upper bound is mainly related to the transmit acoustic power. The larger the transmit power, the larger the received signal level. However, the transmit power cannot be arbitrarily high, but has to comply with the regulations set by the FDA (Food and Drug Administration, USA) [2.11] in order to avoid potential risks to the human body, such as tissue heating and cavitation. As for the lower bound, the electrical noise of the transducer itself sets the level of the minimum detectable signal. In reality, ultrasound transducers are used in imaging systems. The readout electronics in imaging systems inevitably have noise, which results in a reduced overall system dynamic range compared to the intrinsic dynamic range of the transducer. Therefore, the noise of the readout electronics must be minimized by careful design. For today's ultrasound machines, the maximum signal dynamic range is in the order of 120 dB [2.7].

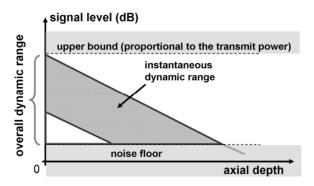

Figure 2.6 illustrates the relationship of the received electrical signal level of an ultrasound transducer and the axial depth. It can be seen that the received signals are located in a belt called "instantaneous dynamic range", which can be understood as the received-signal dynamic range at each imaging depth. However, as discussed in Section 2.2.2, ultrasound signals experience propagation attenuation. The signal level reduces when the imaging depth increases, and finally is drowned out by the noise of the transducer (if we assume for now the noise of the readout electronics is negligible). The instantaneous dynamic range and the dynamic range due to propagation attenuation constitute the overall dynamic range of the received signal.

Fig. 2.6 Illustration of the signal dynamic range in the receive mode.

## 2.2.4 Signal Distortion and Harmonic Generation

The propagation of ultrasound waves in the tissue is non-linear, which results in the generation of harmonics. Take a simple sinusoidal wave as an example. Since the speed of sound is associated with pressure, the wave crests, which have higher pressure propagate faster than the wave troughs which have lower pressure. Gradually, distortion increases and the wave shape changes from a sine wave into a saw-tooth shape. A theoretical saw-tooth signal contains the fundamental frequency and an infinite number of harmonics.

Over the past decade, the non-linear property of ultrasound propagation opened up a new research direction called "ultrasound tissue harmonic imaging" [2.12]. Imaging techniques, such as "second-harmonic imaging" [2.13], and even "super-harmonic imaging" have been reported [2.14]. Compared to fundamental imaging, harmonic imaging has a number of advantages, e.g. enhancement of lateral and axial resolutions, a lower grating lobe level, and near-field artifact elimination.

In our project, we are investigating the feasibility of using the "second-harmonic imaging" technique for 3D TEE application. In the transmit mode, an ultrasound transducer transmits signals at the fundamental frequency, while second-harmonic components are generated during propagation due to inhomogeneity in media. In the receive mode, the reflection and scattering of

this second-harmonic signal is detected. To understand the properties of the second-harmonic waves, proper modeling of non-linear acoustic wave fields in inhomogeneous biomedical tissue is required. This topic has been investigated by team members Demi et al. [2.15][2.16]. There are challenges associated with the imaging system design when using the second-harmonic imaging technique. As reported in [2.15][2.16], second-harmonic signals are expected to be about 1~2 orders of magnitude lower than fundamental signals. Moreover, the second harmonic signals have doubled frequency compared to fundamental signals, thus they are attenuated more on their way back. In order to maintain a reasonable dynamic range for the received second-harmonic signal, sufficient transmit power is needed. However, as described in Chapter 1, for 3D TEE application the power dissipation in the probe tip is a critical design aspect, that also limits the transmit power. This issue is still under investigation.

## 2.3 Matrix Transducer for 3D TEE

## 2.3.1 Transducer Configuration for 3D TEE

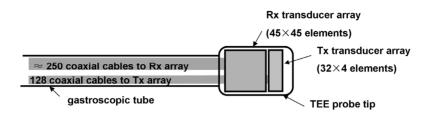

As described in Chapter 1, in our design, we use two transducer sub-arrays to act separately as the transmitter and the receiver. The "second-harmonic imaging" technique is chosen and the designs of sub-arrays are optimized for the 3D second-harmonic TEE. The proposed configuration has a 4 × 32 Tx sub-array that transmits ultrasound pulses at around 3 MHz and a 45 × 45 Rx sub-array that receives echo signals at around 6 MHz. The bandwidth of interest in the receive mode is from 4.5 MHz to 7.5 MHz. The two sub-arrays are placed next to each other and encapsulated in the tip of a TEE probe (Fig. 2.7). The elements in the Tx sub-array are directly connected to the external imaging system with 128 micro-coaxial cables. For the Rx sub-array, micro-beamforming [2.17] will be applied by using an interface receive ASIC to reduce the channel count from 2025 to about 250. In this way, the total number of micro-coaxial cables inside the gastroscopic tube can be kept within 400.

Fig. 2.7 Layout of the Tx and Rx transducers in a TEE probe.

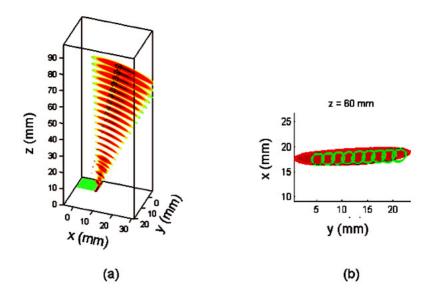

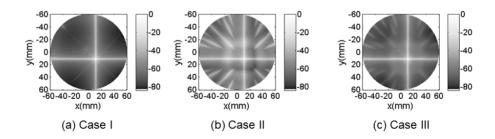

During transmission, the rectangular shaped Tx sub-array transmits broad ultrasound beams to cover an elliptical volume. Later, parallel beamforming [2.18] is used in the receive mode, where the volume defined in the Tx mode is filled by a number of receive beams (see Fig. 2.8). It can be seen in Fig. 2.8a that close to the surfaces of two sub-arrays, there is insufficient overlap of the Tx beam and the Rx beam. As indicated in [2.18], with this design, from a depth of 30 mm, a large part of the transmit beam can be covered with receive beams.

Fig. 2.8 Illustration of parallel beamforming [2.18] (courtesy of S. Blaak): (a) a broad transmit beam and a narrow receive beam, (b) the overlap between 9 parallel receive beams (circles) and a transmit beam (elliptic).

As described in Chapter 1, in this thesis, we focus on the electronics and interconnection designs for the Rx sub-array. Therefore, in the remainder of this section, we will focus on the Rx transducer, and the requirements for the electronics and interconnection scheme will be extracted.

## 2.3.2 Characteristics of the Rx Transducer

## Element geometry

The optimal element geometry for the Rx sub-array has been investigated by team members van Neer et al., [2.4] using finite element methods (FEM). Each transducer element in the  $45 \times 45$  array occupies an area of 0.17 mm  $\times$  0.17 mm. There is a 30  $\mu$ m dicing kerf between adjacent elements. The total Rx sub-array measures 9.0 mm  $\times$  9.0 mm.

## Material

Piezo-material CTS 3203HD [2.19] was chosen to build the Rx (and Tx) transducer sub-array(s). This type of piezo-material has a Curie temperature of 225°C.

## Electrical Model

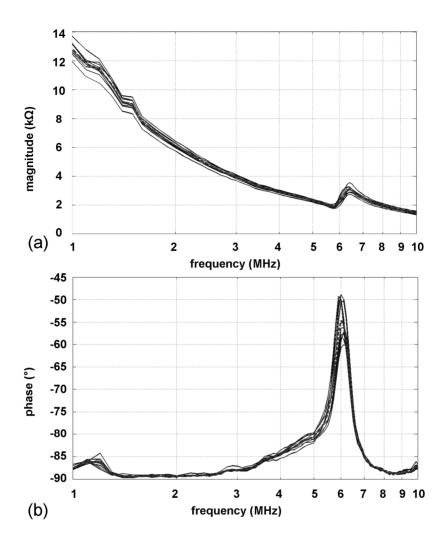

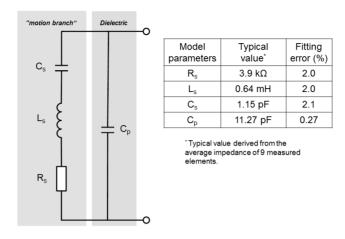

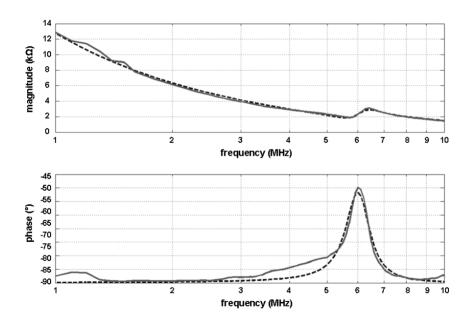

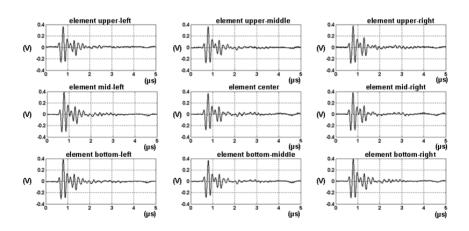

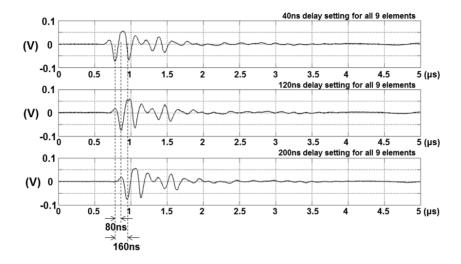

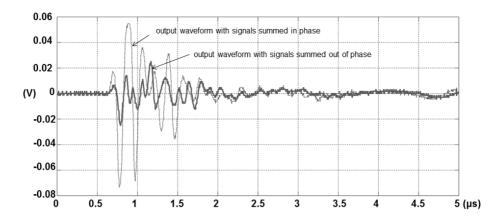

An Rx matrix transducer prototype has been manufactured by Oldelft Ultrasound B.V. The electrical impedance of 9 active transducer elements has been measured in water. Figure 2.9 shows the magnitude and phase diagrams for 9 elements. In order to acquire the parameters of the lumped-element impedance model for each measured element, we used ZView [2.20] for data fitting and model extraction. The extracted model is the same as shown in Fig. 2.2, and is redrawn in Fig. 2.10. It consists of a series RCL branch (R<sub>s</sub>, C<sub>s</sub>, L<sub>s</sub>) that represents the mechanical part of the transducer and a shunting capacitor (C<sub>p</sub>) that represent the dielectric property. Typical values for the model parameters are derived using data from the averaged magnitude and phase based on the measurement of 9 transducer elements. The fitting errors are also indicated in Fig. 2.10. Fig. 2.11 shows the modeled impedance plot (magnitude and phase) compared to the average impedance (magnitude and phase) obtained based on measurement.

Fig. 2.9 Electrical impedance measurement of 9 Rx transducer elements: (a) magnitude plot, (b) phase plot. (dashed line: average value)

Fig. 2.10 Electrical model of the Rx transducer element with typical model parameters derived from the measured impedance of 9 transducer elements.

Fig. 2.11 Electrical impedance of the Rx transducer element: extracted model (dashed line) versus the average impedance (solid line) based on the measurement of 9 transducer elements.

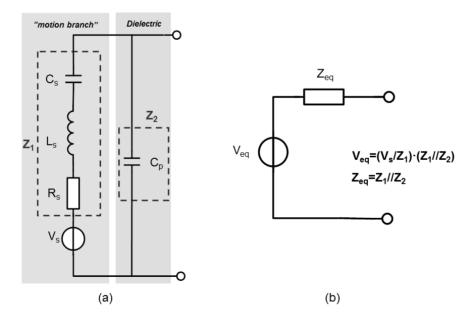

For the interface receive electronics, the Rx transducer works as a signal source. As described in Section 2.1.3, a voltage source  $V_s$  can be included in the impedance model (Fig. 2.12a). This voltage source mimics the transduction from the mechanical domain to the electrical domain and provides the signal that needs to be detected. The model in Fig. 2.12a can be transformed into a Thévenin equivalent circuit for easy observation of sensitivity variations among the elements. As shown in Fig. 2.12b, the equivalent circuit consists of two elements: the equivalent voltage source  $V_{eq}$  and the equivalent source impedance. The equivalent source impedance is derived by shorting the voltage source  $V_s$  and looking into the output terminals of the transducer. The resulting impedance is exactly the same as the impedance model shown in Fig. 2.11. It can be seen that at the resonant frequency, the average source impedance is about 2.5 k $\Omega$ .

Fig. 2.12 Electrical model of a piezoelectric transducer element in the receive mode: (a) lumped model with a voltage source inserted in the "motion branch", (b) Thévenin equivalent circuit.

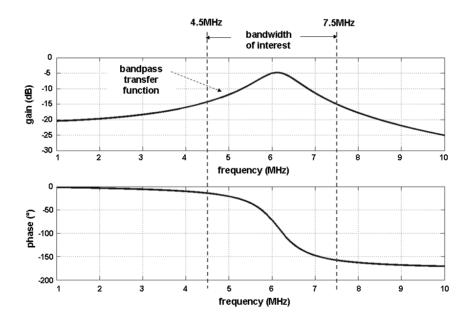

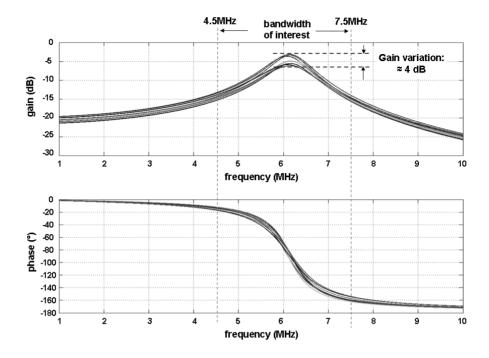

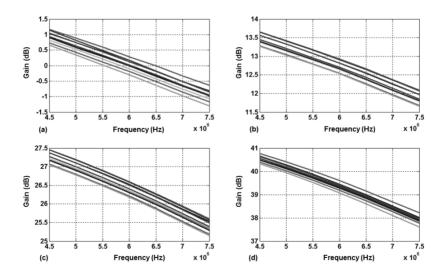

The equivalent voltage source  $V_{eq}$  can be understood as the original source  $V_s$  passing through a band-pass filtering network. Figure 2.13 plots the transfer function of the filtering network  $H = V_{eq}/V_s$  using the typical model parameters. For our transducer, the frequency band of interest in the receive mode is from 4.5 MHz to 7.5 MHz, with a center frequency of 6 MHz. From Fig. 2.9, we can see that the transducer impedance varies from element to element. It is important to know how the impedance variations affect the sensitivities of transducer elements. The analysis on the transfer functions of the filtering network among various transducer elements gives us an order-of-magnitude estimation of the gain variations, or sensitivity variations, that are introduced by the transducer elements themselves. Figure 2.14 shows the transfer functions (gain plot) based on the model parameters of 9 elements. It can be seen from Fig. 2.14 that the sensitivity variation introduced by the transducer elements themselves is about 4 dB within the bandwidth of interest.

Fig. 2.13 Transfer function (gain plot) of the electrical filter network based on the transducer electrical model (typical model parameters are used).

Fig. 2.14 Transfer function (gain plot) of the electrical filter network based on transducer electrical models (model parameters of 9 transducer elements are used).

## 2.3.3 Requirements for Interconnection and Rx Electronics

The analysis of the transducer characteristics provides important implications for the transducer-to-chip interconnection design and the Rx interface electronics design.

## For the transducer-to-chip interconnection design:

## Geometric constraints

Since the space in the TEE probe tip is limited (length: 2 cm, width: 1 cm and height: 1 cm), the most space-saving assembly is to stack the ASIC and the Rx transducer. The overall structure including the Rx transducer, the ASIC, the intermediate layers for connection, plus the Tx transducer, must fit into the available space.

## • Temperature constraints

The piezo-material used to build the Rx transducer (CTS 3203HD) has a Curie temperature of 225°C. To avoid de-polarization (see Section 2.1.1) of the piezo-material during the interconnection process, the process temperature must be controlled well below 225°C and preferably below 50% of the Curie temperature. This requirement imposes a restriction on the choices of interconnection solutions.

## For the Rx electronics design:

## Area constraints

The area of the ASIC should fit within the area of the Rx transducer array. Slight extensions on three sides under the Rx transducer array are permitted. No extension is allowed on the fourth side of the ASIC, because this side is adjacent to the Tx transducer array (Fig. 2.6). The area directly underneath the Rx array is reserved for circuits and bond-pads arranged in a matrix pattern that can be connected to the Rx transducer array. The output signal pads, power pads and some control pads can be placed in the three extended side areas of the ASIC

## • Noise requirement for the readout electronics

As described in Section 2.2.3, the lower bound of the transducer detection limit is set by the noise of the transducer itself. The resistor  $R_s$  in the impedance model (Fig. 2.10) is the noise source. It has a thermal noise density of about  $6.75\times 10^{-17}~V^2/Hz$  (calculated based on the typical model parameter  $R_s$  = 3.95 k $\Omega$ ). The noise is band-pass filtered by the transducer impedance network. To have an order-of-magnitude estimation of the noise generated by the transducer element itself, we chose the bandwidth 4.5 MHz to 7.5 MHz as the noise bandwidth of the transducer. The resulting noise voltage is about 15  $\mu V_{rms}$  over the bandwidth of interest. In practice, the readout circuit will also introduce noise. A proper readout circuit should be designed in such a way that it should have an input referred noise level no larger than the noise level of the transducer element.

## Accuracy requirement

As analyzed in Section 2.3.2, the gain variation of the transducer elements is on the order of 4 dB. Elements with such gain variations are acceptable for producing ultrasound images with good quality. However, to ensure an overall accuracy of the ultrasound receiver, the gain variation of the receive electronics must be below the gain variations of transducer elements.

## 2.4 Conclusions

In this chapter, a comprehensive study on piezoelectric transducers is given. The contents cover the fundamental device physics of the transducers, their structure, the operating principle, their modeling, important signal characteristics, etc. Great emphasis is on the analysis of the Rx transducer, which has been chosen to be used for this thesis project. From the analysis, we obtained meaningful considerations for the electronics design, as well as the interconnection design, which will be presented in the following chapters.

## 2.5 References

- [2.1] J. Karki, "Signal Conditioning Piezoelectric Sensors", *Texas Instrument Application Report*, SLOA033A, Sept. 2000.

- [2.2] S.C. Cobbold, *Foundations of Biomedical Ultrasound*, Oxford University Press, 2007.

- [2.3] A. Arnau, *Piezoelectric Transducers and Application*, Berlin: Springer, 2008.

- [2.4] P.L.M.J. van Neer, *Ultrasonic Superharmonic Imaging*, PhD thesis: Department of Biomedical Engineering, Erasmus University, 2010.

- [2.5] P. Hoskins, K. Martin, A. Thrush, *Diagnostic Ultrasound Physics and Equipment*, Cambridge University Press, 2010.

- [2.6] MP Interconsulting, *Piezoelectric Transducers Modeling and Characterization*, Aug. 2004.

Available at: http://www.mpi-ultrasonics.com/transducers1.html

- [2.7] K. Iniewski, *Medical Imaging, Principles, Detectors and Electronics*, New Jersey: John Wiley & Sons, 2009.

- [2.8] http://en.wikipedia.org/wiki/Piezoelectric\_sensor (July 2011).

- [2.9] H.W. Persson, "Electric excitation of ultrasound transducers for short pulse generation", *Ultrasound in Med. & Biol.*, vol. 7, pp.285-291, 1981.

- [2.10] J. Salazar, A. Turó, J.A. Chávez, J.A. Ortega, M.J. García, "Transducer resolution enhancement by combining different excitation pulses", *Ultrasonics*, vol.38, pp.145-150, 2000.

- [2.11] FDA Regulation, "Guidance for Industry and FDA Staff Information for Manufacturers Seeking Marketing Clearance of Diagnostic Ultrasound Systems and Transducers", Sept. 2008. Available at: http://www.fda.gov/medicaldevices/deviceregulationandguidance/guidanced ocuments/ucm070856.htm#1 (January 2012).

- [2.12] M.A. Averkiou, D.N. Roundhill, J.E. Powers, "A new imaging technique based on the nonlinear properties of tissues", *Proceedings IEEE Ultrasonics Symposium*, vol. 2, pp. 1561-1566, Toronto, Oct. 1997.

- [2.13] F. Tranquart, N. Grenier, V. Eder, L. Pourcelot, "Clinical use of ultrasound tissue harmonic imaging", *Ultrasound Med Biol.* vol. 25, no. 6, pp. 889-94, Jul. 1999.

- [2.14] P. L. M. J. van Neer, G. Matte, M.G. Danilouchkine, C. Prins, F. Van Den Adel, N. De Jong, "Super-harmonic imaging: development of an interleaved phased-array transducer", *IEEE Transactions on Ultrasonics, Ferroelectrics and Frequency Control*, vol. 57, issue 2, pp. 455-468, Feb. 2010.

- [2.15] L. Demi, M. D. Verweij, N. de Jong, K. W. A. van Dongen, "Modeling nonlinear acoustic wave fields in media with inhomogeneity in the attenuation and in the nonlinearity", *Proceedings IEEE Ultrasonics Symposium*, 2010, pp. 2056-2059.

- [2.16] L. Demi, M. D. Verweij, N. de Jong, K. W. A. van Dongen, "Modeling nonlinear medical ultrasound via a linearized contrast source method", *Proceedings IEEE Ultrasonics Symposium*, 2010, pp. 2175-2178.

- [2.17] S. Blaak, Z. Yu, G.C.M. Meijer, C. Prins, C. T. Lancée, J. G. Bosch, N. de Jong, "Design of a micro-beamformer for a 2D piezoelectric ultrasound transducer", *Proceedings IEEE Ultrasonics Symposium*, 2009, pp. 1338-1341.

- [2.18] S. Blaak, C. T. Lancée, J. G. Bosch, C. Prins, A. F. W. van der Steen, N. de Jong, "A matrix transducer for 3D transesophageal echocardiography with a separate transmit and receive subarray", *Proceedings IEEE Ultrasonics Symposium*, 2011.

- [2.19] CTS Corporate, "PZT5A &5H Materials Technical Data", available at: http://www.ctscorp.com/components/pzt/downloads/PZT\_5Aand5H.pdftrans ducer material. (January 2012).

- [2.20] Scribner Associates, Inc., ZView, http://www.scribner.com/zplot-and-zview-for-windows-software-downloads.html (January 2012).

# Front-End Receive-Signal Processing for 3D TEE

In Chapter 2, the characteristics of an Rx ultrasound transducer that is optimized for 3D TEE imaging have been discussed. This transducer contains  $45 \times 45$  elements and is located in the tip of a TEE probe. As introduced in Chapter 1, in order to make the signal acquisition of this transducer via a limited number (less than 250) of cables possible, a frontend application-specific integrated circuit (ASIC) is required to be bonded to the transducer and to provide "appropriate" signal processing in the probe tip to reduce the channel count. The meaning of the word "appropriate" is twofold. Firstly, the signal processing scheme must match with the signal characteristics of the transducer, so that useful information can be extracted from the output signals of the ASIC to form images. Secondly, since the ASIC is also located in the tip of the TEE probe, its size and power consumption cannot be arbitrarily large. Therefore, the signal-processing scheme must be designed in such a way that it is efficient enough to keep the ASIC compact and practically usable in a TEE probe. On the basis that the image quality is not degraded, simple signal-processing scheme is desired. With these considerations in mind, system-level studies have been carried out to derive an effective scheme for front-end signal-processing. The results are described in this chapter. Section 3.1 presents the proposed front-end

43

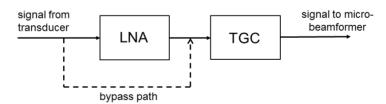

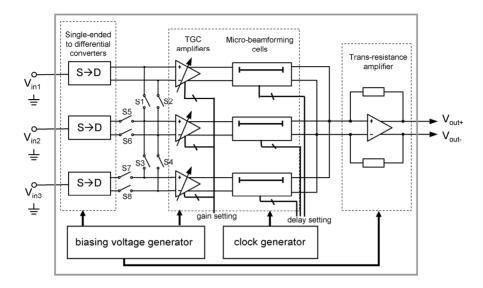

receiver-signal-processing chain, which consists of low-noise amplifiers (LNAs), time-gain-compensation (TGC) amplifiers and analog microbeamformers. To reduce the design complexity, we made simplifications to the TGC scheme and the analog micro-beamforming scheme (Section 3.2). Section 3.3 gives an overview of the ASIC design and its associated requirements.

## 3.1 Architecture of the Receive-Signal Processing

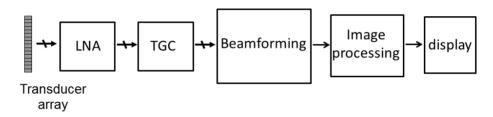

Fig. 3.1 Block diagram of a conventional receive-signal processing flow for ultrasound array transducers.

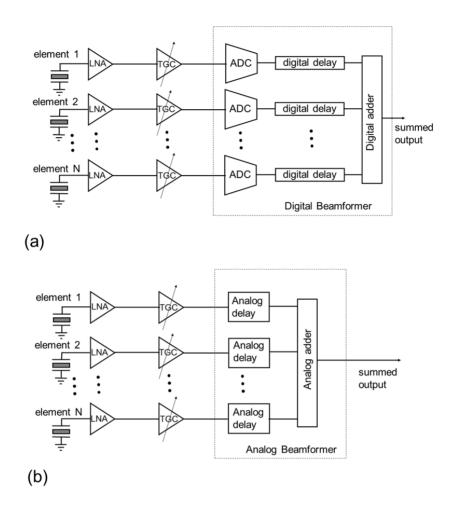

The block diagram of a conventional receive-signal processing flow for an ultrasound array-transducer is depicted in Fig. 3.1. It consists of five function modules: low-noise amplifiers (LNAs), time-gain-compensation (TGC) amplifiers, an Rx beamformer, an image processing module and a display module. Signals from transducer elements are first amplified by LNAs with a proper gain to boost the signal level above the noise level of the remaining circuitry. As described in Section 2.2.2, ultrasound signals experience propagation attenuation. Echo signals from deep tissue are more attenuated than those from nearby tissue and they also take more time to reach the probe. This time-dependent attenuation can be compensated for by using TGC amplifiers, which are able to amplify echo signals with a gain that increases exponentially with time (linearly in decibels). This compensation helps to maintain image uniformity and relaxes the dynamic-range requirements for the remaining circuitry. After TGC amplification, Rx

beamforming is applied. The beamforming principle is based on delaying the signals relative to each other in such a way that waves from a certain point, the focal point, arrive simultaneously and can be coherently summed. The summed signal is further processed in the imaging processing module, where envelope estimation, compression, etc., take place [3.1][3.2]. Finally, an image is formed which can be seen on the display.

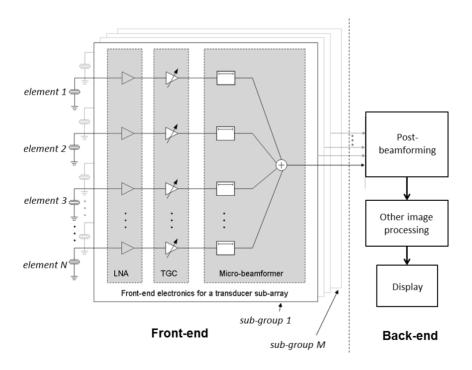

In our 3D TEE application, the aforementioned Rx signal processing flow applies. However, for a practical implementation, proper partitioning of the system is necessary to divide the whole flow into a front-end and a back-end. The front-end processing is realized in an ASIC in the TEE probe tip, while the back-end processing occurs in an external imaging system.

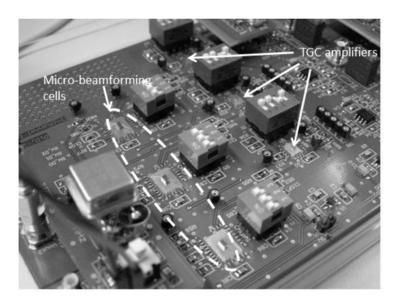

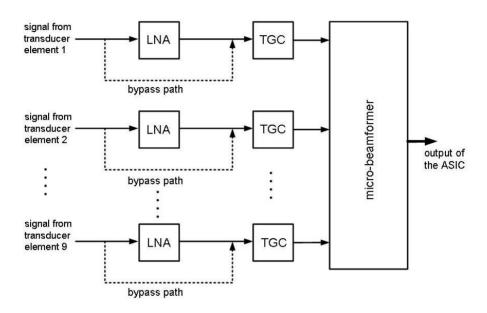

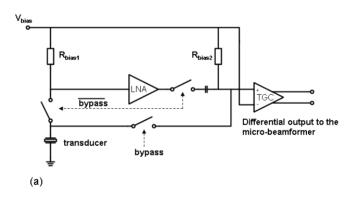

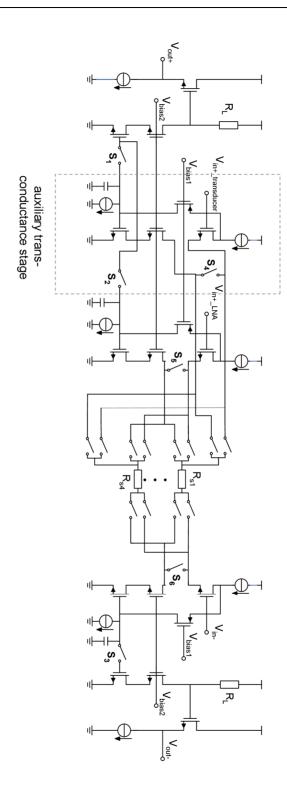

Fig. 3.2 Receive signal processing architecture for 3D TEE (N=9 and M=225).

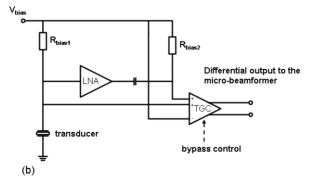

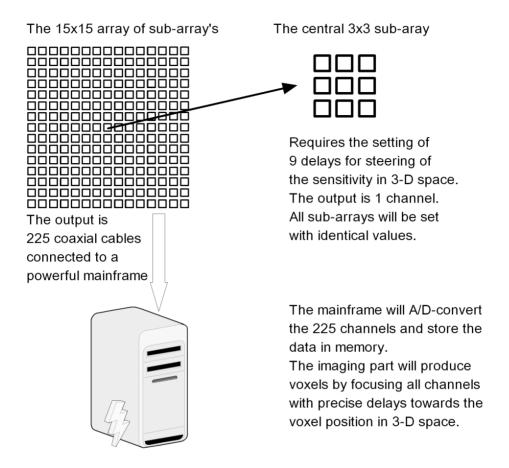

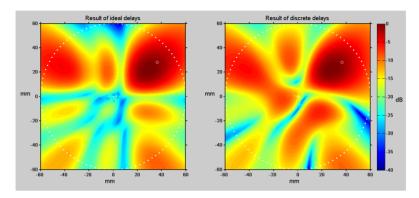

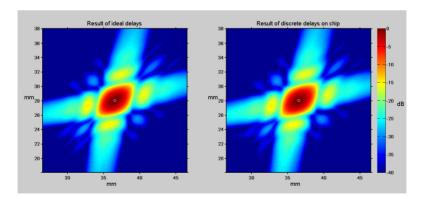

As discussed above, in our project, an Rx transducer with  $45 \times 45$  transducer elements is used and channel-count reduction in the probe tip is a must. Therefore, the delay-and-sum beamforming function is needed in the frontend processing. However, the complete beamforming function requires a

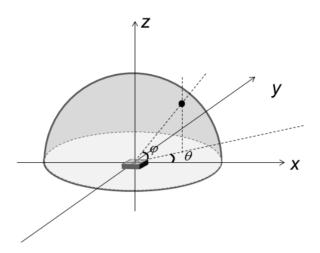

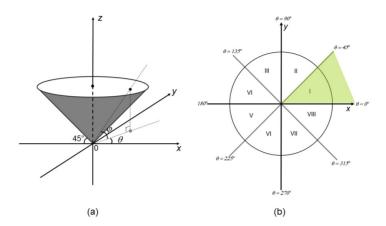

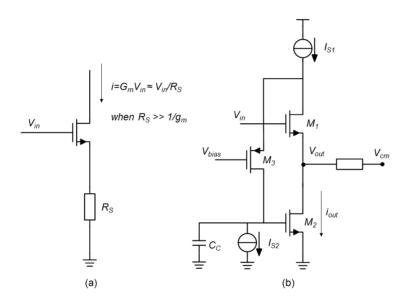

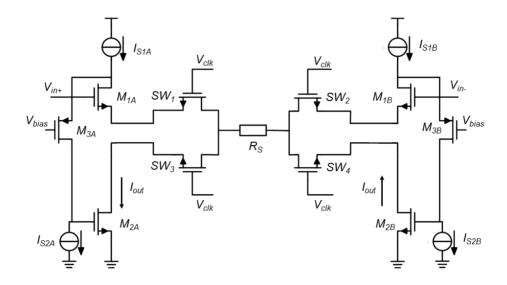

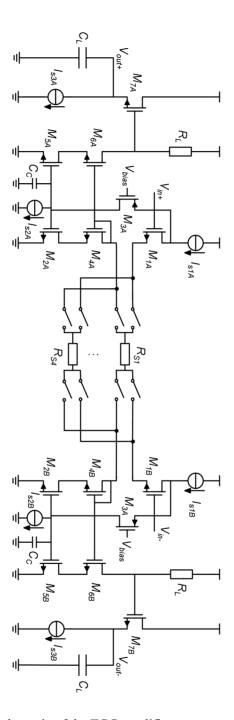

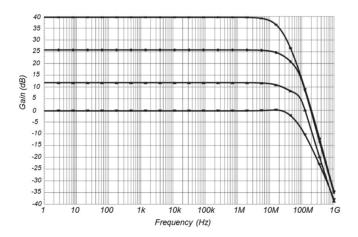

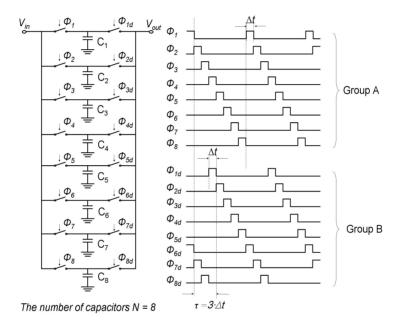

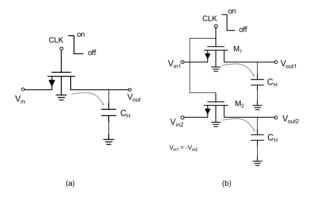

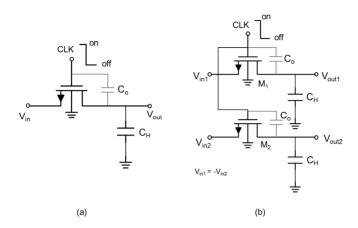

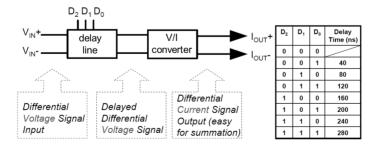

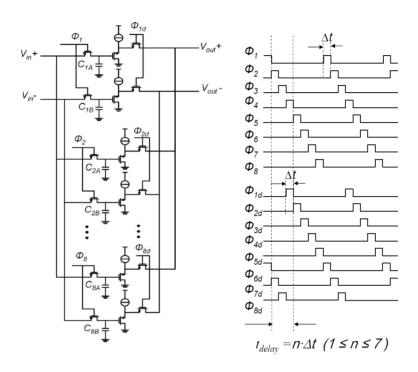

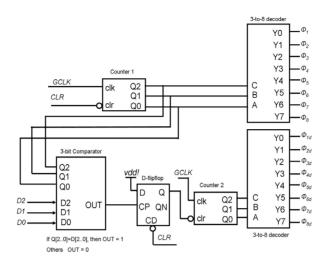

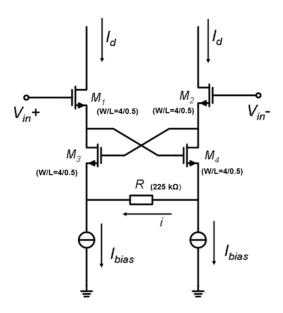

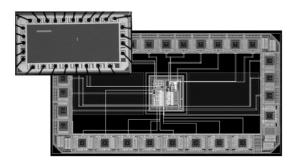

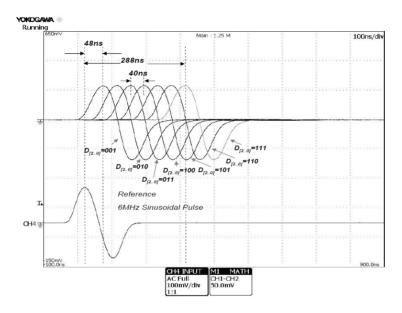

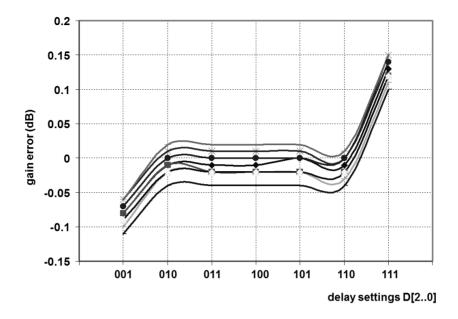

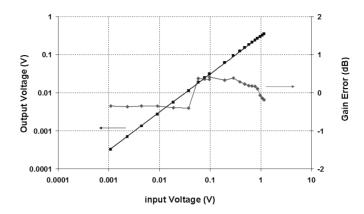

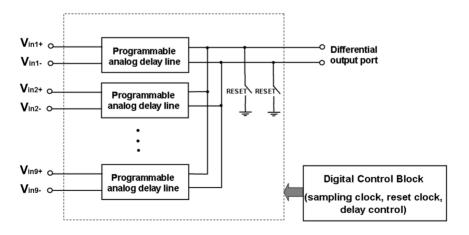

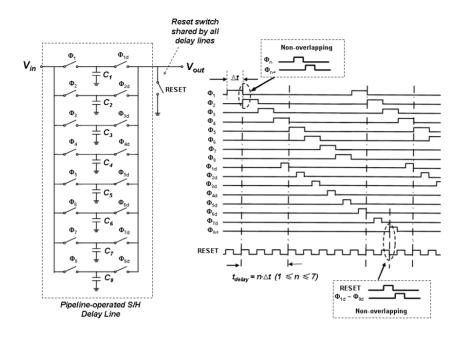

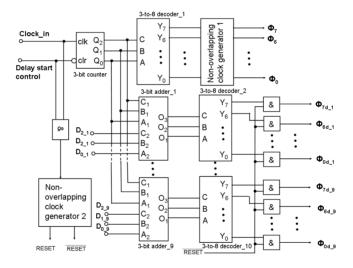

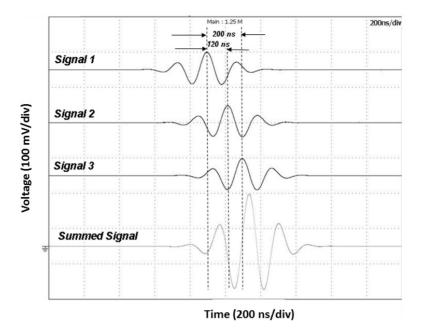

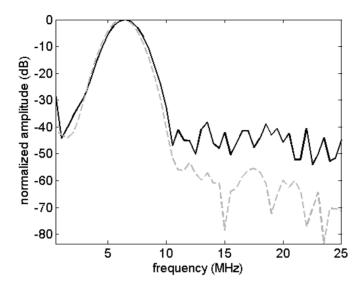

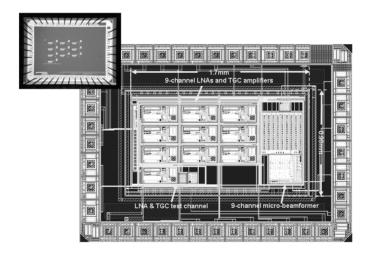

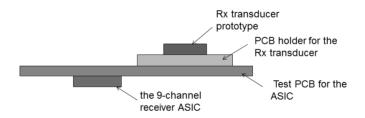

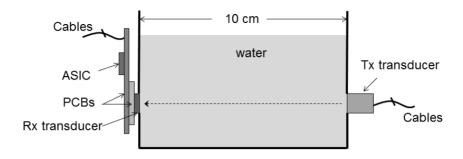

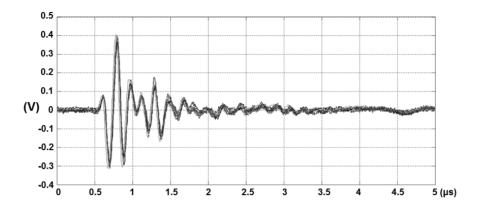

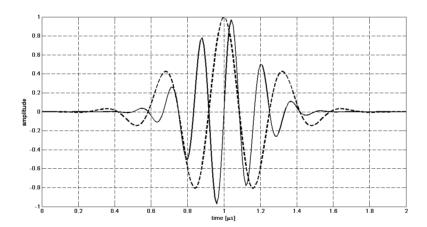

2025:1 channel count reduction, which is impractical to be fully implemented in the ASIC due to overcomplicated electronics. A greater channel-count reduction is likely to require more power consumption and more die area. In view of these factors, the so-called "sub-array beamforming architecture" [3.3] has been chosen. The complete beamforming task is divided into "pre-beamforming" or "microbeamforming", which is implemented in the front-end ASIC, and "postbeamforming", which is implemented in the external imaging system. The micro-beamforming is done in such a way that the large matrix transducer is divided into sub-groups and delays are applied to signals received by the transducer elements within a group to align them in time (Fig. 3.2). Since elements in a sub-group are chosen to be close to each other in space, only fine delays are needed. Realizing these fine delays is feasible with front-end electronics in the TEE probe tip. The delayed signals are summed up to achieve the channel count reduction. We call the circuit which realizes the micro-beamforming function the "micro-beamformer". Each transducer subgroup has its own micro-beamformer. All micro-beamformers operate simultaneously and their output signals are transmitted via micro-coaxial cables to the external imaging system, where post-beamforming takes place. In post-beamforming, a coarse delay is applied to the signals from each subgroup, so that all the signals can be aligned in time and finally summed up.