#### Fan-Out SiC MOSFET Power Module in an Organic Substrate

Hou, Fengze

10.4233/uuid:32355f3a-a62d-4a03-bcc9-a04e904a3ab9

**Publication date**

**Document Version** Final published version

Citation (APA)

Hou, F. (2020). Fan-Out SiC MOSFET Power Module in an Organic Substrate. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:32355f3a-a62d-4a03-bcc9-a04e904a3ab9

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# FAN-OUT SIC MOSFET POWER MODULE IN AN ORGANIC SUBSTRATE

## FAN-OUT SIC MOSFET POWER MODULE IN AN ORGANIC SUBSTRATE

#### **Proefschrift**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus Prof.dr.ir. T.H.J.J. van der Hagen, voorzitter van het College voor Promoties, in het openbaar te verdedigen op donderdag 25 Juni 2020 om 15:00 uur

door

## Fengze Hou

Master of Science in Mechatronic Engineering, Guilin University of Electronic Technology, Guilin, China geboren te Shanxi, China. This dissertation has been approved by the promotors.

Promotor: Prof. dr. G.Q. Zhang Promotor: Prof. dr. J.A. Ferreira

#### Composition of the doctoral comittee:

Rector Magnificus, Chairman

Prof. dr. G.Q. Zhang, Delft University of Technology

Prof. dr. J.A. Ferreira, University of Twente

*Independent members:*

Prof. dr. X.J. Fan, Lamar University, USA

Prof. dr. W.D. van Driel, Delft University of Technology

Prof. dr. Y.F. Qiu, Xiamen University

Prof. dr. L.Q. Cao, Institute of Microelectronics of Chinese Academy of Sciences

Dr. ir. R.H. Poelma, Nexperia

Reserve member:

Prof. dr. P.M. Sarro, Delft University of Technology

Keywords: SiC MOSFET; phase-leg power module; fan-out packaging; organic sub-

strate; material characterization; static characterization; switching characterization; microchannel thermal management; two-phase cooling.

Printed by: Gilde Print

Copyright © 2020 by Fengze Hou

ISBN 978-94-6402-349-7

An electronic version of this dissertation is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

To My Family Fengze Hou

## **CONTENTS**

| No             | menc  | lature    |                                                        | xi |

|----------------|-------|-----------|--------------------------------------------------------|----|

| Su             | mma   | ry        |                                                        | 1  |

| Sa             | menv  | atting    |                                                        | 3  |

| 1 Introduction |       |           |                                                        |    |

|                | 1.1   |           | ound                                                   |    |

|                | 1.2   |           | al of SiC power devices                                |    |

|                | 1.3   |           | OSFET                                                  |    |

|                | 1.4   |           | ational packaging technology                           |    |

|                | 1.5   |           | ns of the conventional packaging                       |    |

|                | 1.6   | Advanc    | eed packaging technology                               | 6  |

|                | 1.7   |           | nges of the advanced packaging                         |    |

|                |       | 1.7.1     | Material selection                                     |    |

|                |       | 1.7.2     | Packaging technology                                   |    |

|                |       | 1.7.3     | Performance characterization                           |    |

|                |       | 1.7.4     | Heat dissipation                                       |    |

|                | 1.8   | The lay   | rout of this dissertation                              | 10 |

|                | Refe  | rences.   |                                                        | 11 |

| 2              | Revi  | ew of pa  | ackaging technologies for power module                 | 19 |

|                | 2.1   | Packag    | ing techniques for the Si power module                 | 20 |

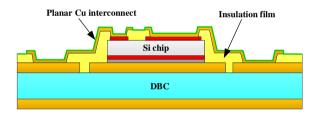

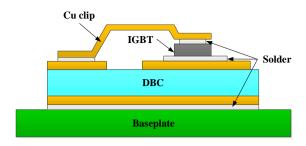

|                |       | 2.1.1     | Planar packaging                                       | 20 |

|                |       | 2.1.2     | Press-pack packaging                                   | 23 |

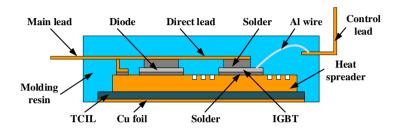

|                |       | 2.1.3     | Embedding packaging                                    | 24 |

|                |       | 2.1.4     | 3D packaging                                           | 31 |

|                |       | 2.1.5     | Hybrid packaging                                       | 33 |

|                | 2.2   | Packag    | ing schemes for SiC power module                       | 36 |

|                |       | 2.2.1     | Planar packaging                                       | 36 |

|                |       | 2.2.2     | Press-pack packaging                                   | 39 |

|                |       | 2.2.3     | 3D packaging                                           |    |

|                |       | 2.2.4     | Hybrid packaging                                       | 41 |

|                | 2.3   | Summa     | ıry                                                    | 44 |

|                | Refe  | rences.   |                                                        | 44 |

| 3              | Selec | ction an  | d characterization of SiC MOSFET and organic substrate | 49 |

|                | 3.1   | Selection | on and characterization of SiC MOSFET                  | 50 |

|                |       | 3.1.1     | Selection of SiC MOSFET                                | 53 |

|                |       | 3.1.2     | Experimental approach                                  |    |

|                |       | 3.1.3     | Experimental results                                   |    |

VIII CONTENTS

|   | 3.2   | Selecti  | on and characterization of organic substrate          |   |       |     |

|---|-------|----------|-------------------------------------------------------|---|-------|-----|

|   |       | 3.2.1    | Selection of organic substrate materials              |   |       | 59  |

|   |       | 3.2.2    | Experimental approach                                 |   |       | 61  |

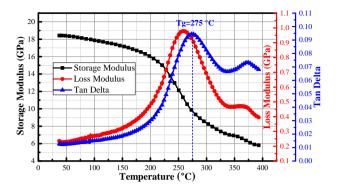

|   |       | 3.2.3    | Experimental results                                  |   |       | 62  |

|   | 3.3   | Summa    | ary                                                   |   |       | 70  |

|   | Refe  | rences.  |                                                       | • |       | 71  |

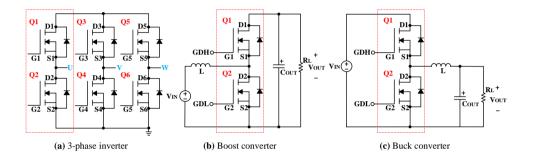

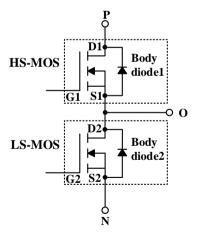

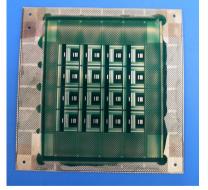

| 4 | Fan-  | out SiC  | MOSFET power module in an organic substrate           |   |       | 73  |

|   | 4.1   | Phase-   | leg SiC MOSFET power module                           |   |       | 74  |

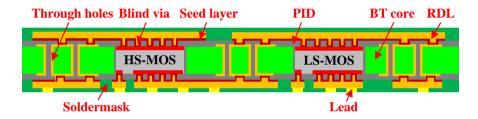

|   | 4.2   | Fan-ou   | tt SiC MOSFET power module packaging                  |   |       | 75  |

|   |       | 4.2.1    | Packaging structure design                            |   |       | 75  |

|   |       | 4.2.2    | Parasitic inductances extraction                      |   |       | 76  |

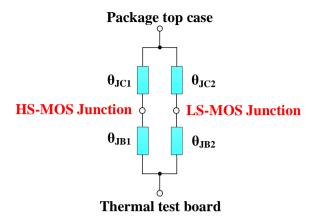

|   |       | 4.2.3    | Thermal modeling analysis                             |   |       | 79  |

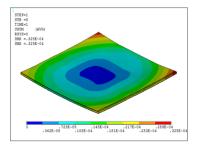

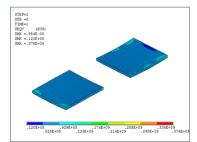

|   |       | 4.2.4    | Thermo-mechanical virtual prototyping                 |   |       | 80  |

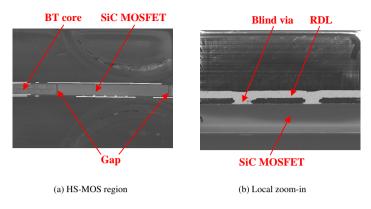

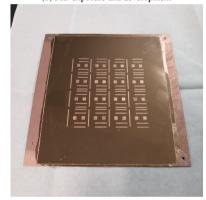

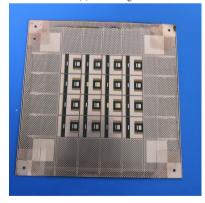

|   | 4.3   | Fan-ou   | at packaging process in an organic substrate          |   |       | 83  |

|   |       | 4.3.1    | Overall packaging process                             |   |       | 83  |

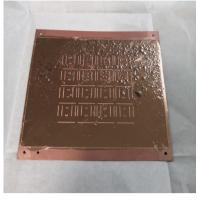

|   |       | 4.3.2    | PID exposure and development technique                |   |       | 84  |

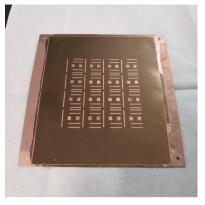

|   |       | 4.3.3    | Panel-level PVD technique                             |   |       | 85  |

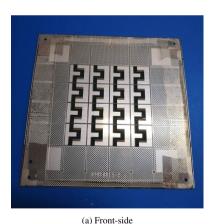

|   |       | 4.3.4    | Double-sided RDL interconnection technique            |   |       | 86  |

|   | 4.4   |          | ary                                                   |   |       | 89  |

|   | Refe  | rences.  |                                                       | • | <br>• | 89  |

| 5 | Stati | c and d  | ynamic characterizations of SiC MOSFETs               |   |       | 91  |

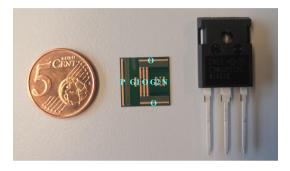

|   | 5.1   |          | mental sample                                         |   |       | 92  |

|   | 5.2   | Static o | characterization                                      |   |       | 93  |

|   |       | 5.2.1    | Experimental approach                                 |   |       | 93  |

|   |       | 5.2.2    | Experimental results                                  |   |       | 93  |

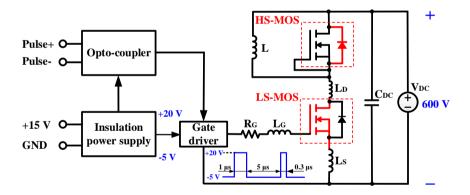

|   | 5.3   | Dynam    | nic characterization                                  |   |       | 97  |

|   |       | 5.3.1    | Experimental approach                                 |   |       | 97  |

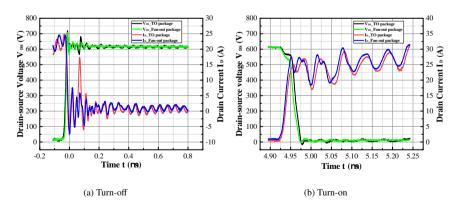

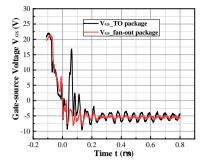

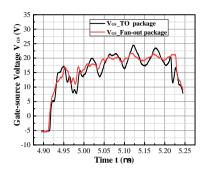

|   |       | 5.3.2    | Experimental results                                  |   |       | 98  |

|   | 5.4   | Summa    | ary                                                   |   |       | 99  |

|   | Refe  | rences.  |                                                       |   |       | 99  |

| 6 | Mici  | ochann   | nel thermal management system with the two-phase flow |   |       | 101 |

|   | 6.1   | Design   | of thermal management                                 |   |       | 102 |

|   |       | 6.1.1    | Two-phase cooling for the fan-out SiC MOSFET          |   |       | 102 |

|   |       | 6.1.2    | TTVs                                                  |   |       | 103 |

|   |       | 6.1.3    | VCRS                                                  |   |       | 104 |

|   |       | 6.1.4    | MHS component                                         |   |       |     |

|   |       | 6.1.5    | Other components                                      |   |       |     |

|   |       | 6.1.6    | Thermodynamic analysis of R1234yf refrigerant         |   |       |     |

|   | 6.2   |          | s and discussion                                      |   |       |     |

|   |       | 6.2.1    | Cooling performance evaluation with TTV1              |   |       |     |

|   |       | 6.2.2    | Effect of the rotational speed of the compressor      |   |       |     |

|   |       | 6.2.3    | Effect of the opening of the throttling device        |   |       |     |

|   |       | 6.2.4    | Effect of TTV layout on MHS                           |   |       |     |

|   |       | 6.2.5    | Effect of a downstream heater                         |   |       | 115 |

| Contents | ix |

|----------|----|

|----------|----|

|     |            | 6.2.6 Discussion on cooling performance enhancement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 118 |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7   | 7.1<br>7.2 | Conclusions Contributions, and recommendations  Conclusions Contributions Contribution Contributio | 123 |

| Ac  | know       | ledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 127 |

| Lis | st of p    | publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 131 |

## **Nomenclature**

$A_{\mathrm{GD}}$  Gate-drain overlap area  $\alpha_{\mathrm{A}}$  CTE of material A  $\alpha_{\mathrm{B}}$  CTE of material B  $\sigma_{\mathrm{T}}$  Thermally-induced stress

$\sigma_{\rm T}$  Thermally-induced stress  $C_{\rm DS}$  Drain-source capacitance

$C_{\rm GD}$  Gate-drain capacitance (Miller capacitance)

$C_{\mathrm{GDJ}}$  Nonlinear depletion capacitance

$C_{GS}$  Gate-source capacitance  $C_{ISS}$  Input capacitance  $C_{OSS}$  Output capacitance  $C_{OX}$  Gate oxide capacitance  $C_{RSS}$  Reverse capacitance  $C_{RSS}$  Thickness of material

EDielectric breakdown strength $E_A$ Young's modulus of material A $E_B$ Young's modulus of material B $\varepsilon_{\rm sic}$ Buck electron mobility of SiC

$I_{\rm D}$  Drain current  $I_{\rm G}$  Gate current M Fitting parameter

n Rotational speed of compressor

$N_{\rm D}$  Doping concentration

$\begin{array}{ll} P & \text{Pressure} \\ q & \text{Heat flux} \\ q_{\text{e}} & \text{Electron charge} \\ R_{\text{drift}} & \text{Drift layer resistance} \end{array}$

R<sub>on</sub> On-resistance

$\Delta T$  Temperature difference of two points along the heat path

$T_{\rm S}$  Saturation temperature

$t_{\rm GDI}$  Depletion thickness between gate and drain

t<sub>OX</sub> Gate oxide thickness

$\mu_{\rm A}$  Poisson's ratio of material A  $U_{\rm PT}$  Voltage of the pressure transducer  $U_{\rm VR}$  Voltage of the variable resistor

V<sub>bi</sub> Built-in potential between the P-body and the N-drift junction

V<sub>BD</sub> Dielectric breakdown voltage

$V_{\rm BR}$  Breakdown voltage of SiC MOSFET

$V_{\rm DS}$  Drain-source voltage  $V_{\rm GS}$  Gate-source voltage

xii Nomenclature

$V_{\rm T}$  Gate-drain overlap depletion threshold w Drain-source un-depleted drift width

$w_{\rm B}$  Thickness of N- drift layer  $w_{\rm DSI}$  Drain-source depletion width

Abbreviations

ABF Ajinomoto build-up film

$\begin{array}{ccc} Ag & Silver \\ Al & Aluminum \\ Al_2O_3 & Alumina \end{array}$

AlN Aluminum nitride

BGA Ball grid array

BT Bismaleimide triazine

CCL Copper clad laminate

Cr Chromium

CTE Coefficient of thermal expansion

Cu Copper

DBC Direct bonded copper DPT Double pulse test

DSC Differential scanning calorimetry

DUT Device under test

ECP Embedded component packaging

EMC Epoxy molding compound

FPC Flexible printed circuit

GaN Gallium nitride

GWP Global warming potential HEMT High-electron-mobility transistor

HP High-pressure

HS-MOS High-side SiC MOSFET

IGBT Insulated-gate bipolar transistor

JFET Junction gate field-effect transistor

LP Low-pressure

LS-MOS Low-side SiC MOSFET

LTCC Low temperature co-fired ceramic

MHS Microchannel heat sink

Mo Molybdenum

MOSFET Metal-oxide semiconductor field-effect transistor

Ni Nickel NP Nanoparticle

PCB Printed circuit board

PCoB Power chip on bus

PCoC Power chip-on-chip

PCoI Power chip-on-inductor

PID Photoimageable dielectric

PMMA Polymethyl methacrylate

POL Power overlay

Nomenclature xiii

ppm parts per million

PVD Physical vapor deposition

Qg Gate charge

RCC Resin-coated copper

RDL Redistribution layer

rpm Revolutions per minute

Si Silicon

SiC Silicon carbide Si<sub>3</sub>N<sub>4</sub> Silicon nitride

SiPLIT Siemens planar interconnect technology

Sn Tin

TBF Temporary bond film TC Thermocouple

TCIL Thermally conductive electrically insulated layer

Tg Glass transition temperature TGA Thermal gravimetric analyzer

Ti Titanium

TIM Thermal interface material TLP Transient liquid phase

TMA Thermal mechanical analyzer

TO Transistor outline

T-PM Transfer molded power module

TTC Thermal test chip

TTV Thermal test vehicle

UV Ultraviolet

VCRS Vapor compression refrigerant system

VDMOS Vertical diffused MOSFET

WBG Wide bandgap

## **SUMMARY**

G reduce the depletion of energy sources but also prevent global warming. Nowadays, 40% of worldwide energy is consumed as electrical energy, so a high-efficient electrical energy conversion is urgently required. The power module plays a critical role in electrical energy conversion. So far, silicon (Si) power devices have still been widely used in the power module. However, they are approaching the theoretical performance limits, which drastically reduces the power module's conversion efficiency. Instead, silicon carbide (SiC) power devices have a great application perspective due to their wider energy bandgap, lower intrinsic carrier concentration, and higher critical electrical field.

However, these superior characteristics cannot be exploited via current mainstream packaging technologies and materials. SiC devices cannot be used merely as a direct drop-in replacement of Si devices.

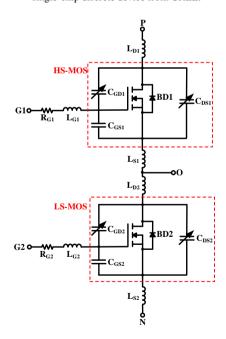

The current mainstream packaging technology for SiC devices is mainly wire-bonding interconnection combined with a direct-bonded copper substrate. However, the wire-bonds do not allow for double-sided cooling and add parasitic inductance, which affects the heat-dissipation efficiency and switching performance of SiC devices. The high parasitic inductance (> 10 nH) can induce voltage overshoots and electromagnetic interference issues when SiC devices are switching at fast speeds. The packaging materials used in the Si-based power module, e.g., die-attach and encapsulant, generally cannot withstand the high temperature and large-temperature cycle, limiting the application of SiC devices in the high temperature. Therefore, to fully explore the potential of SiC devices, it is essential to incorporate advanced packaging with device development.

With the ever-increasing power output and packaging density, SiC devices also face severe cooling challenges, although they can withstand higher temperatures. Their sizes are much smaller than similarly rated Si devices, leading to the high heat flux of SiC devices that could reach up to 1 kW/cm<sup>2</sup>. So, the high-efficient cooling schemes need to be developed to cope with the increasing heat flux.

In this dissertation, firstly, primary packaging schemes for Si power modules, which are the foundation of packaging methods of SiC ones, were reviewed. After that, attempts on packaging techniques for SiC power modules were thoroughly overviewed.

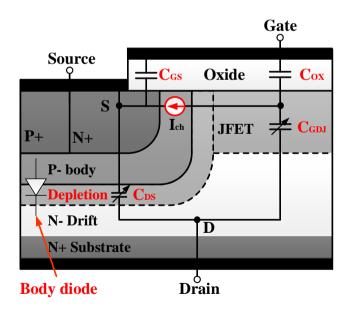

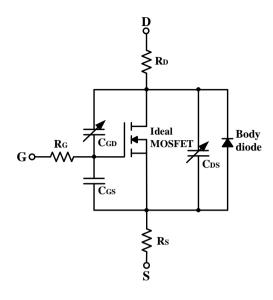

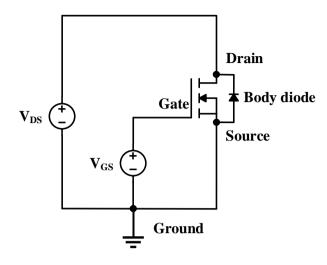

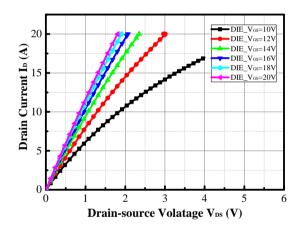

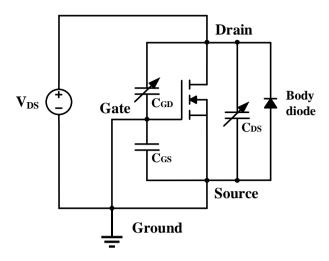

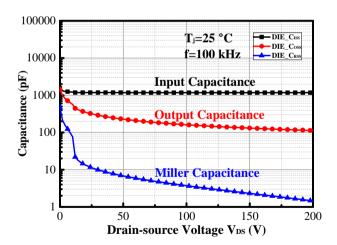

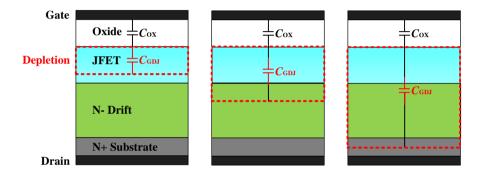

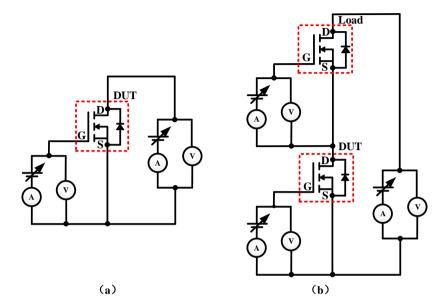

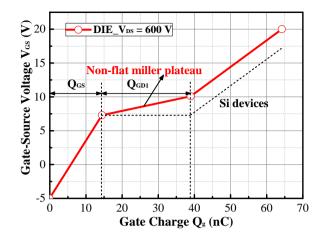

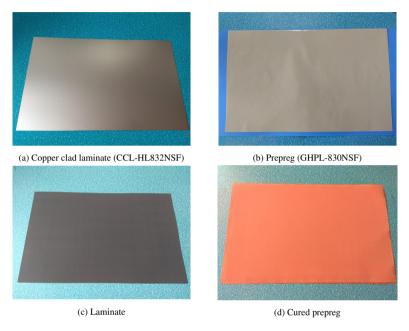

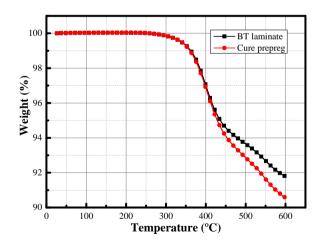

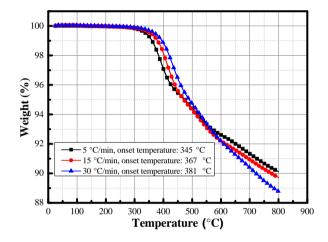

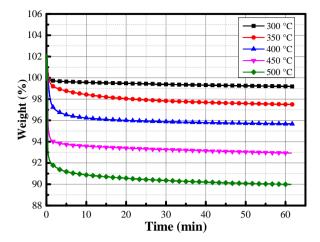

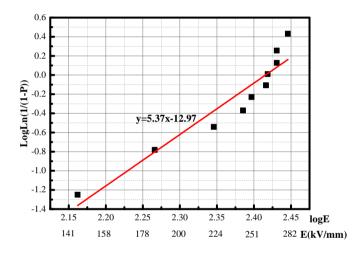

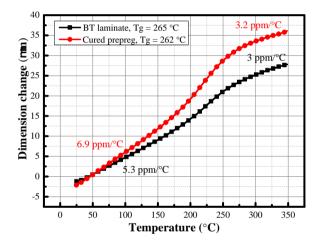

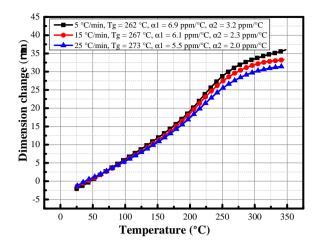

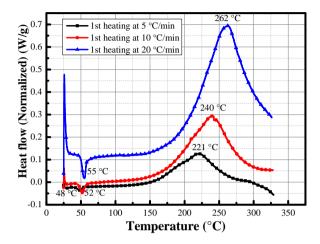

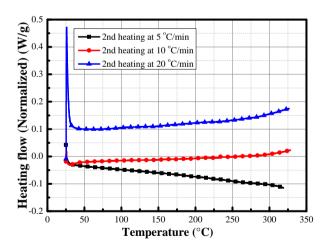

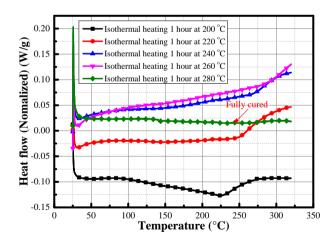

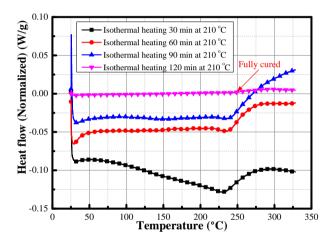

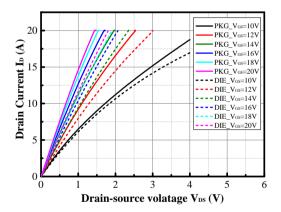

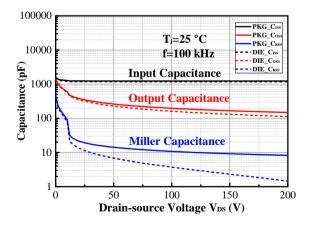

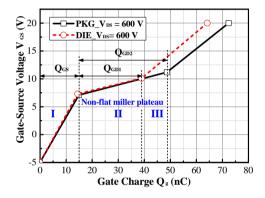

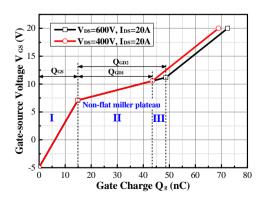

Secondly, SiC metal-oxide-semiconductor field-effect transistor (MOSFET) and organic substrate materials were selected and characterized. I-V, C-V, and gate charge characteristics of SiC MOSFET were analyzed via a custom fixture. The experimental results showed that SiC MOSFET had output characteristics of non-saturation, existed two distinct points in the curve of Miller capacitance versus drain-source voltage, and displayed a non-flat Miller platform. All of these are different from Si devices. After that, thermal stability, dielectric breakdown, thermo-mechanical performance, and cure kinetics of the organic substrate materials were characterized. The experimental results indicated that the substrate materials could withstand the high temperature of 300 °C and the high voltage of 46.9 kV.

2 Summary

The glass transition temperature was as high as over 260 °C, and the coefficient of thermal expansion was matching with SiC. Both one-hour curing at 280 °C and two-hour curing at 210 °C could ensure the full cure of the BT prepreg.

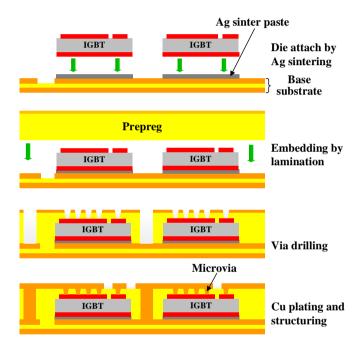

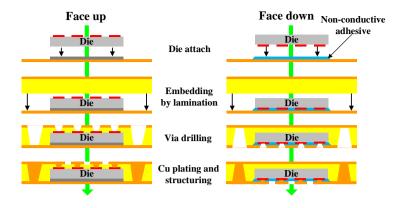

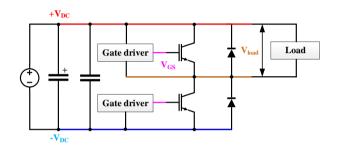

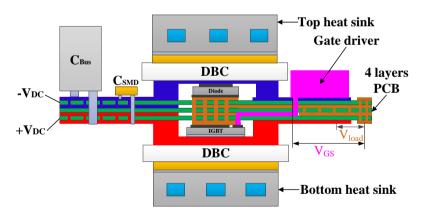

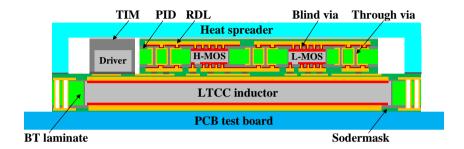

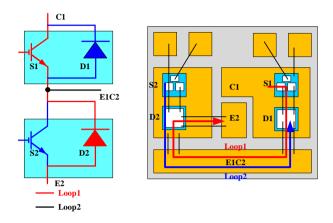

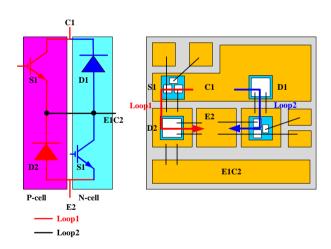

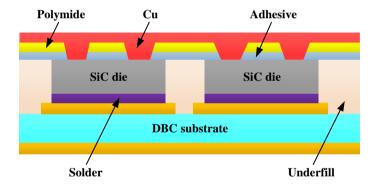

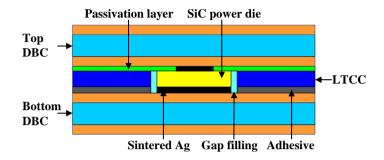

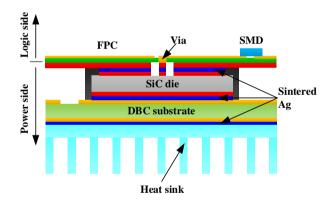

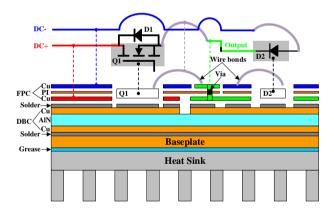

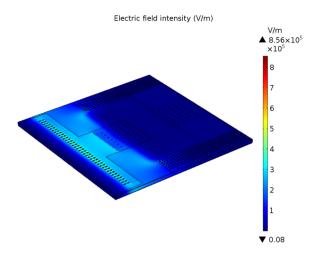

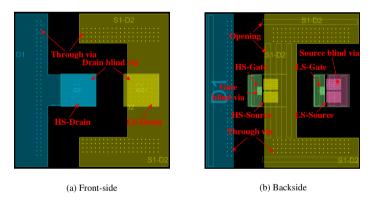

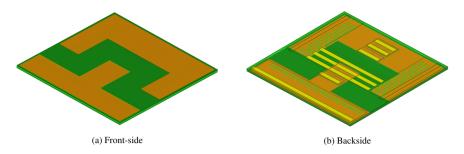

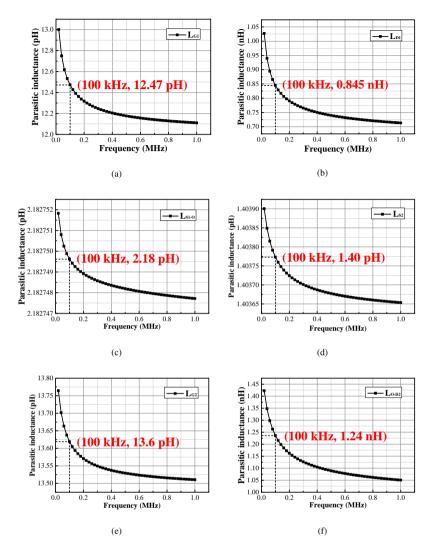

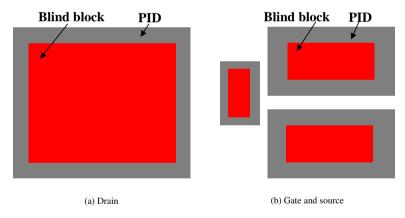

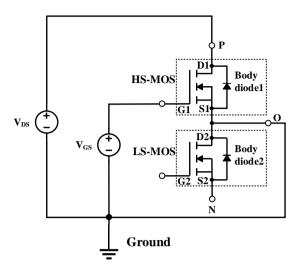

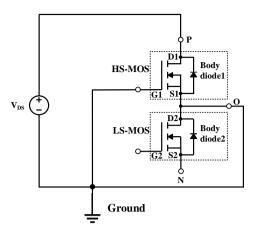

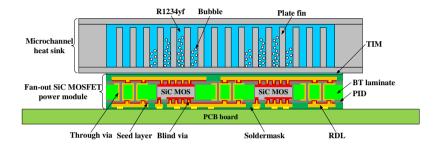

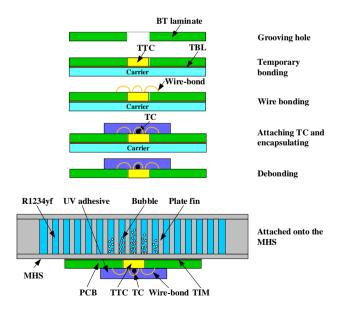

Thirdly, a novel fan-out panel-level packaging technology was proposed for a phase-leg SiC MOSFET power module. The high- and low-side SiC MOSFETs were embedded in an organic substrate, interconnected by double-sided redistribution layers (RDLs) and through vias, finally protected by double-sided soldermasks. Compared with current embedded packaging technologies for Si and GaN devices, the proposed packaging structure has several unique merits, such as structure symmetry and double-sided cooling. The electrical, thermal, and thermal-mechanical simulations were conducted to evaluate and optimize the fan-out packaging performance. After that, a detailed fan-out panel-level packaging process for the phase-leg SiC MOSFET power module was introduced. Three essential packaging processes, including exposure and development of photo imageable dielectric, panel-level physical vapor deposition (PVD), and double-sided RDL interconnection, could replace conventional laser drilling, chip/wafer-level PVD, and wire-bonding, respectively.

Fourthly, the static and dynamic characterizations of the fan-out SiC MOSFET power module were conducted. The effects of the fan-out packaging on I-V, C-V, and gate charge characteristics of SiC MOSFET were analyzed. It is found that the output characteristics of non-saturation of SiC MOSFET were more evident after packaging, and higher drive voltage was required to entirely turn on SiC MOSFET due to the extension of the non-flat Miller plateau. The double pulse test was used to evaluate and compare the switching characteristics of SiC MOSFET in the fan-out phase-leg power module and TO-247 discrete package. The results showed that the fan-out package had smaller voltage overshoot and current oscillation at turn-off and lower voltage oscillation and current overshoot at turn-on than TO-247 package.

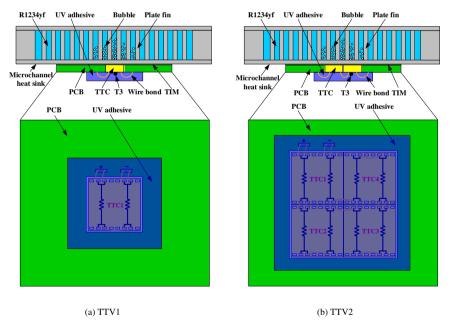

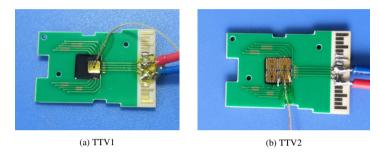

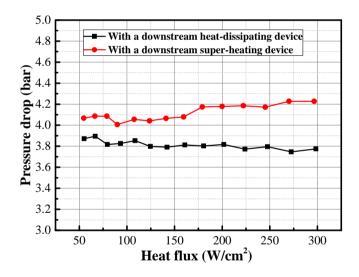

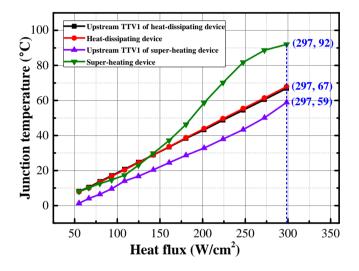

Fifthly, a microchannel thermal management with two-phase flow boiling using refrigerant R1234yf is presented. Both single- and multi-chip silicon thermal test vehicles (TTVs) based on substrate embedded technology were fabricated and attached to a microchannel heat sink (MHS) with two-phase cooling. A vapor compression refrigerant system was implemented to realize and control the phase-change of R1234yf. The system includes two identical aluminum MHSs connected in series, a gas flowmeter, a miniature compressor, a condenser, and a throttling device. The experimental results showed that the thermal management system could dissipate a heat flux of 526 W/cm<sup>2</sup> while maintaining the junction temperature below 120 °C. For SiC MOSFET with a higher junction temperature of 175 °C, the system can be expected to dissipate a heat flux as high as 750 W/cm<sup>2</sup>. The effects of the rotational speed of the compressor, the opening of the throttling device, TTV layout, and a downstream heater on the system's cooling performance were analyzed in detail. The study showed that the opening of the throttling device had a significant effect on cooling performance. For the multi-module system, the chip at the upstream location had the best cooling performance. The downstream TTV on MHS2 could function as a super-heating device instead of a heat-dissipating device, making the junction temperature of upstream TTV at a low value.

Lastly, the main conclusions and contributions are summarized, and several recommendations for future work are discussed.

## **SAMENVATTING**

E opwarming van de aarde heeft onomkeerbare schade veroorzaakt op aarde. Energie besparing kan niet alleen het opraken van energie grondstoffen verminderen, maar ook de opwarming van de aarde. Vandaag de dag wordt 40% van de energie in de wereld geconsumeerd als elektriciteit, dus een hoge elektrische energie conversie efficiëntie is dringend nodig. De vermogensmodule speelt een kritieke rol in deze energieconversie. Tot nu toe zijn silicium (Si) vermogensapparaten veel gebruikt in de vermogensmodule. Helaas bereiken zij inmiddels hun theoretische limieten, wat hun conversie efficiëntie drastisch vermindert. In plaats daarvan bieden siliciumcarbide (SiC) vermogensapparaten een beter perspectief door hun grotere verboden zone, lagere intrinsieke ladingdrager concentraties en een hoger kritisch elektrisch veld. Echter, deze superieure eigenschappen kunnen niet worden uitgebuit met de huidige mainstream behuizingstechnologie en materialen. SiC apparaten kunnen niet zomaar als directe vervanger van Si apparaten worden ingezet.

De huidige mainstream behuizingstechnologie voor SiC apparaten is voornamelijk draad verbinding gecombineerd met een direct gehecht koperen substraat. Echter, draad verbindingen laten geen tweezijdige koeling toe en voegen parasitaire zelfinductie toe, wat de warmte dissipatie en schakel prestaties aantast. De hoge parasitische zelfinductie (>10nH) kan leiden tot voltage overschrijdingen en elektromagnetische interferentie problemen als SiC apparaten schakelen op hoge snelheden. De materialen die gebruikt worden in Si vermogensmodules, zoals de chip bevestigings- en inkapselingsmaterialen, kunnen in het algemeen hoge temperaturen en temperatuur cycli niet aan, wat de toepassing van SiC apparaten limiteert bij hoge temperaturen. Het is daarom essentieel om geavanceerde behuizing in de ontwikkeling te verwerken om het volledige potentiaal van SiC apparaten te benutten.

Door het toenemende vermogen en pakkingsdichtheid krijgen SiC apparaten ook ernstige koeling uitdagingen, ook al kunnen ze hogere temperaturen aan. Ze zijn kleiner dan Si apparaten, wat leidt tot een hoge warmte flux in SiC apparaten tot 1 kW/cm<sup>2</sup>. Uiterst efficiënte koeling moet worden ontwikkeld om deze groeiende warmte flux aan te kunnen.

Dit proefschrift geeft eerst een overzicht van de voornaamste verpakkingsmethodes voor Si vermogensmodules, die ook de bouwstenen vormen voor SiC verpakkingsmethodes. Daarna volgt een overzicht voor verpakkingstechnieken voor SiC vermogensmodule.

Ten tweede zijn de SiC MOSFET en organische substraat materialen geselecteerd en gekarakteriseerd. I-V, C-V en gate eigenschappen van de SiC MOSFET zijn geanalyseerd met een op maat gemaakte armatuur. De experimenten laten zien dat de SiC MOSFET uitvoer niet gesatureerd was, dat er twee punten waren op de Miller capaciteit versus drainsource voltage grafiek en dat er een niet vlak Miller platform was. Allemaal anders dan in Si apparaten. Daarna zijn de thermische stabiliteit, diëlektrische doorslag en thermomechanische prestaties van de organische substraat materialen en de uithardingskinetiek van BT voorgeïmpregneerde vezels gekarakteriseerd. De experimenten aten zien dat de substraat materialen een temperatuur van 300 °C en een hoog voltage van 46.9 kV aankunnen. De glas transitie temperatuur was 260 °C en de thermische expansie coëfficiënt kwam

4 Samenvatting

overeen met die van SiC. Zowel een uur uitharding op 280 °C en twee uur op 210 °C gaf volledige uitharding van de BT voorgeïmpregneerde vezels.

Als derde wordt een nieuw uitwaaierend paneel niveau verpakkingstechnologie voorgesteld voor de fase aansluiting voor een SiC MOSFET vermogensmodule. De hoge en lage kant SiC MOSFETs zijn ingekapseld in een organisch substraat, verbonden met dubbelzijdige verdelingslagen (RDLs), door vias en tenslotte beschermd met dubbelzijdige soldeer maskers. Vergeleken met huidige ingebedde verpakkingen in organische substrates voor Si en GaN apparaten, heeft de voorgestelde verpakkingsstructuur meerdere voordelen, zoals symmetrie en dubbelzijdige koeling. Elektrische, thermische en thermo mechanische simulaties zijn gedaan om de prestaties de evalueren en te optimaliseren. Daarna wordt een gedetailleerd verpakkingsproces voor de fase aansluiting van de SiC MOSFET vermogensmodule geïntroduceerd. Drie essentiële verpakkingsprocessen, waaronder blootstelling en ontwikkeling van fotogevoelig diëlektricum, paneel brede fysische damp depositie (PVD) en dubbelzijdige RDL interconnectie, kunnen respectievelijk laser boring, chip/wafer niveau PVD en draad verbinding vervangen.

Ten vierde zijn de statische en dynamische karakterisaties uitgevoerd van de uitwaaierende SiC MOSFET vermogensmodules. De effecten van de uitwaaierende verpakking op de I-V, C-V en gate lading eigenschappen van de SiC MOSFET zijn geanalyseerd. Het bleek dat de uitvoer eigenschappen van de niet-saturatie van de SiC MOSFET evidenter was na verpakking en dat een hoger aansturingsvoltage nodig was om de SiC MOSFET volledig aan te zetten door de extensie van het niet vlakke Miller plateau. De dubbele puls test was gedaan om de schakel eigenschappen van de SiC MOSFET in de uitwaaierende fase connectie vermogensmodule en de TO-247 verpakking. De resultaten laten zien dat de uitwaaierende verpakking een kleiner voltage overschrijding en stroom oscillaties had bij uitschakeling en lagere voltage oscillaties en dat het lagere stroom overschrijding had bij inschakeling dan de TO-247 verpakking.

Ten vijfde wordt er een mikrokanaal thermisch management systeem gepresenteerd met twee-fase kook stroming met R1234yf koelmiddel. Zowel de enkel- als de multichip silicium thermische test vehikels (TTVs) gebaseerd op ingebedde substraat technologie zijn gefabriceerd en gehecht aan een mikrokanaal warmteput (MHS) met twee-fase koeling. Een dampcompressie koelsysteem was geïmplementeerd om de fasetransitie van R1234yf te realiseren en te controleren. Het systeem bevat twee identieke aluminium MHSs in series verbonden, een gas stroom meter, een miniatuur compressor, een condensator en een regelaar. De resultaten laten zien dat het thermisch management systeem een warmte flux van 526 W/cm<sup>2</sup> aankan en de junctie temperatuur onder de 120 °C houdt. Voor de SiC MOSFET met een junctie temperatuur van 175 °C kan het systeem een warmte flux afvoeren tot 750 W/cm<sup>2</sup>. De effecten van de rotatiesnelheid van de compressor, de opening van de regelaar, de TTV layout en een verwarmer stroomafwaarts op de koelprestaties van het systeem zijn nauwgezet geanalyseerd. Het onderzoek toont aan dat de opening van de regelaar een significant effect had op de koeling. In het multi-module systeem had de meest stroomopwaartse chip de beste koeling. De stroomafwaartse TTV op de MHS2 kon zich gedragen als een oververhittingsapparaat in plaats van een warmte afvoer apparaat, wat de junctie temperatuur van de stroomopwaartse TTV laag maakte.

Ten slotte worden de conclusies en contributies samengevat en worden verscheidene aanbevelingen gemaakt voor toekomstig werk.

# 1

## Introduction

SiC MOSFET is a promising wide-bandgap semiconductor device in the applications of high operating temperature, high blocking voltage, and high switching frequency due to excellent material properties. However, the superior characteristics of SiC MOSFET cannot be exploited via current mainstream packaging technologies and materials. They cannot be used merely as a direct drop-in replacement of Si devices. To fully explore the potential of SiC MOSFET, it is essential to incorporate advanced packaging with device development. With the ever-increasing power output and packaging density, SiC MOSFET also faces severe cooling challenges, although they can withstand higher temperatures. Their sizes are much smaller than similarly rated Si devices, leading to the high heat flux of SiC MOSFET that could reach up to 1 kW/cm². So, the high-efficient cooling schemes need to be developed to cope with the increasing heat flux.

#### 1.1. BACKGROUND

RECENTLY, global warming has caused irreversible damage to the earth. Energy-saving not only can reduce the depletion of energy sources but also prevent global warming. Nowadays, 40% of worldwide energy is consumed as electrical energy [2], so a high-efficient electrical energy conversion is urgently required. The power module plays a critical role in electrical energy conversion. So far, silicon (Si) power devices have still been widely used in the power module. However, they are approaching theoretical physical limits [3]. The practical operating temperature of Si insulated gated bipolar transistor (IGBT) is lower than 175 °C, and the maximum block voltage is lower than 6.5 kV [4]-[5]. Thanks to the bipolar current conduction mechanism, the switching speed of IGBT is lower, leading to a higher switching loss, which affects the energy conversion efficiency, and limiting the high-switching frequencies. Now, wide bandgap (WBG) power devices have gained attention.

#### 1.2. POTENTIAL OF SIC POWER DEVICES

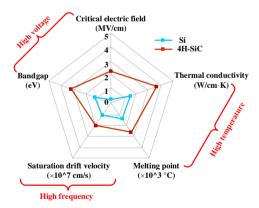

A s a potential WBG semiconductor material, silicon carbide (SiC) has several superior characteristics, as shown in Figure 1.1 [2]. Owing to the wider energy bandgap of 4H-SiC compared with Si, its intrinsic carrier concentration is smaller, which enables SiC devices to operate at higher temperatures (> 200 °C). The 10× critical electric field makes ultra-high voltage (> 10 kV) power devices achievable. The ideal specific conduction resistance enables SiC devices to be smaller, leading to lower parasitic capacitance and higher switching speed. The high switching speed allows for high switching-frequency operation (> 100 kHz) with less switching loss, resulting in a significant reduction of the size, weight, and cost of passive components [5]-[9].

Figure 1.1: Material properties comparison between Si and 4H-SiC [2].

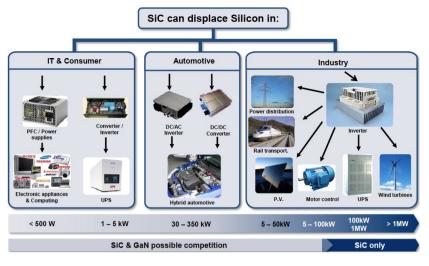

Figure 1.2 shows the possible application fields that SiC devices can displace Si ones in power modules. They can be used in IT and consumer, automotive, and industry. For the super-high power applications, only SiC power devices can be used [10].

3

Figure 1.2: Possible applications of SiC power module in Si power electronics [10].

#### 1.3. SIC MOSFET

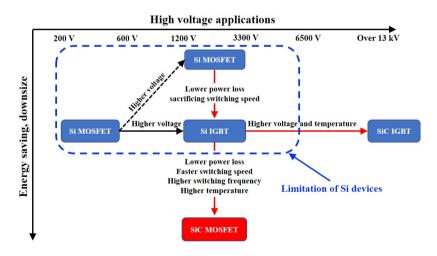

IGURE 1.3 illustrates the application range of Si and SiC power devices [11]-[14]. The blue dashed line is the theoretical performance limitation of Si devices. Si devices are mainly used in the low and medium voltage ranges, SiC metal-oxide-semiconductor field-effect transistor (MOSFET) possesses advantages in the applications of medium-high voltage and high frequency. So far, there have no been available SiC IGBT on the market. It will be used in the higher voltage and temperature ranges.

Figure 1.3: Application range of Si and SiC power devices

SiC MOSFET has much lower output capacitance and gate charge, and they can switch

at much higher dv/dt and di/dt. Switching speed comparison between SiC MOSFET and Si IGBT with the same power rating was performed in Ref. [15]. The devices from Cree's SiC MOSFET (C2M0080120D) and Infineon's third-generation Si IGBT (IKW15N120H3) were selected. The quantitative dv/dt and di/dt of the two devices are shown in Table 1.1. As seen in the table. SiC MOSFET can be switched much faster than Si IGBT.

| E4            | Turn-on    | l           | Turn-off   | ,    |

|---------------|------------|-------------|------------|------|

| Feature       | SiC MOSFET | <b>IGBT</b> | SiC MOSFET | IGBT |

| dv/dt (kV/μs) | 40         | 16          | 27         | 8    |

0.5

1.1

0.3

0.06

Table 1.1: Switching speed evaluation of SiC MOSFET and IGBT [15]

Due to the unipolar structure, the switching loss of SiC MOSFET is relatively low when the switching speed is faster, enabling its promising application in the high frequency. Meanwhile, the switching loss of SiC MOSFET has little variation over temperature. In comparison, Si IGBT with a bipolar structure has higher switching loss, which increases significantly in the high operating temperature as well [12]-[14]. The conduction loss of SiC MOSFET is also lower because of its higher doping concentration in the drift region. The smaller depletion width reduces the on-state resistance of SiC MOSFET, resulting in less conduction loss. Therefore, SiC MOSFET possesses definite advantages in the mediumhigh voltage applications over Si counterparts.

#### 1.4. Conventional packaging technology

di/dt (kA/µs)

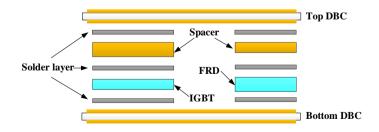

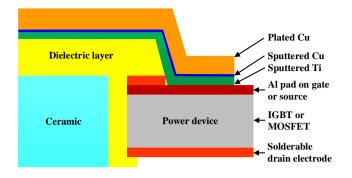

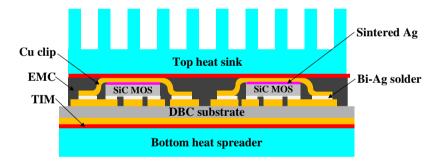

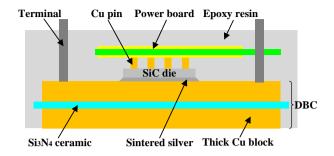

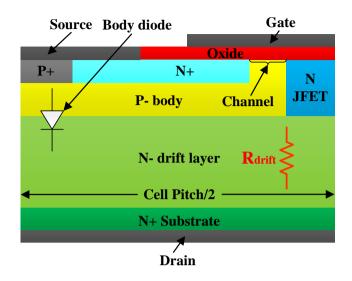

ONVENTIONAL aluminum (Al) wire-bonding interconnection combined with direct-bonded copper (DBC) substrate has still been one of the most preferred packaging technologies for the SiC power module. DBC substrate has a copper-ceramic-copper (Cu-ceramic-Cu) laminated structure, with the top layer patterned to form an electrical circuit, the bottom layer attached to a baseplate, and the ceramic used as an electrically isolating layer [16]. A variety of ceramic materials can be selected, such as alumina (Al<sub>2</sub>O<sub>3</sub>), aluminum nitride (AlN), and silicon nitride (Si<sub>3</sub>N<sub>4</sub>). Al<sub>2</sub>O<sub>3</sub> is the most economical choice but has the lowest thermal conductivity and average mechanical strength. AlN has a higher thermal conductivity than Al<sub>2</sub>O<sub>3</sub> and a better coefficient of thermal expansion (CTE) match with 4H-SiC. Si<sub>3</sub>N<sub>4</sub> is a better choice in terms of much higher thermal cycling reliability, but its disadvantage is higher cost and slightly lower thermal conductivity.

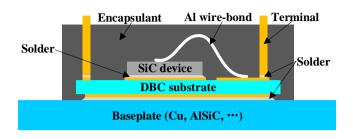

Figure 1.4 illustrates the schematic of conventional packaging technology for the SiC MOSFET power module. As seen in this figure, a SiC chip is soldered to a DBC substrate and afterward wire-bonded to establish the chip top connection. The DBC is then soldered to a baseplate, and load terminals and control connectors are soldered to the DBC substrate. The entire assembly is finally enclosed in an encapsulant to protect the internal structures of the SiC MOSFET power module. The conventional packaging technology provides electrical interconnects (via Al wire-bonds and upper Cu tracks of the DBC substrate), electrical insulation (using the DBC substrate), device protection (by encapsulant), and thermal management (through the bottom side). The conventional package structure is used in the vast majority of the power modules that are currently manufactured. [17].

Figure 1.4: Conventional packaging technology for SiC MOSFET power module

#### 1.5. Problems of the conventional packaging

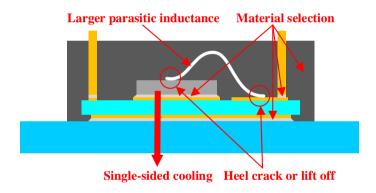

THE conventional packaging technology, however, limits the performance of the SiC MOSFET. Figure 1.5 shows the main problems of the conventional packaging for the SiC MOSFET power module.

Figure 1.5: Problems of the conventional packaging

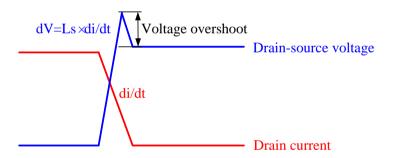

- Wire-bonding interconnection has long commutation paths so that the parasitic inductances could exceed 10 nH. High di/dt at turn-off transient would easily lead to significant voltage overshoot, increasing switching loss of SiC MOSFET, causing electromagnetic interferences, false-triggering, limiting switching frequency, and affecting switching waveforms [17]-[19]. Figure 1.6 illustrates the voltage overshoot caused by parasitic inductance. To avoid excessive overshoot, much smaller parasitic inductance L<sub>S</sub> is required for fully utilizing the fast switching characteristics of SiC MOSFET [20]-[22].

- Limited by available packaging materials, junction temperatures of SiC power modules are subjected to 175 °C, even though SiC devices are, in theory, capable of op-

erating at high temperature up to 600 °C [23]-[24]. Most of the packaging materials adopted in the wire-bonded power module, such as Sn-based solder and encapsulant, cannot withstand high temperature over 200 °C, which limits the application of the power module in the high-temperature environment [25]. High-lead solder, which contains over 85% lead, is currently excluded from the Restriction of Hazardous Substances (RoHS) directive [26]. The high-temperature solders, such as Au80Sn20, Au88Ge12, Zn-12Al, etc., require higher melting points and suitable thermomechanical properties.

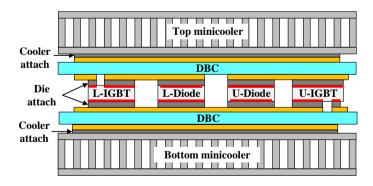

- Furthermore, wire-bonds do not allow for double-sided cooling [27]. Most of the heat generated by SiC MOSFET is dissipated through its bottom side, which affects the thermal performance of the power module. Moreover, as power loss increases with switching frequency, a cooling system that could remove heat from both sides of the die in a power module would be much more efficient for the high power operation of a power module [17].

- As for thermo-mechanical reliability, wire-bonds lift-off and solder joints fatigue are the main failure mechanisms of the conventional packaging due to the CTE mismatch between the Al and the SiC, the SiC and the DBC, and the DBC and the baseplate. The solder joints degradation increases the thermal resistance of the SiC power module and raises the temperature, thus accelerating the lift-off of wire-bonds. The reliability of wire-bonds is closely related to the lifetime of the SiC power module. When the wire-bonds break down, the power module will fail [25]-[28].

Figure 1.6: Illustration of voltage overshoot caused by parasitic inductance

Therefore, to fully explore the potential of SiC MOSFET, it is essential to incorporate advanced packaging technologies with device development.

#### 1.6. ADVANCED PACKAGING TECHNOLOGY

S EVERAL advanced packaging technologies for the SiC power module, e.g., embedded packaging, press-pack, planar packaging, 3D packaging, and hybrid packaging techniques, have been developed in recent years [29]-[42].

7

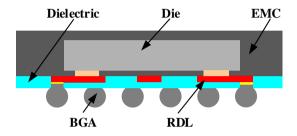

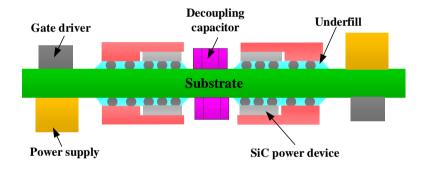

The fan-out packaging is regarded as one of the latest and most potential microelectronic packaging technologies because it possesses lower cost, thinner profile, and better electrical and thermal performance [1], [43]-[44]. Figure 1.7 shows the schematic diagram of a typical fan-out packaging. It is composed of die, epoxy molding compound (EMC), dielectric, redistribution layer (RDL), ball grid array (BGA), etc. Compared with the conventional flip-chip BGA, the fan-out technology eliminates many process steps, e.g., substrate, wafer bumping, flip-chip reflow, flux cleaning, underfill, and so on [45].

Figure 1.7: Schematic diagram of a fan-out packaging

Wafer- and panel-level fan-out packaging technologies are currently conducted [46]-[48]. Organic substrate embedded packaging is one of the panel-level fan-out technologies. Due to its evident advantages, it is considered as one of the promising applicable packaging technologies for the SiC MOSFET power module. In this dissertation, a novel fan-out SiC MOSFET power module in an organic substrate will be investigated.

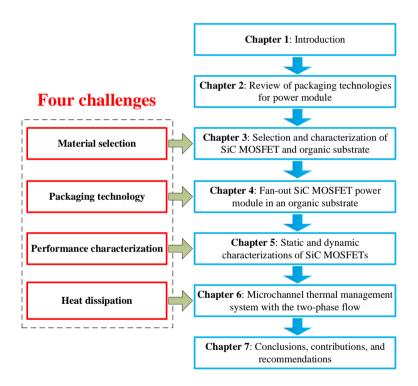

## 1.7. CHALLENGES OF THE ADVANCED PACKAGING

OMPARED with Si counterparts, SiC MOSFET possesses definite advantages in the applications of high operating temperature, high blocking voltage, and high switching frequency. However, these superior performances cannot be fully exploited via current mainstream packaging technologies. SiC MOSFET cannot be used merely as a direct drop-in replacement of Si counterparts in the power module[49]-[51]. To develop the fan-out SiC MOSFET power module, we will face the following four challenges: 1) material selection; 2) packaging technology; 3) performance characterization; 4) and heat dissipation.

#### 1.7.1. MATERIAL SELECTION

The organic substrate is becoming attractive for power electronics as it offers the following advantages: 1) low manufacturing cost for mass production; 2) lightweight; 3) easy high-density integration [52]-[53].

However, most organic substrate materials cannot withstand temperature over 200  $^{\circ}$ C. Their thermal conductivities are as low as 0.35 W/m·K.

With the same breakdown voltage, commercial SiC MOSFET has smaller chip area and thinner thickness compared to Si counterparts, so the organic substrate in a SiC power module needs to sustain higher electric field strength than that in a Si power module [13].

For organic embedding materials, e.g., FR4 prepreg (glass fiber reinforced uncured epoxy resin), resin-coated copper (RCC), and Ajinomoto build-up film (ABF), are often used [54]-[57]. Munding *et al.* [55] selected FR4 prepreg and RCC as embedding material, respectively, and evaluated thermo-mechanical reliability of the two lead-frame based laminate chip embedded packages through temperature cycle and high-temperature storage experiments. A high glass transition temperature (Tg) FR4 prepreg was found to be more suitable for the embedding package.

Besides, SiC power modules are often used in a harsh environment. Under high ambient temperature and operational temperature, CTE mismatch of different materials within the power modules could induce excessive warpage, stress, and strain, leading to SiC die crack, and interface delamination.

Therefore, the organic substrate should satisfy the following requirements: 1) high-temperature stability; 2) high dielectric strength; 3) high Tg; 4) CTE matching with SiC.

#### 1.7.2. PACKAGING TECHNOLOGY

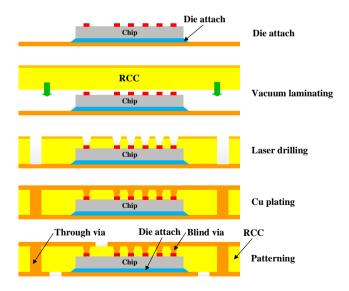

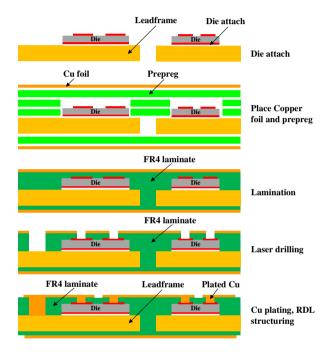

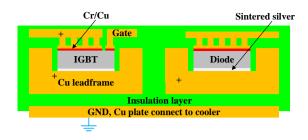

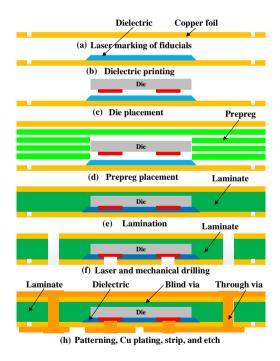

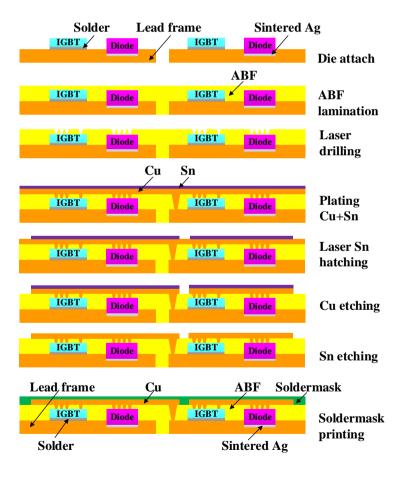

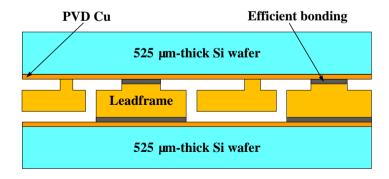

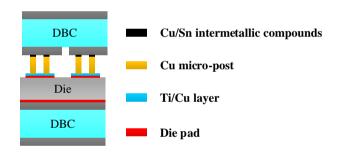

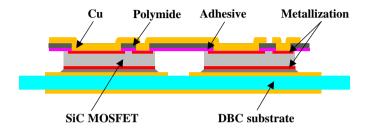

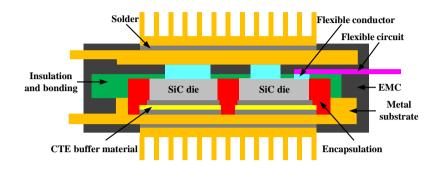

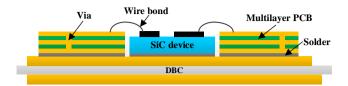

In recent years, several organic embedded packaging technologies have been developed for the power diode [54], IGBT power module [56]-[57], and GaN devices [58]-[60]. Leadframe-based laminate chip technology is one of the significant representatives [55]-[57]. The bottom sides of power devices are soldered or sintered onto a Cu lead-frame, the resulting assembly is then fully embedded in the prepreg. Electrical interconnections of a power device are realized through laser drilling, electroless plating, Cu plating, and some other processes. However, the structure of the lead-frame based chip embedding package is asymmetrical in the thickness direction, which could easily cause significant stress and strain in the package due to the CTE mismatch between the chip and the Cu lead-frame in a harsh environment. A balanced package structure can relieve stress and strain. Besides, the heat generated from a power device is mainly dissipated into the ambient through a Cu lead-frame, which limits the thermal performance of a power module.

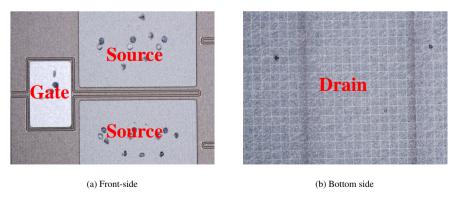

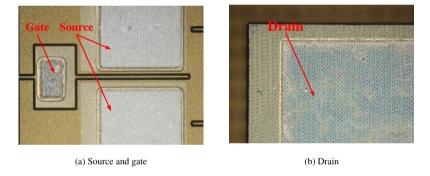

At present, most commercial SiC MOSFETs are designed for Al wire-bonding interconnection. The front-side source and gate metallization of these devices are Al, which cannot be directly used in the fan-out panel-level packaging process. Additional metallization layers on the front-side source and gate pads are required. In Ref. [61], 5 µm thick Cu was added to the MOSFET pads at the wafer level. For SiC MOSFET, however, the cost and risk of pad re-metallization at the wafer-level are high. Kearney *et al.* [56] modified the original metallization layers on the emitter, gate of IGBT chip by sputtering Cr/Cu (5 nm/8 µm) layers, while the dielectric region on the top surface of the IGBT chip was protected with a shadow mask. However, the size of SiC MOSFET is relatively small compared to IGBT, and it is challenging to realize the re-metallization of pads at such a small chip. Besides, SiC MOSFET is a vertical power device, with the gate and source on the front-side and drain on the backside, chip-level physical vapor deposition easily contaminates one side when sputtering the other side. Therefore, the exploration of a new re-metallization technique for the fan-out SiC MOSFET packaging in an organic substrate is essential.

SiC MOSFETs that had the additional metallization layers were then embedded in an organic substrate, followed by blind vias that were usually formed by laser drilling and Cu plating, thus realized the electrical interconnection between the dies and the outer layers [55]-[62]. However, if the laser energy is not properly controlled, the terminal metallization pads could be damaged by laser drilling. The technique is not suitable for devices with very thin pads. Thicker pads are needed. Besides, the drilling process is complex, and the cost is relatively high. A new alternative interconnection technique between the power devices and the outer layers needs to be developed.

#### 1.7.3. Performance Characterization

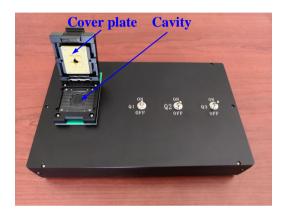

After packaging, the static and dynamic characteristics of the SiC MOSFET power module need to be measured to verify the performance improvement.

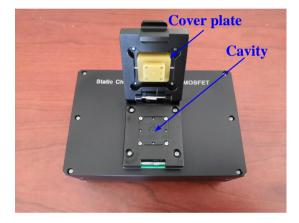

On the one hand, a static performance characterization instrument of SiC MOSFETs generally equips with several fixtures for wafer- and package-level measurements, mainly for bare-die and standard discrete devices. The discrete devices mainly include TO-247 and TO-220 packages. Single bare dies and novel packaging structures cannot be directly measured. Although some vendors could provide the performance information of SiC MOSFET bare dies, they provide the general information, and we cannot obtain the data at the specific application condition. To accurately analyze the effect of the fan-out packaging on the performance of bare dies, it is essential to develop the same kind of custom fixture so that we can conduct measurements under the same experimental condition.

On the other hand, it is challenging to accurately compare the dynamic characteristics of the two types of packages. One belongs to the surface mount device, and the other is the TO-247 package. In order to ensure the equality of comparison, the distance and width of the power loop and driver loop of the two packages should be nearly the same, respectively.

#### 1.7.4. HEAT DISSIPATION

The heat flux of the next generation Si IGBT used in pure and hybrid electric vehicles applications would be as high as  $500 \text{ W/cm}^2$ , more than three times in comparison with the current level of  $100\text{-}150 \text{ W/cm}^2$  [63]-[65]. As form factor of SiC MOSFET tends to be smaller, its heat flux could reach up to  $1 \text{ kW/cm}^2$  in comparison with Si IGBT with the same voltage blocking capability, even higher heat flux is anticipated [66]-[68].

Such high heat fluxes cannot be addressed by using conventional cooling solutions such as vapor chamber [69]-[70], and single-phase liquid cooling [71]-[74]. Vapor chamber in combination with forced convection could dissipate heat flux no more than 100 W/cm² [75], while single-phase liquid cooling could reach 350 W/cm² [76]-[79]. Recently, immersion pool boiling and liquid metal cooling schemes have been reported for high heat flux electronics [75], [80]-[82]. The immersion pool boiling, which requires dielectric fluid to be in contact with the ICs directly, is usually limited by the critical heat flux of dielectric fluid and thus insufficient cooling capacity. The liquid metal has much better thermophysical properties using eutectic alloys of different materials such as gallium, indium, and tin [82], but it may not be compatible with the metal piping and fittings. The cost of liquid metal is also much higher in comparison with other coolants [83].

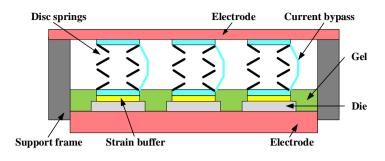

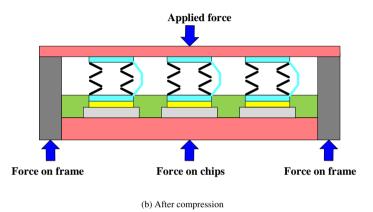

Two-phase flow boiling regimes have received extensive attention in power electronics applications in recent years. Taking advantage of the latent heat vaporization of liquid refrigerant during its boiling process, it can provide higher heat transfer coefficients, lower flow rates, more uniform surface temperatures, and lower pumping power than single-phase cooling scheme [63], [84]-[86]. However, the refrigerant boiling requires a wise control of the pressure and temperature of the refrigerant in the evaporator, so that the isothermal heat absorption can be achieved during the flow boiling process.

#### **1.8.** The Layout of this dissertation

B ased above four challenges, with the motivation of developing new packaging technology and thermal management scheme for SiC MOSFET power module, the dissertation is divided into seven chapters. The dissertation layout is shown in Figure 1.8.

Figure 1.8: Dissertation layout

In chapter 2, primary packaging schemes for Si power modules, which are the foundation of packaging methods of SiC ones, were first reviewed. Then, attempts on packaging techniques for SiC power modules are thoroughly overviewed. Lastly, a summary of the state-of-the-art packaging technologies for SiC power modules was performed.

1

- In Chapter 3, SiC MOSFET and organic substrate materials were selected. I-V, C-V, and gate charge characteristics of SiC MOSFET were first analyzed via a custom fixture. Then, thermal stability, dielectric breakdown, and thermo-mechanical performance of the organic substrate materials and cure kinetics of BT prepreg were characterized.

- In Chapter 4, a novel fan-out SiC MOSFET power module in an organic substrate

was proposed. The electrical, thermal, and thermal-mechanical simulations were

conducted to evaluate and optimize the fan-out packaging performance. A detailed

fan-out panel-level packaging process for the phase-leg SiC MOSFET power module

was introduced, and three key packaging processes were highlighted.

- In Chapter 5, the static and dynamic characteristics of the fan-out SiC MOSFET power module were studied. First of all, the effects of the fan-out packaging on I-V, C-V, and gate charge characteristics of SiC MOSFET were analyzed. Then, the switching performance of the fan-out phase-leg SiC MOSFET was evaluated via double pulse tests. A phase-leg that is composed of two TO-247 discrete packages was used as a benchmark.

- In Chapter 6, a microchannel thermal management system with the two-phase flow is presented for the fan-out SiC MOSFET power module. Due to no available SiC-based thermal test chips on the market, Si-based thermal test vehicles (TTVs) were developed to evaluate the cooling performance of the proposed thermal management system. Environment-friendly refrigerant R1234yf with low boiling points was selected to fill the system. The system mainly consisted of two identical Al microchannel heat sinks (MHSs), a compressor, a condenser, a throttling device, and several accessory measurement components. The cooling performance of the system with one single-chip TTV was first analyzed. For SiC devices with a higher junction temperature of 175 °C, the system's heat dissipation capacity was evaluated. Then, the effects of the rotational speed of the compressor, the opening of the throttling device, TTV layout on MHS, and a downstream heater on the system's cooling performance were analyzed in detail. Lastly, the potential of the cooling performance enhancement was also discussed.

- Chapter 7 concluded the dissertation, summarized the contributions, and discussed the recommendation derived from the results of this dissertation for future research.

#### REFERENCES

- [1] F. Hou, T. Lin, L. Cao, F. Liu, J. Li, X.J. Fan, G.Q. Zhang, "Experimental Verification and Optimization Analysis of Warpage for Panel-Level Fan-Out Package," *IEEE Trans. Comp. Packag. Manuf. Technol.*, vol. 7, no. 10, pp. 1721-1728, Oct. 2017.

- [2] J. Millán, P. Godignon, X. Perpiñà, A. Pérez-Tomás, and J. Rebollo, "A Survey of Wide Bandgap Power Semiconductor Devices," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2155-2163, 2014.

- [3] M. R. Ahmed, R. Todd, and A. J. Forsyth, "Analysis of SiC MOSFETs under hard and soft-switching," in proc. *IEEE Energy Convers. Congr. Exp. (ECCE)*, 20-24 Sept. 2015 2015, pp. 2231-2238.

- [4] C. DiMarino et al., "Design and Experimental Validation of a Wire-Bond-Less 10-kV SiC MOSFET Power Module," *IEEE Trans. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 1, pp. 381-394, 2020.

- [5] R. Khazaka, L. Mendizabal, D. Henry, and R. Hanna, "Survey of High-Temperature Reliability of Power Electronics Packaging Components," *IEEE Trans. Power Electron.*, vol. 30, no.5, pp. 2456-2464, 2015.

- [6] J. Fabre, P. Ladoux, and M. Piton, "Characterization and Implementation of Dual-SiC MOSFET Modules for Future Use in Traction Converters," *IEEE Trans. Power Electron.*, vol. 30, no. 8, pp. 4079-4090, 2015.

- [7] J. Fabre and P. Ladoux, "Parallel Connection of 1200-V/100-A SiC-MOSFET Half-Bridge Modules," *IEEE Trans. Ind. Electron.*, vol. 52, no. 2, pp. 1669–1676, 2016.

- [8] D. P. Sadik, K. Kostov, J. Colmenares, F. Giezendanner, P. Ranstad, and H. Nee, "Analysis of Parasitic Elements of SiC Power Modules with Special Emphasis on Reliability Issues," *IEEE Trans. Emerg. Sel. Topics Power Electron.*,, vol. 4, no. 3, pp. 988-995, 2016.

- [9] X. She, A. Q. Huang, L. Ó, and B. Ozpineci, "Review of Silicon Carbide Power Devices and Their Applications," *IEEE Trans. Ind. Electron.*, vol. 64, no. 10, pp. 8193-8205, 2017.

- [10] K. Madjour, "Silicon carbide market update: From discrete devices to modules," in *PCIM Europe*, 2014.

- [11] M. Horio, Y. Iizuka, and Y. Ikeda, "Packaging Technologies for SiC Power Modules," *Fuji Electric Review*, Vol. 58 No. 2, pp. 2012.

- [12] S. Hazra, S. Madhusoodhanan, G. K. Moghaddam, K. Hatua, and S. Bhattacharya, "Design Considerations and Performance Evaluation of 1200-V 100-A SiC MOSFET-Based Two-Level Voltage Source Converter," *IEEE Trans. Ind. Appl. Electron.*, vol. 52, no. 5, pp. 4257-4268, 2016.

- [13] C. Chen, F. Luo, and Y. Kang, "A Review of SiC Power Module Packaging: Layout, Material System and Integration," *CPSS Trans. Power Electron. Appl.*, Vol. 2, No. 3, pp. 170-186, 2017.

- [14] Cree, "Application Considerations for Silicon Carbide MOSFETs," Accessed on January 2011, [Online]. Available: https://www.mouser.com/pdfDocs/Cree-Application-Considerations-for-Silicon-Carbide-MOSFETs.pdf.

- [15] A. Anthon, Z. Zhang, and M. A. E. Andersen, "Comparison of a state of the art Si IGBT and next generation fast switching devices in a 4 kW boost converter," in proc. *IEEE Energy Convers. Congr. Expo. (ECCE)*, Montreal, QC, 2015, pp. 3003-3011.

[16] B. Mouawad, B. Thollin, C. Buttay, L. Dupont, V. Bley, D. Fabregue, M. Soueidan, B. Schlegel, J. Pezard, and J. C. Crebier, "Direct Copper Bonding for Power Interconnects: Design, Manufacturing and Test," *IEEE Trans. Comp. Packag. Manuf. Technol.*, vol. 5, no. 1, pp. 143-150. 2015.

- [17] B. Mouawad, M. Soueidan, D. Fabregue, C. Buttay, B. Allard, V. Bley, H. Morel, and C. Martin, "Application of the Spark Plasma Sintering Technique to Low-Temperature Copper Bonding," *IEEE Trans. Comp. Packag. Manuf. Technol.*, vol. 2, no. 4, pp. 553-560. 2012.

- [18] A. Hamidi and D. Cottet, "Parasitics in power electronics packaging," in Proc. *37th IMAPS*, Long Beach, CA, 2004.

- [19] W. Zhang, X. Huang, Z. Liu, F.C. Lee, S. She, W. Du, and Q. Li, "A New Package of High-Voltage Cascode Gallium Nitride Device for Megahertz Operation," *IEEE Trans. Power Electron.*, vol. 31, no. 2, pp. 1344–1353, 2015.

- [20] H. Kono, K. Takao, T. Suzuki, and T. Shinohe, "High-speed and Low Switching Loss Operation of 1700V 60A SiC MOSFETs Installed in Low Parasitic Inductance Module," in Proc. *IEEE Int. Symp. Power Semicond. Devices IC's*, Waikoloa, HI, 2014, pp. 289-292.

- [21] K. Takao, T. Shinohe, T. Yamamoto, K. Hasegawa, and M. Ishida, "1200 V-360 A SiC Power Module with Phase Leg Clustering Concept for Low Parasitic Inductance and High Speed Switching," in Proc. *Int. Conf. Integr. Power Electron. Syst.*, Nuremberg, Germany, 2014, pp. 1-7.

- [22] K. Takao and S. Kyogoku, "Ultra low inductance power module for fast switching SiC power devices," in proc. *IEEE Int. Symp. Power Semicond. Devices IC's*, Hong Kong, 2015, pp. 313-316.

- [23] J. Hornberger, A. B. Lostetter, K. I. Olejniczak T. McNutt, S. Magan Lal, and A. Mantooth, "Silicon-Carbide (SiC) Semiconductor Power Electronics for Extreme High-Temperature Environments," in Proc. *IEEE Aerospace Conference*, Big Sky, MT, 2004, pp. 2538-2555.

- [24] J. Biela, M. Schweizer, S. Waffler, and J. W. Kolar, "SiC versus Si—Evaluation of Potentials for Performance Improvement of Inverter and DC-DC Converter Systems by SiC Power Semiconductors," *IEEE Trans. Ind. Electron.*, vol. 58, no. 7, pp. 2872-2882, 2011.

- [25] L. Xu, M. C. Wang, Y. Zhou, Z. F. Qian, and S. Liu. "Effect of silicone gel on the reliability of heavy aluminum wire bond for power module during thermal cycling test", in Proc. *IEEE Electronic Components and Technol. Conf. (ECTC)*, Las Vegas, NV, 2016, pp. 1005-1010.

- [26] T. Suzuki et al., "Macro- and Micro-Deformation Behavior of Sintered-Copper Die-Attach Material," *IEEE Trans. Device Mater. Rel.*, vol. 18, no. 1, pp. 54-63, 2018.

- [27] C. Neeb, L. Boettcher, M. Conrad, and R. W. D. Doncker, "Innovative and Reliable Power Modules: A Future Trend and Evolution of Technologies," *IEEE Trans. Ind. Electron. Mag.*, vol. 8, no. 3, pp. 6-16, 2014.

- [28] U. Choi, F. Blaabjerg, and K. Lee, "Study and Handling Methods of Power IGBT Module Failures in Power Electronic Converter Systems," *IEEE Trans. Power Electron.*, vol. 30, no. 5, pp. 2517-2533, 2015

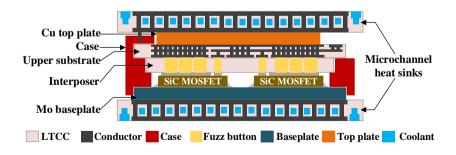

- [29] Rhee, H. Y. Hwang, J. Li, J. B. Lee, H. Y. Zhang, "Miniaturized Double Side Cooling Packaging for High Power 3 Phase SiC Inverter Module with Junction Temperature over 220 °C," in Proc. *IEEE Electron Comp. Technol. Conf.*, Las Vegas, NV, 2016, pp. 1190-1196.

- [30] L. Stevanovic, "Packaging Challenges and Solutions for Silicon Carbide Power Electronics," ECTC Panel Session: Power Electronics A Booming Market, 2012.

- [31] L. Yin, C. Kapusta, A. Gowda, K. Nagarkar, "A Wire-Bondless Packaging Platform for Silicon Carbide Power Semiconductor Devices," *J. Electron. Packag.*, vol. 140, pp. 031009-1-031009 -8, 2018.

- [32] H. Zhang, S. S. Ang, H. A. Mantooth, and S. Krishnamurthy, "A high temperature, double-sided cooling SiC power electronics module," in Proc. *IEEE Energy Convers. Congr. Expo.*, Denver, CO, pp. 2877-2883, 2013.

- [33] H. Ishino, T. Watanabe, K. Sugiura, and K. Tsuruta, "6-in-1 Silicon carbide power module for high performance of power electronics systems," in proc. *IEEE Int. Symp. Power Semicond. Devices IC's*, Waikoloa, HI, 2014, pp. 446-449.

- [34] Y. Xu, I. Husain, H. West, W. Yu and D. Hopkins, "Development of an ultra-high density Power Chip on Bus (PCoB) module," in proc. *IEEE Energy Convers. Congr. Expo.*, Milwaukee, WI, 2016, pp. 1-7.

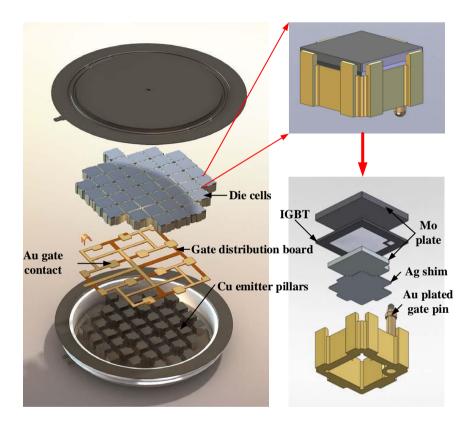

- [35] N. Zhu, H. A. Mantooth, D. H. Xu, M. Chen, and M. D. Glover, "A Solution to Press-Pack Packaging of SiC MOSFETS," *IEEE Trans. Ind. Electron.*, vol. 64, no. 10, pp. 8224-8234, 2017.

- [36] S. Seal, M. D. Glover, A. K. Wallace, and H. A. Mantooth, "Flip-chip bonded silicon carbide MOSFETs as a low parasitic alternative to wire-bonding," in proc. *IEEE Workshop Wide Bandgap Power Devices and Appl. (WiPDA)*, Fayetteville, AR, pp. 194-199, 2016.

- [37] S. Seal, A. K. Wallace, J. Zumbro, and H. A. Mantooth, "Thermo-mechanical Reliability Analysis of Flip-Chip Bonded Silicon Carbide Schottky Diodes," in Proc. *Int. Workshop Integr. Power Packag.*, Delft, Netherlands, 2017, pp. 1-5.

- [38] H. A. Mantooth and S. S. Ang, "Packaging Architectures for Silicon Carbide Power Electronic Modules," in proc. *Int. Power Electron. Conf.*, Niigata, 2018, pp. 153-156.

[39] S. Seal, M. D. Glover, and H. A. Mantooth, "3-D Wire Bondless Switching Cell Using Flip-Chip-Bonded Silicon Carbide Power Devices," *IEEE Trans. Power Electron.*, vol. 33, no.10, pp. 8553-8564, 2018.

- [40] Y. Ikeda, Y. Iizuka, Y. Hinata, M. Horio, M. Hori, and Y. Takahashi, "Investigation on wirebond-less power module structure with high-density packaging and high reliability," in proc. *IEEE Int. Symp. Power Semicond. Devices IC's*, San Diego, CA, 2011, pp. 272-275.

- [41] T. Stockmeier, P. Beckedahl, C. Göbl, T. Malzer, "SKiN: Double side sintering technology for new packages," in proc. *Int. Symp. Power Semicond. Devices IC's*, San Diego, CA, pp. 324-327, 2011.

- [42] P. Beckedahl, S. Bütow, A. Maul, M. Roeblitz, M. Spang, "400A, 1200V SiC power module with 1nH commutation inductance," in proc. CIPS Int. Conf. Integr. Power Electron. Syst., Nuremberg, Germany, pp. 1-6, 2016.

- [43] M. Brunnbauer, E. Fürgut, G. Beer, T. Meyer, H. Hedler, J. Belonio, E. Nomura, K. Kiuchi, K. Kobayashi, "An embedded device technology based on a molded reconfigured wafer," in Proc. *56th IEEE Electron. Compon. Technol. Conf. (ECTC)*, San Diego, CA, 2006, pp. 547-551.

- [44] X.J. Fan, "Wafer level packaging (WLP): Fan-in, fan-out and threedimensional integration," in Proc. 11th Int. Conf. Thermal, Mech. Multiphys. Simulation Experim. Micro-Electron. Micro-Syst. (EuroSimE), Bordeaux, France, 2010, pp. 1-7.

- [45] J. H. Lau, "Patent issues of embedded fan-out wafer/panel level packaging," in Proc. *China Semiconductor Technol. Int. Conf. (CSTIC)*, 2016, pp. 1-7.

- [46] T. Braun et al., "From wafer level to panel level mold embedding," in Proc. 63rd IEEE Electron. Compon. Technol. Conf. (ECTC), Las Vegas, NV, 2013, pp. 1235-1242.

- [47] T. Braun et al., "24"×18" fan-out panel level packing," in Proc. 64th IEEE Electron. Compon. Technol. Conf. (ECTC), Orlando, FL, USA, 2014, pp. 940-946.

- [48] T. Braun et al., "Large area compression molding for fan-out panel level packing," in Proc. 65th IEEE Electron. Compon. Technol. Conf. (ECTC), San Diego, CA, USA, May 2015, pp. 1077-1083.

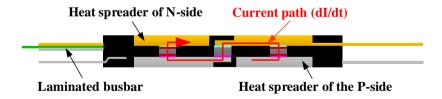

- [49] Z. Chen, Y. Yao, D. Boroyevich, K. Ngo and W. Zhang, "An ultra-fast SiC phase-leg module in modified hybrid packaging structure," in proc. *IEEE Energy Convers. Congr. Expo. (ECCE)*, Pittsburgh, PA, 2014, pp. 2880-2886.

- [50] Z. Huang, Y. Li, L. Chen, Y. Tan, C. Chen, and Y. Kang, "A novel low inductive 3D SiC power module based on hybrid packaging and integration method," in proc. *IEEE Energy Convers. Congr. Expo. (ECCE)*, Cincinnati, OH, 2017, pp. 3995-4002.

16

- [51] S. Toyoshima, S. Hatsukawa, N. Hirakata, T. Tsuno, and Y. Mikamura, "Compact SiC Power Module for High Speed Switching," *EI Technical Review*, No. 80, pp. 81-84, 2015.

- [52] F. Hou, W. Wang, T. Lin, L. Cao, G.Q. Zhang, and J.A. Ferreira, "Characterization of PCB Embedded Package Materials for SiC MOSFETs," *IEEE Trans. Compon.*, *Packag. Manuf. Technol.*, vol. 9, no. 6, pp. 1054-1061, 2019.

- [53] R. Caillaud, C. Buttay, R. Mrad, J. L. Leslé, F. Morel, N. Degrenne, and S. V. Mollov, "Thermal Considerations of a Power Converter With Components Embedded in Printed Circuit Boards," *IEEE Trans. Compon., Packag. Manuf. Technol.*, vol. 10, no. 2, pp. 230-239, 2020.

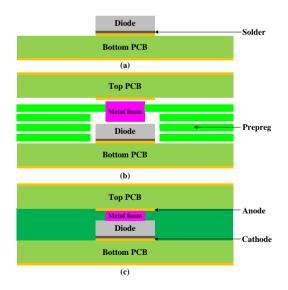

- [54] Y. Pascal, A. Abdedaim, D. Labrousse, M. Petit, S. Lefebvre, and F. Costa, "Using Laminated Metal Foam as the Top-Side Contact of a PCB-Embedded Power Die," *IEEE Electron Device Lett.*, vol. 38, no. 10, pp. 1453-1456, 2017.

- [55] A. Munding, A. Kessler, T. Scharf, B. Plikat, K. Pressel, "Laminate Chip Embedding Technology-Impact of Material Choice and Processing for Very Thin Die Packaging," in Proc. *IEEE Electron Comp. Technol. Conf. (ECTC)*, Orlando, FL, 2017, pp. 711-718.

- [56] D. J. Kearney, S. Kicin, E. Bianda, and A. Krivda, "PCB Embedded Semiconductors for Low-Voltage Power Electronic Applications," *IEEE Trans. Comp. Packag. Manuf. Technol.*, vol. 7, no. 3, pp. 387-395. 2017.

- [57] T. C. Chang, C. C. Lee, C. P. Hsieh, S. C. Hung, R. S. Cheng, "Electrical characteristics and reliability performance of IGBT power device packaging by chip embedding technology," *Microelectron. Reliab.*, vol. 55, pp. 2582–2588, 2015.

- [58] E. Parker, B. Narveson, A. Alderman, and L. Burgyan, "Embedding Active and Passive Components in PCBs and Inorganic Substrates for Power Electronics," in proc. *IEEE Int. Workshop Integr. Power Packag.*, Chicago, IL, 2015, pp. 107-110.

- [59] R. Reiner, B. Weiss, D. Meder, et al., "PCB-Embedding for GaN-on-Si Power Devices and ICs," in proc. *Int. Conf. Integr. Power Electron. Syst.*, Stuttgart, Germany, 2018, pp. 1-6.

- [60] GaN System, "A Basis for Extremely Small GaN Power Transistors", Accessed on Nov. 22, 2016, https://gansystems.com/newsroom/article/basis-extremely-smallgan-power-transistors/.

- [61] D. Yang, M. Kengen, W.G.M. Peels, D. Heyes, W.D. van Driel, "Reliability modeling on a MOSFET power package based on embedded die technology," *Microelectron. Rel.*, vol. 50 923–927, 2010.

- [62] A. Ostmann, A. Neumann, J. Auersperg, C. Ghahremani, G. Sommer, R. Aschenbrenner, and H. Reid, "Integration of Passive and Active Components into Build-up Layers," in proc. *IEEE Electron. Packag. Technol. Conf. (EPTC)*, Singapore, 2002, pp. 223-228.

[63] P. Wang, P. McCluskey, Avram Bar-Cohen, "Two-Phase Liquid Cooling for Thermal Management of IGBT Power Electronic Module," J. Electron. Packag., vol. 135, 021001-021001-11, 2013

- [64] P. Wang, P. McCluskey, and A. Bar-Cohen, "Hybrid Solid- and Liquid-Cooling Solution for Isothermalization of Insulated Gate Bipolar Transistor Power Electronic Devices," *IEEE Trans. Comp. Packag. Manuf. Technol.*, vol. 3, no. 4, pp. 601-611, 2013.

- [65] I. Aranzabal, I. M. de Alegría, N. Delmonte, P. Cova, and I. Kortabarria, "Comparison of the Heat Transfer Capabilities of Conventional Single- and Two-Phase Cooling Systems for an Electric Vehicle IGBT Power Module," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4185-4194, 2019.

- [66] Shailesh N. Joshi, Ercan M. Dede, "Two-phase jet impingement cooling for high heat flux wide band-gap devices using multi-scale porous surfaces," *Appl. Therm. Eng.*, vol. 110, pp. 10–17, 2017.

- [67] A. Bar-Cohen, J. D. Albrecht, and J. J. Maurer, "Near-junction thermal management for wide bandgap devices," in Proc. *IEEE Compound Semicond. Integr. Circuit Symp.*, Waikoloa, HI, USA, 2011, pp. 1–5.

- [68] E. Laloya, Ó. Lucía, H. Sarnago and J. M. Burdío, "Heat Management in Power Converters: From State of the Art to Future Ultrahigh Efficiency Systems," *IEEE Trans. Power Electron.*, vol. 31, pp. 7896-7908, 2016.

- [69] S. Wiriyasart, P. Naphon, "Fill ratio effects on vapor chamber thermal resistance with different configuration structures," *Int. J. Heat Mass Transf.*, vol. 127, pp. 164–171, 2018.

- [70] J. Zeng, S. W. Zhang, G. C., L. Lin, Y. L. Sun, L. Chuai, W. Yuan, "Experimental investigation on thermal performance of Al vapor chamber using micro-grooved wick with reentrant cavity array," *Appl. Therm. Eng.*, vol. 130, pp. 185-194, 2018.

- [71] I. Mudawar, D. Bharathan, K. Kelly, and S. Narumanchi, "Two-Phase Spray Cooling of Hybrid Vehicle Electronics," *IEEE Trans. Comp. Packg. Technol.*, vol. 32, pp. 501-512, 2009.

- [72] D. W. Yang, Y. Wang, G. F. Ding, Z. Y. Jin, J. H. Zhao, G. L. Wang, "Numerical and experimental analysis of cooling performance of single-phase array microchannel heat sinks with different pin-fin configurations," *Appl. Therm. Eng.*, vol. 112, pp. 1547-1556, 2017.

- [73] H. Y. Zhang, D. Pinjala, T. N. Wong, K. C. Toh, Y. K. Joshi, "Single-phase liquid cooled microchannel heat sink for electronic packages," *Appl. Therm. Eng.*, vol. 25, pp. 1472-1487, 2005.

- [74] H. Y. Zhang, D. Pinjala, Y. K. Joshi, T. N. Wong, and K. C. Toh, "Development and Characterization of Thermal Enhancement Structures for Single-Phase Liquid

18

- Cooling in Microelectronics Systems," *Heat Transfer Engineering*, vol. 28, pp. 997-1007, 2007.

- [75] N. Blet, S. Lips, V. Sartre, "Heats pipes for temperature homogenization: A literature review," *Appl. Therm. Eng.*, vol. 118, pp. 490-510, 2017.

- [76] Z. H. Wu, R. Du, "Design and experimental study of a miniature vapor compression refrigeration system for electronics cooling," *Appl. Therm. Eng.*, vol. 31, pp. 385-390, 2011.

- [77] X. C. Tong, "Advanced materials for thermal management of electronic packaging," *Springer*, New York, 2011.

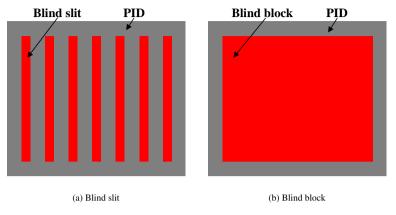

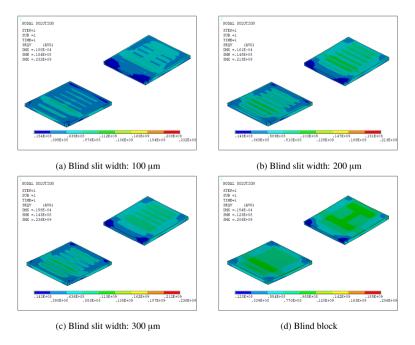

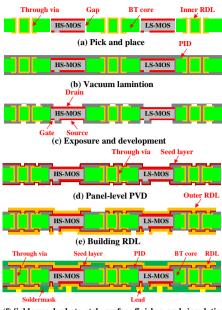

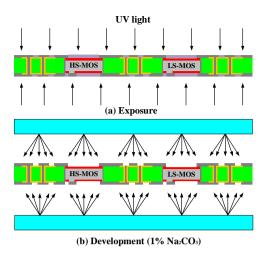

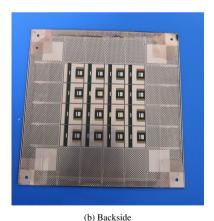

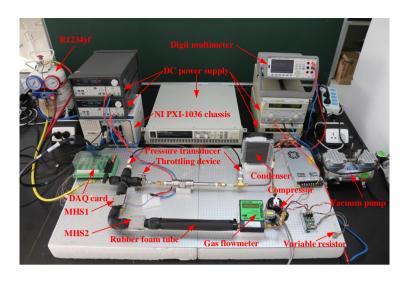

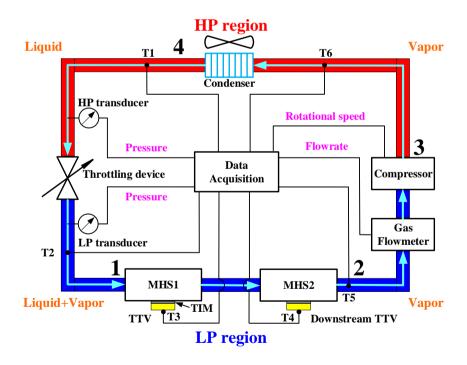

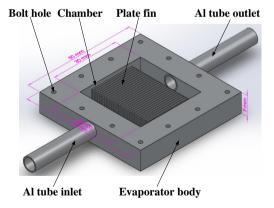

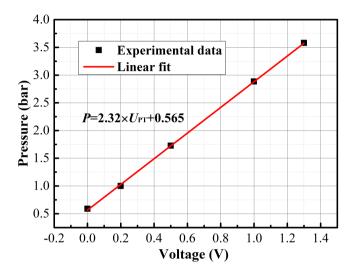

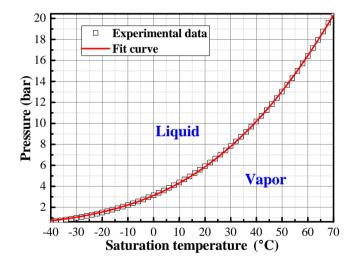

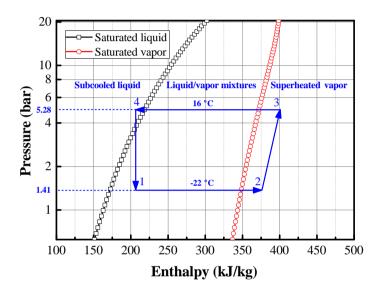

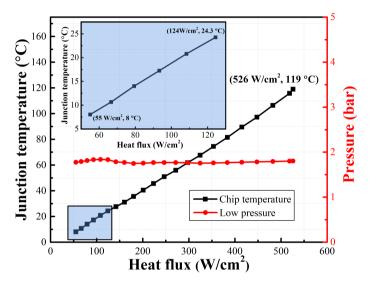

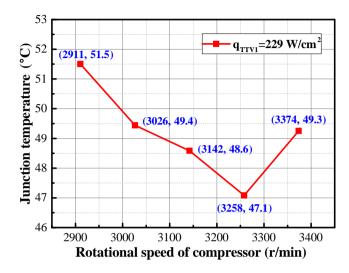

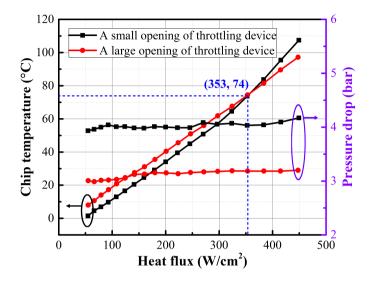

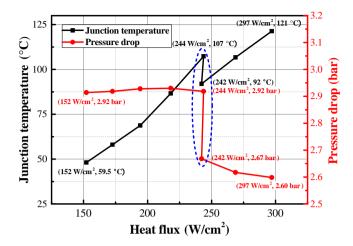

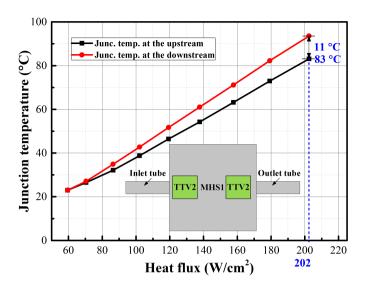

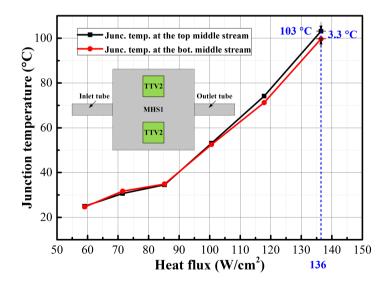

- [78] G. Tang, Y. Han, B. L. Lau, X. Zhang, and D. M. W. Rhee, "Development of a Compact and Efficient Liquid Cooling System With Silicon Microcooler for High-Power Microelectronic Devices," *IEEE Trans. Comp. Packag. Manuf. Technol.*, vol. 6, no. 5, pp. 729-739, 2016.