### Compact Resistor-Based Temperature Sensors for On-Chip Thermal Monitoring

Angevare, J.

10.4233/uuid:d6a157f1-9e33-4f39-9efa-ac83723a9128

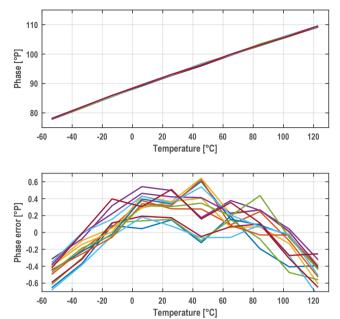

**Publication date**

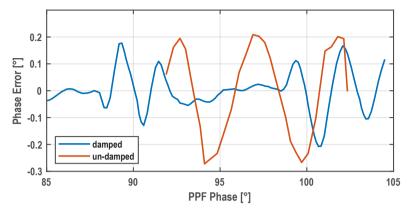

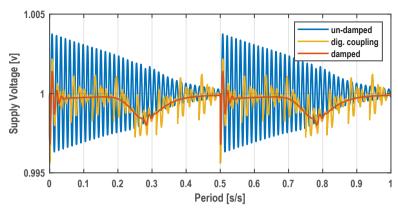

**Document Version** Final published version

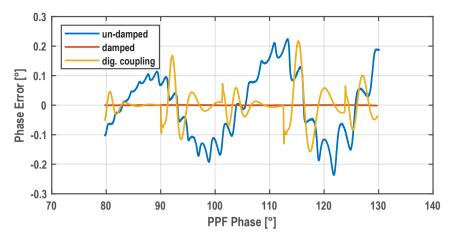

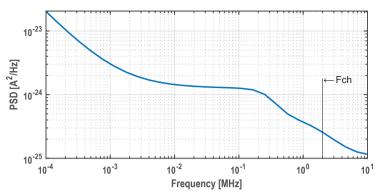

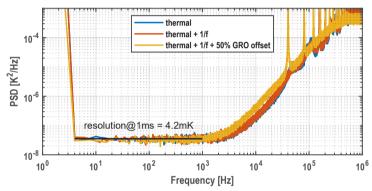

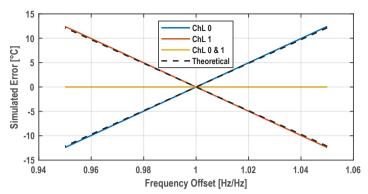

Citation (APA)

Angevare, J. (2024). Compact Resistor-Based Temperature Sensors for On-Chip Thermal Monitoring. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:d6a157f1-9e33-4f39-9efa-ac83723a9128

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Compact Resistor-Based Temperature Sensors for On-Chip Thermal Monitoring

Jan Angevare

# Compact Resistor-Based Temperature Sensors for On-Chip Thermal Monitoring

## **Proefschrift**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.dr.ir. T.H.J.J. van der Hagen, voorzitter van het College voor Promoties, in het openbaar te verdedigen op Woensdag 15 Mei 2024 om 15:00 uur

door

# Johannes Adrianus ANGEVARE

Ingenieur in de Micro-Elektronica, Technische Universiteit Delft, Nederland, geboren te Leiden, Nederland. Dit proefschrift is goedgekeurd door de promotor.

Samenstelling promotiecommissie bestaat uit: Rector Magnificus, voorzitter

Prof. dr. K. A. A. Makinwa, Technische Universiteit Delft, promotor

Onafhankelijke leden:

Dr. J. Shor, Bar-llan U. Israël

Dr M.H. Perrott,

Dr. Y. Chae,

Prof.dr.ir. K. Bult,

Dr.ir. M.A.P. Pertijs

Prof.dr. L.C.N. de Vreede

Texas Instruments, USA

Yonsei U. Sourth Korea

TU Delft / Ethernovia, NL

Technische Universiteit Delft

Technische Universiteit Delft

Published and distributed by: Ipskamp Drukkers B.V.

ISBN 978-94-6473-504-8

Copyright © 2023 by J. A. Angevare

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without written permission of the author.

Printed in the Netherlands

# **Contents**

| Chapter 1   Introduction1                               |

|---------------------------------------------------------|

| 1.1: Thermal Management                                 |

| 1.2: On-Chip Temperature Sensing                        |

| 1.2.1 – BJT-Based Sensors                               |

| 1.2.2 – Thermal Diffusivity-Based Sensors 4             |

| 1.2.3 - MOS-Based Sensors 5                             |

| 1.2.4 – Resistor-Based Sensors 6                        |

| 1.3: Area vs. Accuracy                                  |

| 1.4: Voltage vs. Time-Domain                            |

| 1.5: Thesis Objective                                   |

| 1.6: Thesis Contributions                               |

| 1.7: Thesis Organization                                |

| 1.8: References                                         |

| Chantan 2   Desigton Passed Tomponetum Consons          |

| Chapter 2   Resistor-Based Temperature Sensors          |

| 2.1.1 – Interconnects                                   |

|                                                         |

| 2.1.2 – Diffusion                                       |

| 2.1.3 – Foty-Sitton                                     |

| 2.2: Readout of Resistors                               |

|                                                         |

| 2.2.1 – Amplitude Domain                                |

| 2.3: Miniaturized Temperature-to-Digital Converters     |

| 2.3.1 – Frequency Locked Loop                           |

| 2.3.2 – Phase-Domain Sigma-Delta Modulator              |

| 2.3.2 – Thuse-Domain Signu-Detta Modulator              |

| 2.4. References                                         |

| Chapter 3   Design I: Analog Readout & Limited Accuracy |

| and Area 45                                             |

| 3.1: Single-Ended Wien-Bridge                           |

| 3.2: Phase-Domain Simga-Delta Modulator                 |

| 3.2.1 – Counter Time-Quantization Noise                 |

| 3.2.2 – Up/down Counter                                | 48    |

|--------------------------------------------------------|-------|

| 3.3: CCO                                               |       |

| 3.3.1 – CCO Non-Linearity                              | 50    |

| 3.4: Current Buffer                                    |       |

| 3.5: Shared Bias and Phase Reference Generation        |       |

| 3.6: Measurements                                      |       |

| 3.7: Conclusion                                        | 58    |

| 3.8: References                                        |       |

| Chapter 4   Design II: Digital Readout & Limit Cycling | 63    |

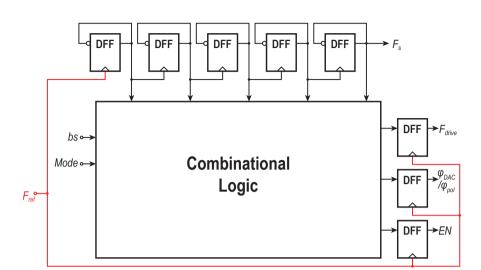

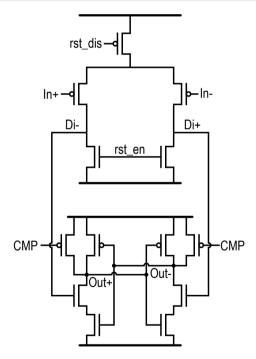

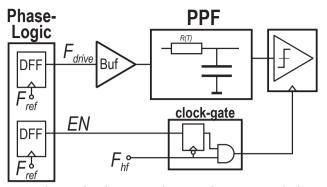

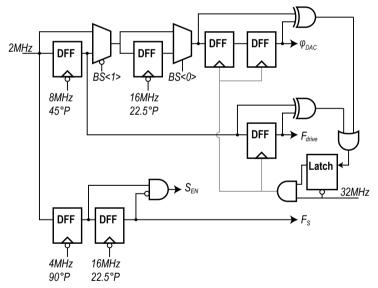

| 4.1: Digital Mixer                                     |       |

| 4.2: Windowing                                         |       |

| 4.2.1 – Time Quantization Noise                        |       |

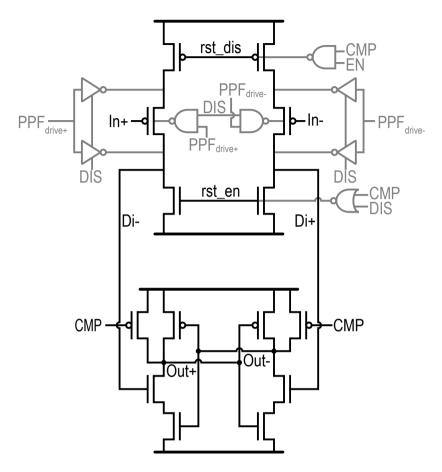

| 4.3: Phase Logic                                       |       |

| 4.4: Dynamic Comparator                                |       |

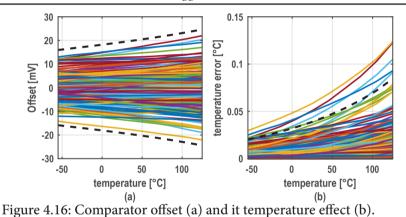

| 4.4.1 – Offset                                         |       |

| 4.4.2 – Delay                                          |       |

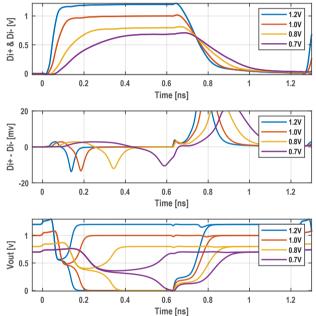

| 4.4.3 – Charge Kickback                                |       |

| 4.4.4 – Overvoltage                                    |       |

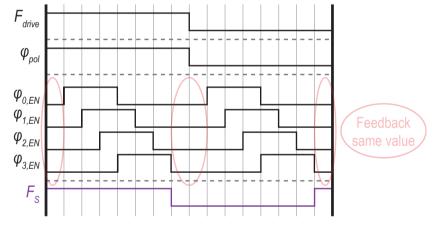

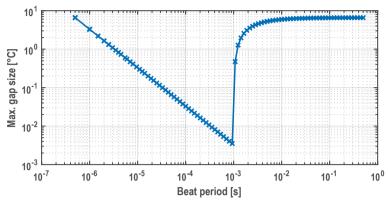

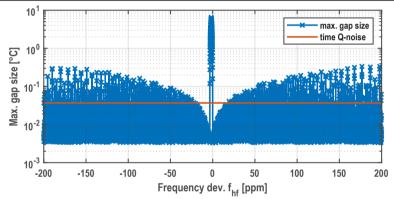

| 4.5: Beat Period                                       |       |

| 4.6: Measurement Results                               |       |

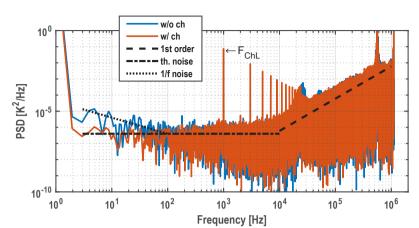

| 4.6.1 – Ringing                                        |       |

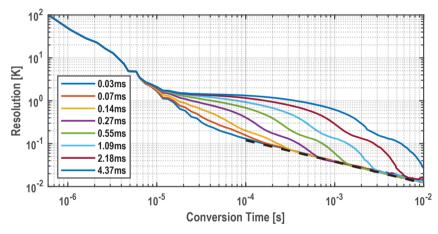

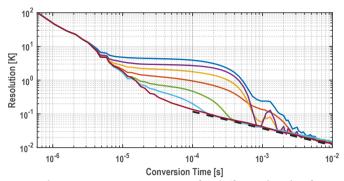

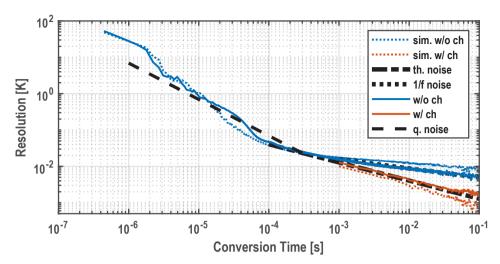

| 4.6.2 – Resolution                                     |       |

| 4.6.3 – DC Supply Sensitivity                          |       |

| 4.7: Conclusion                                        |       |

| 4.8: References                                        |       |

|                                                        |       |

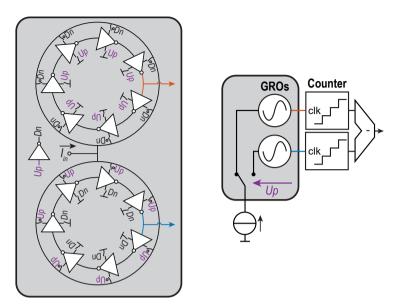

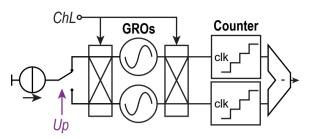

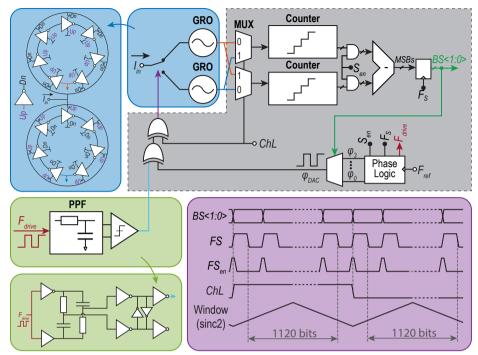

| Chapter 5   Design III: Dual-GRO PDΣΔM                 |       |

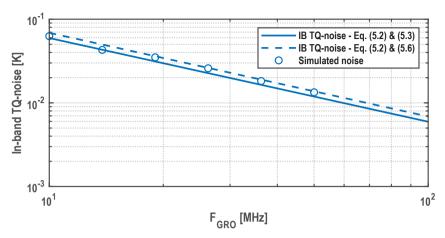

| 5.1: Time Quantization Noise                           |       |

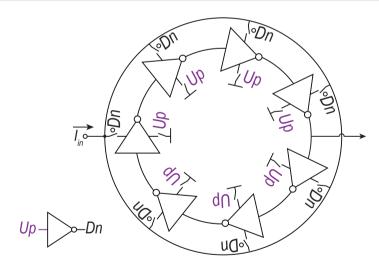

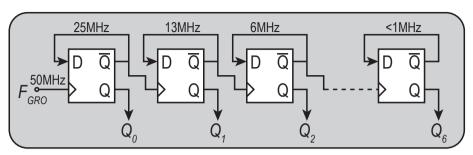

| 5.2: Dual GRO                                          |       |

| 5.2.1 – Current Bias                                   |       |

| 5.2.2 – Offset                                         | . 103 |

| 5.2.3 – Phase Noise                                    |       |

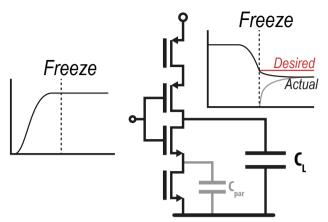

| 5.2.4 – Parasitic Charge                               | . 107 |

| 5.2.5 – Switch-Leakage                                 | . 110 |

| 5.2.6 – Excess Loop Delay                              | . 111 |

| 5.2.7 – Dual-CCO                                       | . 112 |

| 5.3: System                                            | 113   |

| 5 3 1 - Comparator                                     | 114   |

| 5.3.2 - Counter                            | 115   |

|--------------------------------------------|-------|

| 5.3.3 – Subtraction                        | 116   |

| 5.3.4 – Phase DAC                          | 116   |

| 5.4: Measurements                          | 119   |

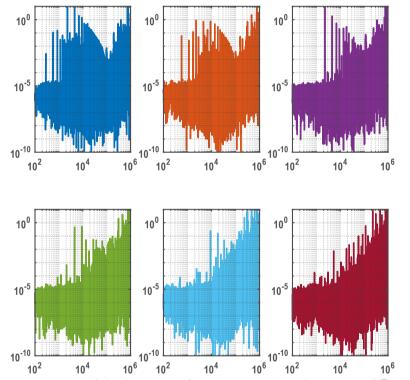

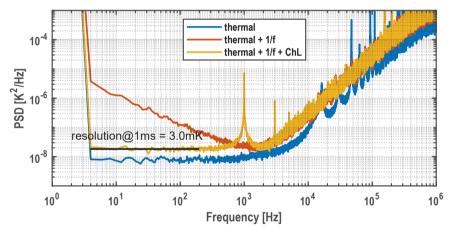

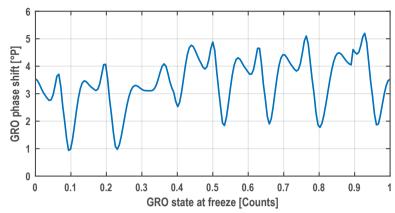

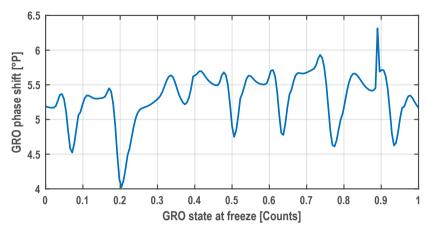

| 5.4.1 – Ringing                            | 120   |

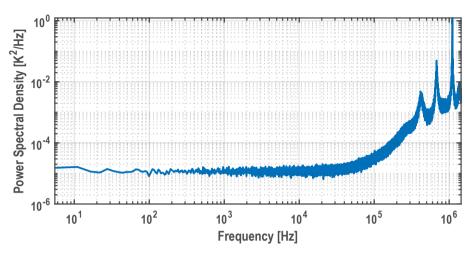

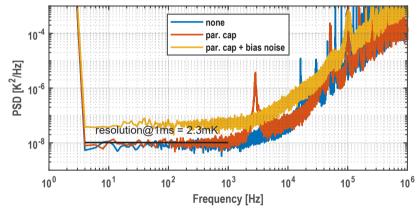

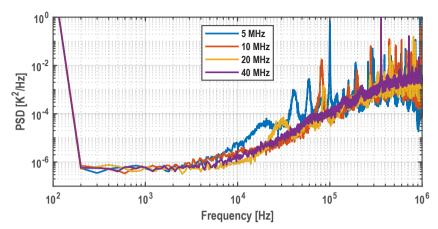

| 5.4.2 – Resolution                         | 120   |

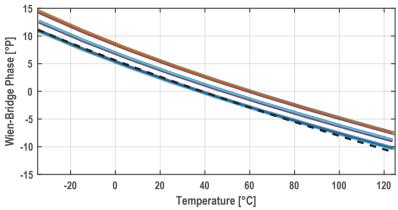

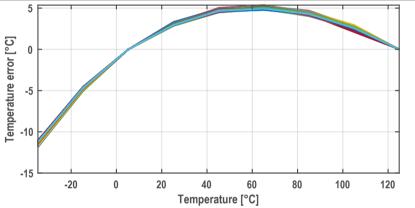

| 5.4.3 – Accuracy                           | 121   |

| 5.4.4 – Aging                              | 123   |

| 5.5: Conclusion                            | 124   |

| 5.6: References                            | 125   |

| Chantan (   Main Findings and Future Worls | 120   |

| Chapter 6   Main Findings and Future Work  |       |

| 6.1: Main Findings                         |       |

| 6.2: Design Considerations                 | 131   |

| 6.3: Future Work                           | 133   |

| 6.3.1 – Front-End                          | 133   |

| 6.3.2 - Readout                            | 134   |

| 6.3.3 – Physics                            | 135   |

| 6.4: References                            | 136   |

| Appendix I   Summary                       | 139   |

| Appendix II   Samenvatting                 |       |

|                                            |       |

| Acknowledgements                           | 147   |

| List of Publications                       | 149   |

| Ah aut tha Authau                          | 1 - 1 |

# Chapter 1 | Introduction

Modern System-on-Chips (SoCs) contain billions of transistors in a tiny area. So when they are operated at high clock frequencies, they can become very hot (>100°C), very quickly (in a few ms) [1]. Although advanced nodes require less switching power, their total switching activity tends to increase due to the increasing number of devices per unit area and/or higher switching frequencies. As a result, the effective energy density is increased, and self-heating is exacerbated. This self-heating can cause the chip to overheat, which in turn leads to logic errors, rapid aging, and in extreme cases, even to permanent damage [2].

2  $\sim$  Introduction  $\sim$

# 1.1: Thermal Management

To prevent overheating, SoCs often require careful thermal design using heatsinks and cooling fans. Even with these measures in place, many of these devices can still overheat when left running at their maximum performance level. Therefore, throttling strategies are required that perform dynamic voltage and frequency scaling (DVFS) when the chip is close to overheating [3]. The costs of these solutions are justified by the large performance boost that is gained by running the SoCs at higher thermal design points (TDPs).

# 1.2: On-Chip Temperature Sensing

To detect the thermal state of the chip, temperature sensors are required. Since SoCs can exhibit significant local self-heating (hotspots) where the local temperature can easily be  $10^{\circ}\text{C}$  higher than that of the surrounding die [2], each of these potential hotspots must be monitored by a temperature sensor. Since many of these sensors will be placed close to dense digital circuitry, they should be small (<<10  $000\,\mu\text{m}^2$ ) and tolerant of supply spikes and substrate noise. It is thus desirable for such sensors to operate from the digital supply voltage, and to maintain their required accuracy (~1°C) in the presence of supply voltage variations. This means that their resolution should also be commensurate, in the order of 0.1°C (rms). Furthermore, since thermal transients may have rise and fall times in the order of a few milliseconds, such sensors should have sampling rates of at least 1 kSa/s. However, their power consumption only needs to be a small fraction of the total system power, which is not difficult to achieve in most applications.

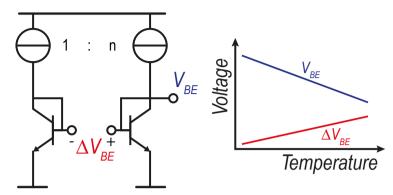

## 1.2.1 - BJT-Based Sensors

The BJT-based bandgap temperature sensor is the most common type of temperature sensor employed in CMOS technologies. These sensors exploit the fact that  $\Delta V_{BE}$  (the difference between the base-emitter voltages of two BJTs biased at different current densities) is proportional to the absolute temperature, while the base-emitter voltage ( $V_{BE}$ ) of a single BJT is complementary to the absolute temperature. This is shown in Figure 1.1 where the current density ratio is n:1. By comparing  $\Delta V_{BE}$  and  $V_{BE}$  to each other ( $\Delta V_{BE}/V_{BE}$ ), the absolute temperature can be determined. These

Figure 1.1: Typical BJT-based temperature sensor operating principle.

Figure 1.2: Diode/BJT discharing temperature sensing principle.

types of temperature sensors have been around for a long time, and their performance — especially their aging and drift — is quite well understood. In miniaturized versions, a BJT device is sometimes placed remotely to save area (as multiple BJTs for multiple temperature readings share the same readout) [2][4]. However, routing these analog lines is not trivial as they must be well shielded from digital circuit activity.

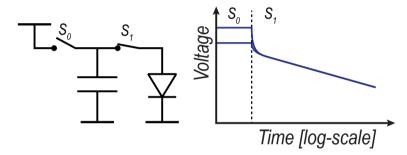

A downside of BJTs is that they require a large amount of headroom. The required base-emitter voltage can be as high as 0.9 V at low temperatures. On top of that, a current mirror is required (see Figure 1.1), which typically limits BJT-based temperature sensors to above 1.1 V. This is undesirable in the thermal management of SoCs because their operating voltages are typically between 0.6-0.9 V. In [5] an alternative biasing technique is proposed that prevents the extra headroom requirement. It involves discharging a pre-charged cap through a diode (Figure 1.2). As long as the initial voltage exceeds the base-emitter voltage, the discharging voltage

3

Figure 1.3: Thermal-diffusivity-based temperature sensing principle.

transient is not dependent on the initial charge. The same trick can also be applied using BJTs [6]. This approach does not require current sources on top of the BJTs, so the required headroom may be as low as 0.95 V [6]. In advanced processes, however, this is still higher than the digital supply voltage.

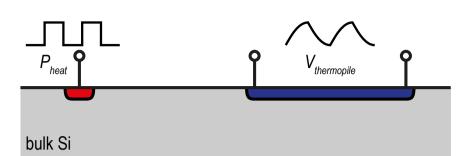

## 1.2.2 - Thermal Diffusivity-Based Sensors

Thermal diffusivity-based temperature sensors use the propagation delay of heat through the silicon as a measure of temperature [7][8]. Since the silicon that is used in advanced CMOS technologies is very pure and crystalline, its thermal diffusivity (the speed at which heat propagates) is well-defined. Typically, a resistor/switch generates a periodic heat pulse that is picked up by temperature difference detectors (thermopiles) to detect and subsequently digitize the phase shift (Figure 1.3). The advantage is that the accuracy of such sensors is mainly limited by lithography, making them quite accurate, even when untrimmed. The downside is that they require a relatively large amount of energy to generate the heat signal (~3 mW) while not achieving good resolution (~300 mK in 1 ms).

Overall, thermal diffusivity-based temperature sensors are well suited to thermal management applications [1]. They are small, accurate out of the box (little trimming required), can operate from any supply voltage, and scale well with technology. However, their energy efficiency is not yet good enough. When tens of temperature sensors are used on a die, they will consume tens of milli-Watts, which can be problematic for battery-powered devices.

Figure 1.4: Typical MOS leakage-based temperature sensor. The frequency ratio between ROs is used to minimize the supply sensitivity.

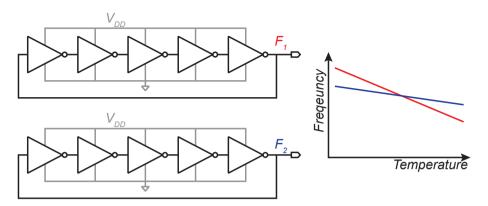

#### 1.2.3 - MOS-Based Sensors

MOS-based temperature sensors come in a variety of methods for measuring temperature. One uses the same approach as BJT-based sensors, but with the BJTs replaced by MOS or dynamic threshold MOS (DTMOS) devices [9][10]. The advantage is that these (DT)MOS-based devices do not require the high headroom that BJTs require. A major disadvantage is that they require large area to achieve good stability and accuracy, and they exhibit poor aging compared to BJTs, mainly due to the trapped charges in the oxide/gate-insulator.

Another method is to use the MOS transistor leakage current to measure temperature. This current is exponentially dependent on the temperature and is usually digitized by a ring oscillator (RO) to save area (see Figure 1.4). As a downside, the leakage current is also exponentially dependent on the drain-source voltage ( $V_{DS}$ ), and also the ring oscillator is highly supply-dependent [11]. Consequently, the main hurdle for these types of temperature sensors is achieving sufficient power-supply rejection to enable operation on the relatively wide and dynamically changing supply range of SoCs. Another bottleneck is that the effect of aging on the temperature accuracy is not well studied but is expected to be much worse than alternatives. This is mainly due to the aging effects of trapped charges in the oxide/gate-insulator that other types of devices, e.g., BJTs, do not experience.

6  $\sim$  Introduction  $\sim$

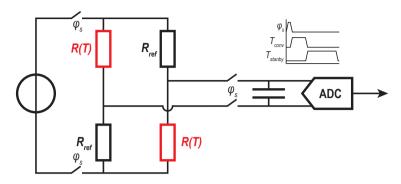

Figure 1.5: Resistor-based temperature sensor [13].

#### 1.2.4 - Resistor-Based Sensors

Resistor-based temperature sensors have become quite popular in recent years [12]. This is mainly because of their high energy efficiency, which is best in class and results from their large temperature coefficient (tempco) and low noise. However, for thermal management, their energy efficiency is already much better than required. On the other hand, accuracy is paramount, which is where resistor-based temperature sensors also do well. They achieve < 1 K accuracy after a 1-pt trim, which is mainly enabled by their trim ability, which is due to their relatively simple underlying physics. On top of that, they are not constrained by voltage headroom and can operate from any voltage.

One example of recent work in resistor-based temperature sensors is [13]. It uses a clocked Wheatstone bridge whose output voltage is sampled and subsequently digitized by a SAR ADC, see Figure 1.5. The Wheatstone bridge employs temperature-dependent resistors and reference (temperature-independent) resistors to generate a temperature-dependent output voltage. During the SAR conversion, the clocked Wien-bridge is disabled to save power.

# 1.3: Area vs. Accuracy

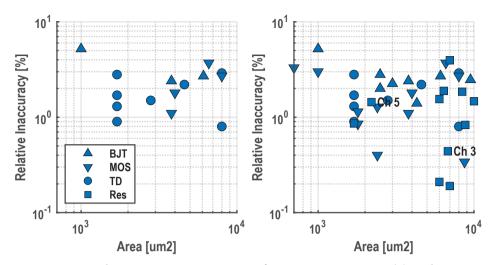

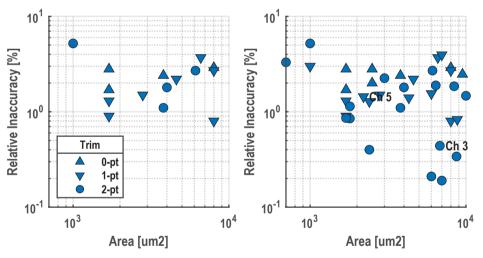

Figure 1.6 shows the relative inaccuracy (i.e., inaccuracy divided by the temperature range) vs. the area of different types of temperature sensors focusing on designs smaller than  $10\,000\,\mu\text{m}^2$  and Figure 1.7 shows the same but then for trimming points. Both show a trend where smaller

Figure 1.6: Relative inaccuracy vs. area of temperature sensors (a) at the start of this work and (b) after this work (2022-11) [12]

Figure 1.7: Relative inaccuracy vs. area of temperature sensors vs. trim points (a) at the start of this work and (b) after this work (2022-11) [12]

designs tend to be less accurate. Although this does not represent a fundamental tradeoff, there are two main reasons why this happens. The first is that readout circuits in such a small footprint usually contribute towards inaccuracy. To fit in such small footprints, they usually employ time-domain readouts that measure small temperature-dependent time constants from compact frontends. Another reason is that mismatch in minimized sensing elements will start to dominate. Usually, the effect

Area vs. Accuracy

8  $\sim$  Introduction  $\sim$

of mismatch is drowned by the effect of process variation. However, the mismatch eventually becomes significant when the sensing element's area is reduced. The area-vs.-accuracy tradeoff is the main challenge in designing temperature sensors for thermal management. Consequently, designers must be cautious when spending area, especially if there is little accuracy return on the spent area.

# 1.4: Voltage vs. Time-Domain

While the scaling of CMOS enables smaller dimensions and higher speeds, it comes at the cost of reducing the supply voltage. Consequently, while the voltage headroom is decreasing, the timing resolution of advanced nodes is increasing. This is the main reason why many designs are ported to the time domain [14]. Another benefit of time domain processing is that it tends to require less area [15]. The latter is mainly because voltage domain designs usually require relatively large transistors as well as capacitors. For these reasons, time-domain readouts should be preferred for thermal management targeted temperature sensors. Consequently, this thesis focuses on scalable, highly digital, time-domain readouts.

# 1.5: Thesis Objective

At the start of the research for this thesis, resistor-based temperature sensors were just gaining popularity because of their high energy efficiency. Although their accuracy and stability were good enough for thermal management, their potential for scaling had not yet been investigated. The goal of this work is to see how well the area of the resistor-based temperature sensors can be scaled without severe loss of accuracy and to see how suitable they are for use in thermal management applications.

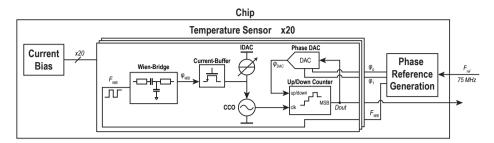

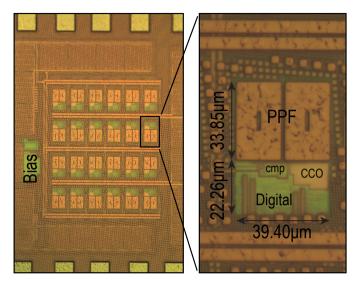

## 1.6: Thesis Contributions

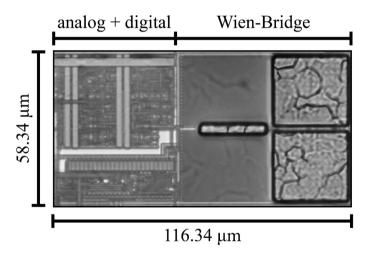

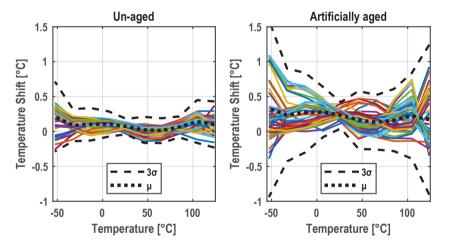

This thesis describes a series of explorations that ultimately resulted in a low area  $(2,210\,\mu\text{m}^2)$  and low power  $(28\,\mu\text{W})$  design that achieves a good resolution of  $12.8\,\text{mK}$  (rms) in a 1 ms conversion time with a  $\pm 1.3^\circ\text{C}$  ( $3\sigma$ ) accuracy from -55°C to  $125^\circ\text{C}$ . These explorations include the design of compact temperature sensors 1) using CCO-based highly-digital

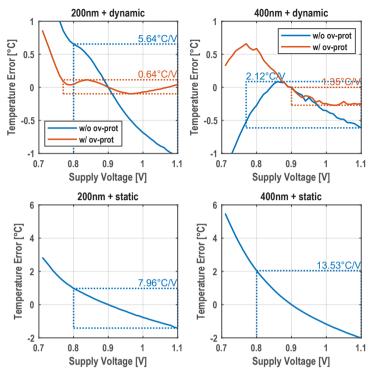

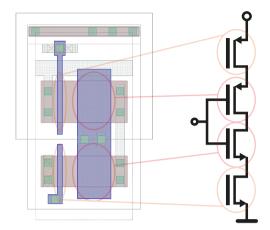

PDSDM, 2) using the combination of a comparator and a counter-based highly-digital PDSDM, and based on the knowledge acquired from these designs, 3) using a dual GRO + counter-based highly digital PDSDM that resulted in the best performance. In the process, the following issues were investigated: 1) time quantization effects in highly digital PDSDMs (such as dead zones and beat cycles), 2) supply sensitivity of poly-phase filters (especially in combination with static/dynamic comparators), and 3) the dual GRO structure (including the impact of leakage, mismatch, offset, and preferred layout).

# 1.7: Thesis Organization

~

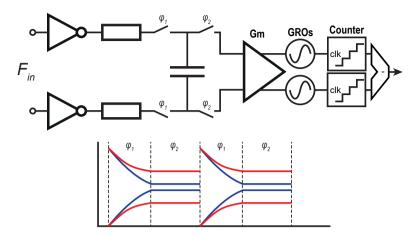

Chapter 2 first gives a short overview of the physical properties of the resistors available in CMOS technologies. It then goes on to discuss a few different ways to digitize resistance, eventually settling on a highly digital phase-domain sigma-delta modulator (PD $\Sigma\Delta M$ ). Finally, some of its important non-idealities are discussed, such as time-domain quantization noise and wrap-around.

The following three chapters describe a series of steps culminating in the final design. First, in Chapter 3, the highly digital CCO-based readout from [16] is merged with a modified single-ended version of the Wien-Bridge sensor from [17]. It is shown that the main accuracy limitation of the design arises from the non-linear current-to-frequency transfer of the CCO. Then, in Chapter 4, the CCO is removed from the signal path using a digital mixer to improve the sensor's accuracy. In this case, the counter is clocked at a constant frequency, revealing an underlying problem of the PD $\Sigma\Delta M$ . This chapter shows that the interaction between the PD $\Sigma\Delta M$ 's counter frequency and the  $\Sigma\Delta M$  sampling frequency causes timing artifacts that negatively impact the sensor's operation. Finally, in Chapter 5, a dual gated-ring oscillator is employed that maintains zero impact from CCO non-linearity and prevents the impact of these timing artifacts. This is enabled by using two oscillator and counter pairs and improves the energy efficiency of the PD $\Sigma\Delta M$  by two orders of magnitude.

Finally, Chapter 6 gives a conclusion and future recommendations.

## 1.8: References

- [1] U. Sonmez, R. Quan, F. Sebastiano, and K. A. A. Makinwa, "A 0.008-mm<sup>2</sup> Area-Optimized Thermal-Diffusivity-Based Temperature Sensor in 160-nm CMOS for SoC Thermal Monitoring," in *ESSCIRC* 2014 40th European Solid State Circuits Conference (ESSCIRC), 2014.

- [2] J. Shor, "Compact Thermal Sensors for Dense CPU Thermal Monitoring and Regulation: A Review," *IEEE Sensors Journal*, vol. 21, no. 11, pp. 12774-12788, 2021.

- [3] J. Shor and K. Luria, "Miniaturized BJT-based thermal sensor for microprocessors in 32-and 22-nm technologies," *IEEE journal of solid-state circuits*, vol. 48, no. 11, pp. 2860-2867, 2013.

- [4] C. -Y. Lu, S. Ravikumar, A. D. Sali, M. Eberlein, and H. -J. Lee, "An 8b subthreshold hybrid thermal sensor with ±1.07°C inaccuracy and single-element remote-sensing technique in 22nm FinFET," in *IEEE International Solid-State Circuits Conference*, San Francisco, 2018.

- [5] M. Eberlein and H. Pretl, "A No-Trim, Scaling-Friendly Thermal Sensor in 16nm FinFET Usig Bulk Diodes as Sensing Elements," *IEEE Solid-State Circuits Letters*, vol. 2, no. 9, pp. 63-66, 2019.

- [6] Z. Tang, S. Pan, and K. A. A. Makinwa, "23.5 A Sub-1V 810nW Capacitively-Biased BJT-Based Temperature Sensor with an Inaccuracy of ±0.15°C (3σ) from -55°C to 125°C," in *IEEE International Solid-State Circuits Conference*, San Fransisco, 2023.

- [7] C. P. van Vroonhoven and K. A. A. Makinwa, "Thermal diffusivity sensors for wide-range temperature sensing," in *SENSORS*, Lecce, Italy, 2008.

- [8] C. P. van Vroonhoven and K. A. A. Makinwa, "A CMOS Temperature-to-Digital Converter with an Inaccuracy of ±0.5 C (3σ) from -55 to 125°C," in *IEEE International Solid-State Circuits Conference*, San Fransisco, 2008.

- [10] Y. Kim, W. Choi, J. Kim, S. Lee, S. Lee, H. Kim, K. A. A. Makinwa, and Y. Chae, "A 0.02mm<sup>2</sup> embedded temperature sensor with ±2°C inaccuracy for self-refresh control in 25nm mobile DRAM," in *ESSCIRC Conference*, 2015.

- [11] Z. Tang, Y. Fang, Z. Shi, X.-P. Yu, N. N. Tan, and W. Pan, "A 1770-μm<sup>2</sup> Leakage-Based Digital Temperature Sensor With Supply Sensitivity Suppression in 55-nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 55, no. 3, pp. 781-793, 2020.

- [12] K. A. A. Makinwa, "Temperature Sensor Performance Survey," [Online]. Available: http://ei.ewi.tudelft.nl/docs/TSensor\_survey. xls. [Accessed 20 November 2022].

- [13] H. Xin, M. Andraud, P. Baltus, E. Cantatore, and P. Harpe, "A 174 pW-488.3 nW 1 S/s-100 kS/s All-Dynamic Resistive Temperature Sensor With Speed/Resolution/Resistance Adaptability," *IEEE Solid-State Circuits Letters*, vol. 1, no. 3, pp. 70-73, 2018.

- [14] M. Baert and W. Dehaene, "A 5-GS/s 7.2-ENOB Time-Interleaved VCO-Based ADC Achieving 30.5 fJ/cs," *IEEE Journal of Solid-State Circuits*, vol. 55, no. 6, pp. 1577-1587, 2020.

- [15] G. Taylor and I. Galton, "A Reconfigurable Mostly-Digital Delta-Sigma ADC With a Worst-Case FOM of 160 dB," *IEEE Journal of Solid-State Circuits*, vol. 48, no. 4, pp. 983-995, 2013.

- [16] R. Quan, U. Sonmez, F. Sebastiano, and K. A. A. Makinwa, "A 4600μm² 1.5°C (3σ) 0.9kS/s thermal-diffusivity temperature sensor with VCO-based readout," in *IEEE International Solid-State Circuits Conference*, San Fransisco, 2015.

- [17] S. Pan, Y. Luo, S. H. Shalmany, and K. A. A. Makinwa, "A Resistor-Based Temperature Sensor With a 0.13 pJ·K<sup>2</sup> Resolution FoM," *IEEE Journal of Solid-State Circuits*, vol. 53, no. 1, pp. 164-173, 2018.

#### $\sim$

# Chapter 2 | Resistor-Based Temperature Sensors

There are many types of resistors that are available in CMOS technology and many types of readout circuits that can be used to digitize their resistance. Not all resistors and readouts, however, can be used to realize a temperature sensor with desirable properties. For thermal management, these sensors must be small ( $<10\,000\,\mu\text{m}^2$ ), have moderate accuracy ( $\sim1\,\text{K}$ ,  $-55-125\,^{\circ}\text{C}$ ), have no or little cross-sensitivities (resulting in temperature errors smaller than its accuracy), and achieve a resolution of  $\sim100\,\text{mK}$  in a bandwidth of 1 ms with negligible power consumption (few mWs). This chapter describes the types of resistors that are available in CMOS and which of them are best suited for thermal management. Then the chapter discusses the different types of readouts that can be used to digitize resistance. In particular, the highly digital phase-domain sigma-delta modulator ( $PD\Sigma\Delta M$ ) proves promising for thermal management. Finally, a few advanced aspects of its operation are covered.

$\sim$

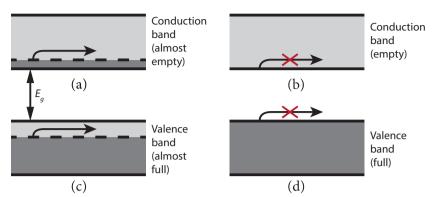

Figure 2.1: Electrical conduction/isolation when (a) free states are available in the conduction band, (b) no charge carriers are available in the conduction band, (c) free states are available in the valence band, and (d) no free states are available in the valence band.

# 2.1: Electrical Conduction

To better understand the merits and behavior of different types of resistors, first a short summary of electrical conduction is given. This is not meant as a comprehensive study, more in-depth analysis of this topic can be found in [1-2].

Electrons experience a mechanical force when subjected to an electric field, which can cause the electrons to change their state and accelerate. However, electrical conduction in solid-state materials can only occur when there are free states available for the electrons to move into, i.e., when they are in the conduction band (Figure 2.1 (a)) or when there are free states in the valence band (*holes*)(Figure 2.1 (c)).

Since metals have either Fermi levels within the conduction band or overlapping conduction and valence bands, there are always free states available to allow conduction. Undoped semiconductors, on the other hand, have Fermi levels in the bandgap; thus, no conduction is possible at 0 K. At higher temperatures, the Fermi-Dirac function widens, which allows small numbers of charge carries to conduct electricity. Doping is added to move the Fermi level closer to either the conduction or valence band, which drastically increases the charge carrier concentration and, therefore, the electrical conduction. The total current density is modeled by  $J = v \cdot e \cdot n$ , where v is the charge velocity, and n is the charge carrier concentration.

Under the influence of an electric field, electrons will accelerate and collide with obstacles along their path, which limits their velocity. The electric field strength and the mean free path between collisions determine the effective electron velocity. However, this collision process is highly statistical and complex. Consequently, it is modeled by the empirical model:  $v = \mu E = e\tau E/m$ , where  $\tau$  is the mean time between collisions,  $\mu$  is the electron/hole mobility, and m is the effective mass [1].

There are two collision mechanisms that dominate in semiconductor materials: 1) *phonon scattering* and 2) *ionized impurity scattering*. The former is due to vibrations in the crystal lattice, which happens at temperatures above 0 K. Higher temperatures cause more vibrations, which generally result in a higher probability of electron-phonon scattering. To first order  $\mu_L \propto T^{-3/2}$ , but in practice  $\mu_L \propto T^{-n}$ , where n is 2.3 for electrons and 2.1 for holes [3]. The latter is due to collisions with (charged) impurities in the lattice. These can arise from either unintended imperfections or the doping of the silicon. In theory, for low to medium impurity concentrations, *ionized impurity scattering* starts dominating at temperatures below 100 K [4]. In general, impure silicon has lower conductivity and its conductivity is less temperature-dependent.

Another collision mechanism observed in materials is *surface scattering*, which happens when charge carriers scatter against the edges of the conductor. This type of scattering only becomes significant as the thickness of the conductor approaches the mean free path of the charge carriers. For silicon, this distance is  $\sim 1.95\,\mu m$ , so silicon conductors with a thickness close to  $2\,\mu m$  or less show a noticeable decrease in electron mobility.

As a result of the many collision mechanisms that determine a resistor's temperature dependence, this is usually quite non-linear. These mechanisms also result in significant resistance spread, which then requires multi-point calibration to mitigate their impact. Consquently, resistor-based temperature sensors often require polynomial correction to remove systematic non-linearity, and multi-point calibration to remove part-to-part inaccuracies.

| resistor<br>type | collision mechanism                  | $TC^1$ [m $\Omega/\Omega/K$ ] |       | TC <sup>2</sup><br>[μΩ/Ω/K <sup>2</sup> ] |       | Rsq<br>[Ω/sq] |        |

|------------------|--------------------------------------|-------------------------------|-------|-------------------------------------------|-------|---------------|--------|

|                  |                                      | min                           | max   | min                                       | max   | min           | max    |

| Interconnect     | phonon, surface scattering           | 2.47                          | 3.29  | -1.62                                     | -0.25 | 0.02          | 0.25   |

| Diffusion        | phonon, impurity, surface scattering | 1.33                          | 1.57  | 0.76                                      | 0.95  | 97.99         | 707.40 |

| Poly-<br>Silicon | impurity, phonon, surface scattering | -0.36                         | -0.02 | 0.36                                      | 0.72  | 129.23        | 817.31 |

| Silicide         | phonon, surface scattering           | 2.08                          | 2.34  | -1.24                                     | -0.69 | 8.77          | 18.39  |

Table 2.1: Resistor types and their typical properties.

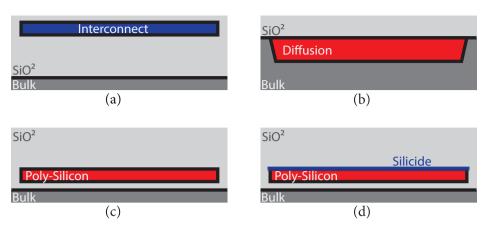

In the next sub-sections, the different types of available resistors in CMOS technologies will be discussed. Table 2.1 shows an overview of the available resistor types and their typical properties. Figure 2.2 (next page) shows a cross-section of the different resistor types.

#### 2.1.1 – Interconnects

Interconnects are used to connect on-chip components to each other and with the outside world. Ideally, since interconnects should not contribute to the electrical behavior of the circuit, their electrical resistance should be as small as possible. Consequently, interconnects are usually made of aluminum and copper, which are good conductors. Electrons in copper have a mean free path that is approximately 40 nm [5]. While this is irrelevant for mature processes which have a minimal metal width that is much wider than 40 nm, due to aggressive scaling, advanced nodes are affected by *surface scattering*.

Due to their many requirements, interconnects make lousy thermistors for thermal management. Their high conductivity means that a very long (and narrow) geometry is required to achieve resistances within a measurable range (larger than a few tens of  $k\Omega$ ). This requires a significant amount of area, especially in more mature technology nodes where the minimum interconnect width is relatively wide. However, the low electron mean free path of copper and its high charge carrier availability result in a conductor whose resistance is purely defined by *phonon scattering*. Therefore, interconnect resistors are expected to be some of the most accurate resistors available in CMOS.

16

Figure 2.2: Cross section of different resistor types; (a) interconnect, (b) diffusion, (c) poly-silicon, and (d) silicide.

Recently, a temperature sensor (for thermal management) using an interconnect resistor as its sensing element was proposed [6]. To achieve a resistance of  $121.7\,\mathrm{k}\Omega$ , a width/length of  $0.02\,\mu\mathrm{m}/1500\,\mu\mathrm{m}$  is used. These dimensions are enabled by a 5 nm technology. Interestingly, the accuracy of the proposed sensor (4 K from -55 to  $125\,^{\circ}\mathrm{C}$ , 1-pt trim,  $3\sigma$ ) is not at par with the state-of-the-art. One reason could be that the interconnect width (20 nm) is smaller than the expected electron mean free path in copper (40 nm). However, it is much more likely that the accuracy is limited by the chosen readout circuit.

# 2.1.2 – Diffusion

$\sim$

The temperature coefficient (TC) of diffusion resistors depends on both *impurity scattering* and *phonon scattering*. Diffusion resistors require doping to create the charge carriers needed for electrical conduction. In turn, these dopant atoms cause impurities in the crystal lattice, resulting in reduced conduction, especially at lower temperatures. As a result, their (higher-order) TC depends, among other factors, on the dopant concentration. This makes diffusion resistors more difficult to trim, as more temperature points are required for accurate trimming. On top of that, diffusion resistors have a charge depletion region at their interface with the p-sub/n-well, which causes leakage currents, voltage sensitivity, and noise coupling from the substrate. As a result, diffusion resistors are undesirable for thermal management applications.

## 2.1.3 – Poly-Silicon

Poly-silicon is an often used gate material that is grown on top of the gate insulator. It is composed of crystalline silicon grains with boundaries between the grains. These boundaries contribute to the resistance and have a negative TC. Furthermore, these boundaries contribute to a voltage coefficient (VC) [7] which can impact supply sensitivity, thus degrading cross-sensitivity and ultimately accuracy. The resulting TC of poly-silicon is determined by a combination of a positive (due to *phonon scattering*) and negative TC (due to *impurity/surface scattering*), resulting in a low TC that depends on multiple parameters. They are also known to be affected by aging (due to electromigration)[8]. Consequently, poly-silicon resistors are undesirable for use in temperature sensors.

#### 2.1.4 - Silicide

To contact a diffusion resistor, an ohmic contact between metal & silicon must be made. To prevent the formation of a Schottky diode, which appears at semiconductor/metal interfaces, a layer of silicide is annealed into the silicon lattice, resulting in a compound material. This silicide layer is used on all semiconductor/metal interfaces, i.e., on top of diffusion and on top of poly. Except for the n-well resistor, all resistors are available with this silicide layer grown over the entire surface. In fact, if unsilicided resistors are required, a special silicide stop layer is necessary to locally prevent the growth of silicide.

The resistance of most silicides exhibit near-linear metal-like behavior over temperature. They only deviate from this linear behavior at extremely low temperatures, i.e., below the Debye temperature (typically  $< 200 \, \text{K}$ ). Some silicides, just like some metals, can also show resistance saturation at higher temperatures (typically  $> 500 \, \text{K}$ ) [9].

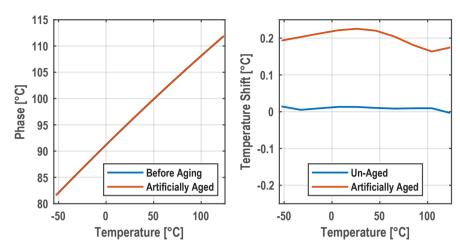

Since silicides exhibit metal-like behavior, metal-like thermistor performance can be achieved without the need for long and narrow interconnects. The main reason for this is that the silicide layer is very thin,

so the sheet resistance of silicided resistors is much higher than that of the metal interconnects. Of the two types of silicided resistors, silicided-poly resistors are the most attractive, as they do not contain a charge depletion region interface with the substrate. Although their behavior is mostly metallic, they have a small VC due to the grain boundaries of the silicide. Also, their effective electron mean free path seems to be around 0.2um [10]. Below this width, their sheet resistance will heavily depend on its width [11]. In principle, they should also be susceptible to aging (through diffusion and electromigration). However, an aging experiment (Chapter 5) indicates that after an initial 1-point trim, their aging does not significantly impact sensor accuracy. Another experiment [12] shows that after 500 hours of rapid aging (at 125°C), the error is smaller than 0.2 K, matching the results of Chapter 5. However, rapid aging measurements of over 10 000 hours using multiple parts are required to gain higher confidence level in silicided poly resistor aging.

Recently, resistor-based CMOS temperature sensors have garnered interest. This is because the high TC of the near-metallic silicided-poly resistor allows it to achieve superior energy efficiency. At the same time, the near metallic silicided-poly resistor has been shown to achieve reasonable accuracy after a 1 or 2-pt trim. This is because its TC is mostly defined by phonon-scattering, resulting in low spread, which allows easy trimming.

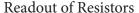

## 2.2: Readout of Resistors

There are two main approaches to reading out resistors: 1) in the amplitude domain and 2) in the time domain. Both cases require a reference to which the resistance is compared. The type of reference that is required and the way digitization takes place differ between these two approaches and have a large impact on the performance.

Figure 2.3: Wheatstone bridge temperature sensor.

## 2.2.1 - Amplitude Domain

The amplitude domain is the most straightforward domain for reading out a resistor. It involves applying a current to the resistor and then digitizing the voltage across it. This approach, which is used by most digital multimeters (DMMs), requires both an accurate current source as well as an accurate voltage source. Since those references require temperature compensation, this approach is not well suited for compact on-chip solutions.

Alternatively, a reference resistor can be used to compare the temperature-sensitive resistor (thermistor) to. The most popular method is to use a Wheatstone bridge configuration (see Figure 2.3), which can achieve superior energy efficiency, as low as  $10 \, \mathrm{fJK^2}$  [13]. In fact, this is quite close to the theoretical limit, which is derived from the bridge noise:

$$v_n^2 = \frac{4kTR}{2T_i} {(2.1)},$$

where k is the Boltzmann constant, T is the temperature, R is the effective Wheatstone-bridge resistance, and  $T_i$  is the integration time. Since the bridge output  $V_{bridge}$  can be expressed as:

$$V_{bridge} = \frac{R_p - R_n}{R_p + R_n} V_{dd} = \frac{\alpha_p T - \alpha_n T}{2 + \alpha_p T + \alpha_n T} V_{dd}$$

(2.2),

the bridge sensitivity is given by:

$$\frac{\partial V_{bridge}}{\partial T} = \frac{2(\alpha_p - \alpha_n)}{\left(2 + T(\alpha_p + \alpha_n)\right)^2} V_{dd} \approx 0.5 (\alpha_p - \alpha_n) V_{dd}$$

(2.3),

Figure 2.4: Temperature-to-digital converter using switched-cap resistor DAC.

where  $\alpha_p$  and  $\alpha_n$  are the first-order TCs. The power consumption is equal to  $V_{dd}^2/R$ . Neglecting the power consumption of the readout circuit and its noise contribution, the theoretical energy efficiency is:

$$\frac{8kT}{\left(\alpha_p - \alpha_n\right)^2} \qquad [JK^2] (2.4).$$

Considering a TC of 0.3 %/K, which is that of a silicided-poly resistor, we reach an ideal energy efficiency of 3.8 fJK<sup>2</sup>.

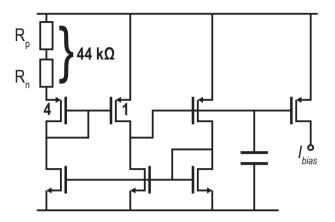

The main difficulty with realizing a Wheatstone bridge sensor is that there are no accurate untrimmed or temperature-stable resistors available in CMOS technology. To maximize temperature sensitivity, Wheatstone bridge sensors usually employ opposite TC resistors. As a result, their noise resolution is improved compared to their temperature-stable reference counterpart. However, as a downside, both resistors contribute towards TC spread and inaccuracy. Therefore, these types of sensors are typically less accurate (0.1—0.5 K) than their single TC counterparts (0.03—0.11 K). As discussed previously, the main difficulty in thermal management is to design sensors that are both accurate as well as small. Therefore, it is undesirable to spend twice the area (two resistors) while also doubling the inaccuracy.

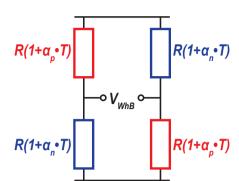

As a halfway house between the amplitude and time domain approaches, a switched capacitor resistor can be used as a temperature-stable resistor [14] (see Figure 2.4). This solution does not suffer from the increased inaccuracy of the dual resistor approach. Furthermore, its output is still a DC output, allowing for good energy efficiency. However, to maintain low

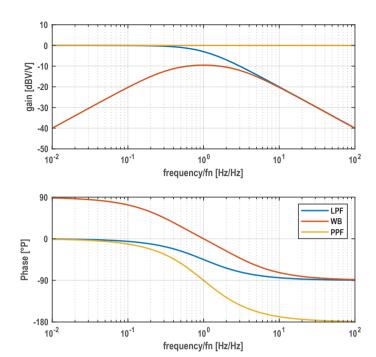

Figure 2.5: LPF, WB, and PPF filter responses; PPF around the nominal frequency has the steepest phase slope.

ripple, a large filter cap  $(C_p)$  is required, which occupies a large amount of area. This comes on top of the area that the analog readout already requires to digitize the temperature. Consequently, this approach is not suitable for use in compact temperature sensors.

#### 2.2.2 - Time Domain

While voltage headroom is reducing in the advanced process nodes where thermal management is required, their speed is increasing as well. Therefore, a better approach for thermal management is the use of a time-domain based readout circuit. This means that scaling/porting time-domain readouts to smaller technologies automatically results in improved timing resolution, accuracy, and energy efficiency.

In a time-domain readout circuit, a resistor is combined with a dynamic element to form a time constant. A capacitor is usually used as the dynamic element since it can be dense and temperature-stable. Instead of a current/voltage reference or resistor reference, this system uses a time reference

Figure 2.6: (a) simplified block diagram of an-LPF based temperature sensor [13] and (b) the transient input of the ADC, which tunes  $\varphi_i$  so its input is zero during  $\varphi_c$ .

to digitize the RC time constant. As a benefit, accurate and temperaturestable time references are readily available in the dense digital circuitry that requires thermal management.

There are three main topologies that comprise capacitors and resistors to make a temperature-dependent time constant. They are the first-order low-pass filter (LPF), the Wien-bridge (WB), and the poly-phase filter (PPF). The phase responses of these filters to a sine-wave input signal are plotted in Figure 2.5. Even though, for complexity reasons, these filters are usually driven by square waves (especially in the case of thermal management), their phase response plots are still a good predictor for phase sensitivity. The next three sub-sections will explore the pros and cons of each of these filter topologies.

#### 2.2.2.1 - Low-Pass Filter

The LPF is the most basic filter topology of the three. Although it requires fewer components than the WB (1 capacitor and 1 resistor), its sensitivity to resistance, and therefore temperature, is the lowest. Consequently, the WB is the preferred filter when directly digitizing the phase response because of its improved temperature sensitivity, reduced power-supply sensitivity, and its band-pass filter.

One published design, which is based on an LPF topology, samples the LPF voltage during its transition to determine the time constant [15] (see Figure 2.6). This is only possible with an LPF since it is composed of only

Figure 2.7: Wien bridge Filter.

a single capacitor that can easily be sampled. The sampled noise is equal to kT/C, where k is the Boltzmann constant, T is the temperature, and C is the capacitor value. Its sensitivity is:

$$\frac{\partial V_s}{\partial T} = \frac{V_{dd} \cdot T_d \cdot \alpha \cdot e^{-T_d}/R_0(1 + \alpha T_d)C}{R_0(1 + \alpha T)^2 C} \approx \frac{V_{dd} \cdot T_d \cdot \alpha \cdot e^{-T_d}/R_0C}{R_0 C}$$

(2.5),

where  $V_s$  is the sampled voltage,  $V_{ad}$  is the supply voltage,  $T_d$  is the sampling moment, which is around the halfway crossing point (i.e.,  $T_d \approx \ln(2)R_0C$ ),  $\alpha$  is the temperature coefficient of the resistor, and  $R_0$  is the resistance at room temperature. This results in:

$$\frac{\partial V_s}{\partial T} \approx \frac{V_{dd} \cdot \ln(2) \cdot \alpha}{2}$$

(2.6).

The consumed energy is  $0.5 \cdot V_{dd}^2 \cdot C$  and the resulting energy efficiency is:

$$FoM \approx \frac{2kT}{\ln(2)^2 \cdot \alpha^2}$$

(2.7).

For  $\alpha$  is 0.3 %/K, the ideal FoM is 1.9 fJK<sup>2</sup>. Surprisingly, this is better than the theoretical FoM of the Wheatstone bridge. However, only the noise caused by the sampling of the capacitors is taken into account. The power of the readout circuit, which is now a discrete time converter, is not.

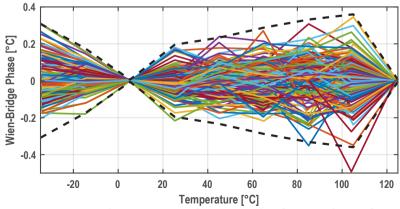

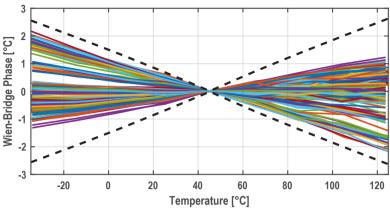

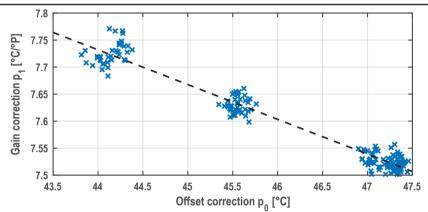

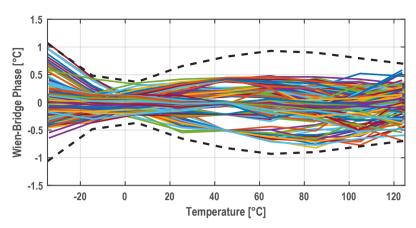

#### 2.2.2.2 – Wien Bridge

The WB combines a first-order LPF and a first-order high-pass filter (Figure 2.7). Compared to the LPF, it requires double the components, but also has double the phase sensitivity (Figure 2.5). One benefit of its inherent LPF is that the DC output voltage is insensitive to supply voltage variations. Therefore, the WB can be used in a single-ended setup (see Chapter 3), reducing the area at little cost to accuracy. The single-ended WB requires the same number of components as the differential first-order LPF, but it has double the sensitivity, resulting in improved accuracy.

The WB is typically readout by a PD $\Sigma\Delta M$  (Ch. 2.3.2), which has decreased energy efficiency compared to the amplitude domain resistor readout. Assuming a sinewave input, the amount of charge that the 1st stage integrator integrates during each  $\Sigma\Delta M$  cycle can be expressed as:

$$\Delta Q = \int_0^{T_{drive}/2} [A_I \sin(2\pi f_{drive}t + \varphi_{WB}) + I_{os}] dt$$

$$- \int_{T_{drive}/2}^{T_{drive}} [A_I \sin(2\pi f_{drive}t + \varphi_{WB}) + I_{os}] dt$$

$$= \frac{2A_I \cos(\varphi_{WB})}{\pi f_{drive}}$$

(2.8),

where  $T_{drive}$  is the period of the signal driving the WB, which is equal to the  $\Sigma\Delta M$  period,  $A_I$  is the amplitude of the current flowing out of the WB,  $f_{drive}$  is the frequency of the signal driving the WB, t is the time,  $\varphi_{WB}$  is the WB phase compared to the PD $\Sigma\Delta M$  phase, and  $I_{os}$  is the offset current that is integrated in the PD $\Sigma\Delta M$ . The integrated noise in the same period is:

$$\Delta Q_n = T_i \sqrt{\frac{4kT}{R} \frac{6}{9} \cdot \frac{1}{2T_i}} \bigg|_{T_i = \frac{1}{f_{drive}}} = \sqrt{\frac{4kT}{R} \frac{6}{9} \cdot \frac{1}{2f_{drive}}}$$

(2.9),

where  $T_i$  is the integration time, which is equal to  $1/f_{arive}$ . The WB phase sensitivity at its corner frequency is  $2/3 \cdot \alpha$ , where  $\alpha$  is the temperature coefficient of the resistor. Its temperature noise is then:

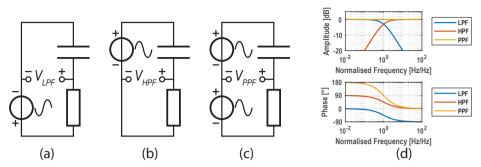

Figure 2.8: Low-pass filter (a), high-pass filter (b), poly-phase filter (c), and their amplitude and phase response (d).

$$\begin{split} T_{n,WB} &= \frac{\partial T}{\partial \varphi_{WB}} \cdot \frac{\partial \varphi_{WB}}{\partial Q} \cdot \Delta Q_n = \frac{3}{2\alpha} \cdot \frac{\pi f_{drive}}{2A_I} \sqrt{\frac{4kT}{R} \frac{6}{9} \cdot \frac{1}{2f_{drive}}} \\ &= \frac{3\pi}{4\alpha A_I} \sqrt{\frac{4kT}{R} \frac{6}{9} \cdot \frac{f_{drive}}{2}} \end{split} \tag{2.10}$$

Its RMS power consumption is  $A_I^2 \cdot R \cdot 3\sqrt{2}/\sqrt{2}$ , and so its FoM is:

$$\frac{A_I^2 \cdot R \cdot 3}{f_{drive}} \cdot \frac{9 \cdot \pi^2}{16 \cdot \alpha^2 A_I^2} \cdot \frac{4kT}{R} \frac{6}{9} \cdot \frac{f_{drive}}{2} = \frac{9 \cdot \pi^2 \cdot kT}{4 \cdot \alpha^2}$$

(2.11).

For a TC of 0.3 %/K, this results in an FoM of 5.9 fJK<sup>2</sup>. However, this assumes a sine-wave input, while usually a square wave is used. Moreover, it neglects the readout, which requires enough bandwidth to minimize its phase-shift contribution. As a result, the effective energy efficiency of WB types of temperature sensors (110 fJK<sup>2</sup> [16]) is lower than Wheatstone bridge types of temperature sensors (10 fJK<sup>2</sup> [13]).

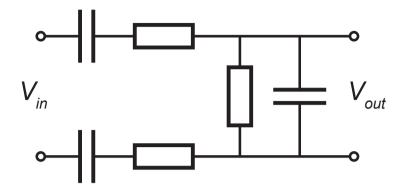

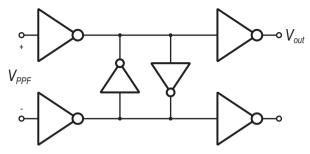

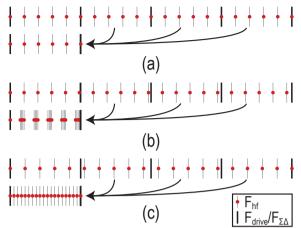

#### 2.2.2.3 – Poly-Phase Filter

As shown in Figure 2.8, a PPF requires only one resistor and one capacitor to achieve a second-order phase response. This is achieved by driving the RC filter with anti-phase signals. When the resistor side is driven, the resulting response is that of an LPF (Figure 2.8 (a)). However, when the

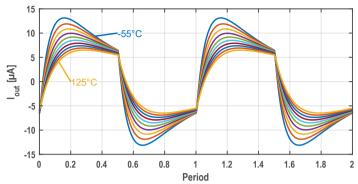

Figure 2.9: PPF transient response for different temperatures and VDD =

capacitor side is driven, the result is that of a high-pass filter (Figure 2.8 (b)). A superposition of these two filters driven in anti-phase (Figure 2.8 (c)) then results in the phase response of a second-order all-pass filter (Figure 2.8 (d)).

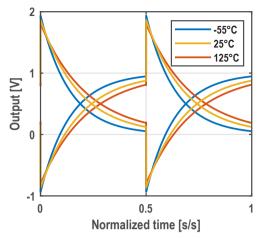

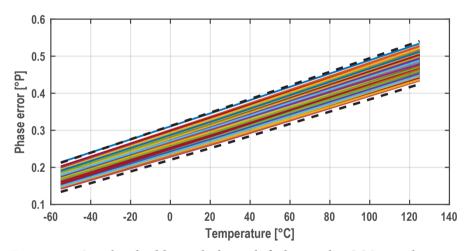

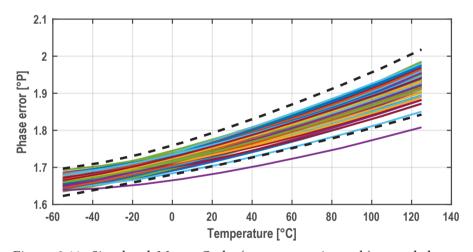

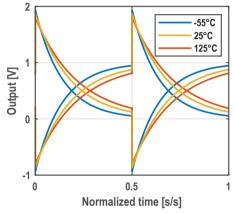

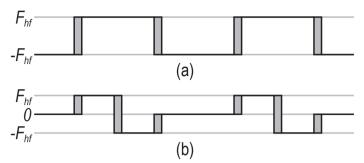

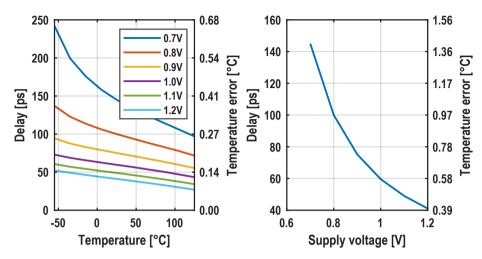

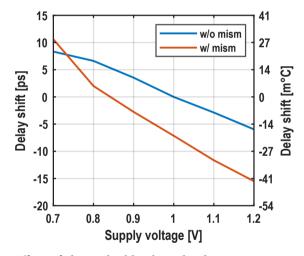

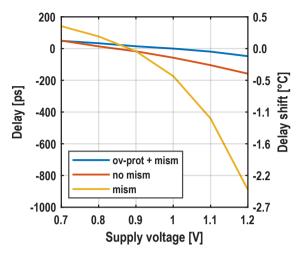

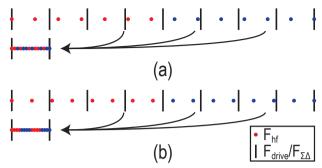

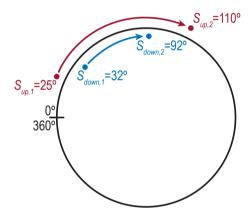

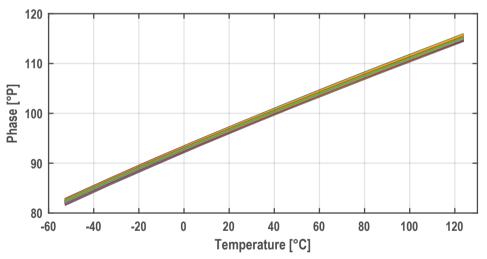

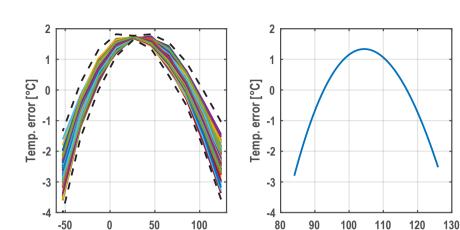

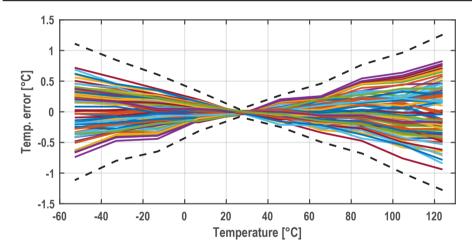

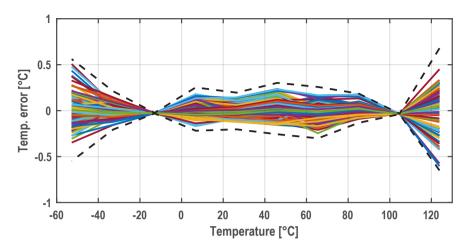

Figure 2.9 shows the PPF output when driven by a square wave for different temperatures. It can be seen that the phases of its zero-crossings (ZCs) are strongly temperature-dependent, making it ideal for readout by a comparator. However, it can also be seen that its output swings beyond the supply rails, which makes the design of the comparator even more challenging.

The use of ZC detection exacerbates the filter's output noise compared to readout circuits in which the filter's output is directly integrated [17]. In a continuous time PD $\Sigma\Delta M$ , the noise bandwidth, which is determined by the integration time, i.e.,  $1/(2 \cdot T_{conv})$ , can be very narrow. In contrast, the comparator directly translates the instantaneous voltage noise of the PPF's

Figure 2.10: PPF's noise sensitivity at zero-crossing.

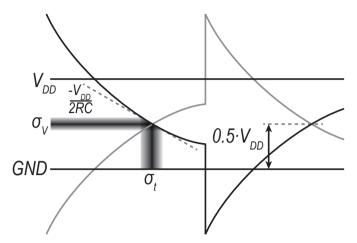

output into a phase error that depends on the slope of the output signal at the ZCs, as shown in Figure 2.10. The slope, and in turn the sensitivity, of the single-ended PPF at the ZC is given by:

$$\left. \frac{\partial \cdot 0.5 \cdot V_{DD} \cdot e^{-t/\tau}}{\partial t} \right|_{t=0} = \frac{-V_{DD}}{2 \cdot \tau} \tag{2.12},$$

where  $V_{dd}$  is the supply voltage, t is the time, and  $\tau$  is the PPF's RC time constant. The voltage noise of the PPF's output  $(\sigma_V)$  is related to kT/C, while the differential PPF has a  $\sqrt{2}$  x noise improvement over the single-ended version:

$$\sigma_t = \frac{2 \cdot \tau}{V_{DD}} \cdot \sqrt{\frac{1}{2} \cdot \frac{kT}{C}} \tag{2.13},$$

where *C* is the PPF capacitor value, *k* is the Boltzmann constant, and *T* is the temperature. The phase noise related to each comparator edge is then found to be:

$$\sigma_P = \frac{360^{\circ}}{T_c} \cdot \sigma_t \tag{2.14},$$

where  $T_s$  is the modulator period. There are two edges during each period  $(T_s)$ , while the total number of periods depends on the total conversion time  $(T_{conv})$ . Therefore, the total in-band phase noise for a given conversion time can be found with:

Figure 2.11: Steady-state PPF output waveform.

$$\sigma_{P,IB} = \sqrt{\frac{T_S \cdot 2}{T_{conv}}} \cdot \sigma_P = \frac{2 \cdot R \cdot C}{V_{DD}} \cdot \frac{360^{\circ}}{T_S} \cdot \sqrt{\frac{kT}{2C} \cdot \frac{T_S \cdot 2}{T_{conv}}} = \frac{720 \cdot R}{V_{DD}} \cdot \sqrt{\frac{kT \cdot C}{T_{conv \cdot T_S}}}$$

(2.15),

where *R* is the PPF resistor value.

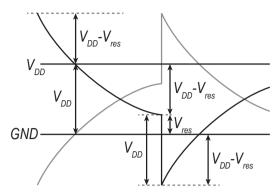

The ZC phase, along with the PPF amplitude and power, can be calculated with the help of Figure 2.11. At the end of each half period,  $V_{res} \cdot C$  charge is left in the capacitor just before the driving voltages toggle. This means that the maximum amplitude is  $2 \cdot V_{DD} - V_{res}$ . At steady state, both the initial and final voltages of each half-period are related:

$$V_{PPF}(T_s/2) = V_{res} = (2V_{DD} - V_{res})e^{-T_s/2\tau}$$

(2.16),

which subsequently results in:

$$V_{res} = \frac{e^{-T_{S/2\tau}}}{1 + e^{-T_{S/2\tau}}} \cdot 2 \cdot V_{DD}$$

(2.17).

The ZC moment happens when the PPF output is equal to half the supply voltage, therefore:

$$V_{PPF}(T_{ZC}) = 0.5 \cdot V_{DD} = (2 \cdot V_{DD} - V_{res}) \cdot e^{-T_{ZC}/\tau}$$

(2.18),

which results in:

$$T_{ZC} = \tau \cdot \ln \frac{4}{1 + e^{-T_{S/2\tau}}} = R \cdot C \cdot \ln \frac{4}{1 + e^{-T_{S/2\cdot R\cdot C}}}$$

(2.19).

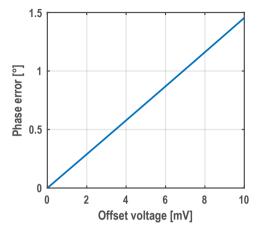

Figure 2.12: ZC phase over normalized driving frequency (top) and PPF phase sensitivity over normalized driving frequency (bottom).

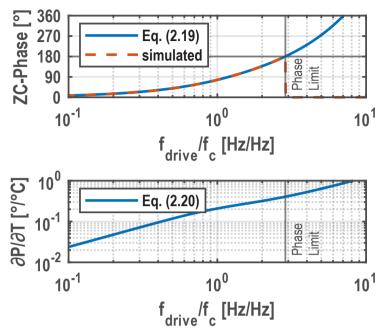

Using Eq. (2.14), the ZC delay is translated into a phase, which is plotted in Figure 2.12 (top). Then, using Eq. (2.19) and under the assumption that the resistor dominates the temperature sensitivity, we can find the phase sensitivity:

$$\frac{\partial P}{\partial T} = \frac{\partial}{\partial R(T)} \cdot \frac{360}{T_s} \cdot R(T) \cdot C \cdot \ln \frac{4}{1 + e^{-T_s}/2 \cdot R(T) \cdot C} \cdot \frac{\partial R(T)}{\partial T}$$

$$= \frac{360 \cdot \tau \cdot \alpha}{T_s} \cdot \left( \ln \left[ \frac{4}{1 + e^{-T_s}/2 \tau} \right] - \frac{T_s \cdot e^{-T_s}/2 \tau}{2 \cdot \tau \cdot \left( 1 + e^{-T_s}/2 \tau} \right) \right) \tag{2.20},$$

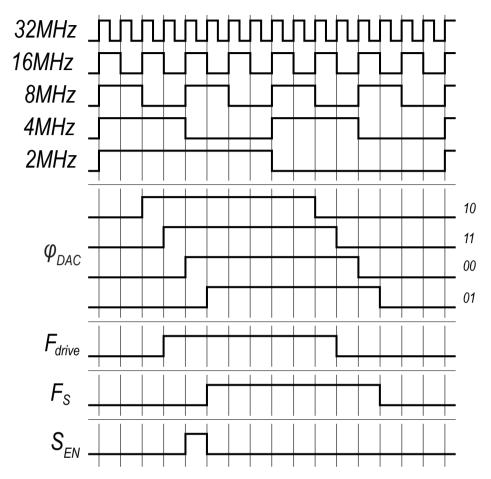

which is shown in Figure 2.12 (bottom), for  $\alpha = 0.3$  %/°C, which is the temperature coefficient of silicided p+ poly-silicon. This shows that to maximize the sensitivity, the driving frequency should also be maximized. However, a phase delay of larger than 180° means there are no ZCs before the driving signal (Fdrive) toggles. The consequence of this can be seen in Figure 2.12 (top, simulated), where the measured phase is equal to the driving signal for ZC delays of larger than 180°. Therefore, the driving frequency should remain below 2.8 times the PPF corner frequency.

Figure 2.13: Average PPF supply current over normalized driving frequency.

The power consumption of the PPF can be calculated by considering the charging and discharging of its capacitors. Every half period, the capacitors are (dis)charged from  $2 \cdot V_{DD} - V_{res}$  to  $V_{res}$ , which results in a total transferred charge every half-period of:

$$Q_{hp} = 2 \cdot (V_{DD} - V_{res}) \cdot C \tag{2.21}.$$

This then results in an average current of:

$$I_{avg} = 2 \cdot \frac{Q_{hp}}{O.5} \cdot T_s = \frac{8 \cdot V_{DD} \cdot C}{T_s} \cdot \frac{1 - e^{-T_s}/2\tau}{1 + e^{-T_s}/2\tau}$$

(2.22),

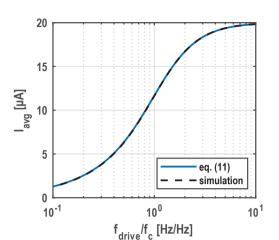

for a differential PPF, see Figure 2.13.

Finally, the ideal resolution FoM is calculated using (2.20), (2.15), and (2.22):

$$FoM = \left(\frac{\partial T}{\partial P} \cdot \sigma_{P,IB}\right)^{2} \cdot I_{avg} \cdot V_{DD} \cdot T_{conv} = \frac{2^{2} \cdot 8 \cdot kT}{\alpha^{2}} \cdot \frac{1 - e^{-T_{S}/2\tau}}{1 + e^{-T_{S}/2\tau}} \cdot \left(\ln\left[\frac{4}{1 + e^{-T_{S}/2\tau}}\right] - \frac{T_{S}}{2 \cdot \tau} \cdot \frac{e^{-T_{S}/2\tau}}{1 + e^{-T_{S}/2\tau}}\right)^{-2}$$

(2.23).

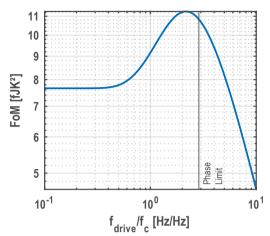

Figure 2.14: Ideal PPF FoM over normalized driving frequency (T = 300 K,  $\alpha$  = 0.3 %/°C).

Unsurprisingly, this is independent of the supply voltage or conversion time. It only depends on the temperature, the resistor's temperature coefficient, and the normalized driving frequency, i.e.,  $F_{drive} = 2\pi\tau/T_s$ . Figure 2.14 shows the FoM for  $T=300\,\mathrm{K}$  and  $\alpha=0.3\,\mathrm{\%/^\circ C}$  as a function of the driving frequency. It can be seen that a FoM as low as  $7.7\,\mathrm{fJK^2}$  can be obtained. This is the ideal, best-case FoM. In reality, driving the PPF and digitizing its phase not only costs energy but also adds noise.

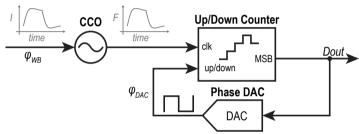

## 2.3: Miniaturized Temperature-to-Digital Converters

The readout circuit that is used to digitize the thermistor plays a significant part in the performance of the sensor. For thermal management, the readout should be small, use few analog components, and be robust to digital supply noise, simple to design and use, and easy to port to advanced processing nodes. Two types of readout are popular: using a frequency locked loop (FLL) or using a PD $\Sigma\Delta M$ . The former locks a frequency to the filter's time constant and is essentially a temperature-to-frequency converter, in which case a frequency-to-digital converter is used to digitize the frequency. The latter drives the filter at a constant frequency and directly digitizes its phase shift. The next two sections will take a closer look at each of these.

Figure 2.15: Simplified block diagram of a PDΣ $\Delta$ M.

#### 2.3.1 - Frequency Locked Loop

~

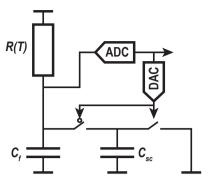

There are two main approaches for making a temperature-to-frequency converter. The first employs a relaxation oscillator to directly generate a frequency that is proportional to the filter's time constant, and hence to temperature [18]. The second approach uses a frequency locked loop (FLL) to lock the frequency of a controlled oscillator to the filter's time constant [19] [20] [15]. In both cases, a consecutive step is required in which the output frequency is digitized. This last step is often neglected in state-of-the-art designs. Assuming that a simple counter can be used to digitize the frequency, the cost of digitization can be quite low. However, to drive the controlled oscillator and make the controlled loop, an analog integrator is required. This integrator involves a capacitor integrator which can occupy a significant proportion of the area. An approach that is more digital and that does not rely on charge (capacitor) based integrators is a better option.

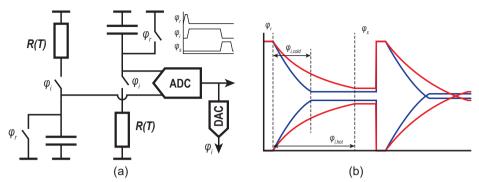

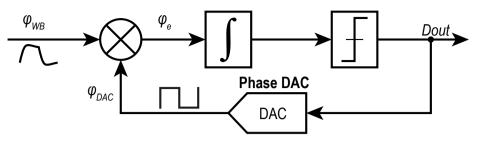

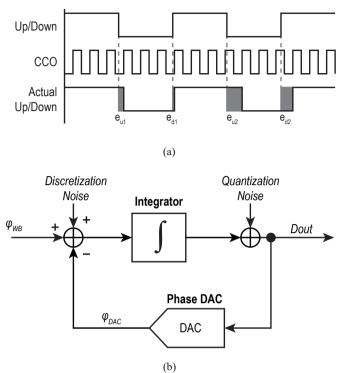

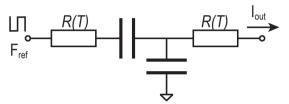

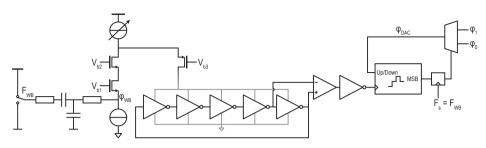

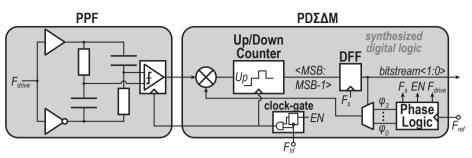

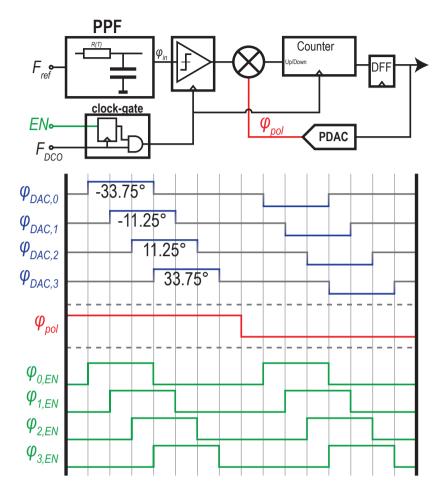

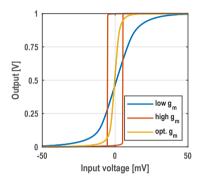

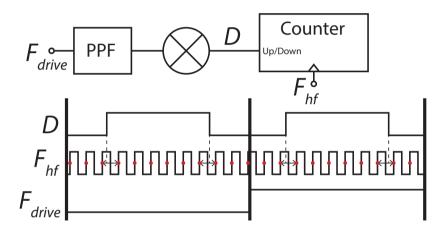

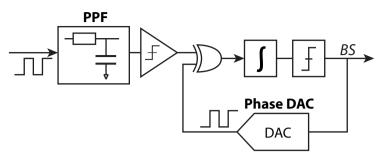

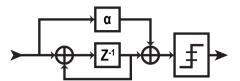

#### 2.3.2 – Phase-Domain Sigma-Delta Modulator

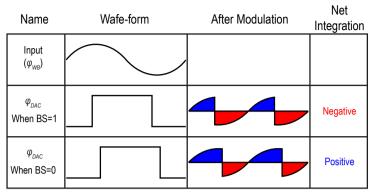

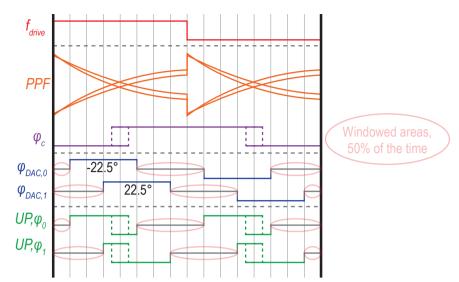

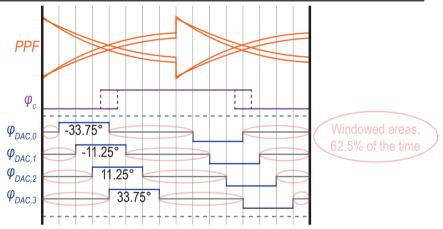

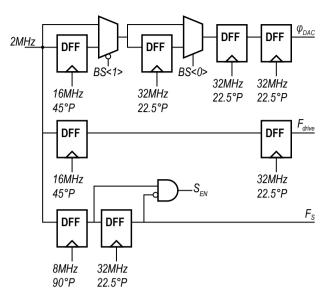

Figure 2.15 shows a simplified block diagram of a PD $\Sigma\Delta M$  [17]. An input phase ( $\varphi_{WB}$ , at a frequency of  $F_{WB}$ ) is first multiplied by a feedback phase ( $\varphi_{DAC}$ , also at a frequency of  $F_{WB}$ ). For sinusoidal signals, this results in a signal  $\varphi_{\epsilon}$  whose DC component is proportional to  $\cos(\varphi_{WB} - \varphi_{DAC})$ . For phase differences close to 90°,  $\cos(\varphi_{WB} - \varphi_{DAC} - 90°) \sim \varphi_{WB} - \varphi_{DAC}$  and so the demodulator effectively performs a phase-domain subtraction. In practice, the higher harmonics present in the WB output and the square wave of the phase DAC output also contribute to  $\varphi_{\epsilon}$  but the deviation is less than 5°. The DC component of  $\varphi_{\epsilon}$  and its harmonics are integrated and then digitized by a 1-bit quantizer whose output is fed back to the phase DAC. This drives the multiplier's DC output to zero so that the average feedback phase  $\varphi_{DAC}$  is equal to  $\varphi_{WB}$  + 90°.

Figure 2.16: Illustration of phase-DAC operation.

Figure 2.16 shows the phase error in the case of a sinusoidal input signal. Here, the phase-DAC generates one of two digital signals whose phases straddle the input phase  $+90^{\circ}$ . If the integrator state is > 0, the chosen phase causes a net negative value to be integrated during that period. Conversely, if the integrator state is < 0, a net positive value will be integrated during that period.

#### 2.3.2.1 - Cosine Non-Linearity

PD $\Sigma\Delta$ Ms use choppers to detect the phases of near-sinusoidal signals and thus suffer from cosine non-linearity [23]. This is a result of the value that is accumulated in the integrator each  $\Sigma\Delta$ M-cycle, which for sinusoidal driving signals can be expressed as:

$$\Delta C = \frac{2}{180} \cdot \frac{A_f}{F_{drive}} \cdot \cos \Delta \varphi \tag{2.24},$$

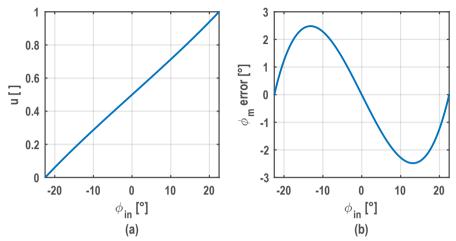

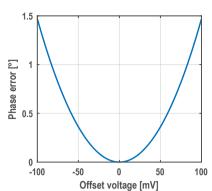

where  $\Delta C$  is the number of counts integrated each  $\Sigma \Delta M$ -cycle,  $A_f$  is the frequency amplitude (which is half the peak-to-peak frequency deviation),  $F_{drive}$  is the driving frequency, which is equal to the  $\Sigma \Delta M$  frequency, and  $\Delta \varphi$  is the difference between the input phase and the demodulating phase minus 90°. Because of the cosine term, this results in a non-linear bitstream average  $\mu$ , which is plotted in Figure 2.17 for  $\pm 22.5^{\circ}$  phase references. The error when linear bitstream averaging is applied is shown on the right and corresponds to  $\pm 2.5^{\circ}$ C.

The disadvantage of the non-linear readout is that it requires higher-order polynomials to correct for this systematic non-linearity. Moreover, because of its distortion, it is more difficult to trim errors in the resistor. More importantly, it prevents the use of a multi-bit  $\Sigma\Delta M$ . Sine-wave

Figure 2.17: Cosine non-linearity in the bitstream average (a) and its phase error (b) for phase references of  $\pm 22.5^{\circ}$ .

Figure 2.18: Block diagram of the highly digital PD $\Sigma\Delta M$ .

demodulation causes the cosine nonlinearity error seen in Figure 2.17 (b) in each LSB segment. It is virtually impossible to trim the sensor and correct for this error, even with higher-order polynomials, which require higher-order trimming.

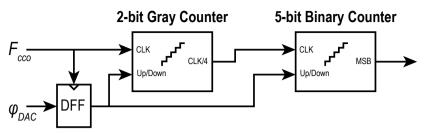

#### 2.3.2.2 - Highly Digital Implementation

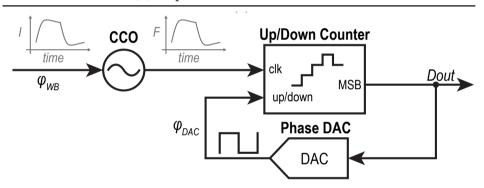

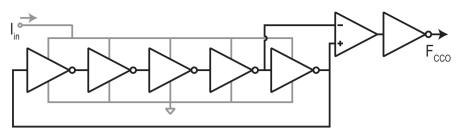

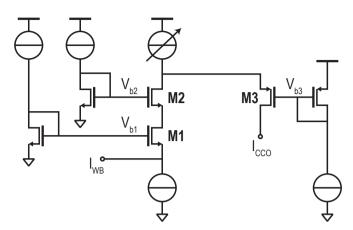

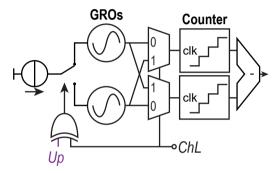

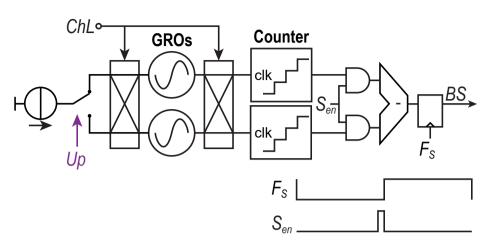

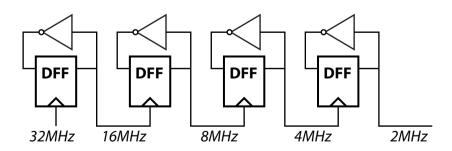

The straightforward implementation of the PD $\Sigma\Delta M$  employs an analog integrator which requires capacitors and an amplifier. Consequently, this implementation is not area-efficient and requires headroom. As an alternative, the analog integrator can be replaced by a time-based integrator, as shown in Figure 2.18. The modulator's loop filter consists of a digital counter which is driven by a current-controlled oscillator (CCO) [21]. The latter converts the input signal from the current domain to the frequency

domain, allowing the counter to be used as an integrator. By toggling the counter's up/down signal, the polarity of this integration can also be toggled, effectively multiplying the input signal with the up/down signal. The modulator's 1-bit quantizer can then be realized by merely sampling and evaluating the counter's MSB. The result is a highly digital PD $\Sigma\Delta M$  [20], which can be easily scaled.

In the case of the highly digital PD $\Sigma\Delta M$ , the value that is integrated each  $\Sigma\Delta M$  cycle ( $\Delta C$ ) can be expressed as:

$$\Delta C = \int_{0}^{T_{drive}/2} \left[ 0.5 F_{pp} \sin(2\pi f_{drive}t + \varphi_{in}) + F_{os} \right] dt$$

$$- \int_{T_{drive}/2}^{T_{drive}} \left[ 0.5 F_{pp} \sin(2\pi f_{drive}t + \varphi_{in}) + F_{os} \right] dt$$

$$= \frac{F_{pp} \cos(\varphi_{in})}{\pi f_{drive}}$$

(2.25),

where  $T_{drive}$  is the  $\Sigma\Delta M$  cycle period, which is equal to the driving period of the filter whose phase shift is digitized,  $F_{pp}$  is the CCO peak-to-peak frequency swing,  $f_{drive}$  is the  $\Sigma\Delta M$  cycle frequency,  $\varphi_{in}$  is the input phase (i.e., filter's output phase) that is digitized, and  $F_{os}$  is the CCO offset frequency. In the case of the counter based PD $\Sigma\Delta M$ , the unit of this value is in counts. This equation is the main equation used to determine phase sensitivity, and will be used many times throughout this thesis. In later chapters (Ch. 4 & 5) this equation is adjusted to reflect changes in the PD $\Sigma\Delta M$  architecture.

#### 2.3.2.3 - Counter Wrap-Around

Unlike an analog integrator, a counter does not clip. Instead, it wraps around. This corrupts the counter's state and must be prevented. After one  $\Sigma\Delta M$  period, the number of counts accumulated by the counter can be simplified to [22]:

$$C_{\Delta} \approx \frac{F_{CCO,pp}}{180^{\circ} \cdot F_{drive}} \cdot (\varphi_e)$$

(2.26),

where  $F_{CCO,pp}$  is the peak-to-peak CCO frequency variation,  $F_{drive}$  is the filter's driving frequency, which is equal to the  $\Sigma\Delta M$  sampling frequency.

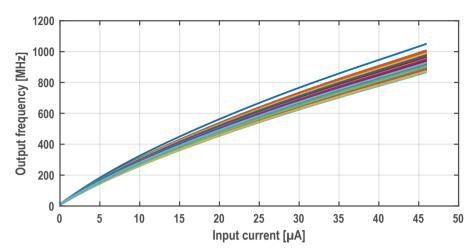

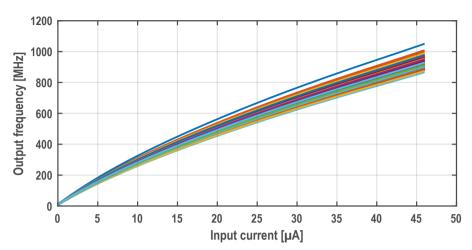

In a PD $\Sigma\Delta M$ , the counter's state oscillates around its mid-code, so to prevent wrap-around,  $C_\Delta$  should never exceed half the counter length. As a result, the counter's size is determined by the CCO frequency swing, the  $\Sigma\Delta M$  period, and the maximum input phase error. Consequently, the power consumption is mostly determined by the CCO frequency. A higher CCO frequency swing requires a higher average CCO frequency, which causes higher power consumption in the counter. Moreover, it also increases the counter size requirements, resulting in even higher power consumption. Consequently, in these highly digital designs the counter is the main power consumer.

Figure 2.19: (a) Timing diagram of the up/down and CCO signals, and (b) Linear model of the VCO-based PD $\Sigma\Delta M$ .

#### 2.3.2.4 - Time-Quantization Noise

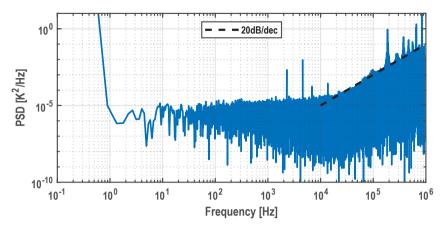

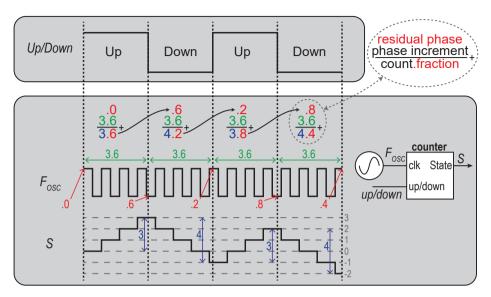

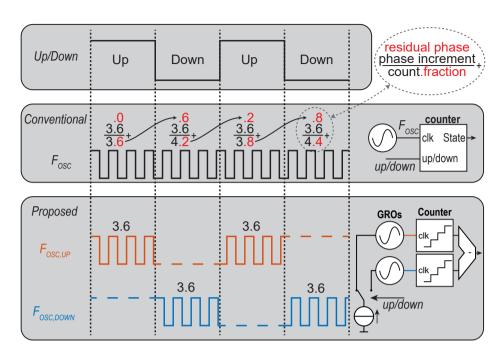

The downside of using a counter as an integrator is that it quantizes the phase of the CCO, and therefore introduces time-domain quantization noise [22]. Figure 2.19 (a) illustrates this: when the up/down signal toggles, the CCO phase, and therefore the integrator's state, is quantized. In this example, the CCO experiences approximately 3.15 cycles in the first "up" counting period. However, the counter truncates this to three cycles, creating an error in the integrator state. On top of that the next cycle starts at the truncated value, creating an error in the subsequent "down" counting period. As shown in Figure 2.19 (b), this time-quantization (TQ) noise can be modeled as an additive white-noise source at the input of the integrator [20], and so does not benefit from noise shaping.

To calculate the in-band TQ noise, the integrated error per  $\Sigma\Delta M$ -period is calculated. Each  $\Sigma\Delta M$ -period contains two moments at which the up/down signal is toggled. During these transitions, the phase of the CCO

is quantized, which incurs a uniform error between 0 and 1 CCO-period (i.e., between 0 and  $T_{CCO}$ ). The resulting integration error is equal to the time shift  $(1/\sqrt{12} \cdot T_{CCO})$  multiplied by the input jump  $(2 \cdot F_{CCO})$ . There are two chopping transitions in each  $\Sigma\Delta M$ -period, so the integrated error each period is:

$$\sigma_{\Delta c}^2 = 2 \cdot \left(\frac{1}{\sqrt{12}} \cdot T_{cco} \cdot 2 \cdot f_{cco}\right)^2 = \frac{2}{3}$$

(2.27).

The resulting in-band phase noise is then:

$$\sigma_{P,IB} = \sqrt{\frac{T_{drive}}{T_{conv}}} \cdot \sigma_{\Delta C} \cdot \frac{180^{\circ} \cdot F_{drive}}{F_{cco,pp}} = \sqrt{\frac{\sigma_{\Delta C}^{2}}{OSR}} \cdot \frac{180^{\circ} \cdot F_{drive}}{F_{cco,pp}} \quad (2.30),$$

where  $T_{drive}$  is the  $\Sigma\Delta M$  and driving period,  $T_{conv}$  is the total  $\Sigma\Delta M$  conversion time, and the OSR is the oversampling ratio. Assuming that the transitions of the up/down signal are random with respect to the CCO phase—which is the case if the CCO frequency ( $F_{CCO}$ ) is asynchronous with respect to the demodulating frequency ( $F_{drive}$ ), and/or if  $F_{CCO}$  is dithered by thermal noise—the counter's rounding error will have a uniform distribution. In that case, the total in-band phase noise (in radians) is given by [22]:

$$\sigma_{P,IB} = \sqrt{\frac{2}{3 \cdot OSR}} \cdot \frac{\pi \cdot F_{drive}}{F_{CCO,pp}}$$

(2.31).

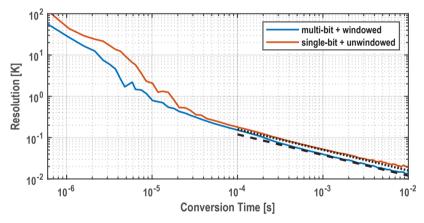

It can be seen that the discretization noise can be minimized either by decreasing  $F_{drive}$ , increasing the modulator's OSR, or increasing the CCO's frequency swing ( $F_{CCO,pp}$ ). Decreasing the driving frequency comes at the cost of area, since the filter's corner frequency must also decrease. Increasing the CCO frequency swing comes at the cost of increased counter power consumption, since it runs at a higher frequency and the counter size has to increase to prevent wrap-around. In practice, counter-based PD $\Sigma\Delta$ Ms are much less energy-efficient than their analog counterparts. However, their area efficiency is also superior, since the integrator size (a small counter) is

| 14016 2:2: 0            | Table 2.2. Overview of variations of important 1 D2Mit metrics.                        |                                                                                        |                                                                                      |                                                                                                    |  |  |

|-------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|

|                         | CCO + w/o<br>windowing<br>(Ch. 3)                                                      | Fixed OSC<br>(digital mixer)<br>(Ch. 4)                                                | Fixed OSC<br>(digital mixer)<br>+ windowing<br>(Ch. 4)                               | GRO (digital mixer) (Ch. 5)                                                                        |  |  |

| Integrated value        | $rac{F_{CCO,pp}}{180^{\circ} \cdot F_{drive}} \ \cdot \cos(arphi_e)$                  | $\frac{2 \cdot F_{OSC}}{180^{\circ} \cdot F_{drive}} \cdot \varphi_e$                  | $\frac{2 \cdot F_{OSC}}{180^{\circ} \cdot F_{drive}} \cdot \varphi_e$                | $\frac{2 \cdot F_{GRO}}{180^{\circ} \cdot F_{drive}} \cdot \varphi_e$                              |  |  |

| Per period<br>TQ error  | 2<br>3                                                                                 | $\frac{4}{3}$                                                                          | 3<br>3                                                                               | _                                                                                                  |  |  |

| Per conversion TQ error | _                                                                                      | _                                                                                      | _                                                                                    | 4<br>2                                                                                             |  |  |

| In band phase-noise     | $\frac{90^{\circ}}{F_{OSC}} \cdot \sqrt{\frac{F_{drive}}{T_{conv}} \cdot \frac{4}{3}}$ | $\frac{90^{\circ}}{F_{OSC}} \cdot \sqrt{\frac{F_{drive}}{T_{conv}} \cdot \frac{3}{3}}$ | $\frac{90^{\circ}}{F_{GRO}} \cdot \sqrt{\frac{F_{ChL}}{T_{conv}} \cdot \frac{4}{2}}$ | $\boxed{\frac{180^{\circ}}{F_{cco,pp}} \cdot \sqrt{\frac{F_{drive}}{T_{conv}} \cdot \frac{2}{3}}}$ |  |  |

Table 2.2: Overview of variations of important PD $\Sigma\Delta M$  metrics.

much smaller than a capacitor-based integrator. In thermal management, the resolution requirement is very relaxed, but the area efficiency is very strict.

In later chapters, the PD $\Sigma\Delta M$  architecture is modified for improved performance which introduces differences in the  $\Sigma\Delta M$ -cycle integrated value ( $\Delta C$ ), the TQ noise, and the in-band phase noise. Table 2.2 gives an overview of these differences.

#### 2.4: References

- [1] D. A. Neamen, Semiconductor Physics and Devices Basic Principles, Third ed., McGraw-Hill, 2003.

- [2] S. Sze, Semiconductor Devices: Physics and Technology, John wiley & sons, 2008.

- [3] C. H-M and *et al.*, "A comprehensive study of polysilicon resistors for CMOS ULSI applications," *Superlattices and Microstructures*, vol. 33, no. 4, pp. 193-208, 2003.

- [4] I.-T. Lu, J.-J. Zhou, J. Park and M. Bernardi, "First-principles ionized-impurity scattering and charge transport in doped materials," *Physical Review Materials*, vol. 6, no. 1, 2022.

- [5] S. X. Shian and D. Z. Pan, "Wire sizing with scattering effect for nanoscale interconnection," in *Asia and South Pacific Conference on Design Automation*, Yokohama, 2006.

- [6] J. Park, J. Kim, K. Kim, J.-H. Yang, M. Choi, and J. Shin, "A 0.65V 1316μm² Fully Synthesizable Digital Temperature Sensor Using Wire Metal Achieving 0.16nJ·%²-Accuracy FoM in 5nm FinFET CMOS," in *International Solid-State Circuit Conference*, San Fransisco, 2022.

- [7] W. A. Lane and G. T. Wrixon, "The design of thin-film polysilicon resistors for analog IC applications," *IEEE Transactions on Electron Devices*, vol. 36, no. 4, pp. 738-744, 1989.

- [8] S. Pan, Y. Cheng, G. Wu, Z. Wang, K. A. A. Makinwa, and H. Wu, "A 0.028mm² 32MHz RC Frequency Reference in 0.18μm CMOS with ±900ppm Inaccuracy from −40°C to 125°C and ±1600ppm Inaccuracy After Accelerated Aging," in *International Solid-State Circuits Conference*, San Francisco, 2024.

- [9] F. Nava, K. Tu, O. Thomas, J. Senateur, R. Madar, A. Borghesi, G. Guizzetti, U. Gottlieb, O. Laborde, and O. Bisi, "Electrical and optical properties of silicide single crystals and thin films," *Materials sience reports*, vol. 9, no. 4-5, pp. 141-200, 1993.

- [10] R. H. Bube, "Electronic transport in polycrystalline films," *Annual Review of Materials Science*, vol. 5, no. 1, pp. 201-224, 1975.

- [11] T. Ohguro, S. Nakamura, M. Koike, T. Morimoto, A. Nishiyama, Y. Ushiku, T. Yoshitomi, M. Ono, M. Saito, and H. Iwai, "Analysis of resistance behavior in Ti- and Ni-salicided polysilicon films," *IEEE Transaction on Electron Devices*, vol. 41, no. 12, pp. 2305-2317, December 1994.

- [12] K-S. Park, N. Pal, Y. Li, R. Xia, T. Wang, A. Abdelrahman, and P. K. Hanumolu, "A Temperature- and Aging-Compensated RC Oscillator With ±1030-ppm Inaccuracy From -40 °C to 85 °C After Accelerated Aging for 500 h at 125 °C," *IEEE Journal of Solid-State Circuits*, vol. 58, no. 12, pp. 3459-3469, Dec. 2023.

~

- [13] S. Pan and K. A. A. Makinwa, "A 10 fJ·K<sup>2</sup> Wheatstone Bridge Temperature Sensor With a Tail-Resistor-Linearized OTA," *IEEE Journal of Solid-State Circuits*, vol. 56, no. 2, pp. 501-510, 2021.

- [14] M. Perrott, J. Salvia, F. Lee, A. Partridge, S. Mukherjee, C. Arft, J.-T. Kim, N. Arumugam, P. Gupta, S. Tabatabaei, S. Pamarti, H. Lee, and F. Assaderaghi, "A Temperature-to-Digital Converter for a MEMS-Based Programmable Oscillator with Better Than ±0.5ppm Frequency Stability," in *IEEE International Solid-State Circuits Conference*, San Francisco, 2012.

- [15] A. Khashaba, J. Zhu, A. Elmallah, M. Ahmed, and P. K. Hanumolu, "A 0.0088mm<sup>2</sup> Resistor-Based Temperature Sensor Achieving 92fJ·K<sup>2</sup> FoM in 65nm CMOS," in *IEEE International Solid-State Circuits Conference*, 2020.

- [16] S. Pan, Ç. Gürleyük, M. F. Pimenta, and K. A. A. Makinwa, "A 0.12mm<sup>2</sup> Wien-Bridge Temperature Sensor with 0.1°C (3σ) Inaccuracy from -40°C to 180°C," in *IEEE International Colid-State Circuits Conference*, 2019.

- [17] C. P. van Vroonhoven and K. A. A. Makinwa, "Thermal diffusivity sensors for wide-range temperature sensing," in *SENSORS*, Lecce, Italy, 2008.

- [18] A. Mordakhay and J. Shor, "Miniaturized, 0.01 mm<sup>2</sup>, Resistor-Based Thermal Sensor With an Energy Consumption of 0.9 nJ and a Conversion Time of 80 µs for Processor Applications," *IEEE Journal of Solid-State Circuits*, vol. 53, no. 10, pp. 2958-2969, 2018.

- [19] W. Choi, Y. Lee, S. Kim, S. Lee, J. Jang, J. Chun, K. A. A. Makinwa, and Y. Chae, "A Compact Resistor-Based CMOS Temperature Sensor With an Inaccuracy of 0.12 °C (3σ) and a Resolution FoM of 0.43 pJ · K² in 65-nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 53, no. 12, pp. 3356-3367, 2018.

- [20] Y. Lee, W. Choi, T. Kim, S. Song, K. A. A. Makinwa, and Y. Chae, "A 5800-  $\mu$ m² Resistor-Based Temperature Sensor With a One-Point Trimmed Inaccuracy of  $\pm 1.2$  °C (  $3\sigma$  ) From -50 °C to 105 °C in 65-nm CMOS," *IEEE Solid-State Circuits Letters*, vol. 2, no. 9, pp. 67-70, 2019.