# A sampled voltage reference

C. T. Rooiiers

# A SAMPLED VOLTAGE REFERENCE

by

## C. T. Rooijers

in partial fulfillment of the requirements for the degree of

Master of Science in Microelectronics

at the Electronic Instrumentation Laboratory,

Department of Electrical Engineering,

Delft University of Technology,

to be defended publicly on Monday January 25, 2016 at 10:00 AM.

| Prof. dr. K. A. A. Makinwa |                                                      |

|----------------------------|------------------------------------------------------|

| Prof. dr. J. H. Huijsing   |                                                      |

| Prof. dr. K. A. A. Makinwa | TU Delft                                             |

|                            |                                                      |

| Dr. M. Pertijs             | TU Delft                                             |

|                            |                                                      |

| Dr. V. Giagka              | TU Delft                                             |

| Prof dr I H Hujising       | TU Delft                                             |

|                            | Prof. dr. J. H. Huijsing  Prof. dr. K. A. A. Makinwa |

This thesis is confidential and cannot be made public until December 31, 2020.

An electronic version of this thesis is available at http://repository.tudelft.nl/.

## **ABSTRACT**

This thesis describes the implementation of a sampled voltage reference. A sampled voltage reference aims to achieve both low-power and low-noise by storing the output of a voltage reference on a capacitor for a long time. This allows the reference to be switched off during the hold period, which leads to lower average power. At the same time, all the voltage reference's noise is pushed down into a bandwidth determined by the refresh frequency, while the buffer can be made low-noise by auto-zeroing.

The design of a continuous-time auto-zeroed buffer with low-noise and low-offset is presented. Various techniques have been used to reduce the transients created by auto-zeroing. In simulation the transients are below 1  $\mu$ V peak-to-peak, but the effectiveness of the techniques could not be evaluated in measurements.

The design of a low leakage sample and hold circuit is also presented. This uses bootstrap techniques to maintain zero potential across critical parasitic diodes. It is shown to be effective, resulting in a drift of about 5  $\mu$ V per second. A mechanism is found which explains how the buffer's residual offset is transferred to the hold capacitor. A special slow-chopping technique is presented and implemented to try to reverse the leakage due to this residual offset.

The final implemented design suffers from a large coupling between the high frequency reference clock and the output. It is shown that this causes a much higher residual offset than expected, which in turn increases the leakage of the hold capacitor. With a measured residual offset in the order of several 100  $\mu$ Vs and an auto-zeroing frequency of 2 kHz, the leakage in 1 s is 34 mV. Via simulation it is shown that with a lower residual offset, the leakage can be greatly reduced.

Methods of improving the current design have been investigated. A new clocking scheme is proposed and simulated. Improvements to the buffer are also proposed, which should lower its 1/f noise corner. This would allow for a lower auto-zeroing frequency, which in turn will further reduce the leakage.

## ACKNOWLEDGEMENT

First I would like to thank Prof. Kofi Makinwa for giving me the opportunity to work in a very inspiring research group on a very interesting project. He helped immensely by recognizing key moments in the project, by reemphasizing between what was key to the design and what was not. His active lobby for good presenting engineers, helped to continuously push my presentation skills.

Next I would like to thank Han Huijsing for his guidance throughout this project. Besides the many technical discussions on Monday and Tuesday, which were always very fruitful, we also had very interesting discussions on non-technical subjects. The fact that I could always reach him, despite his busy schedule, was very helpful and comforting.

I would like to thank Kia Souri for the regular meetings about the project and giving me a nice start at the beginning of the project. I hope that our separate contributions will be combined in the near future.

I would like to thank Jan Angevare for helping out with the digital design and layout, after the design review. I appreciate how friendly he stayed, besides the numerous times that he had to change the pad ring. His calmness was very comforting and helpful, especially when the pressure raised with the tape-out deadline approaching. I would like to thank Atef for his help during the final month before the tape-out with the chip finishing and the transferal of the layout to the manufacturer. His contacts and experience turned out to be priceless.

I would like to thank all group members for their useful feedback and idea's during group meetings and design reviews. You all helped to make my time as a master student a very educational and enjoyable experience. I would like to thank: Jan, Jeroen, Janquan, Yinka, Saleh, Junfeng and Long for helping me in various ways. I would like to thank Zu-yao, Lukasz and Ron for their help with my PCBs, Ron for giving a mini crash course in SMD soldering and Zu-yao for bonding my chips. I would like thank Joyce and Karen for doing the paperwork that makes all other work possible and for the numerous fun activities they organized.

Last but definitely not least, I would like to thank my family for their support and understanding during some of my long days at the university. Your love and support helped me through the less joyful moments of this project.

C. T. Rooijers

Delft, January 2016

# **CONTENTS**

| Lis | t of F | gures                                                                         | xi |

|-----|--------|-------------------------------------------------------------------------------|----|

| 1   | Intro  | duction                                                                       | 1  |

|     | 1.1    | Literature/History                                                            | 2  |

|     | 1.2    | State-of-the-art / recent techniques                                          | 2  |

|     | 1.3    | Motivation                                                                    | 3  |

|     | 1.4    | Key idea                                                                      | 3  |

| 2   | Syste  | m Level Design                                                                | 5  |

| -   | 2.1    | Offset and offset drift cancellation                                          |    |

|     | 2.1    | 2.1.1 Trimming                                                                |    |

|     |        | 2.1.2 Chopping                                                                |    |

|     |        | 2.1.3 Auto-zeroing                                                            |    |

|     |        | 2.1.4 Reducing the unity-gain error                                           |    |

|     |        | 2.1.5 Conclusion                                                              |    |

|     |        | 2.1.6 Specifications                                                          |    |

|     | 2.2    | A continuous-time auto-zeroed buffer                                          |    |

|     | 2.3    | Switching transients                                                          |    |

|     | 2.5    | 2.3.1 Active integration                                                      |    |

|     |        | 2.3.2 Dead time                                                               |    |

|     |        | 2.3.3 Source degeneration                                                     |    |

|     | 2.4    | Residual offset analysis                                                      |    |

|     | 2.5    | Noise analysis                                                                |    |

|     | 2.3    | 2.5.1 Getting low noise in the 0.1 to 10 Hz bandwidth                         |    |

|     |        | 2.5.2 Auto-zero noise                                                         |    |

|     | 2.6    | Achieving a long hold time                                                    |    |

|     | 2.0    | 2.6.1 Body diode leakage                                                      |    |

|     |        | 2.6.2 Channel leakage                                                         |    |

|     |        | 2.6.3 Capacitor selection                                                     |    |

|     |        | 2.6.4 Charge injection/ Clock feedthrough                                     |    |

|     |        | 2.6.5 Input current of the buffer and AZ1                                     |    |

|     | 2.7    | Charge kickback                                                               |    |

|     | 2.7    |                                                                               |    |

|     | 2.8    | Slow-chopping                                                                 | 23 |

| 3   | Tran   | sistor level implementation details                                           | 27 |

|     | 3.1    | Buffer transistor implementation                                              |    |

|     | 3.2    | AZ1 implementation                                                            |    |

|     | 3.3    | AZ2 and AZ3 implementation                                                    | 29 |

|     | 3.4    | Integrator                                                                    | 30 |

|     | 3.5    | Digital design                                                                | 31 |

|     | 3.6    | Layout                                                                        | 32 |

| 4   | Resu   | ts and Future work                                                            | 35 |

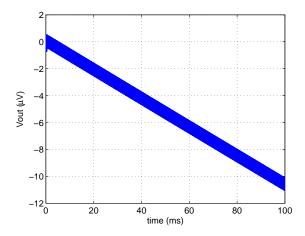

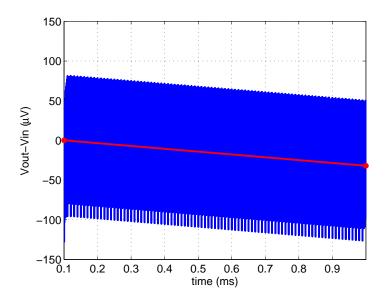

| -   | 4.1    | Simulation of the switching transients                                        |    |

|     |        | 4.1.1 Conventional continuous-time auto-zeroed buffer                         |    |

|     |        | 4.1.2 Continuous-time auto-zeroed buffer with active integration              |    |

|     |        | 4.1.3 Continuous-time auto-zeroed buffer with active integration and deadtime |    |

|     |        | 4.1.4 Post-lavout                                                             | 38 |

X CONTENTS

|     | 4.3 T<br>4.4 M<br>4.5 H<br>4 4<br>4.6 T<br>4.7 F<br>4<br>4.7 F | he me<br>Measur<br>Hold ti<br>.5.1<br>.5.2<br>.5.3<br>he effo<br>.6.1<br>.6.2 | asurement setup. asured effect of the reference clock on the output. ed hold time without auto-zeroing. me with continuous auto-zeroing. Pre-layout simulation. Post-layout simulation Measured. ect of clock signals on the measured leakage The effect of the complementary reference clock. The effect of loading the reference clock. work Changing the clocking scheme Lower the required auto-zeroing frequency Using trimming to compensate the leakage current Other improvements | 39<br>40<br>42<br>43<br>43<br>44<br>45<br>47<br>49<br>50 |

|-----|----------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|     | _                                                              | .7.4<br>.7.5                                                                  | Other improvements                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

| _   | _                                                              |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |

| 5   | Conclu                                                         | isions                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 53                                                       |

| Bil | bliograp                                                       | hy                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 55                                                       |

|     |                                                                |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |

# LIST OF FIGURES

| 1.1  | to-digital conversion and digital-to-analog conversion.                                                                                                | 1  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | The bandgap reference principle.                                                                                                                       | 2  |

| 1.3  | The key idea of a sampled voltage reference.                                                                                                           | 4  |

| 2.1  | Offset compensation techniques. From left to right: trimming, chopping and input sampled autozeroing.                                                  | 6  |

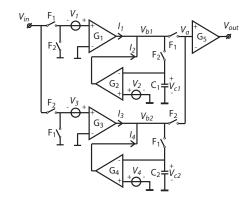

| 2.2  | A ping-pong continuous-time auto-zeroed amplifier [1].                                                                                                 | 7  |

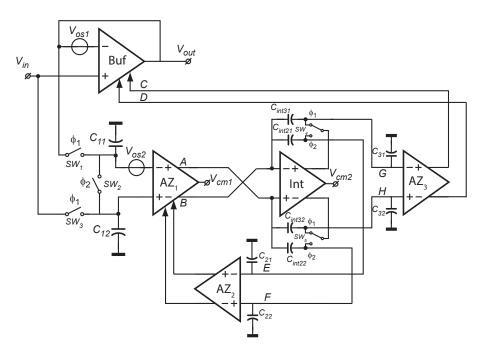

| 2.3  | A conventional continuous-time auto-zeroed buffer                                                                                                      | 7  |

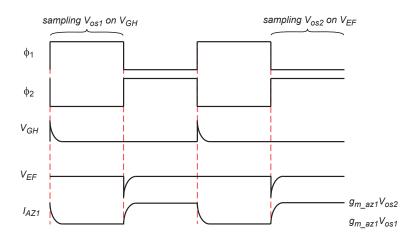

| 2.4  | A sketch of the effect of a limited bandwidth of AZ1 on the output current and the voltage on EF and GH. Drawn for the case that $V_{os2} > V_{os1}$ . | 8  |

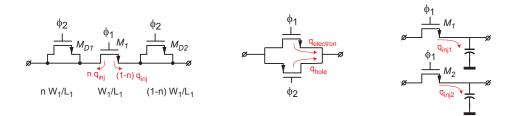

| 2.5  | From left to right: dummy switches, transmission gates and differential sampling                                                                       | 9  |

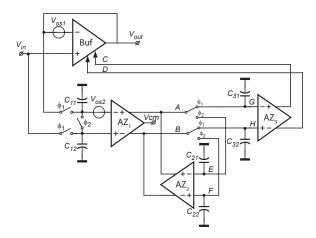

| 2.6  | A continuous-time auto-zeroed buffer with active integration.                                                                                          | 10 |

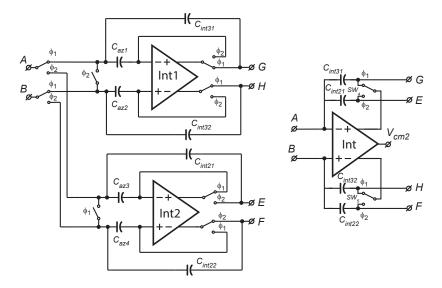

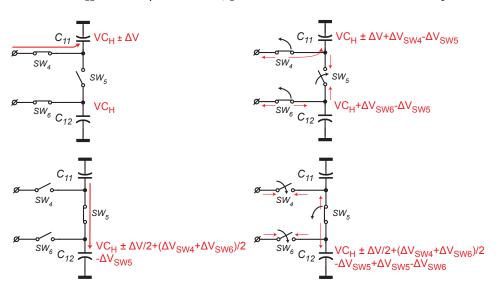

| 2.7  | The two implementations of the active integrator. On the left two auto-zeroed integrators and on the right a shared integrator.                        | 11 |

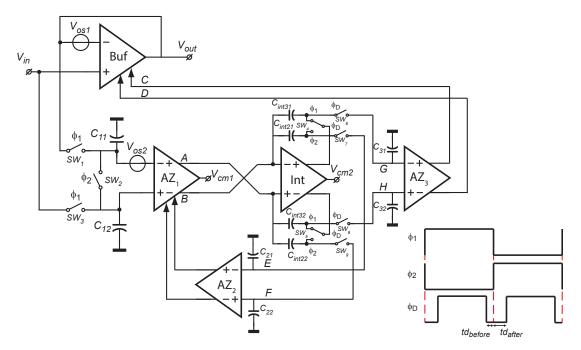

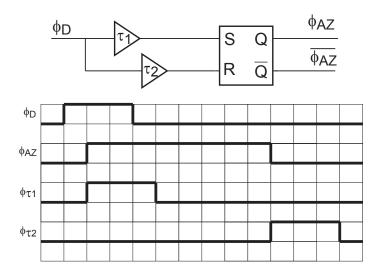

| 2.8  | A continuous-time auto-zeroed buffer with active integration and dead time with the timing of the dead time ( $\phi_d$ ) and the auto-zeroing phases   | 11 |

| 2.10 | Two options for the dead time implementation. On the left the option with two deadtime clocks and on the right with a single shared deadtime clock.    | 12 |

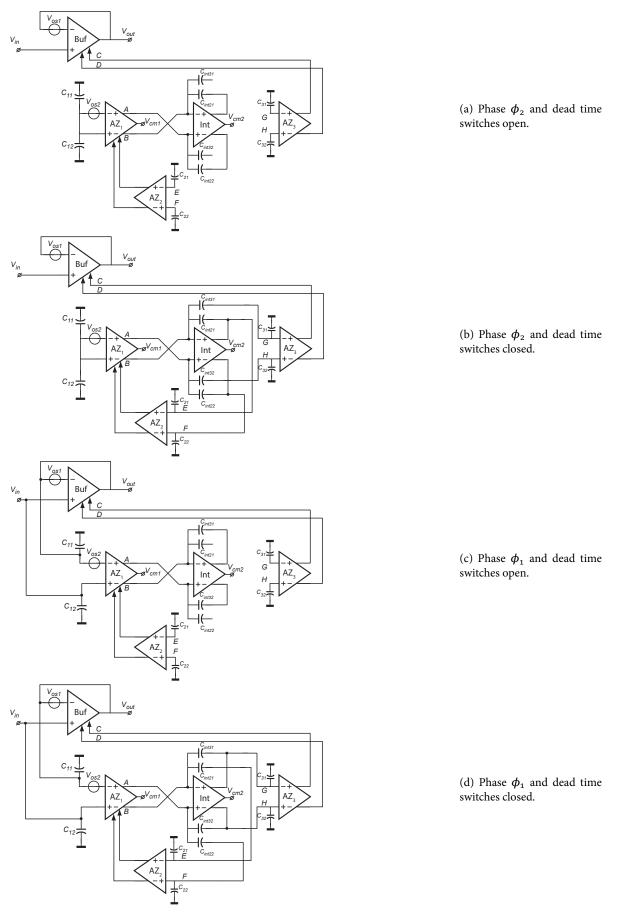

| 2.9  | The different phases that the continuous-time auto-zeroed buffer with active integration and dead time goes through.                                   | 13 |

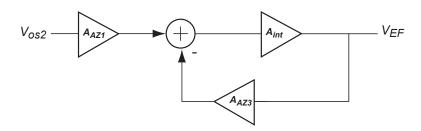

| 2.11 | The equivalent block diagram of the loop measuring Vos2.                                                                                               | 14 |

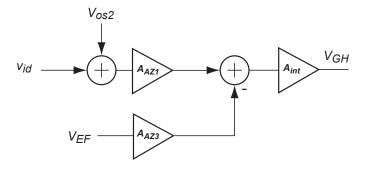

| 2.12 | The equivalent block diagram of the loop measuring Vos1.                                                                                               | 15 |

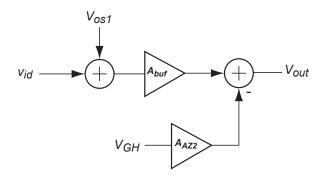

| 2.13 | The equivalent block diagram of the circuit removing the offset of the buffer                                                                          | 15 |

|      | The sinc function for a refresh frequency of 10s                                                                                                       | 17 |

|      | Noise PSD of a typical CMOS amplifier [1]                                                                                                              | 18 |

|      | Noise PSD of an auto-zeroed amplifier [1]                                                                                                              | 18 |

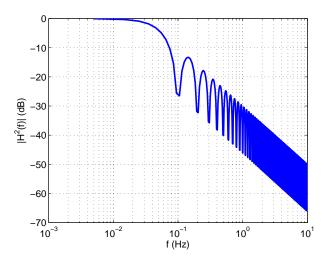

| 2.17 | The output noise spectrum of the buffer without auto-zeroing, with logarithmic y and x-axis                                                            | 19 |

| 2.18 | The output noise spectrum of the buffer with auto-zeroing at 100 kHz                                                                                   | 19 |

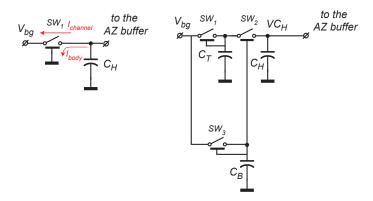

|      | On the left a normal S&H circuit and on the right the special low leakage S&H circuit.                                                                 | 20 |

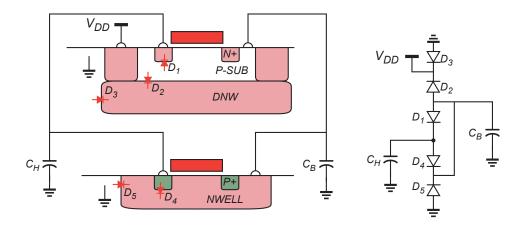

| 2.20 | The different parasitic diodes of the T-gate implementation of switch SW2 in a tripple well process                                                    | 21 |

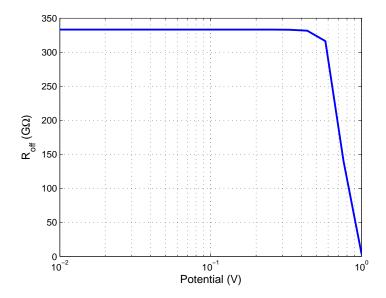

| 2.21 | The off resistance against the potential across the switch.                                                                                            | 22 |

| 2.22 |                                                                                                                                                        | 23 |

| 2.23 | Charge kickback caused by an error on the output.                                                                                                      | 24 |

| 2.24 |                                                                                                                                                        | 24 |

|      | Continuous time auto-zeroed buffer with active integration and leakage reversing slow chopping.                                                        | 25 |

| 2.26 | Simulation result of the slow chopping                                                                                                                 | 26 |

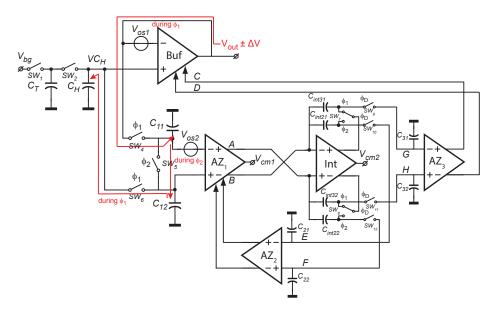

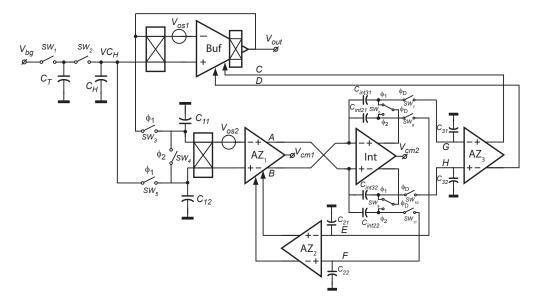

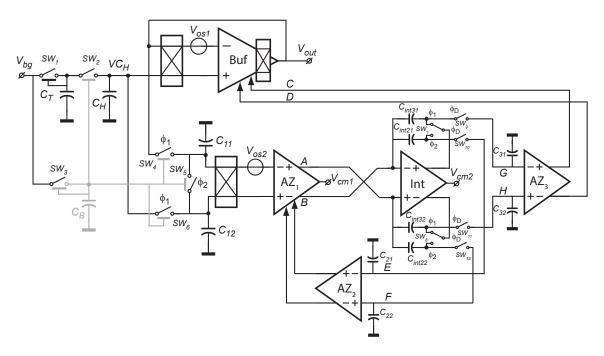

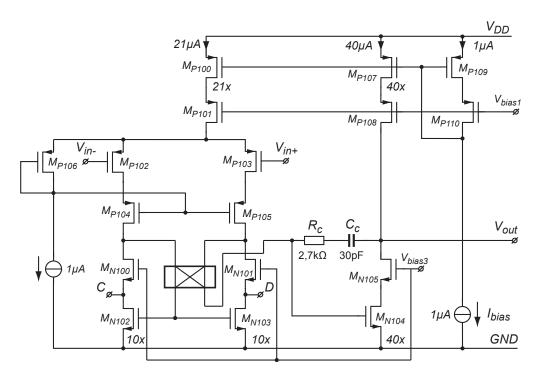

| 3.1  | The complete circuit with continuous-time auto-zeroed buffer and low-leakage sample and hold                                                           | 27 |

| 3.2  | Buffer amplifier, two stage: a telescopic amplifier and a class A output stage                                                                         | 28 |

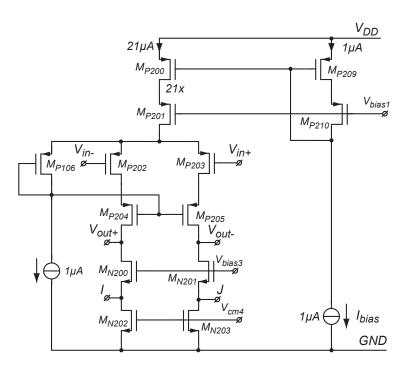

| 3.3  | The implementation of AZ1, a telescopic OTA                                                                                                            | 29 |

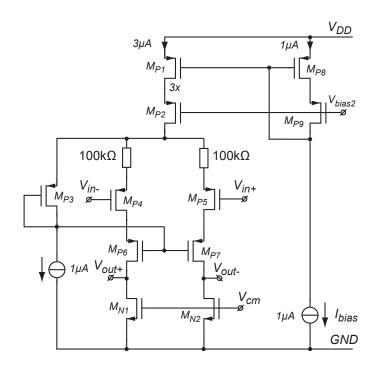

| 3.4  | The implementation of AZ2 and AZ3                                                                                                                      | 30 |

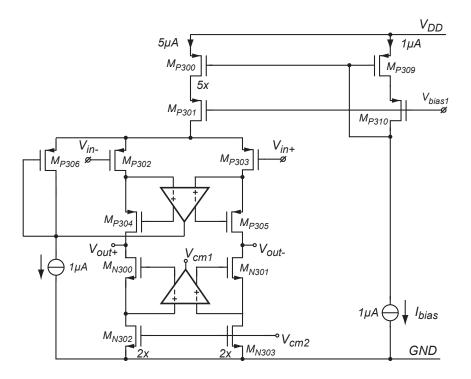

| 3.5  | The integrator implementation                                                                                                                          | 30 |

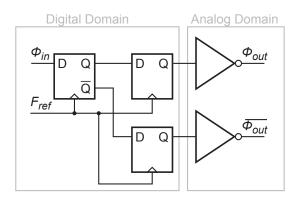

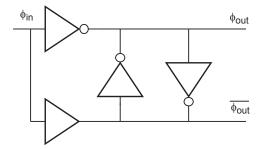

| 3.6  | The digital circuit used to generate synchronized complementary clock signals from a single-ended input clock.                                         | 31 |

| 3.7  | A block diagram of the complete digital circuit.                                                                                                       | 32 |

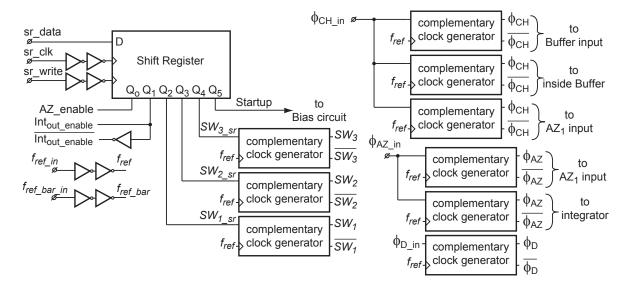

| 3.8  | A micrograph of the implemented chip                                                                                                                   | 33 |

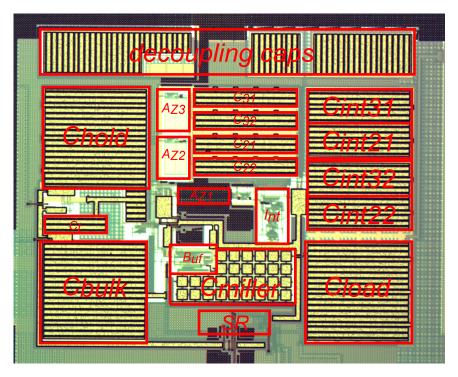

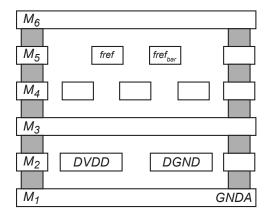

| 3.9  | Cross section of the shielded clock signals in the 6 Metal TSMC process                                                                                | 33 |

Xii List of Figures

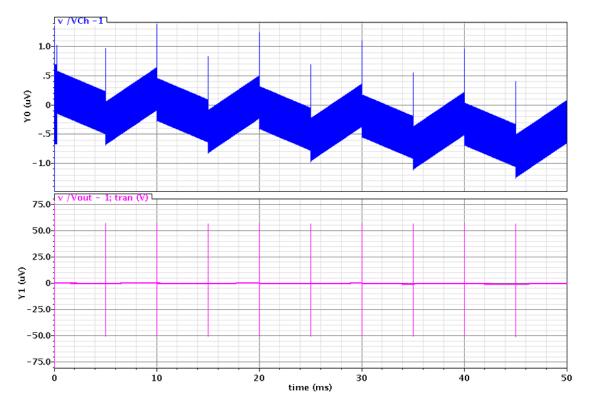

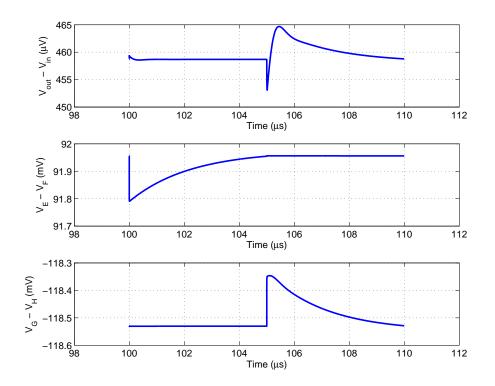

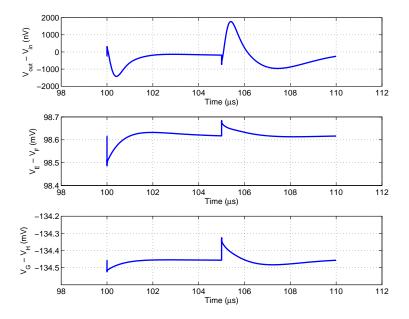

| 4.1  | The simulated switching transients and residual offset of the conventional continuous time auto-zeroed buffer. |

|------|----------------------------------------------------------------------------------------------------------------|

| 4.2  | zeroed buffer                                                                                                  |

| 1.2  | with active integration                                                                                        |

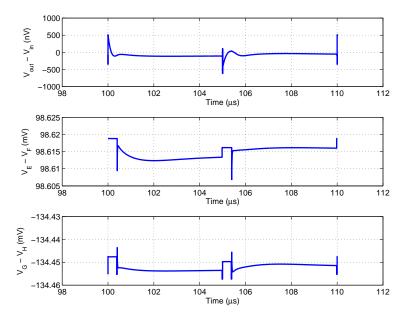

| 4.3  | The simulated switching transients and residual offset of the continuous time auto-zeroed buffer               |

|      | with active integration and dead-time.                                                                         |

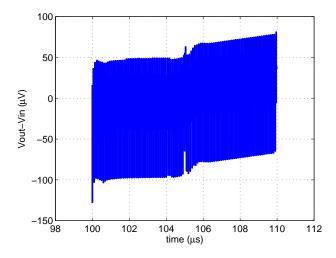

| 4.4  | The simulated switching transients and residual offset of the extracted post-layout circuit                    |

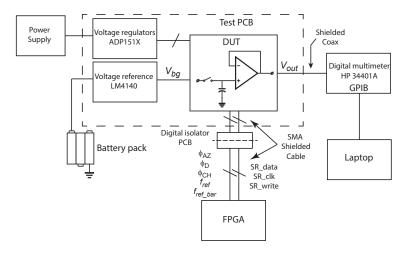

| 4.5  | A block diagram of the measurement setup.                                                                      |

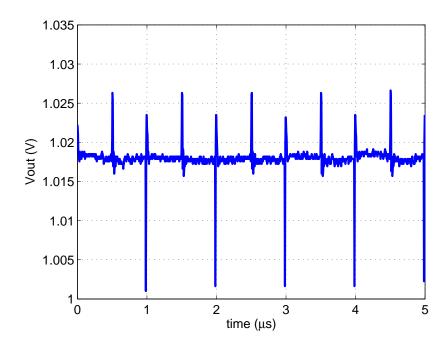

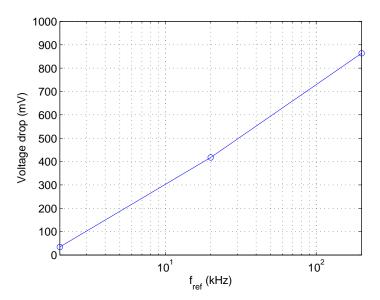

| 4.6  | The measured effect of the reference frequency on the output of the buffer                                     |

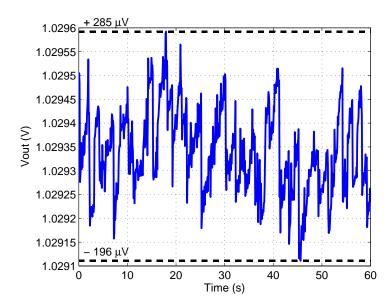

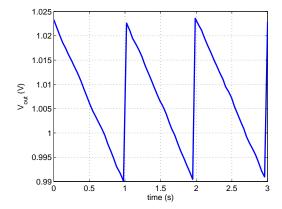

| 4.7  | Leakage measurement without auto-zeroing, with a refresh period of 1s                                          |

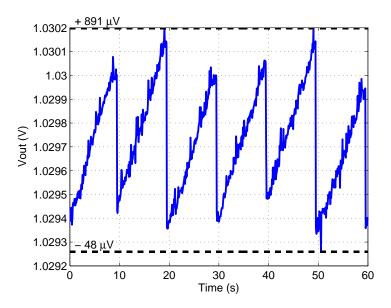

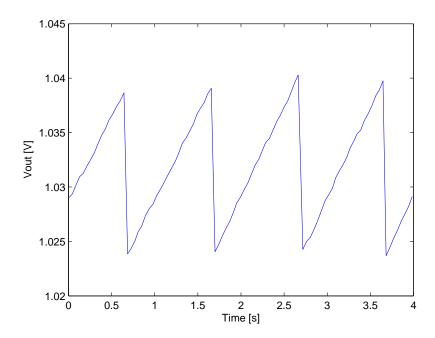

| 4.8  | Leakage measurement without auto-zeroing, with a refresh period of 10s                                         |

| 4.9  | Leakage measurement without auto-zeroing, with a refresh period of 10s and the body capacitor                  |

|      | voltage set at 0.9 V                                                                                           |

| 4.10 | Leakage measurement without auto-zeroing, with a refresh period of 20s and the body capacitor                  |

|      | voltage set at 0.9 V                                                                                           |

| 4.11 | A simulation of the leakage for the pre-layout circuit.                                                        |

|      | A simulation of the leakage for the post-layout circuit                                                        |

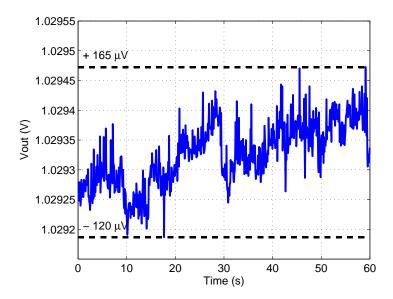

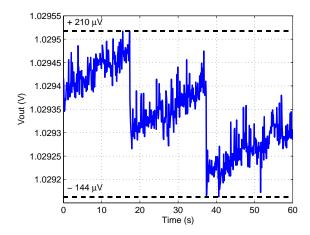

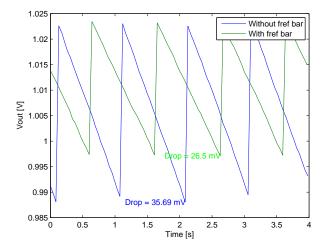

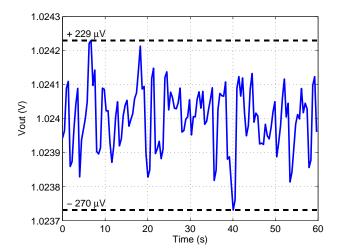

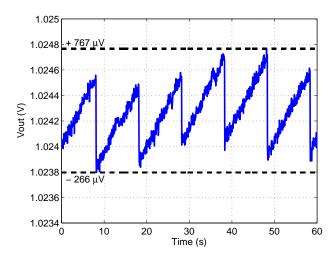

|      | Leakage measurement with auto-zeroing with a frequency of 2 kHz and a refresh period of 1 s                    |

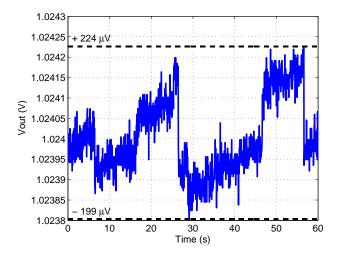

| 4.14 | Leakage measurement with auto-zeroing with a frequency of 2 kHz, with a refresh period of 1 s                  |

|      | and with $fref_{bar}$ .                                                                                        |

| 4.15 | Leakage measurement with auto-zeroing with a frequency of 2 kHz, with a refresh period of 1 s                  |

|      | and with capacitive loading of $fref_{bar}$                                                                    |

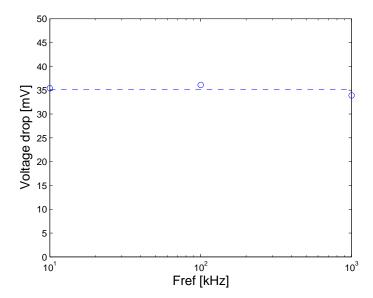

|      | Leakage measurement for different reference frequencies                                                        |

|      | Leakage measurement for different auto-zeroing frequencies                                                     |

|      | The implementation of the SR-latch                                                                             |

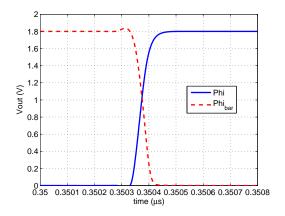

|      | Phi and Phi <sub>bar</sub> generated by the complementary clock generator.                                     |

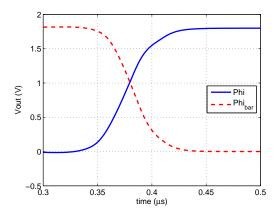

| 4.20 | Phi and Phi <sub>bar</sub> generated by the SR-latch                                                           |

|      | Deriving the auto-zero clock from the dead-time clock                                                          |

|      | The output noise spectrum of the improved buffer without auto-zeroing                                          |

| 4.23 |                                                                                                                |

|      | Leakage measurement for auto-zeroing just during the charge time, with a 1s hold time.                         |

|      | Leakage measurement for auto-zeroing just during the charge time, with a 10s hold time.                        |

|      | Leakage measurement for auto-zeroing just during the charge time, with a 10s hold time and VCb                 |

|      | = Vdd/2                                                                                                        |

# Introduction

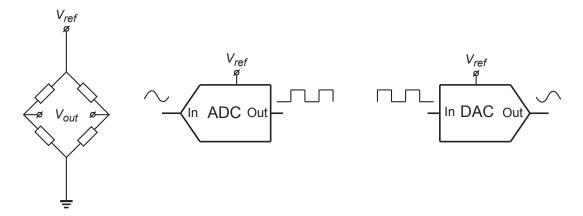

The voltage reference is a commonly used building block in many analog and mixed-signal systems. In a measurement system, the voltage reference provides the standard against which other voltage measurements are referred. To be useful, the reference voltage should be insensitive to environmental variations such as: temperature, supply voltage and time. The application of voltage references include: sensor conditioning, analog-to-digital conversion (ADC) and digital-to-analog conversion (DAC), as shown in Figure 1.1.

Figure 1.1: Some typical applications for a voltage reference. From left to right: sensor conditioning, analog-to-digital conversion and digital-to-analog conversion.

For these applications some key parameters for the voltage reference have been determined:

- Initial accuracy

- Temperature coefficient

- Noise

- · Long-term drift

- Power supply rejection ratio

1. Introduction

## 1.1. LITERATURE/HISTORY

Voltage references have been around for a long time. The first voltage references were the Clark cell and Weston cell developed in the 19th century [2]. These bulky electrochemical cells where mostly used as laboratory standards.

The first semiconductor voltage reference was the zener diode introduced in the late 1950s [3]. The zener reference behaves like a non-linear divider. It works by reverse biasing a PN junction until it reaches the breakdown voltage where the voltage over the junction changes very little with supply current. The breakdown effect is due to two different effects namely: the avalanche effect and the zener effect. The avalanche effect gives a negative temperature coefficient while the zener effect gives a positive temperature coefficient. The residual temperature coefficient of a Zener diode is slightly positive. This positive temperature coefficient can be combined with the negative temperature coefficient of a forward biased diode, to create a temperature compensated Zener diode. In the 1970's [4, 5] zener diodes were placed deeper in the silicon, to get rid of the 1/f noise which is mostly a surface effect.

Even though buried zener references with superior temperature coefficient (0.05 ppm/°C using temperature stabilization) and long term-stability  $(2\mu V/\sqrt{kHr})$  are around [6], they are no longer widely used due to their high supply voltage requirement (>7V) and large current consumption.

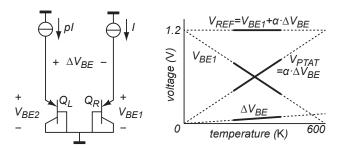

Figure 1.2: The bandgap reference principle.

In 1964 [7] a new principle was introduced by Hilbiber to create a stable voltage reference, this principle is refered to as the bandgap principle. In the bandgap principle, shown in Figure 1.2, two voltages with different temperature coefficients are combined to get a temperature independent output. Most commonly the base-emitter voltage ( $V_{BE}$ ) is used which has a negative temperature coefficient (CTAT), combined with the difference between two base-emitter voltage ( $\Delta V_{BE}$ ) which has a positive temperature coefficient (PTAT). After the introduction by Hilbiber, several circuits have been published that use this principle to create a reference voltage [8–10].

The first bandgap references were first-order temperature compensated, higher-order effects give rise to residual temperature dependency. This results in a typical temperature coefficient of around 0.1 %/°C. To get rid of second-order effects, second-order compensation was introduced [11, 12]. This improves the temperature coefficient by an order of magnitude, to typical values of around 50 ppm/°C. Using two-point trimming [13], the temperature coefficient can be lowered to typical values of 3 ppm/°C. A bandgap reference typically contains a CMOS opamp to combine  $V_{BE}$  with a scaled  $\Delta V_{BE}$ . The spread of  $V_{BE}$  is mainly PTAT, while the offset of a CMOS opamp typically has a non-PTAT temperature drift. Therefore, a single-point trim cannot compensate for both. Using chopping to minimize the offset of the opamp, the temperature coefficient can be below 10 ppm/°C with a one-point trim [14].

## 1.2. STATE-OF-THE-ART / RECENT TECHNIQUES

With the increasing trend towards lower supply voltage and low-power applications. In recent years many publications have been written about bandgap references with an output below the usual 1.2~V~[15,16] and nW-power bandgap references [17,18]. Both of these nW-power bandgap references achieve low power by reducing the current used in the bandgap core. Although not confirmed by published results, this will come at the cost of increased noise.

1.3. MOTIVATION 3

Another approach [19, 20] to getting low-power bandgap references is by using a sampled bandgap reference, to reduce the average required current. By holding the reference voltage created by a bandgap reference on a capacitor, the bandgap core can be switched off, reducing the average required current. The key to getting low power is reducing the leakage to get a long hold time. [20] aims to achieve a long hold time by measuring the leakage of a small capacitor (50 fF) and using this to reduce the leakage of a large hold capacitor. The hold time is dynamically changed, based on the measured voltage droop. This is shown to be effective with an average power consumption of 2.98 nW at room temperature. However, the allowed voltage droop is rather large with 100  $\mu V$ . Furthermore, the hold time drops dramatically for higher temperatures (100 s at 40 °C, 10 s for 50 °C and 0.5 s for 80 °C), which also dramatically increases the average required power. [19] aims to achieve a long hold time by using a buffered hold capacitor voltage to reduce the leakage of the critical junctions. It is shown to be effective with an average power of 170 nW. The hold time is rather low with 100 ms and no mention is made of the voltage droop. Large output transients of 20 mV peak-to-peak also occur during the charging of the hold capacitor. Low noise is claimed, but no data is supplied to support this claim. Without chopping and auto-zeroing, the noise will be limited by the buffer. [21] combines a power-efficient ADC with a low-power reference. The reference only consumes 25 nW and this can be reduced to 2.5 nW by using duty-cycling. The duty-cycling is done with a cascade of three sample-and-hold stages, where each stage lowers the voltage across the switch and reduces the leakage. A duty-cycle of 10% is achieved, with a maximum ripple of 100  $\mu$ V and no performance loss in the ADC.

## 1.3. MOTIVATION

The design of a voltage reference is, just like the design of other analog circuits, a trade-off between different design parameters. The initial accuracy is a reflection on the sensitivity to process variation. Voltage references with very high initial accuracy require special circuit techniques such as dynamic element matching and costly trimming techniques. References with very low temperature coefficients require second-order curvature compensation. Low noise usually comes at the cost of increased power consumption. While references with a low power consumption usually have degraded initial accuracy, temperature coefficient and noise performance.

For these reasons, commercially available low-power voltage references, such as the LT6656 shown in table 1.1, usually have relatively high noise and poorer temperature coefficients. While the really accurate and low-noise voltage references, such as the LTC6655, are relatively power hungry.

|                              | LTC6655 [22] | MAX6126 [23] | LM4140 [24] | LT6656 [25] | X60008 [26]   |

|------------------------------|--------------|--------------|-------------|-------------|---------------|

| Initial accuracy (Max %)     | 0.025        | 0.02         | 0.1         | 0.05        | 0.01          |

| Noise peak-to-peak 0,1 to 10 | 0.25         | 0.63         | 2.15        | 30          | 6             |

| Hz (ppm)                     |              |              |             |             |               |

| Temp co. (ppm/°C)            | 2            | 3            | 3           | 10          | 1             |

| Supply current (Typ $\mu$ A) | 5000         | 380          | 375         | 0.85        | 0.5           |

| Technique                    | Bandgap      | Bandgap      | Bandgap     | Bandgap     | Floating gate |

Table 1.1: Several commercially available voltage references compared, ordered from high to low supply current.

A voltage reference that seems to break this trend is the X60008. This reference has the lowest current consumption of all the parts in Table 1.1 and at the same time achieves the lowest initial accuracy and lowest temperature coefficient. The peak-to-peak noise is higher than most of the other references, but it is still five times better than that of the second lowest power reference, the LT6656. The X60008 voltage reference is based on the floating-gate voltage reference developed by Xicor/Intersil in 2005 [27]. They produced a very low leakage capacitor by using a technology similar to the one used for EEPROM digital memory. They then pre-charged this very low leakage capacitor to a precise reference voltage and used a standard buffer to drive a load. References based on this technology are able to achieve a very low power consumption but the noise performance is still significantly higher than other low noise voltage references.

## 1.4. KEY IDEA

The key idea of this work is to make a voltage reference by storing a reference voltage on a hold capacitor. This hold capacitor is then buffered so that it can supply current to a load without draining the hold capacitor. This approach is similar to the one used in the X60008. However, the goal of this work is to realize a reference in a

4 1. Introduction

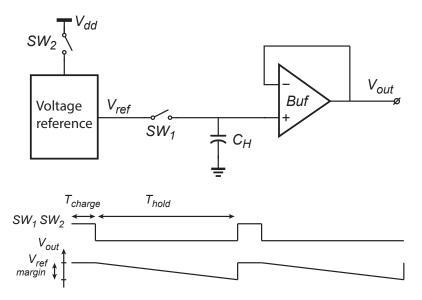

standard CMOS technology, in this case the TSMC  $0.18~\mu m$  1.8V technology. This obviates the need for an exotic ultra-low-leakage High Voltage technology and results in a voltage reference that is generally applicable, also as a part of a system-on-a-chip (SoC). A standard CMOS technology does not allow for a very low leakage capacitor, such as the one used in the Intersil/Xicor product. Therefore a normal leaky capacitor is used, which is recharged periodically to keep the output reference voltage within a certain margin from the desired value. This creates a sampled voltage reference, shown in Figure 1.3.

Figure 1.3: The key idea of a sampled voltage reference.

Keeping the reference voltage stored on a hold capacitor with a long hold time, has two advantages. First, once the hold capacitor is charged to the reference voltage, the voltage reference can be switched off. In this way the average power required by the sampled voltage reference can be lowered.

The average power  $(P_{avg})$  required by the sampled voltage reference, is given by:

$$P_{avg} = dP_{Ref} + P_{Buf} = \frac{T_{charge}}{T_{charge} + T_{hold}} P_{Ref} + P_{Buf}. \tag{1.1}$$

Where d is the duty cycle,  $P_{Ref}$  is the power consumed by the reference and the buffer of the and  $P_{buf}$  the power of the buffer. To benefit from the lower average power consumption, the power consumed by the buffer should be considerably lower than the power consumed by the voltage reference. Furthermore the capacitor should be charged by the reference quickly and the capacitor should hold the voltage for a long time. All to get a low duty cycle, which will reduce the average power consumption.

The second advantage is that the sampling action will shape the noise. All the noise of the voltage reference will be pushed down into a frequency band below the refresh frequency. The system effectively behaves like a switched capacitor filter with a very large time constant. Key to getting the low-noise from the reference is in making the leakage low enough so that the refresh frequency can be low, while the leakage induced error is small enough. During the hold period the only noise present on the output is due to the buffer amplifier. By using dynamic offset compensation techniques this noise can be made very low without using a large amount of power.

Ultimately this should lead to a very precise voltage reference that achieves low noise while at the same time having a very low power consumption. In this thesis the focus is on the design of a low-leakage sample and hold circuit and an offset compensated buffer.

This chapter presents the system level design of the sampled voltage reference. First the design of the offset compensated buffer is presented. Of the different offset compensation techniques, the most appropriate for this application is chosen. Specifications for the buffer are determined, based on a commercially available high performance voltage reference. Next techniques are described to achieve low switching transients and low residual offset. The noise is analyzed for a sampled reference, followed by the design of the low-leakage sample and hold circuit.

Ideally the buffer should provide an exact copy of the reference voltage stored on the capacitor. However, several non-idealities of the buffer work against this. The design challenge is then to keep these non-idealities as small as possible.

Challenges of the buffer design:

- · Low offset and low offset drift

- Low unity-gain error

- Low noise

- Small switching transients

- Low influence on the hold capacitor.

## 2.1. Offset and offset drift cancellation

The buffer should have a low offset and a low offset drift over temperature and time. Any offset will deteriorate the initial accuracy of the reference and any offset drift with temperature will degrade the temperature coefficient of the voltage reference. Finally, any offset drift over time will influence the reference's long-term stability. In CMOS technology an offset of around 1-10 mV is not uncommon [28]. Careful layout and large input transistors can only help to reduce the offset to the millivolt level. However, commercially-available high performance bandgap references, have initial accuracies of  $\pm 0.025$  % and temperature coefficients of 2 ppm/°C [22]. For a reference with a nominal output voltage of 1.250 V this translate into an initial accuracy of  $\pm 312.5~\mu V$  and a temperature coefficient of  $2.5~\mu V$ /°C over a temperature range of -40 to 125 °C. To keep the buffer from negatively influencing the performance of a high performance reference, its offset and offset drift over temperature should at least be of the same order or preferably an order of magnitude better. Therefore a way to reduce the offset and the offset drift from the normal mV-level is desirable, to keep the performance of the overall system similar to a high performance bandgap reference.

## **2.1.1. Trimming**

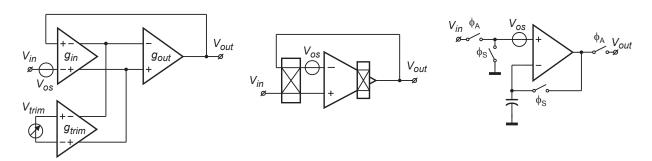

To reduce the offset, two basic techniques can be distinguished namely: static offset reduction and dynamic offset reduction. Static offset reduction, or trimming, works by driving an extra set of inputs with a trimming voltage that compensates for the current generated by the offset voltage, as shown in Figure 2.1. Trimming can easily

reduce the offset to below 312.5  $\mu$ V but it only effectively compensates for offset drift in bipolar devices and is less effective in the case of MOS devices. To get an offset drift below 2.5  $\mu$ V/°C, two point trimming or special circuit techniques together with a one-point trim are necessary [29]. Furthermore, trimming does not reduce 1/f noise and is costly to use, due to the increased production time. In a system combining buffer and bandgap reference, trimming only needs to be done in the bandgap, removing the extra burden of trimming the buffer. Dynamic offset compensation techniques include chopping and auto-zeroing. These techniques use additional circuitry that continually works to reduce the offset. Therefore any slow changes in the offset and noise will also be compensated for.

Figure 2.1: Offset compensation techniques. From left to right: trimming, chopping and input sampled auto-zeroing.

#### 2.1.2. CHOPPING

Chopping can reduce the offset by using two pairs of polarity-reversing switches or choppers. The input chopper modulates the input signal away from DC. An output chopper can then demodulate the signal back to DC, while the offset and 1/f noise is modulated to the chopping frequency and can in principle be filtered out. The modulated offset will be a triangular waveform after being integrated by the output stage, this will result in a triangular ripple on the output. Furthermore the act of chopping at the input introduces spikes which, due to the limited bandwidth of the amplifier and the demodulation at the output, have a residual DC component. For chopper amplifiers, residual offsets of  $\pm 10~\mu Vs$  and ripples with amplitudes of 10~mVs are not uncommon [30], for a voltage reference buffer the offset is acceptable but the ripple is undesirably high. Several techniques exist to reduce the ripple caused by the offset and the spikes. The techniques include nested chopping [31], chopper stabilized amplifiers, ripple reduction loops and switched capacitor notch filters. These techniques can reduce the offset to 100~nVs but the ripple is still in the  $10~\mu Vs$  range [30].

## 2.1.3. Auto-zeroing

Auto-zeroing is based on the sampling of the offset in one phase ( $\phi_s$ ) and compensating the offset in the other phase ( $\phi_A$ ). The simplest forms of auto-zeroing are discrete time based, such as the circuit shown in Figure 2.1. For a generally applicable voltage reference a continuous-time solution is required, since most applications require the output to be continuously available. The advantage of auto-zeroing is that it doesn't use modulation to get rid of the offset, so it also doesn't suffer from the ripple associated with the modulation. Of course there is still some switching involved and therefore spikes still occur at the output. Furthermore, the sampling action of auto-zeroing leads to noise fold-back, which makes it harder to make a low-noise auto-zeroed buffer. So for a sampled voltage reference we have to find ways to realize continuous-time auto-zeroing, while avoiding excessive noise fold back.

#### **2.1.4.** REDUCING THE UNITY-GAIN ERROR

The buffer should have a low unity-gain error. Therefore the buffer should have a large open-loop gain. Any unity-gain error will reduce the initial accuracy of the reference.

## 2.1.5. CONCLUSION

In conclusion, for a voltage reference buffer, two offset reduction techniques are suitable namely: trimming and auto-zeroing. Trimming is more costly to use, unless it is combined with the trimming of the bandgap. It doesn't benefit from the lower 1/f noise achieved by dynamic offset compensation and thus requires more power to achieve low noise. The big advantage is that no switching is involved and therefore no spikes will occur at the output and, as will be discussed later, the buffer's input current will be essentially zero. The second candidate is auto-zeroing which can achieve low residual offset, low noise and at the same time low power. Therefore for

a buffer with low residual offset, low noise, small switching transients and low power, an auto-zeroed buffer is probably the best choice.

## 2.1.6. Specifications

$\begin{array}{lll} \text{Switching transients} & \leq 1 \, \mu \text{Vpp} \\ \text{Offset} & \leq 300 \, \mu \text{V} \\ \text{Offset drift} & \leq 2.5 \, \mu \text{V/}^{\circ}\text{C} \\ \text{Noise (0.1 to 10 Hz)} & \leq 500 \, n \text{Vrms} \\ \text{Power} & \text{as low as possible} \\ \end{array}$

Table 2.1: The specifications of the auto-zeroed buffer.

## 2.2. A CONTINUOUS-TIME AUTO-ZEROED BUFFER

Now that it has been established that an auto-zeroed buffer is the best option. Next it is time to look at how a continuous-time auto-zeroed amplifier can be created. For general voltage reference applications, a continuously available output voltage is desirable. Several topologies exist for continuous-time auto-zeroed amplifiers. The first is based on using two auto-zeroed amplifiers in a ping-pong technique [32], as shown in Figure 2.2. While one of the amplifiers is being auto-zeroed, the other can amplify the signal. The second continuous-time auto-zeroed amplifier is commonly referred to as an auto-zero offset-stabilized amplifier [1]. In this auto-zeroing technique, the buffer stays in the signal path, making it suitable for continuous time applications. The offset of the buffer is removed by a loop, that switches between nulling the offset of the loop itself and nulling the offset of the buffer. Since the ping-pong technique relies on interchanging the two amplifiers, which causes spikes [28], the offset-stabilized architecture is preferred.

Figure 2.2: A ping-pong continuous-time auto-zeroed amplifier [1].

Figure 2.3: A conventional continuous-time auto-zeroed buffer.

In Figure 2.3 a conventional continuous-time auto-zeroed buffer is shown. The buffer has an offset  $V_{os1}$  which has to be removed. To remove this offset a compensation loop is created by the operational transconductance amplifiers (OTA's) AZ1, AZ2 and AZ3. This loop measures the offset of the buffer, stores it on capacitor  $C_{31}$  and  $C_{32}$  and compensates for it. To measure the offset of the buffer, first, the offset of the sensing OTA AZ1 has to be removed. In the next phase this basically offset-less AZ1 can sense the offset of the buffer and compensate for it. These two actions leads to two different phases. Phase  $\phi_2$ , in which the offset of AZ1 is measured and stored by AZ1 and AZ3. Phase  $\phi_1$ , in which the offset of the buffer is measured and stored. Both phases will be analyzed separately.

For the auto-zeroing loop a differential structure is preferred, above a single-ended structure. This is because the charge injection of two switches will than partially cancel and we only have to deal with their charge-injection mismatch.

## 2.3. SWITCHING TRANSIENTS

In the conventional continuous-time auto-zeroing approach shown in Figure 2.3, switching transients occur during the transition from the sampling of the buffer offset ( $V_{OS1}$ ) to the sampling of the AZ1 offset ( $V_{OS2}$ ) and vice versa. Some of the transients are due to the limited bandwidth of the OTA's, while some are due to the non-idealities of the switches connected at the input and output of AZ1. These two contributions can be minimized separately. Since output transients are generally undesirable for voltage reference applications and due to the relatively high auto-zeroing frequency required to get rid-off the 1/f noise (explained in section 2.5), an effort is done to keep them below 1  $\mu$ V.

The dominant source of the output switching transients is due to the limited bandwidth of the OTA's. Therefore this effect is first studied and several techniques are investigated to reduce the transients.

#### Switching transients due to limited bandwidth

In the auto-zeroed buffer shown in Figure 2.3, the output current of AZ1 ( $I_{AZ1}$ ) needs to switch between  $g_{m\_AZ1}V_{os1}$  and  $g_{m\_AZ1}V_{os2}$ . Where  $g_{m\_AZ1}$  is the transconductance of AZ1. Due to the finite bandwidth of AZ1, the transition between these two current levels will take some time, as shown in Figure 2.4. This settling behavior from one output current level to the next will introduce spikes on the nodes GH and EF. Since the voltage on nodes GH directly influence the output, spikes on GH will also be present on the output. The spikes on GH will be attenuated by the ratio of the AZ3 and buffer gain,  $\alpha_1 = \frac{A_{AZ3}}{A_{Buf}} = 30$ , which will be explained in more detail in Section 2.4. This means that for switching transients below 1  $\mu$ V peak-to-peak, the switching transients at GH should be below 30  $\mu$ V.

Figure 2.4: A sketch of the effect of a limited bandwidth of AZ1 on the output current and the voltage on EF and GH. Drawn for the case that  $V_{os2} > V_{os1}$ .

2.3. SWITCHING TRANSIENTS 9

The spikes in Figure 2.4 can be minimized by keeping the offset level of AZ1 and the buffer small and hence close to each other. This can be done by careful layout of the input transistors of AZ1 and the buffer. Furthermore the parasitic capacitance at the output of AZ1 can be minimized, which translates in to a high bandwidth of AZ1. However, these measures alone will not reduce the output switching transients below 1  $\mu$ V peak-to-peak. In the next two sections, techniques will be introduced to further lower these transients.

#### Switching transients due to switching non-idealities

Besides the transients due to the limited bandwidth of AZ1, some of the transients are due to the non-idealities of the switches. In CMOS switches, there are two non-ideal effects that cause transients, namely: charge injection and clock feedthrough. During the on-state of a MOS switch, a channel exists between the source and drain. During the transition to the off-state, this charge escapes the channel to the source, drain and bulk. The total charge in the channel can be expressed as:

$$Q = WLC_{ox}(V_{qs} - V_{th}). (2.1)$$

A first obvious way to minimize the charge injection is to take minimum size transistors as switches. This can be done since speed is not important in this design. A second way would be to minimize the effective gate-source voltage  $(V_{gs} - V_{th})$ .

Besides charge injection, clock feedthrough also creates switching transients. Due to a slight overlap capacitance between gate-drain and gate-source will lead to capacitive coupling of the clock signal. This parasitic capacitance will couple any transition on the gate to the source and drain.

Three well-known techniques exist to minimize the above described effects, shown in Figure 2.5. These techniques are: dummy switches, transmission gates and differential sampling.

Figure 2.5: From left to right: dummy switches, transmission gates and differential sampling.

The use of dummy switches assumes that a predictable fraction of the channel charge will flow to the source and drain. The source and drain then have dummy switches that are sized according to this fraction and switch with the complementary clock. In theory, the charge needed to build the channel in these dummy switches will compensate for the charge of the original switch. In practice the charge injection depends on the impedance seen by the drain and source and the clock rise and fall time [33, 34]. This makes it difficult to predict the precise behavior of the charge, making it hard to implement a proper compensation.

The use of transmission gates relies on the cancellation of the holes injected by a PMOS and the electrons injected by a NMOS. These two charge contributions will only cancel for one precise input voltage. Furthermore the overlap capacitance of a PMOS and a NMOS will generally not match. Previous implementations with dummy switches and transmission gates, seem to favor transmission gates slight above dummy switches [35]. Simulations done on the two compensations schemes give the same result. Furthermore, with overlapping clocks the instantaneous injection of the PMOS and NMOS can cancel before affecting the output. This instantaneous cancellation depends on the simultaneity of the switching of the PMOS and NMOS. Any skew between the clock driving the PMOS and NMOS will reduce the effectiveness of this technique [36].

The final approach is differential sampling. This relies on the fact that the signal can be stored as a differential

voltage on two capacitors and that the charge injection of two transistors into these capacitors is roughly similar. The charge injection transient will therefor occur as a common-mode step on both capacitors. A small differential transient will remain due to the charge injection mismatch of the two switches, which is much smaller than the charge injection of a single switch.

Since the switches in front of AZ1 are directly connected to the output they will directly create transients. If the switches go from on to off, charge needs to go from the channel to a low impedance node. This will lead to a temporarily increased output, which will slowly be corrected by the buffer. If the switches go from off to on, charge will be needed to fill the channel. This will lead to a temporarily decreased output, which will slowly be corrected by the buffer. These switches are necessary for the auto-zeroing operation. To measure the offset of AZ1, the input of AZ1 has to be shorted in phase  $\phi_2$ . Therefore the transients due to these switches can only be minimized and not circumvented. These switches are implemented with transmission gates to minimize the charge injection.

The goal of the design is to keep switching transients below 1  $\mu$ V peak-to-peak. Several techniques are used to achieve this, which are explained in the rest of this paragraph.

## 2.3.1. ACTIVE INTEGRATION

Figure 2.6: A continuous-time auto-zeroed buffer with active integration.

The previous section explained how the limited bandwidth of AZ1 can create output transients. To reduce these transients, the circuit shown in Figure 2.6 may be used. This incorporates an active integrator rather than a passive one. The output current of AZ1 is now steered into a virtual ground. Any transients on this virtual ground will be actively suppressed by the integrator. This results in the transients now being fully determined by the step response of the integrator. Since AZ1 is basically a copy of the buffer to keep the offset and noise contributions about the same, the focus is then on the design of a fast integrator.

The active integrator is present in both phase  $\phi_1$  and  $\phi_2$  of the offset nulling loop. The DC-gain added by the integrator will therefore help to reduce the residual offset, both due to the offset of AZ1 and the buffer. For the implementation of the active integration two options were investigated, shown in Figure 2.7. The first option is to use two integrators, one for each auto-zeroing phase. However, both integrators have to be auto-zeroed, to minimize the mismatch in offset between the two integrators. The second option shares one active integrator for both phases. In a single integrator implementation, the offset of the integrator is sampled in phase  $\phi_2$  together

2.3. SWITCHING TRANSIENTS 11

with the offset of AZ1 and the same offset is compensated for in phase  $\phi_1$ . This omits the need of an auto-zeroed integrator, while at the same time being more power efficient.

Figure 2.7: The two implementations of the active integrator. On the left two auto-zeroed integrators and on the right a shared integrator.

## **2.3.2. DEAD TIME**

The active integration introduced in the previous section still has limited bandwidth and therefore will only be able to partially reduce the transients. To further mitigate the effect of the limited bandwidth of the integrator, a special clocking scheme is used shown in Figure 2.8, similar to the one used in [37].

Figure 2.8: A continuous-time auto-zeroed buffer with active integration and dead time with the timing of the dead time ( $\phi_d$ ) and the auto-zeroing phases.

As shown in Figure 2.8, an extra clock is introduced  $(\phi_D)$  besides the regular auto-zeroing clocks  $(\phi_1 \text{ and } \phi_2)$ . This extra clock is referred to as the dead time clock. The dead time clock has a dead band around the auto-zeroing moments. This clock signal controls four switches  $(SW_6, SW_7, SW_8 \text{ and } SW_9)$  around the active integrator, shown

in Figure 2.8. These switches open a little time before  $(td_{before})$  the auto-zero switching moment and close a little time after the auto-zeroing switch moment  $(td_{after})$ . This results in four different phases that the auto-zeroing circuit goes through, which are shown in Figure 2.9.

Due to the fact that the potentials at nodes GH and EF are continuously held by capacitors  $C_{31}$ ,  $C_{32}$ ,  $C_{21}$  and  $C_{22}$ , the output of the integrator can settle to almost the correct value during the time that the dead-time switches are open. A sufficient large  $td_{after}$ , allows the integrator to settle to the right value and then reconnect the integrator output to the appropriate node, either EF or GH. This circumvents the direct propagation of the transients due to the settling behavior of the integrator.

Figure 2.10: Two options for the dead time implementation. On the left the option with two deadtime clocks and on the right with a single shared deadtime clock.

Two options for the dead time were investigated, as shown in Figure 2.10. The first option is to have a deadtime clock for each auto-zeroing phase. Since during phase  $\phi_2$  capacitors  $C_{31}$  and  $C_{32}$  are not refreshed, they are simply left disconnected from the integrator during this phase. The second option is to have one shared deadtime clock for both phases. During phase  $\phi_2$  capacitors  $C_{31}$  and  $C_{32}$  are now reconnected to the integration capacitors during phase  $\phi_2$  even though they are not recharged. This increases the switching activity and the number of spikes appearing at the output, but since these spikes are attenuated by a factor 30, this is not a real problem. The advantage of the single dead time, is that it lowers the complexity of the clock generation circuitry. Therefore the option of one shared deadtime clock was picked for the final implementation.

Even though more switches are required by the introduction of a dead time, this will not lead to an increased charge injection. The charge injection due to the switches controlled by  $\phi_1$  and  $\phi_2$  will not propagate to the output due to the dead time. The remaining charge injection is due to the charge injection mismatch of the deadtime switches.

## 2.3.3. Source degeneration

For the OTA's AZ2 and AZ3 source degeneration is used. This increases the input voltage range over which the transconductance of AZ2 and AZ3 behave linearly and decreases their transconductance. Therefore large voltage spikes at the input of AZ2 and AZ3 will lead to smaller spikes in the output current domain. This will help to reduce the output spikes due to the spikes at GH and help to improve the settling behaviour.

Figure 2.9: The different phases that the continuous-time auto-zeroed buffer with active integration and dead time goes through.

The source degeneration will also lower the transconductance of AZ2 and AZ3. This will increase the ratio between the AZ1 and AZ2 gain and AZ3 and buffer gain. As will be explained in the next section, this will reduce the sensitivity to the charge injection mismatch and will result in lower offset and lower transients.

The transconductance of AZ2 and AZ3 with source degeneration is given by:

$$g_{m,deg} = \frac{g_m}{1 + g_m R_s} \tag{2.2}$$

Where  $g_m$  is the transconductance of the input transistors and  $R_S$  is the magnitude of the source degeneration resistor.

With a source degeneration resistor of 100 k $\Omega$  and the transconductance of AZ2 and AZ3, equal to  $g_{m\_az2} = g_{m\_az3} = 11.5 \,\mu\text{S}$ . The degenerated transconductance will be around 5.35  $\mu$ S. With an AZ1 and buffer transcondutance of about 143.5  $\mu$ S, the ratio between the buffer and AZ3 gain will be about 30 times.

## 2.4. Residual offset analysis

In this section the residual offset is analyzed, which can be expected from the circuit in Figure 2.6. As mentioned earlier, the auto-zeroing consists of two phases. Phase  $\phi_2$  in which the offset of AZ1 (Vos2) is measured and stored and phase  $\phi_1$  in which the offset of the buffer (Vos1) is measured and stored.

## Phase $\phi_2$

Figure 2.11: The equivalent block diagram of the loop measuring Vos2.

In phase  $\phi_2$  the equivalent block diagram of the circuit measuring the offset of AZ1 (Vos2) is shown in Figure 2.11. This loop settles at :

$$V_{EF} = \frac{A_{AZ1}}{\frac{1}{A_{int}} + A_{AZ3}} V_{os2}.$$

(2.3)

Where  $A_{AZ1}$  is the gain of AZ1,  $A_{AZ3}$  is the gain of AZ3 and  $A_{int}$  is the gain of the active integrator. Since  $A_{int} >> 1$  and the output impedance seen by  $A_{AZ3}$  and  $A_{AZ1}$  are the same, the final value of EF is determined by the ratio of the transconductance of AZ1 and AZ3.

$$V_{EF} = \frac{g_{m\_az1}}{g_{m\_az3}} V_{os2} \tag{2.4}$$

At the end of phase  $\phi_2$ ,  $V_{EF}$  is sampled and the charge injection associated with this sampling will introduce an error  $\Delta V_{EF}$ , therefore the sampled value is:

$$V_{EF} = \frac{A_{AZ1}}{\frac{1}{A_{Int}} + A_{AZ3}} V_{os2} + \Delta V_{EF}.$$

(2.5)

## Phase $\phi_1$

Figure 2.12: The equivalent block diagram of the loop measuring Vos1.

In phase  $\phi_1$  the equivalent block diagram of the circuit measuring the offset Vos1 of the buffer is shown in Figure 2.12. The voltage on  $V_{GH}$  is given by:

$$V_{GH} = A_{AZ1}(v_{id} + V_{os2}) - A_{AZ3}V_{EF}. (2.6)$$

Where  $v_{id}$  is the differential voltage seen at the input of the buffer. Combining Equation 2.6 and the previously found equation for  $V_{EF}$  (2.5) leads to:

$$V_{GH} = A_{AZ1}A_{int}v_{id} + \frac{A_{AZ1}A_{int}}{1 + A_{AZ3}A_{int}}V_{os2} - A_{AZ3}A_{int}\Delta V_{EF}.$$

(2.7)

Figure 2.13: The equivalent block diagram of the circuit removing the offset of the buffer.

The equivalent block diagram of the circuit continuously working to remove the offset of the buffer is shown in Figure 2.13. The output voltage of the buffer is given by:

$$V_{out} = (v_{id} + V_{os1})A_{buf} - V_{GH}A_{AZ2}.$$

(2.8)

Combing this with the previously found equation for  $V_{GH}$  (2.7), gives:

$$V_{out} = (A_{buf} + A_{AZ1}A_{AZ2}A_{int})v_{id} + A_{buf}V_{os1} + \frac{A_{AZ1}A_{AZ2}A_{int}}{1 + A_{AZ3}A_{int}}V_{os2} - A_{AZ2}A_{AZ3}A_{int}\Delta V_{EF}. \tag{2.9}$$

According to the definition of residual offset:  $v_{id} = V_{os\_res}$  and  $V_{out} = 0$ . Using this definition on the previously found expression of  $V_{out}$ , gives the following approximate expression for the residual offset:

$$V_{os\_res} \approx \frac{A_{buf}}{A_{AZ1}A_{AZ2}A_{int}}V_{os1} + \frac{1}{A_{AZ3}A_{int}}V_{os2} + \frac{A_{AZ3}\Delta V_{EF}}{A_{AZ1}}.$$

(2.10)

This assumes that the gain of the offset reduction loop  $(A_{AZ1}A_{AZ2}A_{int})$  is much larger than the gain of the buffer alone. If we now define the gain ratios:  $\alpha_1 = A_{buf}/A_{AZ2}$  and  $\alpha_2 = A_{AZ1}/A_{AZ3}$ , this leads to:

$$V_{os\_res} \approx \frac{\alpha_1}{A_{AZ1}A_{int}}V_{os1} + \frac{\alpha_2}{A_{AZ1}A_{int}}V_{os2} + \frac{\Delta V_{EF}}{\alpha_1}.$$

(2.11)

This equation is valid for phase  $\phi_1$ , but for phase  $\phi_2$   $V_{GH}$  is sampled which leads to a sampling error  $\Delta V_{GH}$ . This sampling error changes output by:  $\Delta V_{Out} = A_{AZ2} \Delta V_{GH}$ , which results in:

$$V_{os\_res} \approx \frac{\alpha_1}{A_{AZ1}A_{int}}V_{os1} + \frac{\alpha_2}{A_{AZ1}A_{int}}V_{os2} + \frac{\Delta V_{EF}}{\alpha_1} + \frac{\Delta V_{GH}}{\alpha_2}$$

(2.12)

for phase  $\phi_2$ . From equation 2.12 it is clear that when  $A_{int}=1$  (which is the case for the conventional circuit) it is not trivial to get low offset. For a low sensitivity to charge injection, the gain ratios  $\alpha_1$  and  $\alpha_2$  should be large. At the same time the first two terms of Equation 2.12 require low ratios  $\alpha_1$  and  $\alpha_2$ . The addition of active integration allows the first terms to be minimized by making a large integrator gain ( $A_{int}$ ). While at the same having a low sensitivity to charge injection by having large gain ratios  $\alpha_1$  and  $\alpha_2$ . The offset of AZ2, AZ3 and the integrator were not taken into account in this analysis but since they are also present in the sampling and compensation loops they will also be compensated for by the loops.

With Equation 2.12 and some typical gain values, the expected residual offset can now be calculated. The typical gain of the integrator ( $A_{int}$ ) is around 105 dB. The typical gain of OTA AZ1 ( $A_{AZ1}$ ) is around 55 dB, with a typical offset for the buffer of OTA AZ1 around 5 mV and charge-injection step of 3  $\mu$ V. The residual offset will be:

| Term 1 and 2:                                   | Term 3 and 4:                                                         | Total:    |

|-------------------------------------------------|-----------------------------------------------------------------------|-----------|

| $\frac{\alpha_{1,2}}{A_{AZ_1}A_{int}}V_{os1,2}$ | $\frac{\Delta V_{EF}}{\alpha_1}$ and $\frac{\Delta V_{GH}}{\alpha_2}$ |           |

| = 1.5  nV                                       | $= 3 \mu V/30 = 100 \text{ nV}$                                       | = 203  nV |

Table 2.2: The calculated residual offset contribution for typical values of the gain.

From Table 2.2 it is clear that the residual offset will typically be around 203 nV for phase  $\phi_2$  and around 103 nV for phase  $\phi_1$ . The main contributor to the residual offset is the due to charge injection mismatch of the deadtime switches.

## 2.5. Noise analysis

A low-noise bandgap voltage reference usually requires significant current to lower the noise generated by the bandgap core and large load capacitors to limit the bandwidth. A sampled voltage reference can reduce the bandwidth of the output noise by sampling at a very low frequency, while the same action will also lower the average required supply current. The output noise above the sampling frequency is determined by the noise of the buffer, which can be made low-noise and low-power by using dynamic offset compensation.

In this paragraph two noise reduction mechanisms are explained. The first is the reduction of the noise bandwidth, by the noise shaping caused by sampling and holding at a low frequency. The second is the reduction of the low frequency noise above the refresh frequency, by auto-zeroing the buffer which reduces 1/f noise.

#### 2.5.1. Getting low noise in the 0.1 to 10 Hz bandwidth

For voltage references used in low frequency application the most important noise is in the 0.1 to 10Hz range. The sample and hold function will not reduce the total integrated noise, but it will shape the noise. Due to the low

2.5. Noise analysis

refresh frequency, the input noise will be undersampled. This will cause all the noise of the input to foldback to the frequency band below the refresh frequency.

Assuming that the hold time is much larger than the time needed to charge the hold capacitor, the sample and hold circuit can be seen as an ideal sampler combined with a zero-order hold. In this case it can be deduced [38] that the PSD of the hold voltage noise is given by:

$$S_h(f) = \operatorname{sinc}^2(\pi f T_s) \sum_{n=-\infty}^{\infty} S_{in}(f - \frac{n}{T_s}).$$

(2.13)

In equation 2.13 the left term is the noise shaping due to the hold function and the right term the noise folding due to the under-sampling of the input noise.

Assuming that the input noise is ideally low-pass filtered white noise with a noise level of  $S_0$  and bandwidth B, equation 2.13 reduces to [38]:

$$S_h(f) = \frac{2B}{f_s} S_0 \operatorname{sinc}^2(\pi f T_s). \tag{2.14}$$

In equation 2.14 the first term is the under-sampling ratio. This equation shows that the noise is reduced in bandwidth by the sinc function, but at the same time it is increased in that smaller bandwidth due to the undersampling.

Figure 2.14: The sinc function for a refresh frequency of 10s.

If the hold time of the sample and hold circuit can be 10s or higher than all the noise will be folded to a bandwidth below 0.1Hz, due to the noise shaping of the sinc function. For a refresh frequency of 10s the noise shaping done by the zero-order hold is shown in Figure 2.14. From the figure it is clear that the main lobe stops at 0.1Hz, focusing the majority of the noise below this frequency.

The sampling action via the on-resistance of the switches will also introduce kT/C noise. For a 30 pF capacitor the kT/C noise will be 12  $\mu V_{rms}$ .

#### 2.5.2. Auto-zero noise

During the hold period, the noise above the refresh frequency is fully determined by the output noise of the buffer. Since the buffer is implemented in CMOS, the output noise will be dominated by 1/f noise up until a few kHz, such as shown in Figure 2.15. To get a low 1/f noise and offset, auto-zeroing is employed for the buffer. The advantage of auto-zeroing is that the low frequency noise is removed by the auto-zeroing action, due to the correlation between the sampled noise that is subtracted from the real-time noise. The disadvantage is that due to the sampling action,

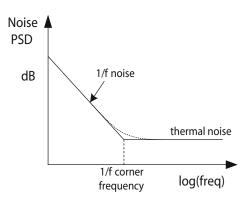

Figure 2.15: Noise PSD of a typical CMOS amplifier [1].

Figure 2.16: Noise PSD of an auto-zeroed amplifier [1].

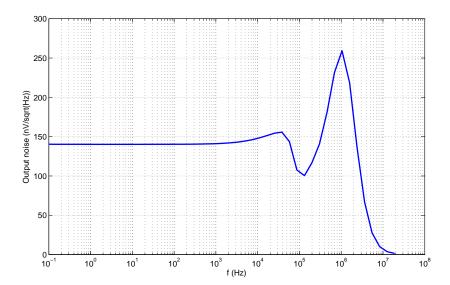

all noise above the auto-zeroing frequency, is folded back due to aliasing. Most auto-zeroing amplifiers take the bandwidth of the auto-zeroing loop to be about five times larger than the auto-zeroing frequency. This allows the auto-zeroing loop to fully settle within one period. The resulting output noise spectrum is shown in Figure 2.16.

To achieve a low output noise two aspects are important. One, the auto-zeroing frequency should be higher than the 1/f corner of the non-auto-zeroed buffer. Otherwise the 1/f noise will fold back. Secondly, for minimal fold back the bandwidth of the auto-zeroing loop should be well below the auto-zeroing frequency. As shown in figure 2.16, the foldback is determined by the ratio of the auto-zeroing loop bandwidth  $(BW_{az})$  and the auto-zeroing frequency.

The potential drawback of having a bandwidth of the auto-zeroing loop which is much lower than the auto-zeroing frequency is that the auto-zeroing now requires several auto-zeroing cycles to settle. However, for most voltage reference applications taking a while after startup to settle is acceptable. The auto-zeroing loop bandwidth ( $BW_{az}$ ) is limited by the integrator bandwidth. The integrator bandwidth can be set by picking a value of the integration capacitors, that ensures that the integrated noise over the 0.1 to 10 Hz bandwidth is within the required specification of 500 n $V_{rms}$ . Taking integration capacitors that ensure that this requirement is met, allows the auto-zeroing loop to settle as fast as the noise requirement allows.

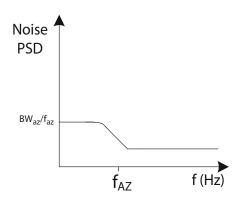

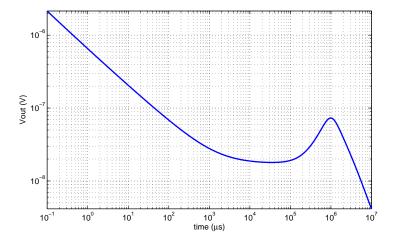

Figure 2.17 show the output noise spectrum of the buffer. It shows that the 1/f noise start to flatten above 200 kHz. This shows that a rather high auto-zeroing frequency is necessary, to keep the 1/f noise from folding over too much, due to the relatively small area of the input transistors of the buffer and AZ1.

The transconductance of the buffer is around  $g_m = \frac{I}{nV_t}$ , where  $nV_t = 60$  mV. With a current of  $10~\mu$ A, the transconductance will be about 167  $\mu$ S. This will give a noise spectral density of:  $V_n = \sqrt{16kT/gm} = 20~nV/\sqrt{Hz}$ .

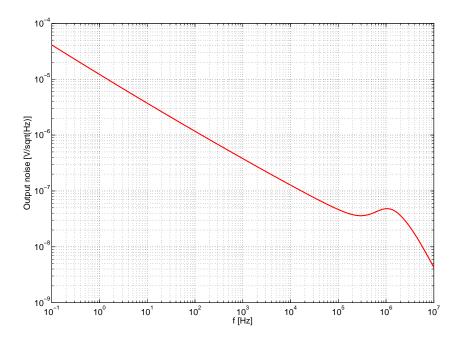

Figure 2.18 shows the output noise spectrum of the buffer with auto-zeroing. The auto-zeroing frequency is chosen as 100 kHz. In the output spectrum some folding can be observed. For low frequency the noise power spectral density is 140 nV/ $\sqrt{Hz}$ . The integrated output noise over the 0.1 to 10 Hz bandwidth is with 440 n $V_{rms}$  below the required 500 n $V_{rms}$ .

The noise is within specifications but could actually be a lot lower. Due to the fact that the auto-zeroing frequency is chosen slightly lower than the actual 1/f corner, some 1/f noise will be folded back. The top contributors are flicker noise from AZ1 and the buffer. The auto-zero bandwidth is defined by  $BW_{az} = g_{m\_int}/2\pi C_{int}$  which is around 240 kHz for this design. This makes the ratio of auto-zero bandwidth and auto-zeroing frequency, around a factor 2.4. Therefore the contribution of the folded white noise of AZ1 and the buffer is around  $70 \, \text{nV}/\sqrt{Hz}$ . This is about half of the achieved  $140 \, \text{nV}/\sqrt{Hz}$ . Increasing the size of the input transistors in AZ1 and the buffer could further reduce the noise.

2.5. Noise analysis

Figure 2.17: The output noise spectrum of the buffer without auto-zeroing, with logarithmic y and x-axis.

Figure 2.18: The output noise spectrum of the buffer with auto-zeroing at 100 kHz.

## **2.6.** ACHIEVING A LONG HOLD TIME

The key to realizing a sampled voltage reference with both low-noise bandwidth and low-power, lies in achieving a long hold time. From the previous section it is clear that, to push all the noise below 0.1 Hz, a hold time of at least 10 s is necessary. This long hold time is achieved by reducing the leakage of the hold capacitor. In this paragraph several leakage mechanisms in CMOS switches are explained and several techniques are described to reduce the leakage.

The leakage of the hold capacitor can be split into two different components: one is the leakage due to the sample and hold circuit and two is the leakage due to the auto-zeroed buffer connected to the hold capacitors. These two components can be individually examined and optimized for low leakage.

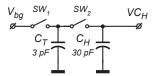

Figure 2.19: On the left a normal S&H circuit and on the right the special low leakage S&H circuit.

In a normal sample and hold circuit, shown in Figure 2.19, the main source of leakage is due to the leakage of the sample and hold switches in the off state. The effects that mainly contribute to this are the leakage of the different junctions, such as the body diode leakage ( $I_{body}$ ) and the channel leakage ( $I_{channel}$ ).

The leakage of the auto-zero circuit is mainly due to the input switches. For chopper amplifiers it is known that adding switches to the input increases the input current [39, 40]. For auto-zero amplifiers this effect is not well documented. Therefore in the rest of this chapter the input current due to auto-zeroing will also be discussed.

There are several effects that contribute to the hold capacitor leakage, that will be discussed in the following sections.

#### 2.6.1. BODY DIODE LEAKAGE

The body and the channel of a MOS transistor form a parasitic PN-junction diode, which is reversed biased under normal conditions. The current through this reversed biased diode can be described by:

$$I = I_S \left[ \exp \left( \frac{V_d}{NV_t} \right) - 1 \right]. \tag{2.15}$$

From equation 2.15 it is clear that the diode current equals zero if there is no voltage across the diode. This can be achieved by biasing the body at a bias voltage equal to the drain and source voltage. For a p-substrate process with a n-well, the PMOS body can be biased at a different potential easily by the availability of an isolated n-well. However switches  $SW_1$ ,  $SW_2$  and  $SW_3$  in Figure 2.19 are created with transmission gates, containing both NMOS and PMOS transistors.

For a NMOS devices in a p-substrate process, all the bodies are connected together by the shared substrate. The use of a triple-well technology allows the creation of a p-substrate area (p-sub) which is isolated from the rest of the substrate. This isolation is achieved by placing a deep n-well around a part of the substrate, which created an

electrically isolated p-substrate area. The availability of this isolated p-sub allows the body of the NMOS used in the transmission gate to be biased at a different potential.

Figure 2.20: The different parasitic diodes of the T-gate implementation of switch SW2 in a tripple well process