# High-Speed Data Path for a Laser Communication Terminal

Building a 100 Mbit/s Laser Communication

Terminal for CubeSats

Alexander Matthijs van Leeuwen

## High-Speed Data Path for a Laser Communication Terminal

## Building a 100 Mbit/s Laser Communication Terminal for CubeSats

by

## Alexander Matthijs van Leeuwen

to obtain the degree of Master of Science in Computer Engineering at the Delft University of Technology,

to be defended publicly on Monday July 20, 2020 at 10:00.

Student number: 4351436

Project duration: February, 2019 – June, 2020

Thesis committee: Dr. ir. J. S. S. M. Wong, TU Delft, supervisor

Dr. ir. A. J. van Genderen, TU Delft Dr. ir. C. J. M. Verhoeven, TU Delft

Dr. ir. S. Engelen Hyperion Technologies, daily supervisor

This thesis is confidential and cannot be made public until July 20, 2022.

An electronic version of this thesis is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

## **Abstract**

In the recent years the satellite industry has progressed on the subject of optical communication for use in space. With recorded speeds over 5 Gb/s it has shown to be an alternative for radio communication. In the CubeSat market this technology is new, underdeveloped, and could lead to new missions that were not possible before. As such, TNO and Hyperion joined forces to create the CubeCAT LCT (Laser Communication Terminal). The core part of this LCT is the high-speed digital data path, which was not implemented. This thesis discusses the design, implementation, and verification of the high-speed data path of the CubeCAT LCT (Laser Communication Terminal) that has a targeted speed of 100 Mb/s, with a future upgrade path to 1 Gb/s.

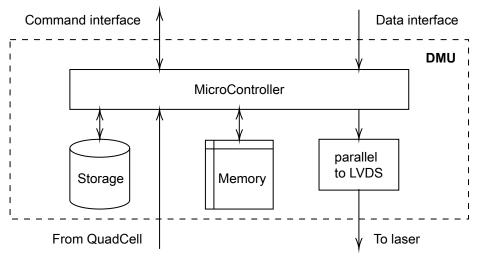

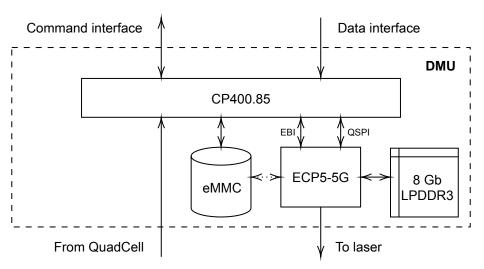

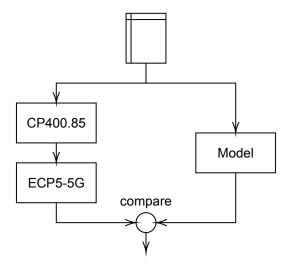

The CubeCAT module consists of multiple modules, of which the DMU (Data Management Unit) hosts the high-speed data path. As the DMU was not implemented, a design for the DMU is proposed in this thesis. For this design multiple architectures, interconnects, and components where considered. The proposed design is based on an Hyperion CP400.85 microprocessor connected to a Lattice ECP5-5G FPGA, together with extra external memory and external storage.

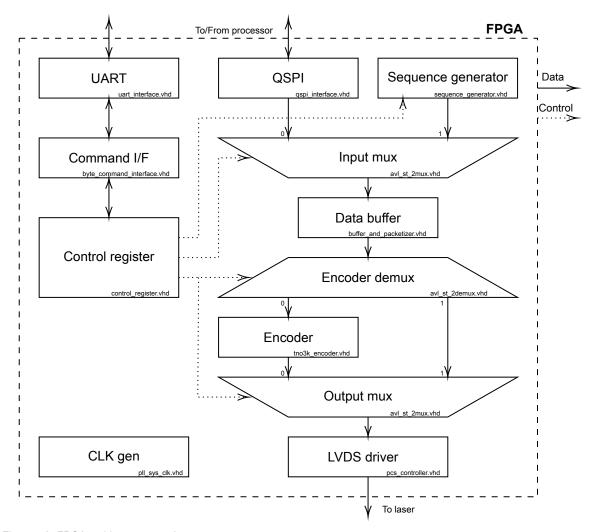

Then, an implementation of the high-speed data path was made that is based on a QSPI link between the microprocessor and the FPGA. This implementation is based on streaming the data from the microprocessor to the FPGA, in which the data is encoded according to the TNO3k FEC (Forward Error Correction) scheme. After encoding, the data is outputted as an LVDS signal to the laser output.

The implementation of the high-speed data path was verified by simulation and on a development setup. This was done by first verifying all submodules, with focus on the QSPI link and the TNO3k encoder, and then as a whole system. All submodule tests were successful, with a note to the verification of the QSPI link. It was found that the development setup was limited to a SPI frequency of 41.50 MHz due to signal integrity issues.

During the system test it was found that the there was a lack of LVDS test material. As such the LVDS output was replaced by a UART output. With this output the whole system has been validated for a QSPI link speed of 119.2 Mb/s and an internal FPGA speed of 3.2 Gb/s. The system, with LVDS output, is estimated to consume 1 watts of power.

With the validation of the whole system, the high-speed data path of the CubeCAT LCT has been implemented. The design of the DMU allows for a later, 1 Gb/s upgrade of the high-speed data path.

## **Preface**

With this thesis my time at Hyperion comes to an end. Almost one and a half years ago I started there, working with colleagues. Now when I look back I'll leave friends there.

My (almost) one and a half years at Hyperion were not always spent on working on this thesis project. In the meantime I've worked on two other projects, delaying the finalisation of this thesis by about three months. Besides, I've mingled in with the system administrators at Hyperion, as the setup was, in my opinion, in dire need of an update. This side-track helped me acquire some skills that I otherwise wouldn't have picked up. At other times I spent time helping colleagues with their code, as I couldn't resist their call for help.

With this big delay and unclear ending date I think I've stressed out my girlfriend Sofie a bit, as she hopes to buy a house, which is impossible on a thesis compensation. My sincere apologies for that and I thank her very much for the patience that you had.

Other people that I'd like to thank are my parents for helping me get where I am now. Then I'd like to thank my friends for their support and motivation, without them the thesis journey would have been significantly harder.

Additionally, I'd like to thank the people at Hyperion and the people on the TNO CubeCAT side for offering me the chance to gain experience my time at Hyperion. My supervisor, Steven, and I had some great discussions about computing technology, making me wonder if he really did study Aerospace Engineering. Thank you Steven for these discussions and for your guidance.

Lastly, I'd like to thank Stephan Wong, my professor, for guiding me in the thesis process especially when I was getting lost halfway through.

Sander van Leeuwen Oegstgeest, July 2020

## **Table of Contents**

| Al | ostrac                                        | et en                                                                                                                                                    | iii                              |

|----|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Pr | eface                                         |                                                                                                                                                                                              | ٧                                |

| Li | st of F                                       | Figures                                                                                                                                                                                      | хi                               |

| Li | st of T                                       | Tables                                                                                                                                                                                       | xiii                             |

|    | ossaı                                         |                                                                                                                                                                                              | χv                               |

|    |                                               |                                                                                                                                                                                              |                                  |

| A  | crony                                         | ms :                                                                                                                                                                                         | xvii                             |

| 1  | 1.1<br>1.2                                    | Problem statement and Goals                                                                                                                                                                  | 2                                |

| 2  | <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul> | kground SmallSats Hardware in space 2.2.1 Thermal considerations 2.2.2 Ionization effects 2.2.3 Mitigation CubeCAT 2.3.1 System overview 2.3.2 Coding scheme Related work 2.4.1 CubeCAT work | 5<br>6<br>6<br>6<br>7<br>9       |

| •  |                                               | 2.4.2 Non-CubeSat                                                                                                                                                                            | 11<br>12                         |

| 3  | 3.1                                           | A Management Unit Responsibilities                                                                                                                                                           | 15<br>15<br>16<br>16<br>16<br>17 |

|    | 3.3                                           | 3.2.3 Components  Data Management Unit build-up.  3.3.1 HummingBoard Pulse with ECP5-5G via PCle  3.3.2 TQMa8Xx with ECP5-5G via PCle  3.3.3 CP400.85 with ECP5-5G via QSPI and EBI.         | 23<br>25<br>25<br>26             |

|    | 3.4                                           | Subsystem responsibilities                                                                                                                                                                   | 27                               |

|    | 3.5                                           | Conclusion                                                                                                                                                                                   | 29                               |

viii Table of Contents

| 1   | Data        | Path I  | mplementation 3                 | 1 |

|-----|-------------|---------|---------------------------------|---|

| 7   |             |         |                                 |   |

|     |             |         |                                 |   |

|     | 4.2         |         | Architecture and Implementation |   |

|     |             | 4.2.1   | Control interface               |   |

|     |             | 4.2.2   | Clock generator                 |   |

|     |             | 4.2.3   | QSPI peripheral                 |   |

|     |             | 4.2.4   | Sequence generator              |   |

|     |             | 4.2.5   | Input mux                       | 5 |

|     |             | 4.2.6   | Data buffer                     | 5 |

|     |             | 4.2.7   | Encoder demux                   | 5 |

|     |             | 4.2.8   | Encoder                         | 5 |

|     |             | 4.2.9   | Output mux                      | 8 |

|     |             | 4.2.10  | LVDS driver                     |   |

|     | 4.3         |         | re Implementation               |   |

|     |             | 4.3.1   | SPI-NOR                         |   |

|     |             | 4.3.2   | Custom SPI-MEM controller       |   |

|     |             | 4.3.3   | QSPI driver DMA                 |   |

|     |             |         |                                 |   |

|     |             |         | Integrated driver               |   |

|     | 4.4         | Conclu  | sion                            | 9 |

| 5   | Test        | ing and | I validation 4                  | 1 |

| •   |             |         | ind setup                       | _ |

|     |             |         |                                 |   |

|     | J. <u>Z</u> |         | Encoder                         |   |

|     |             |         |                                 |   |

|     | E 2         |         | QSPI peripheral                 |   |

|     | 5.3         |         | re                              |   |

|     |             |         | QSPI driver                     |   |

|     | 5.4         |         | 1                               |   |

|     |             |         | QSPI communication              |   |

|     |             |         | End-to-end                      |   |

|     | 5.5         | Power   |                                 |   |

|     |             | 5.5.1   | Method                          | 8 |

|     |             | 5.5.2   | Results                         | 9 |

|     |             | 5.5.3   | Discussion                      | 9 |

|     | 5.6         | Conclu  | sion                            | 9 |

| _   | 0           | -11     | and Friting Mark                |   |

| 6   |             |         | and Future Work 5               |   |

|     | 6.1         | Summ    | ary                             | 1 |

|     |             |         | sion                            |   |

|     | 6.3         |         | ontributions                    |   |

|     | 6.4         |         | work                            |   |

|     |             |         | Work on the FPGA                |   |

|     |             | 6.4.2   | Work on the Software            | 3 |

| Rik | alioa       | raphy   | 5                               | 5 |

|     |             |         |                                 | J |

| Α   |             | DS 142  |                                 | - |

|     |             | _       |                                 |   |

|     | A.2         | Implen  | nentation                       | 2 |

|     |             | A.2.1   | Add TF ASM                      | 2 |

|     |             | A.2.2   | Byte-to-bit stream              | 2 |

|     |             | A.2.3   | Slicer                          |   |

|     |             | A.2.4   | Psuedo-Randomizer               |   |

|     |             |         | Add CRC                         |   |

|     |             |         | Add Termination bits            |   |

|     |             | A.2.7   | Convolutional Encoder           |   |

|     |             | A.2.8   | Code interleaver                |   |

|     |             | _       | Accumulator                     |   |

|     |             | ,Z.J    | , 100dinated                    | J |

Table of Contents ix

|   | A.2.10 PPM Symbol Mapper                |    |

|---|-----------------------------------------|----|

|   | A.2.11 Channel interleaver              | 34 |

|   | A.2.12 Add Codeword ASM                 | 34 |

|   | A.2.13 Repeater                         | 34 |

|   | A.2.14 Slot mapper                      |    |

|   | A.2.15 Guard slot insertion             |    |

| В | HummingBoard                            | 65 |

|   | HummingBoard<br>B.1 PCle                | 35 |

|   | B.1.1 FPGA PCIe core                    | 35 |

|   | B.1.2 Linux PCle driver                 | 35 |

|   | B.1.3 Traces                            |    |

| С | • • • • • • • • • • • • • • • • • • • • | 67 |

|   | C.1 Initial stream mechanism            | 37 |

|   | C.2 Avalon Streaming interface          | 39 |

## List of Figures

| 1.1        | LEO orbit illustration                                                                                                                                                               | 1        |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1<br>2.2 | TNO CAT optical communication systems overview  CubeCAT System overview                                                                                                              | 7<br>8   |

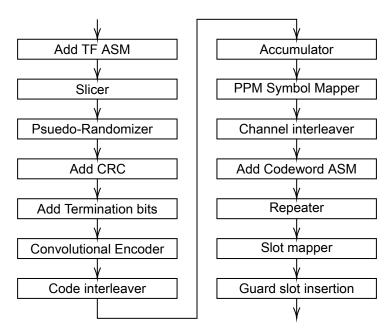

| 2.3<br>2.4 | CCSDS 131.0b3 overview                                                                                                                                                               | 9<br>10  |

| 2.5        | TNO3k overview                                                                                                                                                                       | 11       |

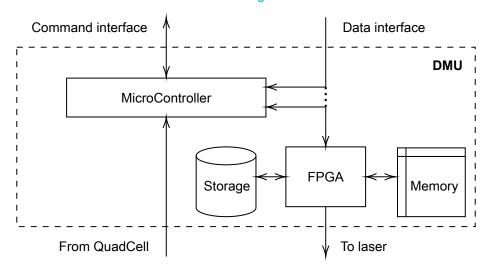

| 3.1<br>3.2 | Data Management Unit interfaces  Microcontroller LVDS bridge interface architecture                                                                                                  | 15<br>17 |

| 3.3        | Microcontroller with an FPGA architecture                                                                                                                                            | 18       |

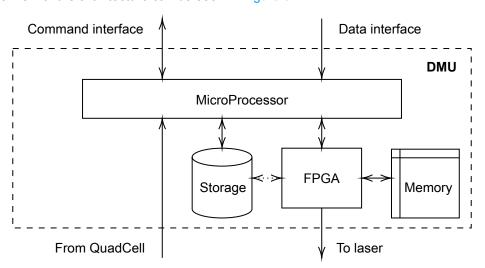

| 3.4        | Microprocessor with an FPGA architecture                                                                                                                                             | 18       |

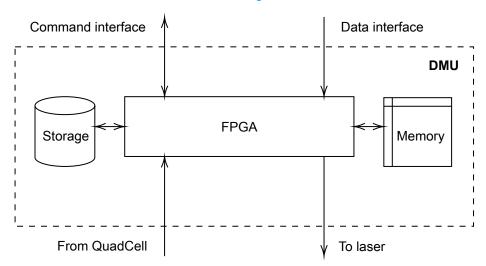

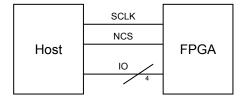

| 3.5<br>3.6 | FPGA only architecture                                                                                                                                                               | 19<br>20 |

| 3.7        | SD connection                                                                                                                                                                        | 20       |

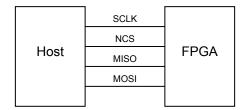

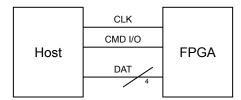

| 3.8        | QSPI connection                                                                                                                                                                      | 21       |

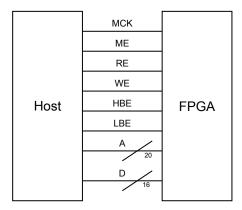

|            | EBI connection                                                                                                                                                                       | 21<br>22 |

| 3.11       | PCle connection                                                                                                                                                                      | 22       |

| 3.12       | DMU build-up with the CP400.85 and the ECP5-5G                                                                                                                                       | 26       |

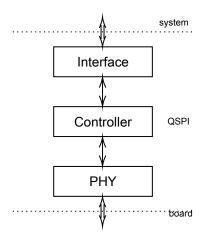

|            |                                                                                                                                                                                      | 32       |

| 4.2<br>4.3 | FPGA architecture overview                                                                                                                                                           | 33<br>34 |

| 4.4        | TNO3k encoder implementation overview                                                                                                                                                | 36       |

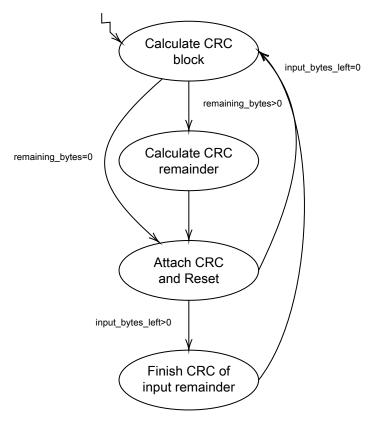

| 4.5        | CRC implementation state diagram                                                                                                                                                     | 37       |

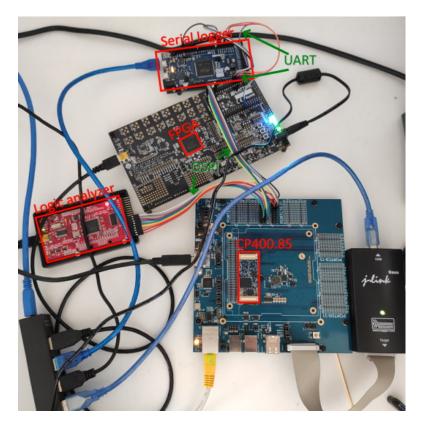

|            |                                                                                                                                                                                      | 42       |

| 5.2<br>5.3 | Attach Marker cocotb result in GTKWave                                                                                                                                               | 42<br>45 |

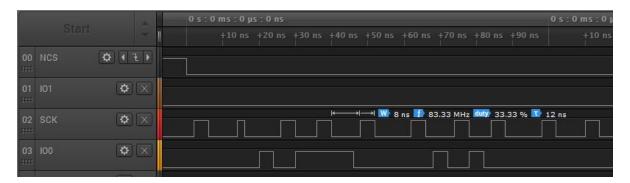

| 5.4        | QSPI interface test logic analyser trace of a 83 MHz transmission, showing noise on the                                                                                              | 40       |

|            | lines                                                                                                                                                                                | 46       |

| 5.5<br>5.6 | QSPI interface test logic analyser trace of a 55 MHz transmission, with coupling occurring. QSPI interface test logic analyser trace of a 83 MHz transmission, showing a significant | 47       |

|            | phase shift                                                                                                                                                                          | 47       |

| 5.7        | End-to-end system test overview.                                                                                                                                                     | 48       |

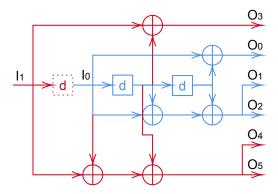

|            |                                                                                                                                                                                      | 61       |

| A.2        | Convolutional encoder. In blue the one-input version. The red extends the one-input version to a two output version, where the dotted delay element is implicitly the second         |          |

|            |                                                                                                                                                                                      | 63       |

## **List of Tables**

| 3.1 | Data Management Unit requirements. The <i>Importance</i> column specifies the importance       |    |

|-----|------------------------------------------------------------------------------------------------|----|

|     | for the CubeCAT project.                                                                       | 16 |

| 3.2 | DMU architecture choice matrix                                                                 | 19 |

| 3.3 | DMU interconnection choice matrix. N denotes the link width.                                   | 23 |

| 3.4 | FPGA responsibilities. The <i>Importance</i> column specifies the importance for the Cube-     |    |

|     | CAT project                                                                                    | 27 |

| 3.5 | Software responsibilities. The <i>Importance</i> column specifies the importance for the Cube- |    |

|     | CAT project                                                                                    | 27 |

| 5.1 | QSPI driver test results. Ratio as calculated from the reported dd speed / theoretical         |    |

|     | bandwidth. The theoretical bandwidth is 4 bits * SPI speed                                     | 44 |

| 5.2 | QSPI interface test results. Ratio as calculated from the reported dd speed / theoretical      |    |

|     | bandwidth. The theoretical bandwidth is 4 bits * SPI speed.                                    | 45 |

| 5.3 | QSPI interface test results with improved cables. Ratio as calculated from the reported        |    |

|     | dd speed / theoretical bandwidth. The theoretical bandwidth is 4 bits * SPI speed.             | 46 |

## Glossary

- **1U** The standard unit (U) of a CubeSat is 10 cm x 10 cm x 10 cm. xv, 1, 2, 5–7, 12, 13, 16, 51

- API A specification of a system interface, to be used by other systems. 28, 39

- **back-pressure** The concept where a receiver needs the transmitter to pause since the receiver is still processing its data. 67

- **bit** one binary element. iii, 1, 2, 5, 7, 9–13, 16, 17, 20–22, 24–26, 29, 32–34, 36–39, 44, 46–49, 51–53, 62–64

- byte eight binary elements. xv, 20, 21, 25, 27, 28, 33-37, 44-46, 62-64

- **CCSDS** is an international organization that is focused on the development of communication and data systems standards for spaceflight. Members include ESA, NASA and JAXA. 9, 10, 27, 61

- constellation a group/ pack of satellites. 5

- **CubeCAT** A Laser Communication Terminal being developed by Hyperion and TNO. iii, v, 1–3, 5–13, 15, 16, 24–26, 29, 51–53

- **CubeSat** A satellite built around standardized size modules. See also 1U. iii, xv, 1, 2, 5–7, 11–13, 23, 51

- **GEO** an orbit in which a satellite, relative to earth, stays fixed at on position, for example a TV broadcasting satellite. The distance relative to Earth is around 35700 km.. 6, 11

- **latch-up** is an electrical event where a line is stuck at a (logic) level. In the case of a non-permanent latchup the solution is a reset (power cycle) of the circuitry. 23

- **LEO** an orbit in which a satellite moves around Earth, for example the ISS (International Space Station). The distance relative to Earth is 2000 km or less.. 1, 6–8, 10–12, 17, 23, 26

- **NewSpace** the change of the space sector toward more private companies that develop faster and provide cheaper access to spaceflight. 1

- **PCIe** is a high-speed interconnect on computing systems. On version 2.0, with a x1 link the maximum data throughput is 500 MB/s. Compared to version 2.0, 3.0 supports a 984.6 MB/s maximum data throughput. 19, 20, 22–25, 65

- PPM a signal modulation technique. 10, 64

- **RS-485** a serial protocol that can be used to communicate with multiple nodes over a bus topology. 7, 15, 16, 25, 27, 28

- **SEL** an undesired, state change of the circuitry where the state remains. A power-cycle can fix non-permanent latchups. 6, 13, 51

- **SEU** an undesired state change of circuitry due to a radioactive particle hitting the circuitry. 6, 13, 24, 25, 51

- SmallSat A satellite with a total weight of (usually) less than 500 kg. 3, 5, 13, 51

xvi Glossary

**SSD** an SSD is a type of storage that is build around multiple parallel flash banks, providing high data rates and good random read write performance due to no mechanical limitations. 25

- **TID** the total dose of radiation accumulated over time that the device can handle before stopping to function. 6, 13, 51

- **TNO** Is a Dutch research organization focussing on applied science. iii, xv, 1, 2, 6, 7, 10, 38, 52, 53, 63

- **validation** The process of checking a system where the primary question is "Are we building the right system?"[1]. See also verification. xvi, 48, 49, 52

- **verification** The process of checking a system where the primary question is "Are we building the system right?"[1]. See also validation. xvi, 3, 41, 42, 44, 45, 49, 52

- Verilog a Hardware Description Language. 65

## **Acronyms**

```

ADC Analog to Digital Converter. 19

BER Bit Error Rate. 9, 61

CRC Cyclic Redundancy Check. 36, 37, 45, 53, 62, 63

DDR Double Data Rate. 20, 21, 24

DLR Deutsches Zentrum für Luft- und Raumfahrt. 10, 11

DMA Direct Memory Access. 23, 28, 39, 44, 51

DMU Data Management Unit. iii, 8, 9, 15, 16, 23, 25, 26, 28, 29, 31, 41, 48, 49, 51–53

EBI External Bus Interface. 19, 21, 23, 24, 26–29, 39, 51, 53

ECC Error-Correcting Codes. 6, 23, 25

eMMC embedded MultiMediaCard. 25, 29, 49, 51

ESA European Space Agency. 10, 11

FD-SOI Fully Depleted Silicon On Insulator. 23

FEC Forward Error Correction. iii, 2, 5, 7–10, 52, 61, 62, 67

FIFO First-In, First-Out. 33–35, 38, 48

FPGA Field Programmable Gate Array. iii, 3, 5, 17–29, 31, 32, 34, 35, 38, 39, 41, 44–49, 51–53, 64,

FSM Fine Steering Mirror. 8, 12

HDL Hardware Description Language. xvi, 31, 36, 41, 42, 65, 67

IP Intellectual Property. 31, 33, 34, 38, 65

ISS International Space Station. xv

JPL Jet Propulsion Laboratory. 6

LCT Laser Communication Terminal. iii, xv, 1, 2, 5, 7, 11–13, 23, 51, 53

LDPC Low-Density Parity Check. 10

LSE Lattice Synthesis Engine. 31

LVDS Low-Voltage Differential Signaling. iii, 9, 15–18, 20, 24, 25, 27, 29, 32, 38, 48, 49, 51, 52

MMC MultiMediaCard. 25

NASA National Aeronautics and Space Administration. 5, 6, 10, 12

NVMe Non-Volatile Memory Express. 22

```

xviii Acronyms

```

OBC On-Board Computer. 24

OS Operating System. 18

OSI Open Systems Interconnection. 65

QSPI Quad SPI. iii, 19–21, 23–29, 31, 34, 35, 38, 39, 41, 42, 44, 46, 47, 49, 51–53

RAM Random Access Memory. 63, 64

REST Representational State Transfer. 28

RS Reed-Solomon. 36

SD Secure Digital. 19, 20, 24, 25

SDR Single Data Rate. 20

SerDes Serializer/Deserializer. 38

SoC System on a Chip. 24

SoM System on Module. 23, 24, 65

SPI Serial Peripheral Interface. iii, 19–21, 35, 44, 48, 53

UART Universal Asynchronous Receiver-Transmitter. iii, 28, 33, 41, 45, 48

UFS Universal Flash Storage. 25

USB Universal Serial Bus. 7, 15, 16, 19, 21–25, 27, 28

VHDL VHSIC-HDL (Very High Speed Integrated Circuit Hardware Description Language). 31, 37, 41,

42, 49, 52, 62, 65

```

1

## Introduction

You grab your phone and take a picture of a famous bridge. With 4 taps the picture is sent to a friend and within an instant you have a reply with a picture of his cat. All this is made possible by the fast, land-based internet infrastructure. This is different for satellites, especially satellites in Low-Earth Orbit (LEO). Satellites in LEO fly over a coordinate every 90 to 120 minutes and can only communicate when a ground station is in 'sight'. Therefore, when a ground station is in sight it will only have a few minutes to send all stored data, as is illustrated by Figure 1.1.

Figure 1.1: LEO orbit illustration

With the increasing scarcity of available radio-frequencies for satellite communication, the satellite link becomes a limiting factor for a mission. For example, a satellite could have plenty of storage and the best-in-class camera, but it can only take ten images per orbit because more images cannot be sent over the 19 kb/s link[2]. Compromises can be made by compressing or resizing the images, reducing them in quality and size making it possible to send more images over this link. Having more available bandwidth for the link would enable more and better quality images to be photographed and communicated.

The bandwidth problem has led the industry to develop high-bandwidth antennas for faster links. Some of the solutions include foldable satellite dishes, which can unfold in flight to save space during launch. These high-bandwidth antennas use different radio bands which can be harder to operate.

Another development to increase the bandwidth is using lasers for optical communication. Bigger satellites have already demonstrated high-speed links in space and to ground[3], proving it a viable technology. However, the CubeSats of the NewSpace industry lacks modules that support optical communication.

The Dutch research institute TNO started a project in collaboration with Hyperion Technologies (hereafter Hyperion) under the name of CubeCAT which envisions a 1 unit (1U) LCT (Laser Communication Terminal) for CubeSats. The envisioned CubeCAT module would feature a 1 Gb/s downlink and a 200 kb/s uplink that is operated from a satellite in Low-Earth Orbit (LEO) orbit.

2 1. Introduction

During the project TNO is responsible for the optical, photonic, and the ground station parts, where Hyperion is responsible for the electronics. For the first iteration the goal is to achieve 100 Mb/s with hardware that is capable of 1 Gb/s. Later in the project this speed could be increased to 500 Mb/s with the final goal to meet the 1 Gb/s. As ultimate goal for the Laser Communication Terminal a speed of 10 Gb/s is envisioned.

#### 1.1. Problem statement and Goals

One of the key features of the CubeCAT LCT is the high-speed digital data path which is responsible for the, first 100 Mb/s and later, 1 Gb/s throughput of the system. Despite the importance of this feature, this is still an open point that has not been implemented yet.

For the implementation of this high-speed digital data path, a design needs to be made with in mind the constraints of a CubeSat system, as well as the environment the module operates in, and the possibility of data corruption during transmission. The constraints manifest themselves in terms of power and size. Power in a CubeSat is limited due to the limited space for solar arrays and batteries in a satellite. The constrained size is due to the room required for the optics and other electronics in the 1U available volume. The environment CubeCAT will operate in is space, requiring hardware that can handle this environment. Furthermore, as data will be downlinked from space, it will be attenuated by Earths atmosphere. To reduce the possible corruption introduced by this attenuation, a FEC (Forward Error Correction) must be implemented.

As all the aforementioned items need to be addressed the following research question arises:

"How can the high-speed digital data path of the CubeCAT be implemented in such way that it provides a robust, upgradable, 100 Mb/s link, with constrained power and size?"

From this research question multiple goals can be devised. By achieving all goals the research question can be answered. The goals are as follows:

- A Provide a design for the high-speed digital data path.

- **B** Provide an implementation for the high-speed digital data path.

- C Ensure robust communication by implementing a Forward Error Correction.

#### 1.2. Methodology

Before being able to achieve the set goals, intermediate steps need to be performed. The following methodology is devised to address these intermediate steps, the goals and the research question.

- Explore where the CubeCAT module will be used as context for the design.

- Explore hardware in space as context for the design.

- Explore the CubeCAT project as context for all goals.

- Explore comparable work as context for the project.

- Detail the requisites of the high-speed digital data path for the design and implementation.

- Explore the design space.

- Propose a design for Goal A.

- · Implement the Forward Error Correction.

- Verify the Forward Error Correction for Goal C.

- · Implement the high-speed digital data path.

- Verify the whole high-speed digital data path for Goal B.

- · Validate the results of the verification to the set goals.

- Conclude on the work done to answer the research question.

- Propose recommendations for future work on the high-speed digital data path.

1.3. Thesis Outline 3

#### 1.3. Thesis Outline

The first part of Chapter 2 focusses on the SmallSat sector, followed by a discussion of the challenges of hardware in space. Following this discussion is a planar explanation of the CubeCAT project, its subsystems, and its coding scheme. Finally an overview of related work is included, with a conclusion given at the end. With the CubeCAT system explained, Chapter 3 zooms in on the design of the high-speed digital data path, by describing the design options, possible configurations, and the designs subsystem responsibilities. In Chapter 4 the design and implementation of the high-speed digital data path can be found. This is split up in a discussion about the FPGA implementation and the software implementation. Tests to verify the correct behaviour of the (sub-)systems are described in Chapter 5. Here, the power consumption of the system is also characterized. Lastly, in Chapter 6, a final conclusion is given for the thesis, with its main contributions, as well as future work.

## Background

In this chapter information can be found that gives extra context to the market of the Laser Communication Terminal, the environment it operates in, the CubeCAT build-up, and its competitors. This information is later used as context for the design.

This chapter is organised as follows: in Section 2.1 the concept of SmallSats is explained. After that, the challenges of hardware in space are discussed in Section 2.2 after which the CubeCAT project is explained in Section 2.3, with special focus on the Forward Error Correction in Subsection 2.3.2. Following is the related work found in Section 2.4. Finally, a conclusion is given in Section 2.5.

#### 2.1. SmallSats

Satellites like the Hubble telescope[4] use scientific equipment that can only fit in large satellites. The envisioned mission determines the size of the scientific equipment necessary. This also comes with extra mass, making them expensive to build and launch. When the scientific equipment is smaller in size a SmallSat can be used.

A SmallSat is a satellite with a total mass of (usually) less than 500 kg. Compared to bigger satellites SmallSats are cheaper since they require less space in the launch vehicle and less mass to get into orbit. Additionally, because they are smaller in size they are cheaper to design and produce. In most SmallSats commercial-off-the-shelf components are used, further reducing the costs. This enables larger production quantities of the satellites. The reduced total cost has the advantage that multiple satellites can be launched within the same budget. Multiple satellites improve redundancy in the mission, covering a ground target more frequently, or covering multiple ground targets. Multiple SmallSats can, for example, also be used to build constellations, for testing and qualifying hardware, for connectivity servicing (for example Hiber[5]), for earth observation and for student projects.

A sub-category of SmallSats is the CubeSat. It is a satellite based on modules of a standardized size, where 1 unit (1U) is a cube with edges of 10 cm. The standardized format allows for the creation of off-the-shelf components, making it easier, cheaper, and faster to build a satellite. Besides, more focus can be given to the payload, the core of the mission, as the rest of the components can be bought off-the-shelf.

With the CubeCAT Laser Communication Terminal a terminal of 1 unit (1U) is envisioned to enable SmallSat missions that require a lot of bandwidth, for example imaging missions. Compared to a traditional S-band transceiver[6] the downlink capability goes from 10 Mb/s to 1 Gb/s, resulting in a two decade gain. This gain in downlink capability it could enable missions that were otherwise not possible.

#### 2.2. Hardware in space

In 1994 J.H. Trainor from NASA released a document[7] describing the effects of radiation in space. This document includes examples of missions encountering these kinds of problems. Trainor acknowledges in this document that the industry was making efforts to cope with the effects of radiation on hardware.

Since the publication, the industry hasn't stopped innovating. For example, Xilinx has radiation hardened FPGA families in its product portfolio that have been designed and tested with the help of

6 2. Background

JPL and have even been independently tested by NASA[8]. Another example is BAE Systems with the RAD750 microprocessor[9]: a processor especially developed for use in space missions, such as the Mars 2020 Rover mission[10]. This hardware can deal with the challenges of the temperature and the effects of radiation in space. In the following subsections these challenges will be further detailed and mitigation options are discussed.

#### 2.2.1. Thermal considerations

In space the temperatures can vary significantly. In a Low-Earth Orbit (LEO) the temperatures can change with 100 °C during one orbit on a 1U CubeSat[11]. This temperature change is smaller if it is measured at the circuitry. From [12] it can be seen that thermal cycling, for example from orbiting Earth, a chip can cause problems.

#### 2.2.2. Ionization effects

On earth the atmosphere protects us from ionized particles coming from the galactic cosmic or the sun[13]. In space, these particles are not obstructed by the atmosphere and only affected by a magnetic field of a planet. The ionized particles can cause problems like Single Event Latchup (SEL), Single Event Upset (SEU), and Total Ionizing Dose (TID). These problems can be reduced/ mitigated as will be explained in the following subsubsections.

#### **SEL**

A Single Event Latchup (SEL) is caused by a particle hitting circuitry and inducing an electric charge. This can temporarily or permanently alter the function of circuitry by, for example, disabling the ability of a chip to change the state of one of its I/O pins[14]. If the problem is of temporary nature, then the problem can be solved by power-cycling the circuitry.

#### SEU

As with a SEL a Single Event Upset (SEU) is caused by a particle hitting circuitry and inducing an electric charge. The charge will change the state of, for example, a communication line, changing its binary value from a '0' to a '1'. The event is of temporary nature and will only induce a single error in the system, but will corrupt the communication that was ongoing on the communication line. Most noticeable are the upsets in memory, since the memory makes up large areas in chips. According to [15] multiple bit flips can happen per day.

#### TID

The Total Ionizing Dose (TID) closely relates to the doping of the semiconductors in a chip. Due to radiation the composition of the materials slightly changes over time[16]. This affects the doping of a semiconductor, changing its conductivity. The effects on a transistor (the fundamental building blocks of a chip) can be that the leak current increases, the transition speeds changes, or it stops functioning at all.

#### 2.2.3. Mitigation

Thermal issues can be mitigated by installing heaters against the cold and radiators against the heat. These measures can reduce the difference in temperature. The effects of thermal cycling can be reduced by limiting the chip size.

Several options of mitigation exist for radiation. In circuitry blocks can be implemented redundantly, with a voting system such that one block can fail and the function of system as a whole isn't compromised. Another option is to shield the hardware from radiation[16], reducing the chance of particles actually hitting the circuitry. Data can be protected against corruption by radiation by using ECC (Error-Correcting Codes)[15], making it possible to repair data.

#### 2.3. CubeCAT

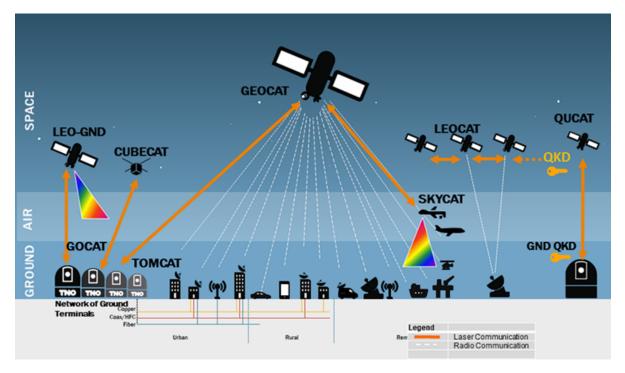

CubeSat Communication Adaptive Terminal (CubeCAT) is part of a larger project of TNO where TNO envisions high-speed optical communication on a variety of vehicles, including airplanes, drones, ships, and satellites. The satellites can be split into GEO-satellites, LEO-ground-satellites, CubeSats, LEO-LEO-satellites (LEOCAT), and QUCAT (quantum key distribution). The TNO CAT systems are visualized in Figure 2.1.

2.3. CubeCAT 7

Source: TNO website[17], TNO Insights Superfast internet using laser-satellite communications, ©TNO 2018

Figure 2.1: TNO CAT optical communication systems overview

CubeCAT is marketed as a 1 Gb/s downlink Laser Communication Terminal for use in CubeSats, requiring less than 15 watts of power and having an uplink channel capable of 200 kb/s. It is an Hyperion product that is the joint effort of TNO and Hyperion.

CubeCAT's intended usage orbit is LEO, to keep the distance between the terminal and the ground station minimal, allowing the 1 Gb/s in a 1U format with 15 watts power. To be able to support this downlink speed the CubeCAT has internal storage that acts as a buffer for the science data. During the transmission, data is read from the buffer at high speed, whilst in mission mode the science data can come in at a much lower rate via a RS-485 connection or a USB connection.

The optical link the Laser Communication Terminal has with the ground station is through Earth's atmosphere, meaning that the signal is attenuated by for example clouds and other atmospheric features. To reduce data corruption by attenuation the data that is downlinked is also encoded with a Forward Error Correction scheme.

In the Subsection 2.3.1 the CubeCAT components will be discussed in more detail. The Forward Error Correction codes discussed during the project are further detailed in Subsection 2.3.2.

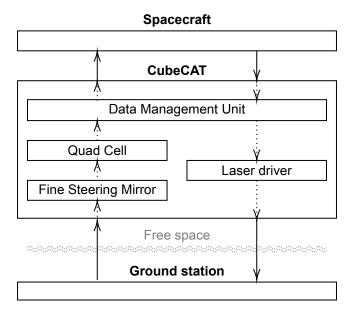

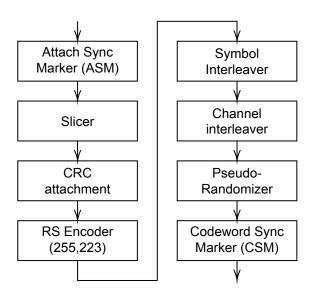

#### 2.3.1. System overview

The CubeCAT consists of multiple submodules, such as the controller for the *Fine Steering Mirror*, a *Quad Cell* detector, a *Laser driver* and a *Data Management Unit*. An abstract overview of the CubeCAT system with data flows is given in Figure 2.2. In the following subsubsections the submodules will be explained.

8 2. Background

Figure 2.2: CubeCAT System overview

#### **Data Management Unit**

The DMU (Data Management Unit) provides an interface for the satellite to communicate with the CubeCAT, both for sending commands and for data. It stores the data received from the satellite on its internal storage bank and, when a link is established, downlinks the data at the required speed through the *Laser Driver* to the ground station. During the downlink, the data is also encoded by the DMU with a FEC (Forward Error Correction) code to reduce the data corruption during the transmission.

In Figure 2.2 it can be seen that the DMU has a path through the *Laser Driver* to the ground station. The path from the DMU to the *Laser Driver* is the end of the high-speed digital data path. Inside the DMU the high-speed digital data path starts. This is at the point where a file is loaded from the internal storage bank. As such the DMU is responsible for the high-speed digital data path.

The DMU has not been implemented, which means that to reach Goal A, a design needs to be made for the DMU. This design can then be used for Goal B; to implement the high-speed digital data path.

#### **Quad Cell**

A *Quad Cell* is a configuration of four photosensitive elements that can be used to detect the position of an incoming light beam. Based on the received power per photosensitive element the spot location, the centre of the incoming beam, can be calculated. Furthermore, the total received power can be calculated, which can be used as an indicator of how much interference the optical link has. Possibly, this interference indicator can be used to dynamically adjust the bitrate of the downlink, to prevent data corruption or to increase the bandwidth. Besides, the total received power over time can be used as an uplink channel to communicate with the satellite, completely removing the need for a radio link with the satellite.

#### Fine Steering Mirror

Ensuring the uplink and the downlink channels are aligned by only pointing the body of the satellite to the ground station is challenging. A satellite in LEO has an orbital velocity of more than 7 km/s, requiring very precise manoeuvres of the satellite to track the ground station that are not always possible.

To ease the stringent control of the satellite, a FSM (Fine Steering Mirror) is added to the CubeCAT. An FSM is a mirror attached to mechanical actuators to control the mirror's tip and tilt. It is used to aim the incoming laser beam on the *Quad Cell* and the outgoing beam on the ground station.

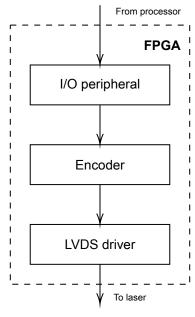

#### Laser driver

The Laser Driver is an electrical circuit designed to boost the low power data signal coming from the DMU to a signal that is able to drive the actual laser at the desired speed. In the CubeCAT system

2.3. CubeCAT 9

a LVDS signal coming from the DMU is used to drive a laser at a maximum of 2.5 Gb/s for the first iteration.

#### 2.3.2. Coding scheme

A is noted by Goal C a Forward Error Correction is needed to ensure robust communication. Different coding schemes can have different implications on the data rate, received BER (Bit Error Rate), and coding overhead. The decision for a coding scheme should fit with the intended application, otherwise the performance might be lower than is possible. In [18] can be read that choosing for one standard introduces a coding overhead of a factor 8.00, for a reparability of 25.00% of its input data (HPE-TC). If the link introduces little error then a coding scheme with an overhead of 3.78 and a reparability of 16.7% (HPE-TM) might be more suitable and doubles the achievable bandwidth for a link.

This section will briefly discuss three different coding schemes that were considered during the project, focussing on the reason it was considered, the design of the scheme, and if applicable, the reason it was changed in favour of another scheme.

#### CCSDS 131.0b3

During the early stages of the CubeCAT project in 2018 there where no standards for optical space communication. What was already available for space communication was the CCSDS 131.0b3 standard *TM Synchronization and Channel Coding*.

The standard was developed with radio communication in mind and contains a multitude of options for use in different scenarios as can be seen in Figure 2.3.

Figure 2.3: CCSDS 131.0b3 overview

Optical communication has extra challenges that are not covered by the 131 standard. With the discovery of the concept version of the 142 standard, the 131 standard was dropped in favour of the 142 standard.

#### CCSDS 142.0b1

First discovered as the concept version (CCSDS 142.0r1) the 142.0b1 standard was found to be more suitable for the challenge of optical communication. It is designed for a high-photon efficiency optical link and compared to the 131 standard adds a *channel interleaver* and a *PPM symbol mapper* as can be seen in Figure 2.4.

10 2. Background

Figure 2.4: CCSDS 142.0b1 overview

The *channel interleaver* reorders the data stream in time, such that the data is communicated in a different order. This has as a consequence that a fade in the signal or a temporary loss of signal results in errors in multiple packets instead of the loss of packets. With the used error correction these erroneous packets can then be repaired.

A *PPM symbol mapper* places bits in transmission time slots, changing the detection method from '0' or '1' per instant to the time slot it was most likely received in.

The biggest problem of this standard was the lack of throughput. This is due to the fact that the standard has been designed with deep-space (long distance) communication in mind, whereas a CubeCAT terminal would be placed in LEO and communicate with a ground station (relatively short distance).

During discussions with TNO it became apparent another standard, the O3k standard, was in development. The O3k standard focusses on high-speed optical LEO links, matching exactly the purpose of CubeCAT.

The O3k standard was unfortunately, at the time of writing, only available in private communication in the working group. TNO has people in this working group and it was decided to move to self-made variant of the O3k standard; the TNO3k standard.

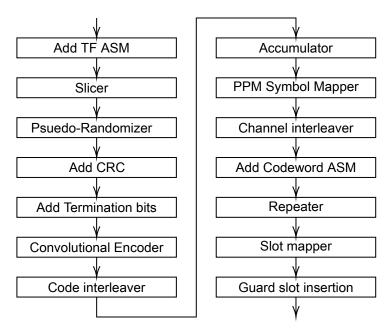

The efforts made on the 142 standard before the switch to the TNO3k standard can be found in Appendix A.

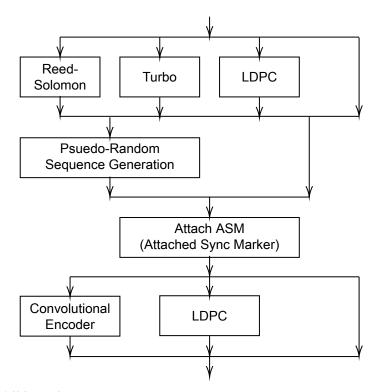

#### TNO3k

The CCSDS has a working group focussed on the development of the O3k standard. This standard focusses on 10 Gb/s (or divided by  $2^N$ ) optical LEO links, including LEO-to-ground links. With the development of the standard still in progress at the time of writing, the decision was made by TNO and Hyperion to make a variant on the standard with the CubeCAT system in mind: the TNO3k standard[19] (the name doesn't mention Hyperion due to the perfect match with the TNO name).

The base of the O3k standard, the Forward Error Correction, is the biggest discussion of the standard. Multiple parties, such as NASA, ESA and DLR each propose a different FEC scheme. These include Reed Solomon, Turbo coding, LDPC, and a variant on Turbo coding, with different parameters.

At the time of writing the TNO3k standard, the timeline for the first demonstration mission of Cube-CAT was short. The amount of work that needed to be done, both at the CubeCAT side, as well as the ground station (the place of the decoder), was still significant. It was therefore decided to implement Reed-Solomon for Forward Error Correction due to its relative simple implementation for the decoder.

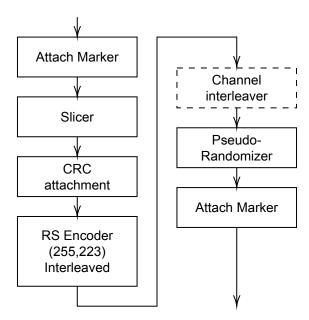

The functional structure of the encoder is quite similar to the 142 standard, without the PPM-modulation and repeater as can be seen in Figure 2.5.

2.4. Related work

Figure 2.5: TNO3k overview

#### 2.4. Related work

In the industry there are multiple initiatives for the development of a Laser Communication Terminal. These terminals can be split up based on their market as Non-CubeSat and CubeSat. This section lists those terminals in their respective market, but starts of with related work done on the CubeCAT.

#### 2.4.1. CubeCAT work

On the 6th of July 2018 D.G. Bakker defended his thesis on the topic of *A Lasercom terminal for CubeSats*[20]. His thesis describes the architecture of the Laser Communication Terminal, with a focus on the quad cell receiver. His thesis was done at Hyperion, providing the fundamentals of the CubeCAT.

#### 2.4.2. Non-CubeSat

CubeCAT is intended for the CubeSat market. However, on bigger satellites there is also work done on the subject of laser communication. A subset of this work is listed here.

#### AlphaSat TDP1

In 2007 ESA published an article [21] about the AlphaSat satellite in which the Inmarsat "Geomobile" Mission was explained. The satellite has four technology demonstration platforms, of which one is a Low-Earth Orbit (LEO) to Geosynchronous Equatorial Orbit (GEO) LCT (Laser Communication Terminal). With this LCT ESA aimed to achieve high data throughput of up to 1.8 Gb/s[22], with a reduced latency [3]. This Laser Communication Terminal has been used as a basis for the *SpaceDataHigh-Way*. Compared to CubeCAT this module achieves a higher throughput and achieves it over a longer distance, since a LEO to GEO link is over 30000 km.

#### SpaceDataHighWay

In the ESA LCT article a collaboration between ESA, Airbus, TESAT-Spacecom and DLR was announced. This collaboration envisioned a *SpaceDataHighway* built upon laser communication to provide time-critical data at a low latency to Earth. Under the Copernicus project of ESA, satellites collect information about Earth. The Sentinels 1 and 2 developed under this project are equipped with an LCT that can make use of the *SpaceDataHighway*. The EDRS-series satellites relay the data coming from the Sentinels back to earth at data rates of 1.8 Gb/s[23]. With links over 40000 km[24] the *SpaceDataHighway* is focussing on a different application than CubeCAT. At this distance the throughput goes up to 1.8 Gb/s, meaning it is also faster than CubeCAT.

#### TerraSAR-X

In the same year DLR also demonstrated an inter-satellite optical link and a satellite to ground optical link [25] on the TerraSAR-X Earth Observation satellite. The module has mechanisms for fine pointing,

12 2. Background

course pointing, and has a telescope. Furthermore, the module uses a base plate of 50 cm by 50 cm[26]. During a link of about 8 minutes a peak data rate of 5.6 Gb/s was achieved for a LEO to LEO link[26] using , on average, 35 watts of power. Compared to the CubeCAT it is faster, requires more power, and is significantly bigger.

#### 10 Gb/s future mission

In 2012 NASA stated that for future Earth observation missions a downlink capability of 1 to 9 Gb/s is needed. H. Hemmati and J.M. Kovalik of the Jet Propulsion Laboratory of California Institute of Technology are designing and validating an LCT that is capable of 10 Gb/s[27]. This LCT is intended for use in LEO to ground links. Unfortunately it is unknown to the writer of this thesis what this technology developed into.

#### BiROS: OSIRISv2

The BiROS satellite is a satellite optimized for fire detection, flying at an altitude of around 500 km[28]. One of the modules used on the satellite is an LCT, the OSIRISv2[29]. This LCT is aimed to work at 1 Gb/s with an uplink channel of 1 Mb/s. The LCT also features a *Quad Cell* and uses a beacon for alignment.

In the latest update of the OSIRIS program the satellite has been launched, but the OSIRISv2 payload has not been tested yet[30]. The module works at 37 watts, which is more than double the amount of CubeCAT. In functionality it is comparable to CubeCAT, meaning that CubeCAT might compete with the OSIRISv2 for its reduced power requirement.

#### 2.4.3. CubeSats

The intended market for the CubeCAT is the CubeSat market. Other than CubeCAT there are more LCTs in development. A subset is given here.

#### Nice<sup>3</sup> (The Nice Cube)

The Nice<sup>3</sup> is a project of the Université Côte d'Azur that aims to create an LCT, while keeping the satellite as a whole in a 1U CubeSat format. With this LCT a transmission rate of 1+ Kb/s)[31] is envisioned. Due to the size requirements of the Nice<sup>3</sup> satellite, it has less space for the LCT. This results in a limited transmission rate compared to CubeCAT.

#### Sinclair Interplanetary

Sinclair Interplanetary is working on a Laser Communication Terminal for full-duplex communication between satellites at a rate of 100 Mb/s, with a maximum distance of 250 km[32]. Operating the terminal is done at less than 10 W with a volume of the terminal that is less than 1U. Another Laser Communication Terminal Sinclair is working on is designed for downlinking data at a rate of 1 Gb/s at 1000 km[32]. This terminal is also designed to operate at less than 10 W and requires less than 1U volume. Compared to CubeCAT, Sinclair has a relative competitive 1 Gb/s terminal. Sinclairs terminal requires less space and power, but lacks any form of encoding, storage, or tracking capabilities.

#### MIT: CLICK B

The Click B[33] is a university Laser Communication Terminal that aims to provide full duplex 20+ Mb/s for links between 25 km to 580 km. With a peak power requirement of 40 W and a size of 1.5 U it can be used for CubeSats. Compared to CubeCAT it requires more power and space, to provide less bandwidth.

#### **CubeLCT**

Tesat-Spacecom has a Laser Communication Terminal that is capable of a 100 Mb/s downlink [34] and aims to achieve 1 Gb/s[35]. With only 0.3U it is designed to be able to communicate over a maximum distance of 1500 km. For this it requires at maximum 10 watts of power and uses a beacon and a FSM for alignment. As encoding the CCSDS 03k standard will be implemented. Compared to CubeCAT it lacks the ability to store data.

2.5. Conclusion 13

#### 2.5. Conclusion

With a 1 unit (1U) Laser Communication Terminal, CubeCAT focusses on the CubeSat industry. This industry faces the challenge to protect the hardware against the effects of thermal differences, Single Event Latchup, Single Event Upset and Total Ionizing Dose. After two iterations of coding schemes the TNO3k standard will be used for the CubeCAT to ensure robust communication.

Multiple cases on bigger satellites that have already proved the optical laser communication technology are already on the market. In the SmallSat subset of the market Tesat-Spacecom has the *CubeLCT* that is capable of 100 Mb/s in a 0.3 U size and Sinclair is working on an 1U 1 Gb/s terminal. Other terminals are mostly university projects.

## **Data Management Unit**

This chapter discusses the design of the DMU (Data Management Unit) to effectuate the high-speed digital data path. Here, multiple options for the design are discussed, as well as responsibilities, of the DMU. The options are used to select a design, effectively achieving Goal A.

Before reading this chapter the reader is expected to have read Section 2.2 about hardware in space and Section 2.3 about the CubeCAT project and the role of the DMU in the CubeCAT module.

This chapter is organised by first discussing the responsibilities of the DMU in Section 3.1. After that the design options for the DMU are discussed, differentiating between the architecture, interconnections and the components, which can be found in Section 3.2. In Section 3.3 three different designs are presented that were the options during the project. In Section 3.4 the subsystem responsibilities are further detailed, based on the selected design. A conclusion can be found in Section 3.5.

#### 3.1. Responsibilities

This section discusses the responsibilities of the DMU by looking into the interfaces the DMU has in the CubeCAT system, followed by further detailing the tasks the DMU is responsible for. Lastly, these responsibilities are condensed into requirements. These requirements are then, later in this chapter, used to base the design choices on.

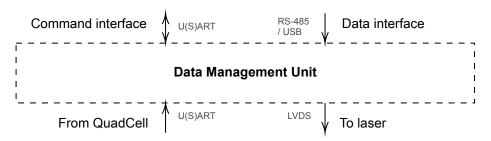

#### 3.1.1. System interfaces

As was seen in Figure 2.2 the DMU is responsible for interfacing with the satellite. This includes both handling the data coming from the satellite as well as handling the commands coming from it. The data interface is either a RS-485 connection or an USB connection. A command interface is provided by re-using the data interface or a simple U(S)ART connection.

Furthermore, the *Quad Cell* interfaces with the DMU, providing sensor data meant for logging. This connection is a U(S)ART connection. A data path to the ground station is provided via the connection to the *Laser Driver*. The *Laser Driver* amplifies an incoming LVDS signal, meaning that the DMU should output an LVDS signal. The interfaces are summarized in Figure 3.1.

Figure 3.1: Data Management Unit interfaces

#### 3.1.2. Tasks

In the CubeCAT the DMU has multiple tasks to ensure the correct operation of CubeCAT as a system. These tasks can be grouped in three main tasks, namely:

- **Data aggregation**: The DMU is responsible for storing the data from the data interface. It is also responsible for logging sensor data.

- Data encoding: To reduce data corruption during transmission the CubeCAT system should encode the data coming from the satellite. The DMU is responsible for encoding this data according to the TNO3k standard.

- **Data output**: Upon establishment of an optical link the CubeCAT system should start sending data to the ground station. The stored data should be sent to the *Laser Driver* in a non-interrupt data stream at a 100 Mb/s rate for the first iteration of CubeCAT. Later iterations/ updates should stream at a 500 Mb/s, 1 Gb/s or 10 Gb/s rate.

Both Data encoding and Data outputting are needed for the high-speed data path.

#### 3.1.3. Requirements

The DMU needs to interface with the rest of the system of CubeCAT, as well as fulfil its own tasks within CubeCAT. Besides, it should fit with the rest of the CubeCAT in 1U and it should not draw too much power. As such, there are requirements for the design of the DMU. These are defined in Table 3.1.

| Table 3.1: Data Management Unit requirements. | <ol> <li>The Importance column</li> </ol> | specifies the import | ance for the CubeCAT project. |

|-----------------------------------------------|-------------------------------------------|----------------------|-------------------------------|

|                                               |                                           |                      |                               |

| Requirement         | Importance  | Description                                                 |

|---------------------|-------------|-------------------------------------------------------------|

| Time                | Medium      | The DMU should be finished before September 2020.           |

| Power               | Medium      | The DMU power should remain under 2 watts.                  |

| Size                | High        | The DMU PCB should fit in a 8 cm by 8 cm area.              |

| RS-485              | High        | The DMU should be able to interface with RS-485.            |

| USB                 | High        | The DMU should be able to interface with USB.               |

| Quad Cell inter-    | High        | The DMU should be able to interface with the Quad Cell with |

| face                |             | U(S)ART.                                                    |

| Satellite interface | High        | The DMU should be able to process U(S)ART commands from     |

|                     |             | the satellite.                                              |

| Storage             | High        | The DMU should be able to store data.                       |

| TNO3k encoding      | High        | The DMU should encode the data according to the TNO3k       |

|                     |             | standard.                                                   |

| 3 ms channel in-    | Low         | The TNO3k encoder should have a channel interleaver depth   |

| terleaver           |             | interleaving 3 ms of data.                                  |

| 100 ms channel      | Low         | The TNO3k encoder should have a channel interleaver depth   |

| interleaver         |             | interleaving 100 ms of data.                                |

| 300 ms channel      | Low         | The TNO3k encoder should have a channel interleaver depth   |

| interleaver         |             | interleaving 300 ms of data.                                |

| 100 Mb/s speed      | High        | The DMU should be able to output data at a steady 100 Mb/s. |

| 500 Mb/s speed      | Medium-High | The DMU should be able to output data at a steady 500 Mb/s. |

| 1 Gb/s speed        | Medium      | The DMU should be able to output data at a steady 1 Gb/s.   |

| 10 Gb/s speed       | Future      | The DMU should be able to output data at a steady 10 Gb/s.  |

| Hardware            | High        | The DMU hardware should be capable of meeting Require-      |

|                     |             | ment '1 Gb/s speed' and Requirement '3 ms channel inter-    |

|                     |             | leaver '.                                                   |

| LVDS                | High        | The DMU output should be LVDS.                              |

#### 3.2. Design options

This section discusses the design options for the DMU. It starts by discussing the different possible architectures. This is followed by discussing the possible interconnections needed to support some

3.2. Design options

architectures. Lastly, components are listed that would support the required functionality as well as to be able to survive in LEO.

### 3.2.1. Architecture

With different architectures come different advantages and disadvantages. For example, an architecture could allow for a more flexible swap of components during the project when issues are found with that component. Another architecture would require to redo all the work with that component, causing a set-back in time. With Requirement 'Time' in mind, it is thus nessacary to explore different architectures.

An important element in all architectures is the use of extra memory to support Requirement '3 ms channel interleaver' due to Requirement 'Hardware'. Calculated from Requirement '3 ms channel interleaver' and Requirement '1 Gb/s speed' a memory of at least 300 Mbit is needed. To support Requirement '100 ms channel interleaver' and Requirement '300 ms channel interleaver' at least respectively 1 Gbit or 3 Gbit is needed.

In this subsection the following architectures will be explored. First a microcontroller with an LVDS interface will be discussed, followed by a discussion of a microcontroller with an FPGA. Then a microprocessor with an FPGA is explored. Lastly, an architecture with only an FPGA is discussed.

#### Microcontroller with LVDS interface

Interfacing with the satellite can be handled by a microcontroller. They allow for deterministic program flows, at relatively low power. Regarding I/O microcontrollers are flexible and can emulate digital interfaces they don't have peripherals for. For the LVDS interface a converter is needed, or special microcontrollers need to be used. The memory for the *Channel Interleaver* is connected to the microcontroller, as well as the storage.

On the other hand, micro controllers are limited in speed, with, for example, simple ARM M0 cores working at (not limited to) 48 MHz and more advanced M7 cores working at (not limited to) 480 MHz, with instruction- and data cache and 64-bit floating point support. Operation at 1 Gb/s of the laser will be challenging with the I/O handling overhead, the encoding, storage handling and incoming data from the QuadCell.

An overview of this architecture can be seen in Figure 3.2.

Figure 3.2: Microcontroller LVDS bridge interface architecture

#### Microcontroller with FPGA

As with the *Microcontroller with LVDS interface*, the microcontroller can implement the interfacing with the satellite and the QuadCell. Interfacing with the laser is handled by the LVDS driver of an FPGA, as this interface is quite common on FPGAs. Optionally, the data interface can be connected directly to the FPGA, reducing overhead in the microcontroller. With this option the data can also be stored directly by the FPGA, because it is connected with the storage. Encoding the data can be done efficiently at the FPGA, reducing the load on the microcontroller as well. This requires the FPGA to also interface with the memory to support the *Channel Interleaver*.

A downside of this configuration is the effort needed on the FPGA side to implement all drivers and logic in-between the drivers. The storage driver will need to interface with the memory, deal with delays and needs to be able to recover state between power cycles. This can be offloaded by the microcontroller, which commands for data movements and loads the state of the storage. Another disadvantage of using an FPGA is the increased power consumption. It does however allow for faster operation.

An overview of the architecture can be seen in Figure 3.3.

Figure 3.3: Microcontroller with an FPGA architecture

#### Microprocessor with FPGA

Replacing the microcontroller with a microprocessor enables the use of Linux, instead of writing baremetal software. Drivers for the processors peripherals are written and tested, shifting the focus to data handling rather than implementation. Besides, peripherals for high-speed data storage are available and their drivers are ready to use, making attaching or swapping storage only a physical effort. With the increased possibilities of a microprocessor the power consumption can increase, that is, if those possibilities are used.

The FPGA will then still do the TNO3k encoding of the data and drive the LVDS signal. This means that the effort on the FPGA part is the same as with the microcontroller.

The downside of this configuration is that the use of an OS like Linux obstructs (near) real-time handling of commands, leading to potential problems that are timing related. Using an real-time OS would improve this, but would require more focus on the drivers and the program flow.

An overview of the architecture can be seen in Figure 3.4.

Figure 3.4: Microprocessor with an FPGA architecture

3.2. Design options

#### Only FPGA

Another architecture that can be used only using an FPGA that interfaces directly with the satellite. This solution can be the most efficient implementation in terms of speed and responsiveness, as all operations are in hardware. However, this architecture comes at the highest development effort, as both the command interface and the *Quad Cell* interface need to be handled by the FPGA.

An overview of the architecture can be seen in Figure 3.5.

Figure 3.5: FPGA only architecture

#### Architecture decision matrix

Based on the architectures discussed before a choice table has been made. This table gives an overview of the implications on *power*, *speed*, *design effort*, *size* and *expandability* of the different architectures relative to each other. The overview can be seen in Table 3.2.

| Parameter     | Microcontroller with LVDS controller | Microcontroller with FPGA | Microprocessor with FPGA | FPGA<br>only |

|---------------|--------------------------------------|---------------------------|--------------------------|--------------|

| Power         | Low                                  | Medium                    | Medium-High              | Medium       |

| Speed         | Low                                  | Medium                    | High                     | High         |

| Design effort | Low                                  | High                      | Medium                   | High         |

| Size          | Low                                  | Medium                    | High                     | Medium       |

| Expandability | Low                                  | Medium                    | High                     | Medium       |

From this table can be seen that the choice of architecture depends on multiple factors; there is no one solution that fits them all. Choosing an architecture depends on the power available, desired speed, maximum size allowed, expandability desired and how much time is available to design and implement the architecture.

#### 3.2.2. Interconnection

The *Microcontroller with FPGA* and the *Microprocessor with FPGA* architectures require communication with an FPGA. This communication can be realized by different protocols, resulting in different speeds and implementation complexity.

In this subsection the following protocols will be discussed: SPI, SD, QSPI, EBI, USB and PCIe. Focus will be put on the relative speed, but also on the design effort for Requirement 'Time', upgradability for Requirement 'Hardware' and the amount of traces for Requirement 'Size'.

#### SP

SPI is used for many interfaces, such as in an accelerometer, ADC, gyroscope or flash memory for which the industry has developed the SPI-NOR standard. The SPI protocol is duplex and uses four

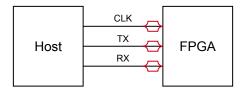

traces: one clock line (SCLK), one chip select (NCS), one line to the slave and one line from the slave. This can be seen in Figure 3.6 as well.

Figure 3.6: SPI connection

With the data rate directly related to the clock speed of SCLK, the data rate can get as high as the clock speed can. This clock rate usually starts around 1 MHz and can go up to 250 MHz on for example a Raspberry Pi 3, as this maximum is defined by the peripheral bus. On boards that have higher peripheral bus speeds, the speed can be increased even further to 400 MHz. With this in mind Requirement '100 Mb/s speed' can be met with SPI, but Requirement '500 Mb/s speed' will be hard as transmission line effects start to get into play at higher frequencies. Switching from SDR to DDR for SPI doubles the data throughput, but will still not reach the 1 Gb/s for Requirement '1 Gb/s speed', but 500 Mb/s for Requirement '500 Mb/s speed' should be reachable.

As SPI is a common standard its design complexity is low; a SPI peripheral can be found on many devices. Since the only way to upgrade the speeds is to increase the clock frequency, it is not quite upgradable.

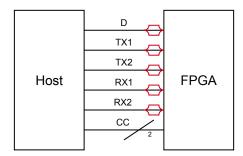

#### SD

SD is a common storage interface that can be found on phones, mp3 players, dashcams and many other types of devices. With the increasing demand for faster SD-cards, the SD Association has developed multiple iterations on the standard. The original standard starts with a bus speed of 100 Mb/s and with the latest iteration (8.00) the speeds goes up to 3940 Mbyte/s using PCle[36]. To enable these fast bus speeds LVDS pins were added to SD interfaces. Ignoring these extra pins for Requirement 'Hardware', the SD interface can go up to 104 Mbyte/s.

The layout of an SD interface without LVDS pins is as follows. There is a clock line to sync the data on (CLK). Then there is a line to signal commands to the slave and for data there are four lines available. A visualisation of an SD connection can be seen in Figure 3.7. An SD interface with LVDS pins would add two differential pairs.

Figure 3.7: SD connection

A lot of microprocessor/microcontroller manufacturers include an SD peripheral in their products, easing the connection to this kind of storage. For an FPGA there are open source designs available such as [37]. The problem with the SD standard for upgradability is that its bus protocol changes for increased speeds, meaning that per iteration a significant design effort has to be made.

#### **QSPI**

Based on the SPI standard, QSPI extends the amount of lines with two extra generic IO lines and repurposes the MISO and MOSI lines to generic IO lines, totalling to four (Quad) IO lines. With these extra lines and as basis the SPI standard the bus throughput is 4 times as big. For reference, using the Raspberry Pi 3 SPI clock speed a bus throughput of 1 Gb/s is possible on SDR. The QSPI connection is visualized in Figure 3.8.

3.2. Design options

Figure 3.8: QSPI connection

The QSPI interface is mostly used as an extension of the SPI-NOR standard. QSPI peripherals used in microcontrollers/microprocessors might implement the command structure of the SPI-NOR standard, requiring the FPGA implementation to also work according to this command structure. This increases the design complexity, but with the basis of SPI it is still a reasonable effort.

Compared to SPI it inherits the same issues for the upgradability. Only the clock frequency can be increased if DDR is already implemented.

#### EBI

An EBI (External Bus Interface) can be implemented in a microcontroller/microprocessor to expose the internal peripheral interconnection and utilize the available infrastructure in the chip to increase the possible bandwidth with devices connected on this bus. It consists of a clock line (MCK), multiple addressing lines (A), multiple data lines (D) and five control lines. These control lines include a chip select (ME), a read enable (RE), a write enable (WE), a lower byte enable (LBE) and a high byte enable (HBE). These lines are visualized in Figure 3.9. If needed, multiple address lines can be ignored as the data handled by the FPGA will not work with addresses.

Figure 3.9: EBI connection

Due to the amount of data lines it is possible to send multiple bytes per clock. With 16 data lines working at 100 MHz a data throughput of 1.6 Gb/s is possible, meeting Requirement '1 Gb/s speed'. Implementing this interface is, however, harder due to the fact that it is less popular and thus the available examples are scarce. Besides, with 16 lanes for data extra care needs to be taken to ensure all signals are in phase. The upgradability of this interface has the same issues as SPI. As the amount of lanes are set, the speed can only be further increased by increasing the clock speed.

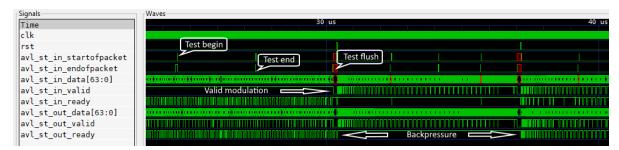

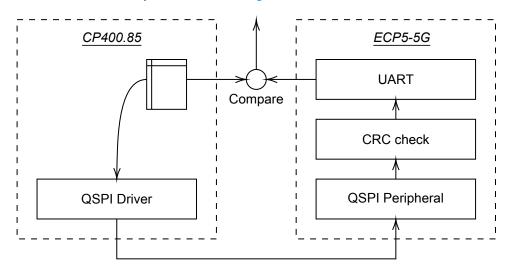

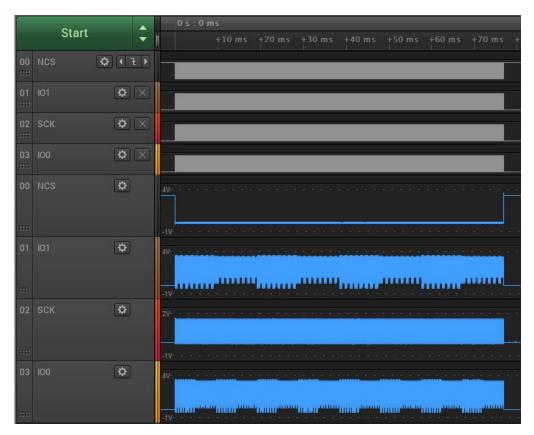

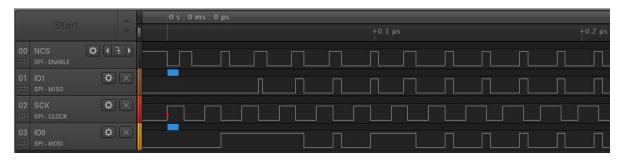

# **USB**