# qRV32

RISC-V 32-bit instruction set extension to address the control of diamond qubits

Master's Thesis Report Jacopo Costantini

## RISC-V 32-bit instruction set extension to address the control of diamond qubits

by

Jacopo Costantini

To obtain the degree of Master of Science at the Delft University of Technology. To be defended publicly on Thursday, August 24th, at 1.30 PM

Student number:5610893Project Duration:September 2022 - July 2023Thesis committee:Prof. dr. ir. J.S.S.M. Wong<br/>Dr. ir. F. SebastianoTU Delft, supervisor<br/>Tu Delft, QuTech

An electronic version of this thesis is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

Cover: Dall-E generated picture

### Preface

This work is the end of my academic journey, at least for now. Five years of struggles and happy moments that changed completely who I am.

During this project, I had the luck to work with amazing people, like Stephan Wong, Matti Dreef, and Folkert de Ronde. I wish you all the best.

Most importantly, I would like to thank my family, which has always made sacrifices for me, and my friends, that have supported me.

Jacopo Costantini Delft, August 2023

### Abstract

RISC-V is an open-source Instruction Set Architecture that offers a simple, modular, and scalable design. Its extensions allow for customization and optimization based on specific execution workloads. One of these workloads could be quantum computing, which exploits the concepts of superposition and entanglement to manipulate qubits and perform computations that would be infeasible for classical computers. The customization offered by RISC-V presents a remarkable opportunity to develop specialized architectures that can efficiently address the execution of quantum algorithms, bridging the gap between classical and quantum computation.

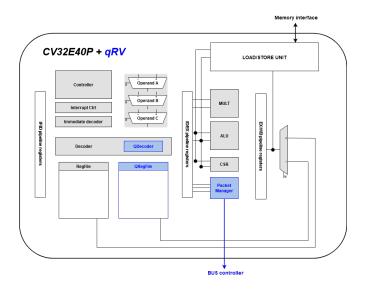

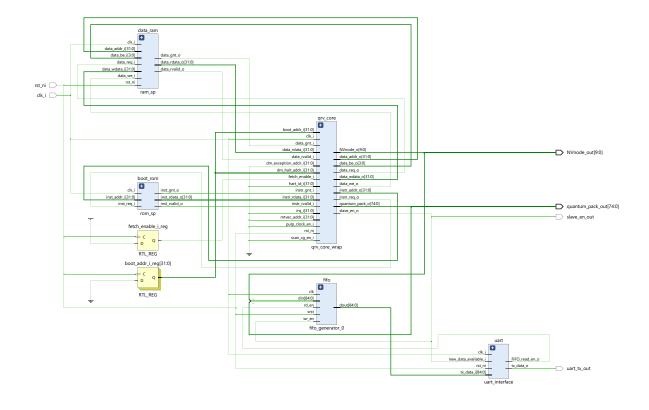

In this thesis work, a RISC-V 32-bit instruction set extension called qRV32 is developed to address the control of diamond qubits, based on an existing QISA. The architecture defines the encoding syntax for the machine-level instructions and the exchange protocol for control and data in the system. Accordingly to this specification, the hardware of a control core processing the ISE has been designed. Custom functional units and necessary peripherals have been added to the base core CV32E40P in order to implement the desired control functionalities.

The thesis also proposed additional work to ease the complete design and functionality of the system. In particular, an assembler targeting qRV32 has been developed, enabling the automated translation of assembly instructions to machine-level code. Furthermore, an experimental model is developed to evaluate the parallelism of the system.

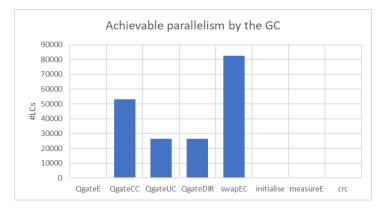

The resulting architecture is eventually tested and evaluated. Software simulations are used to test the functionality of the control core and the custom components. Eventually, a simplified version of the model is used to estimate the parallelism of the core, which can control 23605 network nodes when operating at  $f_{clk} = 55MHz$ .

### Contents

| Pr | eface                             | i i                                                                                                                                                                                                                             |

|----|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ab | strac                             | it ii                                                                                                                                                                                                                           |

| 1  | Intro<br>1.1<br>1.2<br>1.3<br>1.4 | Deduction       1         Thesis Project       1         Research Question       1         Methodology       2         Report Overview       2                                                                                  |

| 2  | 2.1                               | kground information3Quantum Information Theory32.1.1 Quantum bit32.1.2 Quantum gates42.1.3 Qubits operations5                                                                                                                   |

|    | 2.2                               | NV Center Quantum Computers         5           2.2.1         Qubits         6           2.2.2         Analog control         6           2.2.3         Digital control         6                                               |

|    | 2.3                               | RISC-V Instruction Set Architecture       7         2.3.1 History of RISC-V       7         2.3.2 Characteristics       8                                                                                                       |

|    | 2.4                               | Conclusion                                                                                                                                                                                                                      |

| 3  | Mod<br>3.1<br>3.2<br>3.3<br>3.4   | leling the Control Plane9Instruction Execution93.1.1 Flowchart93.1.2 Profiling10Time Diagrams113.2.1 Ideal case113.2.2 Accounting for processing123.2.3 Accounting for communication13Model definition14Conclusion15            |

| 4  | <b>qRV</b><br>4.1<br>4.2<br>4.3   | 32 Instruction Set Extension16RISC-V Extensions16Diamond QISA17qRV32 Instruction Set Extension174.3.1 Instructions encoding184.3.2 Communication with LCs21Conclusion22                                                         |

| 5  | Harc                              | dware Implementation 24                                                                                                                                                                                                         |

|    | 5.1<br>5.2                        | 32-bit RISC-V Cores Survey       24         5.1.1 Comparison       25         Global Controller Design       26         5.2.1 ISE Execution       27         5.2.2 Architecture       27         5.2.3 GD/202 Evention       27 |

|    | 5.3                               | 5.2.3       qRV32 Functional Units       28         System on Chip Design       30         5.3.1       System Memory       30                                                                                                   |

|    | 5.4               | 5.3.2       UART                                                                                                                                                                                                                                                                          | 31<br>31<br>31<br>32                         |

|----|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 6  | 6.1<br>6.2<br>6.3 | <b>32 Assembler</b> Assembly-level instructions analysis         Development steps         6.2.1 Opcode Identification         6.2.2 Pseudo-instructions Substitution         6.2.3 Register Management         6.2.4 Parameters Translation         Assembler outputs         Conclusion | 34<br>35<br>35<br>35<br>35<br>36<br>36<br>37 |

| 7  | 7.1               | ults and Discussion         Software Simulations         Model evaluations         Conclusion                                                                                                                                                                                             | <b>38</b><br>38<br>39<br>40                  |

| 8  | 8.1<br>8.2        | clusion         Summary         Main contributions         Future work                                                                                                                                                                                                                    | <b>41</b><br>41<br>42<br>42                  |

| Re | feren             | nces                                                                                                                                                                                                                                                                                      | 44                                           |

| Α  | QISA              | A Instructions                                                                                                                                                                                                                                                                            | 47                                           |

| В  | B.1<br>B.2        | qRV32 Encoding Tables                                                                                                                                                                                                                                                                     | <b>49</b><br>49<br>50<br>53                  |

| С  | C.1<br>C.2        | & SoC HDL design           Global Controller           System on Chip           C.2.1 Sytem Memory           C.2.2 UART                                                                                                                                                                   | <b>54</b><br>54<br>64<br>65<br>67            |

| D  | Asse              | embler code                                                                                                                                                                                                                                                                               | 77                                           |

| Е  | Simu              | ulation Results                                                                                                                                                                                                                                                                           | 84                                           |

### Introduction

Quantum computing, a revolutionary field of study at the intersection of physics and computer science, has garnered significant attention and excitement in recent years. Unlike classical computers that operate based on bits, quantum computers harness the fundamental principles of quantum mechanics to process information using quantum bits, or *qubits*.

The journey of quantum computing can be traced back to the early 1980s when physicist Richard Feynman envisioned the possibility of harnessing quantum systems to perform calculations more efficiently than classical computers [17]. In the mid-1990s, Peter Shor developed a groundbreaking quantum algorithm for integer factorization [41], highlighting the immense computational advantage of quantum computers in certain areas, such as cryptography. In 1998, Isaac Chuang and Neil Gershenfeld at the IBM Almaden Research Center demonstrated the first 2-qubit quantum computer [7]. IBM's 127-qubit Eagle [23], Rigetti's 80-qubit Aspen-M-2 [8], and Google's 53-qubits Sycamore [27] are the three most advanced quantum computers currently available.

### 1.1. Thesis Project

Despite the fact that these computers employ qubits to perform quantum operations, control electronics play a vital role in manipulating and maintaining the delicate quantum states, ensuring coherence and enabling complex quantum operations. A collection of analog-operating classical electronics, such as lasers and microwave generators, and a layer of digital control logic, that manages the electronics, need to be included in a quantum computer.

This thesis project aims to build a **prototype of the global control electronics** required by diamondbased quantum computers, guaranteeing flexibility through the use of an instruction-set architecture (ISA) that captures the actions of the digital controller without putting any restrictions on the underlying hardware. To ensure compatibility with the most cutting-edge open hardware currently on the market, the Global Controller (GC) control core was chosen to be implemented as a **RISC-V** 32-bit core.

### **1.2. Research Question**

The research question can be formulated as the following:

### Can the control of a diamond-based quantum computer be addressed using the inherent extendable architecture structure of the RISC-V ISA?

In order to answer the question, the following goals in the development of the global controller have been set:

- 1. Define custom RISC-V instructions based on the available Quantum ISA (QISA)

- 2. Define a communication protocol between GC and the rest of the control plane

- 3. Implement Functional Units to address the execution the said instructions

### 1.3. Methodology

A number of actions must be carried out in order to accomplish the objectives. This will guarantee a thorough understanding of the functionality of quantum computers based on diamond NV qubits, which the core must control, and of the scalability of the RISC-V ISA, which the core will implement.

### 1. Understanding of the existing system definition and requirements

A control plane has already been initially defined. At the moment of starting the thesis, a system simulator and a compiler to address the Global Controller have been developed.

- Profiling of the existing QISA and creation of RISC-V-compliant encoding QISA instructions, defined at assembly-level, model the operations to be performed by the quantum computer. They are then mapped to machine-level following the RISC-V guidelines.

- Design and implementation of the Global Controller core and SoC From an existing RV 32-bit core, functional units and communication interface must be designed to create the GC hardware.

- Development of a custom assembler

An assembler must be developed to translate the outputs of the compiler into the novel qRV32 ISA format.

- Design validation and evaluation Simulations must be used to verify the design of the controller. Its control ability are then evaluated.

### 1.4. Report Overview

The structure of this thesis is now presented. Chapter 2 delves into Quantum Information Theory, NV Center Quantum Computers, and the RISC-V Instruction Set Architecture, providing crucial background knowledge to support our research. Transitioning to Chapter 3, our focus shifts to the modeling of the control plane, where we thoroughly explore the concept of parallelism. Advancing further, Chapter 4 takes a closer look at the qRV32 Instruction Set Extension. As we proceed to Chapter 5, we showcase the hardware implementation, which includes conducting a survey of 32-bit RISC-V cores, designing the Global Controller and the System on Chip. Within Chapter 6, we delve into the intricacies of the qRV32 Assembler and the development steps involved. Subsequently, Chapter 7 unfolds the results, encompassing software simulations and model evaluations. Ultimately, Chapter 8 brings the thesis to a conclusion, summarizing key findings and presenting potential future research directions.

$\sum$

### **Background information**

The ideas of quantum computing and qubits were introduced in the preceding chapter, along with a mention of the system specification of the quantum computer stack. Given that they are essential for fully comprehending the thesis work, these topics are presented in this chapter.

Section 2.1 presents an overview of Quantum Information Theory. Section 2.2 focuses on NV center quantum computers, discussing their fundamental principles and the analog (Sec.2.2.2) and digital (Sec.2.2.3) control required. Eventually, Section 2.3 delves into the essential aspects of RISC-V, including its features and properties.

### 2.1. Quantum Information Theory

Quantum information theory investigates the principles and limitations of transmitting classical and quantum information over quantum channels, utilizing concepts from quantum mechanics and information theory to develop advanced communication protocols and quantum technologies [14].

A brief review of quantum information theory will be provided in this section. It will introduce quantum bits (qubits) and describe how they differ from conventional bits. The definition of Diamond Quantum Computers and their purpose will also be covered in this section. The notions of quantum algorithms and quantum gates will be introduced at the end of the section.

### 2.1.1. Quantum bit

Qubits, the fundamental units of quantum information, lie at the heart of quantum computing. In contrast to traditional bits, which represent information as either 0 or 1, qubits exploit the principles of quantum mechanics to exist in a linear superposition of states [26]. Qubits are represented by the *braket* notation, introduced by P. Dirac and commonly used in quantum mechanics.

The two orthogonal states are represented as  $|0\rangle \equiv \begin{pmatrix} 1 \\ 0 \end{pmatrix}$  and  $|1\rangle \equiv \begin{pmatrix} 0 \\ 1 \end{pmatrix}$ , while a superposition

state  $\psi$  is described by Equation 2.1.

$$|\psi\rangle = \alpha|0\rangle + \beta|1\rangle \equiv \begin{pmatrix} \alpha \\ 0 \end{pmatrix} + \begin{pmatrix} 0 \\ \beta \end{pmatrix} = \begin{pmatrix} \alpha \\ \beta \end{pmatrix}$$

(2.1)

In the equation,  $\alpha$  and  $\beta$  are complex numbers called *probabilistic amplitudes* [26]. They represent the probability of the state collapsing into one of the orthogonal states of the measurement basis. In particular, during measurement, the qubit always collapses into the  $|0\rangle$  or the  $|1\rangle$  state, with probabilities  $|\alpha|^2$  and  $|\beta|^2$  respectively [26]. Consequently  $|\alpha|^2 + |\beta|^2 = 1$ .

Moreover, the state of a qubit can be visually represented using the concept of the *Bloch sphere* [6], depicted in Figure 2.1. The state of the qubit, characterized by the polar angle  $\theta \in [0, \pi]$  and the azimuthal angle  $\phi \in [0, 2\pi]$ , can be mathematically expressed by Equation 2.2.

$$|\psi\rangle = \cos\frac{\theta}{2}|0\rangle + e^{i\phi}\cos\frac{\theta}{2}|1\rangle$$

(2.2)

Figure 2.1: Bloch phere [6] of a qubit.

This visualization is particularly useful to grasp the concept of single-qubit operations, as they can be modeled as rotations along the sphere over a specified axis.

### 2.1.2. Quantum gates

Qubits are the basic unit of information in a quantum system. The manipulation of qubits states is performed by *quantum gates* (**unitary, reversible operations**) on any number of qubits. Using the vector notation, quantum gates can be represented by a matrix. These matrixes can be used to calculate the state of the qubit after the quantum gate by multiplying them with the quantum state vector, producing an output vector.

### **Single Qubits**

A Bloch vector is a unit vector  $[cos(\phi)sin(\theta), sin(\phi)sin(\theta), cos(\theta)]$  used in quantum mechanics to represent the state of a two-level quantum system, such as a qubit, on a Bloch sphere [29]. A quantum gate applied on a single qubit 'rotates' the Bloch vector at some angle along a specified axis.

For example, the commonly used **Pauli-X**, **-Y** and **-Z** gates (Figure 2.2) perform a rotation of  $\pi$  radians over the specified axis, equivalent to flipping the bit around the sphere over their respective axis [31]. The possibility for intricate and interconnected quantum computations increases as we move from the domain of single-qubit quantum gates to multiple-qubit quantum gates.

| $\begin{bmatrix} 0 & 1 \\ 1 & 0 \end{bmatrix}$ | $\begin{bmatrix} 0 & -i \\ i & 0 \end{bmatrix}$ | $\begin{bmatrix} 1 & 0 \\ 0 & -1 \end{bmatrix}$ |

|------------------------------------------------|-------------------------------------------------|-------------------------------------------------|

| (a) Pauli-X                                    | <b>(b)</b> Pauli-Y                              | <b>(c)</b> Pauli-Z                              |

Figure 2.2: Pauli-X, Pauli-Y and Pauli-Z gates matrices

### **Multiple Qubits**

While a single-qubit rotation is completely independent of any other external condition, it is also possible to create rotations based on the state of a second qubit. These multi-qubit gates are called *controlled gates*. The prototypical controlled operation is the **controlled-NOT** (Figure 2.3a), a quantum gate with two input qubits, known as the control qubit and target qubit [32].

| $\begin{bmatrix} 1 & 0 & 0 \end{bmatrix}$ | $\begin{bmatrix} 1 & 0 & 0 \end{bmatrix}$      | $\begin{bmatrix} 1 & 0 & 0 \end{bmatrix}$      |

|-------------------------------------------|------------------------------------------------|------------------------------------------------|

| 0 1 0 0                                   | 0 1 0 0                                        | 0 1 0 0                                        |

| $0 \ 0 \ 0 \ 1$                           | $\begin{bmatrix} 0 & 0 & 0 & -i \end{bmatrix}$ | $0 \ 0 \ 1 \ 0$                                |

|                                           | $\begin{bmatrix} 0 & 0 & i & 0 \end{bmatrix}$  | $\begin{bmatrix} 0 & 0 & 0 & -1 \end{bmatrix}$ |

| (a) Controlled-X                          | (b) Controlled-y                               | (c) Controlled-Z                               |

Figure 2.3: Controlled-X (CNOT), Controlled-Y and Controlled-Z gates matrices

### Entanglement

Quantum computing's fundamental qubit entanglement phenomenon is crucial to achieving computational advantages over classical systems [1]. When two or more qubits exhibit a quantum correlation that makes their states interdependent and entangled, this is referred to as entanglement.

Entangled qubits have a combined state that **can not be broken down into the individual states** of the individual qubits. The concurrence is an entanglement measure [9] of a multi-qubit state (Eq. 2.3), and it is useful as a separability criterion. The value of the concurrence  $C \in [0, 1]$  can be used to determine if two qubits are maximally entangled and can be calculated with equation 2.4. Maximal entanglement is reached when the concurrence is 1. The probability amplitudes are indicated by the parameters  $\alpha_{00}, \alpha_{01}, \alpha_{10}, \alpha_{11}$ .

$$|\psi\rangle = \alpha_{00}|00\rangle + \alpha_{01}|01\rangle + \alpha_{10}|10\rangle + \alpha_{11}|11\rangle$$

(2.3)

$$C(|\psi\rangle) \equiv 2|\alpha_{00}\alpha_{11} - \alpha_{01}\alpha_{10}| \tag{2.4}$$

In particular, characteristics of a maximally entangled state, such as  $|\psi\rangle = |01\rangle + |10\rangle$ , include nonlocality, which allows measurements on one qubit to instantly change the state of another, regardless of their spatial separation. In fact, measuring the first qubit will cause it to collapse onto either the  $|0\rangle$  or  $|1\rangle$  state; however, if the second qubit is measured afterward, the outcome will be identical to the first.

### 2.1.3. Qubits operations

A quantum system can change the state of a qubit or a group of qubits by employing either unitary or non-unitary gates. Unitary gates are reversible and preserve the information in the quantum system. On the contrary, non-unitary gates are irreversible and destroy a portion of the current qubit state. This section will present operations that involve non-unitary gates as they allow us to measure and reset qubits.

### Initialization

An essential step in quantum computing is qubit initialization, which involves setting up qubits in specific quantum states to facilitate subsequent quantum operations. The goal of the qubit initialization process is to set up the quantum system so that the qubits are in a superposition of the known states  $|0\rangle$  and  $|1\rangle$ . Due to the fact that initialization is an irreversible process that forces the qubit into a specific state regardless of its previous state, it is not a unitary quantum gate.

For qubit initialization, a number of methods have been developed, including electron spin resonance, microwave-based approaches and optical pumping [18]. These techniques use specific gate sequences and meticulously controlled external fields to manipulate the qubits into the desired initial state. For performing trustworthy quantum computations and obtaining precise results, the capacity to initialize qubits accurately is crucial.

### Measurement

The measurement operation is a fundamental component of quantum computing that allows the extraction of information from qubits. Qubit measurement entails performing a measurement in a specific basis, typically the computational basis represented by  $|0\rangle$  and  $|1\rangle$ , in order to determine the state of a qubit. With a probability determined by the coefficients in the superposition, the measurement process collapses the entangled or superposition state of the qubit into one of the basis states. The state of the qubit can be inferred probabilistically from various measurement results.

Different measurement methods have been developed, including non-projective methods like weak measurement [25] and quantum non-demolition measurement [43] as well as projective methods [42] using quantum logic gates. For obtaining trustworthy results and validating the outcomes of quantum computations, accurate qubit measurement is essential.

### 2.2. NV Center Quantum Computers

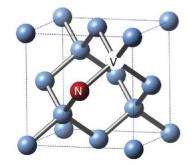

Different technology for quantum computations have been developed over the past decades, such as silicon's phosphorous qubits [20] or superconducting qubits. The latter technology was made recently scalable by Google [27], however, it shows relatively short coherence times [13], while **nitrogen**-

Figure 2.4: NV center representation [28]. N identifies the nitrogen atom and V the vacancy.

vacancy (NV) centers are known for their longer coherence times [33]. This technology is the focus of this thesis, and it will be presented in this section.

### 2.2.1. Qubits

The optimal condition to build a quantum computer is to ensure system isolation and individual qubit control, a scenario that happens in an atom trap [24]. A diamond Nitrogen-Vacancy center is formed in a diamond crystal from which two carbon atoms are missing, 1 of them replaced with a Nitrogen atom (Figure 2.4). This point defect center can be compared to an atom in a trap because the defect-free isotopic 12C diamond crystal, with its large bandgap of 5.4 eV, has properties resembling those of a vacuum [35]. The negatively charged NV- state can be artificially created by capturing an additional electron from the environment using lasers.

Specifically, one of the qubit states is associated with the **electron spin** of the NV center, while the additional **Carbon-13 isotopes** can also be used as qubits. The  $e^-$  qubit is easily controllable by electromagnetic fields and photons, but it is also susceptible to noise; by contrast,  ${}^{13}C$  qubits are less susceptible to noise and decoherence but cannot be controlled directly. Therefore, from an architectural point of view, the first ones are suitable to perform operations, while the latter model data memory.

### 2.2.2. Analog control

Direct control of the electron spin qubit in an NV center can be achieved using **electromagnetic fields and photons** [40], providing a pathway to realize the quantum operations described in Sections 2.1.2 and 2.1.3.

Manipulation of the NV center's single-qubit rotations, particularly the  $e^-$  qubit, can be achieved through the magnetic field. The  ${}^{13}C$  qubit can also be rotated in controlled and uncontrolled ways, as demonstrated by [4]. Initialization of the qubit is achieved through charge pumping [18] in which the NV center is continuously hit with photons. Measurement is achieved in a process where the absorption of photons indicates the qubit state. Moreover, photons can be employed to entangle two distinct NV centers by using electron-photon pair creation [15].

This plethora of ways to interface with the qubits creates the foundation of the *Quantum-to-Classical* layer, which employs various analog actuators for its implementation. One such actuator is the Microwave Arbitrary Waveform Generator, which generates micro- or radio-frequency waves for the rotation of electron and carbon nuclei. Additionally, lasers and switches are utilized to illuminate the diamond and deliver photons, while a photon detector counts the emitted photons and stores the count value in a register.

These analog actuators pave the way for exploring digital control techniques, unlocking new possibilities for enhanced precision and scalability in qubit operations.

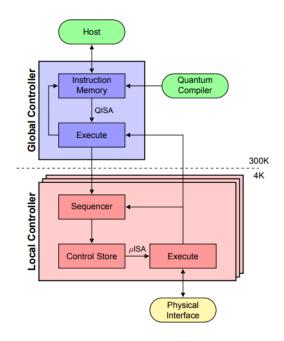

### 2.2.3. Digital control

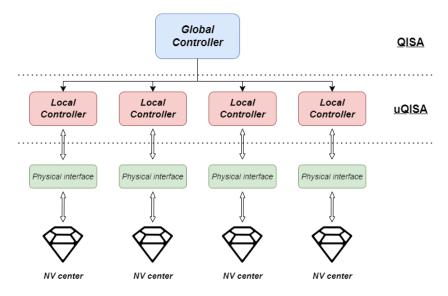

The analog control hardware described must be coordinated in order to ensure the correct execution of a quantum program. In order to achieve this, the layered digital control architecture proposed in [40] and refined in [16] is employed in this work. This architecture consists of two layers: the lower layer comprising *Local Controllers* (LCs), dedicated to individual NV centers, and the upper layer comprising of single a *Global Controller* (GC) responsible for the entire system. Figure 2.5 provides a visual

Figure 2.5: Overview of the envisioned hardware architecture [16].

depiction of this hierarchical structure.

The **local controller** plays a vital role in activating and controlling the underlying analog electronics used for NV center operations. It employs a *Local Micro-instruction Set Architecture* (uQISA) [16] and comprehends registers and ports used to control the underlying Quantum-to-Classical layer. A detailed design of such controllers is out of the scope of this work.

By leveraging the localized control, NV centers across the network have the potential to operate in parallel when addressed by the Global Controller. Furthermore, their entanglement scheme based on photons facilitates on-chip interaction between neighboring NV centers.

#### **Global Controller**

Object of this thesis work and main component of the control plane, the Global Controller is responsible for the execution of quantum algorithms.

The Global Controller utilizes a *Quantum Instruction Set Architecture* (QISA) to comprehensively handle algorithm execution. This architecture incorporates custom instructions that explicitly capture all required parameters. An example of such a structured QISA can be found in [47]. Moreover, further advancements will be explored in the current study.

In addition to program execution, the GC plays a crucial role in coordinating local controllers to achieve parallelism and managing data transfers to and from the lower layers. Efficiently addressing the local controllers is essential for achieving parallel processing and ensuring seamless data flow.

### 2.3. RISC-V Instruction Set Architecture

RISC-V is an open and extensible instruction set architecture that has gained significant popularity in recent years due to its simplicity, modularity, and scalability. By adopting the RISC-V ISA, the project aims to leverage its flexibility and robustness to design and implement the GC, enabling efficient and effective control over the lower layers of the system. This section provides an introduction to the RISC-V ISA and its relevance in the context of this work.

### 2.3.1. History of RISC-V

The RISC-V instruction set architecture (ISA) has emerged as a prominent and influential open-source standard in the field of computer architecture. Its history dates back to the early 2010s when researchers at the University of Berkeley, recognized the need for an open and customizable ISA to drive innovation in processor design. The RISC-V project was initiated under the leadership of *Prof.*

*Krste Asanović* and *Prof. David Patterson*, resulting in the development of an ISA that offers simplicity, modularity, and extensibility [45].

The aim of creating RISC-V was to address the drawbacks of closed and proprietary ISAs, which limit access to the underlying architecture and obstruct experimentation and research. By offering an **open-source ISA**, RISC-V fosters industry-wide innovation, academic research, and collaboration. It provides a **flexible platform** for academia, business, and individuals to create, implement, and modify processors in accordance with their unique needs, enabling novel approaches and ideas to be explored without proprietary constraints. The implications are far-reaching: a wide range of applications, from embedded systems to high-performance computing, have quickly adopted and used the RISC-V ISA. Notably, the open-source nature of RISC-V has led to the establishment of the RISC-V Foundation, a consortium of organizations driving the development and standardization of the architecture [39].

Importantly, the RISC-V ISA has seen the creation of a number of illustrious processors. The University of Berkeley developed the first-ever RISC-V processor, known as the *Rocket* core, which served as the model for later improvements to the architecture [2]. On the other hand, the *SweRV EH1* core, developed by Western Digital, is recognized as one of the most performant RISC-V processors, delivering high clock frequencies and efficient execution [3].

### 2.3.2. Characteristics

The RISC-V ISA is designed with a modular and extensible structure, offering flexibility and customization options to meet diverse computing requirements. The base RISC-V ISA provides a **minimal set of instructions** necessary for building a functional processor. This simplicity allows for easy adoption and implementation of the architecture.

With a base integer instruction set that is subsequently expanded by optional *standard extensions*, the RISC-V ISA adopts a layered design strategy. The base set is available in four variants: 32-bit (**RV32I**), 64-bit (**RV64I**), 128-bit (**RV128I**), and embedded 32-bit (**RV32E**). The standard extensions include modules for integer multiplication and division [*M*], atomic instructions [*A*], floating-point operations [*F*], and more. By choosing the proper extensions, designers can modify the RISC-V instruction set to meet their unique requirements. This encourages a scalable method of processor design, where extra capability can be added as needed, without extra complexity or overhead.

One of the most intriguing characteristics of the ISA is its modularity. The architecture allows for the creation of unique extensions in addition to the standard ones, providing unequaled flexibility for particular computing workloads. The *RVV* vector extension is one such addition that adds vector processing capabilities for effective parallel data processing tasks, which are frequently utilized in scientific computing and multimedia applications [37]. The *RVC* cryptography extension is another noteworthy addition. It offers hardware acceleration for cryptographic operations, improving security-related computations in embedded devices and communication [38]. Accordingly, the goal of this thesis project is to create a RISC-V Instruction Set Extension (ISE) to handle the control of NV center diamond quantum computers.

### 2.4. Conclusion

In conclusion, this chapter presented the background knowledge required to comprehend the thesis work. Beginning with an explanation of quantum computing and qubits, it detailed the physics behind this technology. Quantum bits, quantum gates, and qubit operations were some of the subjects covered in the discussion of quantum information theory. Furthermore, the chapter looked into NV Center Quantum Computers, exploring the key components of qubits and the control mechanisms involved, including analog and digital control. Finally, a summary of the RISC-V Instruction Set Architecture was given, emphasizing its background and salient features. This foundation lays the groundwork for the subsequent chapters, which explore in depth how control electronics are implemented in contemporary quantum computers.

3

### Modeling the Control Plane

In this chapter, we present a mathematical model aimed at determining the allocation of local controllers to global controllers within the Digital Control Layer. By developing this model, we can establish guidelines for achieving an optimized and scalable control structure that attempts to minimize idle states and maximize the overall system efficiency.

This chapter explores the modeling of the control plane, starting with the execution of instructions (Section 3.1). Time diagrams are then discussed, considering ideal cases (Section 3.2.1) and accounting for processing (Section 3.2.2) and communication (Section 3.2.3). The chapter concludes with the definition of the model (Section 3.3).

### **3.1. Instruction Execution**

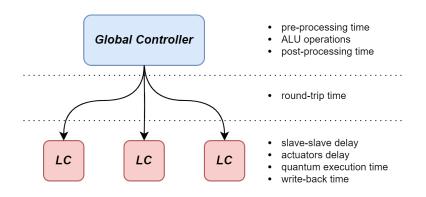

In order to develop an accurate mathematical model, the initial step involves identifying the comprehensive sequence of actions required for a complete quantum instruction execution within the layer, spanning from the Global Controller to the Local Controller. To accomplish this, a high-level flow chart illustrating the execution process is presented in this section, providing a visual roadmap. Following the flow chart, a more precise definition and profiling of each step are presented, allowing for a thorough understanding of the intricate processes involved in the execution sequence.

### 3.1.1. Flowchart

Figure 3.1 visualize a high-level flow chart of the execution. This representation aims to offer a **functional and hardware-agnostic** perspective, providing insights into the elaboration and communication data flow.

Figure 3.1: The high-level flowchart of the digital control plane. Here are represented the execution steps: on the left in the GC, while on the right in the LC

Figure 3.2: Classification of the parameters based on the origin of latency generation

### 3.1.2. Profiling

The provided flowchart can be used as a basis for starting a more detailed investigation of the system's execution steps. In particular, in this section, the emphasis is on determining each latency interval needed and parameterizing them uniquely. Table 3.1 presents a description and defines a symbol for each identified **parameter**, while Figure 3.2 classifies them based on the hardware components responsible for introducing latency.

| Name                      | Description                                                                               | Symbol                        |

|---------------------------|-------------------------------------------------------------------------------------------|-------------------------------|

| Pre-processing latency    | Data conversion and management<br>needed to execute the instruction( <i>i</i> )           | $\alpha \cdot Tpe_G(i)$       |

| Calculation latency       | Calculation of actuator control values, based on the parameters                           | $eta \cdot Tc_L(i)$           |

| Round Trip Time (RTT)     | Latency that models the master-slave round communication (to node <i>j</i> )              | $\gamma \cdot RTT_C(j)$       |

| Propagation delay         | Latency that models the intra-slaves communication (from node <i>j</i> to node <i>k</i> ) | $\delta \cdot Tpd_C(j,k)$     |

| Phisical layer latency    | Latency needed by the actuators<br>(mw generator, lasers, etc.) to get activated          | $\varepsilon \cdot Tact_L(i)$ |

| Quantum execution latency | Quantum gate or qubit operations execution (measured experimentally)                      | $Tqex_L(i)$                   |

| Write back latency        | Writing the results from the physical sensors to the appropriate registers                | $\xi \cdot Twb_L$             |

| Post-processing latency   | Data management to correctly store the execution results                                  | $\zeta \cdot Tpo_G(i)$        |

Table 3.1: Profiling of the execution parameters

In the above table, particular notations have been used to define the symbols:

- The coefficients  $\alpha, \beta, \gamma, \delta, \varepsilon, \zeta \in 0, 1$  are added to exclude specific variables, making the module simpler if needed.

- The index (i) indicates the influence of the executed instruction on the parameter value.

- The indexes (*j*,*k*) indicate the influence of the positions of the nodes on the parameter value.

- The subscripts "<sub>G</sub>", "<sub>L</sub>" and "<sub>C</sub>" indicate the origin of latency generation, the GC, the LC, or the communication infrastructure.

Having analyzed the execution profiling of the system, we now turn our attention to the generation of time diagrams. Those are helpful to correlate the presented parameters and formulate an accurate model that captures the execution dynamics effectively.

### 3.2. Time Diagrams

In this section, time diagrams are generated and analyzed using the previously identified parameters. By considering different levels of idealities, incorporating additional parameters, and varying the workload of controllers with send, receive and mixed operations, we can gain valuable insights into the temporal dynamics of the system. These time diagrams provide a comprehensive and intuitive representation of the system's behavior, enabling us to optimize performance and make informed decisions for system design and resource allocation.

The aim of this analysis is to determine the maximum achievable parallelism of Local Controllers for a specific instruction (*i*). To estimate this, we create and analyze workload scenarios designed to present limitations and extreme cases, which help in identifying the boundaries of the parallelism. The focus is on the relative values of the latency parameters rather than on their representativity of real workloads.

Note that, in the study proposed, the Global Controller is constrained to address Local Controller LC#1 immediately upon completing its execution, thereby preventing any idle state. By doing this, the maximum parallelism of LCs can be estimated.

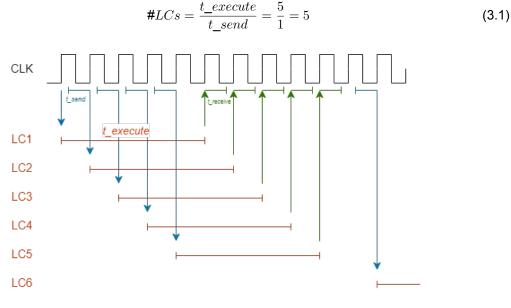

### 3.2.1. Ideal case

The first case accounts only for the processing time: namely send and receive processing on the GC and execution time on the LCs. Table 3.2 sums up the latency values for a workload dominated by the local execution time and with equal communication delays, expressed in clock cycles  $t_{clk}$ .

| GC | t_send    | $1 \cdot t_{clk}$ |

|----|-----------|-------------------|

| GC | t_receive | $1 \cdot t_{clk}$ |

| LC | t_execute | $5 \cdot t_{clk}$ |

Table 3.2: Parameters used in the ideal case.

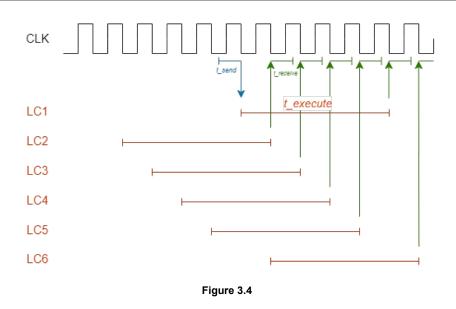

• Scenario 1: The GC sends data and control to as many LCs until the first needs to send its results back (Figure 3.3). The parallelism #LCs = 5 can be calculated as:

Figure 3.3

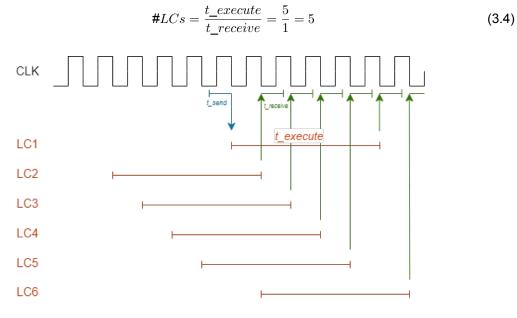

• Scenario 2: The GC sends data and control to LC#1 and addresses as many LCs until LC#1 needs to send its results back (Figure 3.4). The parallelism #LCs = 5 can be calculated as:

$$#LCs = \frac{t\_execute}{t\_receive} = \frac{5}{1} = 5$$

(3.2)

In this simplified scenario, the parallelism is solely determined by the execution latencies of the controllers. Furthermore, both workloads yield the same parallelism value since the latencies for sending and receiving processing are equal. However, this simplistic representation does not accurately model real-world scenarios, and thus, additional flexibility is introduced in the subsequent case.

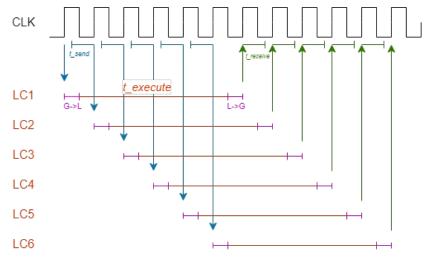

### 3.2.2. Accounting for processing

The second case presents a difference in the processing times in the GC, as described in Table 3.3. In this scenario, *t\_send* is different than *t\_receive*, in order to study any difference in parallelism created by this inequality. To highlight this, a mixed workload is also analyzed.

| GC | t_send    | $2 \cdot t_{clk}$ |

|----|-----------|-------------------|

| GC | t_receive | $1 \cdot t_{clk}$ |

| LC | t_execute | $5 \cdot t_{clk}$ |

Table 3.3: Parameters used in the second case.

• Scenario 1: The GC sends data and control to as many LCs until the first needs to send its results back (Figure 3.5). The parallelism #LCs = 2 can be calculated as:

Figure 3.5

• Scenario 2: The GC sends data and control to LC#1 and addresses as many results until LC#1 needs to send its results back (Figure 3.6). The parallelism #LCs = 5 can be calculated as:

• Scenario 3: The GC sends data and control to LC#1 and addresses as many LCs until LC#1 needs to send its results back (Figure 3.7). The parallelism is measured as: #LCs = 4.

This study case offers interesting insights about the boundaries of parallelism. In particular, the slower send processing time corresponds to the lower boundary, while the faster receive processing time identifies the upper boundary. Accordingly, the mixed workload corresponds to a parallelism value within the boundaries.

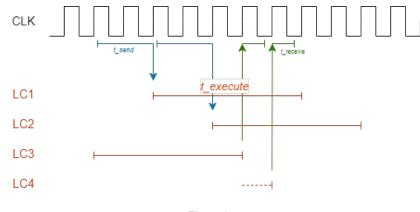

### 3.2.3. Accounting for communication

By incorporating communication delays, a more general expression can be formulated to calculate the parallelism, considering latencies beyond the Global and Local Controllers. Despite the small value of the delay, its impact is already significant and greatly influences the overall result. This highlights the importance of accurately accounting for external latencies when evaluating the system's parallelism. Figure 3.8 presents the same scenario as in the ideal case, with the addition of the  $t_latency$  parameter, specified in Table 3.4. The parallelism is now increased to #LCs = 6 due to the communication delay, which gives more time to the GB to address additional LCs. It can be calculated as:

$$#LCs = \frac{t\_execute + 2 \cdot t\_latency}{t\_receive} = \frac{6}{1} = 6$$

(3.5)

|       |           | -                   |

|-------|-----------|---------------------|

| GC    | t_send    | $2 \cdot t_{clk}$   |

| GC    | t_receive | $1 \cdot t_{clk}$   |

| LC    | t_execute | $5 \cdot t_{clk}$   |

| Comm. | t_latency | $0.5 \cdot t_{clk}$ |

Table 3.4: Parameters used in the third case.

Figure 3.8

In this section, various workloads of the control plane were examined, and their corresponding parallelism was evaluated through the analysis of time diagrams. These findings shed light on the interplay between latencies and workload types, providing valuable insights into the system's performance. The next section focuses on the development of a complete model, which will encapsulate the collective understanding of execution profiling, time diagrams, and instruction execution, aiming to provide a mathematical formulation that accurately represents the system's behavior and characteristics.

### 3.3. Model definition

Once the execution has been completely profiled in Section 3.1 and its parallelism has been estimated in Section 3.2, the goal is now to create a comprehensive model that uniquely defines the parallelism of the control plane.

From the time diagram analysis, we observed that the parallelism of the Local Controllers is always bounded between the two extremes defined by the *send* and *receive* operations while it is incremented by the communication latency. The relationship can be therefore expressed as follows:

$$\frac{t\_execute_L + t\_latency}{max(t\_send_G, t\_receive_G)} \le \#LCs \le \frac{t\_execute_L + t\_latency}{min(t\_send_G, t\_receive_G)}$$

(3.6)

Equation 3.6 lays the initial foundation for the module's development, serving as a starting point for further improvements. The next step is to establish the precise definition of each quantity by incorporating the execution parameters outlined in Section 3.1. The following equivalences hold true:

- $t\_execute_L \equiv \beta \cdot Tc_L(i) + Tqex_L(i) + \varepsilon \cdot Tact_L(i) + \xi \cdot Twb_L$

- $t\_latency \equiv \gamma \cdot RTT_C(j) + \delta \cdot Tpd_C(j,k)$

•

$$t\_send_G \equiv \alpha \cdot Tpe_G(i)$$

•  $t\_receive_G \equiv \zeta \cdot Tpo_G(i)$

Consequently, including these definitions in Eq.3.6 we obtain the following equations:

$$#LCs \leq \frac{\beta \cdot Tc_L(i) + Tqex_L(i) + \varepsilon \cdot Tact_L(i) + \xi \cdot Twb_L + \gamma \cdot RTT_C(j) + \delta Tpd_C(j,k)}{min(\alpha \cdot Tpe_G(i), \zeta Tpo_G(i))}$$

(3.7)

$$#LCs \ge \frac{\beta \cdot Tc_L(i) + Tqex_L(i) + \varepsilon \cdot Tact_L(i) + \xi \cdot Twb_L + \gamma \cdot RTT_C(j) + \delta Tpd_C(j,k)}{max(\alpha \cdot Tpe_G(i), \zeta \cdot Tpo_G(i))}$$

(3.8)

For the rest of the analysis, the focus will be on Equation 3.7, but equivalent results can be derived with analog rationale for Equation 3.8. It is worth noting that the parameter values used in the precedent section were just example quantities, and the actual analysis is only valid when the latencies are representative of the real system.

Based on the dependency of the parameters on the instruction executed (*i*) and on the physical location of the nodes involved (*j*,*k*), it can be inferred that also the parallelism is dependent on the same variables. Consequently, a more correct relationship is defined in Equation 3.9.

$$\#LCs(i,j,k) \le \frac{\beta \cdot Tc_L(i) + Tqex_L(i) + \varepsilon \cdot Tact_L(i) + \xi \cdot Twb_L + \gamma \cdot RTT_C(j) + \delta \cdot (j,k)}{min(\alpha \cdot Tpe_G(i), \zeta Tpo_G(i))}$$

(3.9)

Based on this intermediate outcome, the maximum achievable parallelism for controlling Local Controllers in parallel during each QISA instruction is already determined. To further generalize and construct the final general model, a few additional considerations need to be taken into account. These deliberations will contribute to refining the model and capturing a holistic representation of the system's behavior:

- 1. Remove the physical dependency from the parallelism value, by accounting for worst-case scenarios. Call #*LCs*(*i*) the result of Eq.3.9 for each instruction.

- 2. Define  $w_i$  as a weight representing the statistical frequency of the instruction *i* to appear in a given workload

- 3. Define M as the total number of QISA instructions creating the workloads

The complete final model calculating the control plane parallelism can be then defined as the weighted average of the parallelism of each instruction:

$$\#LCs = \frac{\sum_{i=1}^{M} \#LCs(i) \cdot w_i}{\sum_{i=1}^{M} w_i}$$

(3.10)

By defining the comprehensive and unified model shown in Equation 3.10, the control plane's achievable parallelism can now be accurately calculated, providing valuable insights into the system's performance and optimization potential.

### 3.4. Conclusion

In this chapter, we focused on modeling the control plane of the system to understand its behavior and performance. We began by analyzing the instruction execution process, presenting a detailed flowchart and profiling of the steps involved. This provided valuable insights into the sequence and timing of instructions. With the help of time diagrams, different workload scenarios and their impact on parallelism have been evaluated.

This served as a foundation for the definition of a model that provides a unified framework to calculate the achievable parallelism of the control plane, taking into account various factors and parameters. In this thesis work, we will eventually utilize this model to evaluate the design of the global controller.

4

### qRV32 Instruction Set Extension

This chapter represents our first step in transitioning the focus of the work toward the operation of the global controller within a diamond-based color-center quantum computer. As we shift our focus, we embark on designing an instruction extension following the RISC-V standard and tailored to a Quantum Instruction Set Architecture (QISA) for NV-center quantum computing. This extension will allow us to incorporate the essential functionalities required for efficient control and coordination of the quantum computing system into an existing industry-level ISA. By encoding these additional instructions, we pave the way for the realization of the global controller.

Throughout this chapter, we will explore the intricacies of the qRV32 set extension and its design considerations and trade-offs. Firstly, RISC-V extensions (Section 4.1) and the Diamond QISA (Section 4.2) are introduced. The focus then shifts to the qRV32 Instruction Set Extension (Section 4.3), covering instructions encoding (Section 4.3.1) and communication with LCs (Section 4.3.2). The chapter concludes with a summary (Section 4.4).

### 4.1. RISC-V Extensions

The RISC-V ISA is based on a modular instruction set architecture design, which natively welcomes Instruction Set Extensions (ISE), particularly supporting the design of domain-specific central computing units. Implementing RISC-V extensions requires careful consideration of various factors, in particular, the compatibility with the existing RISC-V standard must be ensured to maintain interoperability.

As described in the RISC-V Instruction Set Manual [46], the ISA provides a flexible framework for incorporating both standard and custom extensions. The base ISA, either RV32I or RV64I, can be combined with selected standard extensions, such as IMAFD, Zicsr, and Zifencei, to form a "general-purpose" ISA denoted as RV32G or RV64G. In addition to supporting general-purpose software development, RISC-V also aims to provide a foundation for specialized instruction-set extensions and customized accelerators. The instruction encoding spaces and optional variable-length instruction encoding facilitate leveraging the standard ISA toolchain when designing customized processors.

The major opcodes for the RISC-V general-purpose ISA, or *RVG*, are presented in Table **??**, where Major opcodes with 3 or more lower bits set are reserved for instruction lengths greater than 32 bits. *Custom-0* and *custom-1* opcodes are intended for use by custom instruction-set extensions, while *custom-2/rv128* and *custom-3/rv128* opcodes are reserved for future use in RV128. It is important to

| inst[4:2] | 000    | 001      | 010      | 011      | 100    | 101      | 110            |

|-----------|--------|----------|----------|----------|--------|----------|----------------|

| inst[6:5] |        |          |          |          |        |          |                |

| 00        | LOAD   | LOAD-FP  | custom-0 | MISC-MEM | OP-IMM | AUIPC    | OP-IMM-32      |

| 01        | STORE  | STORE-FP | custom-1 | AMO      | OP     | LUI      | OP-32          |

| 10        | MADD   | MSUB     | NMSUB    | NMADD    | OP-FP  | reserved | custom-2/rv128 |

| 11        | BRANCH | JALR     | reserved | JAL      | SYSTEM | reserved | custom-3/rv128 |

Table 4.1: RISC-V base opcode map, inst[1:0]=11 [46]

avoid using reserved opcodes to ensure compatibility with future standard extensions.

Each instruction encoding space represents a specific number of instruction bits used to encode a base ISA or an ISA extension. RISC-V supports varying instruction lengths, and even within a single length, different encoding space sizes are available. For example, the base ISA is defined within a 30-bit encoding space (bits 31-2 of the 32-bit instruction), while the atomic extension "A" fits within a 25-bit encoding space (bits 31-7). The term "prefix" refers to the bits to the right of an instruction encoding space, and it is stored at earlier memory addresses in little-endian instruction fetch order. The base ISA prefix is the two-bit "11" field (bits 1-0), while the atomic extension "A" prefix is the seven-bit "0101111" field (bits 6-0) representing the AMO major opcode.

To ensure compatibility and coexistence of various instruction encoding spaces, a standard-compatible global encoding allocates a unique non-conflicting prefix for each included space, targeting one or more available opcode spaces of Table **??**. This allows the base ISA, standard extensions, and non-standard extensions to be part of the global encoding. Non-standard extensions can be included as long as they do not conflict with standard extensions and can use standard prefixes if the associated standard extensions are not included. This approach enables a common toolchain to target the standard subset of any RISC-V standard-compatible global encoding.

### 4.2. Diamond QISA

The control hardware architecture [16] for the system is structured into layers, as illustrated in Figure 4.1. At the core of this architecture is the Global Controller, serving as the central component responsible for overseeing the entire system. It receives input in the form of a program written in the Quantum Instruction Set Architecture. Using these instructions, the global controller performs necessary computations and issues commands to the local controllers accordingly.

Figure 4.1: Schematic of the layered digital control adopted .

The literature provides multiple versions of Instruction Set Architectures specifically tailored for NV centers quantum computing. An initial version is presented in [47], followed by a more accurate and enhanced alternative described in [40] and [16].

For the purpose of this work, the QISA proposed in [16] is adopted as the reference. It offers a clear separation of functionalities between the Global and Local controllers, along with improved instruction specificity. While a partial listing of the QISA instructions can be found in Appendix A, further details, currently under embargo, are out of the scope of this project.

### 4.3. qRV32 Instruction Set Extension

In this section, we delve into the design of the Instruction Set Extension. Our objective is to create a RISC-V standard-compatible global encoding that can effectively handle the complete range of

functionalities offered by the QISA and its associated parameters. Furthermore, we address the crucial aspect of establishing a communication standard between the Global and Local Controllers.

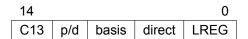

### 4.3.1. Instructions encoding

The **qRV32 ISE** targets the Global Controller of a diamond-based quantum computer, and it must grant classical instruction for communication and data management on top of correctly mapping the structure of the QISA. Specifically, it must include **memory operations** (load, store), **immediate** operations, and **move** operations, because it is envisioned that the GC hardware will employ a separate register file, called *QREG*, to store the parameters of the QISA. Eventually, the architecture is envisioned to grant Direct Memory Access (DMA) to the LCs to write back their results, therefore avoiding the need for *send* and *receive* instructions.

A fundamental aspect of the process is the analysis of the instruction parameters. Due to the limited encoding space of 32bits instructions, not all the parameters can be expressed in immediate fields and may need to be preemptively stored in the QREG. Therefore a study of their nature and possible values is now presented. More information about this can be found in Table B.1 of Appendix B.

- The "*preserve*" and "*dir*" parameters used in *qgate* instructions represent binary values, and can therefore be expressed using 1 bit

- The "basis" used during the swap instruction can be either x, y, z, therefore can be expressed using 2 bits

- While the entanglement process and the network structure are still not completely defined, a *"direction"* parameter is used to indicate the relative position of NV centers. A 3-bit binary number is used to represent 8 different directions

- · Up to 32 registers are anticipated in the LCs, therefore 5 bits must be used to address them

- The "phase" and "angle" parameters used in qgate- instructions represent fractions of  $\pi$ . Therefore a fixed point <16,14> binary number is used to represent angles with accuracy of  $\pi/16384$

- The frequencies "sweepStart", "sweepStep", "sweepStop" for the detectCarbon and magbias instructions can be expressed as 16-bit unsigned numbers

- Similarly, the times "*sweepStart*", "*sweepStep*", "*sweepStop*" for the *rabicheck* instruction are also 16-bit unsigned numbers

It looks clear that, among all the parameters, only "preserve", "dir", "basis", "phase" and "angle" can actually be expressed in immediate fields and still leave space for the actual encoding. Eventually, the parameters "NV" (number of NV centers per GC) and "C13" (number of <sup>13</sup>C qubits per NV center), as well as the depth of the QREG file, need to be maximized during the encoding process. The **target** for the number of NV centers per GC is set at 1000, while at least 10 <sup>13</sup>C qubits are planned per NV center.

It is worth noticing that the encoding process involves a trade-off between the number of addressable elements and the size of instruction identification fields. Increasing the number of bits used to identify specific elements, such as NV centers, reduces the available bits for identifying individual instructions, and vice-versa. As a result, the Instruction Set Extension may require additional major encoding spaces to accommodate the growing number of instructions.

The rest of the section presents three different encoding schemes for the qrv32 ISE. A complete listing of the encodings, comprehending all the instructions, can be found in Tables B.2, B.3, B.4 of Appendix B.

### **Encoding A**

The first encoding presented in this work does not employ any optimization. It aims to encode all the instructions of the QISA in a single RISC-V major opcode, *custom-0*, and can be seen as a starting point for the design. The instructions can be divided into subgroups, accounting for similarities in functionality and parameters. Their encodings are presented in the following list.

- 1. *G-type* instructions comprehend the *qgate-* instructions and also *set* and *entangle*. The 3-bit parameter field can be used to express single-bit flags, like *dir* and *preserve*.

- 2. *N-ype* instructions comprehend the remaining qubit operations. The field *function-4* (*(f4)* provides a unique identification for the instructions included. The 5-bit parameter field is used for entanglement *direction* or swap *basis*.

| 29 - 27 | 26 - 23        | 22 - 19                   | 18 - 16                          | 15 - 10                                         | 9 - 7                                                    | 6                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                             |

|---------|----------------|---------------------------|----------------------------------|-------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| par.    | QRS2           | QRS1                      | C13                              | NVNode                                          | \$ID                                                     | 00010                                                                                                                                                  | 11                                                                                                                                                                                                                                                                                                                            |

|         |                |                           |                                  |                                                 |                                                          |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                               |

| 28 — 23 | 3 22 —         | 19 18                     | 8 - 16 1                         | 5 —— 10                                         | 9 - 7                                                    | 6                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                             |

| х       | QRI            | EG                        | C13 I                            | VVNode                                          | \$ID                                                     | 00010                                                                                                                                                  | 11                                                                                                                                                                                                                                                                                                                            |

|         | par.<br>28 — 2 | par. QRS2<br>28 — 23 22 — | par. QRS2 QRS1<br>28—23 22—19 18 | par. QRS2 QRS1 C13<br>28 — 23 22 — 19 18 - 16 1 | par. QRS2 QRS1 C13 NVNode<br>28 - 23 22 19 18 - 16 15 10 | par.         QRS2         QRS1         C13         NVNode         \$ID           28 - 23         22 - 19         18 - 16         15 - 10         9 - 7 | 29 - 27       26 - 23       22 - 19       18 - 16       15 - 10       9 - 7       6         par.       QRS2       QRS1       C13       NVNode       \$ID       0 0 0 1 0         28 - 23       22 - 19       18 - 16       15 - 10       9 - 7       6         x       QREG       C13       NVNode       \$ID       0 0 0 1 0 |

3. *C-type* instructions comprehend the calibration functions, such as *detectCarbon*, *magbias* and *rabicheck*. Those instructions require up to 4 QREGs to correctly store all the needed parameters, which are not immediates.

| • •    |        |        |        | 15 —- 10 | • .  | •     | 0  |

|--------|--------|--------|--------|----------|------|-------|----|

| QREG 4 | QREG 3 | QREG 2 | QREG 1 | NVNode   | \$ID | 00010 | 11 |

4. The instructions move, qld and qst present in their encodings space to specify either one 4-bit QREG and one gpREG field, or two 4-bit QREG fields. The immediate field function-2 (f2) is used to distinguish among these 4 instructions. The memory operations supported, use the available encoding space for the offset parameter (11-bit) passed as immediate.

| 31 ——— 21        | 20 - 19 | 18 — 14 | 13 — 10 | 8 - 7 | 6     | 0  |

|------------------|---------|---------|---------|-------|-------|----|

| immediate [11:0] | f2      | QREG2   | QREG1   | \$ID  | 00010 | 11 |

5. The *qldi* instruction is used to load a 16-bit wide immediate value into a QREG.

| 31 ——— 16        | 15 - 14 | 13 — 10 | 8 - 7 | 6     | 0  |

|------------------|---------|---------|-------|-------|----|

| immediate [14:0] | х       | QREG1   | \$ID  | 00010 | 11 |

While the encoding scheme enables the representation of quantum elements and instructions, it is important to acknowledge that the current implementation falls significantly short of the desired targets. Specifically, the architecture allows for a maximum of 8  $^{13}C$  qubits per NV center, 64 color centers per GC, 16 quantum registers, and supports 16-bit immediate loads. It is clear that these values fall well below the desired targets, and is therefore crucial to address the problem.

### **Encoding B**

It is clear, from encoding A, that the 25-bit space is limiting the number of addressable elements. To overcome such limitations, an additional instruction *NV-choose* is introduced to set which node is going to be addressed. As for the previous encoding scheme, subgroups are now listed.

1. The *NV-choose* instruction provides a 13-bit wide field to specify the NV node address. This allows the system to increase the number of color centers per GC.

| 31 — 27 | 26 — 14 | 13 - 10 | 9 - 7 | 6     | 0  |

|---------|---------|---------|-------|-------|----|

| 11111   | NV node | х       | \$ID  | 00010 | 11 |

In encoding B, the Q-type subgroup comprehends all the quantum operations, from gates to initialization. This is achieved by employing the encoding space earned by the removal of the NV center address to specify QREGs, parameters and a *function-5* field.

|    |        |      |      | 13 - 10 9 - 7 |      | -     | 0  |

|----|--------|------|------|---------------|------|-------|----|

| f5 | param. | QRS2 | QRS1 | C13           | \$ID | 00010 | 11 |

|    | 29 — 25 | =      |        | -      | -    | -     | 0  |

|----|---------|--------|--------|--------|------|-------|----|

| f2 | QREG 4  | QREG 3 | QREG 2 | QREG 1 | \$ID | 00010 | 11 |

- 3. The *C-type* (calibration) subgroup, comprehending *detectCarbon*, *magbias* and *rabicheck*, still employs 4 QREGs to store all the parameters. The newly available encoding space allows increasing the address fields up to 5-bit.

- 4. The instructions *move*, *qld* and *qst* and *qldi* present the same encoding discussed in the previous paragraph.

Encoding B completely mitigates the limitations created by encoding A. In fact, the architecture allows for 16  $^{13}C$  qubits per NV center, 8000 color centers per GC and 32 quantum registers while still offering a 16-bit immediate load. Unfortunately, the architectural separation between *NV-choose* and the quantum operation instructions can create a non-negligible overhead in the compilation and execution of algorithms.

### **Encoding C**

This last encoding format tackles the limitations of encoding A with another solution: the QREG file structure is modified, and each register is envisioned to be 48-bit wide, which each 16-bit chuck as an independently loadable subregister. This reduces the portion of encoding space needed to declare multiple quantum registers, like in *C-type* instructions. Once again, instruction types are listed below:

1. *G-type* instructions comprehend all the quantum gates available. Within the parameter field, C13 (4-bit) and a single-bit flag can be specified.

| 31 - 29 | 28 - 24 | 23 — 19 | 18 ——— 9 | 8 - 7 | 6     | 0  |

|---------|---------|---------|----------|-------|-------|----|

| f3      | param.  | QREGs   | NV node  | \$ID  | 00010 | 11 |

2. The remaining quantum operations belong to the *Q-type* instructions. The 6-bit parameter field can be used to specify QREG and LREG addresses (5-bit), C13, basi (2-bit), or direct (3-bit).

| 31 | 30 - 27 | 26 ——— 19  | 18 — 9  | 8 - 7 | 6     | 0  |

|----|---------|------------|---------|-------|-------|----|

| f1 | f4      | parameters | NV node | \$ID  | 00010 | 11 |

3. The *move* instruction, available in two flavors (move from and move to) based on the value of *f1*, does not use additional parameters

|    |    |       |      | 18 ——— 9 | 8 - 7 | 6     | 0  |

|----|----|-------|------|----------|-------|-------|----|

| 10 | f1 | gpREG | qREG | Х        | \$ID  | 00010 | 11 |

4. As usual, *qld* and *qst* use the available encoding space for the offset parameter (11-bit) passed as immediate.

Ex. qst rs2 \$rs1(imm)

|    | 29 — 24    |       |       |           | • •  | -     | 0  |

|----|------------|-------|-------|-----------|------|-------|----|

| f2 | imm [10:5] | QREG2 | QREG1 | imm [4:0] | \$ID | 00010 | 11 |

5. The *qldi* instruction is used to load an immediate value in a sub-register. Once again the immediate is 16-bit wide, and the *sel* parameter identifies which sub-register will be loaded.

| 31 ——— 24       | 23 —- 19 | 18 - 17 | 16 — 9         | 8 - 7 | 6     | 0  |

|-----------------|----------|---------|----------------|-------|-------|----|

| immediate[15:8] | QREGd    | sel     | immediate[7:0] | \$ID  | 00010 | 11 |

Figure 4.2: Global to Local communication packet

By adopting Encoding C, the limitations introduced by Encoding A are effectively mitigated. This enhanced architecture now supports up to 16  $^{13}C$  qubits per NV center, 1000 color centers per GC, 32 quantum registers, and retains the 16-bit immediate load capability, all without requiring any architectural modifications. However, it is important to note that this advancement comes at the cost of increased hardware complexity within the QREG structure.

### Comparison

In this section, we explored three different encoding approaches for integrating the QISA into the RISC-V standard. Encoding A served as the initial design, fulfilling the required functionalities but falling short of meeting the design targets. Encoding B and Encoding C were proposed as alternative solutions to address the limitations. While Encoding B offered a straightforward approach, it introduced challenges in the quantum stack. In contrast, Encoding C appeared to overcome this limitation by increasing the complexity of the qreg. Ultimately, Encoding C emerged as the optimal and final solution, as the hardware overhead it introduced was manageable and easily implementable.

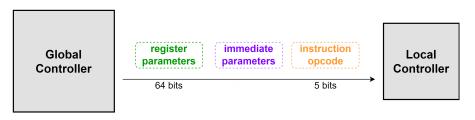

### 4.3.2. Communication with LCs

The preceding section provided an in-depth explanation of the instruction encoding design, which established a clear syntax for communication with the Global Controller. However, once the GC decodes and processes the instructions, it needs to transmit the appropriate control signals and instruction data to each Local Controller. Therefore, a communication standard between the GC and LCs must also be defined.

This communication packet must encompass the quantum operation to be executed, as well as all the immediate and register parameters required for its execution. Figure 4.2 visually illustrates the message and its individual components. The *register parameters* occupy a width of 64 bits and directly correspond to an entry in the Quantum Register File. The *instruction opcode* consists of a 5-bit code that uniquely identifies the QISA instructions, following the encoding table B.5 provided in Appendix B. Lastly, the *immediate parameters* field encompasses all the possible parameters expressed as immediate values at the instruction level.

Notably, the *immediate parameters* field varies for each executed instruction, making its encoding more complex. The remaining part of this section will present two potential encodings and compare them, taking into account their physical effects and trade-offs.

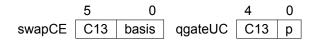

### **Fixed-length packet**

The immediate parameters can be encoded using a fixed-length packet, which offers a simpler approach. In this method, each instruction sends 15 bits within the communication message to transmit the value of each possible immediate parameter. If a parameter is not utilized, the corresponding bits are set to zero. Since the order of the parameters remains constant, the decoding logic in the local controller is straightforward. An illustration of the fixed-length packet representation is provided below.

### Variable-length packet

Alternatively, a variable-length packet can be employed to transmit only the parameters required by the instruction. This can be achieved by maintaining a fixed order of possible parameters but sending out only those that are actually used. This approach reduces the message length since the packet

is always smaller than 6 bits. Two examples of such encoding, one for the *swapEC* instruction and another for the *qgateUC* instruction, are demonstrated below.

#### Comparison

The two encoding schemes, fixed-length and variable-length packets, have different tradeoffs and considerations in terms of decoding logic, power consumption, and overall efficiency.

- Decoding Logic on LC: In the fixed-length packet scheme, the decoding logic in the Local Controller is relatively simple since the order of the parameters is always the same. Each parameter has a fixed position in the packet, making it easier to extract and interpret the values. On the other hand, the variable-length packet requires additional logic to determine which parameters are present in the message and their respective positions. This increases the complexity of the decoding process in the LC.

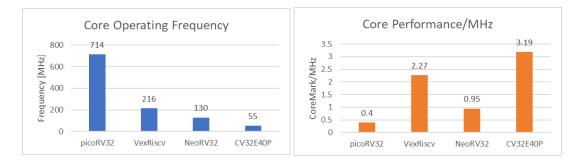

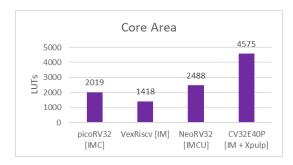

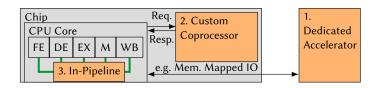

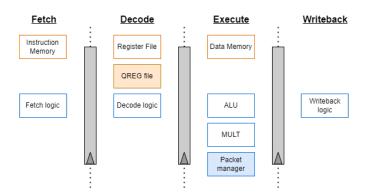

- Transmission Power Consumption: The transmission power consumption is influenced by the width of the communication message and the distance it needs to travel. In the fixed-length packet scheme, all 15 bits are transmitted regardless of whether a parameter is used or not. This results in a wider message and potentially higher power consumption during transmission, especially when considering longer distances or operating at different temperatures. In contrast, the variable-length packet only transmits the necessary parameters, reducing the width of the message and potentially lowering power consumption.