# Computer Engineering

Mekelweg 4, 2628 CD Delft The Netherlands http://ce.et.tudelft.nl/

# MSc THESIS

# A Flexible Electronic Paper with Integrated Display Driver using Single Grain TFT Technology

Wei Man Chim

#### Abstract

CE-MS-2009-01

DIMES and the department Computer Engineering from the University of Technology Delft are developing an Electronic Paper Display. This display will have a paper-like appearance (paper-white, wide view angle), and it can retain its display contents even after power down. The E-paper Display will have its own display driver integrated in the display itself. In the future it will be possible to integrate with the E-Paper Display, large and complex digital circuits or even microcontrollers with their peripherals.

We are using the Single Grain TFT (SG-TFT) Technology developed at DIMES for the integrated electronics. Using this technology we are able to create high performance transistors out of amorphous silicon film. With these TFTs, a Display Driver is build that will control the QR-LPD E-Paper material from Bridgestone. This E-Paper material has an ultra fast pixel response, which makes it possible to use this E-Paper to view animations.

This E-Paper Display will showcase some of the possibilities that the SG-TFT Technology has to offer: 1) Mixed signals, both analog and digital circuits are present in this display; 2) High voltage SG-TFTs (70V) to control the QR-LPD E-Paper material; 3) Flexible Electronics, the possibility to fabricate on plastic substrate and make a fully flexible E-Paper Display, including the integrated electronics.

# A Flexible Electronic Paper with Integrated Display Driver using Single Grain TFT Technology

## THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

COMPUTER ENGINEERING

by

Wei Man Chim born in Amsterdam, The Netherlands

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

# A Flexible Electronic Paper with Integrated Display Driver using Single Grain TFT Technology

#### by Wei Man Chim

#### Abstract

IMES and the department Computer Engineering from the University of Technology Delft are developing an Electronic Paper Display. This display will have a paper-like appearance (paper-white, wide view angle), and it can retain its display contents even after power down. The E-paper Display will have its own display driver integrated in the display itself. In the future it will be possible to integrate with the E-Paper Display, large and complex digital circuits or even microcontrollers with their peripherals.

We are using the Single Grain TFT (SG-TFT) Technology developed at DIMES for the integrated electronics. Using this technology we are able to create high performance transistors out of amorphous silicon film. With these TFTs, a Display Driver is build that will control the QR-LPD E-Paper material from Bridgestone. This E-Paper material has an ultra fast pixel response, which makes it possible to use this E-Paper to view animations.

This E-Paper Display will showcase some of the possibilities that the SG-TFT Technology has to offer: 1) Mixed signals, both analog and digital circuits are present in this display; 2) High voltage SG-TFTs (70V) to control the QR-LPD E-Paper material; 3) Flexible Electronics, the possibility to fabricate on plastic substrate and make a fully flexible E-Paper Display, including the integrated electronics.

**Laboratory** : Computer Engineering

Codenumber : CE-MS-2009-01

Committee Members :

Advisor: Dr. Ir. A. van Genderen, CE, TU Delft

Advisor: Dr. R. Ishihara, ECTM, TU Delft

Chairperson: Dr. K.L.M. Bertels , CE, TU Delft

Member: Dr. J.S.S.M. Wong, CE, TU Delft

I would like to dedicate this thesis to my parents, may they rest in peace. Much love goes out to my brother Steven, for taking care of us in the absence of our parents.

# Contents

| $\mathbf{Li}$ | st of | Figures                                              | xi   |

|---------------|-------|------------------------------------------------------|------|

| $\mathbf{Li}$ | st of | Tables                                               | xiii |

| $\mathbf{A}$  | cknov | wledgements                                          | хv   |

| 1             | Intr  | roduction                                            | 1    |

|               | 1.1   | Motivation                                           | 1    |

|               | 1.2   | Project Goals                                        | 3    |

|               | 1.3   | Project Organization                                 | 3    |

|               | 1.4   | Thesis Organization                                  | 4    |

| 2             | The   | Technologies                                         | 5    |

|               | 2.1   | $\mu$ -Czochralski Single Grain Thin-Film Transistor | 5    |

|               |       | 2.1.1 SG TFT Process Steps                           | 6    |

|               |       | 2.1.2 SG Thin-Film Transistor performance            | 8    |

|               |       | 2.1.3 Standard Cell Library for Digital Logic        | 8    |

|               |       | 2.1.4 High Voltage Transistors                       | 10   |

|               | 2.2   | Quick-Response Liquid Powder Display                 | 10   |

|               |       | 2.2.1 The Liquid-Powder                              | 11   |

|               |       | 2.2.2 QR-LPD Structure                               | 13   |

|               | 2.3   | Summary                                              | 14   |

| 3             | The   | Electronic Paper Display                             | 15   |

|               | 3.1   | Display Driving Scheme                               | 15   |

|               |       | 3.1.1 Passive or Active Matrix?                      | 15   |

|               | 3.2   | Write and Erase                                      | 17   |

|               |       | 3.2.1 Erase before Write                             | 18   |

|               | 3.3   | Structure of this E-Paper Display                    | 19   |

|               | 3.4   | Display Interface Signals                            | 19   |

|               | 3.5   | Specifications of our E-Paper Display                | 21   |

|               | 3.6   | Conclusions                                          | 22   |

| 4             | Imp   | elementation of the Electronics                      | 23   |

|               | 4.1   | Display Organization                                 | 23   |

|               | 4.2   | Low Voltage Components                               | 24   |

|               |       | 4.2.1 Display Driver                                 | 24   |

|               |       | 4.2.2 Pattern Generator                              | 27   |

|               |       | 4.2.3 Ring Oscillator                                | 28   |

|               |       | 10.1 D #                                             | 0.0  |

|   | 4.3  | High Voltage Components                              | 29              |

|---|------|------------------------------------------------------|-----------------|

|   |      | 4.3.1 Active Matrix Backplane                        | 30              |

|   |      | 4.3.2 High Voltage Level Shifter                     | 32              |

|   |      | 4.3.3 Digital to Analog Converter                    | 32              |

|   | 4.4  | E-Paper Simulator                                    | 34              |

|   | 4.5  | Conclusions                                          | 36              |

| 5 | The  | Process of Design and Implementation                 | 39              |

|   | 5.1  | Design Exploration                                   | 39              |

|   | 5.2  | Structured Design                                    | 40              |

|   | 5.3  | Synthesis                                            | 40              |

|   |      | 5.3.1 Synthesis of Pattern Generator                 | 41              |

|   | 5.4  | Layout                                               | 42              |

|   |      | 5.4.1 Layout of Data Unit                            | 43              |

|   |      | 5.4.2 Layout of Comparator                           | 45              |

|   | 5.5  | Verification                                         | 46              |

|   |      | 5.5.1 Simulation                                     | 47              |

|   |      | 5.5.2 LVS                                            | 47              |

|   |      | 5.5.3 DRC                                            | 48              |

|   | 5.6  | Timing Analysis                                      | 48              |

|   | 5.7  | Conclusions                                          | 49              |

| 6 | Tost | t Circuits                                           | 51              |

| U | 6.1  | Digital Circuits                                     | 51              |

|   | 0.1  | 6.1.1 Output Buffer                                  | 51              |

|   |      | 6.1.2 Ring Oscillator                                | 51              |

|   |      | 6.1.3 4 bits Counter                                 | $\frac{52}{52}$ |

|   |      | 6.1.4 Logic Cells                                    | $\frac{52}{52}$ |

|   | 6.2  | Test Results                                         | $\frac{52}{52}$ |

|   | 0.2  |                                                      | 53              |

|   |      | 6.2.1 Ring Oscillator measurement results            | 56              |

|   |      | 6.2.3 The 4 bits Counter results                     | 59              |

|   | 6.3  |                                                      |                 |

|   | 6.4  | Short Circuit                                        | 61              |

| _ |      |                                                      |                 |

| 7 |      | rent State of Development                            | 63              |

|   | 7.1  | Progress                                             | 63              |

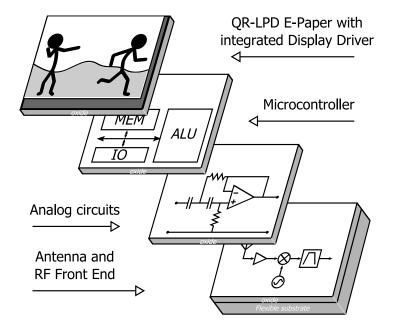

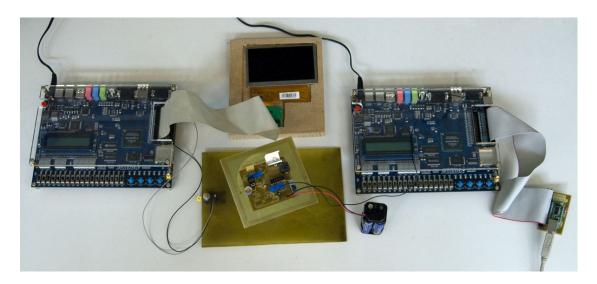

|   | 7.2  | A Practical example Product: Super E-Paper           | 64              |

|   | 7.3  | Considerations for Future SG Designs and Future Work | 65              |

| 8 | Sun  | nmary                                                | 67              |

|   |      |                                                      |                 |

| 9 | Con  | nclusions                                            | 71              |

| A            | bbrev | riations                              | 77         |

|--------------|-------|---------------------------------------|------------|

| $\mathbf{A}$ | Test  | Plan for the SG-TFT Digital Circuits  | <b>7</b> 9 |

|              | A.1   | Test plan ring_osc                    | 80         |

|              | A.2   | Test plan logic                       | 82         |

|              | A.3   | Test plan count123                    | 83         |

| В            | Die   | Photos of the SG-TFT Digital Circuits | 85         |

|              | B.1   | Ring Oscillator                       | 85         |

|              | B.2   | Logic Gates                           | 86         |

|              | B.3   | 4 Bits Counter                        | 86         |

# List of Figures

| 1.1  | A mockup of how the E-Paper Display will look like                                                                                                                                                                                                                        | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

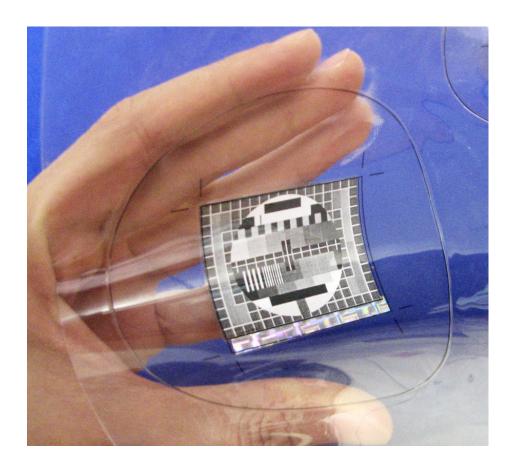

| 2.1  | The SG-TFT process: From the applied SiO <sub>2</sub> (b) on top of the substrate (a), a grain filter (c) is made. The a-Si (d) deposited and melted by an Excimer laser where a Single Grain is formed (e). On this Single Grain a PMOS Thin-Film Transistor is made (f) | 6  |

| 2.2  | • •                                                                                                                                                                                                                                                                       | 7  |

| 2.3  | 3D circuits integration concept                                                                                                                                                                                                                                           | 1  |

|      | X, Y, XY, C                                                                                                                                                                                                                                                               | 7  |

| 2.4  | Layout of cells in the Standard Cell Library. Starting from top left: inv,                                                                                                                                                                                                |    |

|      | inv4, inv16, nand2, nor2, dff, buf4 and buf16                                                                                                                                                                                                                             | 9  |

| 2.5  | Left: The Conventional structure; Right: The Lightly Doped Drain (LDD)                                                                                                                                                                                                    |    |

|      | structure;                                                                                                                                                                                                                                                                | 10 |

| 2.6  | A QR-LPD Display                                                                                                                                                                                                                                                          | 11 |

| 2.7  | The forces that work upon the Liquid-Powder particles                                                                                                                                                                                                                     | 12 |

| 2.8  | Graph showing the pixel reponse time of both white and black Liquid-                                                                                                                                                                                                      |    |

|      | Powder                                                                                                                                                                                                                                                                    | 12 |

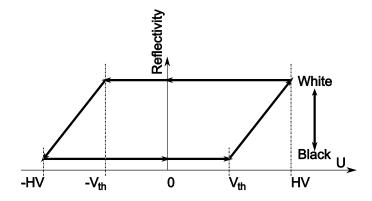

| 2.9  | Hysteresis plot, reflectivity versus applied voltage. (HV stands for High                                                                                                                                                                                                 |    |

|      | Voltage and $V_{th}$ for the Threshold Voltage.)                                                                                                                                                                                                                          | 13 |

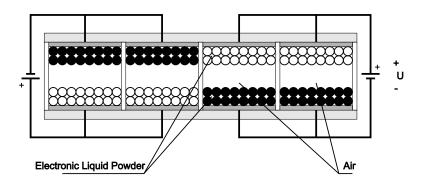

| 2.10 | Simple structure of the QR-LPD display here showing four pixels cells                                                                                                                                                                                                     | 13 |

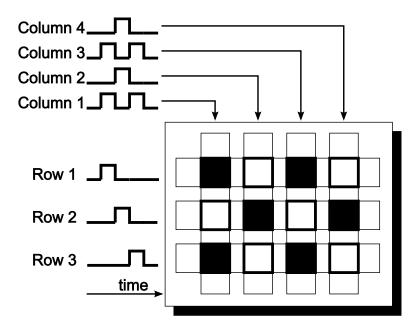

| 3.1  | Basic driving matrix scheme                                                                                                                                                                                                                                               | 16 |

| 3.2  | Basic Active Matrix schematic for four pixels                                                                                                                                                                                                                             | 17 |

| 3.3  | Top- One terminal drive: pixel electrode need both positive and negative                                                                                                                                                                                                  |    |

|      | voltages, the common electrode is grounded; Bottom- two terminal drive:                                                                                                                                                                                                   |    |

|      | only positive voltages needed for pixel electrode and common electrode                                                                                                                                                                                                    | 18 |

| 3.4  | Cross section of a pixel with a SG PMOS transistor                                                                                                                                                                                                                        | 19 |

| 3.5  | top: Horizontal timing for a single row; bottom: Vertical timing for whole                                                                                                                                                                                                |    |

|      | frame                                                                                                                                                                                                                                                                     | 20 |

|      |                                                                                                                                                                                                                                                                           |    |

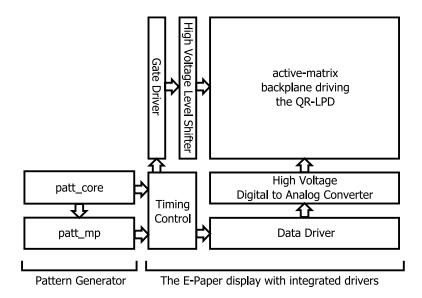

| 4.1  | A block diagram of the E-Paper Display with integrated drivers and ad-                                                                                                                                                                                                    |    |

|      | ditional circuits.                                                                                                                                                                                                                                                        | 24 |

| 4.2  | Movie Mode frame timing where the incoming image data is buffered                                                                                                                                                                                                         |    |

|      | before sending to the display. At the same time the upcoming row is                                                                                                                                                                                                       | 25 |

| 4.0  | erased before it gets written                                                                                                                                                                                                                                             | 25 |

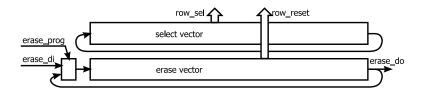

| 4.3  | Block diagram of the Gate Driver.                                                                                                                                                                                                                                         | 26 |

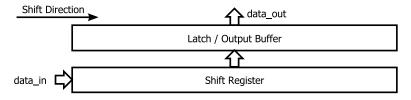

| 4.4  | Block diagram of the Data Driver                                                                                                                                                                                                                                          | 26 |

| 4.5  | The Display Driver with an build in Pattern Generator                                                                                                                                                                                                                     | 28 |

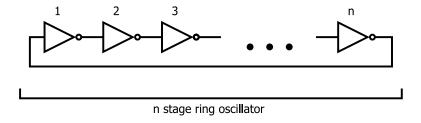

| 4.6  | Circuits of a n-stage ring oscillator, where n is the odd number of stages.                                                                                                                                                                                               | 28 |

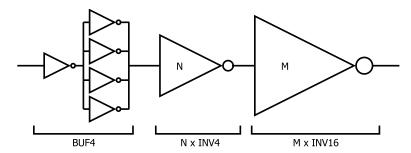

| 4.7  | Generic 4 stage buffer, with parameters N and M for the number of parallel                                                                                                                                                                                                | 00 |

|      | inverters                                                                                                                                                                                                                                                                 | 29 |

| 4.8        | Active Matrix schematic for four pixels                                                                                                                                                                               | 30       |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.9        | Cross section of a pixel with a SG PMOS transistor                                                                                                                                                                    | 31       |

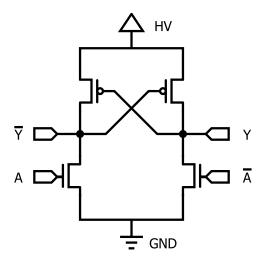

| 4.10       | Level shifter circuit. Input $A$ , ouput $Y \dots \dots \dots \dots \dots$                                                                                                                                            | 32       |

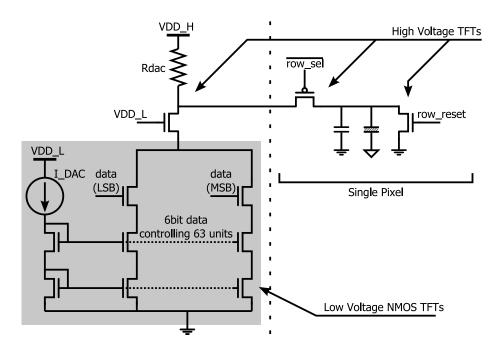

| 4.11       | Schematic of the current driven DAC (left) connected to a single pixel circuit (right). The pixel is modeled as a capacitor, and connected to a                                                                       | 0.6      |

| 4 10       | common electrode $V_{common}$                                                                                                                                                                                         | 33       |

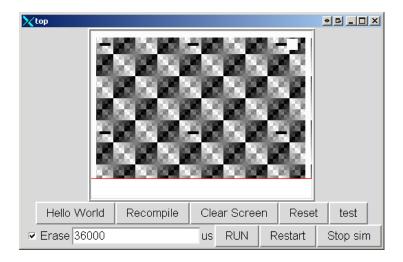

|            | The Modelsim E-Paper simulator written in Tcl/Tk. The line that is being erased is shown in red                                                                                                                       | 34       |

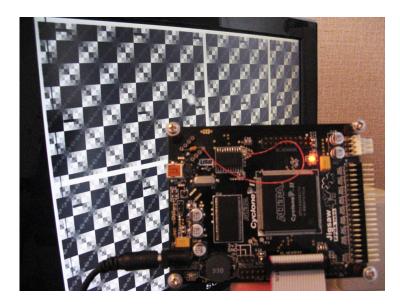

| 4.13       | The hardware E-Paper simulator running on FPGA. The content is put on a standard computer screen                                                                                                                      | 35       |

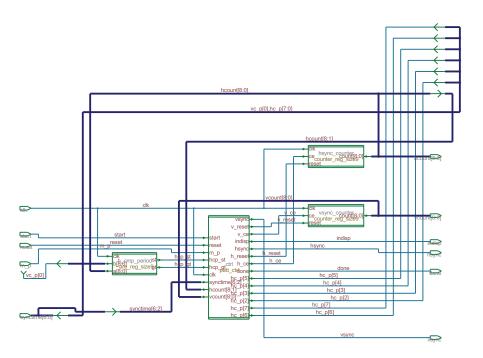

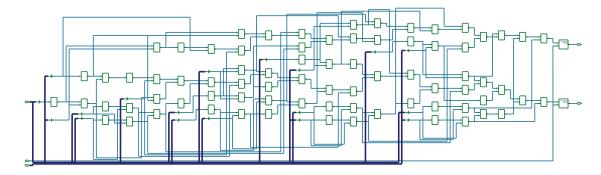

| 5.1        | Structural synthesis of the pattern generator core after re-structuring in the synthesis tool.                                                                                                                        | 41       |

| 5.2        | Behavioural synthesis of the pattern generator core                                                                                                                                                                   | 42       |

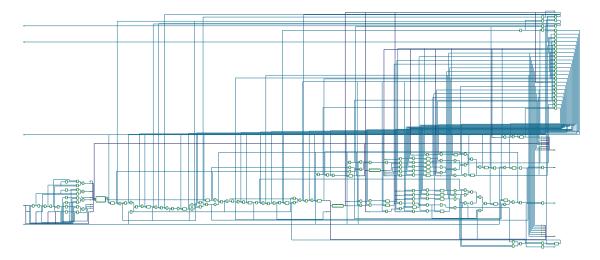

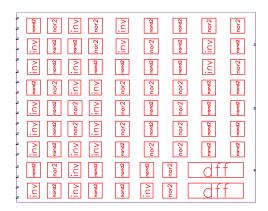

| 5.3        | The regular structure found in the schematics of the Data Unit                                                                                                                                                        | 43       |

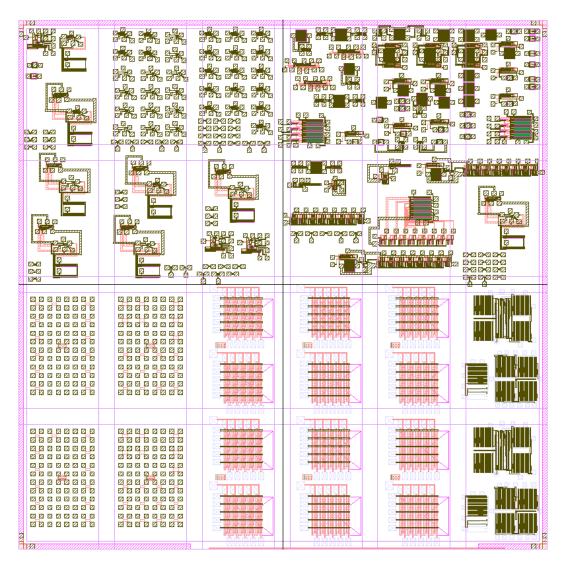

| 5.4        | The regular structured placement of the Data Unit                                                                                                                                                                     | 44       |

| 5.5        | A portion of the Data Driver, three the Data Units are seen here                                                                                                                                                      | 44       |

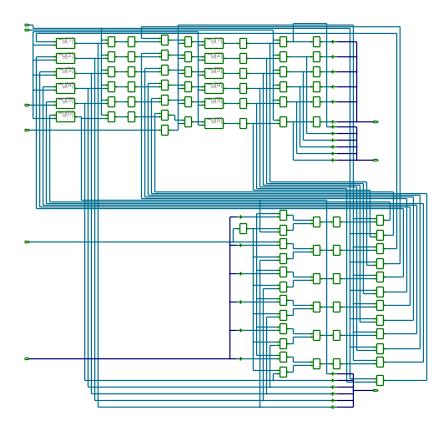

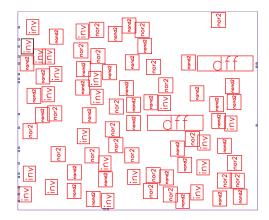

| 5.6        | The irregular structure of the 9 bit comparator                                                                                                                                                                       | 45       |

| 5.7        | The result of manual placing the 9 bit comparator                                                                                                                                                                     | 46       |

| 5.8        | The result of auto placing the 9 bit comparator, but unable to route                                                                                                                                                  | 46       |

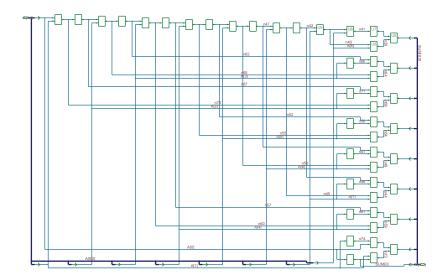

| 5.9        | Schematics of the incrementer, used in the Pattern Generator                                                                                                                                                          | 49       |

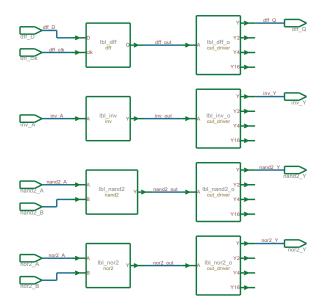

| 6.1        | Logic gates from the Standard Cell Library, each with an output driver connected to its output                                                                                                                        | 53       |

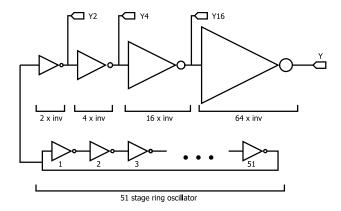

| 6.2        | Schematic of the 51-stage Ring Oscillator with intermediate output buffer                                                                                                                                             |          |

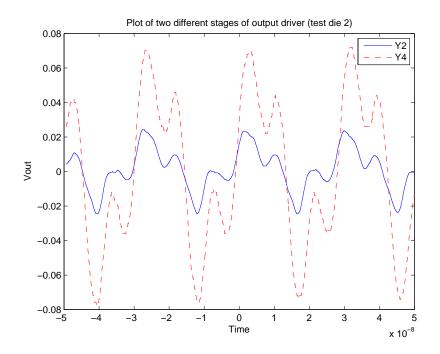

| 6.2        | signals                                                                                                                                                                                                               | 54<br>54 |

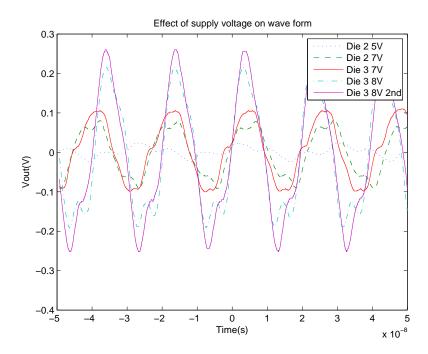

| 6.3<br>6.4 | Die 2 at 5V, directly measured with an oscilloscope on output Y2 and Y4.  Different oscillation wave form shapes, dependent on applied voltage and                                                                    | 94       |

|            | differs from die to die. The effects before and after overvoltage is seen in the two plots of die 3 at 8V                                                                                                             | 56       |

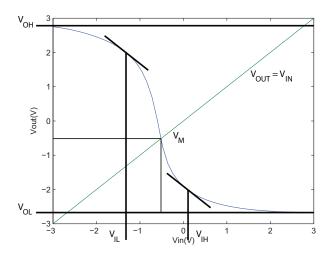

| 6.5        | Inverter voltage transfer characteristic                                                                                                                                                                              | 57       |

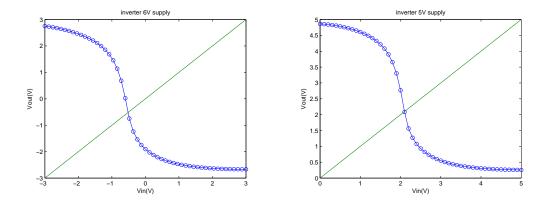

| 6.6        | Voltage Transfer Characteristics of the inverter. On the left $V_{dd}$ =3V and                                                                                                                                        | 01       |

|            | $V_{ss}$ =-3V; On the right $V_{dd}$ =5V and $V_{ss}$ =0V                                                                                                                                                             | 57       |

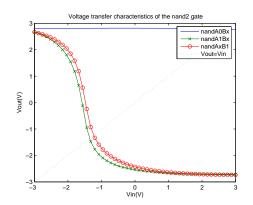

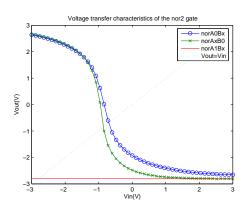

| 6.7        | Voltage Transfer Characteristics of the nand2 and nor2 logic gate. The x indicates the pin that is being changed                                                                                                      | 58       |

| 6.8        | Left: 'false' DRC error. Right: DRC violation leading to a short of two                                                                                                                                               | 61       |

| 6.9        | different nets                                                                                                                                                                                                        | 61<br>61 |

| 7.1        | Super E-Paper prototype: image data is send from PC via USB to the right FPGA. It then gets transmitted in a wireless fashion to the second FPGA on the left, connected to a LCD screen instead of an E-Paper screen. | 64       |

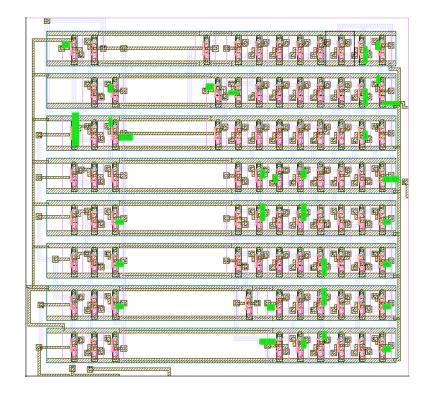

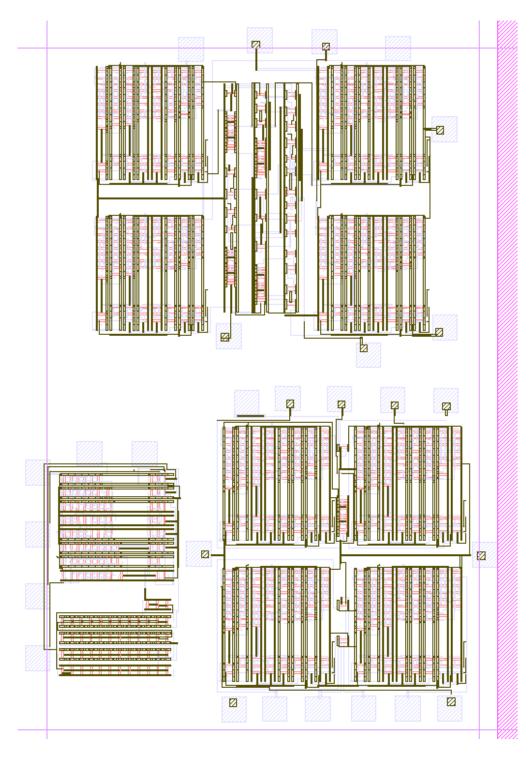

| A.1        | Photograph of the complete die with different test circuits, the digital test circuits are located on the bottom right.                                                                                               | 80       |

| A.2 | A closeup photo of the three digital test circuits. Top: count123; Left:                                                                        |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | ring_osc; Right: logic;                                                                                                                         | 81  |

| A.3 | The test pads with the correct labels. Left: ring_osc; Right: logic;                                                                            | 82  |

| A.4 | Test circuit count123 with labeled test pads                                                                                                    | 83  |

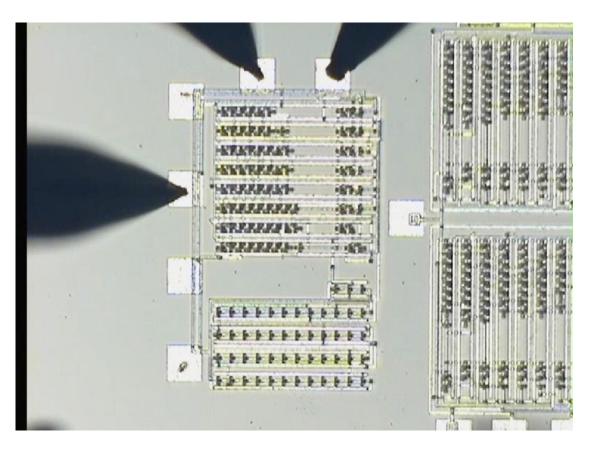

| B.1 | The 51-stage Ring Oscillator is at the bottom. At the top the output driver can be seen, together with the test pad for the intermediate buffer |     |

|     | , C                                                                                                                                             | 0.5 |

| ъ.  | stages                                                                                                                                          | 85  |

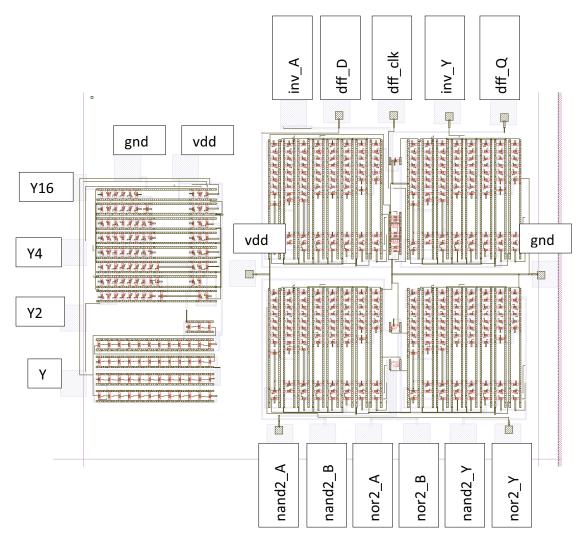

| В.2 | The logic gates: inv, nand2, nor2 and dff are in located the middle, placed                                                                     |     |

|     | in a vertical orientation. Four output buffers are seen in each of the                                                                          |     |

|     | corners, these are connected to the output of each logic gate                                                                                   | 86  |

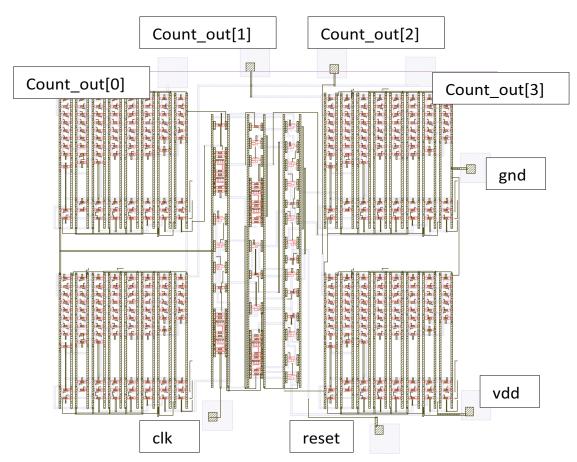

| В.3 | The 4 bits counter is seen in the middle, each bit had an associated output                                                                     |     |

|     | driver                                                                                                                                          | 86  |

|     |                                                                                                                                                 |     |

# List of Tables

|     | SG-TFT Performance Parameters                                             |    |

|-----|---------------------------------------------------------------------------|----|

| 2.2 | The Standard Cells Library                                                | 9  |

| 3.1 | E-Paper Signal Timing Specifications                                      | 20 |

| 3.2 | Desired E-Paper Specifications                                            | 21 |

| 4.1 | The range of the Digital to Analog Converter                              | 34 |

| 6.1 | Die 1 at 5V measured with a 1:10 probe on different output pins           | 54 |

| 6.2 | Ring Oscillator measurement results of 3 dies                             | 55 |

| 6.3 | Inverter parameters with two different supply voltages. All values are in |    |

|     | Volts (V)                                                                 | 58 |

| 6.4 | Truth table for nand2 and nor2                                            | 58 |

| 6.5 | Parameters for the logic gates inv, nand2 and nor2. All values are in     |    |

|     | Volts (V)                                                                 | 59 |

| A.1 | Terminal pin names per test circuit                                       | 79 |

# Acknowledgements

First of all, I would like to thank my supervisor Arjan van Genderen for guiding me through my Master Thesis. I want to thank him for taking the time to give me useful advice all along this project and for proofreading my paper and this thesis.

I am grateful to Ryoichi Ishihara, for allowing me to take part in the developments of the SG-TFT E-Paper project. And also for assigning me to be the technical assistant for the Super E-Paper Bachelor group. Thank you for re-triggering my interests in analog electronic and semiconductor physics.

I also want to express my gratitude to Alessandro Baiano, for his time and efforts put in the measurements of digital test circuits, the frustrations and the joyful moments. And of course I would like to express my thanks to Nitz Saputra, for the fruitful discussions on the analog electronics.

As for the Super E-Paper Bachelor group, Michel Verhulst, Rico van Dongen, Sander Geursen, Daniel Petrarca and Vladimir Shirokov, I had a great time being the technical assistant. Thank you all for that wonderful barbecue, price money well spend in my opinion.

Last, but not least, I would like to give my special thanks to Stephan Wong and Koen Bertels for being part of my graduation committee.

Wei Man Chim Delft, The Netherlands January 27, 2009

Introduction

Since the first transistor was turned on that historic day, December  $23^{rd}$  1947, the researchers of Bell Laboratories would not have any idea what role the transistor will play after this historic event. After the point-contact transistor, many types of transistors were invented. Among these are Bipolar, JFET, MOSFET, TFT etc. The work described in this thesis is based on the new Single Grain Thin-Film Transistor (SG-TFT) made with  $\mu$ -Czochralski process, a special type of high performance TFT. An Electronic Paper display with integrated Display Drivers will be build using the SG-TFTs to show the possibilities with this technology.

This introduction chapter is organized as follows: Section 1.1 presents the motivation behind the presented work. Subsequently, project goals are identified in Section 1.2. Section 1.3 lists the persons involved with the development of the E-Paper Display. Section 1.4 concludes this introduction chapter with an overview of this thesis' organization.

### 1.1 Motivation

After the introduction of the transistor, electronic devices rapidly became part of the lives for most people all over the world. Nowadays, it is for them unimaginable to picture a world, without the ease and comforts these electronic devices offer them. The possibilities seem endless with electronics, and with the SG-TFT technology even flexible electronics are possible.

With the use of  $\mu$ -Czochralski Single Grain Thin-Film Transistor Technology [32], it is possible to fabricate TFTs at relative low-temperatures ( $<350^{\circ}$ ) with near SOI performances [27]. These SG-TFTs can be used for building analog, RF and digital circuits. With this technology it is possible to fabricate these circuits on flexible substrate for flexible electronics and it is possible to stack these SG-TFT circuits on top of each other for 3D integration of ICs [10]. Until now, only analog and RF [11] circuits are build and tested using these SG-TFTs. Digital circuits are not realized yet with this technology.

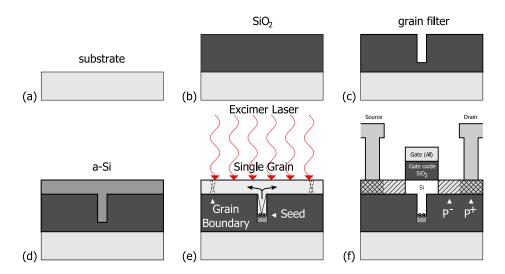

We want to build a flexible Electronic Paper (E-Paper) Display with the  $\mu$ -Czochralski SG-TFT technology. E-Paper is a display type that has a paper-like appearance (paper white, wide view angle) and can retain an image without power. The Display Driver will control a Quick-Response Liquid Power Display (QR-LPD) [17] as E-Paper material. A mockup of our E-Paper Display prototype can be seen in Figure 1.1. Although this is a mockup, the integrated Display Drivers can be seen on the edges. With this E-Paper Display we want to showcase the possibilities and versatility of the SG-TFT technology. The E-Paper Display Driver will be made solely using the SG transistors. Both analog and digital circuits are required for the Display Driver. A large part of the analog circuit needs to be designed for high voltages up to 70V, this is

required by the E-Paper material and a specially designed high voltage SG-TFT is used. For digital circuits, an automated design flow using a Standard Cell Library is essential for designing more complex digital circuits. Using this Standard Cell Library it is possible to design big and more complex devices like processors. It starts with a hardware description in HDL (Hardware Description Language), that then gets translated in logic gates based on the SG-TFT Standard Cell Library [36].

The versatility of the SG Technology showcased by the E-Paper Display is listed here:

- Mixed Signal: both Analog and Digital Circuits

- Standard Cell Library for Digital Circuits

- High Voltage SG-TFT (up to 70V)

- Flexible Electronics

Figure 1.1: A mockup of how the E-Paper Display will look like.

# 1.2 Project Goals

At the start of this project the main project goal was clear, to build an E-Paper Display with integrated Display Drivers using the Single Grain Transistors. To reach this goal, the project can be divided in the following different stages:

- First do the research and define what is needed and required by the QR-LPD E-Paper material. Using this information, define a organization for the Display Driver while keeping in mind that the implementation is done using the SG-TFT technology.

- 2. Second, investigate how the functional blocks of the organization can be implemented. Make clear distinction between the different implementation domains: digital analog, low voltage high voltage. And implement these functional blocks.

- 3. Since we want to make a real E-Paper Display, the implemented functional blocks need to be realized in silicon. Requiring a layout stage, to place and route the different components.

- 4. Make an E-Paper Display prototype.

- 5. Testing and measurements on the prototype to improve the SG Technology and future E-Paper Displays with integrated Display Drivers.

- 6. Next to the Display Driver, some simulation and development tools need to be made. For development of E-Paper applications without the E-Paper Display.

# 1.3 Project Organization

Since this E-Paper Display is made as a collaborative project, this thesis will also cover the work of others to give a complete view of the E-Paper Display development. The involvement of the persons directly related to the E-Paper Display development are listed as follows:

Person - Responsible for

R. Ishihara : E-Paper project leader

A. van Genderen : SG Standard Cell Library

A. Baiano : SG-TFT pixel cell and High Voltage SG-TFT

N. Saputra : Analog Circuit Design

W.M. Chim : Analog and Digital Circuits

# 1.4 Thesis Organization

The thesis is organized as follows. The E-Paper Display that is being developed here is based on two technologies. The Single Grain TFT Technology developed at DIMES for the integrated electronics and the QR-LPD E-Paper material from Bridgestone. The technology inner workings and operational principles are explained in Chapter 2. Based on constraints and requirements of the two technologies, the E-Paper Display driving concepts are made, and presented in Chapter 3. Keeping in mind what the constraints and properties are of the QR-LPD E-Paper material, and how it is possible to construct a feasible E-Paper Display using the SG-TFT technology. From these driving concepts, a functional block diagram is made of the complete E-Paper Display. The implementations of the functional blocks in the block diagram are presented in Chapter 4 together with the E-Paper simulator for development of E-Paper applications. Chapter 5 is a discussion about the process of design and implementation regarding to the digital parts of the Display Driver. These digital components follow the automated design flow: Starting of as VHDL files (a hardware description language); They get synthesized and mapped on to logic gates of the Single Grain Standard Cell Library; The Netlist of gates then get placed and routed for a chip layout. A test chip is made with various test circuits, the digital test circuits are described in Chapter 6, together with the test results of these circuits. In Chapter 7 the current state of development is presented and what still is needed to be done. Together with the future design considerations when designing digital circuits with the SG technology and a practical example of how the E-Paper can be used. Finally, this thesis is summarized in Chapter 8 and concluded in Chapter 9.

The Technologies

The E-Paper Display that we are developing at the TU Delft is based on two technologies. The first is the  $\mu$ -Czochralski Single Grain Thin-Film Transistor technology. This is used for the integrated electronics. The second is the Quick-Response Liquid Powder Display technology developed by Bridgestone, the E-Paper material for our E-Paper Display.

This chapter is organized in two sections, explaining the SG-TFT Technology (Section 2.1) and the QR-LPD E-Paper material (Section 2.2). The subsections of Section 2.1 will cover the following points: The SG-TFT process steps (Subsection 2.1.1), performance of SG-TFTs (Subsection 2.1.2) and the Standard Cell Library based on the SG-TFT technology for designing logic using EDA tools (Subsection 2.1.3). For Section 2.2 we have the following two subsections: The Liquid-Powder with its properties explained (Subsection 2.2.1) and the structure of the QR-LPD cells forming the E-Paper pixels (Subsection 2.2.2).

# 2.1 $\mu$ -Czochralski Single Grain Thin-Film Transistor

Transistors can be made out of different materials. Looking only at silicon transistors, it is possible to make them out amorphous silicon (a-Si), poly-crystalline silicon (p-Si) and single-crystalline silicon (c-Si) [13]. The difference is in the way how the silicon atoms are organized and are characterized by size of the ordered regions within the material. An ordered region is where the silicon atoms have regular geometric arrangement or periodicity. a-Si lacks such ordered regions, while p-Si have ordered regions, but vary in size and orientation with respect to one other. These ordered regions are called grains and separated from each other by grain boundaries. c-Si has a regular geometric periodicity throughout the entire material, all with the same grain (single grain). The c-Si electrical properties are superior compared to a-Si and p-Si, since c-Si lacks the grain boundaries that degrade the electrical characteristics, making it a suitable material for high performance transistors.

The Thin-Film Transistor (TFT) is a type of MOS transistor where the active semi-conductor material (silicon) is deposited as a thin-film over a supporting substrate. The substrate can be a large panel, for example glass, for making large LCD screens. Since the silicon is deposited, the type of silicon is limited to a-Si or p-Si type. In contrast, regular type MOS transistors are made from c-Si wafers. These wafers are grown from a single seed (by Czochralski process for example), and have regular geometric periodicity throughout the entire wafer.

The  $\mu$ -Czochralski Single Grain Thin-Film Transistor (SG-TFT) technology is a method to produce high performance transistors out of amorphous silicon by Excimerlaser crystallization. These SG-TFTs out perform the a-Si and p-Si TFTs, and yet the electrical performance is comparable to c-Si transistors [12]. SG-TFT technology has

Figure 2.1: The SG-TFT process: From the applied  $SiO_2$  (b) on top of the substrate (a), a grain filter (c) is made. The a-Si (d) deposited and melted by an Excimer laser where a Single Grain is formed (e). On this Single Grain a PMOS Thin-Film Transistor is made (f).

the advantage of high performance SG transistors that can be manufactured on a panel substrate, for example glass or plastic, with the possibility to use these transistors in analog, digital and RF circuits.

#### 2.1.1 SG TFT Process Steps

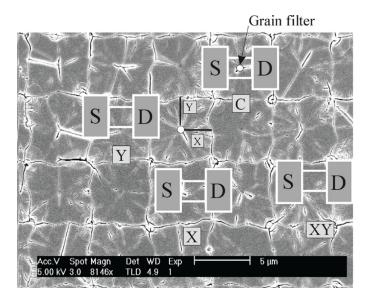

The first steps for making SG-TFTs is depicted in Figure 2.1. It starts with the creation of so called *single grains*, small islands of single grain silicon for making reliable TFTs on it. The process of making one single grain is illustrated in Figure 2.1. We start of with a substrate, were SiO<sub>2</sub> is deposited on top. Small cavities are patterned in the SiO<sub>2</sub>, these cavities are called the grain filters. A layer of a-Si is deposited on top, covering everything and filling up the cavities. An Excimer laser is used to crystallize the silicon: the laser partially melts the a-Si, the bottom of the cavities stays unmelted and forms the seed for the crystallization of the upper silicon. The grain filter ensures that the crystallization is grown from a single grain. The result can be seen in Figure 2.3, where the single grains form a grid and the grain filters can be found in the middle of each square shaped single grain. Inside these grains, source and drains are made by implanting with phosphorus and boron for NMOS SG-TFT and PMOS SG-TFT respectively. Ideally, these islands are of a single grain. Although planar defects are present inside the single grain, it has been reported that these defects are less active than random grain boundaries [19] [20]. These planar defects often grown out the grain filter radially [28] and can be seen in Figure 2.3. It is possible to place the transistor channel parallel to these planar defects so that the current flow does not cross these defects, resulting in a higher mobility for better transistors. In Figure 2.3, the transistor placed in position X has the highest field effect mobility.

Figure 2.2: 3D circuits integration concept.

All the fabrication steps can be done at relatively low temperatures (<350°). This makes it possible to fabricate SG-TFT on cost-effective plastic substrate for flexible electronics. In our case a flexible display with integrated display drivers. Another advantage of this technology is that it is possible to stack SG-TFTs on top of each other. A concept of this can be seen in Figure 2.2, each layer is used for a different purpose; display, digital, analog and RF electronics.

Figure 2.3: SEM image of a grid of grains formed by the  $\mu$ -Czochralski process. Different TFT channel orientation with respect to the grain filter with positions X, Y, XY, C.

## 2.1.2 SG Thin-Film Transistor performance

The SG Thin-Film Transistor have better electrical characteristics compared to the a-Si and p-Si transistors. Near SOI\* performance have been reported [27], with high field effect mobility ( $\mu_{FE}$ ) of average 600 cm<sup>2</sup>/Vs and 270 cm<sup>2</sup>/Vs for n-channel and p-channel respectively. In Table 2.1 the performance parameters the mobility ( $\mu_{FE}$ ), subthreshold swing (V/dec), threshold voltage (V) and off-current (A) are seen for both NMOS and PMOS SG-TFTs [12].

### Field Effect Mobility

One of the most important parameters to characterize TFTs is the Field Effect Mobility  $(\mu_{FE})$ . The mobility relates the carrier (electron or hole) velocity to the electric field (expressed in  $\mu_{FE}$ ).

#### Subthreshold Swing

The subthreshold swing slope factor S describes the quality of the turn-on characteristics. The slope factor S defines the amount of gate voltage needed to change to drain current by a factor of 10 (expressed in V/dec). For digital applications, an ideal switch-like behavior is desired. An ideal transistor has a S parameter of 60 mV/dec.

### Threshold Voltage

The gate-source voltage at wich conduction appears in the channel is called the threshold voltages. A low threshold voltage is desired, so that the TFT operational regime is within a reasonal voltage range.

#### **Off-Current**

The off-current is the minimum current in the transfer characteristics of the TFT. It is the current that still is present when the TFT is off.

| SG-TFT<br>Device | $egin{aligned} \mathbf{Mobility} & \mu_{FE} \ (\mathbf{cm}^2/\mathbf{Vs}) \end{aligned}$ | $\begin{array}{c} \textbf{Sub-threshold} \\ \textbf{Swing} \ (\textbf{V}/\textbf{dec}) \end{array}$ |      | $\mathbf{I}_{off}(\mathbf{A})$ |

|------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|--------------------------------|

| NMOS             | 600                                                                                      | 0.2                                                                                                 | 0.5  | $1.3 \cdot 10^{-13}$           |

| PMOS             | 270                                                                                      | 0.13                                                                                                | -2.3 | $1.10^{-14}$                   |

Table 2.1: SG-TFT Performance Parameters.

## 2.1.3 Standard Cell Library for Digital Logic

It is possible to design digital circuits manually, connecting transistors in CMOS pairs to make digital circuits. When the circuits gets larger, the manual labor grows dramatically, and mistakes are easily made. To make the SG-TFT technology useful for future large

<sup>\*</sup>Silicon On Insulator technology, used to reduce parasitic device capacitance and thereby improve transistor performance.

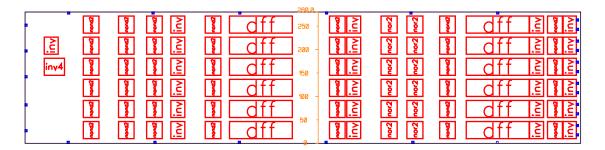

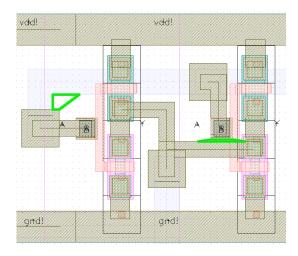

Figure 2.4: Layout of cells in the Standard Cell Library. Starting from top left: inv, inv4, inv16, nand2, nor2, dff, buf4 and buf16.

scale digital circuits, an automated design design flow is needed. A SG Standard Cell Library is made based on previous work [36], this library consists of a number of standard logic cells. With this Standard Cell Library it is possible to map digital circuits on to the logic cells based on SG-TFTs using EDA tools.

Table 2.2: The Standard Cells Library.

| Type of cell | Cell name | Cell description    |

|--------------|-----------|---------------------|

|              | inv       | Inverters with      |

| Inverters    | inv4      | different sizes     |

|              | inv16     | 1, 4 and 16.        |

| NAND Gate    | nand2     | Two ports NAND Gate |

| NOR Gate     | nor2      | Two ports NOR Gate  |

| Flip-Flop    | dff       | D Type Flip-Flop    |

| Buffers      | buf4      | Buffer with         |

| Dullers      | buf16     | sizes 4 and 16.     |

The library currently consists only of a few standard cells. This is because the SG-TFT technology is still under development, and adjustments to improvements the technology are expected in the future. This means that the standard cells will need to be modified as well, and by limiting the number of standard cells, the amount of work needed to update the library is reduced. Once the technology is matured enough, a more complete library can be made with more standards cells, for a better and optimized logic mapping. The currently library consists of inverters, NAND gate, NOR gate, flip-flop and buffers. The complete list of cells can be seen in Table 2.2.

## 2.1.4 High Voltage Transistors

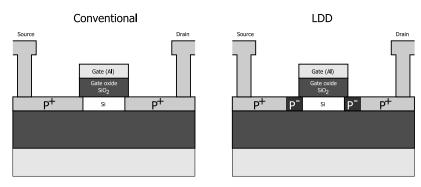

The E-Paper material requires a high driving voltage of 70V (see next Section 2.2). This high voltage will cause breakdown and destroy the normal SG-TFTs. Compared to a normal transistor, the specifically designed high voltage transitor has a thicker gate oxide and a change in doping profile(see Figure 2.5). By introducing lighter doped regions, the peak electric field in the space charge region is reduced and the breakdown and hot electron effects are minimized. Besides the obvious additional process steps, LDD devices have another disadvantage, the increase in drain resistance. However, the result is a transistor with LDD profile will show significant performance improvement under high voltages. In the cross section it can be seen that the source terminal is also in a lightly doped region. This does not improve transistor performance, but reduces fabrication complexity.

Figure 2.5: Left: The Conventional structure; Right: The Lightly Doped Drain (LDD) structure;

Because the low voltage and high voltage transistors are made with the same process some design considerations had to be made. It is possible to make gate-oxides with two different thicknesses in the same process (30nm and 300nm for low voltage and high voltage respectively). In order to reduce cost and manufacturing complexity, all the transistors are LDD type TFTs, even though this is not beneficial for the low voltage transistors.

# 2.2 Quick-Response Liquid Powder Display

With the introduction of the personal computer in office environment, some people believed that the PC will make paper redundant for routine tasks such as record-keeping and bookkeeping, creating a paperless office, the office of the future. Contrary to this paperless office vision, the introduction of the computer has led to an increase of paper usage. Due to the preference of many people who prefer reading e-mails and documents off paper rather than reading off the computer screen. With sufficient lighting, the strain on the eyes is minimal when reading off paper, while reading off the computer screens can get uncomfortable for extended periods of time.

An ideal Electronic Paper (E-Paper) display has a paper-like appearance with all the advantages of paper, when reading off of it. The Japanese company Bridgestone

Figure 2.6: A QR-LPD Display.

has developed a new *Electric Liquid-Powder* suitable for making E-Paper Displays, the QR-LPD (Quick-Response Liquid Powder Display). The Liquid-Power is a high-fluidity material, a combination of powder and liquid properties and is highly sensitive to electric fields. QR-LPD has a paper like appearance and has shown excellent image stability, quick response, high resolution, clear threshold characteristics and low power consumption [39]. And with the simple display structure a cost effective display can be made, making QR-LPD and ideal technology for electronic paper displays.

The Subsection 2.2.1 will describe the properties of the Liquid-Powder and what forces the particles are subjected to, and in Subsection 2.2.2 the structure of the QR-LPD is explained.

#### 2.2.1 The Liquid-Powder

The new developed material by Bridgestone behaves like a liquid despite its powder form. Two types of powders were developed: a white colored powder with a negative charge, and a black colored powder with a positive charge. The two powders are attracted to each and make a gray mass. The Liquid-Powder is moved when subjected to an electric field, white particles are attracted to the positive electrode and black particles are drawn to the negative electrode.

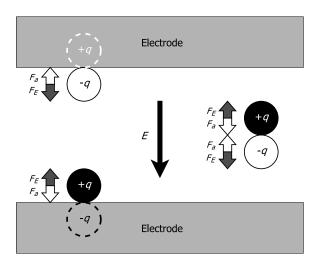

The forces that work on these particles are summed up in Figure 2.7, with the two different colored and different charged powders. The charge is intrinsic to the particle itself, and does not require external friction to obtain this charge. The attractive force  $F_a$  is the force that attracts the positive and negative particles. This attractive force  $F_a$  consists of the Coulomb force  $F_q$  and the Van der Waals force  $F_v$ . At the surface of the electrode, the attractive force is similar but with an additional force: The image charge force, due to the polarization of the electrode by the charged particle. These attractive and repulsive forces between particles and electrodes make the QR-LPD bistable, and are able to retain an image on the display without power. When a voltage potential is put across the electrodes, the electric field E acts as a repulsive force to the pair of oppositely charged particles. The pair of particles will separate when the electric field force  $F_E$  is strong enough to overcome the attractive force  $F_a$ . The particles then travels

Figure 2.7: The forces that work upon the Liquid-Powder particles.

Figure 2.8: Graph showing the pixel reponse time of both white and black Liquid-Powder.

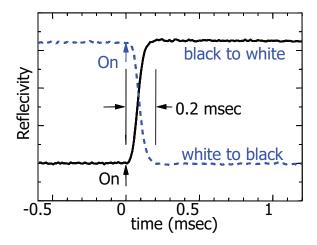

to the electrode of opposite charge with respect to the charge of the particle it self. The same principle holds for separating particles from electrode. The attractive force is represented by  $F_a = F_q + F_v = k q^2/r^2 + F_v$ . The electric field force is given by  $F_E = qE$ , where q is the charge of the particle. When particles travel from one electrode to the opposide one, the particles accelerate to high speeds. It has been reported that the particle transfer speed was over 11.11m/sec ( $\sim 40$ km/hour) [39]. This high speed transfer results in a fast pixel response of about 0.2 ms for both white tot black and black to white pixel transistion seen in Figure 2.8.

The bistable nature of the Liquid-Powder particles is observed in the hysteresis plot in Figure 2.9. The threshold voltage can be seen very clearly. Depending on the current state of the particles, the applied voltage can move the particles to a new state. The QR-LPD requires a relative high driving voltage of 70V, the threshold voltage to overcome the attractive force is about 35V. The voltage potentials between 35V and 70V is interesting

for gray-scale levels, it does not make any sense to have full control over 0V to 70V since everything below the threshold level will not have any effects on the Liquid-Powder.

Figure 2.9: Hysteresis plot, reflectivity versus applied voltage. (HV stands for High Voltage and  $V_{th}$  for the Threshold Voltage.)

### 2.2.2 QR-LPD Structure

The structure of the QR-LPD is shown in Figure 2.10. In a single cell there are the two types of powders (negatively charged white powder and positively charged black powder) and plain air to fill the remaining space of the cell. Two electrodes on top and bottom generate an electric field. With this electric field the Liquid-Powder can be controlled. When applying a negative voltage over a cell, the top electrode will attract the black particles and the top of the cell will turn black. And when a positive voltage is applied to a cell, the white particles will move to the top electrode making the cell top white. The powder particles can move fast through the air within the cell, resulting in an ultra fast pixel response time of 0.2ms. With this simple cell structure a roll-to-roll manufacturing process is possible [24] for efficiently making inexpensive flexible QR-LPD.

Figure 2.10: Simple structure of the QR-LPD display here showing four pixels cells.

# 2.3 Summary

Two technologies were discussed in this chapter, the  $\mu$ -Czochralski Single Grain Thin-Film Transistor (SG-TFT) technology and the Quick-Response Liquid Powder Display (QR-LPD). By combining these two technologies, we want to make a Flexible E-Paper Display.

The SG-TFT technology is used to make high performance transistors out of a-Si (amorphous silicon) by Excimer-laser crystallization. The electrical performance of these SG-TFTs are comparable to single-crystal transistors. These TFTs can be used for analog, RF and digital circuits. All the fabrication steps can done at relatively low temperatures ( $<350^{\circ}$ ). This makes the SG-TFT Technology suitable for electronics on glass substrate or cost effective plastic substrate for flexible electronics. It is even possible to stack TFTs on top of each other, for making 3D chips. High electrical performances have been reported, with field effect mobility ( $\mu_{FE}$ ) of average 600 cm<sup>2</sup>/Vs and 270 cm<sup>2</sup>/Vs for n-channel and p-channel respectively. For digital circuits, a small Standard Cell Library is made with a few logic gates, buffers and a flip-flop. This library is used to design digital circuits according to an automated design flow. High voltage TFTs are also designed, capable of surviving voltages of up 70V. These transistors are needed to control the E-Paper material.

The QR-LPD developed by Bridgestone has a paper-white appearance with high contrast and high reflectivity, suited to be used for E-Paper Displays. The QR-LPD uses a new developed Liquid-Powder. This powder is electrical sensitive and combines the properties of both powder and liquid. The QR-LPD Display is build up out of cells that contains of a black and white Liquid-Powder mixture. These powders are of opposite charge, negatively charged white powder and positively charged black powder. By applying an electric field the Liquid-Powder can be controlled. The powder particles can move fast through the air within the cell, resulting in an ultra fast pixel response time of 0.2 ms. The QR-LPD requires a relative high driving voltage of 70V with a clear threshold voltage of 35V. The bistable nature of the Liquid-Powder makes the QR-LPD retain its image after writing and even when there is no power at all.

The Electronic Paper Display

Before designing anything, it is important to know what to design for, what the constraints and requirements are. This chapter will discuss the ways to control the E-Paper material given the constraints and properties of QR-LPD and knowing the limits of the technology. After this, some requirements or goals can be defined for the prototype display.

This chapter is organized as follows: In Section 3.1 the driving scheme is discussed for addressing the individual pixels in an efficient way. In Section 3.2 writing and erasing the E-Paper are discussed. How the SG-TFT electronics is connected to the QR-LPD material can be found in Section 3.3. The chosen specifications for interfacing the E-Paper display can be found in Section 3.4. Knowing how the QR-LPD material is controlled, some design goals are setup. The specifications can be found in Section 3.5.

# 3.1 Display Driving Scheme

The most straight forward way to control a plane of pixels is to control each pixel individually. This is of course not an efficient way to work, considering that each pixel will need its own set of separate wires. One way to control the pixels is to organize them in a matrix. Pixels can then be controlled at the borders of the plane and addressed by row and column lines. This is the most common way to address a display [9]. The number of wires required for a matrix organized display is now reduced to the sum of the number of rows and columns. This basic principle of controlling matrix organized display is depicted in Figure 3.1. A small matrix screen of 4 by 3 pixels is controlled by seven lines, four for the columns and three for the rows. The crossing of a column line with a row line will control the pixel on that position. Instead of writing each pixel one by one, it is faster and more practical to write a whole row at once. This is also seen in Figure 3.1 for a small  $4\times3$  screen, first the pixel data is put on the column lines. Next is to select a row, when a row is activated, the pixel data will be transferred to the pixels on the activated row. The result is that one row of pixels is written with the corresponding pixel data. For writing the whole display, these steps are repeated for the remaining rows.

#### 3.1.1 Passive or Active Matrix?

There are two common ways two address the pixels. Both methods can be used for the QR-LPD display. They are called Passive Matrix addressing and Active Matrix addressing. The situation depicted in Figure 3.1 can be considered to be passive matrix addressing. This is when the row and column lanes are directly used to control the pixels. In our display, the crossing of these lines will generate the required electrical field

Figure 3.1: Basic driving matrix scheme.

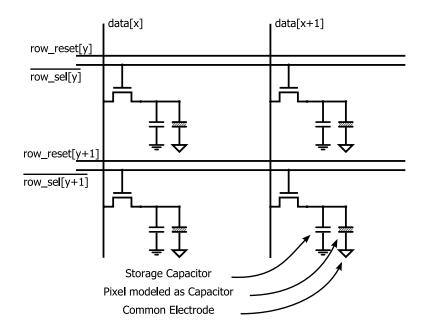

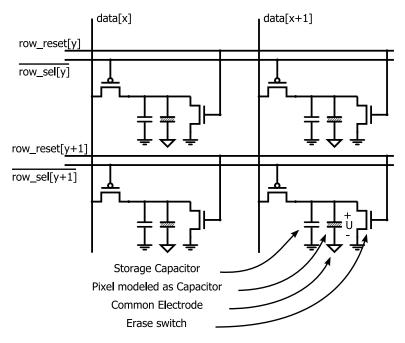

for the Liquid-Powder to change state. An active matrix addressed display works with transistors as switches for each pixel. Usually the rows of the display are connected to the transistor gates, and the columns wires are connected to the drains of the corresponding transistors. Each transistor is than controlling its own pixel. This structure can be seen in Figure 3.2 with the transistor connected to its pixel. When writing a line, a single row is activated. The transistors on that row will pass the voltage from columns to the pixels, writing a line. The rest of the pixels stay unchanged, because the transistors of those lines are not activated. The structure seen in Figure 3.2 is commonly found in the literature. The schematics also show the pixel modeled as an capacitor, and storage capacitor. In Chapter 4 Section 4.3.1 the final design of the Active Matrix schematic is explained.

The major advantage of Passive Matrix addressing its simplicity. Only horizontal and vertical wires are needed, stretching across the whole screen. A drawback of passive matrix addressing is the crosstalk among wires. This is more problematic for other types of displays than compared to QR-LPD, because the Liquid-Powder has a high and clear threshold voltage. QR-LPD is suitable for Passive Matrix addressing. A Passive Matrix addressed QR-LPD will most likely have three voltage levels or more, for example HV (70V) MV (35V) and GND (0V). The middle voltage level MV is needed, so that pixels can stay unchanged when they should not be written or erased. Ensuring that only the pixels on the activated row can have a potential difference higher than the threshold voltage (>35V), the other pixels not on the activated row may have voltages anywhere between 0V to 35V. Anything that is below the threshold level will not effect the pixels, and this is desired since we want to write only one row. Passive Matrix addressing with two voltage levels is not sufficient, pixels on the rows that are not activated can still be influenced by the pixel data on the column lines.

Figure 3.2: Basic Active Matrix schematic for four pixels.

Active Matrix addressing is not affected by cross talk. When writing a line, the transistors on that row ensure that the pixels are activated so that the column voltage will only go to these pixels. The other lines stay inactive, leaving the remaining display unchanged. Adding a storage capacitor per pixels, makes it more robust and less prone to noise. It is also possible to write an image faster compared to passive matrix addressing, it is not needed to wait the 0.2 ms per line for pixels to change state (see Figure 2.8 for the pixel response time). Therefore an higher frame rate is possible with Active Matrix addressing.

For our display we have decided to use the Active Matrix addressing, with the advantages of robustness and speed. The basic Active Matrix schematic of Figure 3.2 is modified: for each pixel a PMOS transistor is placed, activating the pixel when writing. This can be seen in a schematic shown in Figure 4.8 of Section 4. A NMOS transistor is also found in the schematics, this is for erasing the pixel. Write and Erased are explained in the upcoming section, Section 3.2.

### 3.2 Write and Erase

Writing and erasing pixels for the QR-LPD is done by applying an electric field. Depending on the current state of the pixel (e.g. black or white), an applied potential difference greater than threshold voltage will cause the Liquid-Powder to move and change the pixel state (to white or black for example).

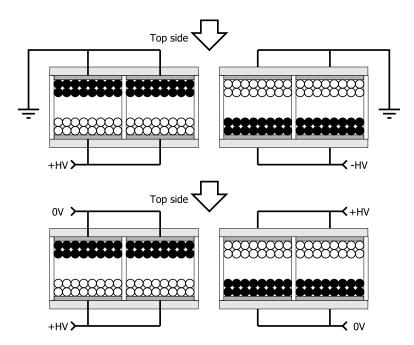

There are two ways to change the polarity (see Figure 3.3). The first is by changing only one terminal with the second terminal grounded. This means that the terminal than needs to switch between positive and negative voltage, and in our case +70V and -70V. The second option is to change both terminals, eliminating the need of negative

Figure 3.3: Top- One terminal drive: pixel electrode need both positive and negative voltages, the common electrode is grounded; Bottom- two terminal drive: only positive voltages needed for pixel electrode and common electrode.

voltages.

We have decided to go for the second option and control the potentials of the two terminals instead of dealing with negative voltages. The second option is more save, the voltage swing is at most 70V comparing to the 140V of the first option. By adding an additional transistor we can erase the pixel very easily. More on this can be read in section regarding the Active Matrix Backplane, Section 4.3.1.

# 3.2.1 Erase before Write

The QR-LPD can hold an image even when there is no power, this is due to the bistability properties of the Liquid-Powder. For most applications it is required to erase the screen before writing. You can compare this when using a black board for lectures. After the board is filled up, the professor needs to clean the board before continuing the lecture. A board that is overwritten multiple times without cleaning is useless for the students to take notes off. This also holds for the E-Paper Display. Although there are situations thinkable where it is not needed to erase before writing, but generally speaking, this is not the case.

We can define two use cases for our E-Paper: Picture mode and Movie mode. The first use case is when it is not required to update the images frequently. It can be used for displaying images (electronic photo frame), slide shows, e-book readers etc etc. The QR-LPD materials has ultra fast pixel response of 0.2 ms. We can use this property to display moving pictures with the E-Paper Display, hence Movie mode.

For the first use case, Picture mode, erase before writing is straight forward. Before

writing or updating a displayed image, the whole screen needs to be erased. This does not work well for Movie mode, when the frames (images) need to be updated multiple times per second. The display time of the first line will be longer than the display time of the last line. It is better to erase it line by line instead of the whole frame at once. This guarantees that all the lines get an equal amount of display time.

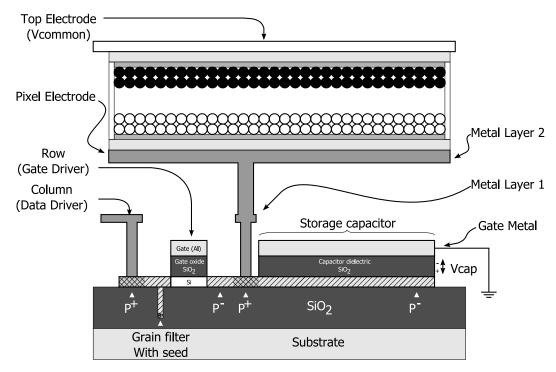

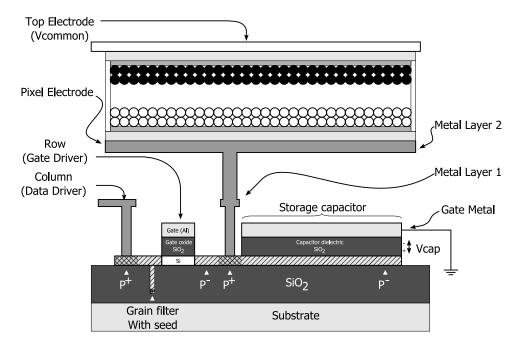

# 3.3 Structure of this E-Paper Display

The QR-LPD E-Paper material can be seen as polymer sheet with cells filled with black and white Liquid-Powder. The idea is to glue the E-Paper sheet on top of the Active Matrix Backplane to form an E-Paper Display. This can be seen in Figure 3.4 as a cross section of a single pixel. On the top of the E-Paper material, we have a common electrode. An ITO plane, both electrical conductive and optical transparent, called  $V_{common}$ . On the other side, at the bottom of each pixel, we have the other electrode connected to the source of the transistor corresponding to that pixel. With these two electrodes, it is now possible to apply a voltage across the QR-LPD cells, to generate an electric field to move the Liquid-Powder particles.

Figure 3.4: Cross section of a pixel with a SG PMOS transistor.

# 3.4 Display Interface Signals

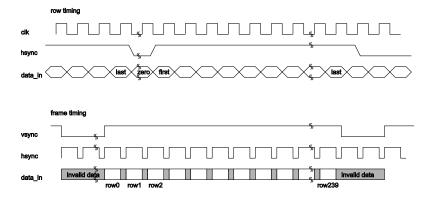

A display is useless without a proper defined communication interface. The communication interface for our E-Paper Display is based on the VGA monitor signals [3]. This

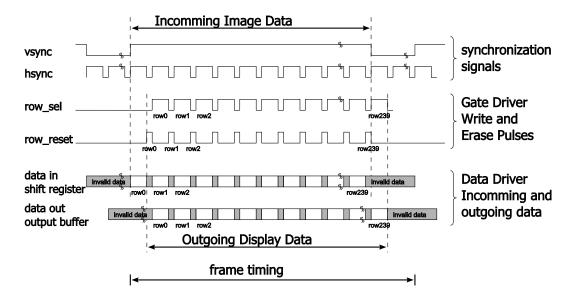

is an easy way to format the data for the display requiring only two synchronization control signals: hsync and vsync. In Figure 3.5 the wave forms can be seen that are based on the VGA monitor signals. The horizontal synchronization signal hsync (Top of Figure 3.5) synchronizes the incoming data, denoting the start of a row and the validity of the data when hsync is high. A low signal is given between two consecutive rows, this is called the horizontal sync pulse. For frame synchronization, we have the vertical synchronization signal vsync (Bottom of Figure 3.5). Similar to hsync, vsync marks the start of the frame, and the validity of the rows when vsync is high. A low signals is also given between two consecutive frames, this is called the vertical sync pulse. The VGA monitor signals has so called back porch and front porch parts in the sync signals, this is where the data is invalid even though the synchronization signal is high. The back porch and front porch are not defined in the E-Paper Display interface nor it can be found in Figure 3.5. The length of the horizontal and vertical sync pulse is not fixed. The Display Driver should be capable of handling sync pulses of at least one clock cycle for hsync and one line for vsync. For a 320×240 E-Paper screen, the signal timing specifications for the Display Driver can be found in Table 3.1.

Table 3.1: E-Paper Signal Timing Specifications.

| Row Timing        |                                |  |

|-------------------|--------------------------------|--|

| Pixel Data        | 320 clock cycles               |  |

| hsync pulse width | > 1 clock cycle                |  |

| Total row time    | hsync pulse + 320 clock cycles |  |

| Frame Timing      |                                |  |

| F)                | rame Timing                    |  |

| Lines             | rame Timing 240 lines          |  |

|                   | 0                              |  |

Figure 3.5: top: Horizontal timing for a single row; bottom: Vertical timing for whole frame.

# 3.5 Specifications of our E-Paper Display

Knowing the different aspects of the technologies we want to use and having a general idea of how an QR-LPD display can be constructed, we can compile a list of design goals for the prototype QR-LPD E-Paper Display with the integrated SG-TFT Display Drivers. The specifications are summed up in Table 3.2.

We want to design a monochrome E-Paper Display with the screen format of  $320\times240$  pixels (QVGA). Each pixel will have 64 gray-scale levels (6bits) and will be  $150\times150\mu\mathrm{m}$  big (about 170 pixels per inch). The viewable screen size will be  $4.80\times3.60\mathrm{cm}$ , a screen diagonal of 6.0cm (about 2.3inch). Our aim is to reach 25 frames per second, making it possible to view animations fluently. With the given number of pixels and the desired number of frames, we can determine the minimal operating speed. The number of pixels per frame multiplied with the frames per second results in minimal clock of 1.92 MHz. Why minimal clock? Because the sync pulses are not taken in to account. We can say that the system clock frequency will be at least 2 MHz.

For moving the Liquid-Powder particles, a high voltage of about 70V is required. To design all the electronics for 70V is not practical, the high voltage SG-TFTs are not as suited as the normal SG-TFTs for logic circuitry. It is better to design the digital part of the display driver using low voltage gates, and use high voltage electronics to drive the pixels. So there is a separation in driving electronics, low voltage and high voltage.

Table 3.2: Desired E-Paper Specifications.

| Display Specifications |                               |  |

|------------------------|-------------------------------|--|

| Pixel pitch            | $150~\mu\mathrm{m}$           |  |

| Pixels Per Inch        | 170 ppi                       |  |

| Screen format          | $320\times240~\mathrm{QVGA}$  |  |

| Screen size            | $4.80 \times 3.60 \text{ cm}$ |  |

| Screen diagonal        | 6.0 cm or 2.3 inch            |  |

| Gray-scale levels      | 64 levels 6 bits              |  |

| Frame rate             | 25 fps                        |  |

| Clock frequency        | 2 MHz                         |  |

| Logic voltage          | 5V                            |  |

| Driving voltage        | 70V                           |  |

## 3.6 Conclusions

This chapter discussed a way to control the E-Paper material given the constraints and properties of QR-LPD and knowing the limits of the SG-TFT technology. The concepts presented in this chapter form the bases for the implementation of the Display components.

Although QR-LPD is suited to be controlled with a Passive Matrix, an Active Matrix addressing is chosen. The Display Driver together with the Active Matrix Backplane will be made using the SG-TFT technology. With the advantage that the display will be less prone to noise and the possibility to write faster, compared to Passive Matrix, for higher frame rates. By controlling the E-Paper with the SG-TFT technology, it will be a nice demo platform to showcase the possibilities with this technology. The possibilities with a bistable screen requires extra care for writing and erasing. Two use cases are defined, for viewing still images: Picture Mode; and for viewing animation and videos: Movie Mode. An Erase before Write scheme is defined for the Movie Mode, to make sure that pixels are cleared and erased before rewriting them. The structure of the E-Paper Display is seen in Figure 3.4. The QR-LPD material will be glued on top of the Active Matrix Backplane. The Display Interface is based on the VGA timing signals, but not compatible. The interface is synchronized with two synchronization signals, horizontal hsync and vertical vsync similar to VGA. The Display Interface Timing Specifications are given in Table 3.1. And finally, the desired E-Paper Specifications are defined in Table 3.2.

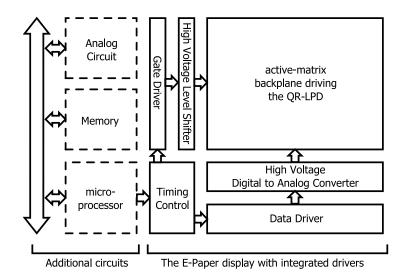

# Implementation of the Electronics

In the previous chapter, Chapter 3, we have seen how QR-LPD can be used to construct an E-Paper Display. With this as a starting point, we will further develop the basic concepts in to a feasible E-Paper implementation. Because the Liquid-Powder requires a high driving voltage, we have split the Display Driver in to two domains, the low voltage for digital circuits and high voltage for driving the QR-LPD.