# **EMC** oriented ISR design

# Wouter van der Heijden

A thesis presented for the degree of: Master of Science

Faculty Electrical Engineering, Mathematics and Computer

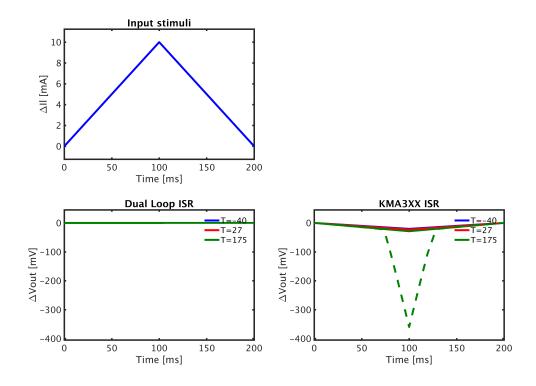

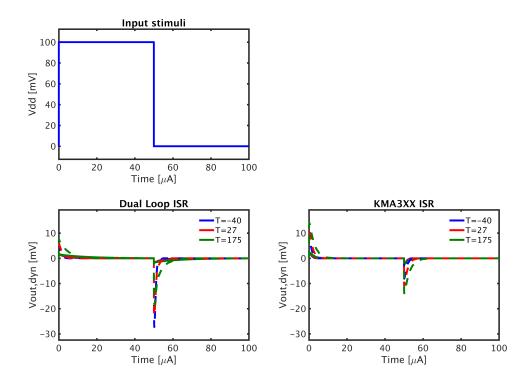

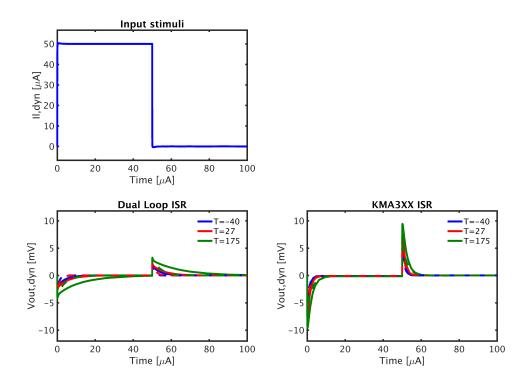

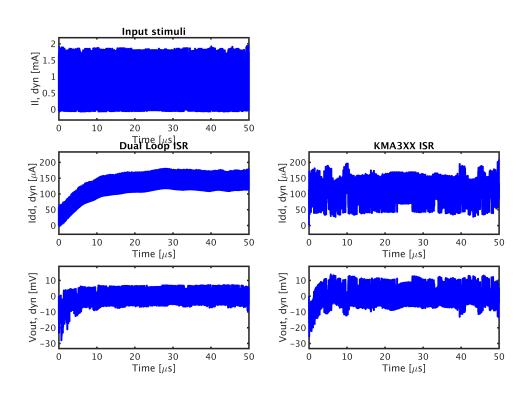

Science

Technical University Delft

The Netherlands

# **Abstract**

Electromagnetic Compatibility (EMC) is a growing issue in the automotive industry. Integrated Circuits (IC's) must adhere to strict Electromagnetic Emission (EME) and Electromagnetic Susceptibility (EMS) regulations to ensure safety in the automotive vehicle. The Internal Supply Regulator (ISR) plays a critical role in the EMC performance of an IC.

In this thesis, four types of linear regulator topologies are defined, based on the output stage: NMOS series, PMOS series, NMOS shunt, and PMOS shunt. Several important parameters are defined to describe the performance of a regulator. These are used to compare the four topologies. Only shunt regulators were found able to have good performance in both emission and Power Supply Rejection (PSR). Unfortunately, they come with some disadvantages, especially in power efficiency.

A dual loop concept is proposed in order to alleviate these disadvantages. The concept is analyzed on system level and specifications are determined for the system blocks. The system blocks were then implemented on circuit level. Simulations have been performed on each system block. They confirm an improvement in terms of emission and PSR compared to the ISR that is currently used within NXP. Especially the performance in emission shows great improvement; The attenuation for all frequencies in the band of interest is approximately 30dB. A power efficiency that is only slightly larger than the series topologies has been achieved.

# **Acknowledgements**

I would like to thank a number of people who have helped me through the challenging process of research and writing this thesis. The rough circumstances in my personal life has made your support more important than ever.

First of all, a lot of gratitude goes out to my daily supervisors at NXP: Daniele Raiteri and Marijn van Dongen. I could not have wished for better guidance during the project. You have spent time and effort to help me with my research, while operating in a busy working environment. Daniele, I really appreciate the time you took to be critical with my writing. You have helped me lift this thesis to a higher level. Marijn, thank you for your kindness and support. I will miss you as a colleague but wish you all the best during your new career overseas.

Special thanks to the person who gave me the opportunity to prove myself within NXP, Arjan Leeuwenburgh. Your management style, kindness and trust are exceptional. You have stood out for me in difficult times. For this, I am most grateful.

I would also like to thank the professors at TU Delft for their guidance during the project and the Microelectronics track. Although there is still a lot to learn, I believe I have been given the tools to continue on my own.

Last but not least, my dear family, who give me courage, love and full support. I will always keep you with me.

# **Contents**

| 1 | Intr     | oductio        | n                                            | 8            |

|---|----------|----------------|----------------------------------------------|--------------|

|   | 1.1      | Problei        | m statement                                  | 9            |

|   |          | 1.1.1          | Goal                                         | 9            |

|   |          | 1.1.2          | Scope                                        | 9            |

|   | 1.2      | EMC in         | n IC's                                       | 10           |

|   | 1.3      | Introdu        | uction to the ISR                            | 12           |

|   |          | 1.3.1          | Function                                     | 12           |

|   |          | 1.3.2          | Linear regulators versus switched regulators | 12           |

|   | 1.4      | Topolo         | ogies                                        | 14           |

|   |          | 1.4.1          | Open loop approach                           | 15           |

|   |          | 1.4.2          | The high voltage transistor                  | 16           |

|   |          | 1.4.3          | Non-ideal current source                     | 16           |

|   | 1.5      | Outline        | e of this thesis                             | 17           |

| _ | <b>D</b> | -              |                                              | 10           |

| 2 |          |                | ce of standard topologies                    | <b>18</b> 19 |

|   | 2.1      |                | mance parameters                             | _            |

|   |          | 2.1.1<br>2.1.2 | Power supply rejection                       | 19           |

|   |          |                | Emission                                     | 30           |

|   |          | 2.1.3          | Minimum drop-out voltage                     | 37           |

|   |          | 2.1.4          | Power efficiency                             | 39           |

|   |          | 2.1.5          | Load regulation                              | 40           |

|   |          | 2.1.6          | Line regulation                              | 41           |

|   |          | 2.1.7          |                                              | 41           |

|   |          | 2.1.8          | Line transient                               | 43           |

|   |          | 2.1.9          | Gain-Bandwidth Product                       | 44           |

|   | 0.0      | 2.1.10         |                                              | 49           |

|   | 2.2      |                | l comparison                                 | 49           |

|   | 2.3      |                | the KMA3xx family                            | 50           |

|   |          | 2.3.1          | Description                                  | 50           |

| 3 | Des      | ign of t       | the ISR                                      | 52           |

|   | 3.1      | System         | n design                                     | 53           |

|   |          | 3.1.1          | Concept                                      | 53           |

|   |          | 3.1.2          | Current regulation loop                      | 53           |

|   |          | 3.1.3          | Voltage regulation loop                      | 56           |

|   |          | 3.1.4          | Regulating loops interaction                 | 57           |

|   |          | 3.1.5          | Performance parameters                       | 60           |

|   |          | 3.1.6          | System overview                              | 71           |

|    |      | 3.1.7    | Start-up behavior              | . 73 |  |  |

|----|------|----------|--------------------------------|------|--|--|

|    | 3.2  | Circuit  | design                         | . 74 |  |  |

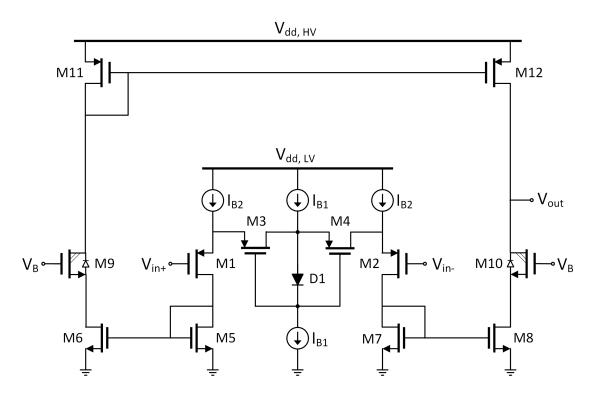

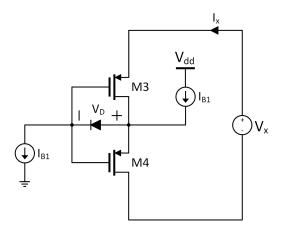

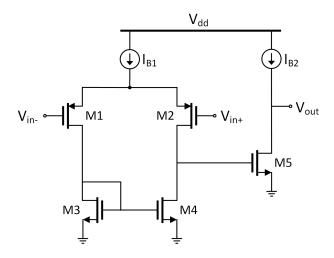

|    |      | 3.2.1    | TA1                            | . 74 |  |  |

|    |      | 3.2.2    | TA2                            | . 77 |  |  |

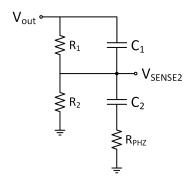

|    |      | 3.2.3    | Feedback network               | . 78 |  |  |

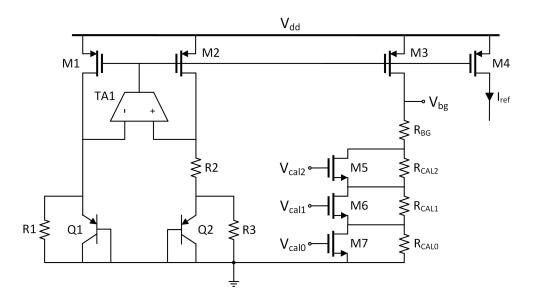

|    |      | 3.2.4    | Bandgap and current references | . 80 |  |  |

|    |      | 3.2.5    | Output stage MOS transistors   | . 81 |  |  |

|    |      | 3.2.6    | Capacitors                     | . 81 |  |  |

|    |      | 3.2.7    | Start-up circuit               | . 82 |  |  |

| 4  | Simi | ulations |                                | 84   |  |  |

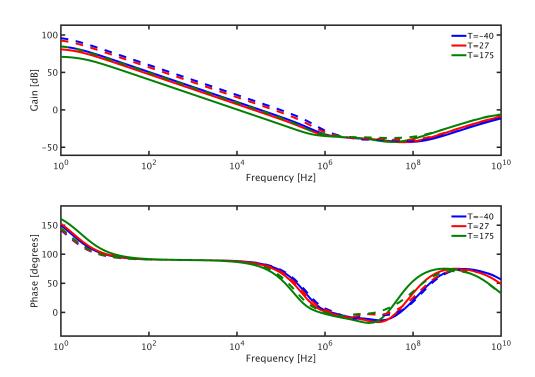

| -  | 4.1  |          | imulations                     | -    |  |  |

|    |      | 4.1.1    | Current regulation loop        |      |  |  |

|    |      | 4.1.2    | Voltage regulation loop        |      |  |  |

|    | 4.2  |          | nance parameters               |      |  |  |

|    |      | 4.2.1    | Power supply rejection         |      |  |  |

|    |      | 4.2.2    | Emission                       |      |  |  |

|    |      | 4.2.3    | Line regulation                |      |  |  |

|    |      | 4.2.4    | Load regulation                |      |  |  |

|    |      | 4.2.5    | Line transient                 |      |  |  |

|    |      | 4.2.6    | Load transient                 |      |  |  |

|    | 4.3  | _        | c transient load               |      |  |  |

|    | 4.5  | rteansti | C transient load               | , 50 |  |  |

| 5  | Con  | clusion  |                                | 98   |  |  |

|    | 5.1  | Contrib  | oution to science              | . 99 |  |  |

|    | 5.2  | Future   | activities                     | . 99 |  |  |

|    | 5.3  | Recom    | mendations for further study   | . 99 |  |  |

| Αp | pend | lix A N  | Natlab scripts                 | 100  |  |  |

| Αn | pend | lix B T  | ransistor models               | 108  |  |  |

| •  |      |          |                                |      |  |  |

| Δr | mena | 11 Y L I | mai ioon nroiect files         | 113  |  |  |

# List of Abbreviations

A-BCD Advanced Bipolar CMOS DMOS. A process used in the NXP auto-

motive branch. This work has also been implemented in the A-BCD

process.

CRL Current Regulation Loop. The feedback loop that regulates the DC

quiescent current  $(I_Q)$  to a certain reference current  $(I_{REF})$ .

ECU Engine Control Unit. Electrical unit inside the automotive vehicle that

interfaces between the sensors and the engine.

EMC Electromagnetic Compatibility. The situation where multiple elec-

tronic devices can function in the same environment without disturb-

ing one another.

EME Electromagnetic emission. Radiation caused by varying currents inside

a conductive object.

EMI Electromagnetic interference. Interferences that propagate through

non-conductive materials as electromagnetic radiation. Can be picked

up by other circuits and reduce their performance.

EMS Electromagnetic susceptibility. The vulnerability of an electric circuit

towards EMI.

GBW Gain-Bandwidth. The gain of an amplifier multiplied by its bandwidth

is a commonly used parameter to describe speed performance.

GO Used when referring to the Gate Oxide capacitor. This type of capac-

itor makes use of the capacitance between the poly silicon gate and

the substrate.

HV domain High Voltage domain. Circuit domain where the supply voltage ex-

ceeds 1.8V.

ISR Internal Supply Regulator. Circuit block that converts the external

supply voltage to an on chip supply voltage.

KCL Kirchoffs Current Law. Basic law stating that the amount of current

going in to a circuit node must be equal to the amount of current

going out of that node.

LP product Loopgain Poles product. Product of the loop gain and poles within a

feedback loop. This product can be used to estimate the bandwidth

capabilities of the loop.

LV domain Low voltage domain. Circuit domain where the supply voltage does

not exceed 1.8V.

MIM capacitor Metal-Insulator-Metal capacitor. A type of capacitor that utilizes the

capacitance between two metal layers.

PSR Power Supply Rejection. Small signal gain from the supply voltage to

the output node of the regulator.

PWM Pulse Width Modulator. A circuit block that converts an analog input

signal to a digital pulse width modulated output.

SOI technology Silicon on Insulator technology. Technology where the bulk of the

silicon wafer is separated from the thin top layer by an oxide layer. Has the advantage that certain areas on the wafer may be isolated

using STI.

TA Transconductance Amplifier. Amplifier that has a voltage input and

a current output.

UGF Unity Gain Frequency. The frequency at which the gain is equal to

unity.

VRL Voltage Regulation Loop. The feedback loop that regulates the out-

put voltage to a voltage proportional to a bandgap reference.

# Chapter 1

# Introduction

In the early days of the automotive industry, most systems where realized mechanically as electronic solutions were found too unreliable. The large boost in the IC industry has made it possible to make electrical systems more reliable with decreased manufacturing costs. The modern car is now equipped with a large number of smart sensors, some even fulfilling critical functions. For example, sensors are used in: engine control, brake control, tire pressure monitoring, transmission, and much more [3]. Some of these sensors can be located close to the engine or to the brakes, therefore they need to work in very harsh environment conditions: e.g. in contact with chemicals or in a wide temperature range spanning from -40°C up to 175°C. Furthermore components that are supplied from the car battery have to deal with large supply variations caused by e.g. cold cranking, ignition switch bounce, load dumps or other effects [1].

### 1.1 Problem statement

Sensors in the automotive vehicle are connected to the Engine Control Unit (ECU) by cable. These cables can reach lengths up to three meters and will emit and radiate electromagnetic fields. As the number of sensors in a single vehicle is increasing and the automotive safety requirements are harsh, Integrated Circuit (IC) designers face a challenging Electromagnetic Compatibility (EMC) problem.

### 1.1.1 Goal

The Internal Supply Regulator (ISR) is a circuit block that plays a key role in the EMC behavior of the IC. However, in a lot of ISR designs, the emphasis is on other specifications, e.g. power efficiency or drop-out voltage. EMC is often considered in the final phase of the design and adjustments are made if the requirements are not met.

The goal of this thesis is to increase the EMC performance of the ISR by considering EMC in an early stage of the design phase. The use of an external capacitor is undesired as it would substantially increase the total cost and size of the product. The ISR that is being used in the KMA3xx angular sensor family is chosen as a reference for performance.

## 1.1.2 **Scope**

The scope of this thesis is the design of an ISR with improved EMC performance. Only the core and startup circuitry of the regulator will be investigated, while other auxiliary circuits are not implemented or ported from the reference design. Examples of parts that will not be investigated are: the bandgap reference, circuits for testability, and calibration circuits. The bandgap reference of the reference design was re-used during the design of the new ISR.

The design is implemented in the Advanced Bipolar CMOS DMOS (A-BCD) process which is a Silicon On Insulator (SOI) technology supporting High Voltage (HV) applications. Table 1.1 shows the most interesting features of the process.

| Specification            | CMOS14 A-BCD |  |

|--------------------------|--------------|--|

| Minimum feature size     | $0.14\mum$   |  |

| Handle wafer             | SOI          |  |

| Metal layers             | 5            |  |

| Metal type               | Aluminum     |  |

| Gate Oxide thickness 1   | 2.9nm        |  |

| Gate Oxide thickness 2   | 7.2nm        |  |

| Vias                     | Tungsten     |  |

| Shallow Trench Isolation | yes          |  |

| Medium Trench Isolation  | yes          |  |

| MIM capacitors           | yes          |  |

Table 1.1: Specifications of the A-BCD process.

### 1.2 EMC in IC's

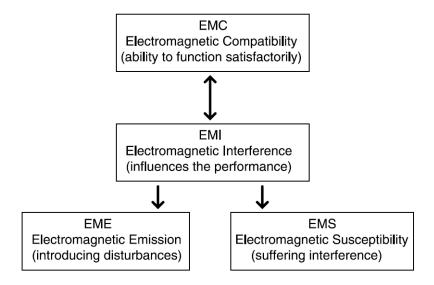

Before beginning to investigate proper design for EMC in the ISR, some fundamental knowledge about EMC in IC's is necessary. EMC can be described as the situation in which several electronic devices can operate simultaneously without affecting each others functionality. The need for EMC is caused by the existence of Electromagnetic Interference (EMI). In order to achieve an electromagnetic compatible situation, devices must conform to a set of rules regarding Electromagnetic Emission (EME) and Electromagnetic Susceptibility (EMS). The relations between these terms are shown in figure 1.1.

Figure 1.1: Interrelationships in EMC [5]

All conductive objects can both emit and radiate electromagnetic fields and thus behave as an antenna. The measure in which a conductive object will act as an antenna is dependent on the so called 'electrical length'.

Electrical

$$length = \frac{L}{\lambda} = \frac{fL}{c}$$

(1.1)

Conductors that have an electrical length smaller than 1/20 or even 1/50, in case of large impedance mismatches, can be considered to be electrically short [5].

Electrically short conductors can be accurately described by basic circuit theory. For electrically long devices, the effect of electromagnetism needs to be taken into account. Table 1.2 shows the electrical length of a set of relevant conductors in the functional setup of the IC.

It can be seen that for frequencies up to 1GHz, the IC tracks, IC bondwires, package leads and pins may be considered electrically short. The external wiring has a maximum length of 3 meters in the application and must be considered to be electrically long for frequencies above 5MHz.

|                     | Physical length    | EMI frequency | Electrical length |

|---------------------|--------------------|---------------|-------------------|

| IC tracks           | $10 \mu$ m- $1$ mm | 150kHz        | 0                 |

|                     |                    | 1GHz          | 0-0.003           |

| IC bondwires,       | 1mm-1cm            | 150kHz        | 0                 |

| package leads, pins |                    | 1GHz          | 0.003-0.03        |

| PCB tracks          | 1cm-10cm           | 150kHz        | 0                 |

|                     |                    | 1GHz          | 0.03-0.3          |

| External wiring     | 10cm-10m           | 150kHz        | 0-0.005           |

|                     |                    | 1GHz          | 0.3-30            |

Table 1.2: The electrical length for several conductive objects in the setup of an IC [5].

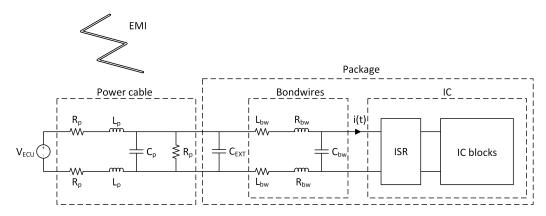

Figure 1.2 shows the power supply of the KMA3xx, provided by the ECU. An external capacitor  $(C_{EXT})$  is located inside the package to reduce the EMI picked up and radiated by the power cable.

Figure 1.2: Model of the KMA3xx angular sensor connected to the power source through a power cable.

In general, EMI can be further subdivided into three coupling methods:

- 1. Inductive interference: Interferences that are emitted and radiated through near field coupling are called inductive interferences. A magnetic or electric field is generated on one side and received by an antenna of the same type (a magnetic loop antenna or electric dipole antenna). Examples are crosstalk or the coupling between two magnetic coils.

- 2. Radiated interference: Interferences that are emitted and radiated through far field coupling are called radiated interferences. An accelerating voltage or current will generate an electric or magnetic field respectively. The generated field will generate a field of the opposite type and radiation occurs. An example is the electromagnetic field while switching a large current on or off.

- 3. Conducted interference: Interferences that are introduced through coupling by a common impedance are called conducted interferences. Conducted interference happens when two current loops share a common impedance so that the current loops start to interact. An example is the power supply variation due to fast switching digital circuits.

All three types of EMI may be picked up and/or emitted through the power cable. By

limiting the bandwidth of the current going into the ISR (i(t)), all three types of EME can be reduced.

### 1.3 Introduction to the ISR

In this section, the function of the ISR and its architecture is explained. A comparison is made between linear regulators and switched regulators. Note that an important convention is used to distinguish DC signals from AC signals:

$$V_x = V_X + v_x \tag{1.2}$$

Here  $V_x$  is a voltage that contains a DC component,  $V_X$ , and an AC component,  $v_x$ . This convention is used throughout the thesis.

### 1.3.1 Function

The function of the ISR is to supply internal blocks in the IC with a stable DC voltage. Its output impedance should be low so that the output voltage is independent on the current drawn from the supply. External interferences should be suppressed.

Digital circuits are in general quite robust against variations on the supply. However, the fast switching nature of digital circuits demand fast peaking load currents from the supply, polluting the supply voltage. Analog circuits, on the other hand, are usually quite sensitive to variations on the supply. As their current consumption is more constant than in digital circuits, they are less polluting. In order to keep the analog supply clean from variations, the analog and digital domains are often isolated by using a separate ISR, .

The ISR must also ensure a proper start-up after a voltage is applied to the supply pins of the IC.

## 1.3.2 Linear regulators versus switched regulators

Many approaches of designing a voltage regulator exist in literature. A widely accepted way to categorize the voltage regulator is by defining two main categories: linear regulators and switched regulators.

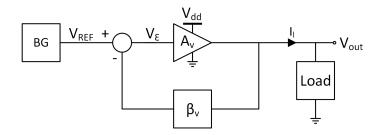

In this section, the architecture of both categories will be discussed and their main advantages and disadvantages will be presented. Both categories make use of a Voltage Regulation Loop (VRL) to regulate the output voltage  $(V_{out})$  to a voltage proportional to a bandgap voltage  $(V_{REF})$ .

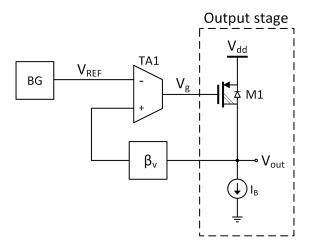

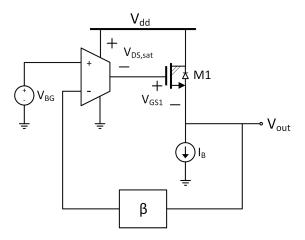

Figure 1.3: Architecture of a linear regulator.

### Linear regulator

The basic linear regulator architecture (figure 1.3) consists of a bandgap reference, a voltage amplifier, and a feedback network ( $\beta_v$ ).

As the maximum output voltage  $(V_{out})$  of the voltage amplifier is the supply voltage  $(V_{dd})$ , the linear regulator is only used to realize a  $V_{out}$  that is lower than  $V_{dd}$ . To achieve a certain voltage drop from  $V_{dd}$  to  $V_{out}$ , the minimum amount of dissipated power  $(P_{MIN})$  in the output stage of the voltage amplifier is given by:

$$P_{MIN} = (V_{DD} - V_{OUT})I_L (1.3)$$

This power dissipation results in a lot of heat production and therefore puts a limit on the maximum  $I_L$  that can be provided. Also due to this dissipation, the linear regulator is in general not very power efficient.

The simplicity of the design, makes it possible to design the voltage amplifier for high speeds, so that the bandwidth of the VRL may approach the  $f_t$  of the technology [6].

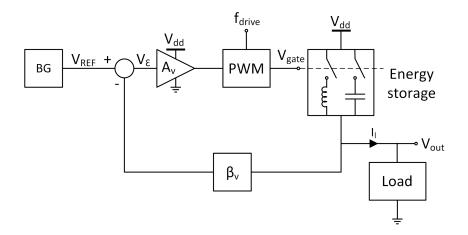

#### Switched regulator

The switched regulator architecture (figure 1.4) utilizes a Pulse Width Modulator (PWM) to drive one or multiple switches that dynamically connect/disconnect energy storage elements (inductors and capacitors) to the circuit.

The use of energy storage elements allows an output voltage  $(V_{out})$  that is higher or lower than the supply voltage  $(V_{dd})$ . As the energy storage elements are ideally loss-less, high power efficiency's (between 80% and 95%) can be achieved [6]. Less power is dissipated than in the linear regulator, and so heat production is less of a problem. This makes the switched regulator more suitable for providing large load currents  $(I_L)$ .

The use of a switch in the output stage, driven by a clocked signal, will cause a voltage ripple at the output. This ripple is often unacceptable for sensitive analog circuits. The switched output stage draws fast transient currents from the supply, i.e. a large bandwidth current. As discussed in section 1.2, this results in unwanted EME.

In order to keep the switched regulator stable, the bandwidth of the VRL must be about a decade below the driving frequency of the PWM  $(f_{drive})$  [6]. Therefore the maximum attainable bandwidth of the VRL lies about a decade below the  $f_t$  of the technology.

Figure 1.4: Architecture of a switched regulator.

### Comparison

Table 1.3 shows the strengths and weaknesses of the two main architectures.

|                      | Linear | Switched |

|----------------------|--------|----------|

| Output voltage range | -      | +        |

| Power efficiency     | -      | ++       |

| Maximum output power | -      | +        |

| EMC                  | +      | _        |

| Output noise         | +      | -        |

| Bandwidth            | +      | -        |

| Simplicity           | +      | -        |

Table 1.3: Comparison between the switched

The main advantages of the switched regulator architecture are power related. Although power consumption is not negligible in the automotive sensors application, it is not critical. Due to better EMC performance and bandwidth capabilities the focus in this thesis will be on the linear regulator.

## 1.4 Topologies

As explained in the previous section, generally a lot of power is dissipated in the output stage of the voltage amplifier and so large transistors are required. The characteristics of these transistors are dominant in the performance of the ISR. For this reason the voltage amplifier of figure 1.3 is split into a Transconductance Amplifier (TA) and an output stage (figure 1.5).

Figure 1.5: Linear regulator topology with the voltage amplifier split into a TA and an output stage.

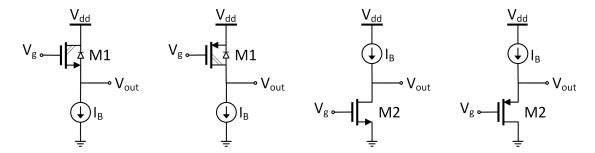

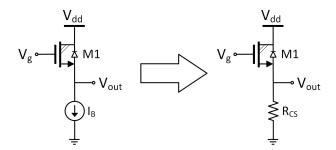

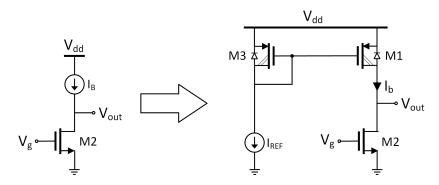

In figure 1.5, the output stage is a common source amplifier formed by M1 and bias current source  $I_B$ . Four possibilities are identified as suitable candidates for an output stage (figure 1.6).

Figure 1.6: The output stages for the four different topologies. From left to right: NMOS series, PMOS series, NMOS shunt, and PMOS shunt.

Topologies where the transistor is located between the supply  $(V_{dd})$  and the output  $(V_{out})$  are referred to as 'series regulators'. If the regulating transistor is located between  $V_{out}$  and ground, the regulator is considered a 'shunt regulator'. The four topologies are referred to as NMOS series, PMOS series, NMOS shunt, and PMOS shunt respectively. As the application requires a high breakdown voltage, high side transistors are implemented as HV transistors. The properties of the HV transistor will be discussed in section 1.4.2.

## 1.4.1 Open loop approach

At low frequencies, the performance of the regulator is mainly dominated by the VRL. After the Unity Gain Frequency (UGF) of the VRL, the loop may be considered to be broken and the performance of the regulator is only determined by the output stage.

In this thesis, an open loop approach is used to be able to compare the performance of the different output stages.

### 1.4.2 The high voltage transistor

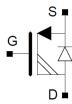

As mentioned in section 1.1, the supply voltage from the car battery can vary due to numerous reasons. Although the ECU provides regulation, the KMA3xx family still needs to withstand supply voltages up to 20V. To meet this requirement, the HV transistor (figure 1.7), available in the A-BCD process, needs to be used.

Figure 1.7: Symbol of the HV transistor.

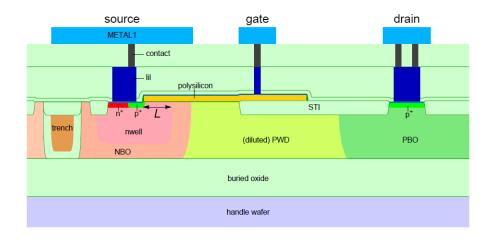

These transistors have an extend drain to enable a maximum  $V_{DS}$  of 60V. The downside of this extended drain is that the parasitic overlap capacitance between drain and gate  $(C_{GD,ov})$  is substantially large. Body and source are internally connected and so the high voltage transistor must be considered as an unsymmetrical device that has a back-gate diode. Figure 1.8 shows the cross section of a HV PMOS transistor.

Figure 1.8: Cross section of a HV PMOS transistor.

### 1.4.3 Non-ideal current source

Until now, the bias current source has been represented by an ideal source. However, the parasitics of the current source are not negligible and need to be taken into account.

In series topologies, the current source is connected in parallel to the output  $(V_{out})$ . As the output voltage is kept stable by the VRL, current source  $I_B$  can be implemented by a resistor (figure 1.9).

Figure 1.9: Implementation of bias current source  $I_B$  in series topologies.

In the shunt topologies, the current source is connected to the supply  $(V_{dd})$  and so a HV transistor is necessary to implement the current source. The current source is modeled as in figure 1.10.

Figure 1.10: Implementation of bias current source  $I_B$  in shunt topologies.

The DC reference current  $(I_{REF})$  flows to ground and decreases power efficiency. To avoid a large power loss it must be kept small. In this work, the ratio considered to be acceptable is:

$$I_{REF} = \frac{I_B}{1000} \tag{1.4}$$

It follows that:

$$(W/L)_1 = \frac{(W/L)_3}{1000} \tag{1.5}$$

## 1.5 Outline of this thesis

In this chapter a problem statement and some background knowledge was given to help understand the research problem. Chapter 2, presents several performance parameters. These are then used to analyze and compare the different topologies. The main focus is on parameters that affect the EMC performance. Based on the findings in chapter 2, a new topology is proposed in chapter 3. The topology is examined on both system level and circuit level. In chapter 4, the simulation results of the proposed topology are shown. Finally a conclusion is given in chapter 5.

# Chapter 2

# Performance of standard topologies

In this chapter several performance parameters are defined and explained. The parameters described in this chapter are commonly used in literature about linear voltage regulators. Symbolic expressions are found for the performance parameters of the four topologies that were defined in section 1.4. The expressions that were found for the Power Supply Rejection (PSR) and emission are verified by simulation.

In section 2.2, the results of the performance analysis are summarized. A table containing the advantages and disadvantages of eacht topology is presented.

Finally, the architecture of the ISR inside the KMA3xx family is shown in section 2.3.

## 2.1 Performance parameters

Many parameters exist to characterize the performance of different voltage regulators [2]. The most essential parameters are described in this section.

### 2.1.1 Power supply rejection

In this section the concept of Power Supply Rejection (PSR) is described and compared by deriving equations. The PSR is an important parameter to indicate the regulators susceptibility to interferences. The resulting equations are verified with simulations.

### Description

The PSR is a small signal parameter that represents the circuits capability to suppress a voltage disturbance on the supply line  $(v_{dd})$ , to the output  $(v_{out})$ .

$$PSR = \frac{\delta v_{dd}}{\delta v_{out}} \tag{2.1}$$

Ideally,  $v_{out}$  is totally independent from  $v_{dd}$ , resulting in an infinite PSR.

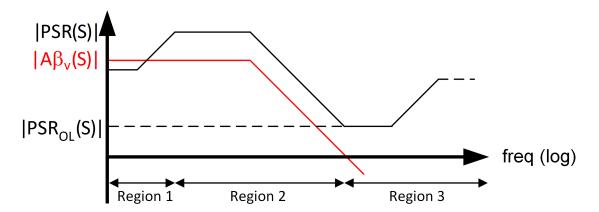

Figure 2.1 shows an example of the PSR of an internally compensated regulator over frequency. The loop gain is shown in red. The curve is divided into three regions [8]:

Figure 2.1: Example of a PSR curve for a voltage regulator.

In region 1, the PSR of the bandgap reference  $(PSR_{BG})$  is dominant. Any disturbance seen on the bandgap voltage will be transferred to the output by the closed loop gain. The PSR of the regulator in region 1  $(PSR_1)$  is given by:

$$PSR_{1} = \frac{A_{v}PSR_{BG}(s)}{1 + A(s)\beta_{v}}$$

$$\approx \frac{PSR_{BG}(s)}{\beta_{v}}$$

(2.2)

The output resistance of a bandgap circuit is in general quite high. The output is usually decoupled by a capacitor, resulting in a zero in  $PSR_{BG}$  at low frequency.

The PSR in region 2  $(PSR_2)$  is no longer dominated by  $PSR_{BG}$  as its contribution is diminished by the decoupling capacitor.  $PSR_2$  can be described as:

$$PSR_2 = PSR_{OL}[1 + A(s)\beta_v] \approx PSR_{OL}A(s)\beta_v \tag{2.3}$$

Where  $PSR_{OL}$  is the PSR of the regulator when the feedback loop would be broken. In region 3, the loop gain drops below unity. The loop can be considered to be broken and the PSR is completely determined by open loop PSR.

$$PSR_3 = PSR_{OL}[1 + A(s)\beta_v] \approx PSR_{OL}(s)$$

(2.4)

If the bandgap reference would have been supplied from the output of the regulator  $(V_{out})$  instead of directly from the supply  $(V_{dd})$ ,  $PSR_{BG}$  would be significantly higher and would not be the dominant factor in  $PSR_1$ . In this case the total PSR can be given by the single equation:

$$PSR = PSR_{OL}[1 + A(s)\beta_v]$$

(2.5)

### Comparison

If the loop gain for all topologies is assumed to have an equal bandwidth, the difference in PSR performance is solely determined by  $PSR_{OL}$ . Therefore analyzing only the  $PSR_{OL}$  of the topologies is sufficient to compare the PSR performance. A thorough bandwidth analysis is done in subsection 2.1.9.

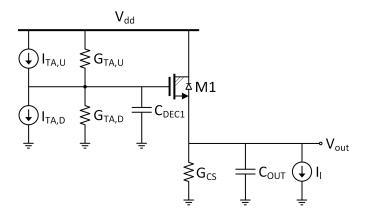

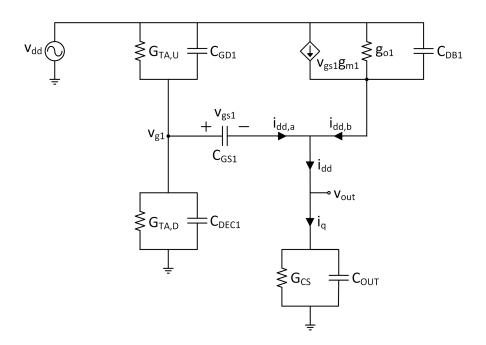

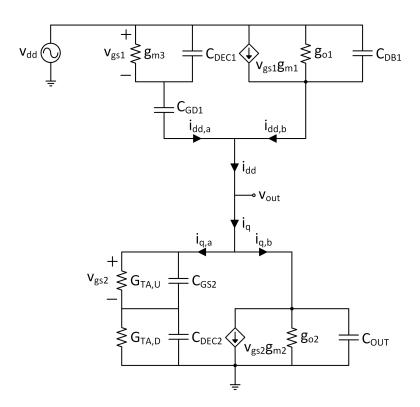

**NMOS Series** The transistor model of the open loop NMOS series topology is shown in figure 2.2. To increase the EMC performance at high frequencies, decoupling capacitor  $C_{DEC1}$  is added to the circuit.

In the NMOS series topology, both the output stage transistor (M1) and the TA must be implemented in the HV domain. The TA has to be supplied from  $V_{dd}$ , and thus it requires a high PSR.

In order to calculate the open loop PSR, the circuit is converted to its small signal equivalent (figure 2.3). The small signal load current is replaced by an open as it is not relevant when calculating the PSR.

The open loop PSR can be determined by using Kirchoffs Current Law (KCL) on the  $v_{out}$  node of the circuit:

$$i_{dd} = i_{dd,a} + i_{dd,b} = i_q$$

(2.6)

Figure 2.2: Open loop transistor model of the NMOS series regulator.

Figure 2.3: Small signal equivalent of the open loop NMOS series model.

In order to express  $i_{dd}$  in terms of  $v_{dd}$  and  $v_{out}$ , an expression for  $v_{g1}$  is found by using KCL on the  $v_{g1}$  node:

$$(v_{dd} - v_{g1})(G_{TA,U} + sC_{GD1}) = v_{g1}(G_{TA,D} + sC_{DEC1}) + (v_{g1} - v_{out})sC_{GS1}$$

$$v_{g1} = \frac{v_{dd}(G_{TA,U} + sC_{GD1}) + v_{out}sC_{GS1}}{G_{TA,U} + G_{TA,D} + s(C_{DEC1} + C_{GD1} + C_{GS1})}$$

(2.7)

The currents are expressed in terms of nodal voltages and admittances:

$$i_{dd,a} = (v_{g1} - v_{out})sC_{GS}$$

$$i_{dd,b} = (v_{g1} - v_{out})g_{m1} + (v_{dd} - v_{out})(g_{o1} + sC_{DB1})$$

$$i_{g} = v_{out}(G_{CS} + sC_{OUT})$$

(2.8)

A second order expression for  $PSR_{OL}$  is found by substituting the currents from equation 2.8 into equation 2.6 and substituting  $v_{g1}$  by equation 2.7.

$$PSR_{OL} = \frac{N(s)}{D(s)} = \frac{N_1 s^2 + N_2 s + N_3}{D_1 s^2 + D_2 s + D_3}$$

(2.9)

To simplify the resulting factors, the approximation is made that:  $g_{m1} \gg (g_{o1} + G_{CS})$  and  $C_{OUT} \gg (C_{GS1} + C_{DB1})$ .

$$N_{1} \approx C_{OUT}(C_{DEC1} + C_{GD1} + C_{GS1}) - C_{GS1}^{2}$$

$$N_{2} \approx (G_{TA,U} + G_{TA,D})C_{OUT} + g_{m1}(C_{DEC1} + C_{GD1} + C_{GS1}) - g_{m1}C_{GS1}$$

$$N_{3} \approx g_{m1}(G_{TA,U} + G_{TA_{D}})$$

$$D_{1} \approx C_{GD1}C_{GS1} + C_{DB1}(C_{DEC1} + C_{GD1} + C_{GS1})$$

$$D_{2} \approx g_{m1}C_{GD1} + G_{TA,U}C_{GS1} + (G_{TA,D} + G_{TA,D})C_{DB1} + g_{o1}(C_{DEC1} + C_{GD1} + C_{GS1})$$

$$D_{3} \approx g_{m1}G_{TA,U} + g_{o1}(G_{TA,U} + G_{TA,D})$$

$$(2.10)$$

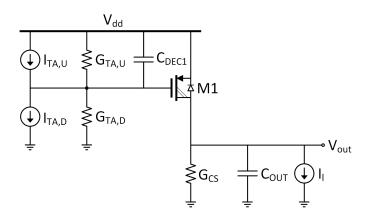

**PMOS Series** The transistor model of the open loop PMOS series topology is shown in figure 2.4. To increase the EMC performance at high frequencies, decoupling capacitor  $C_{DEC1}$  is added to the circuit.

In the PMOS series topology, both the output stage transistor (M1) and the TA must be implemented in the HV domain due to the voltage range specification (subsection 1.4.2). To avoid current flow due to a small signal disturbance on the supply  $(v_{dd})$ , the signal on the gate of M1 should be identical to  $v_{dd}$ . This suggests that the preferred PSR of the TA is unity.

In order to calculate the open loop PSR, the circuit is converted to its small signal equivalent (figure 2.5). The small signal load current is replaced by an open as it is not relevant when calculating the PSR. The gate-source capacitance of M1 ( $C_{GS1}$ ) adds to the decoupling capacitance ( $C_{DEC1}$ ) and is not drawn for simplicity.

Figure 2.4: Open loop transistor model of the PMOS series regulator.

Figure 2.5: Small signal equivalent of the open loop PMOS series model.

The open loop PSR can be determined by using KCL on the  $v_{out}$  node of the circuit:

$$i_{dd} = i_{dd,a} + i_{dd,b} = i_q$$

(2.11)

In order to express  $i_{dd}$  in terms of  $v_{dd}$  and  $v_{out}$ , an expression for  $v_{g1}$  is found by using KCL on the  $v_{g1}$  node:

$$(v_{dd} - v_{g1})(G_{TA,U} + sC_{DEC1}) = v_{g1}G_{TA,D} + (v_{g1} - v_{out})sC_{GD1}$$

$$v_{g1} = \frac{v_{dd}(G_{TA,U} + sC_{DEC1}) + v_{out}sC_{GD1}}{G_{TA,U} + G_{TA,D} + s(C_{DEC1} + C_{GD1})}$$

(2.12)

The currents are expressed in terms of nodal voltages and admittances:

$$i_{dd,a} = (v_{g1} - v_{out})sC_{GD1}$$

$$i_{dd,b} = (v_{dd} - v_{g1})g_{m1} + (v_{dd} - v_{out})(g_{o1} + sC_{DB1})$$

$$i_{q} = v_{out}(G_{CS} + sC_{OUT})$$

(2.13)

A second order expression for  $PSR_{OL}$  is found by substituting the currents from equation 2.13 into equation 2.11 and substituting  $v_{q1}$  by equation 2.12.

$$PSR_{OL} = \frac{N(s)}{D(s)} = \frac{N_1 s^2 + N_2 s + N_3}{D_1 s^2 + D_2 s + D_3}$$

(2.14)

To simplify the resulting factors, the approximation is made that:  $g_{m1} \gg (G_{TA,U} + G_{TA,D})$  and  $C_{OUT} \gg C_{DB1}$ .

$$N_{1} \approx C_{DEC1}C_{GD1} + C_{OUT}(C_{DEC1} + C_{GD1})$$

$$N_{2} \approx g_{m1}C_{GD1} + (g_{o1} + G_{CS})(C_{DEC1} + C_{GD1}) + (G_{TA,U} + G_{TA,D})C_{OUT}$$

$$N_{3} \approx (g_{o1} + G_{CS})(G_{TA,U} + G_{TA,D})$$

$$D_{1} \approx C_{DEC1}C_{GD1} + C_{DB1}(C_{DEC1} + C_{GD1})$$

$$D_{2} \approx g_{m1}C_{GD1} + G_{TA,U}(C_{DB1} + C_{GD1}) + G_{TA,D}C_{DB1})$$

$$D_{3} \approx g_{m1}G_{TA,D}$$

$$(2.15)$$

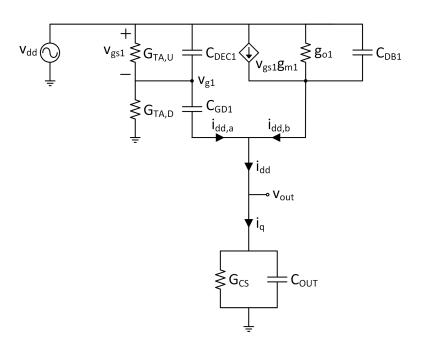

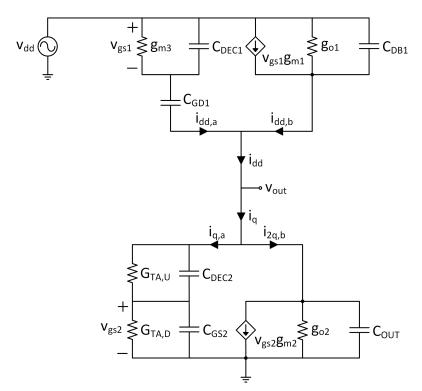

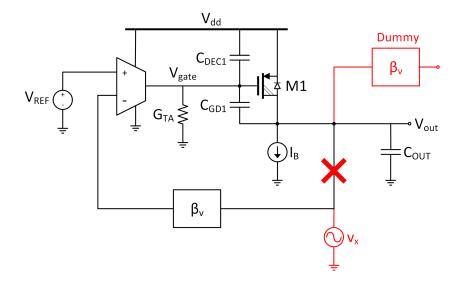

**NMOS Shunt** The transistor model of the open loop NMOS shunt topology is shown in figure 2.6. To increase the EMC performance at high frequencies, two decoupling capacitances are added to the circuit:  $C_{DEC1}$  and  $C_{DEC2}$ .

In the NMOS shunt topology, both the output stage transistor (M2) and the TA can be implemented in the low voltage (LV) domain. The current source must be implemented in the HV domain due to the voltage range specification (subsection 1.4.2). The TA may be supplied from  $V_{out}$ , relaxing its requirement to have a high PSR.

Figure 2.6: Open loop transistor model of the NMOS shunt regulator.

In order to calculate the open loop PSR, the circuit is converted to its small signal equivalent (figure 2.7). The small signal load current is replaced by an open as it is not relevant when calculating the PSR. The gate-source capacitance of M1  $(C_{GS1})$  and gate-drain capacitance of M2  $(C_{GD2})$  add to the decoupling capacitances  $(C_{DEC1})$  and  $(C_{DEC2})$  respectively) and are not drawn for simplicity. The drain-bulk capacitance of M2  $(C_{DB2})$  is in parallel to the output capacitance  $(C_{OUT})$  and is neglected.

Figure 2.7: Small signal equivalent of the open loop NMOS shunt model.

The open loop PSR can be determined by using KCL on the  $v_{out}$  node of the circuit:

$$i_{dd} = i_{dd,a} + i_{dd,b} = i_q = i_{q,a} + i_{q,b}$$

(2.16)

The currents are expressed in terms of nodal voltages and admittances:

$$i_{dd,a} = (v_{dd} - v_{out})Y_{dd,a}$$

$$i_{dd,b} = (v_{dd} - v_{out})Y_{dd,b}$$

$$i_{q,a} = v_{out}Y_{q,a}$$

$$i_{q,b} = v_{out}Y_{q,b}$$

(2.17)

The admittances can be easily seen from the circuit:

$$Y_{dd,a} = \frac{sC_{GD1}(g_{m3} + sC_{DEC1})}{g_{m3} + s(C_{GD1} + sC_{DEC1})}$$

$$Y_{dd,b} = \frac{sC_{GD1}}{g_{m3} + s(C_{DEC1} + C_{GD1})}g_{m1} + g_{o1} + sC_{DB1}$$

$$Y_{q,a} = \frac{(G_{TA,U} + sC_{DEC2})(G_{TA,D} + sC_{GS2})}{G_{TA,U} + G_{TA,D} + s(C_{DEC2} + C_{GS2})}$$

$$Y_{q,b} = \frac{G_{TA,U} + sC_{DEC2}}{G_{TA,U} + G_{TA,D} + s(C_{DEC2} + C_{GS2})}g_{m2} + g_{o2} + sC_{OUT}$$

(2.18)

An expression for  $PSR_{OL}$  is found by substituting the currents from equation 2.17 into equation 2.16:

$$PSR_{OL} = \frac{\delta v_{dd}}{\delta v_{out}} = \frac{Y_{dd,a} + Y_{dd,b} + Y_{q,a} + Y_{q,b}}{Y_{dd,a} + Y_{dd,b}}$$

(2.19)

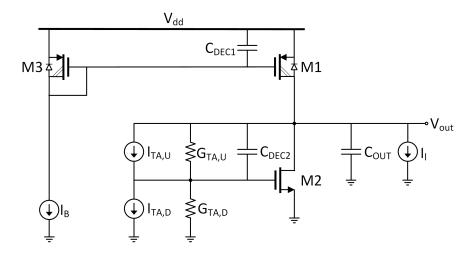

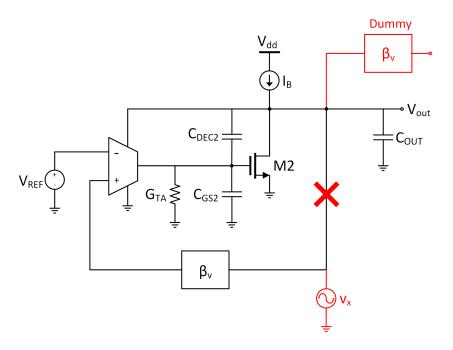

**PMOS Shunt** The transistor model of the open loop PMOS shunt topology is shown in figure 2.8. To increase the EMC performance at high frequencies, two decoupling capacitances are added to the circuit:  $C_{DEC1}$  and  $C_{DEC2}$ .

In the PMOS shunt topology, both the output stage transistor (M2) and the TA can be implemented in the LV domain. The current source must be implemented in the HV domain due to the voltage range specification (subsection 1.4.2). The TA may be supplied from  $V_{out}$ , relaxing its requirement to have a high PSR.

Figure 2.8: Open loop transistor model of the PMOS shunt regulator.

In order to calculate the open loop PSR, the circuit is converted to its small signal equivalent (figure 2.9). The small signal load current is replaced by an open as it is not relevant when calculating the PSR. The gate-source capacitance of M1  $(C_{GS1})$  and gate-drain capacitance of M2  $(C_{GD2})$  add to the decoupling capacitances  $(C_{DEC1})$  and  $(C_{DEC2})$  respectively) and are not drawn for simplicity. The drain-bulk capacitance of M2  $(C_{DB2})$  is in parallel to the output capacitance  $(C_{OUT})$  and is neglected.

Figure 2.9: Small signal equivalent of the open loop PMOS shunt model.

The open loop PSR can be determined by using KCL on the  $v_{out}$  node of the circuit:

$$i_{dd} = i_{dd,a} + i_{dd,b} = i_q = i_{q,a} + i_{q,b}$$

(2.20)

The currents are expressed in terms of nodal voltages and admittances:

$$i_{dd,a} = (v_{dd} - v_{out})Y_{dd,a}$$

$$i_{dd,b} = (v_{dd} - v_{out})Y_{dd,b}$$

$$i_{q,a} = v_{out}Y_{q,a}$$

$$i_{q,b} = v_{out}Y_{q,b}$$

(2.21)

The admittances can be easily seen from the circuit:

$$Y_{dd,a} = \frac{sC_{GD1}(g_{m3} + sC_{DEC1})}{g_{m3} + s(C_{GD1} + sC_{DEC1})}$$

$$Y_{dd,b} = \frac{sC_{GD1}}{g_{m3} + s(C_{DEC1} + C_{GD1})}g_{m1} + g_{o1} + sC_{DB1}$$

$$Y_{q,a} = \frac{(G_{TA,U} + sC_{GS2})(G_{TA,D} + sC_{DEC2})}{G_{TA,U} + G_{TA,D} + s(C_{DEC2} + C_{GS2})}$$

$$Y_{q,b} = \frac{G_{TA,U} + sC_{DEC2}}{G_{TA,U} + G_{TA,D} + s(C_{DEC2} + C_{GS2})}g_{m2} + g_{o2} + sC_{OUT}$$

$$(2.22)$$

An expression for  $PSR_{OL}$  is found by substituting the currents from equation 2.21 into equation 2.20:

$$PSR_{OL} = \frac{\delta v_{dd}}{\delta v_{out}} = \frac{Y_{dd,a} + Y_{dd,b} + Y_{q,a} + Y_{q,b}}{Y_{dd,a} + Y_{dd,b}}$$

(2.23)

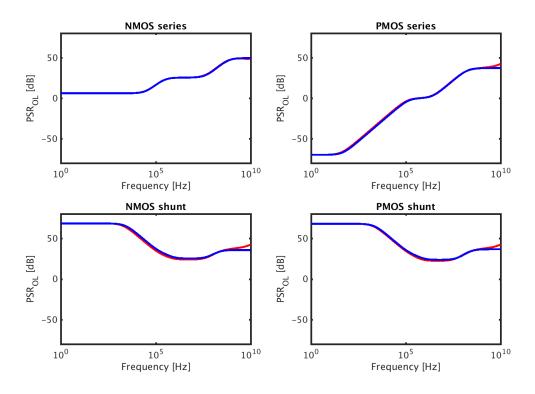

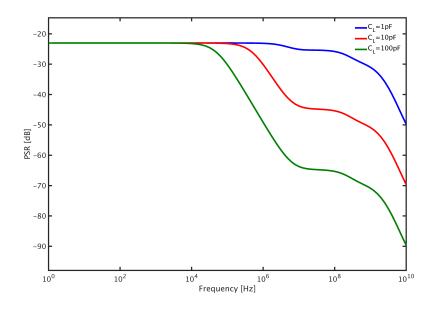

#### Model verification

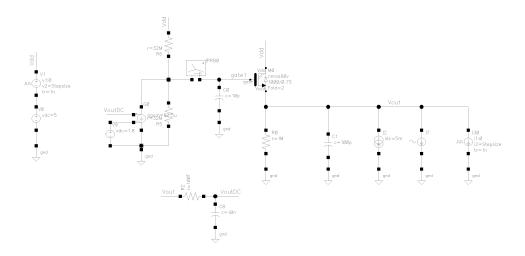

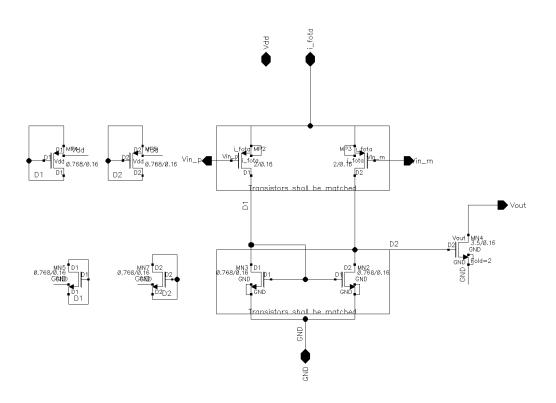

The open loop PSR has been simulated using the transistor models from the A-BCD9 library. DC feedback was used to bias the output stage. The circuits used for simulation can be found in the appendix B. The small signal parameters of the circuit are shown in table 2.1.

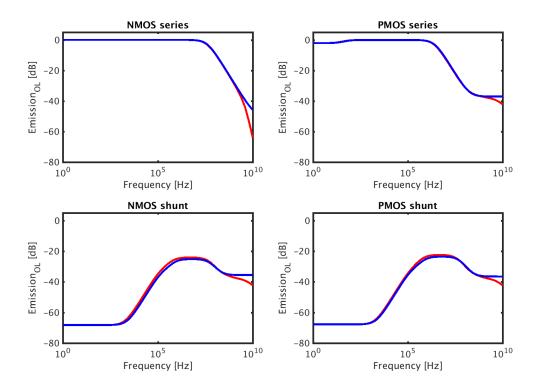

The parameters are directly mapable to the small signal circuits from section 2.1.1 and can be used to verify the equations with the simulated models. Figure 2.10 shows the equations for the open loop PSR versus the simulated open loop PSR.

|            | Shunt        |              | Series      |             |

|------------|--------------|--------------|-------------|-------------|

|            | NMOS         | PMOS         | NMOS        | PMOS        |

| $(W/L)_1$  | 3000/0.75    | 3000/0.75    | 1000/0.75   | 3000/0.75   |

| $(W/L)_2$  | 200/0.16     | 600/0.16     | N.A.        | N.A.        |

| $g_{m1}$   | 38.4mS       | 38.4mS       | 34.9mS      | 28.5mS      |

| $g_{m2}$   | 32.7mS       | 31.3mS       | N.A.        | N.A.        |

| $g_{m3}$   | $91.3 \mu S$ | $91.3 \mu S$ | N.A.        | N.A.        |

| $g_{o1}$   | $6.9 \mu S$  | $6.9 \mu S$  | $3.4 \mu S$ | $3.7 \mu S$ |

| $g_{o2}$   | 1.4mS        | 1.2mS        | N.A.        | N.A.        |

| $G_{CS}$   | N.A.         | N.A.         | $1\muS$     | $1\muS$     |

| $C_{DB1}$  | 383.9fF      | 383.9fF      | 190.8fF     | 383.3fF     |

| $C_{DEC1}$ | 10pF         | 10pF         | 10pF        | 10pF        |

| $C_{DEC2}$ | 1pF          | 1pF          | N.A.        | N.A.        |

| $C_{GD1}$  | 1.4pF        | 1.2pF        | 569fF       | 1.1pF       |

| $C_{GS1}$  | 8.6pF        | 8.6pF        | 3.6pF       | 8.5pF       |

| $C_{GS2}$  | 0            | 0            | N.A.        | N.A.        |

| $C_{OUT}$  | 100pF        | 100pF        | 100pF       | 100pF       |

| $I_L$      | 5mA          | 5mA          | 5mA         | 5mA         |

Table 2.1: Values of the small signal parameters during simulation.

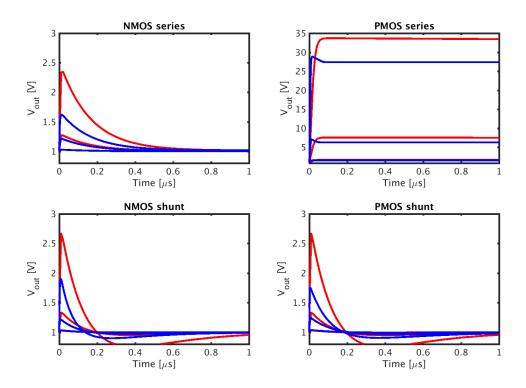

Figure 2.10: The simulated  $PSR_{OL}$  using the transistor models (blue) versus the calculated equation for the  $PSR_{OL}$  (red).

It can be seen that the transistor models show a zero at frequencies beyond 1GHz that is not included in the equations. This zero is caused by the finite drain resistance of the HV PMOS transistor in all topologies except for the NMOS series topology. Aside from this high frequency zero, the simulations match the equations quite well.

### 2.1.2 Emission

The analysis of emission is treated in the same manner as the PSR in the previous section. The emission is an important parameter to indicate how much the ISR is able to suppress interference caused by the load current.

### **Description**

Emission is a small signal parameter that represents the change in current on the supply line  $(i_{dd})$  if a change in load current  $(i_l)$  occurs. The emission is defined as:

$$Emission = \frac{\delta i_{dd}}{\delta i_l} \tag{2.24}$$

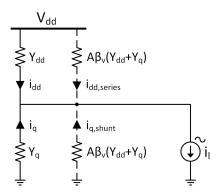

Ideally only the DC component of the load current is delivered from the supply node, resulting in zero emission. The influence of the VRL on emission is different for series and shunt regulators. This is due to the fact the the VRL increases the conductance seen to  $V_{dd}$  for series regulators and to ground for shunt regulators (figure 2.11).

Figure 2.11: The VRL of the series or shunt topology result in a different conductance to ground.

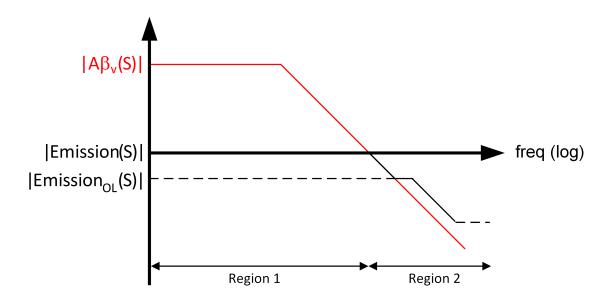

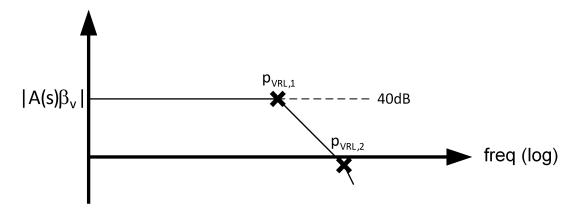

Figure 2.12 shows an example of an emission response over frequency for a series regulator.

Figure 2.12: Example of an emission curve for a series regulator.

It can be seen that the regulation loop decreases the emission performance for a series regulator.

In region 1 the emission is mainly determined by the gain of the VRL. The VRL forces most of  $i_l$  to flow from  $i_{dd,series}$ . The emission in this region  $(Emission_1)$  is given by:

$$Emission_1(s) = \frac{Y_{dd} + (Y_{dd} + Y_q)A(s)\beta_v}{(Y_{dd} + Y_q)(1 + A(s)\beta_v)} \approx 1$$

(2.25)

In region 2, the gain of the VRL drops below unity. The VRL can considered to be broken and the emission is completely determined by the open loop emission.

$$Emission_2(s) = \frac{Y_{dd} + (Y_{dd} + Y_q)A(s)\beta_v}{(Y_{dd} + Y_q)(1 + A(s)\beta_v)} \approx \frac{Y_{dd}}{Y_{dd} + Y_q} \approx Em_{OL}$$

(2.26)

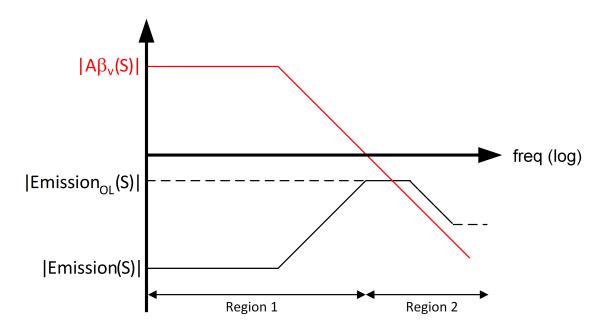

Figure 2.13 shows an example of an emission response over frequency for a shunt regulator.

In contrast to the series regulator, the VRL increases the emission performance for a shunt regulator.

In region 1 the emission is mainly determined by the open loop emission and the gain of the VRL. The VRL forces most of  $i_l$  to flow from the parallel current branch  $(i_{q,shunt})$ .

$$Emission_1 = \frac{Y_{dd}}{(Y_{dd} + Y_q)[1 + A(s)\beta_v]} \approx \frac{Em_{OL}}{A(s)\beta_v}$$

(2.27)

In region 2, the loop gain drops below unity. The loop can be considered to be broken and the emission is completely determined by open loop emission.

Figure 2.13: Example of an emission curve for a shunt regulator.

$$Emission_2 = \frac{Y_{dd}}{(Y_{dd} + Y_q)[1 + A(s)\beta_v]} \approx \frac{Y_{dd}}{Y_{dd} + Y_q} \approx Em_{OL}$$

(2.28)

### Comparison

The same open loop approach as used in the previous section will be used. Analyzing the  $Em_{OL}$  of the topologies is sufficient to compare the emission performance of the four topologies.

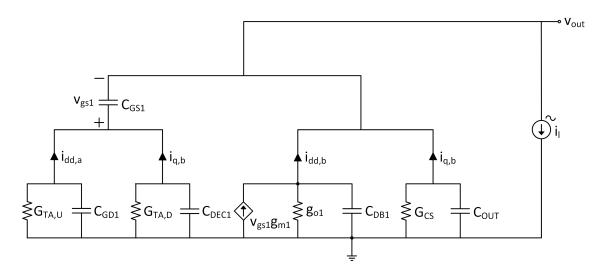

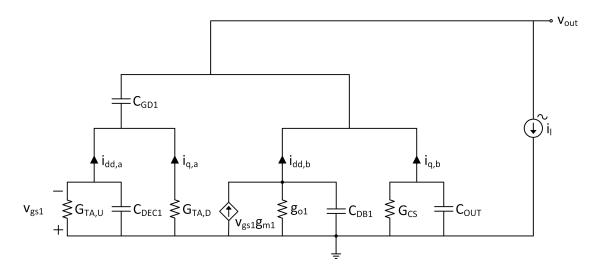

**NMOS Series** In order to calculate the open loop emission, the same transistor model as used during the calculation of  $PSR_{OL}$  (figure 2.2) is converted to its small signal equivalent (figure 2.14). The small signal supply voltage is replaced by a short as it is not relevant when calculating the emission. The parasitics are simplified in the same way as during the calculation of the open loop PSR (subsection 2.1.1).

The small signal load current  $(i_l)$  is divided into a quiescent current  $(i_q)$  and a current coming from the supply  $(i_{dd})$ .

$$i_l = i_{dd} + i_g = i_{dd,a} + i_{dd,b} + i_{g,a} + i_{g,b}$$

(2.29)

Figure 2.14: Small signal equivalent of the open loop NMOS series model.

Four admittances can be defined:

$$Y_{dd,a} = \frac{-i_{dd,a}}{v_{out}} = \frac{sC_{GS1}(G_{TA,U} + sC_{GD1})}{G_{TA,U} + G_{TA,D} + s(C_{DEC1} + C_{GD1} + C_{GS1})}$$

$$Y_{dd,b} = \frac{-i_{dd,b}}{v_{out}} = \frac{G_{TA,U} + G_{TA,D} + s(C_{DEC1} + C_{GD1})}{G_{TA,U} + G_{TA,D} + s(C_{DEC1} + C_{GD1} + C_{GS1})}g_{m1} + g_{o1} + sC_{DB1}$$

$$Y_{q,a} = \frac{-i_{q,a}}{v_{out}} = \frac{sC_{GS1}(G_{TA,D} + sC_{DEC1})}{G_{TA,U} + G_{TA,D} + s(C_{DEC1} + C_{GD1} + C_{GS1})}$$

$$Y_{q,b} = \frac{-i_{q,b}}{v_{out}} = G_{CS} + sC_{OUT}$$

(2.30)

$i_{dd}$  is a portion of  $i_l$ , which magnitude is determined by the admittances of equation 2.30. This results in an expression for  $Em_{OL}$ :

$$Em_{OL} = \frac{\delta i_{dd}}{\delta i_l} = \frac{Y_{dd,a} + Y_{dd,b}}{Y_{dd,a} + Y_{dd,b} + Y_{q,a} + Y_{q,b}}$$

(2.31)

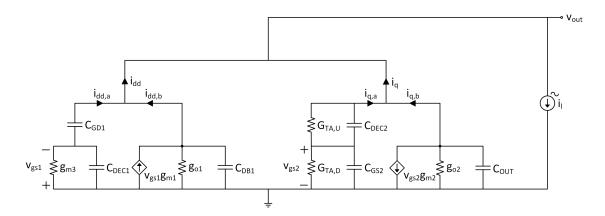

**PMOS Series** In order to calculate the open loop emission, the same transistor model as used during the calculation of  $PSR_{OL}$  (figure 2.4) is converted to its small signal equivalent (figure 2.15). The small signal supply voltage is replaced by a short as it is not relevant when calculating the emission. The parasitics are simplified in the same way as during the calculation of the open loop PSR (subsection 2.1.1).

The small signal load current  $(i_l)$  is divided into a quiescent current  $(i_q)$  and a current coming from the supply  $(i_{dd})$ .

$$i_l = i_{dd} + i_g = i_{dd,a} + i_{dd,b} + i_{g,a} + i_{g,b}$$

(2.32)

Figure 2.15: Small signal equivalent of the open loop PMOS series model.

Four admittances can be defined:

$$Y_{dd,a} = \frac{-i_{dd,a}}{v_{out}} = \frac{sC_{GD1}(G_{TA,U} + sC_{DEC1})}{G_{TA,U} + G_{TA,D} + s(C_{DEC1} + C_{GD1})}$$

$$Y_{dd,b} = \frac{-i_{dd,b}}{v_{out}} = \frac{sC_{GD1}}{G_{TA,U} + G_{TA,D} + s(C_{DEC1} + C_{GD1})}g_{m1} + g_{o1} + sC_{DB1}$$

$$Y_{q,a} = \frac{-i_{q,a}}{v_{out}} = \frac{sC_{GD1}G_{TA,D}}{G_{TA,U} + G_{TA,D} + s(C_{DEC1} + C_{GD1})}$$

$$Y_{q} = \frac{-i_{q}}{v_{out}} = G_{CS} + sC_{OUT}$$

$$(2.33)$$

$i_{dd}$  is a portion of  $i_l$ , which magnitude is determined by the admittances of equation 2.33. This results in an expression for  $Em_{OL}$ :

$$Em_{OL} = \frac{\delta i_{dd}}{\delta i_l} = \frac{Y_{dd,a} + Y_{dd,b}}{Y_{dd,a} + Y_{dd,b} + Y_{q,a} + Y_{q,b}}$$

(2.34)

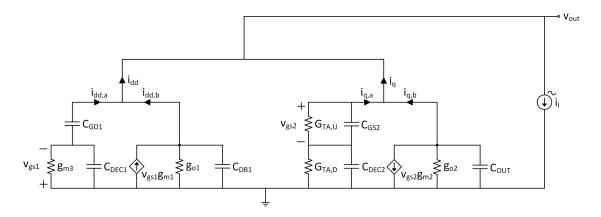

**NMOS Shunt** In order to calculate the open loop emission, the same transistor model as used during the calculation of  $PSR_{OL}$  (figure 2.6) is converted to its small signal equivalent for the calculation of the emission (figure 2.16). The small signal supply voltage is replaced by a short as it is not relevant when calculating the emission. The parasitics are simplified in the same way as during the calculation of the open loop PSR (subsection 2.1.1).

The small signal load current  $(i_l)$  is divided into a quiescent current  $(i_q)$  and a current coming from the supply  $(i_{dd})$ .

$$i_l = i_{dd} + i_g = i_{dd,a} + i_{dd,b} + i_{g,a} + i_{g,b}$$

(2.35)

Figure 2.16: Small signal equivalent of the open loop NMOS shunt model.

Four admittances can be defined:

$$Y_{dd,a} = \frac{-i_{dd,a}}{v_{out}} = \frac{sC_{GD1}(sC_{DEC1} + g_{m3})}{g_{m3} + s(C_{DEC1} + C_{GD1})}$$

$$Y_{dd,b} = \frac{-i_{dd,b}}{v_{out}} = \frac{sC_{GD1}}{g_{m3} + s(C_{DEC1} + C_{GD1})}g_{m1} + g_{o1} + sC_{DB1}$$

$$Y_{q,a} = \frac{-i_{q,a}}{v_{out}} = \frac{(G_{TA,U} + sC_{DEC2})(G_{TA,D} + sC_{GS2})}{G_{TA,U} + G_{TA,D} + s(C_{DEC2} + C_{GS2})}$$

$$Y_{q,b} = \frac{-i_{q,b}}{v_{out}} = \frac{G_{TA,U} + sC_{DEC2}}{G_{TA,U} + G_{TA,D} + s(C_{DEC2} + C_{GS2})}g_{m2} + g_{o2} + sC_{OUT}$$

$$(2.36)$$

$i_{dd}$  is a portion of  $i_l$ , which magnitude is determined by the admittances of equation 2.36. This results in an expression for  $Em_{OL}$ :

$$Em_{OL} = \frac{\delta i_{dd}}{\delta i_l} = \frac{Y_{dd,a} + Y_{dd,b}}{Y_{dd,a} + Y_{dd,b} + Y_{q,a} + Y_{q,b}}$$

(2.37)

**PMOS Shunt** In order to calculate the open loop emission, the same transistor model as used during the calculation of  $PSR_{OL}$  (figure 2.8) is converted to its small signal equivalent (figure 2.17). The small signal supply voltage is replaced by a short as it is not relevant when calculating the emission. The parasitics are simplified in the same way as during the calculation of the open loop PSR (subsection 2.1.1).

The small signal load current  $(i_l)$  is divided into a quiescent current  $(i_q)$  and a current coming from the supply  $(i_{dd})$ .

$$i_l = i_{dd} + i_q = i_{dd,a} + i_{dd,b} + i_{q,a} + i_{q,b}$$

(2.38)

Four admittances can be defined:

Figure 2.17: Small signal equivalent of the open loop PMOS shunt model.

$$Y_{dd,a} = \frac{-i_{dd,a}}{v_{out}} = \frac{sC_{GD1}(g_{m3} + sC_{DEC1})}{g_{m3} + s(C_{GD1} + sC_{DEC1})}$$

$$Y_{dd,b} = \frac{-i_{dd,b}}{v_{out}} = \frac{sC_{GD1}}{g_{m3} + s(C_{DEC1} + C_{GD1})}g_{m1} + g_{o1} + sC_{DB1}$$

$$Y_{q,a} = \frac{-i_{q,a}}{v_{out}} = \frac{(G_{TA,U} + sC_{GS2})(G_{TA,D} + sC_{DEC2})}{G_{TA,U} + G_{TA,D} + s(C_{DEC2} + C_{GS2})}$$

$$Y_{q,b} = \frac{-i_{q,b}}{v_{out}} = \frac{G_{TA,U} + sC_{DEC2}}{G_{TA,U} + G_{TA,D} + s(C_{DEC2} + C_{GS2})}g_{m2} + g_{o2} + sC_{OUT}$$

$$(2.39)$$

$i_{dd}$  is a portion of  $i_l$ , which magnitude is determined by the admittances of equation 2.39. This results in an expression for  $Em_{OL}$ :

$$Em_{OL} = \frac{\delta i_{dd}}{\delta i_l} = \frac{Y_{dd,a} + Y_{dd,b}}{Y_{dd,a} + Y_{dd,b} + Y_{a,a} + Y_{a,b}}$$

(2.40)

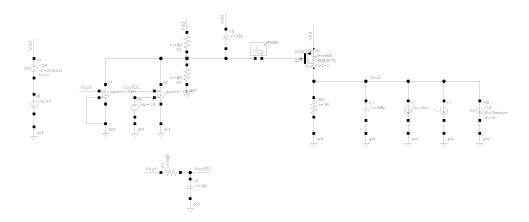

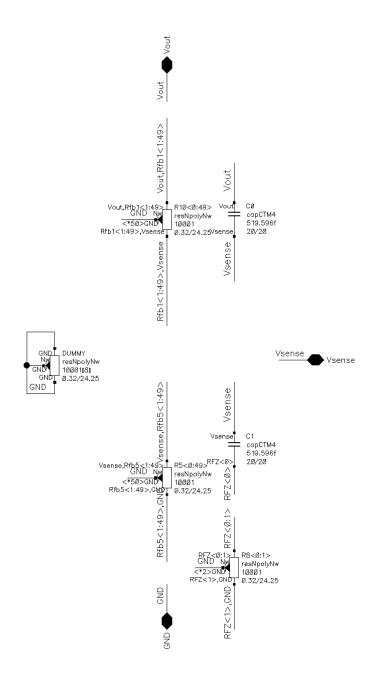

#### Model verification

The open loop emission has been simulated using the transistor models from the A-BCD9 library. DC feedback was used to bias the output stage. The circuits used for simulation can be found in appendix C. The small signal parameters of the circuits can be found in table 2.1. The parameters are directly mapable to the small signal circuits from section 2.1.2 and can be used to verify the equations with the simulated models. Figure 2.18 shows the equations for the open loop emission versus the simulated open loop emission.

The same zero as in the  $PSR_{OL}$  (caused by the finite drain resistance of the HV PMOS) now occurs as a pole in the  $Em_{OL}$ . Apart from this pole, the simulation matches the equations quite well.

Figure 2.18: The simulated  $Em_{OL}$  using the transistor models (blue) versus the calculated equation for the  $Em_{OL}$  (red).

## 2.1.3 Minimum drop-out voltage

The minimum drop-out voltage  $(V_{DO,min})$  is a parameter that indicates the minimum supply voltage  $(V_{DD,min})$  under which the ISR can operate. The drop-out voltage  $(V_{DO})$  during operation is often chosen to be slightly above  $V_{DO,min}$  in order to have some margin for disturbances.

## Description

$V_{DO,min}$  is defined as the difference between  $V_{DD,min}$  and the specified output voltage  $(V_{OUT})$ .

$$V_{DO,min} = V_{DD,min} - V_{OUT} \tag{2.41}$$

Where  $V_{DD,min}$  is defined as the supply voltage where  $V_{OUT}$  drops to 90% of its specified value.  $V_{dd,min}$  should be determined under worst case conditions, i.e. maximum load current, maximum temperature, and slow transistors.

In this application,  $V_{DD,min}$  is specified to be 3.5V and the ISR should regulate  $V_{OUT}$  to 1.8V. These specifications allow a maximum  $V_{DO,min}$  of 1.7V.

## Comparison

$V_{DO,min}$  is mostly determined by the output stage. During comparison, the topologies from figure 1.6 should be kept in mind.

**NMOS** series To determine  $V_{DO,min}$  of the NMOS series topology, the basic architecture is shown in figure 2.19.

Figure 2.19: Basic architecture of the NMOS series topology.

In order for the NMOS to be in saturation, it must hold that  $V_{GS1} > V_{TH1}$ . In order to keep the output stage of the TA in saturation, the supply voltage should be at least  $V_{DS,sat}$  above the output voltage of the TA.  $V_{DO,min}$  is given by:

$$V_{DO,min} = V_{GS1} + V_{DS,sat}$$

$$= V_{TH1} + \sqrt{\frac{2I_L}{(W/L)_1 k_1}} + V_{DS,sat}$$

(2.42)

To reduce  $V_{DO,min}$ , a large W/L ratio for M1 can be chosen at the cost of increased area and parasitics.

**PMOS** series During operation of the PMOS series topology the HV PMOS must stay in saturation.  $V_{DO,min}$  of the PMOS series regulator is given by:

$$V_{DO,min} = V_{DS,sat1}$$

$$= \sqrt{\frac{2I_L}{(W/L)_1 k_1}}$$

(2.43)

**Shunt regulators** In the shunt topologies the HV PMOS is operated as a current source. Just as in the PMOS series topology, this HV PMOS must stay in saturation during operation. The only difference with the PMOS series topology is the amount of current that runs through the HV PMOS. The  $V_{DO,min}$  of the shunt topologies is given by:

$$V_{DO,min} = V_{DS,satCS}$$

$$= \sqrt{\frac{2I_B}{(W/L)_1 k_1}}$$

(2.44)

## 2.1.4 Power efficiency

In many applications the power efficiency is an important property of the regulator. The maximum power efficiency of a linear regulator is often determined from system level by specifying the desired  $V_{DO}$ . The current efficiency ( $\lambda$ ) then determines how close the actual power efficiency meets the maximum attainable power efficiency set by the  $V_{DO}$ .

## Description

The power efficiency  $(\eta)$  of a linear regulator is defined as the ratio between the amount of power delivered to the load and the amount of power drawn from the supply. By expressing these powers in voltages and currents, the power efficiency can be expressed in terms of  $V_{DO}$ , the load current  $(I_L)$ , the quiescent current  $(I_Q)$ , and current used for auxiliary circuits  $(I_{AUX})$ .

$$\eta = \frac{P_L}{P_{DD}} = \frac{V_{OUT}I_L}{V_{DD}(I_L + I_Q + I_{AUX})} = (1 - \frac{V_{DO}}{V_{DD}})\lambda$$

(2.45)

### Comparison

In general  $I_{AUX} \ll I_Q$  and so  $\lambda$  is dominated by  $I_Q$ . In the following subsections, the design considerations that determine the magnitude of  $I_Q$  are discussed.

**Series regulators** In series regulators, the DC quiescent current  $(I_Q)$  is determined by bias current  $I_B$ . The DC current through the regulating transistor is given by:

$$I_D = I_L + I_B (2.46)$$

Although it is possible to let  $I_B$  approximate zero, this is often not done as the regulator could switch off during low loading conditions. Generally a small value for  $I_B$  is chosen, making series regulators very power efficient.

**Shunt regulators** In shunt regulators,  $I_Q$  is determined by the difference between  $I_B$  and  $I_L$ . The DC current through the regulating transistor is given by:

$$I_D = I_B - I_L = I_Q (2.47)$$

To avoid the regulator from switching off during high loading conditions,  $I_B > I_{L,max}$ . Consequently,  $I_Q$  is quite large during low loading conditions, making shunt regulators rather power inefficient. In addition, knowledge about  $I_L$  is required in order to minimize the power inefficiency.

## 2.1.5 Load regulation

## Description

Load regulation is defined as the static dependency of the output voltage on the load current. It is a large signal parameter given by:

$$Load\ regulation = \frac{\Delta I_L}{\Delta V_{OUT}} \tag{2.48}$$

The load regulation is expressed in [A/V] and is only valid within a specified current range. As a change in load current also changes the biasing conditions of the output stage, the load regulation is non-linear. A first order approximation of the load regulation can be made through the small signal output conductance.

### Comparison

The output conductance is reduced by the VRL. The closed loop output conductance is given by:

$$Load\ regulation \approx G_{OUT} = G_{OUT,OL}(1 + A_{DC}\beta_v) \tag{2.49}$$

Table 2.2 shows the open loop output conductances ( $G_{OUT,OL}$ ) for the different topologies.

| Topology    | $G_{OUT,OL}$                                                                                                  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| NMOS series | $g_{o1} + G_{CS} + g_{m1}$                                                                                    |  |  |  |

| PMOS series | $g_{o1} + G_{cs}$                                                                                             |  |  |  |

| NMOS shunt  | $g_{o1} + g_{o2} + \frac{G_{TA,U}G_{TA,D}}{G_{TA,U} + G_{TA,D}} + \frac{G_{TA,U}}{G_{TA,U} + G_{TA,D}}g_{m2}$ |  |  |  |

| PMOS shunt  | $g_{o1} + g_{o2} + \frac{G_{TA,U}G_{TA,D}}{G_{TA,U} + G_{TA,D}} + \frac{G_{TA,D}}{G_{TA,U} + G_{TA,D}}g_{m2}$ |  |  |  |

Table 2.2: Open loop conductances for the different topologies.

## 2.1.6 Line regulation

## Description

Line regulation is defined as the static dependency of the output voltage on the supply voltage. It is a large signal parameter given by:

$$Line\ regulation = \frac{\Delta V_{DD}}{\Delta V_{OUT}} \tag{2.50}$$

Line regulation is expressed in [V/V] and is only valid within a specified supply voltage range. A change in supply voltage does not affect the biasing conditions and so the load regulation is linear. The line regulation is therefore equal to the DC value of the small signal PSR.

### Comparison

The PSR of the topologies have already been extensively analyzed in section 2.1.1. Recall that the closed loop PSR is related to  $PSR_{OL}$  by the loop gain of the VRL:

$$Line\ regulation = PSR_{DC} = PSR_{OL,DC}(1 + A_{DC}\beta_v)$$

(2.51)

Table 2.3 shows the  $PSR_{OL,DC}$  for the different topologies.

| Topology    | $PSR_{OL,DC}$                                                                                          |

|-------------|--------------------------------------------------------------------------------------------------------|

| NMOS series | $\frac{g_{m1}(G_{TA,U} + G_{TA,D})}{g_{m1}G_{TA,U} + g_{o1}(G_{TA,U} + G_{TA,D})}$                     |

| PMOS series | $\frac{(g_{o1}+G_{cs})(G_{TA,U}+G_{TA,D})}{g_{m1}G_{TA,D}}$                                            |

| NMOS shunt  | $\frac{(g_{o1}+g_{o2})(G_{TA,U}+G_{TA,D})+G_{TA,U}G_{TA,D}+G_{TA,U}g_{m2}}{g_{o1}(G_{TA,U}+G_{TA,D})}$ |

| PMOS shunt  | $\frac{(g_{o1}+g_{o2})(G_{TA,U}+G_{TA,D})+G_{TA,U}G_{TA,D}+G_{TA,D}g_{m2}}{g_{o1}(G_{TA,U}+G_{TA,D})}$ |

Table 2.3:  $PSR_{OL,DC}$  for the different topologies.

## 2.1.7 Load Transient

In a realistic system, the load current can be very dynamic. The ISR must have a well controlled response to load steps up to a certain magnitude and with a certain rise time.

## Description

The load transient response shows the dynamic behavior of the output voltage  $(V_{out}(t))$  caused by a step in the load current  $(I_l(t))$ . Important parameters to observe are the settling time and the peak amplitude of the output voltage.

The transient behavior can be predicted from the small signal output impedance [7]. Current steps with a large amplitude will deviate from this response due to large signal effects.

## Comparison

The load step response can be approximated by doing an inverse Laplace transform on the output voltage  $(V_{OUT}(s))$ .

$$V_{out}(t) = \mathcal{L}^{-1} \{V_{OUT}(s)\}$$

$$= \mathcal{L}^{-1} \left\{ \frac{-I_L(s)}{Y_{OUT}(s)} \right\}$$

(2.52)

The VRL increases the output admittance of the output stage:

$$Y_{OUT}(s) = Y_{OUT,OL}(s)[1 + A(s)\beta_v]$$

(2.53)

The open loop output admittances  $(Y_{OUT,OL})$  of the different topologies is given by:

$$Y_{OUT,OL}(s) = Y_{dd} + Y_q \tag{2.54}$$

Where  $Y_{dd}$  and  $Y_q$  are the admittances that were found in section 2.1.2.

## Model verification

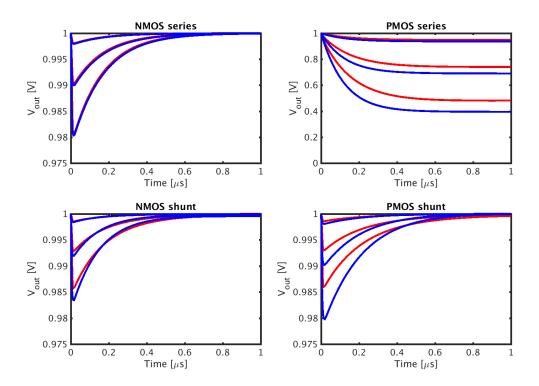

It can be seen that the equations match quite well with the simulated model, even for current steps of 1mA.

Figure 2.20: The simulated load transient response for load steps of 100uA, 500uA and 1mA. The response of the transistor models (blue) is compared to the Laplace transform of the output impedance of the model (red).

## 2.1.8 Line transient

The ISR must be able to cope with dynamic variations on the supply. As mentioned in chapter 1, the conditions in the automotive environment are quite harsh. The effects described in [1] can cause voltage peaks as high as 70V with rise times that can be as short as 5ns. Extensively large voltages are mostly handled by protection diodes within the IC. Nonetheless the ISR is directly supplied from the external supply and therefore needs to be robust against line variations.

## **Description**

The line transient response shows the dynamic behavior of the output voltage  $(V_{out}(t))$  caused by a step in the supply voltage  $(V_{dd}(t))$ . Important parameters to observe are the settling time and the peak amplitude of the output voltage.

The transient behavior can be predicted from the small signal PSR. Voltage steps with a large amplitude will deviate from this response due to large signal effects.

## Comparison

The line step response can be approximated by doing an inverse Laplace transform on the output voltage  $(V_{OUT}(s))$ .

$$V_{out}(t) = \mathcal{L}^{-1} \left\{ V_{OUT}(s) \right\}$$

$$= \mathcal{L}^{-1} \left\{ \frac{V_{DD}(s)}{PSR(s)} \right\}$$

(2.55)

The VRL increases the PSR of the output stage:

$$PSR(s) = PSR_{OL}(s)[1 + A(s)\beta_v]$$

(2.56)

For the  $PSR_{OL}$  expressions of the different topologies, see section 2.1.1.

### Model verification

Figure 2.21: The simulated line transient response for supply steps of 1V, 10V and 50V. The response of the transistor models (blue) is compared to the Laplace transform of the output impedance of the model (red).

It can be seen that the equations match quite well with the simulated model. The simulations start to deviate at voltage steps above 10V due to large signal behavior.

## 2.1.9 Gain-Bandwidth Product

The open loop approach disregards the influence of the VRL. However the choice of topology does have an effect on the maximum Gain-Bandwidth (GBW) that can be

achieved in the VRL. In the following subsections, the Gain-Bandwidth capabilities of the topologies will be investigated.

## Description

The GBW is mainly dependent on the parasitic capacitances within the VRL and the transconductances of the transistors. A large GBW results in a fast loop response to disturbances with high suppression.

## Comparison

An estimate for the maximum attainable bandwidth of the loop can be made using the Loopgain-Poles product (LP product) [10]. The LP product is defined as:

$$LP_n = (1 - L_{DC}) \prod_{i=1}^{n} |p_i|$$

(2.57)

Where n is the number of poles in the loop and  $L_{DC}$  is the DC loop gain. The maximum attainable UGF is given by:

$$\omega_{n,max} = \sqrt[n]{LP_n} = \sqrt[n]{(1 - L_{DC}) \prod_{i=1}^{n} |p_i|}$$

(2.58)

**NMOS** series The two largest capacitances that influence the loop in the NMOS series topology are  $C_{DEC1}$  and  $C_{OUT}$  (figure 2.22). To calculate the equation for the loop gain, the loop is broken at the input of the feedback network. The loop gain is now calculated as:

$$A(s)\beta_v = \frac{v_{out}}{v_x} = -\frac{Gm_{TA}g_{m1}\beta}{(G_{TA} + sC_{DEC1})(g_{o1} + G_{CS} + G_{\beta_v,in} + g_{m1} + sC_{OUT})}$$

(2.59)

The pole at the output node can be considered as a non-dominant pole. The maximum attainable UGF as indicated by the LP-product is given by:

$$\omega_{max} = \left(1 + \frac{Gm_{TA}g_{m1}\beta}{G_{TA}(g_{o1} + G_{CS} + G_{\beta_{r},in} + g_{m1})}\right) \frac{G_{TA}}{C_{DEC1}}$$

(2.60)

Figure 2.22: Schematic for determining the loop transfer function of the NMOS series regulator.

**PMOS** series The three largest capacitances that influence the loop in the PMOS series topology are  $C_{DEC1}$ ,  $C_{GD1}$ , and  $C_{OUT}$  (figure 2.23). To calculate the equation for the loop gain, the loop is broken at the input of the feedback network. The poles are first approximated without the influence of  $C_{GD1}$ . The poles of the simplified system are given by:

$$p_{1} = -\frac{G_{TA}}{C_{DEC1}}$$

$$p_{2} = -\frac{g_{o1} + G_{CS} + G_{\beta_{v},in}}{C_{OUT}}$$

(2.61)

The maximum UGF as indicated by the LP-product is given by:

$$\omega_{n,max} = \sqrt{\left(1 + \frac{Gm_{TA}\beta g_{m1}}{G_{TA}}\right)\left(\frac{G_{TA}}{C_{DEC1}}\right)\left(\frac{g_{o1} + G_{CS} + G_{\beta_v,in}}{C_{OUT}}\right)}$$

(2.62)

If  $p_1 > p_2$ ,  $C_{GD1}$  will be subdued to the Miller effect and will have a substantial impact on the frequency behavior of the loop. The local feedback through  $C_{GD1}$  causes  $p_1$  and  $p_2$  to split. The splitting of the poles will lower the LP-product by [10]:

$$\frac{LP_{after}}{LP_{before}} = \frac{C_{DEC1}C_{OUT}}{C_{DEC1}C_{OUT} + C_{GD1}(C_{DEC1} + C_{OUT})}$$

(2.63)

Figure 2.23: Schematic for determining the loop transfer function of the PMOS series regulator.

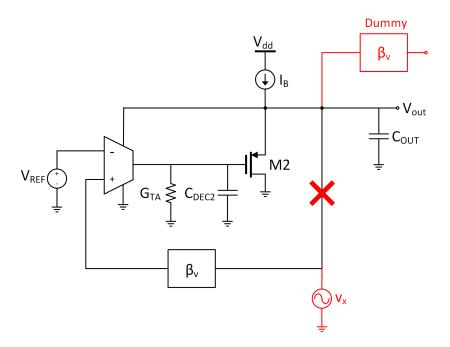

**NMOS** shunt The two capacitances that influence the loop in the NMOS shunt topology are  $C_{DEC2}$ , and  $C_{OUT}$  (figure 2.24). To calculate the equation for the loop gain, the loop is broken at the input of the feedback network. The poles are first approximated without the influence of  $C_{DEC2}$ . The poles of the simplified system are given by:

$$p_{1} = -\frac{G_{TA}}{C_{GS2}}$$

$$p_{2} = -\frac{g_{o2} + G_{CS} + G_{\beta_{v},in}}{C_{OUT}}$$

(2.64)

The maximum UGF as indicated by the LP-product is given by:

$$\omega_{n,max} = \sqrt{(1 + \frac{Gm_{TA}\beta g_{m2}}{G_{TA}})(\frac{G_{TA}}{C_{GS2}})(\frac{g_{o2} + G_{CS} + G_{\beta_v,in}}{C_{OUT}})}$$

(2.65)

If  $p_1 > p_2$ ,  $C_{DEC2}$  will be subdued to the Miller effect and will have a substantial impact on the frequency behavior of the loop. The local feedback through  $C_{DEC2}$  causes  $p_1$  and  $p_2$  to split. The splitting of the poles will lower the LP-product by [10]:

$$\frac{LP_{after}}{LP_{before}} = \frac{C_{GS2}C_{OUT}}{C_{GS2}C_{OUT} + C_{DEC2}(C_{GS2} + C_{OUT})}$$

(2.66)

Figure 2.24: Schematic for determining the loop transfer function of the NMOS shunt regulator.

**PMOS** shunt The two largest capacitances that influence the loop in the PMOS shunt topology are  $C_{DEC2}$  and  $C_{OUT}$  (figure 2.25). To calculate the equation for the loop gain, the loop is broken at the input of the feedback network. The loop gain is now calculated as:

$$A(s)\beta_v = \frac{v_{out}}{v_x} = -\frac{Gm_{TA}g_{m2}\beta}{(G_{TA} + sC_{DEC2})(g_{o2} + G_{CS} + G_{\beta_v,in} + g_{m2} + sC_{OUT})}$$

(2.67)

The pole at the output node can be considered as a non-dominant pole. The maximum UGF as indicated by the LP-product is given by:

$$\omega_{max} = \left(1 + \frac{Gm_{TA}g_{m2}\beta}{G_{TA}(g_{o2} + G_{CS} + G_{\beta_{n},in} + g_{m2})}\right) \frac{G_{TA}}{C_{DEC2}}$$

(2.68)

Figure 2.25: Schematic for determining the loop transfer function of the PMOS shunt regulator.

## 2.1.10 Area

In ISR designs where  $C_{OUT}$  is integrated, this capacitance is often the largest component. The main purpose of  $C_{OUT}$  is to supply load current for transient loads that are faster than the regulation loop. Only if the loop can be made fast enough to supply these transient load currents, significant area might be saved by reducing  $C_{OUT}$ . Although substantially smaller, the output MOS transistor is still quite large as it needs to dissipate a lot of power. The shunt topologies require larger output stage transistors as both current source  $I_B$  and the output transistor need to be able to handle the maximum amount of  $I_L$ .

# 2.2 Overall comparison

The topologies are compared by evaluating the performance parameters that were discussed in section 2. The results are shown in table 2.4.

As the focus of research in this thesis is mainly on EMI performance, the emission and PSR parameters are of most importance. In most literature, the series regulator is preferred over the shunt regulator due to its benefits in power efficiency. Although a very good PSR performance can be achieved using a NMOS series topology, it will not perform as well on emission as a shunt topology. If one would choose to use the shunt topology, a few downsides have to be faced:

- 1. Poor power efficiency

- 2. Limited current output range

- 3. Small increase in area

|                  | Shi  | unt  | Series |      |  |

|------------------|------|------|--------|------|--|

|                  | NMOS | PMOS | NMOS   | PMOS |  |

| PSR              | +    | +    | ++     |      |  |

| Emission         | +    | ++   |        | -    |  |

| Drop-out voltage | ++   | ++   | -      | ++   |  |

| Power efficiency | -    | -    | +      | +    |  |

| Load regulation  | -    | +    | ++     | -    |  |

| Line regulation  | -    | +    | ++     | -    |  |

| Load transient   | -    | +    | ++     | -    |  |

| Line transient   | -    | +    | ++     | -    |  |

| Bandwidth        | -    | ++   | +      |      |  |

| Area             | -    |      | ++     | +    |  |

Table 2.4: Comparison between the four regulator topologies, using the performance parameters.

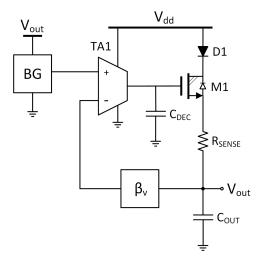

# 2.3 ISR in the KMA3xx family

## 2.3.1 Description

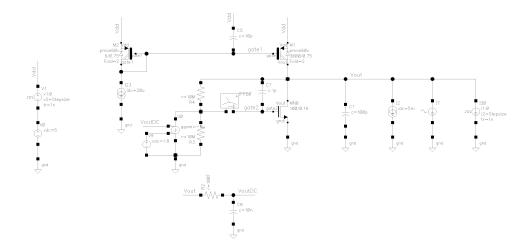

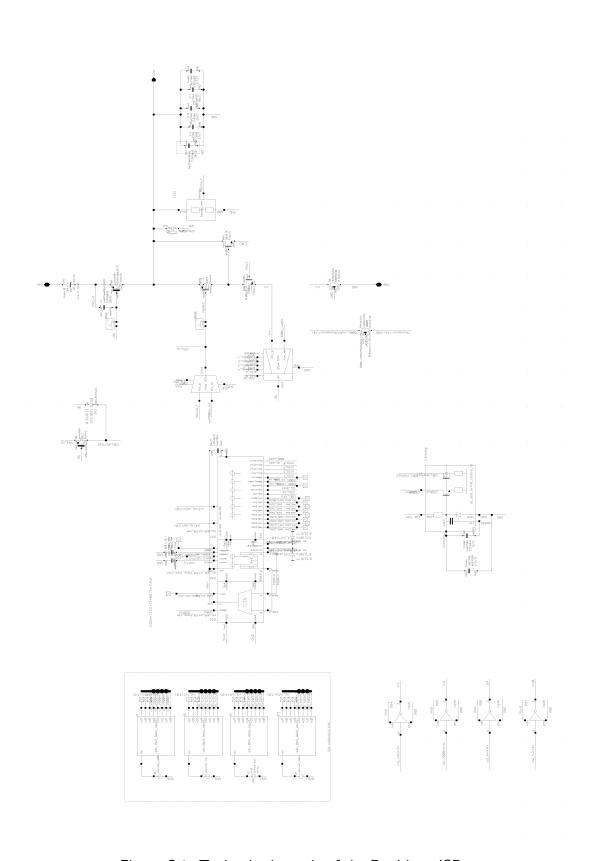

The digital regulator that is used in the KMA3xx angular sensors is used as a reference design for performance. The topology is shown in figure 2.26. Component values are shown in table 2.5.

Figure 2.26: Architecture of the KMA3xx NMOS series regulator.

$R_{sense}$  is placed in the load current path for testability. As a side effect,  $R_{sense}$  has significant impact on the EMC performance at high frequencies.

D1 is needed to protect M1 from a large inrush current in case the supply pins are reverse connected. In the NMOS series topology, it has no significant impact on the drop-out voltage.

The area of the toplevel components in figure 2.26 is shown in table 2.6.

It can be seen that most area in the design is consumed by the bandgap reference.

| Circuit parameter | Value                  |  |  |

|-------------------|------------------------|--|--|

| $C_{DEC1}$        | 25.31pF                |  |  |

| $C_{OUT}$         | 73.5pF                 |  |  |

| $R_{SENSE}$       | $53\Omega$             |  |  |

| $(W/L)_1$         | 960                    |  |  |

| $V_{BG}$          | 900mV                  |  |  |

| $\beta_v$         | 0.5                    |  |  |

| $R_{TA}$          | $763 \mathrm{M}\Omega$ |  |  |

| $A_{DC}$          | 87.6dB                 |  |  |

Table 2.5: Component values for the KMA3xx ISR as shown in figure 2.26.

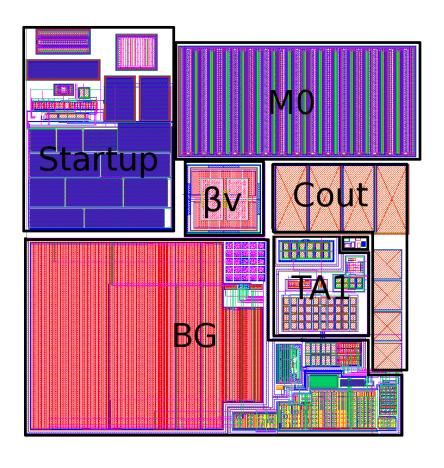

| System block | Area ( $\mu m^2$ ) | <b>Area</b> (%) |  |

|--------------|--------------------|-----------------|--|

| BG           | 56939.7            | 68.9            |  |

| $C_{OUT}$ *  | 6715.6             | 8.1             |  |

| $\beta_v$    | 6630.7             | 8.0             |  |

| M1           | 6408.2             | 7.8             |  |

| TA1          | 4218.3             | 5.1             |  |

| D1           | 1682.6             | 2.0             |  |

| $R_{SENSE}$  | 62.2               | 0.1             |  |

| $C_{DEC}$ *  | 0                  | 0               |  |

Table 2.6: Area of the toplevel components of the KMA3xx NMOS series regulator. \*: The area consumed by MIM capacitors is excluded.

# Chapter 3

# Design of the ISR

In this chapter, a new topology will be proposed based on the knowledge that was acquired in the previous chapter. The chapter is divided in a section that describes the ISR on system level and a section that describes the ISR on circuit level. At the end of the system level section, all the circuit blocks are defined along with the specifications they should meet. These specifications are then used in the circuit level section, while designing the individual circuit blocks.

# 3.1 System design

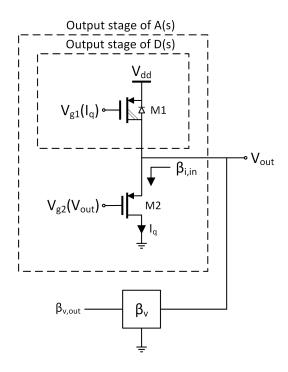

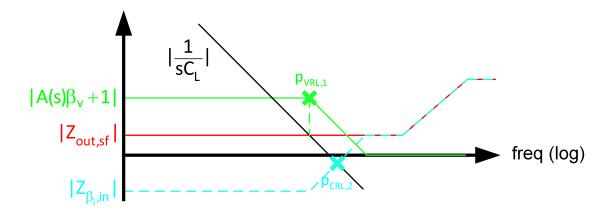

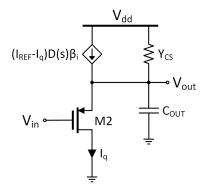

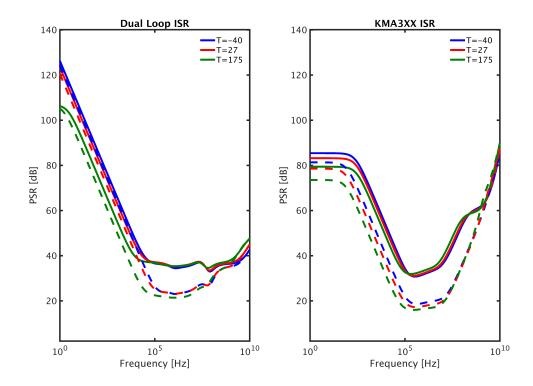

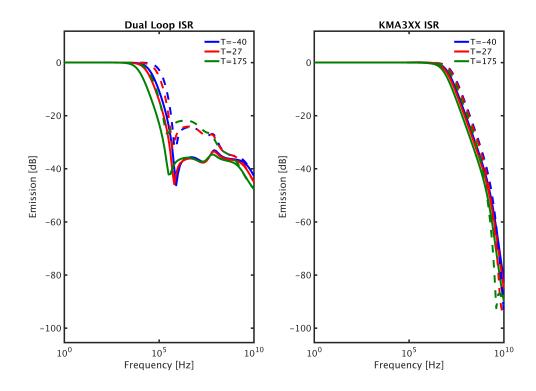

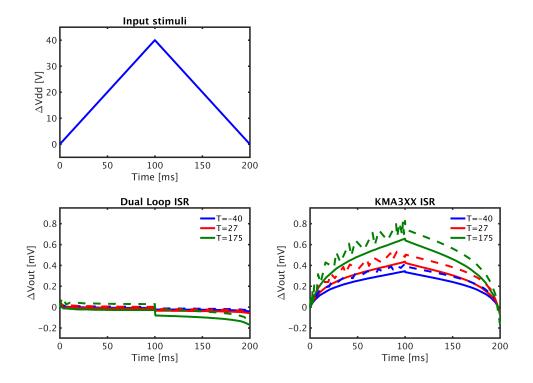

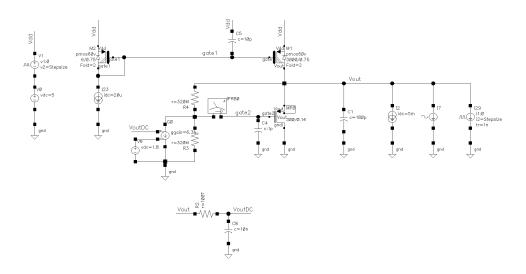

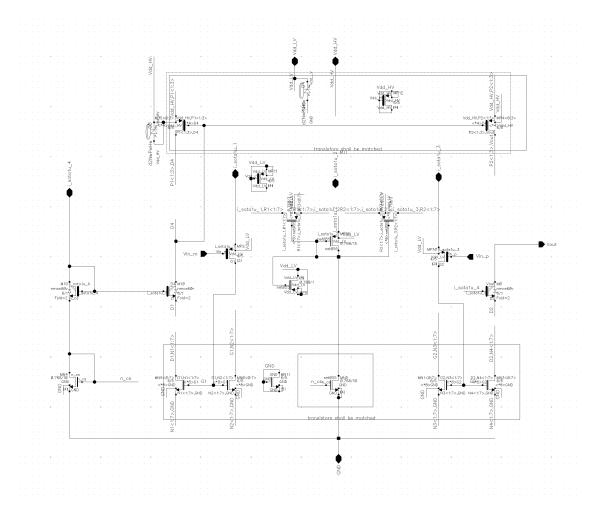

With the performance parameters of table 2.4 in mind, a topology based on a shunt regulator is proposed. The shunt regulator is chosen due to its capability to attain good performance on both PSR and emission.

## 3.1.1 Concept

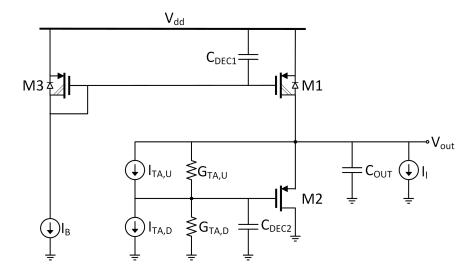

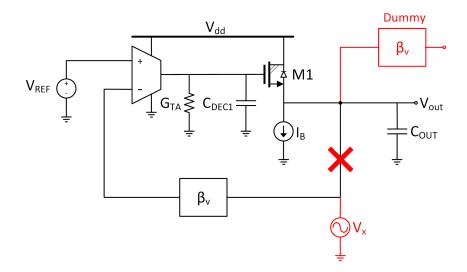

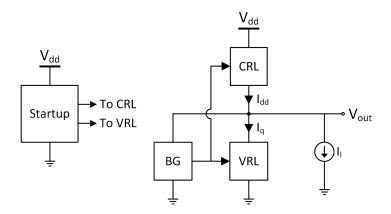

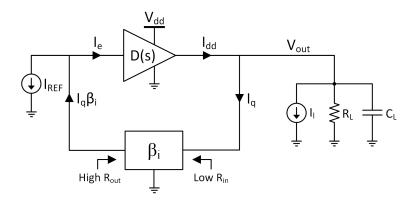

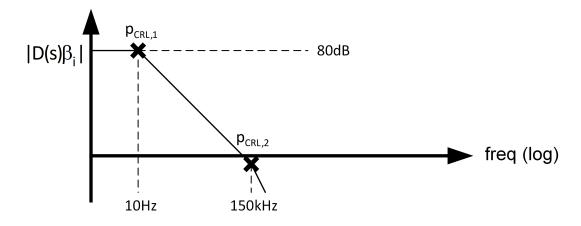

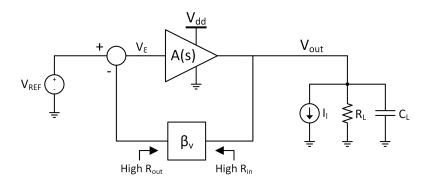

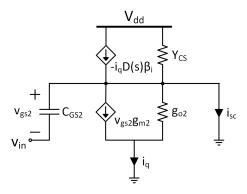

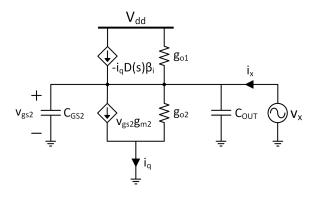

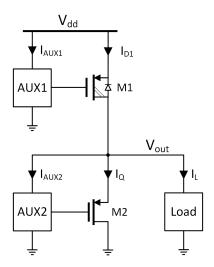

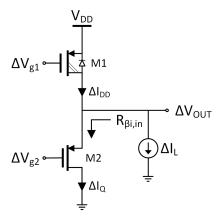

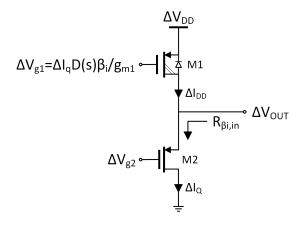

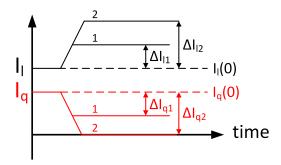

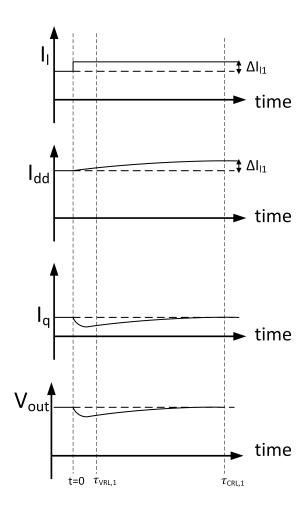

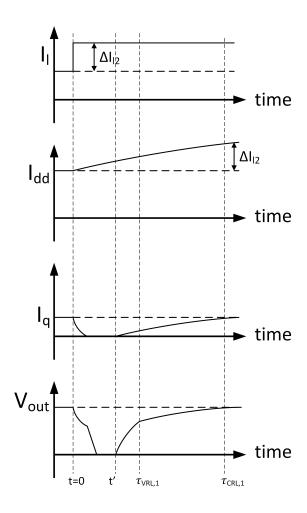

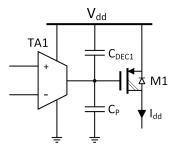

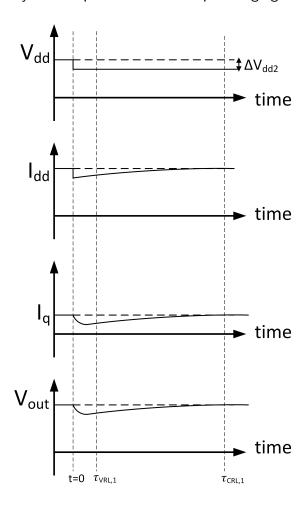

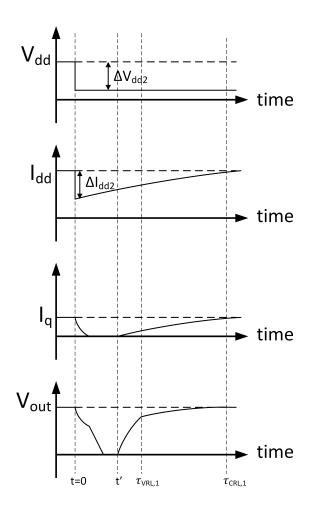

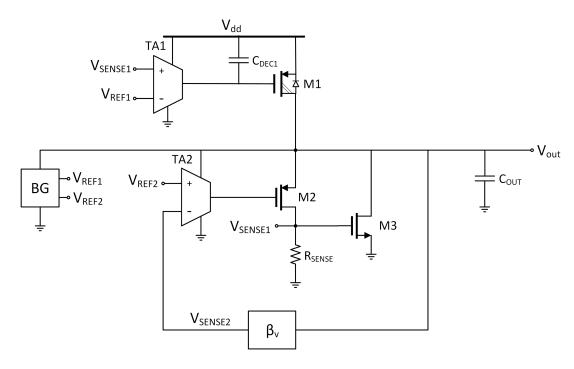

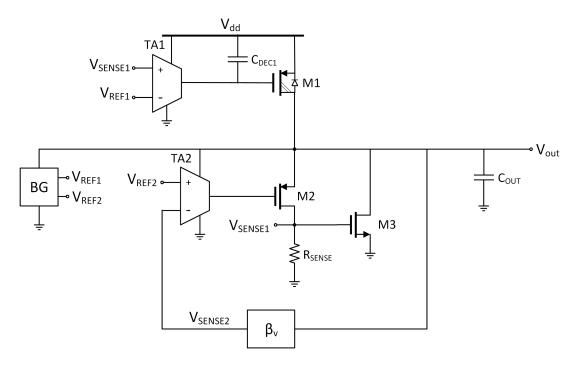

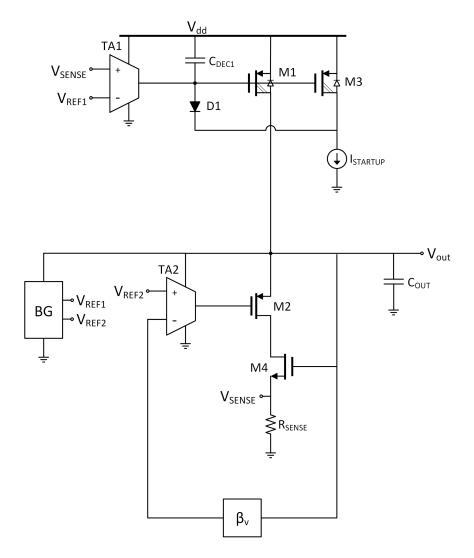

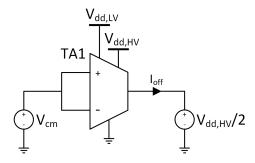

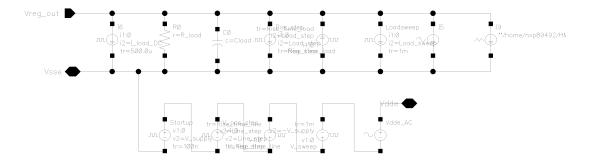

A lot of disadvantages of the shunt regulator topologies are caused by the fact that the bias current of the output stage  $(I_Q)$  is dependent on the load current  $(I_L)$ . A second regulation loop is proposed in order to keep  $I_Q$  constant (figure 3.1).

Figure 3.1: Proposed dual loop topology.