# ELECTRONIC INSTRUMENTATION

# ELECTRONIC INSTRUMENTATION

## P.P.L. REGTIEN

Delft

Academic

Press

© Delft Academic Press

Third edition 2015 - hardcover reprint 2017

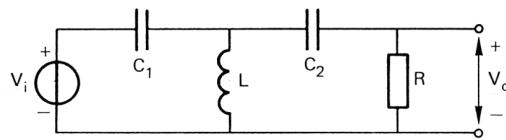

Published by:

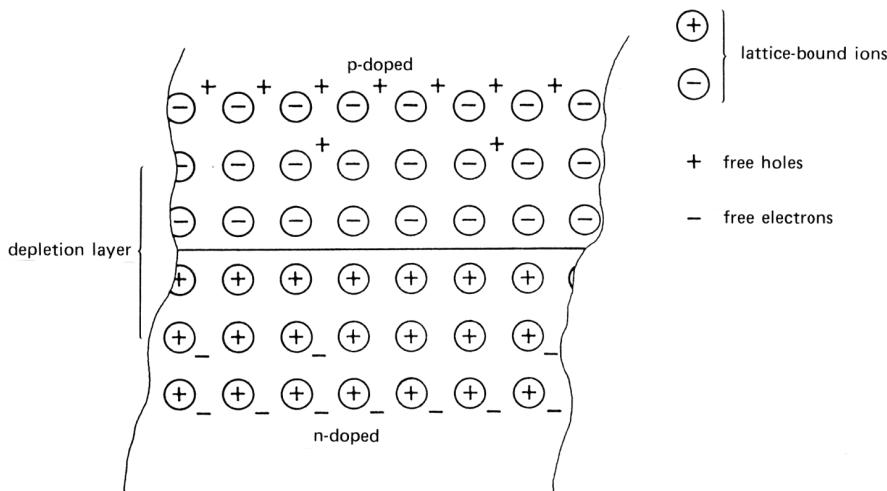

Delft Academic Press /VSSD

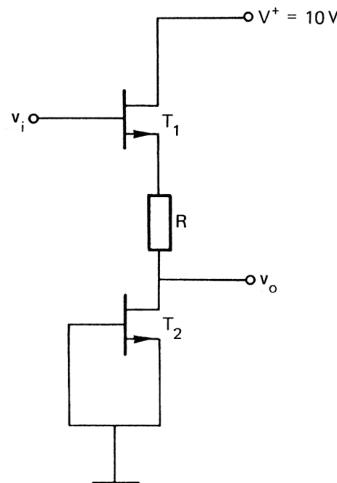

Leeghwaterstraat 42, 2628 CA Delft, The Netherlands

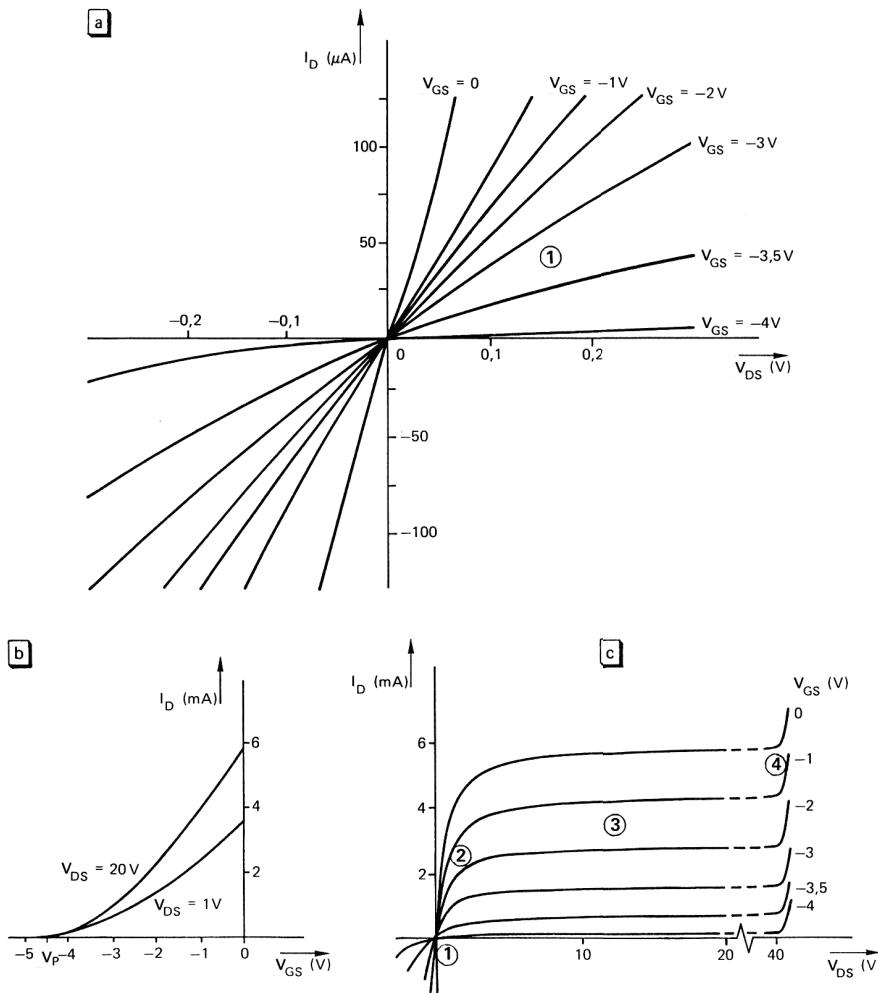

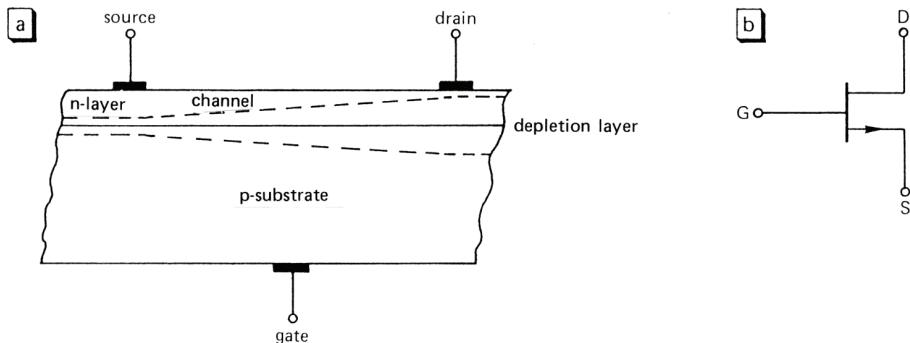

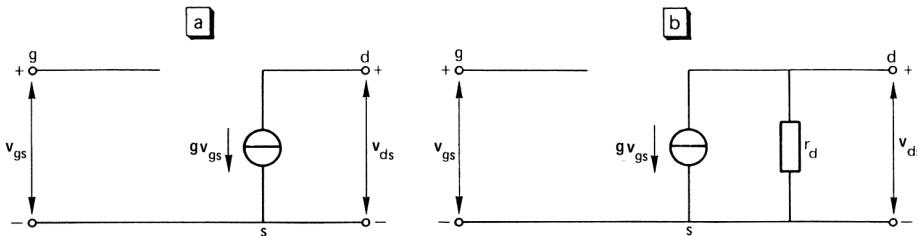

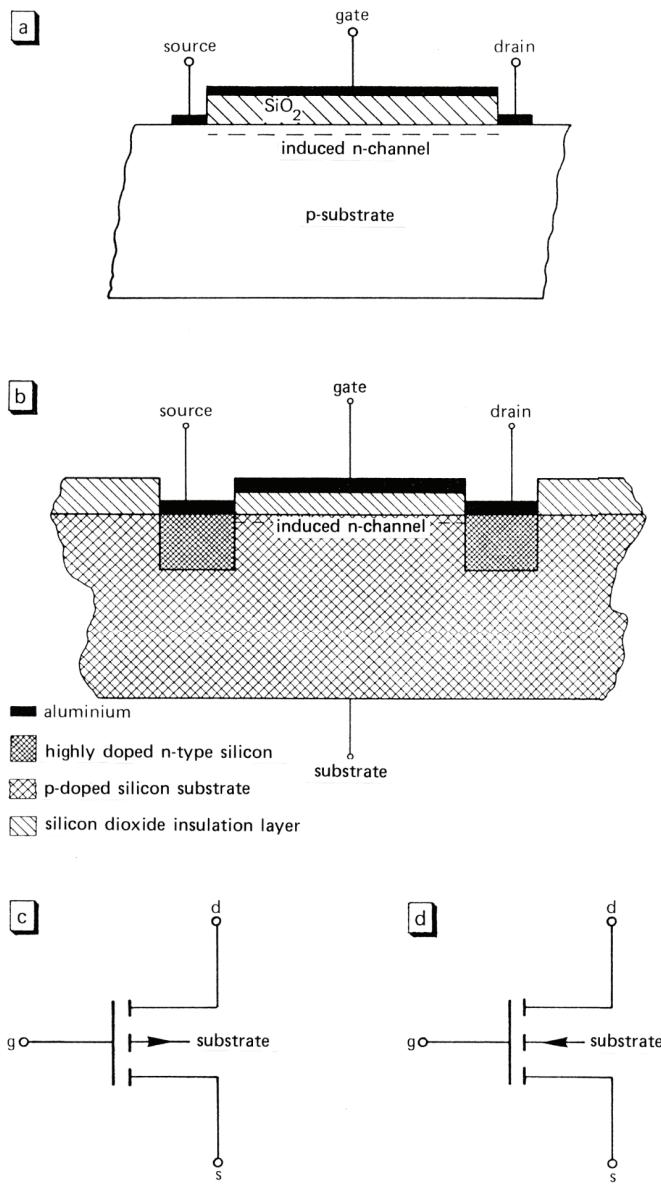

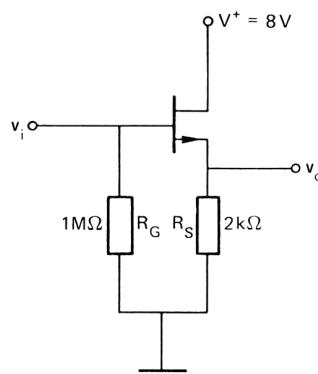

tel. +31 15 27 82124

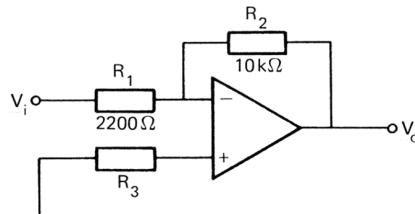

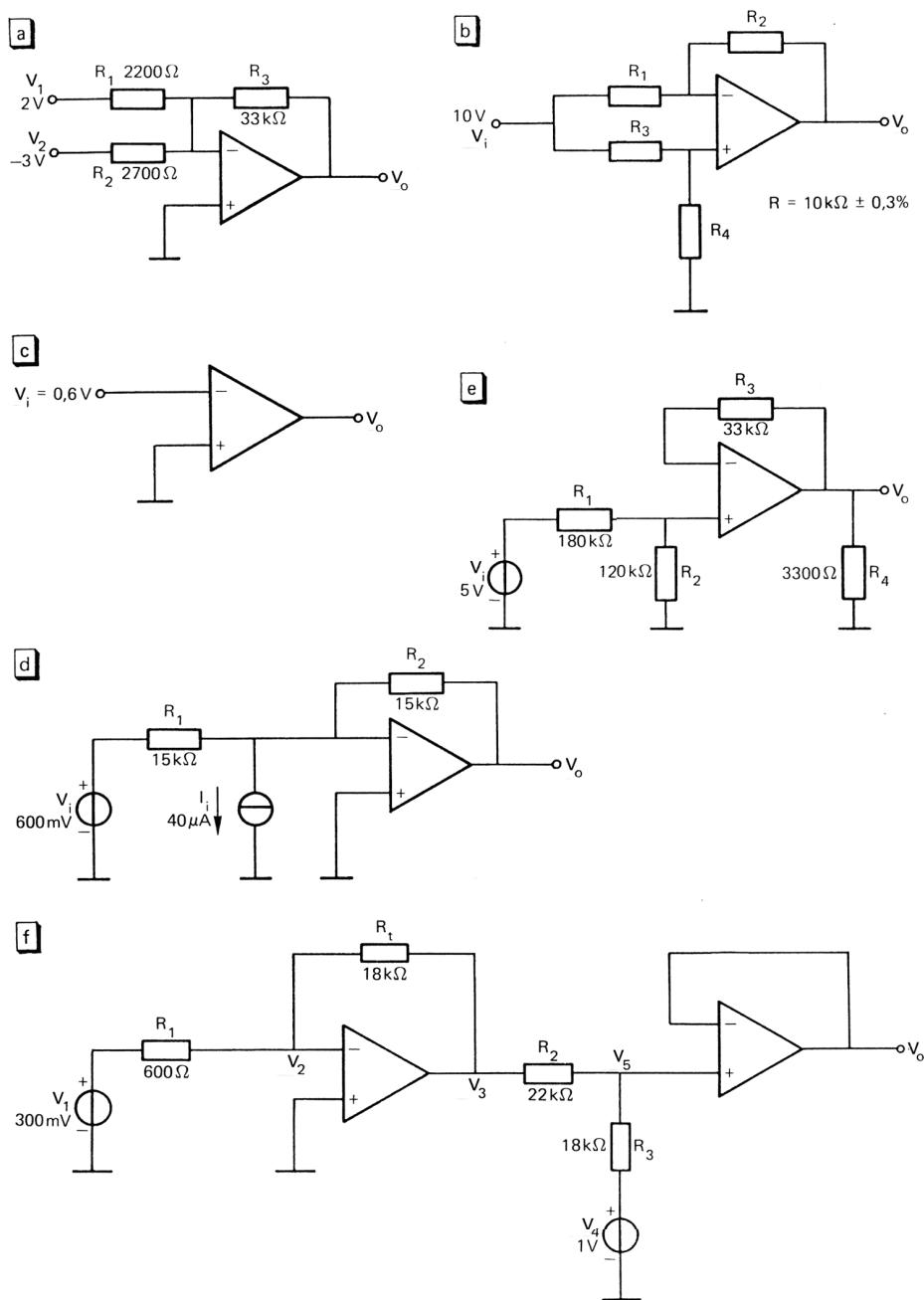

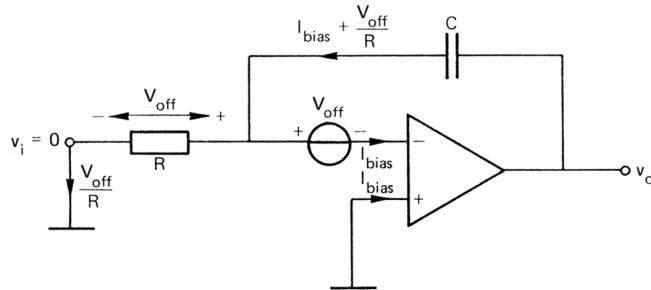

[dap@vssd.nl](mailto:dap@vssd.nl)

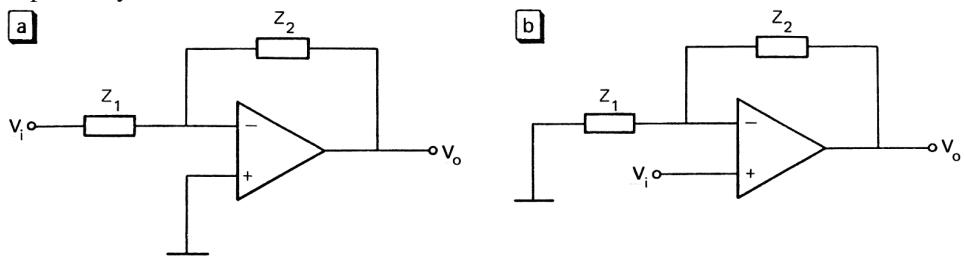

[www.delftacademicpress.nl](http://www.delftacademicpress.nl)

[www.delftacademicpress.nl/e008.php](http://www.delftacademicpress.nl/e008.php)

A collection of digital pictures and/or an electronic version can be made available for lecturers who adopt this book. Please send a request by e-mail to [dap@vssd.nl](mailto:dap@vssd.nl)

*All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.*

Printed in The Netherlands.

ISBN 97890-6562-4130

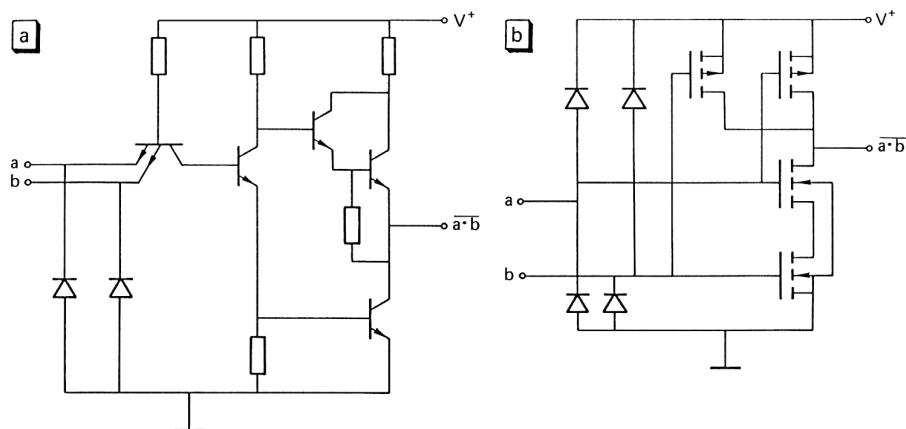

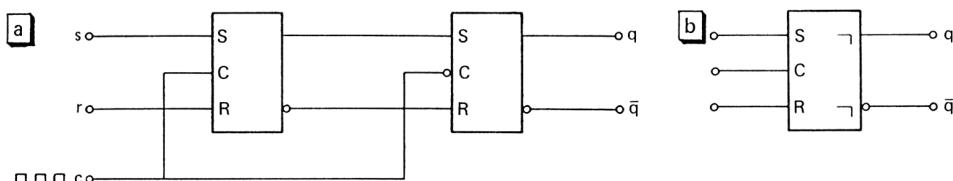

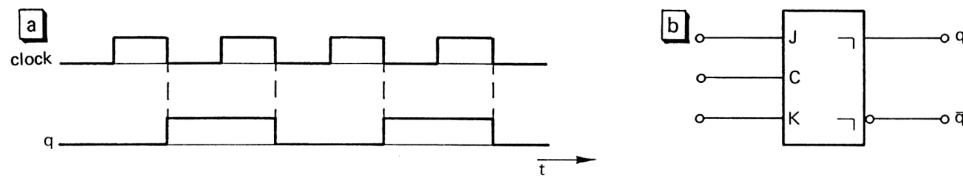

NUR 959

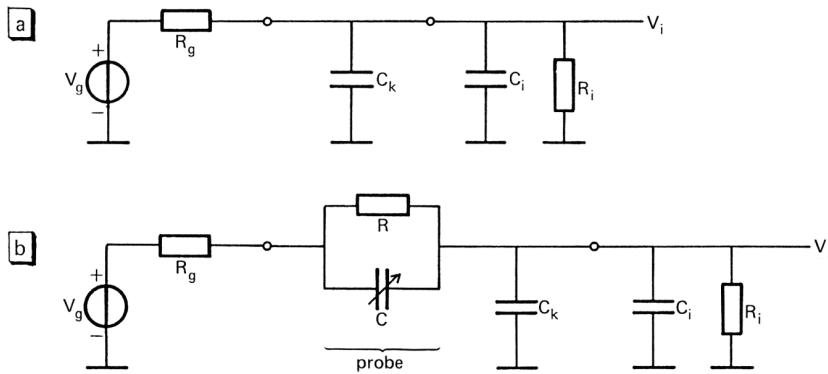

*Keywords:* electronic instrumentation

---

## Preface

Electronic systems have made deep inroads into every aspect of daily life. One need only look around homes, offices and industrial plants to see that they feature almost everywhere. Indeed, it is practically impossible to name any appliances, tools or instruments that do not contain electronic components. In order to compete with rival companies or just remain a step ahead of them, the designers of technical systems and innovative products must be fully aware of both the assets and the limitations of electronic components and systems. Users of electronic systems also need to have a basic knowledge of electronic principles. In order to fully exploit an instrument's potential, to be aware of its limitations, to correctly interpret the measurement results and to be able to arrive at well-balanced decisions relating to the purchasing, repairing, expansion or replacement of electronic equipment, all users of such systems also need to have a basic knowledge of electronic principles.

This book offers such basic knowledge and provides guidance on how to obtain the relevant skills. The kinds of topics dealt with are operating principles, the performance of analog and digital components and circuits, and the precise characteristics of electronic measuring systems. Throughout the book, every endeavor is made to impart a critical attitude to the way in which such instruments should be implemented.

The book is based on various series of courses on electronics and electronic instrumentation that were given by the author during the many years when he lectured at Delft University of Technology in the Netherlands. The courses were designed for students from various departments such as: Mechanical Engineering, Aeronautical Engineering and Mining Engineering. When numbers of non-Dutch-speaking Master of Science students started to rise it became necessary to publish an English version of the book.

The particular way in which the book has been organized makes it suitable for a much wider readership. To meet the demands of divergent groups it has been structured in a modular fashion. Each chapter discusses just one particular topic and is divided into two parts: the first part provides the basic principles while more specific information is given in the second part. Each chapter ends with a summary and several exercises. Answers to all the exercises are given at the back of the book. This approach is conducive to self-study and to the composition of tailor-made course programs.

The required background knowledge is a basic grounding in mathematics and physics equivalent to any first-year academic level. No background knowledge of electronics is needed to understand the contents of the book. For further information on particular

subjects the reader is referred to the many course books that exist on the subjects of electronics, measurement techniques and instrumentation.

I am indebted to all the people who contributed to the realization of this book. In particular I would like to thank Johan van Dijk who carefully refereed the original Dutch text. I am grateful also to Reinier Bosman for working out all the exercises, to G. van Berkel for creating the more than 600 illustrations, to Jacques Schievink for processing the original Dutch editions and this English version of the book and to Diane Butterman for reviewing the entire English text.

Paul Regtien

Hengelo, August 2004

### **Preface to the third edition 2015**

In this edition several corrections have been made to the second edition.

The publisher

Delft, september 2015

---

|                                                                       |    |

|-----------------------------------------------------------------------|----|

| Preface .....                                                         | v  |

| 1 Measurement systems .....                                           | 1  |

| 1.1 System functions .....                                            | 1  |

| 1.2 System specifications .....                                       | 5  |

| SUMMARY .....                                                         | 11 |

| EXERCISES .....                                                       | 12 |

| 2 Signals .....                                                       | 14 |

| 2.1 Periodic signals .....                                            | 14 |

| 2.1.1 A classification of signals .....                               | 14 |

| 2.1.2 Signal values .....                                             | 15 |

| 2.1.3 Signal spectra .....                                            | 17 |

| 2.2 Aperiodic signals .....                                           | 22 |

| 2.2.1 Complex Fourier series .....                                    | 22 |

| 2.2.2 The Fourier integral and the Fourier transform .....            | 24 |

| 2.2.3 A description of sampled signals .....                          | 26 |

| 2.2.4 A description of stochastic signals .....                       | 27 |

| SUMMARY .....                                                         | 32 |

| EXERCISES .....                                                       | 34 |

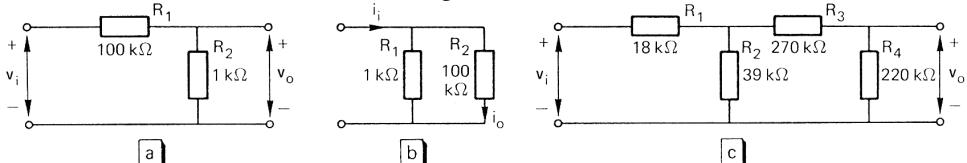

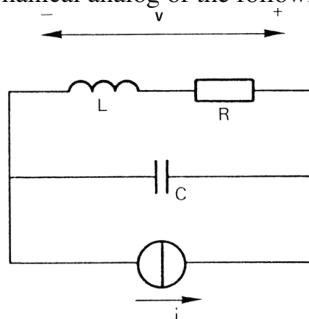

| 3 Networks .....                                                      | 36 |

| 3.1 Electric networks .....                                           | 36 |

| 3.2 Generalized network elements .....                                | 41 |

| SUMMARY .....                                                         | 45 |

| EXERCISES .....                                                       | 46 |

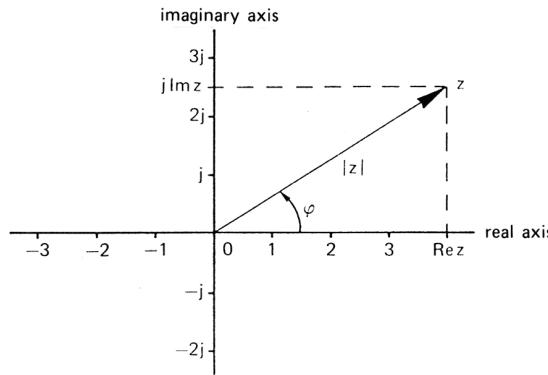

| 4 Mathematical tools .....                                            | 48 |

| 4.1 Complex variables .....                                           | 48 |

| 4.1.1 The properties of complex variables .....                       | 48 |

| 4.1.2 The complex notation of signals and transfer functions .....    | 49 |

| 4.1.3 Impedances .....                                                | 50 |

| 4.2 Laplace variables .....                                           | 52 |

| 4.2.1 The Laplace transform .....                                     | 52 |

| 4.2.2 Solving differential equations with the Laplace transform ..... | 54 |

| 4.2.3 Transfer functions and impedances in the p-domain .....         | 55 |

| 4.2.4 The relation to the Fourier integral .....                      | 56 |

| SUMMARY .....                                                         | 57 |

| EXERCISES .....                                                       | 58 |

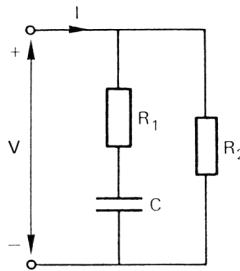

| 5 Models .....                                                        | 60 |

| 5.1 System models .....                                               | 60 |

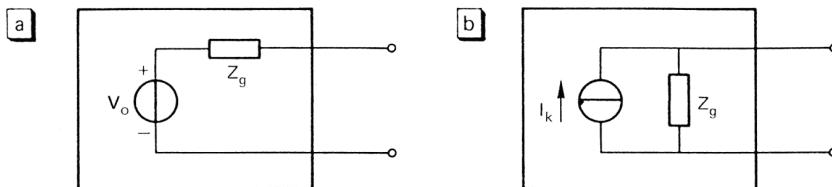

| 5.1.1 Two-terminal networks .....                                     | 60 |

| 5.1.2 Two-port networks .....                                         | 61 |

| 5.1.3 Matching .....                                                  | 65 |

| 5.1.4 Decibel notation .....                                          | 68 |

| 5.2 Signal models .....                                               | 69 |

| 5.2.1 Additive errors .....                                           | 69 |

| 5.2.2 Noise .....                                                     | 72 |

| SUMMARY .....                                                         | 73 |

| EXERCISES .....                                                       | 75 |

| 6 Frequency diagrams .....                                            | 77 |

| 6.1 Bode plots .....                                                  | 77 |

|        |                                                   |     |

|--------|---------------------------------------------------|-----|

| 6.1.1  | First order systems .....                         | 77  |

| 6.1.2  | Higher order systems .....                        | 79  |

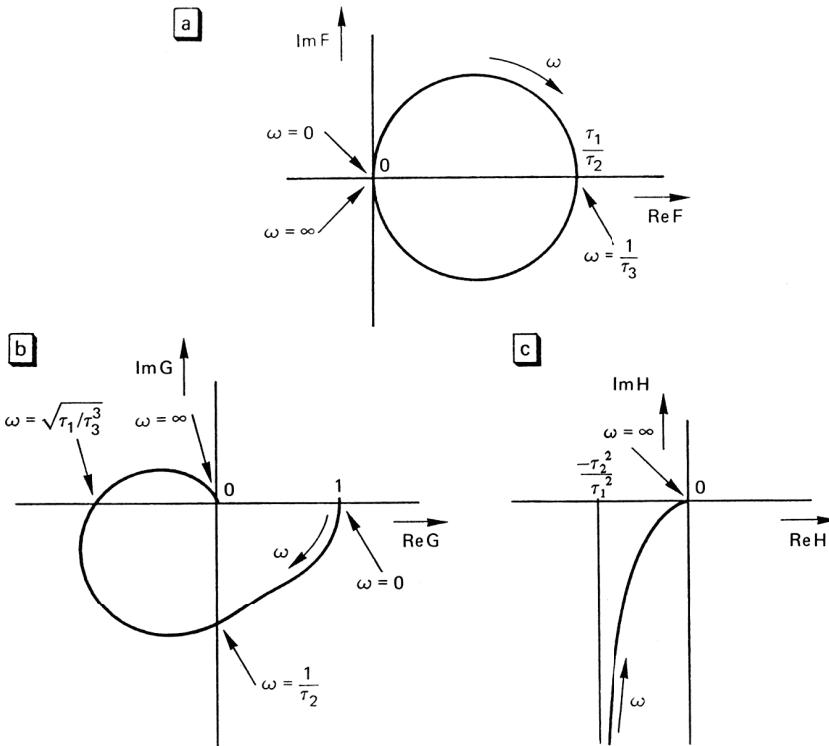

| 6.2    | Polar plots .....                                 | 82  |

| 6.2.1  | First order functions .....                       | 82  |

| 6.2.2  | Higher order functions .....                      | 84  |

|        | SUMMARY .....                                     | 87  |

|        | EXERCISES .....                                   | 88  |

| 7      | Passive electronic components .....               | 90  |

| 7.1    | Passive circuit components .....                  | 90  |

| 7.1.1  | Resistors .....                                   | 90  |

| 7.1.2  | Capacitors .....                                  | 92  |

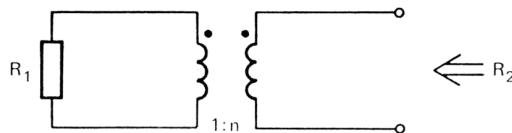

| 7.1.3  | Inductors and transformers .....                  | 94  |

| 7.2    | Sensor components .....                           | 97  |

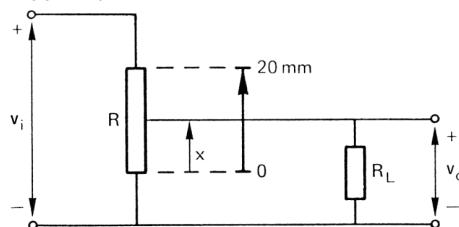

| 7.2.1  | Resistive sensors .....                           | 97  |

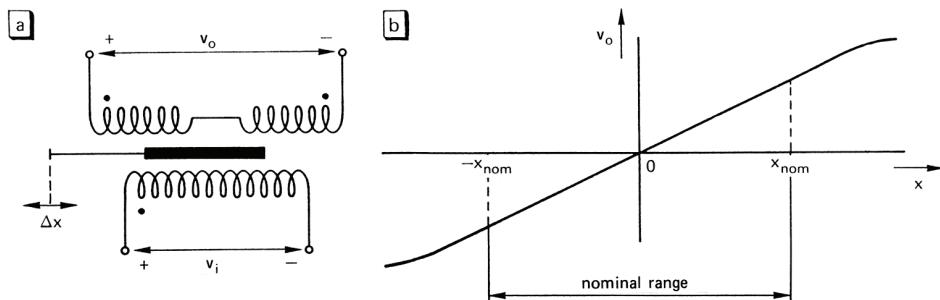

| 7.2.2  | Inductive sensors .....                           | 101 |

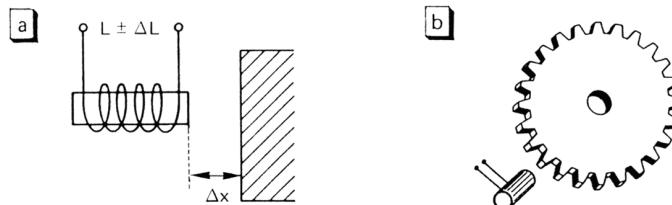

| 7.2.3  | Capacitive sensors .....                          | 102 |

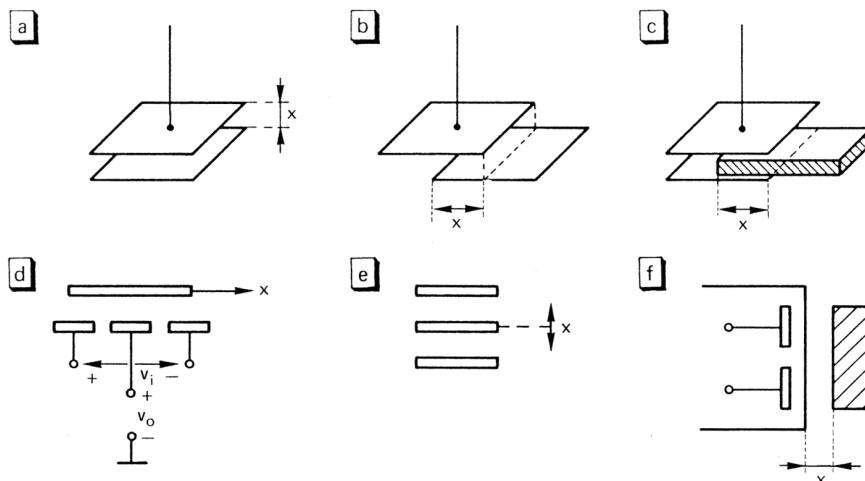

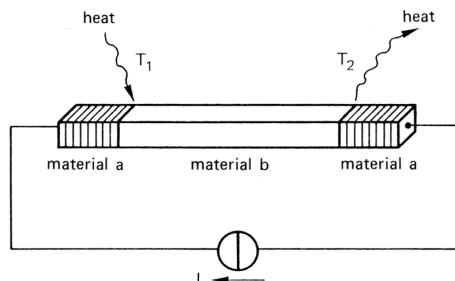

| 7.2.4  | Thermoelectric sensors .....                      | 103 |

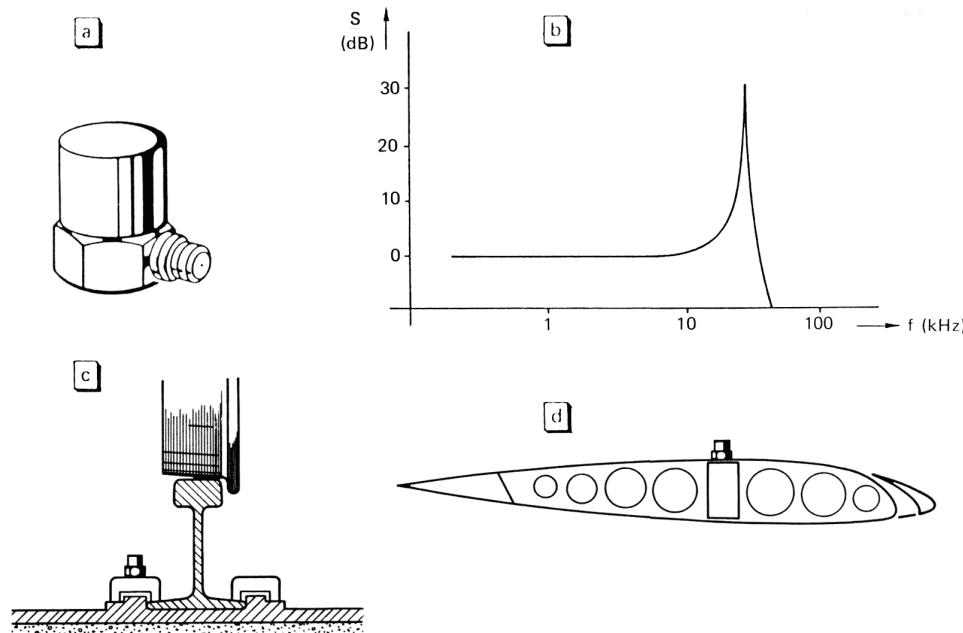

| 7.2.5  | Piezoelectric sensors .....                       | 106 |

|        | SUMMARY .....                                     | 108 |

|        | EXERCISES .....                                   | 109 |

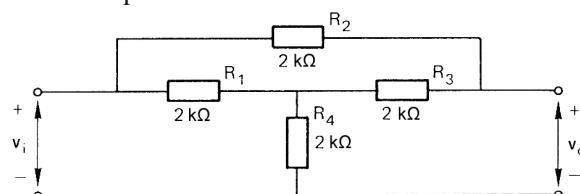

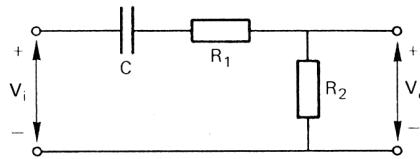

| 8      | Passive filters .....                             | 111 |

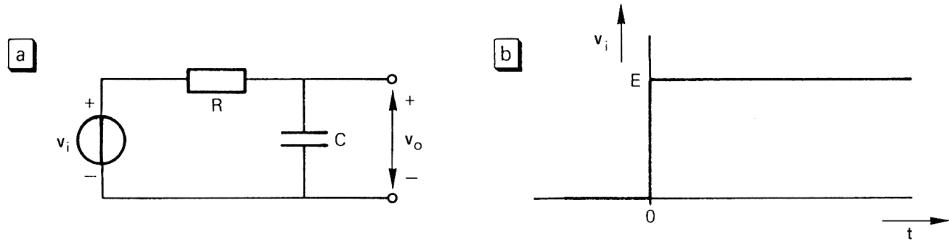

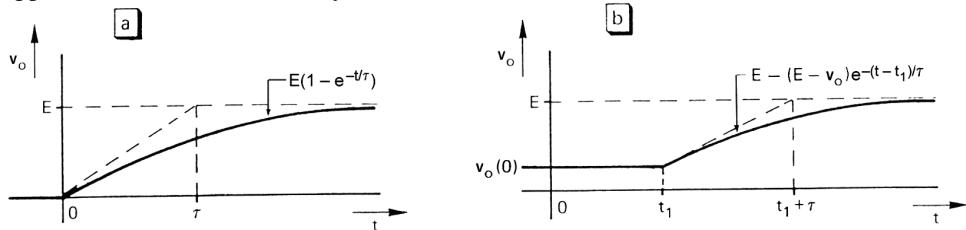

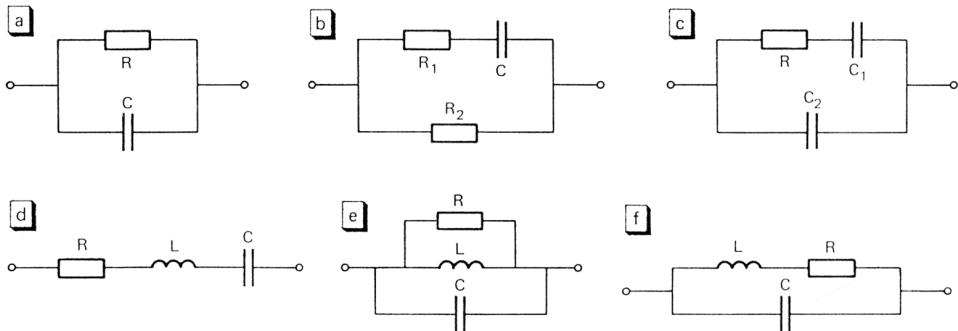

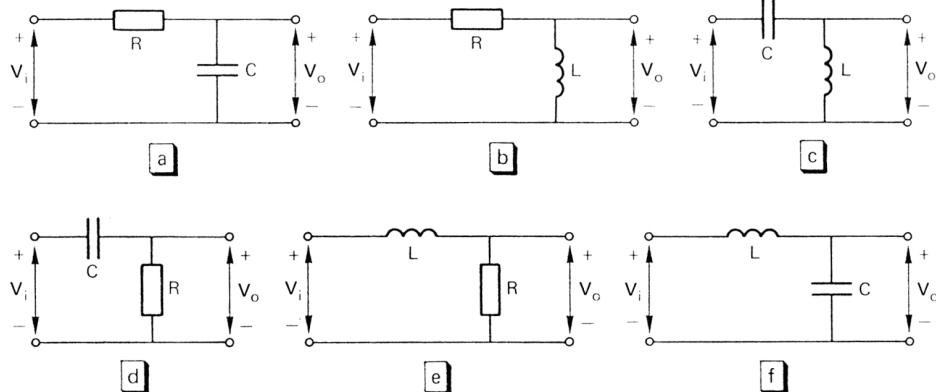

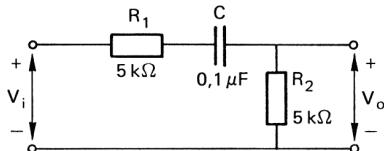

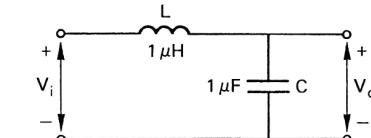

| 8.1    | First and second order RC-filters .....           | 112 |

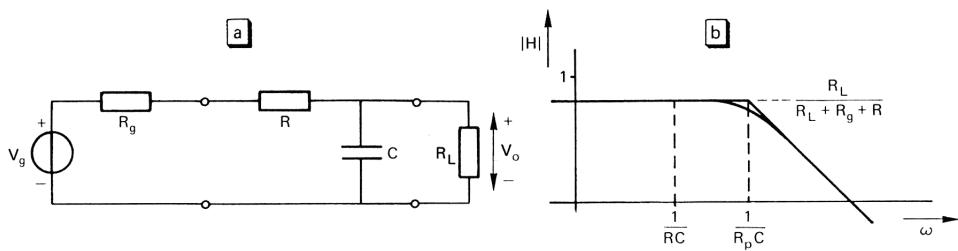

| 8.1.1  | Low-pass first-order RC-filter .....              | 112 |

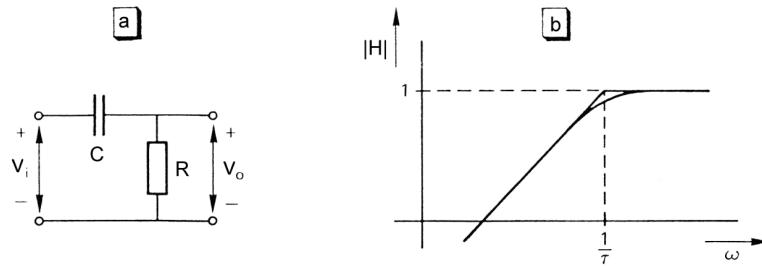

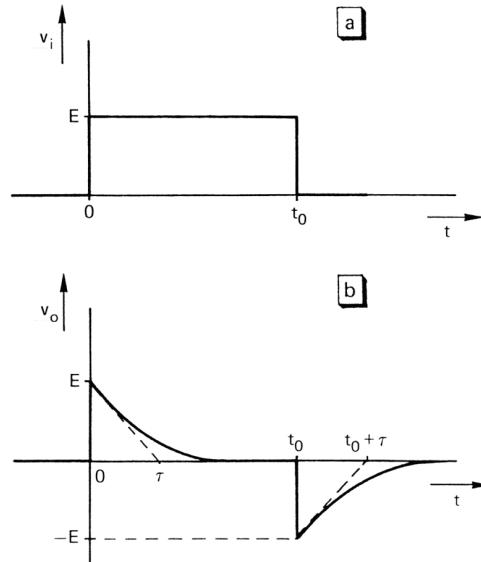

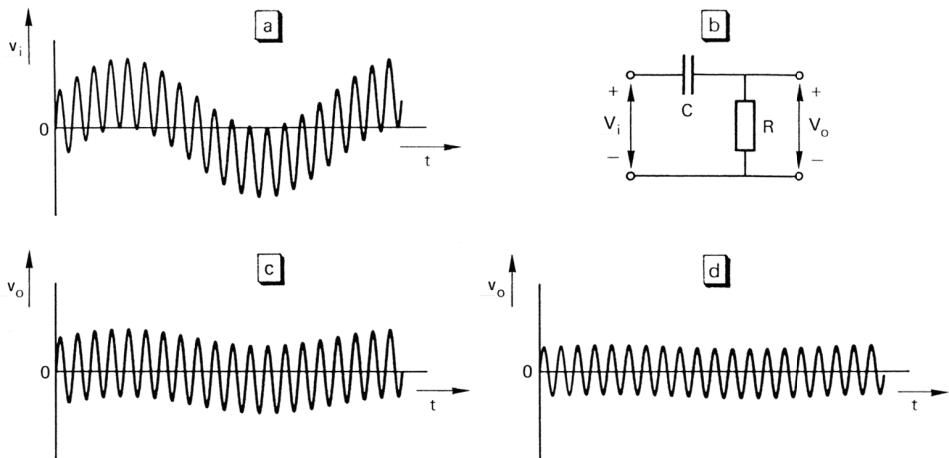

| 8.1.2  | Highpass first-order RC-filter .....              | 115 |

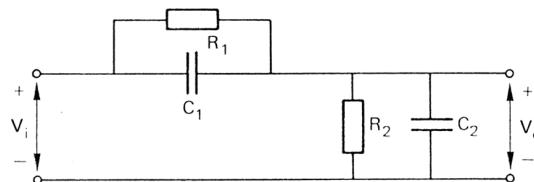

| 8.1.3  | Bandpass filters .....                            | 118 |

| 8.1.4  | Notch filters .....                               | 119 |

| 8.2    | Filters of higher order .....                     | 120 |

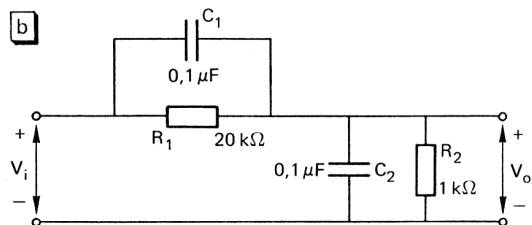

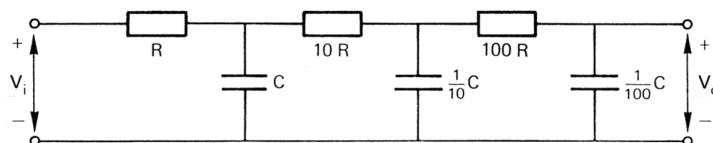

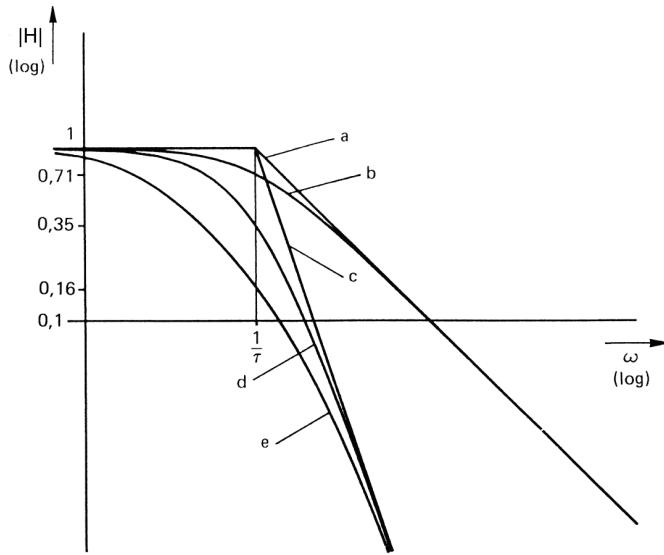

| 8.2.1  | Cascading first-order RC-filters .....            | 120 |

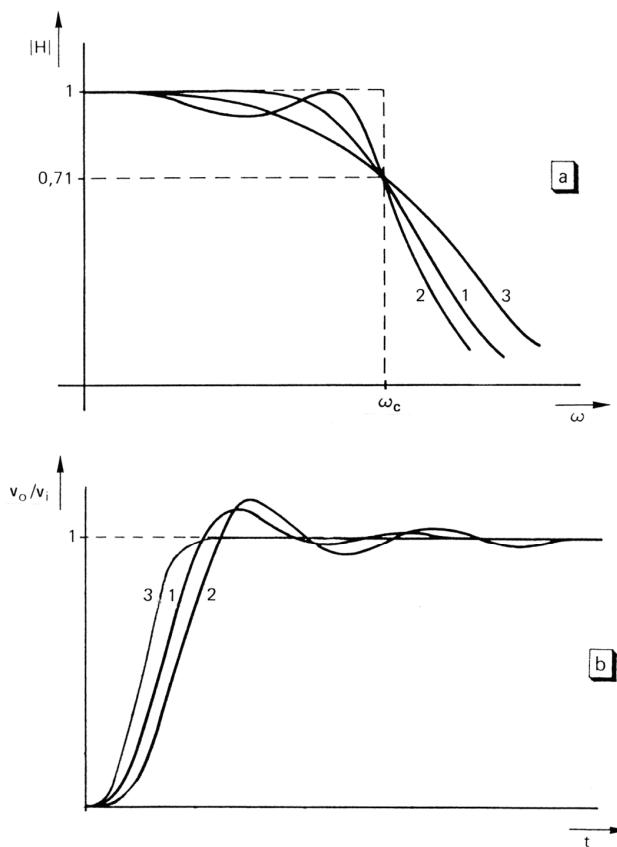

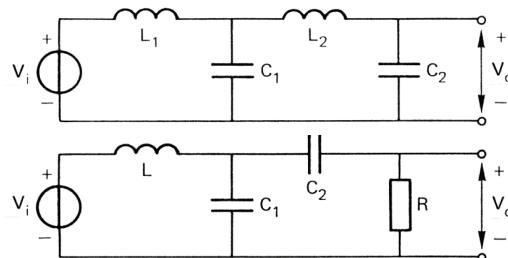

| 8.2.2  | Approximations of the ideal characteristics ..... | 121 |

|        | SUMMARY .....                                     | 123 |

|        | EXERCISES .....                                   | 124 |

| 9      | PN-diodes .....                                   | 126 |

| 9.1    | The properties of pn-diodes .....                 | 126 |

| 9.1.1  | The operation of pn-diodes .....                  | 126 |

| 9.1.2  | Photodiodes .....                                 | 130 |

| 9.1.3  | Light-emitting diodes (LEDs) .....                | 132 |

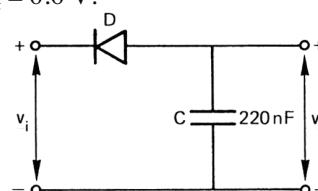

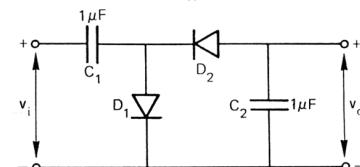

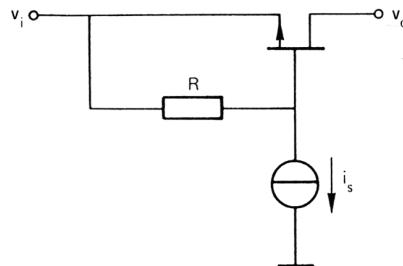

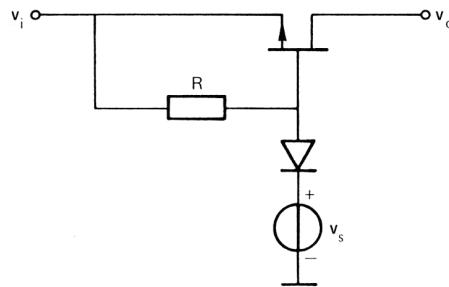

| 9.2    | Circuits with pn-diodes .....                     | 132 |

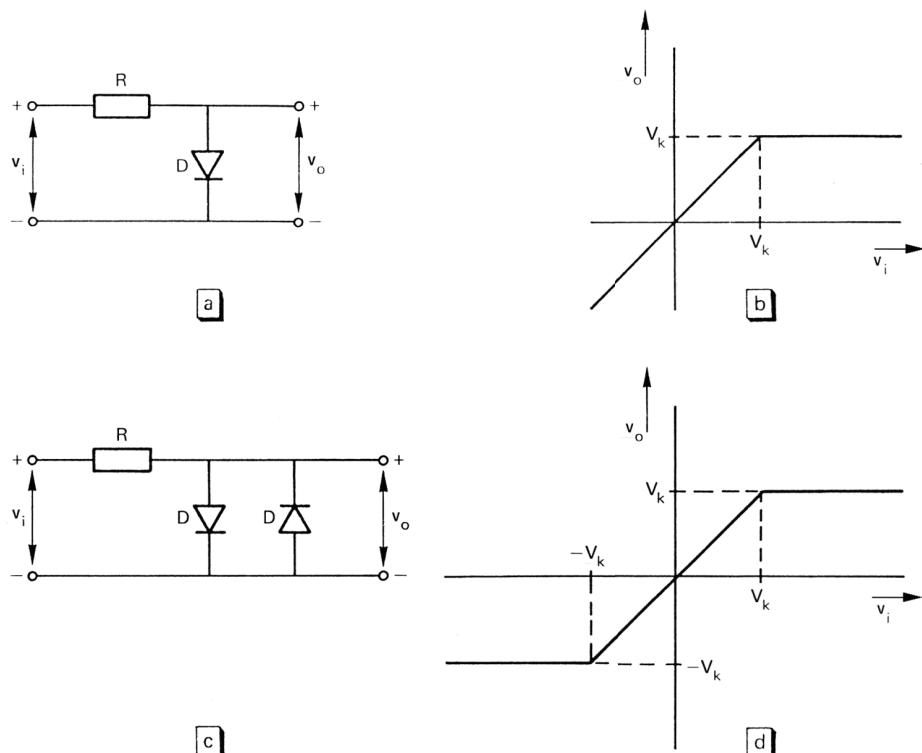

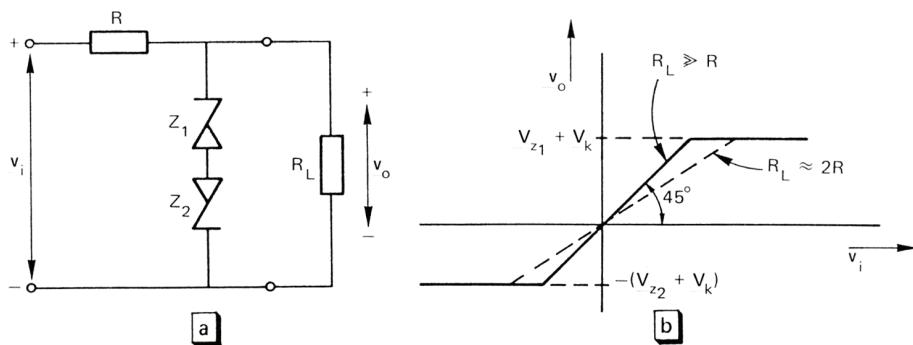

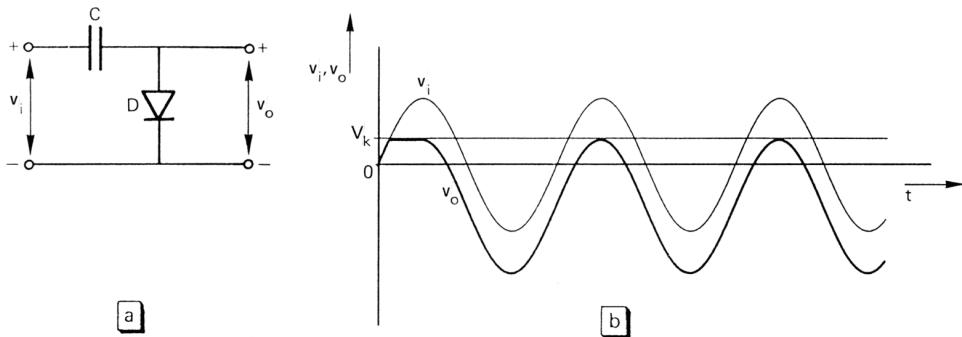

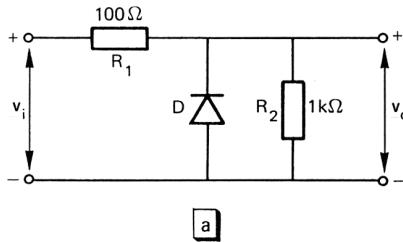

| 9.2.1  | Limiters .....                                    | 133 |

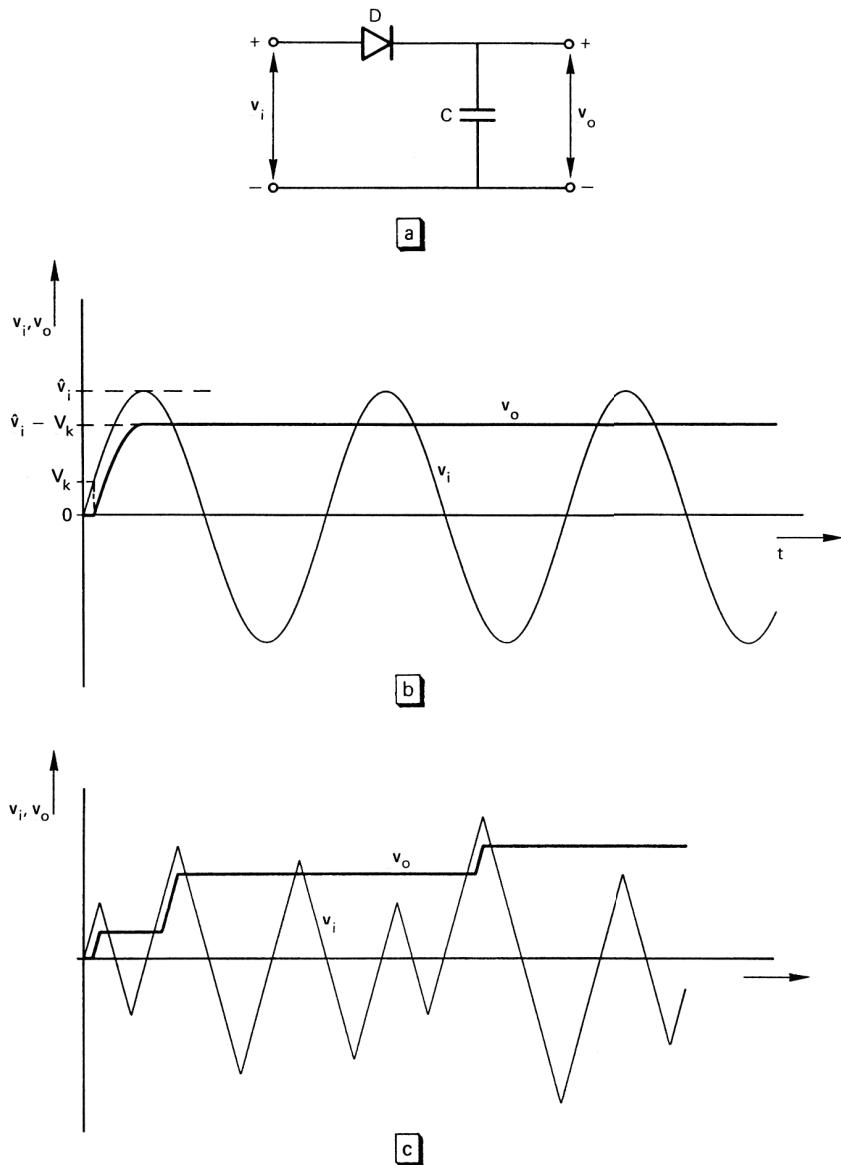

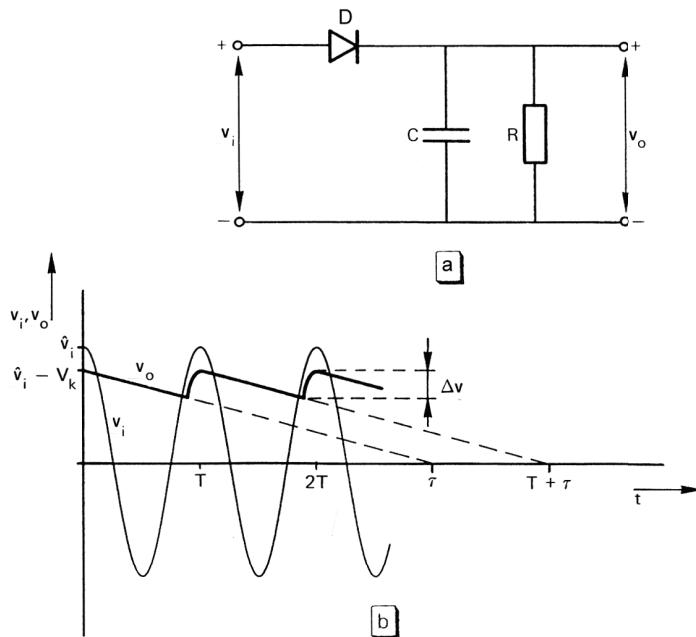

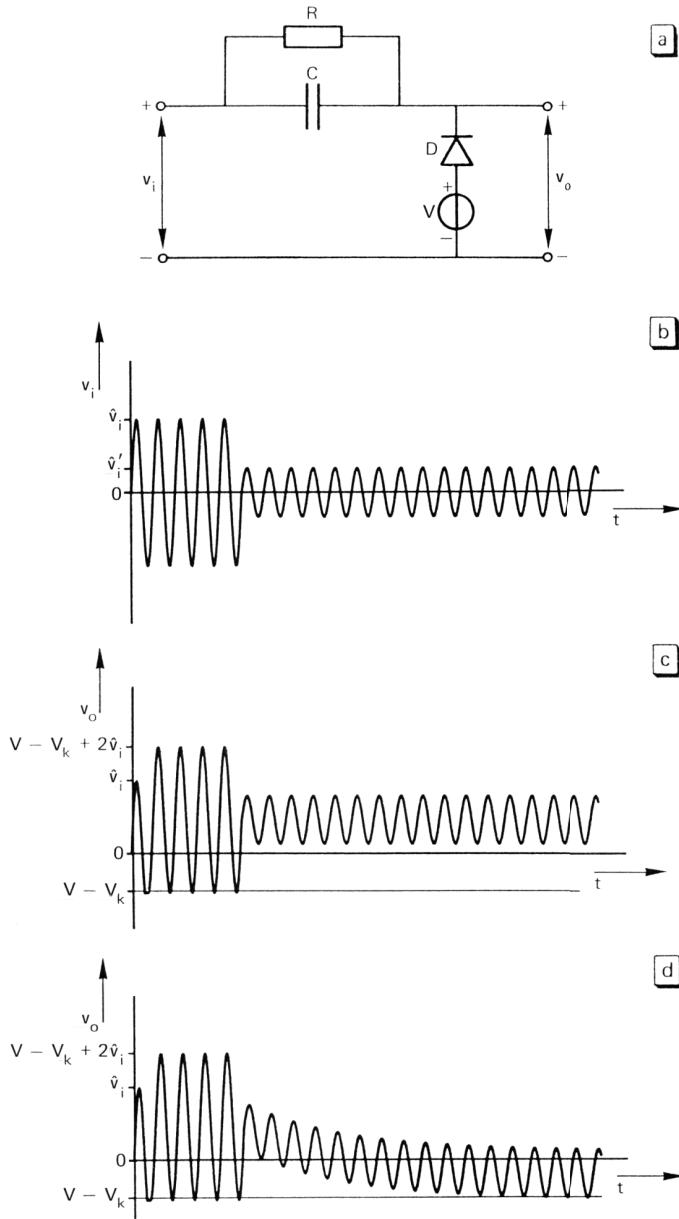

| 9.2.2  | Peak detectors .....                              | 134 |

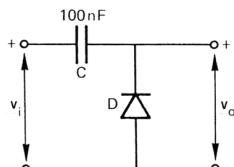

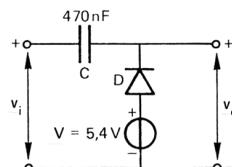

| 9.2.3  | Clamp circuits .....                              | 136 |

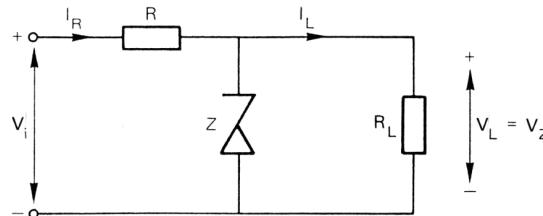

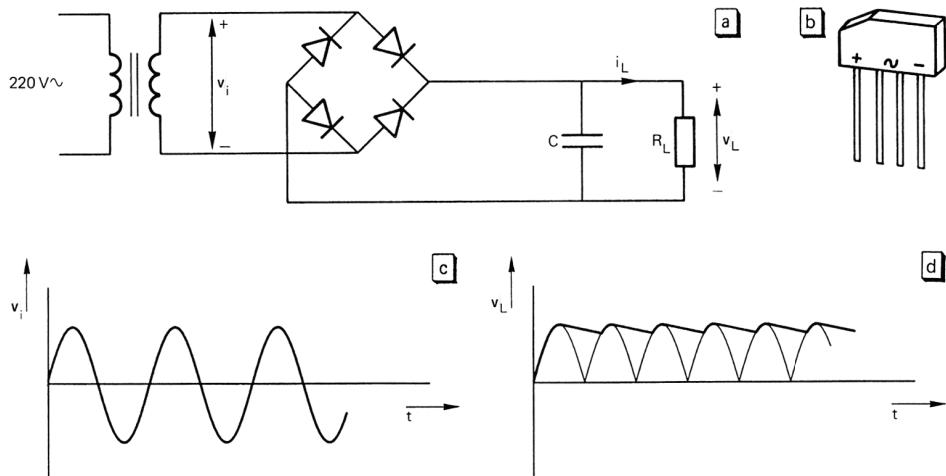

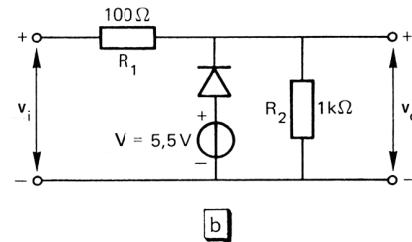

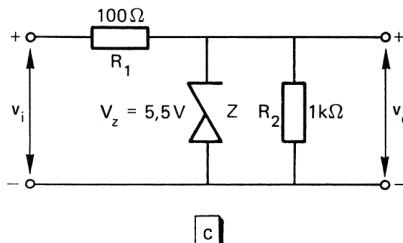

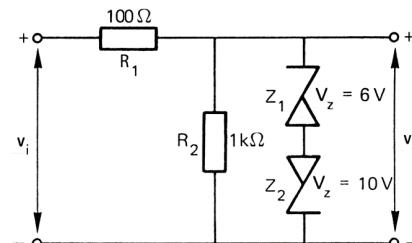

| 9.2.4  | DC voltages sources .....                         | 139 |

|        | SUMMARY .....                                     | 140 |

|        | EXERCISES .....                                   | 142 |

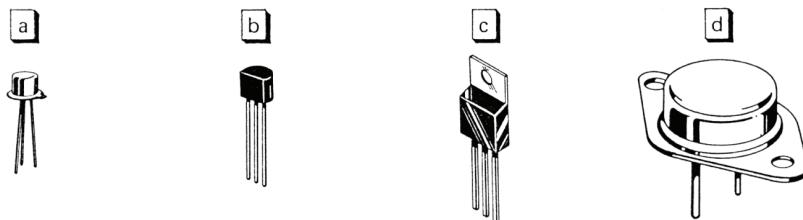

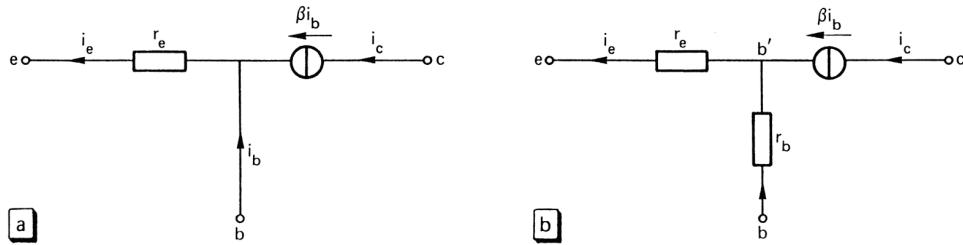

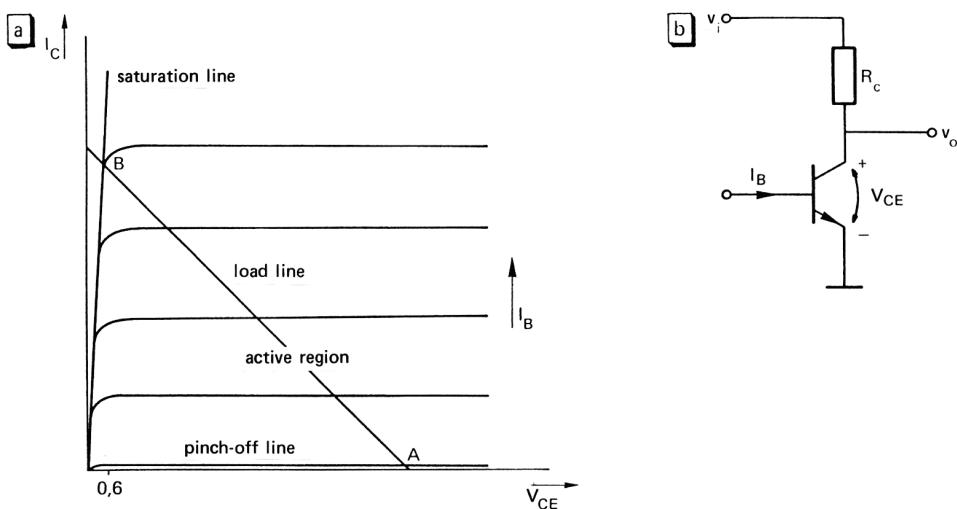

| 10     | Bipolar transistors .....                         | 144 |

| 10.1   | The properties of bipolar transistors .....       | 144 |

| 10.1.1 | Construction and characteristics .....            | 144 |

| 10.1.2 | Signal amplification .....                        | 146 |

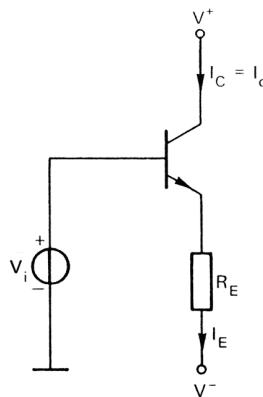

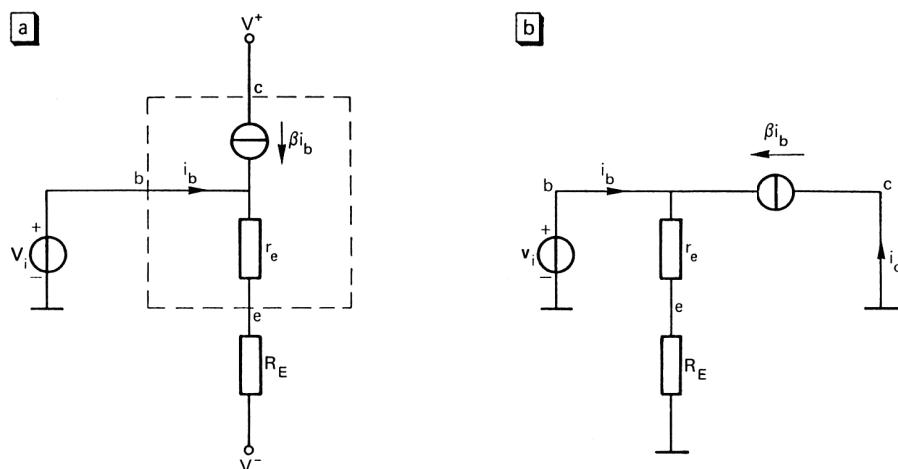

| 10.2   | Circuits with bipolar transistors .....           | 148 |

| 10.2.1 | Voltage-to-current converter .....                | 148 |

---

|                 |                                                                                 |            |

|-----------------|---------------------------------------------------------------------------------|------------|

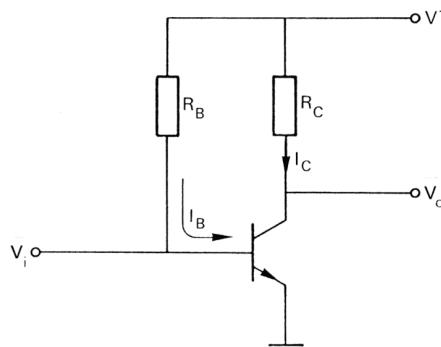

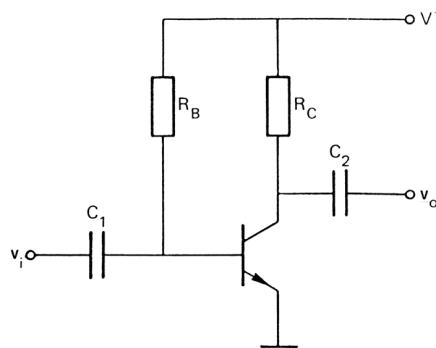

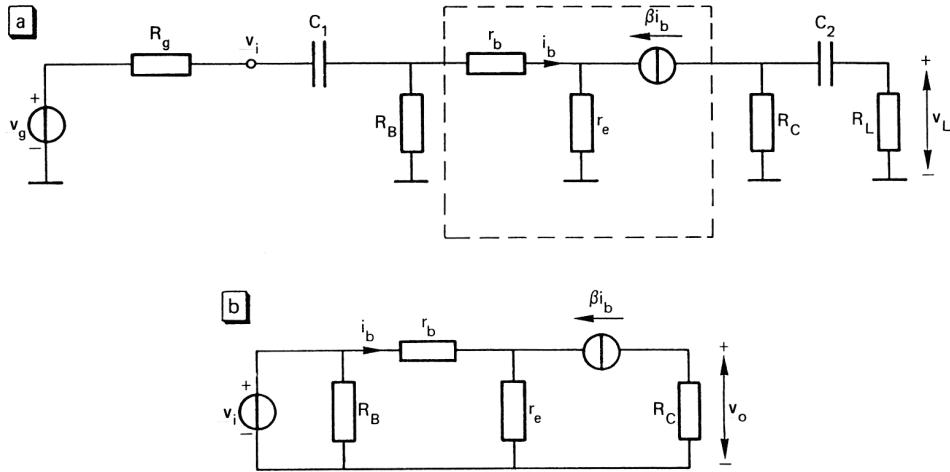

| 10.2.2          | The voltage amplifier stage with base-current bias.....                         | 150        |

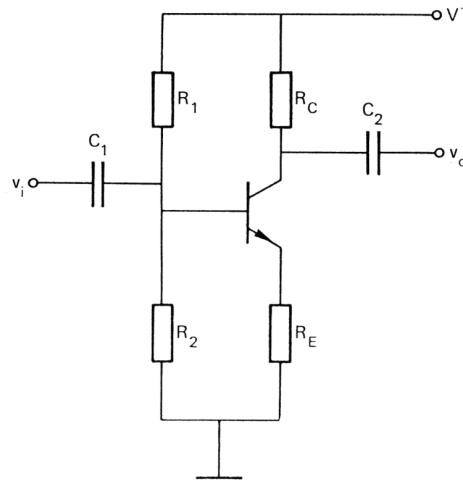

| 10.2.3          | The voltage amplifier stage with a base-voltage bias.....                       | 153        |

| 10.2.4          | The emitter follower .....                                                      | 156        |

| 10.2.5          | The differential amplifier stage.....                                           | 158        |

| SUMMARY .....   |                                                                                 | 160        |

| EXERCISES ..... |                                                                                 | 161        |

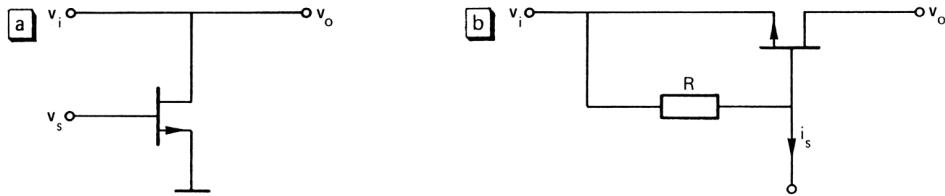

| <b>11</b>       | <b>Field-effect transistors.....</b>                                            | <b>164</b> |

| 11.1            | The properties of field-effect transistors .....                                | 164        |

| 11.1.1          | Junction field-effect transistors.....                                          | 164        |

| 11.1.2          | MOS field-effect transistors .....                                              | 168        |

| 11.2            | Circuits with field-effect transistors.....                                     | 170        |

| 11.2.1          | Voltage-to-current converter .....                                              | 171        |

| 11.2.2          | The voltage amplifier stage.....                                                | 171        |

| 11.2.3          | The source follower.....                                                        | 172        |

| 11.3            | SUMMARY .....                                                                   | 174        |

| EXERCISES ..... |                                                                                 | 175        |

| <b>12</b>       | <b>Operational amplifiers.....</b>                                              | <b>178</b> |

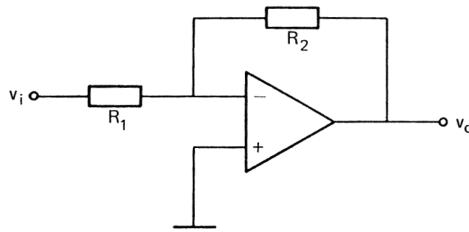

| 12.1            | Amplifier circuits with ideal operational amplifiers .....                      | 178        |

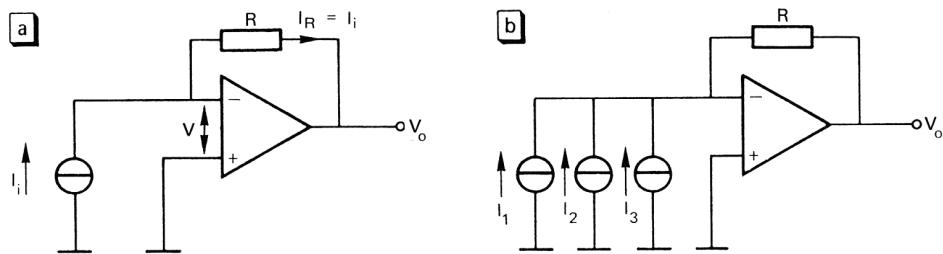

| 12.1.1          | Current-to-voltage converters.....                                              | 180        |

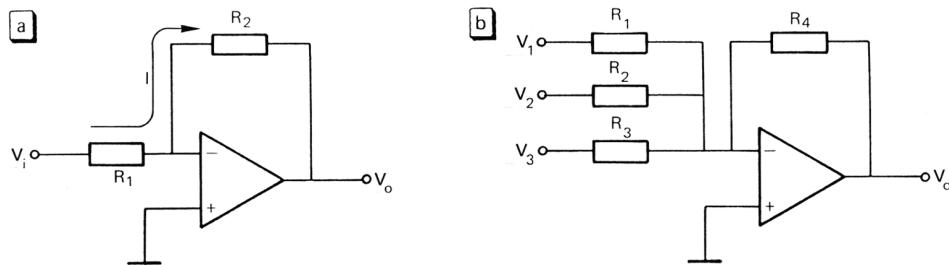

| 12.1.2          | Inverting voltage amplifiers .....                                              | 180        |

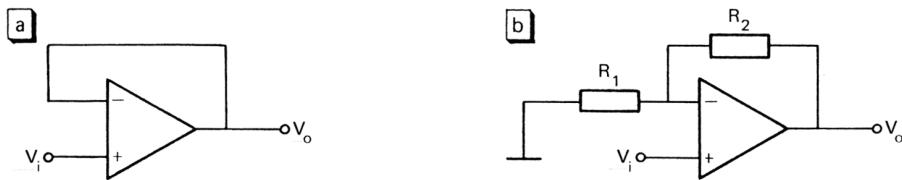

| 12.1.3          | Non-inverting voltage amplifiers .....                                          | 181        |

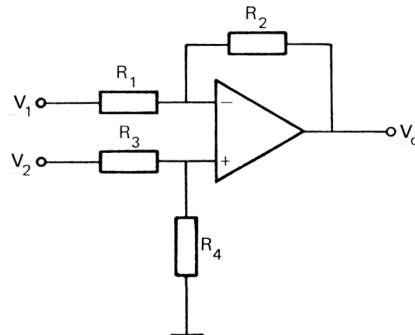

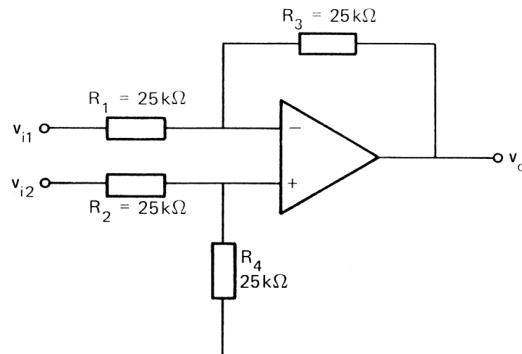

| 12.1.4          | Differential amplifiers .....                                                   | 182        |

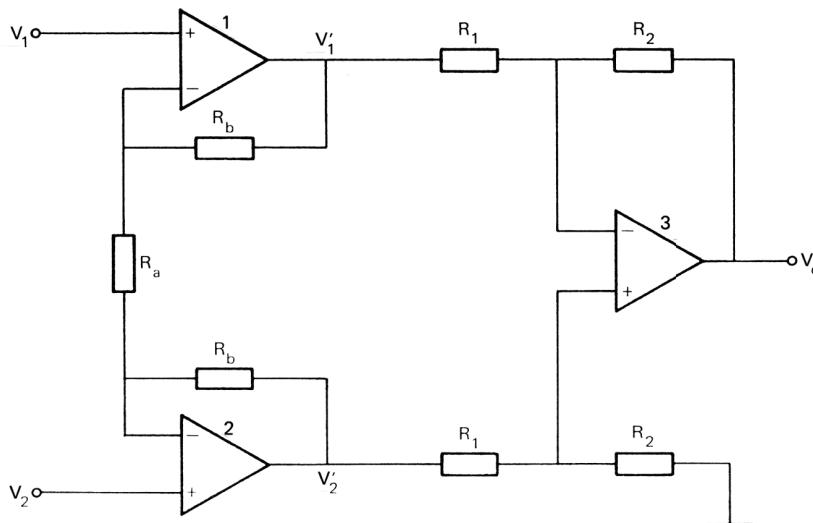

| 12.1.5          | Instrumentation amplifiers.....                                                 | 184        |

| 12.2            | Non-ideal operational amplifiers.....                                           | 185        |

| 12.2.1          | The specifications of operational amplifiers .....                              | 185        |

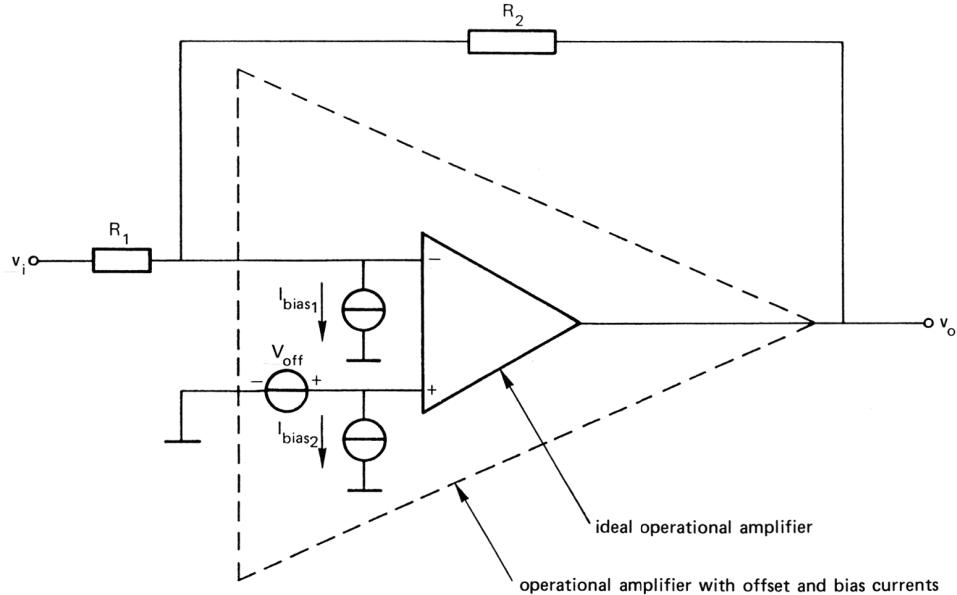

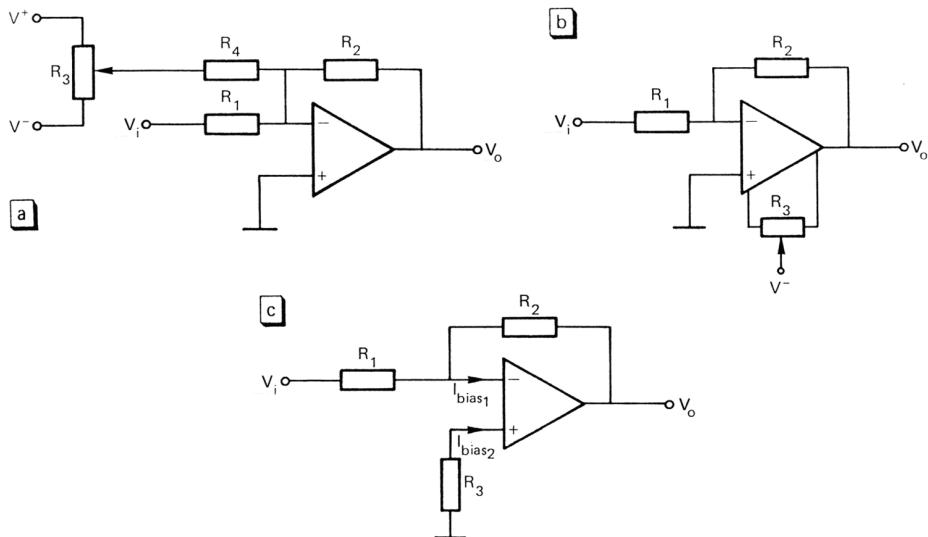

| 12.2.2          | Input offset voltage.....                                                       | 186        |

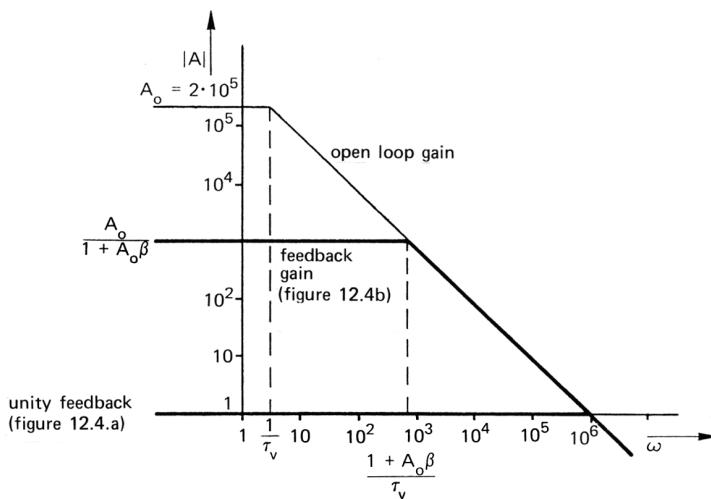

| 12.2.3          | Finite voltage gain.....                                                        | 189        |

| SUMMARY .....   |                                                                                 | 191        |

| EXERCISES ..... |                                                                                 | 192        |

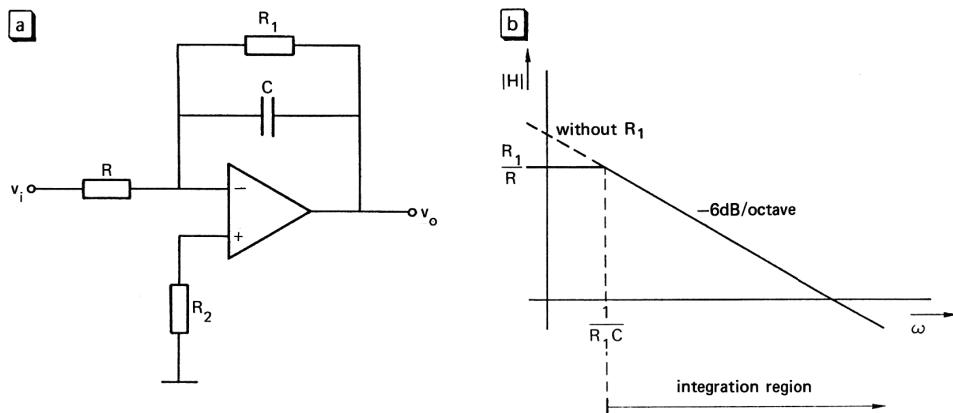

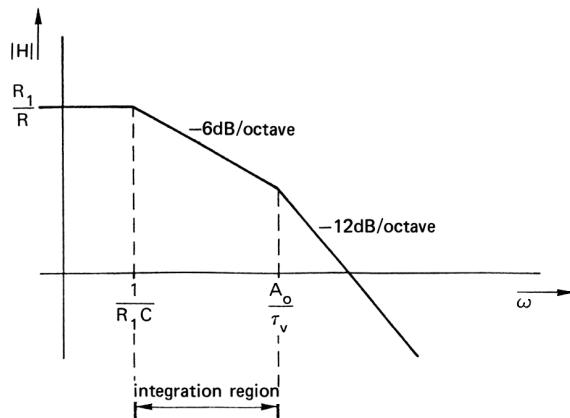

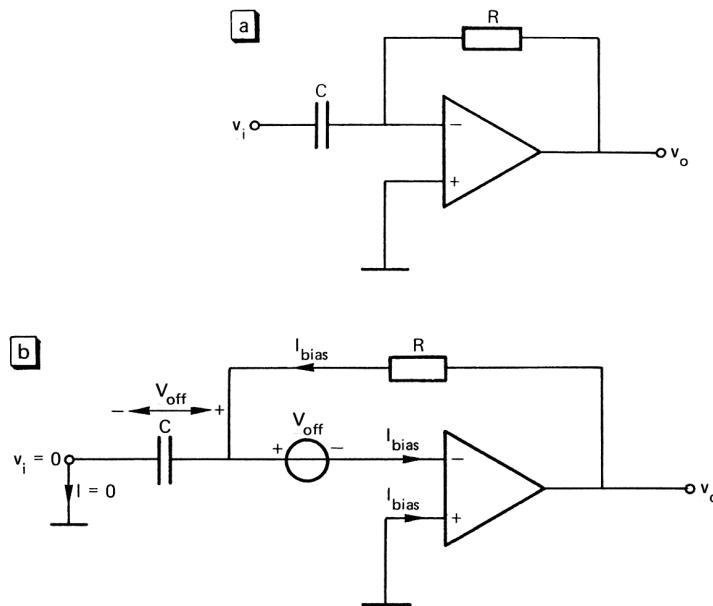

| <b>13</b>       | <b>Frequency selective transfer functions with operational amplifiers .....</b> | <b>194</b> |

| 13.1            | Circuits for time domain operations .....                                       | 194        |

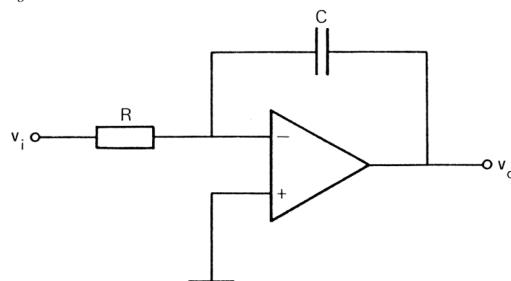

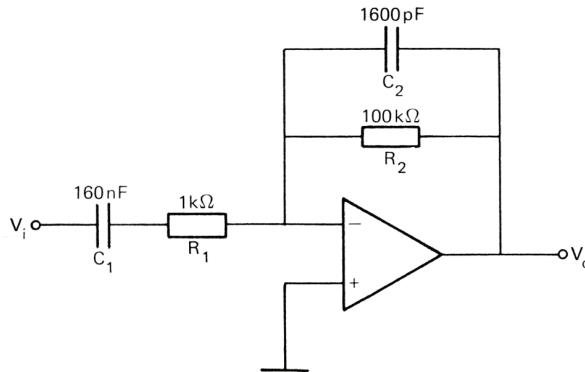

| 13.1.1          | The integrator .....                                                            | 194        |

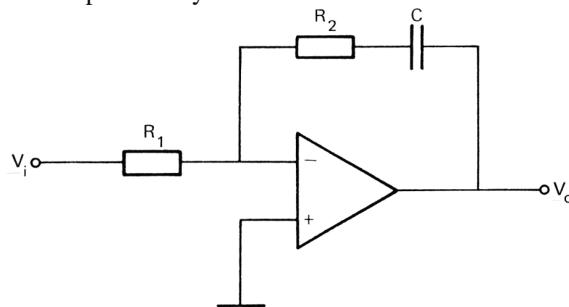

| 13.1.2          | Differentiator.....                                                             | 198        |

| 13.1.3          | Circuits with PD, PI and PID characteristics.....                               | 199        |

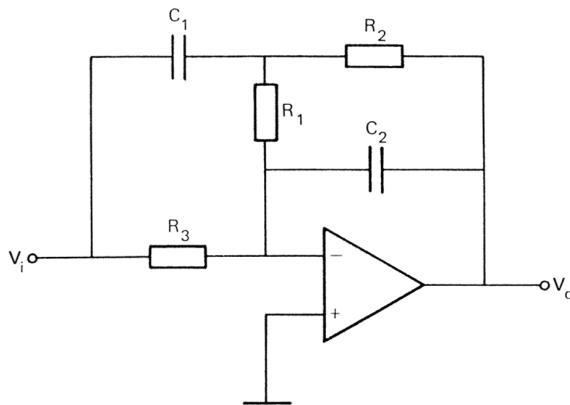

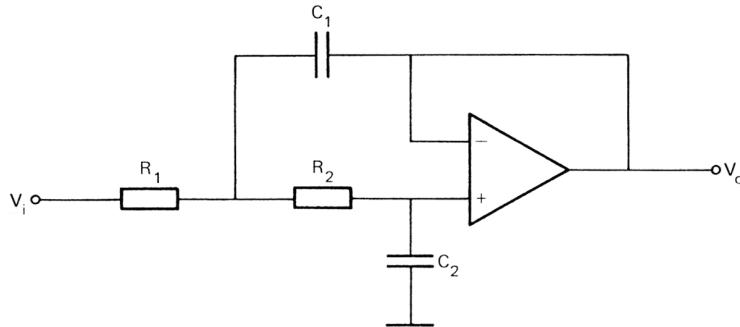

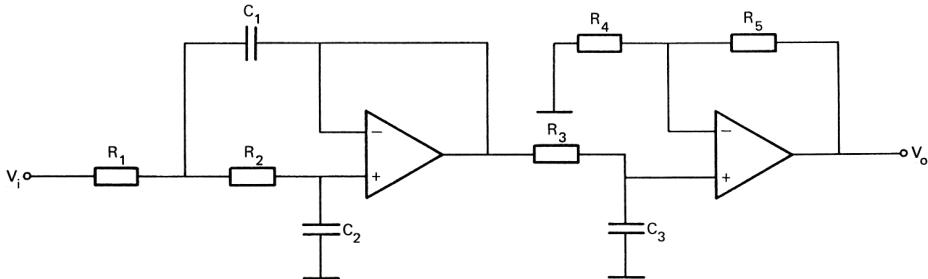

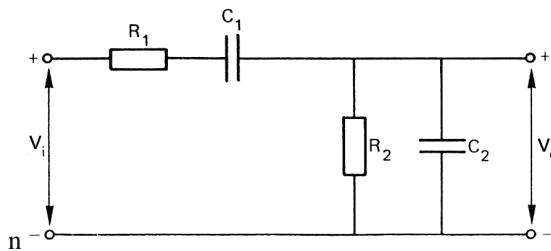

| 13.2            | Circuits with high frequency selectivity .....                                  | 201        |

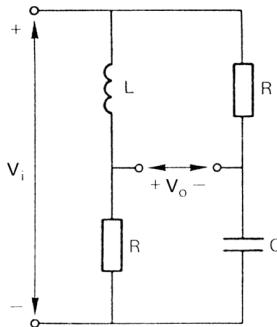

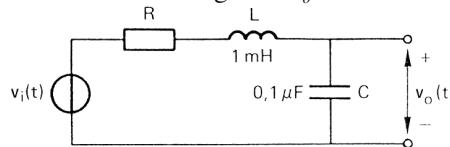

| 13.2.1          | Resonance filters .....                                                         | 201        |

| 13.2.2          | Active Butterworth filters.....                                                 | 206        |

| SUMMARY .....   |                                                                                 | 207        |

| EXERCISES ..... |                                                                                 | 208        |

| <b>14</b>       | <b>Nonlinear signal processing with operational amplifiers .....</b>            | <b>211</b> |

| 14.1            | Nonlinear transfer functions .....                                              | 211        |

| 14.1.1          | Voltage comparators.....                                                        | 211        |

| 14.1.2          | Schmitt-trigger .....                                                           | 213        |

| 14.1.3          | Voltage limiters .....                                                          | 215        |

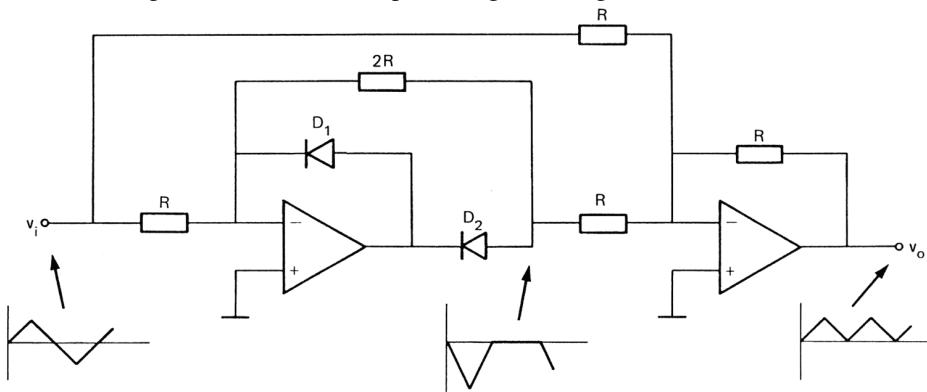

| 14.1.4          | Rectifiers .....                                                                | 217        |

| 14.2            | Nonlinear arithmetic operations .....                                           | 218        |

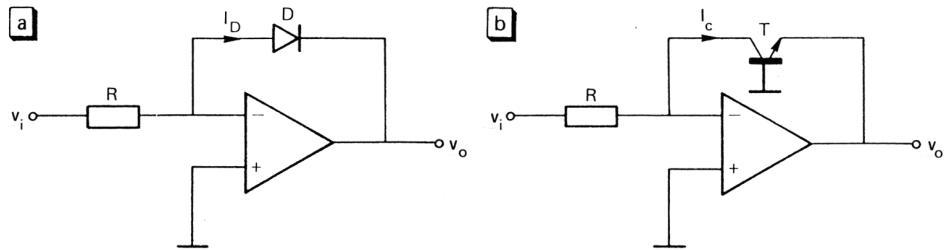

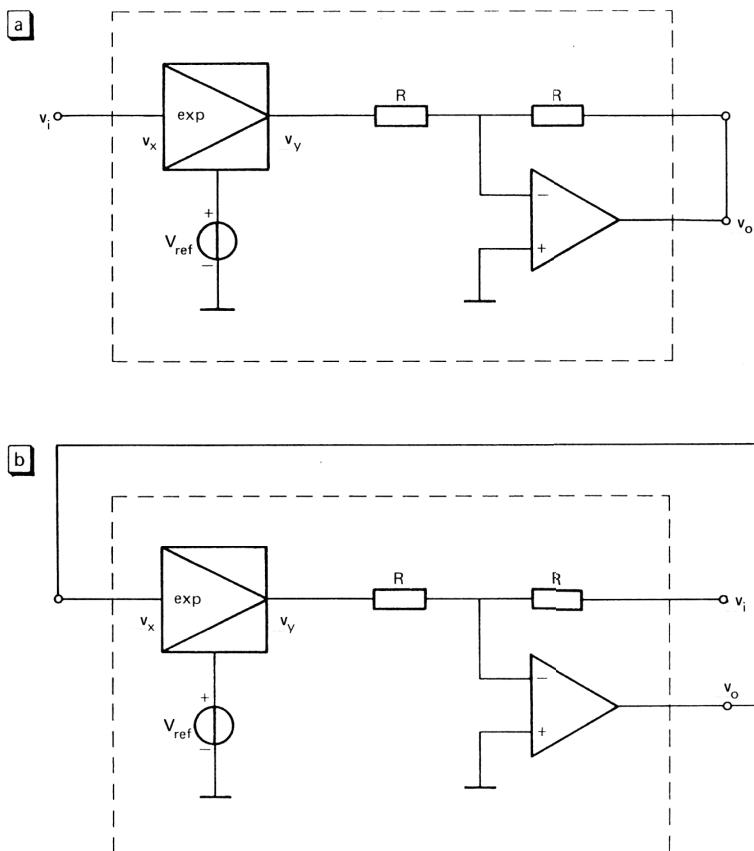

| 14.2.1          | Logarithmic converters .....                                                    | 218        |

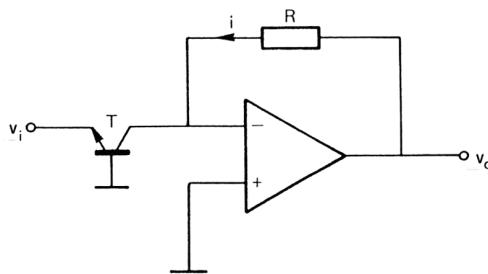

| 14.2.2          | Exponential converters.....                                                     | 220        |

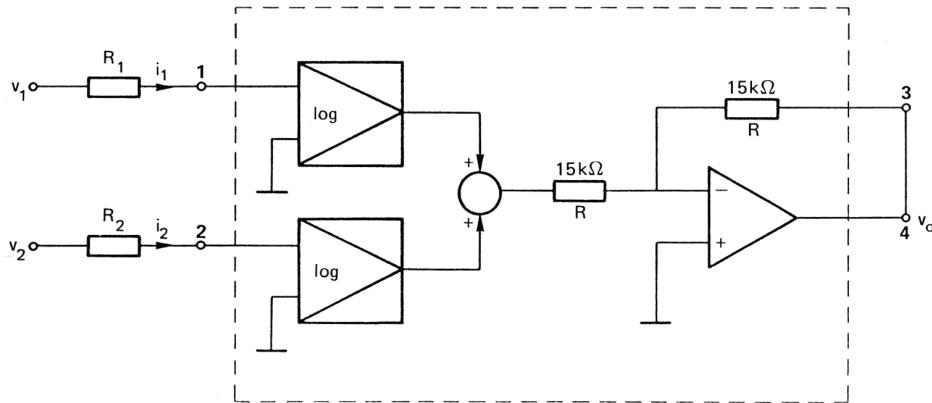

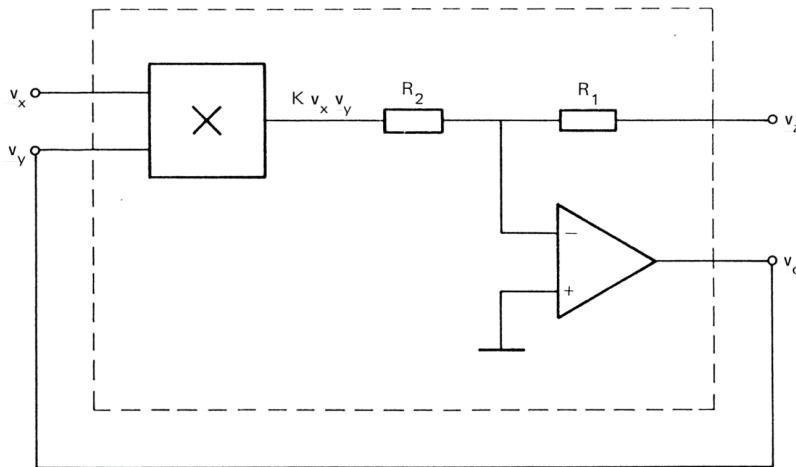

| 14.2.3          | Multipliers .....                                                               | 221        |

|                                                                               |            |

|-------------------------------------------------------------------------------|------------|

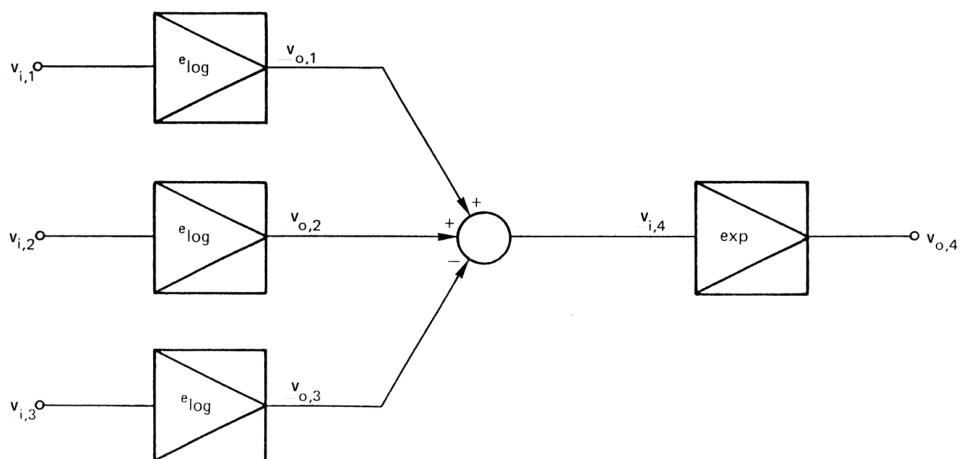

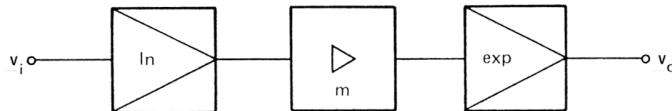

| 14.2.4 Other arithmetic operations .....                                      | 223        |

| 14.2.5 A piecewise linear approximation of arbitrary transfer functions ..... | 225        |

| SUMMARY .....                                                                 | 227        |

| EXERCISES .....                                                               | 228        |

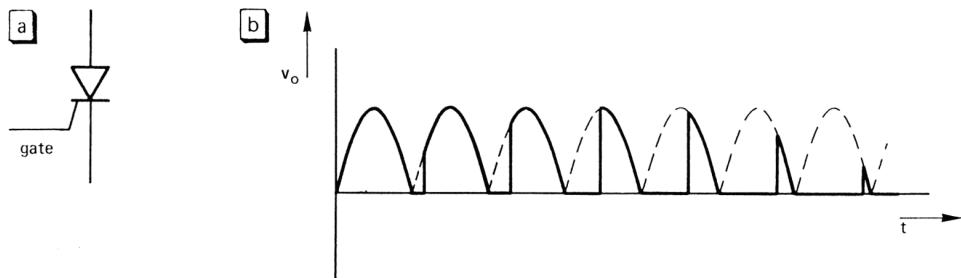

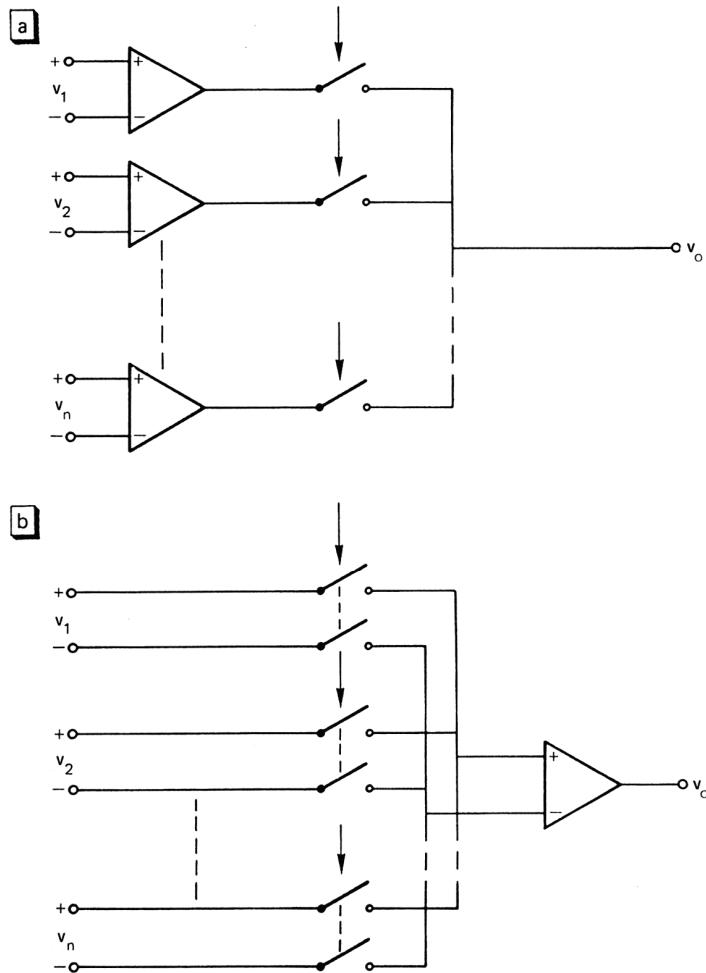

| <b>15 Electronic switching circuits .....</b>                                 | <b>231</b> |

| 15.1 Electronic switches .....                                                | 231        |

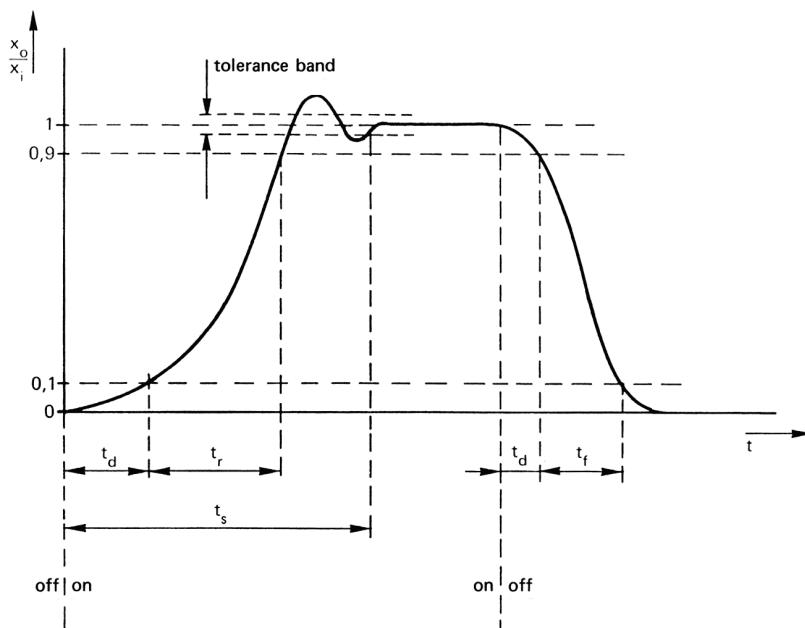

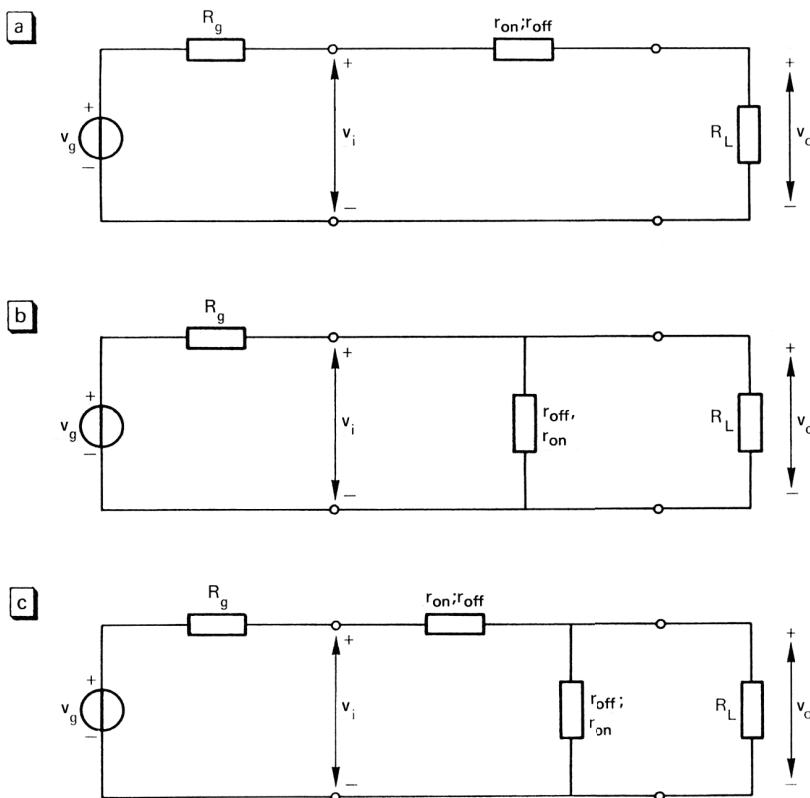

| 15.1.1 The properties of electronic switches .....                            | 231        |

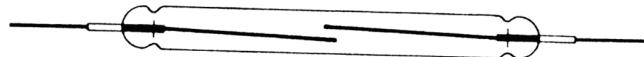

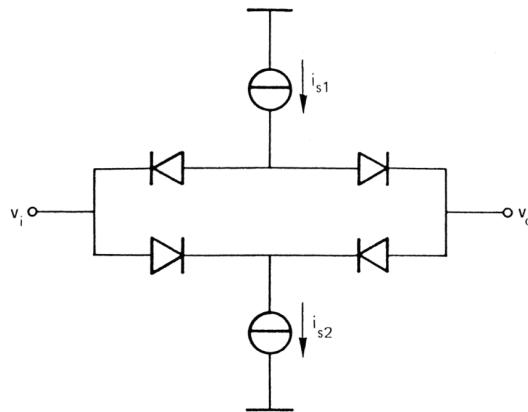

| 15.1.2 Components as electronic switches .....                                | 235        |

| 15.2 Circuits with electronic switches .....                                  | 239        |

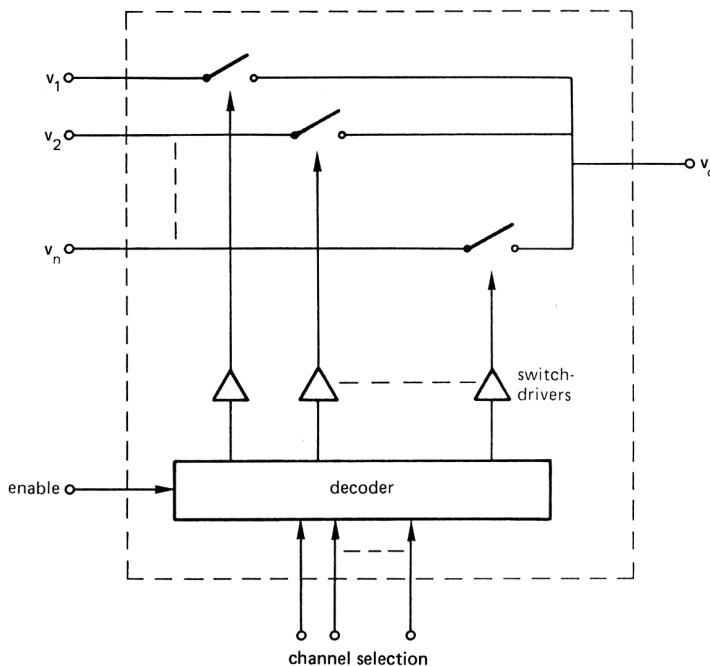

| 15.2.1 Time multiplexers .....                                                | 239        |

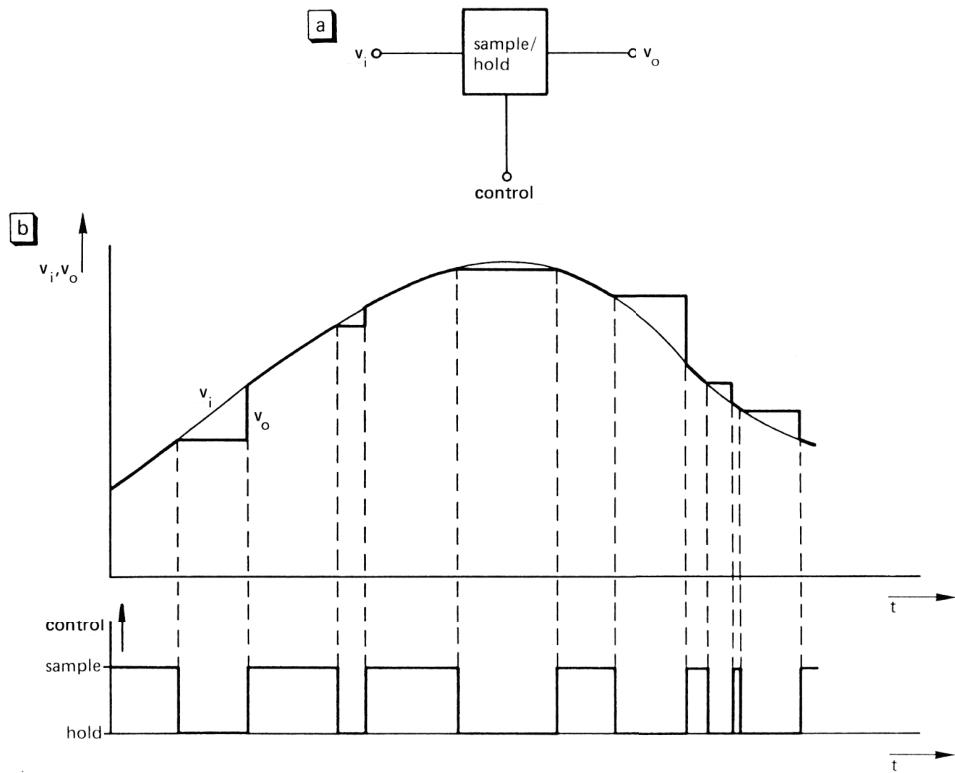

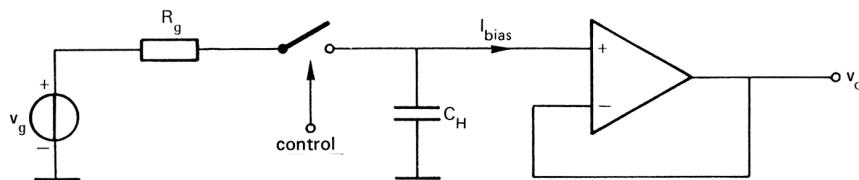

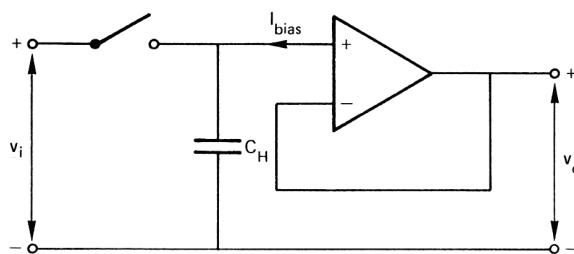

| 15.2.2 Sample-hold circuits .....                                             | 241        |

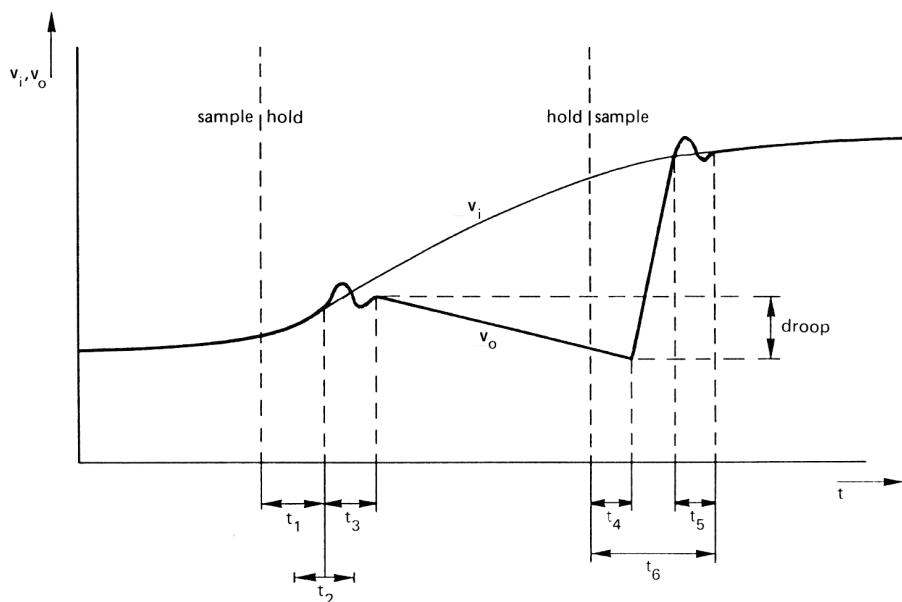

| 15.2.3 Transient errors .....                                                 | 244        |

| SUMMARY .....                                                                 | 248        |

| EXERCISES .....                                                               | 248        |

| <b>16 Signal generation .....</b>                                             | <b>252</b> |

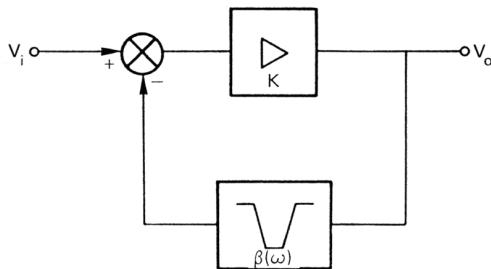

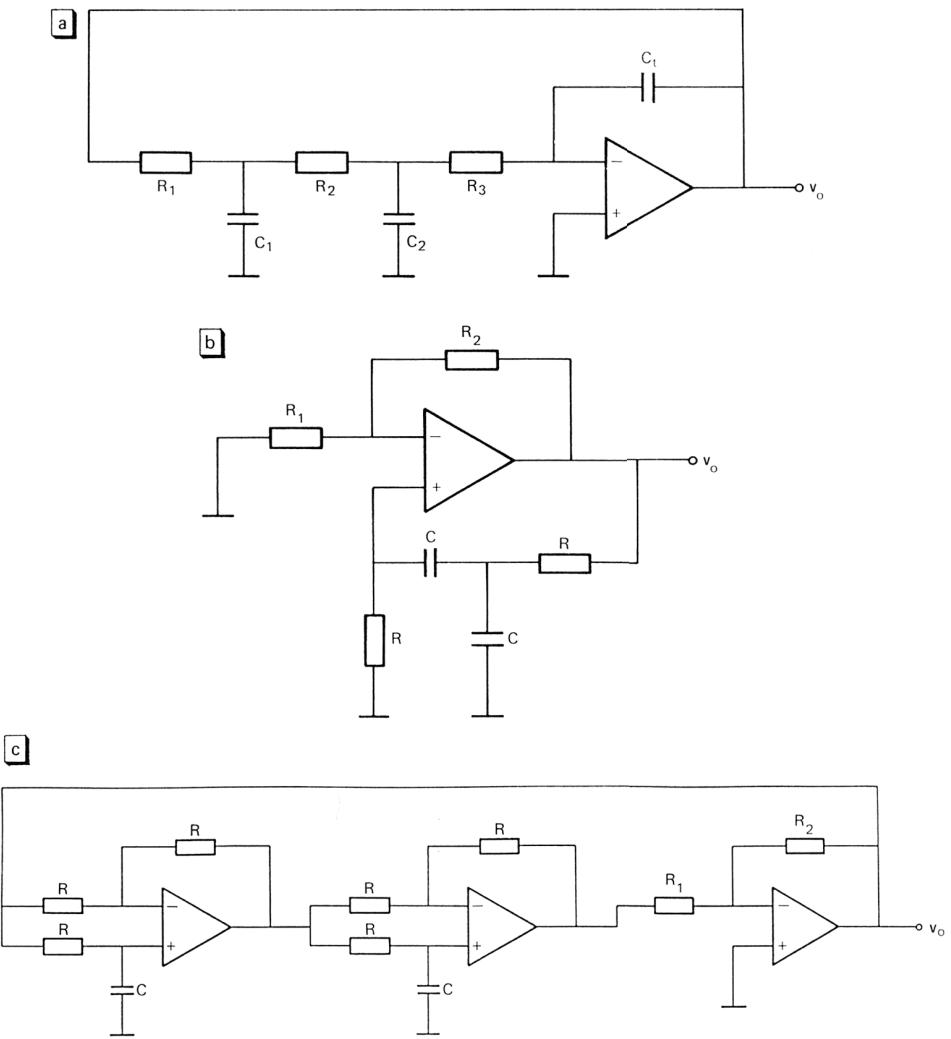

| 16.1 Sine wave oscillators .....                                              | 252        |

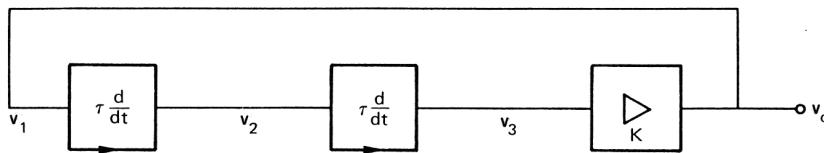

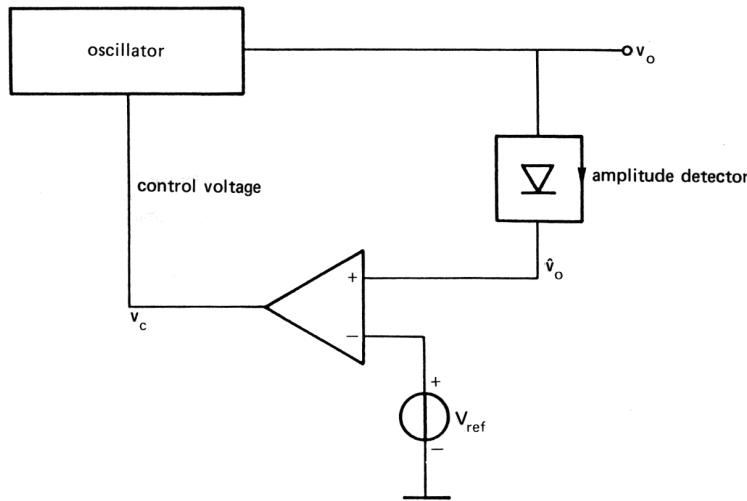

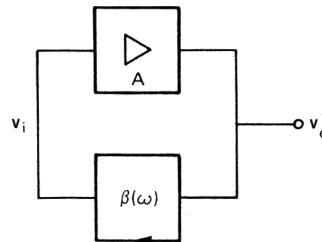

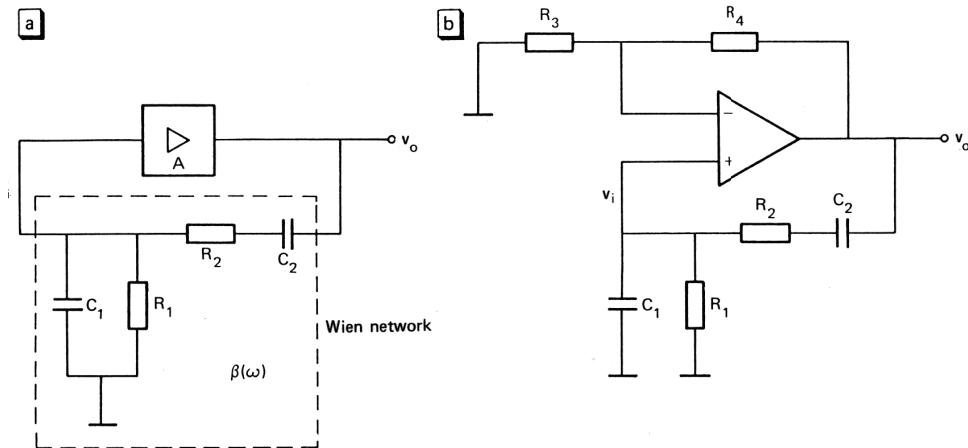

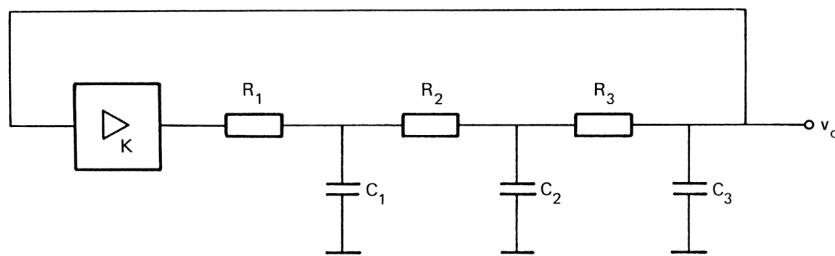

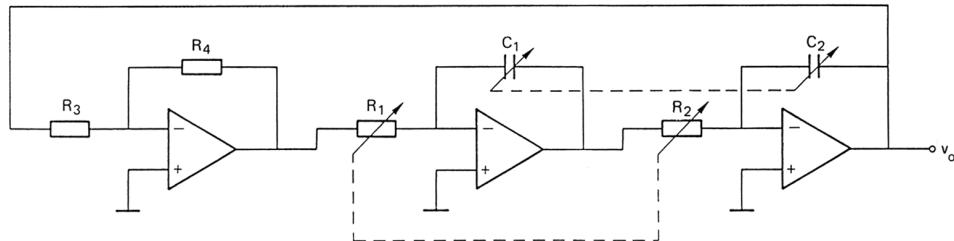

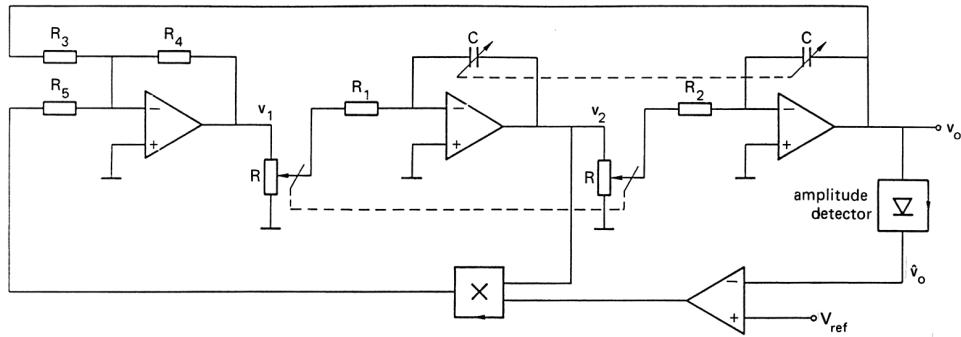

| 16.1.1 Harmonic oscillators .....                                             | 252        |

| 16.1.2 Harmonic oscillator circuits .....                                     | 255        |

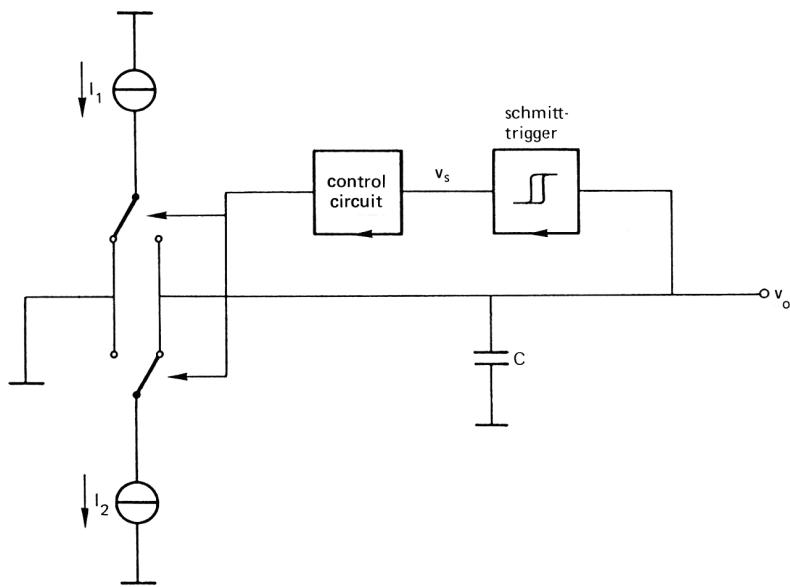

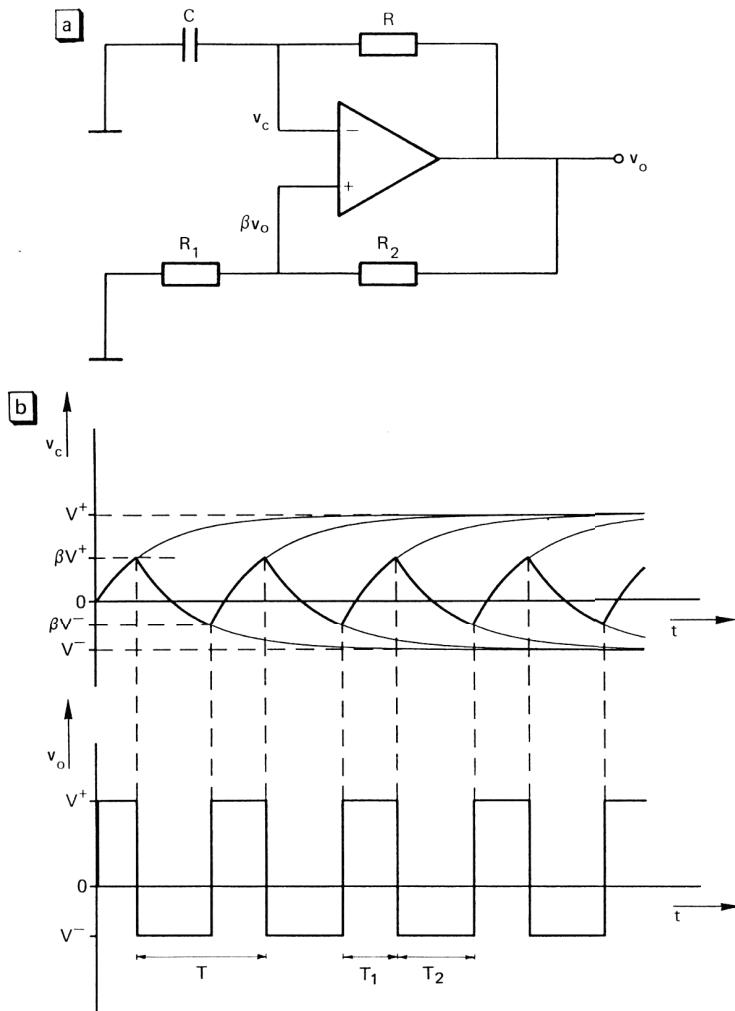

| 16.2 Voltage generators .....                                                 | 258        |

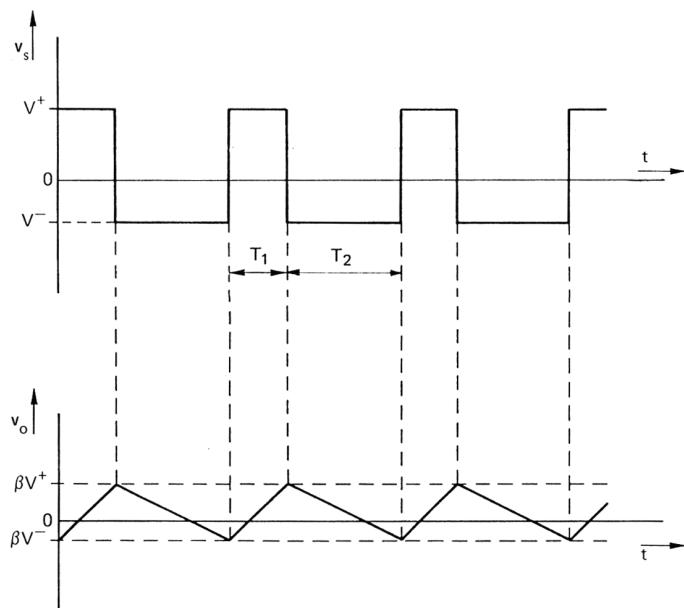

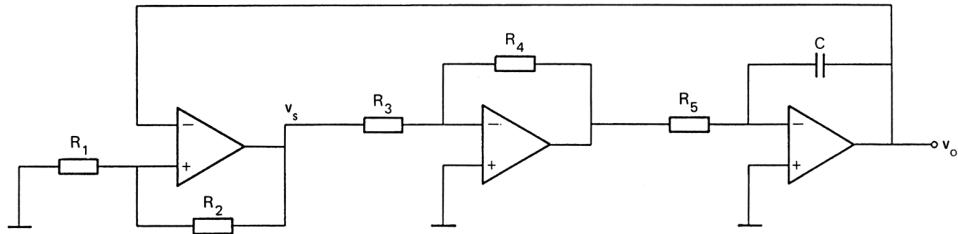

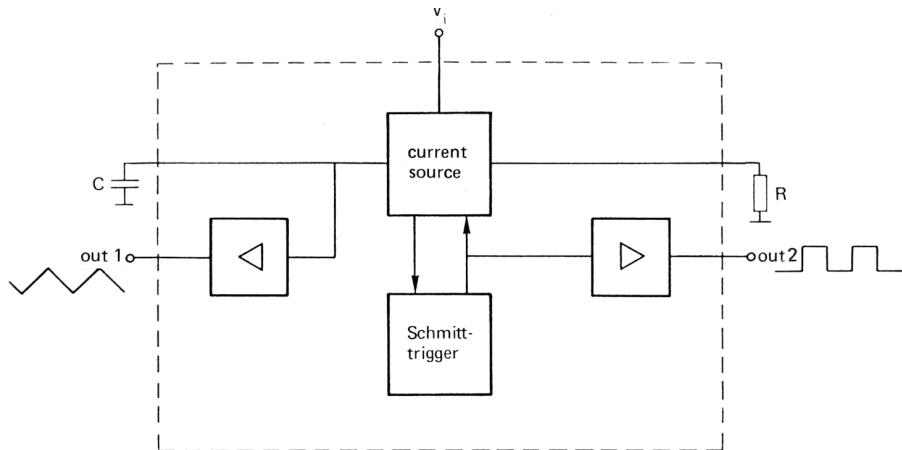

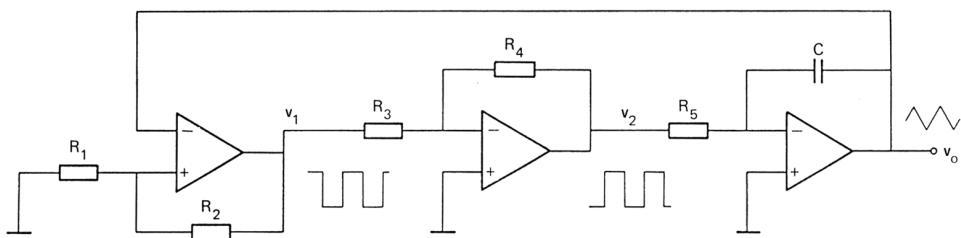

| 16.2.1 Triangle voltage generators .....                                      | 258        |

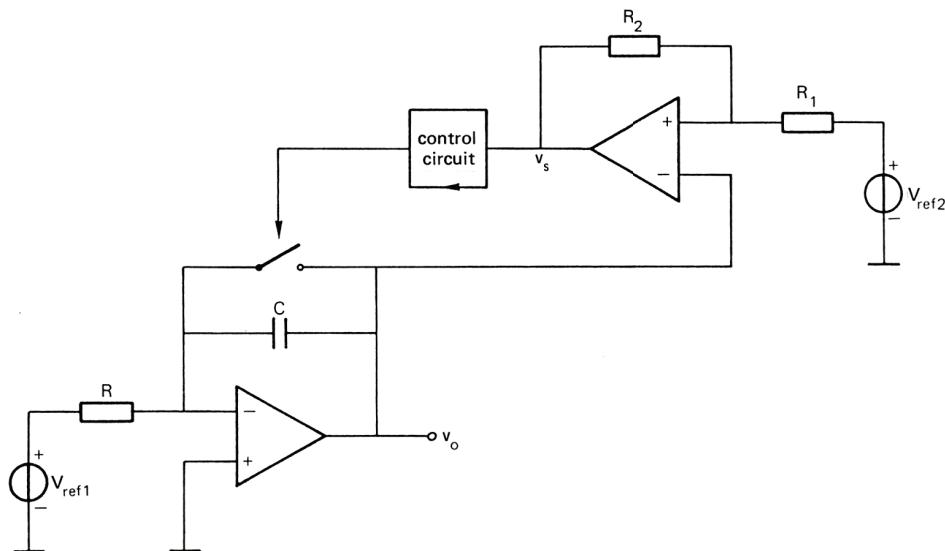

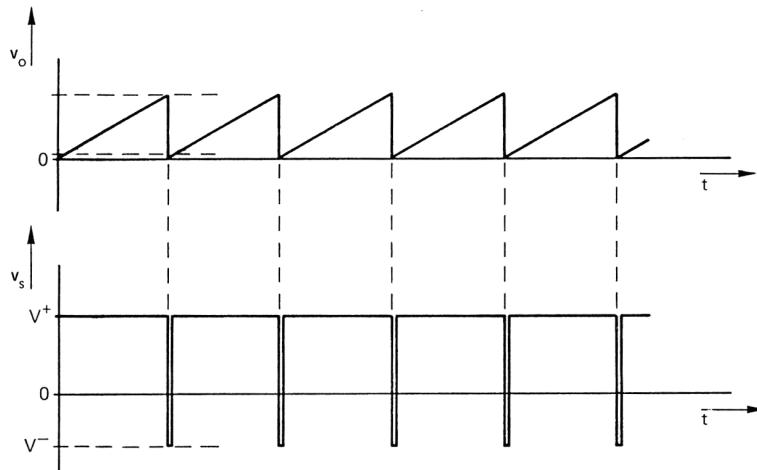

| 16.2.2 The ramp generator .....                                               | 260        |

| 16.2.3 Square wave and pulse generators .....                                 | 262        |

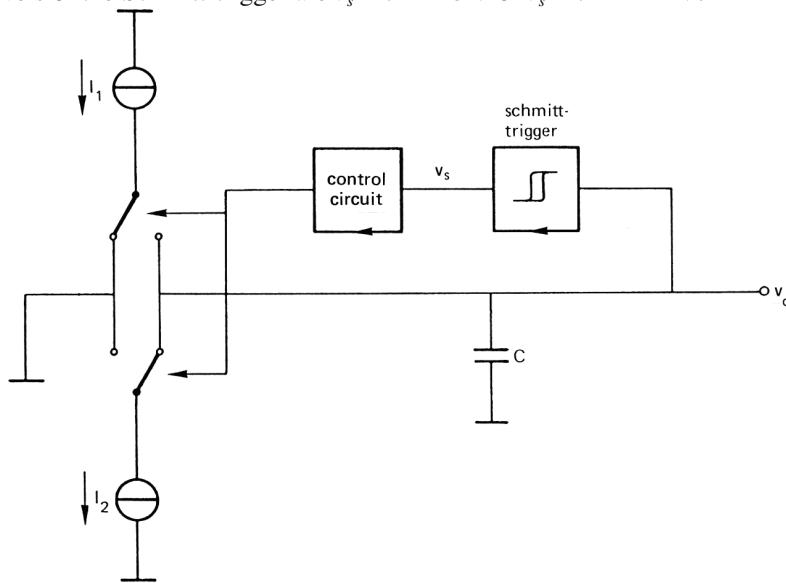

| 16.2.4 Voltage-controlled oscillators .....                                   | 263        |

| SUMMARY .....                                                                 | 264        |

| EXERCISES .....                                                               | 265        |

| <b>17 Modulation and demodulation .....</b>                                   | <b>268</b> |

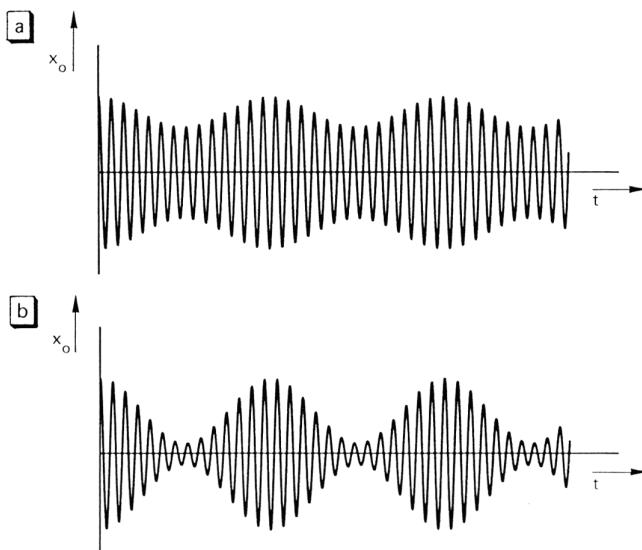

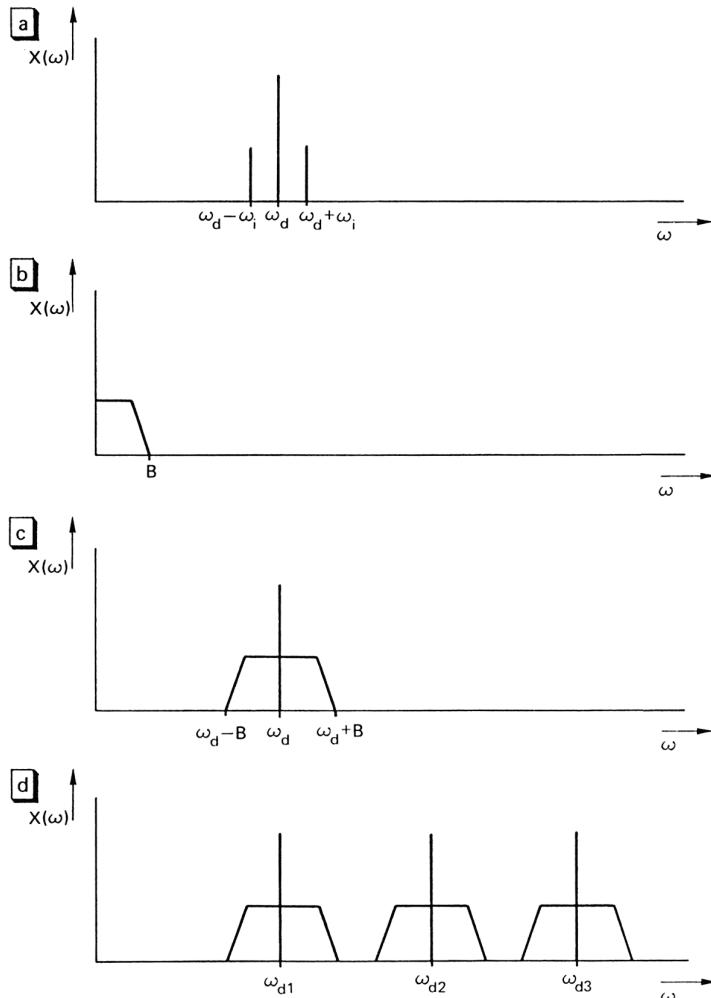

| 17.1 Amplitude modulation and demodulation .....                              | 270        |

| 17.1.1 Theoretical background .....                                           | 270        |

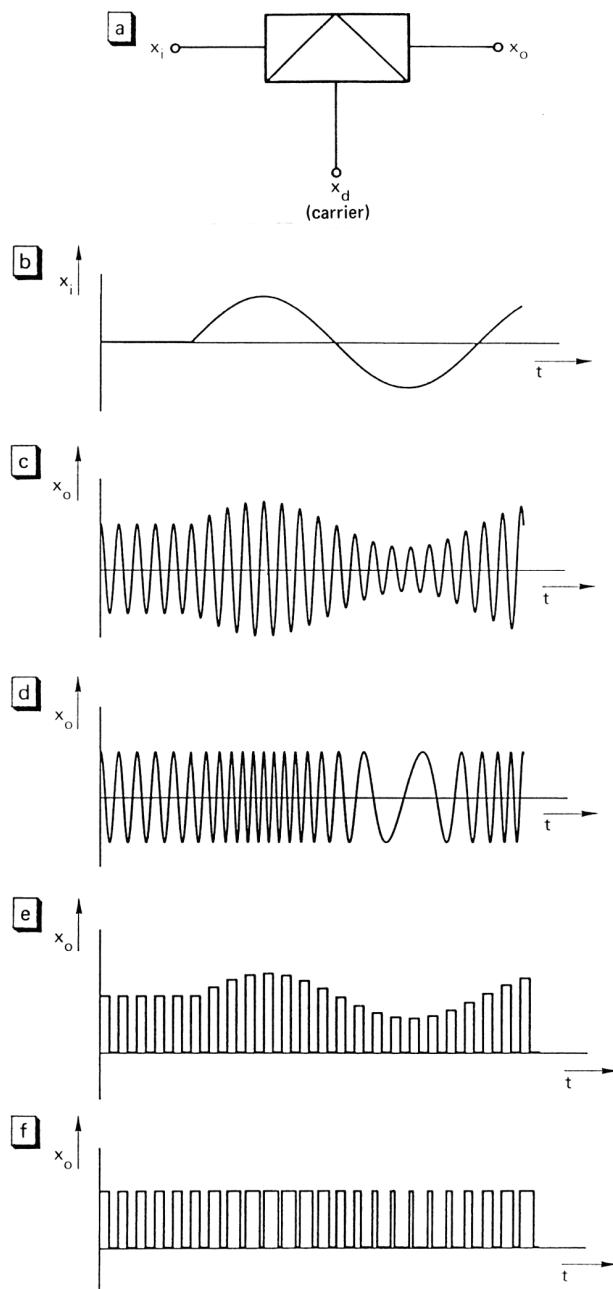

| 17.1.2 Amplitude modulation methods .....                                     | 272        |

| 17.1.3 Demodulation methods .....                                             | 276        |

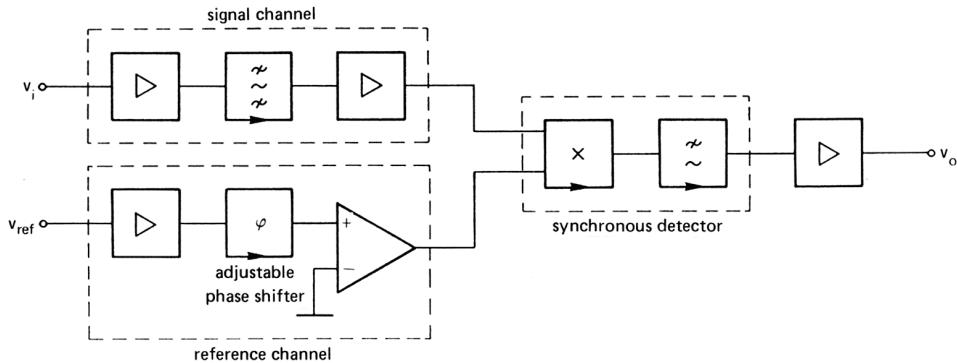

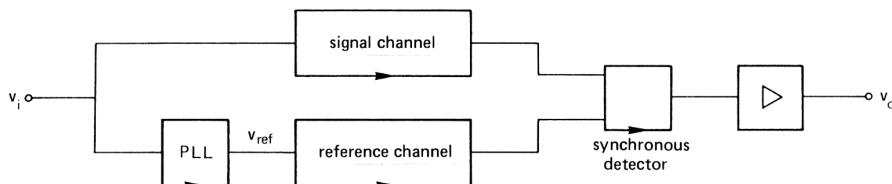

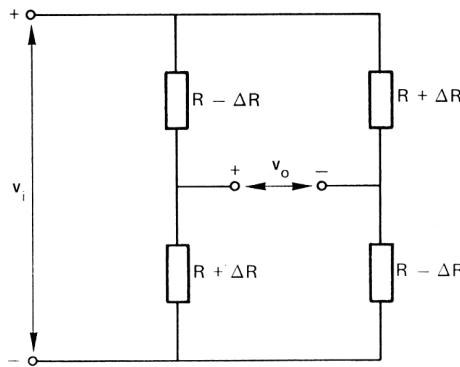

| 17.2 Systems based on synchronous detection .....                             | 278        |

| 17.2.1 The phase-locked loop .....                                            | 279        |

| 17.2.2 Lock-in amplifiers .....                                               | 280        |

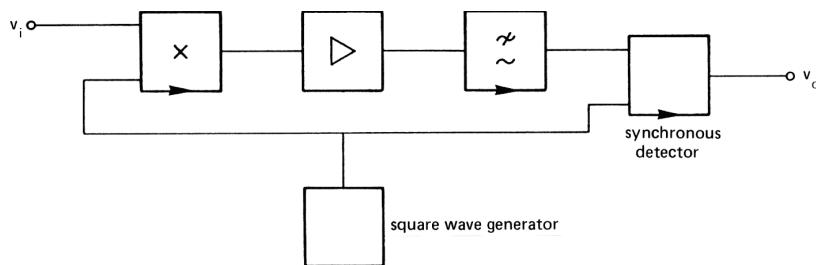

| 17.2.3 Chopper amplifiers .....                                               | 281        |

| SUMMARY .....                                                                 | 282        |

| EXERCISES .....                                                               | 283        |

| <b>18 Digital-to-analogue and analogue-to-digital conversion .....</b>        | <b>286</b> |

| 18.1 Parallel converters .....                                                | 286        |

| 18.1.1 Binary signals and codes .....                                         | 286        |

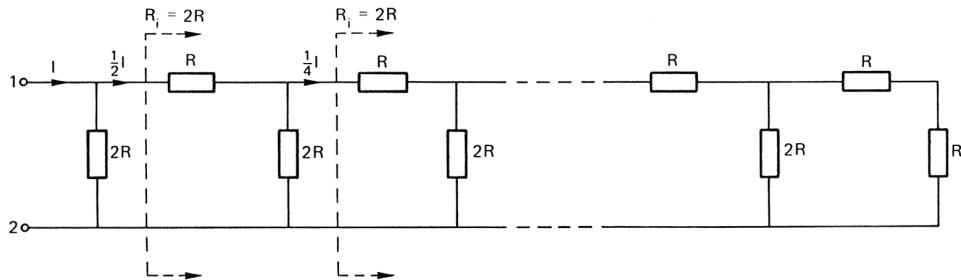

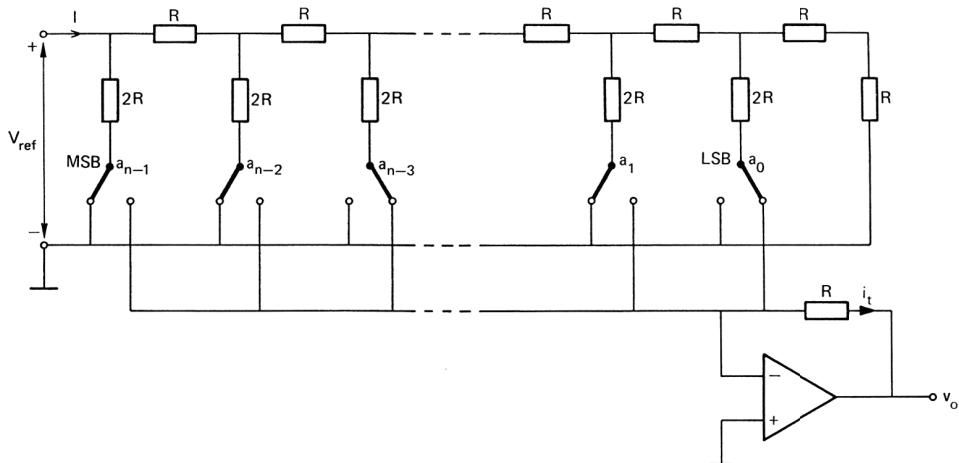

| 18.1.2 Parallel DA-converters .....                                           | 289        |

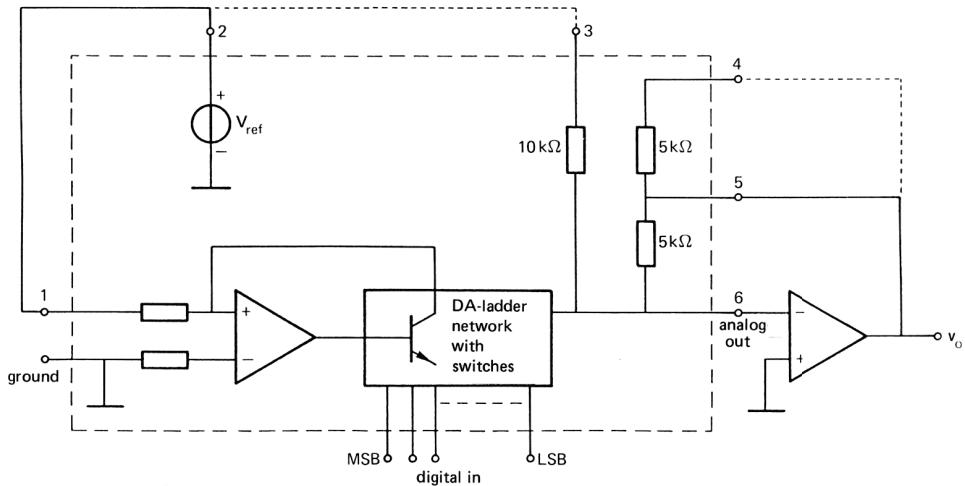

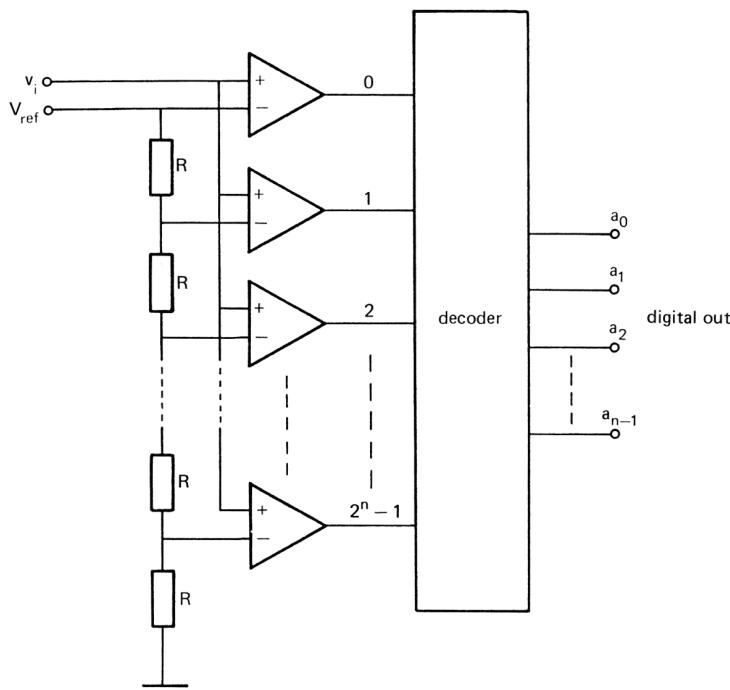

| 18.1.3 Parallel AD-converters .....                                           | 293        |

| 18.2 Special converters .....                                                 | 296        |

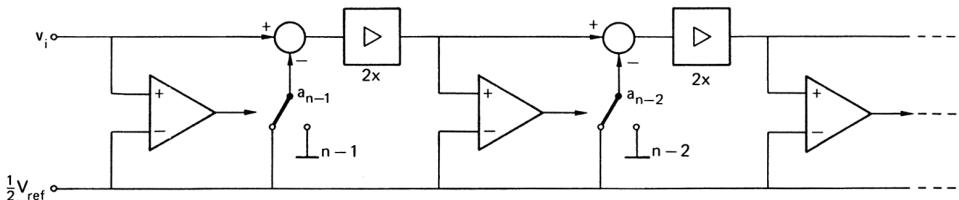

| 18.2.1 The serial DA-converter .....                                          | 297        |

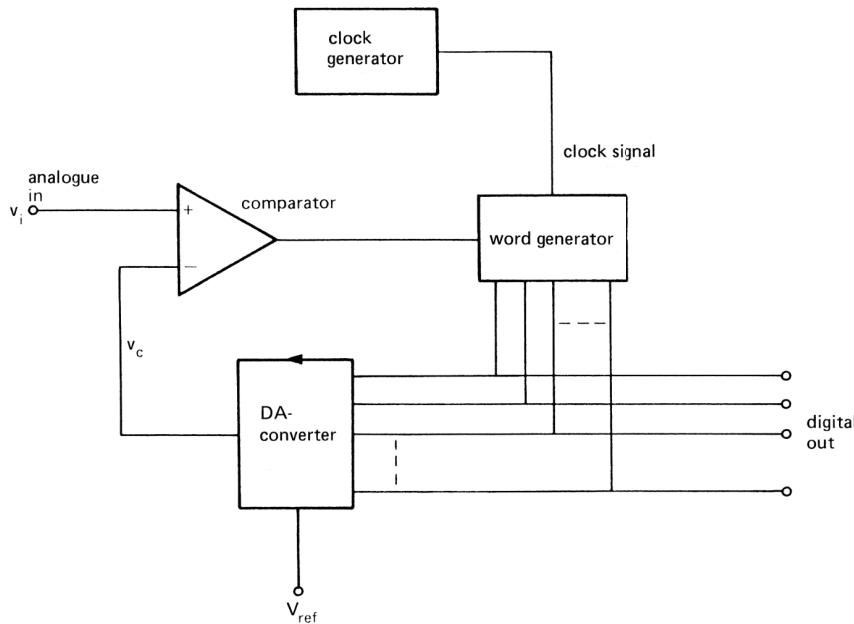

| 18.2.2 The direct AD converter .....                                          | 298        |

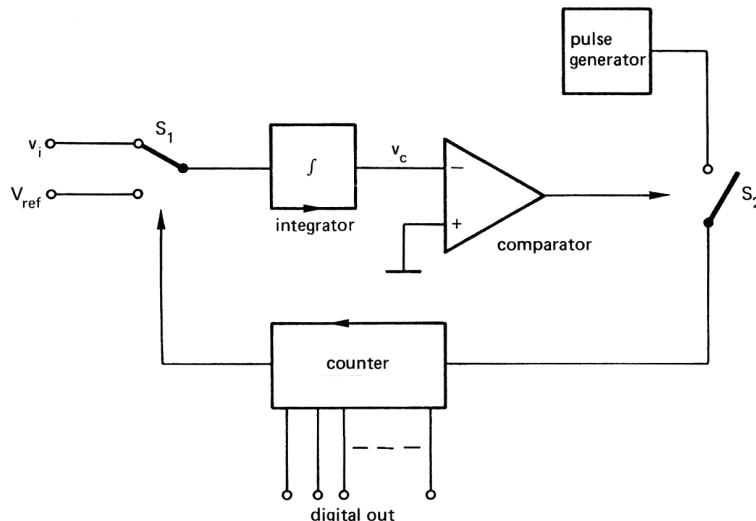

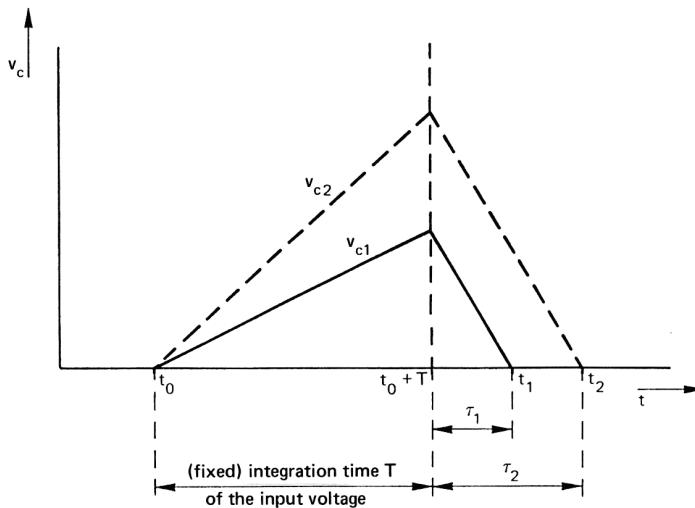

| 18.2.3 Integrating AD-converters .....                                        | 299        |

| SUMMARY .....                                                                 | 302        |

| EXERCISES .....                                                               | 303        |

| <b>19 Digital electronics .....</b>                                           | <b>305</b> |

| 19.1 Digital components .....                                                 | 305        |

---

|                                                                   |            |

|-------------------------------------------------------------------|------------|

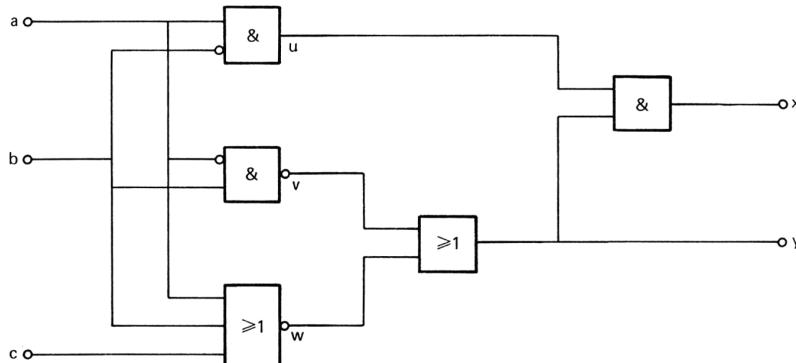

| 19.1.1 Boolean algebra.....                                       | 305        |

| 19.1.2 Digital components for combinatory operations .....        | 310        |

| 19.1.3 Digital components for sequential operations .....         | 313        |

| 19.1.4 The SR flip-flop .....                                     | 313        |

| 19.1.5 JK flip-flops.....                                         | 315        |

| 19.2 Logic circuits.....                                          | 317        |

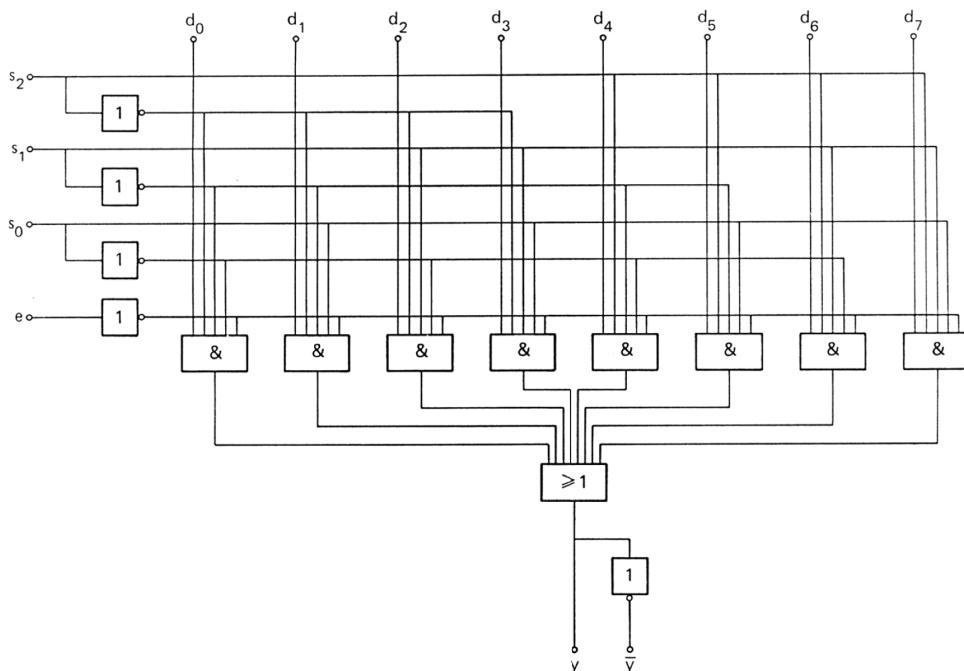

| 19.2.1 Digital multiplexer .....                                  | 317        |

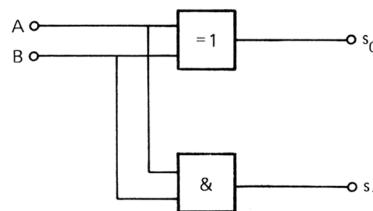

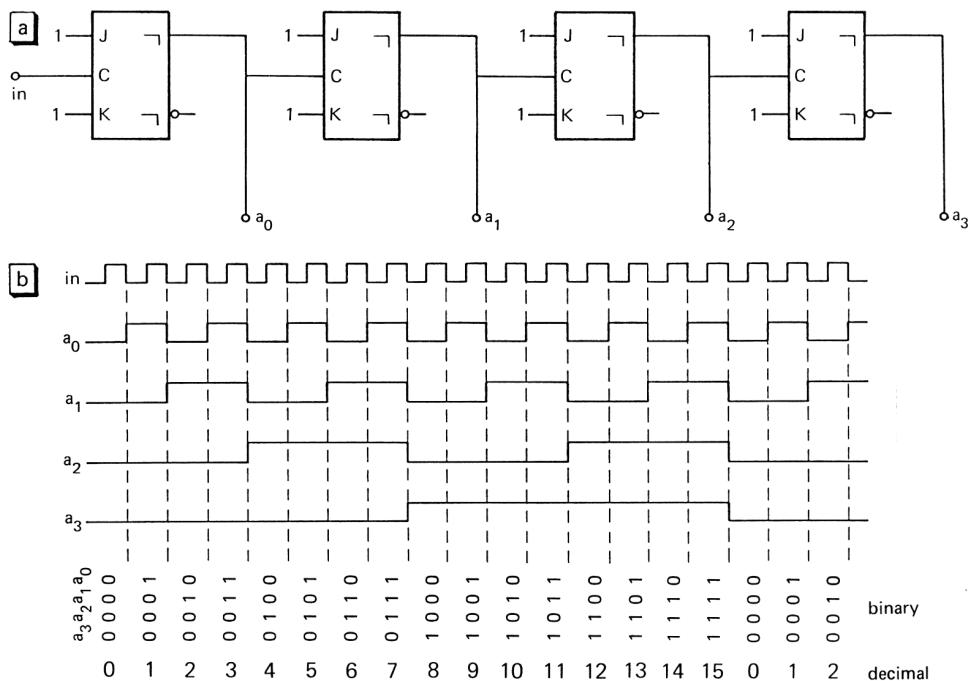

| 19.2.2 The digital adder.....                                     | 318        |

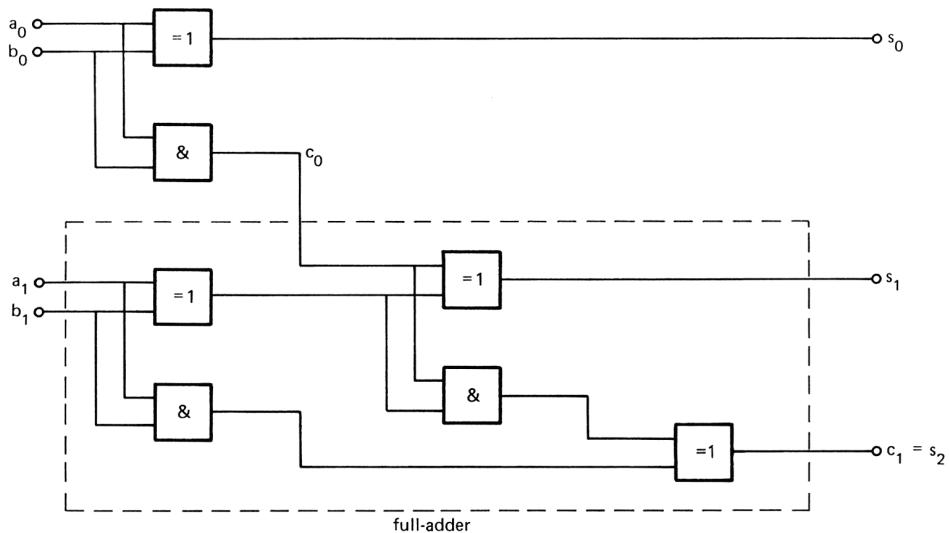

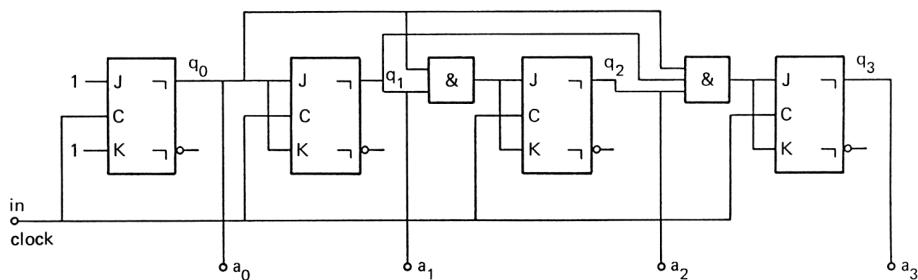

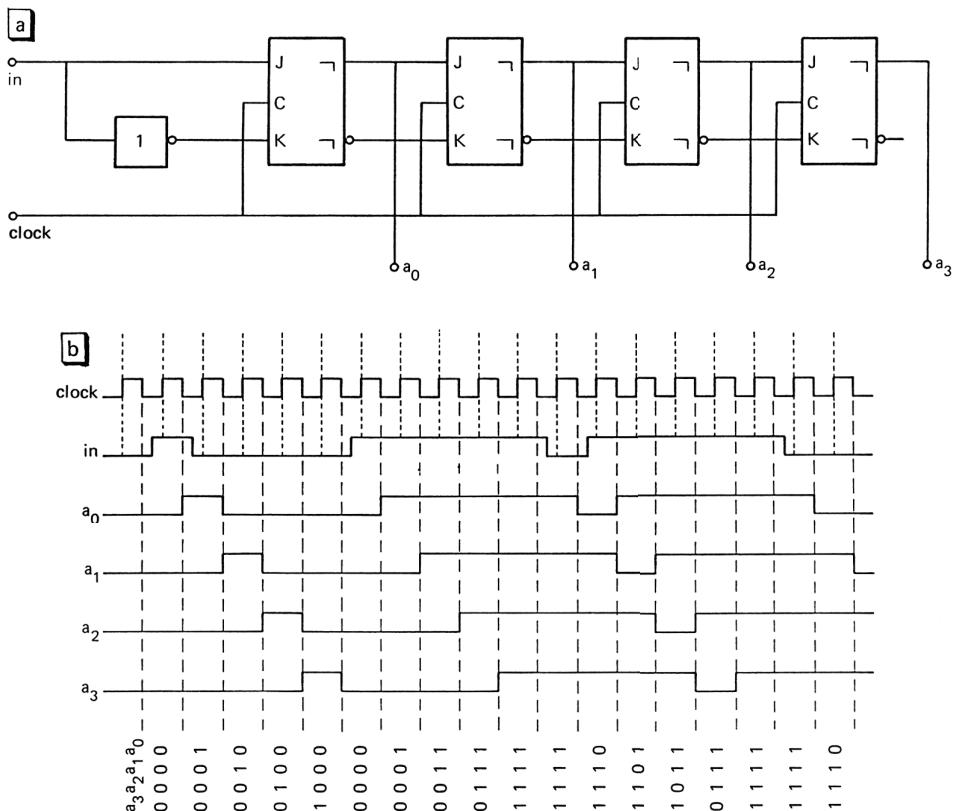

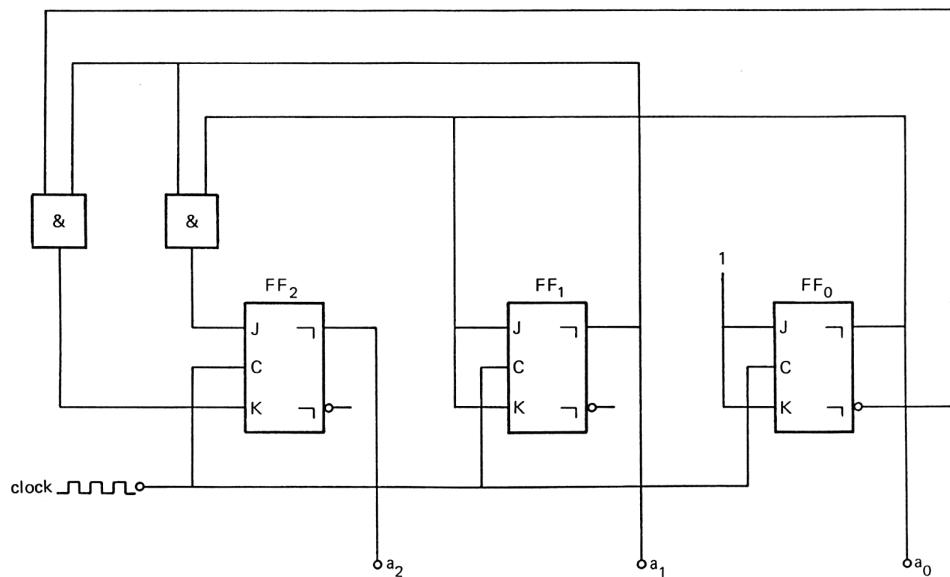

| 19.2.3 Digital counters.....                                      | 320        |

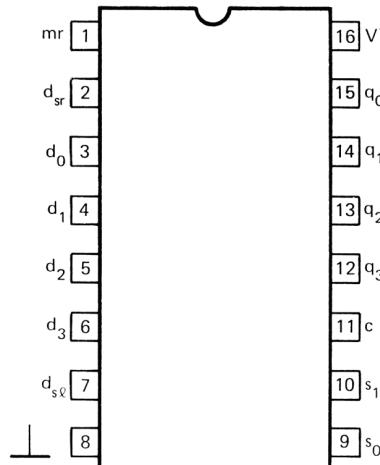

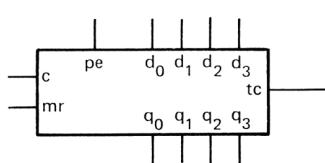

| 19.2.4 Shift registers.....                                       | 322        |

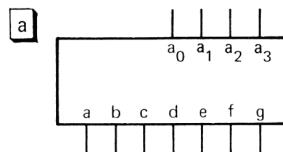

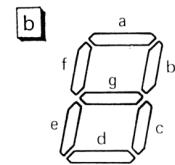

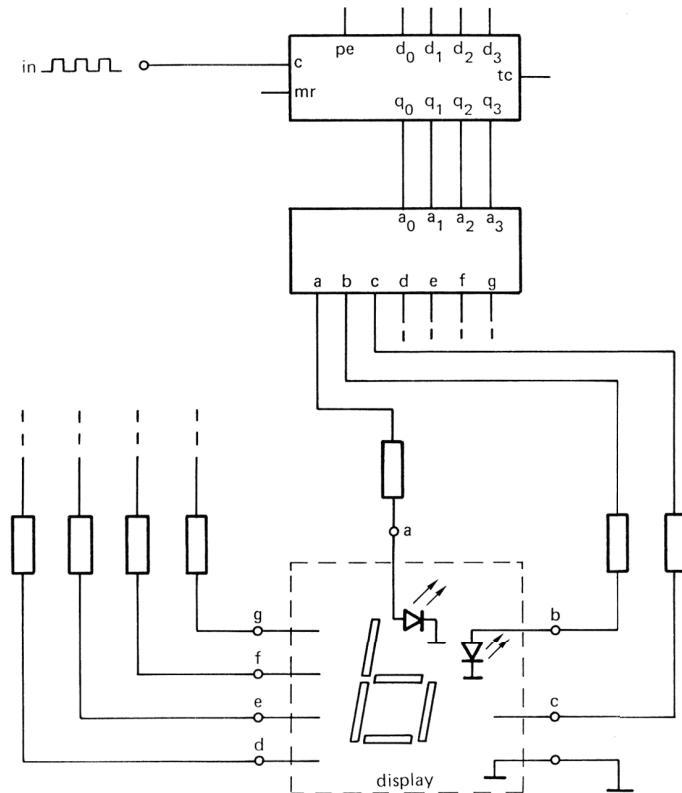

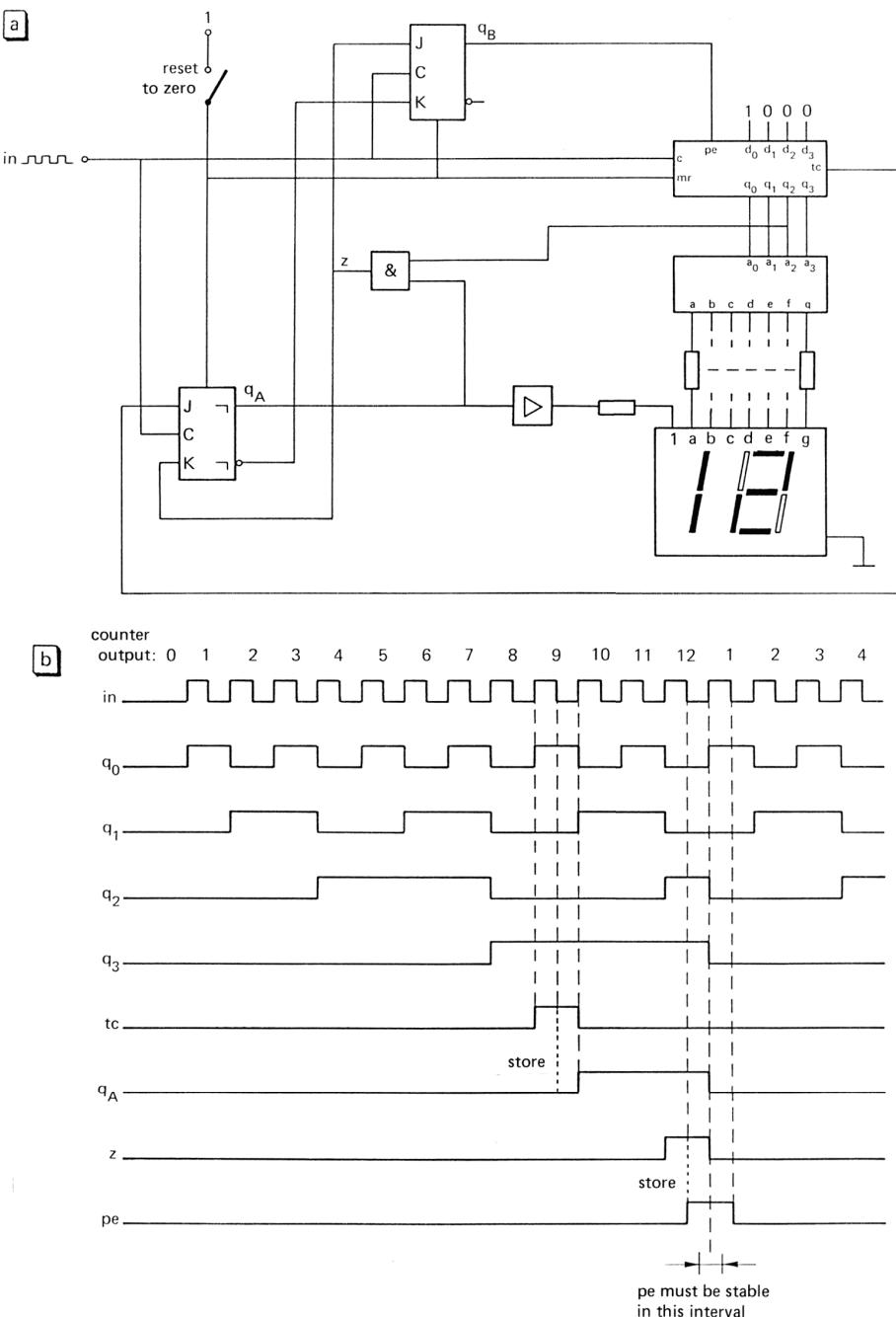

| 19.2.5 An application example .....                               | 324        |

| SUMMARY .....                                                     | 330        |

| EXERCISES .....                                                   | 331        |

| <b>20 Measurement instruments.....</b>                            | <b>333</b> |

| 20.1 Stand-alone measurement instruments .....                    | 333        |

| 20.1.1 Multimeters.....                                           | 334        |

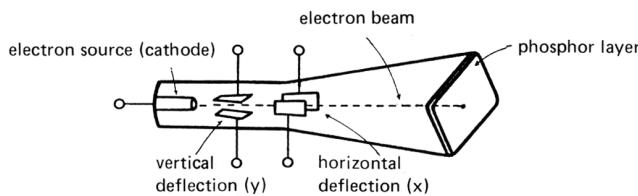

| 20.1.2 Oscilloscopes .....                                        | 334        |

| 20.1.3 Signal generators.....                                     | 340        |

| 20.1.4 Counters, frequency meters and time meters.....            | 341        |

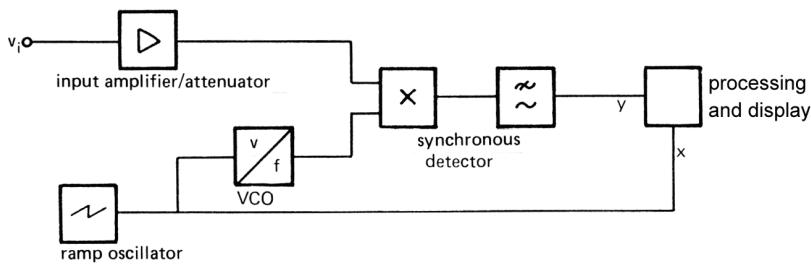

| 20.1.5 Spectrum analyzers .....                                   | 342        |

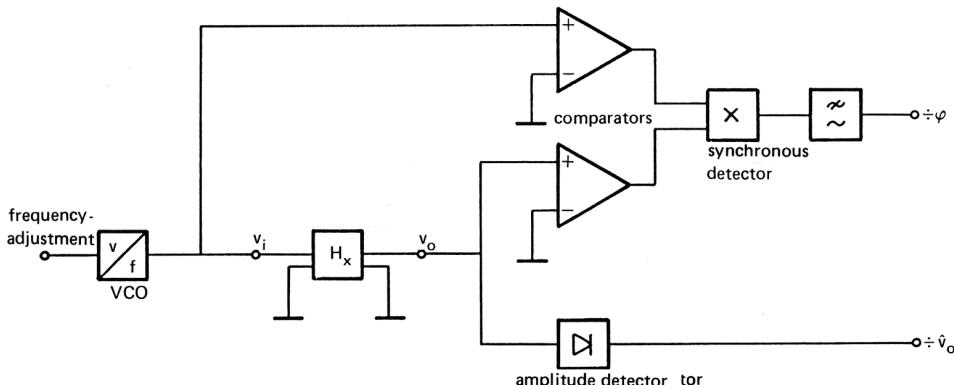

| 20.1.6 Network analyzers.....                                     | 342        |

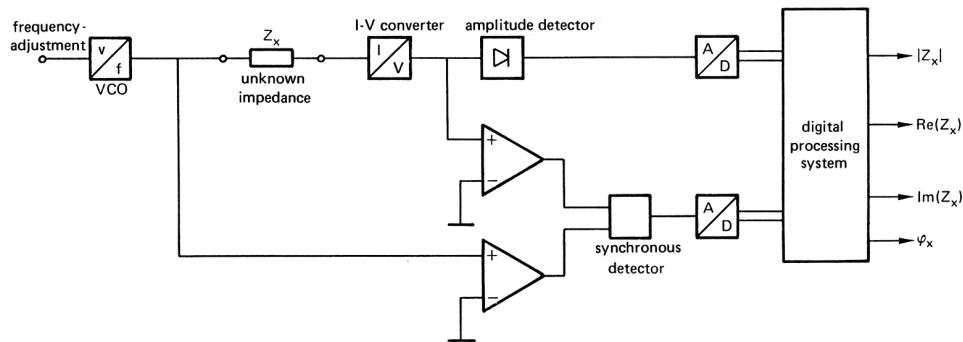

| 20.1.7 Impedance analyzers .....                                  | 344        |

| 20.2 Computer-based measurement instruments .....                 | 344        |

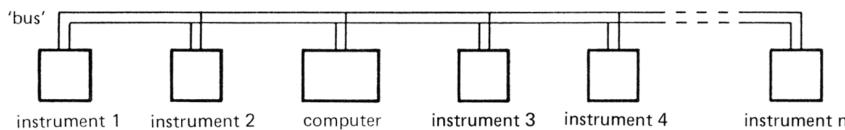

| 20.2.1 Bus structures .....                                       | 345        |

| 20.2.2 An example of a computer-based measurement system .....    | 348        |

| 20.2.3 Virtual instruments .....                                  | 350        |

| SUMMARY .....                                                     | 351        |

| EXERCISES .....                                                   | 352        |

| <b>21 Measurement uncertainty.....</b>                            | <b>355</b> |

| 21.1 Measurement uncertainty described.....                       | 355        |

| 21.1.1 Types of uncertainty .....                                 | 355        |

| 21.1.2 Error propagation .....                                    | 358        |

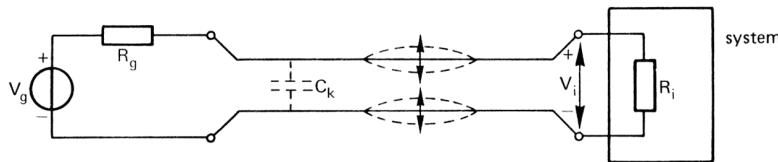

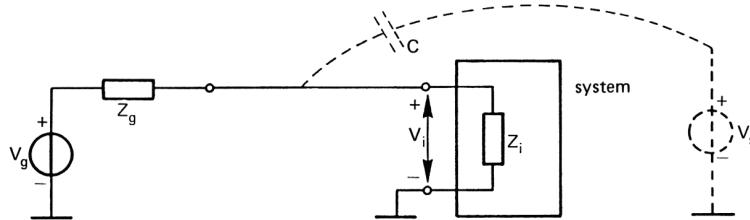

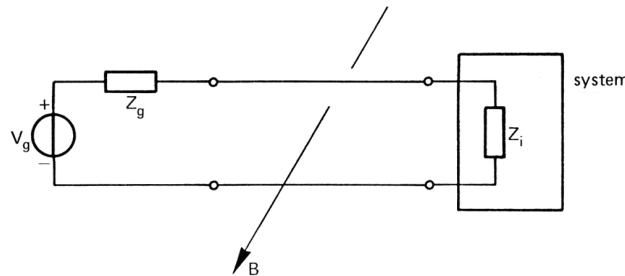

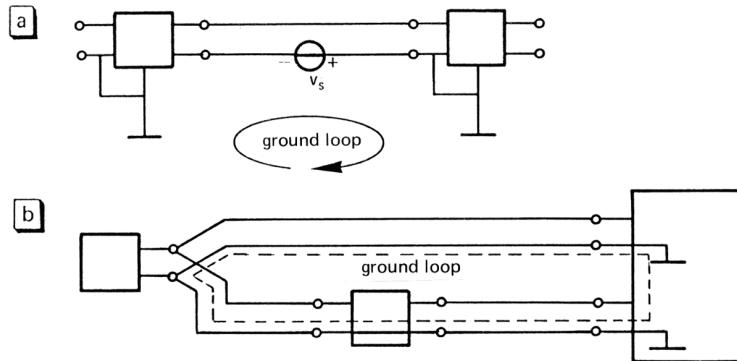

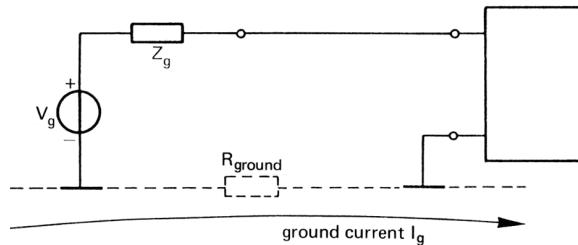

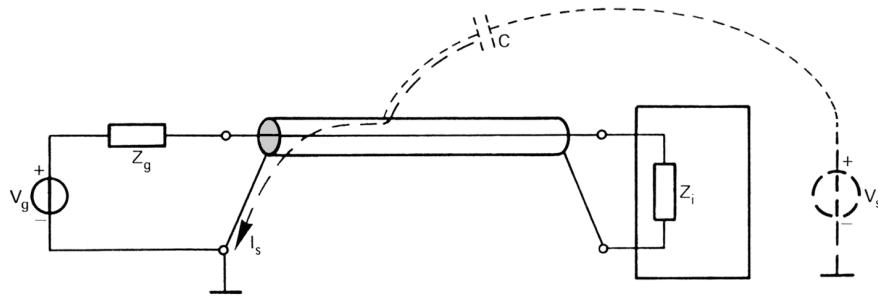

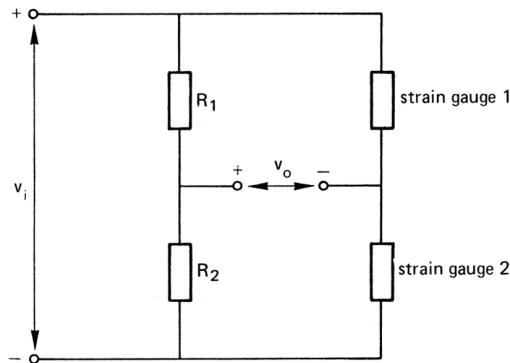

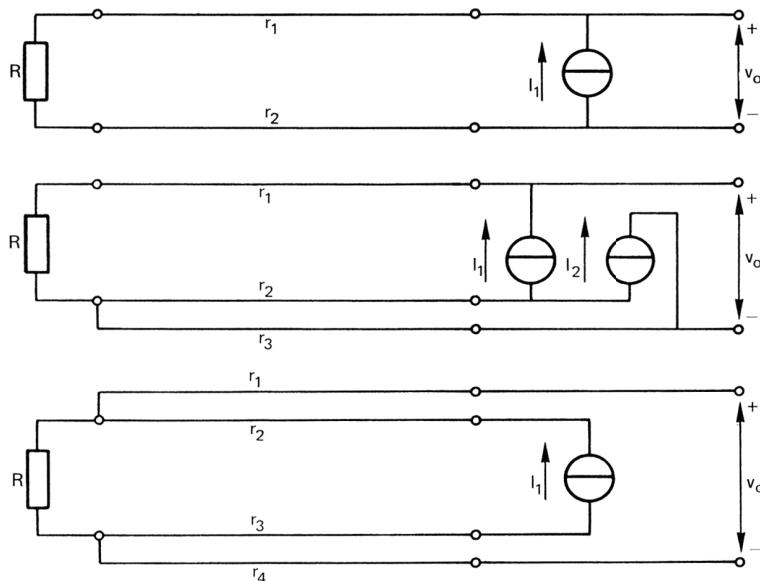

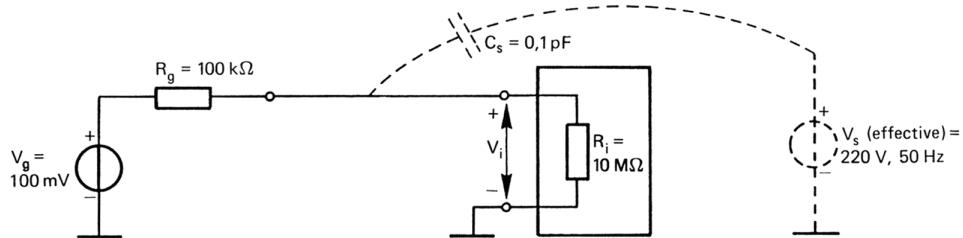

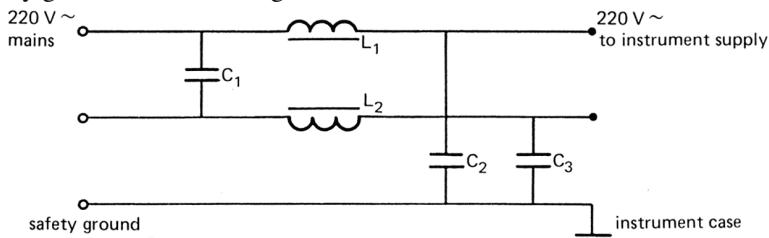

| 21.2 Measurement interference .....                               | 359        |

| 21.2.1 Causes of interference .....                               | 360        |

| 21.2.2 Remedies .....                                             | 362        |

| SUMMARY .....                                                     | 366        |

| EXERCISES .....                                                   | 367        |

| <b>Appendix.....</b>                                              | <b>370</b> |

| A.1 Notation.....                                                 | 370        |

| A.1.1 Symbols .....                                               | 370        |

| A.1.2 Decimal prefixes .....                                      | 371        |

| A.1.3 SI-units .....                                              | 371        |

| A.1.4 Physical constants .....                                    | 373        |

| A.2 Examples of manufacturer's specifications .....               | 374        |

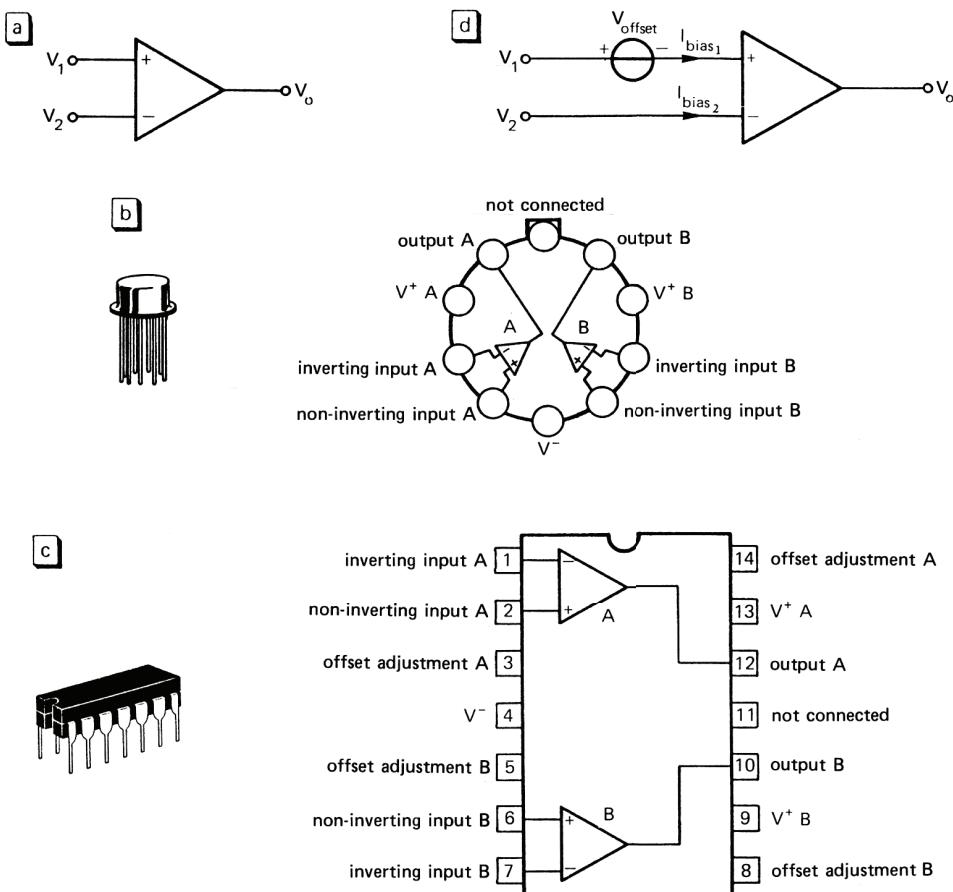

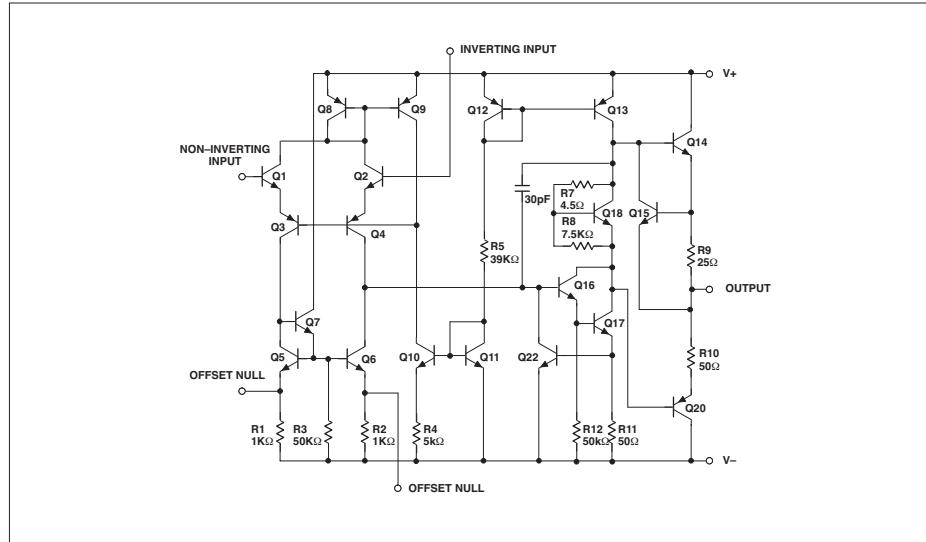

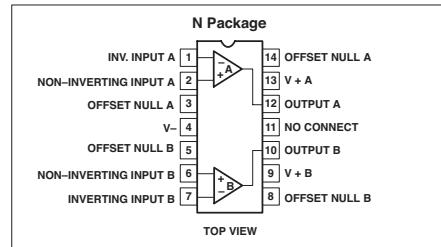

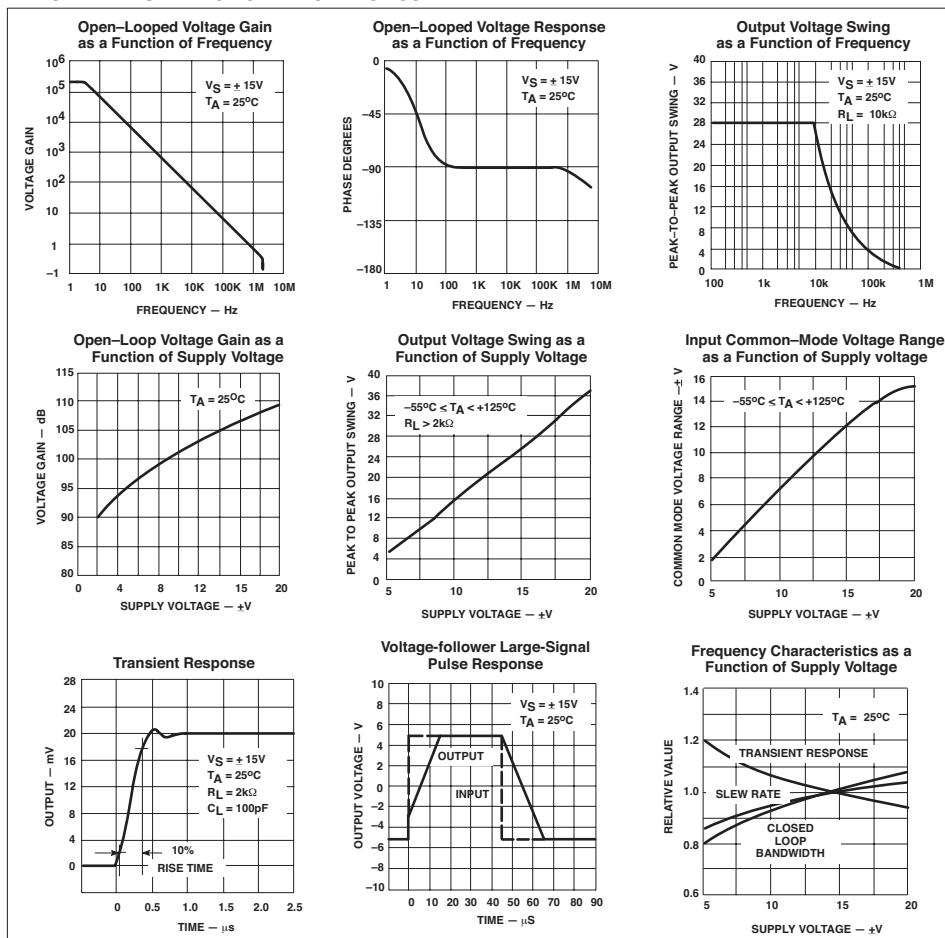

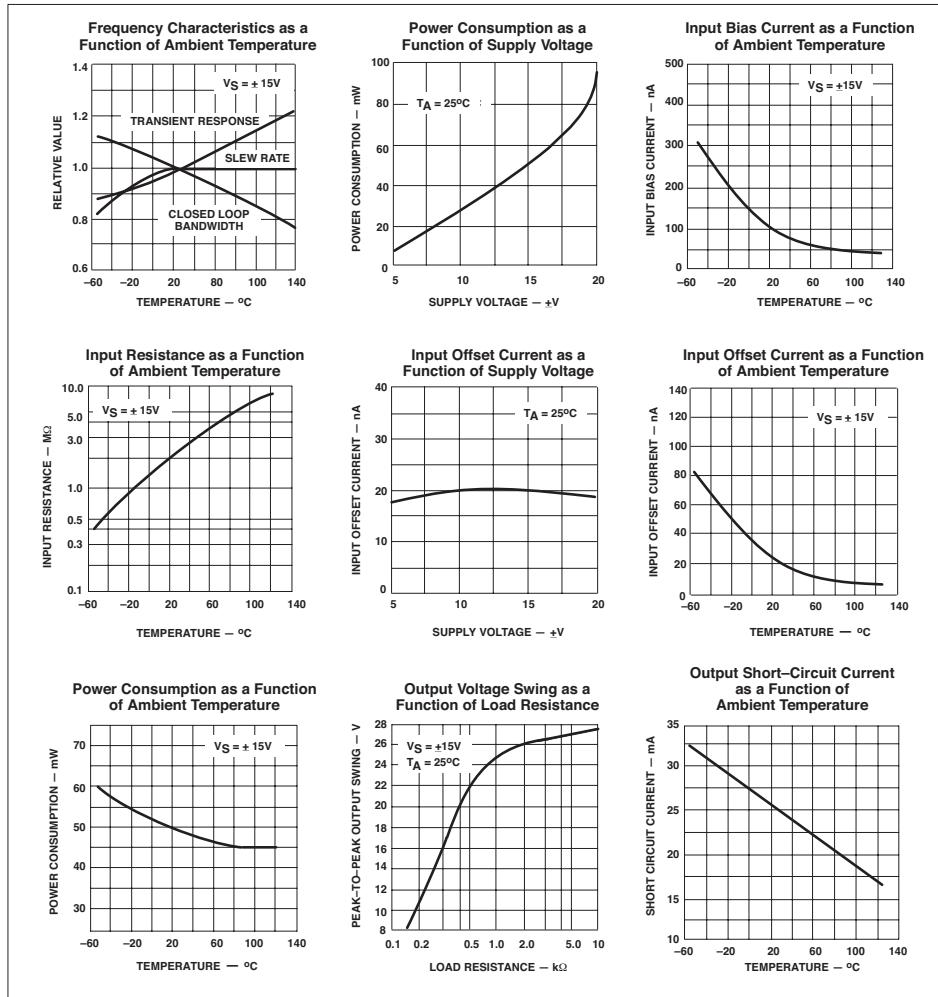

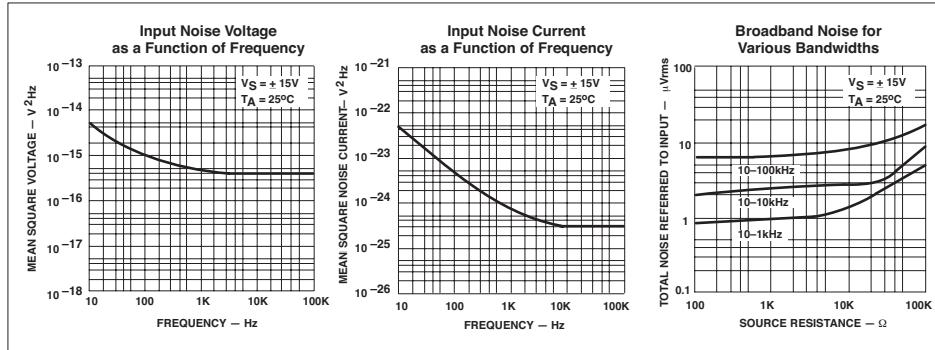

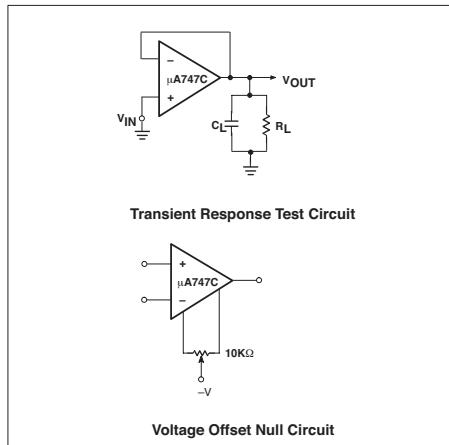

| A.2.1 Specifications of the $\mu$ A747 (an analogue circuit)..... | 375        |

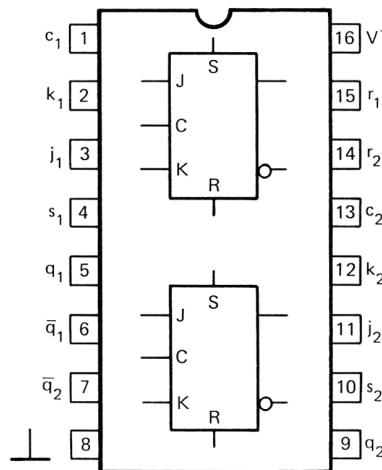

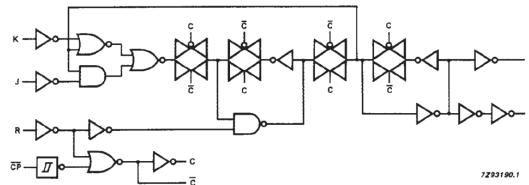

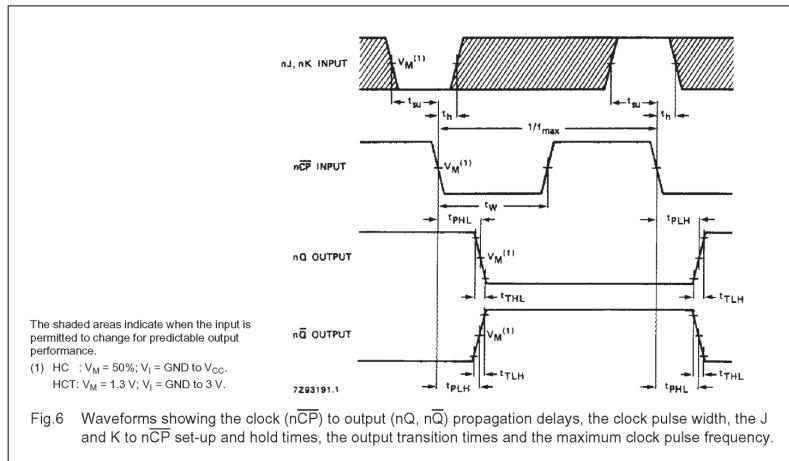

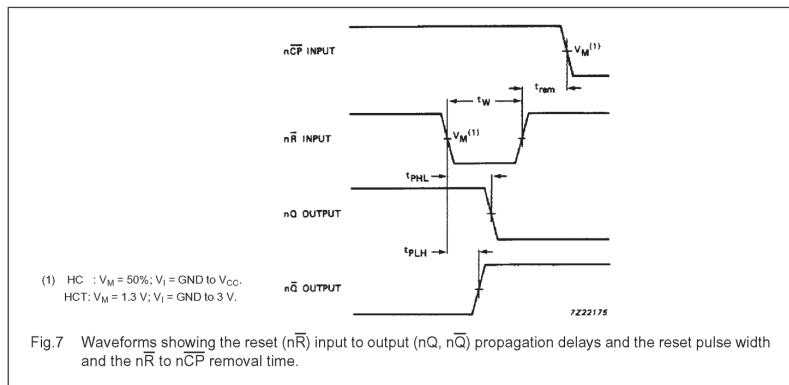

| A.2.2 Specifications of the 74HCT73 (a digital circuit) .....     | 380        |

| Answers to exercises.....                                         | 386        |

| Index.....                                                        | 387        |

# 1 Measurement systems

The aim of any *measuring system* is to obtain information about a physical process and to find appropriate ways of presenting that information to an observer or to other technical systems. With electronic measuring systems the various instrument functions are realized by means of electronic components.

Various basic system functions will be introduced in the first part of this chapter. The extent to which an instrument meets the specified requirements is indicated by the system specifications, all of which will be discussed in the second part of the chapter.

## 1.1 System functions

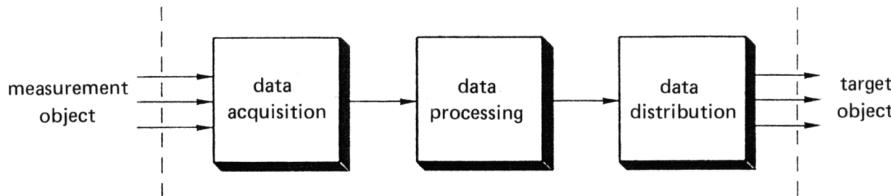

Figure 1.1. The three main functions of any measuring system.

- *Data acquisition*: this involves acquiring information about the measurement object and converting it into electrical measurement data. What multiple input, as illustrated in Figure 1.1, indicates is that invariably more than one phenomenon may be measured or that different measurements may be made, at different points, simultaneously. Where there are single data outputs this means that all data is transferred to the next block through a single connection.

- *Data processing*: this involves the processing, selecting or manipulating – in some other way – of measurement data according to a prescribed program. Often a processor or a computer is used to perform this function.

- *Data distribution*: the supplying of measurement data to the target object. If there is multiple output then several target instruments may possibly be present, such as a series of control valves in a process installation.

It should be pointed out that the above subdivision cannot always be made; part of the system may sometimes be classified as both data acquisition and data processing. Some authors call the entire system shown in Figure 1.1 a data acquisition system, claiming that the data is not obtained until the target object is reached.

In the next section the data acquisition and data distribution parts are subdivided into smaller functional units.

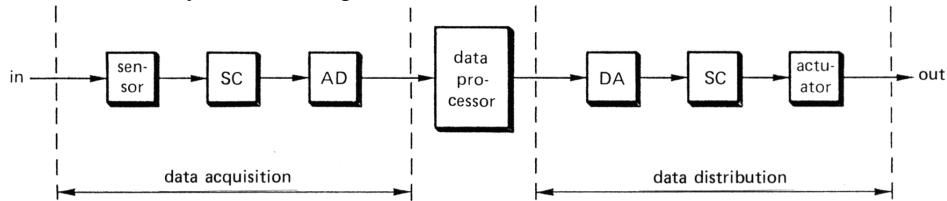

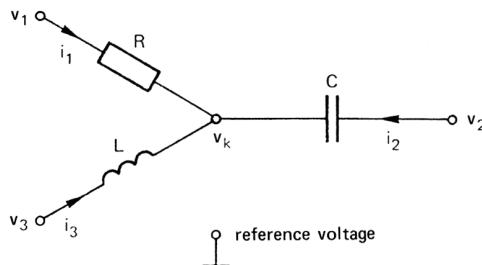

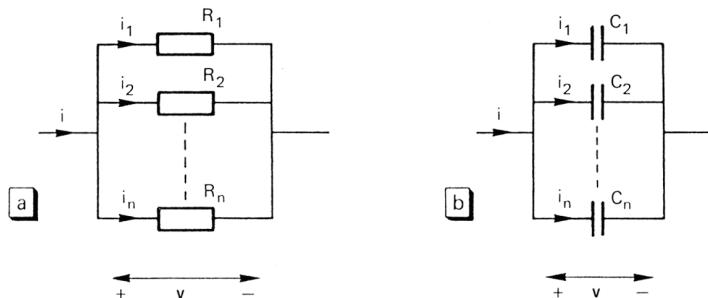

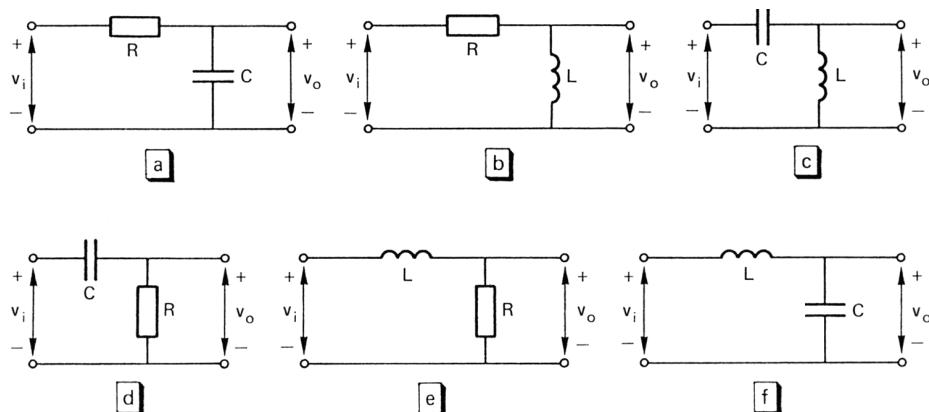

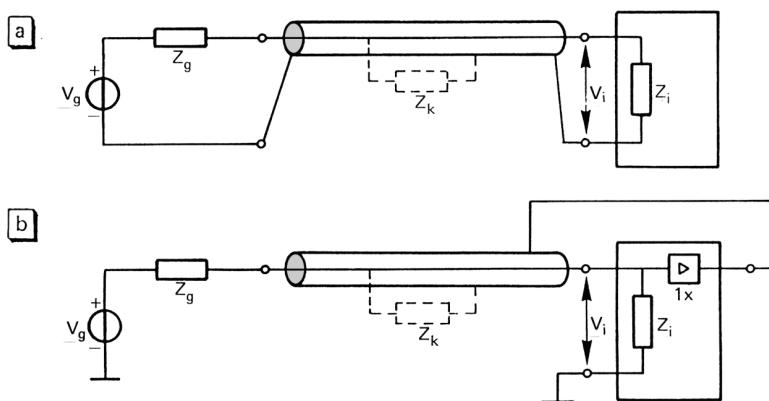

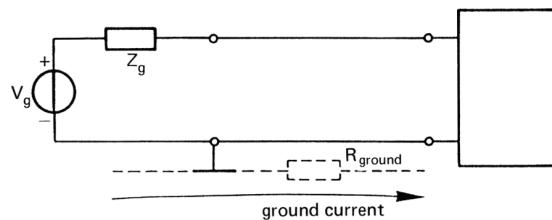

Since most physical measurement quantities are non-electric, they should first be converted into an electrical form in order to facilitate electronic processing. Such conversion is called transduction and it is effected by a transducer or sensor (Figure 1.2). In general, the transducer is kept separate from the main instrument and can be connected to it by means of a special cable.

Figure 1.2. A single channel measuring system.

The sensor or input transducer connects the measuring system to the measurement object; it is the input port of the system through which the information enters the instrument.

Many sensors or transducers produce an analog signal; that is a signal whose value, at any given moment, is a measure of the quantity to be measured: the signal continuously follows the course of the input quantity. However, much of the processing equipment can only cope with digital signals, which are binary coded signals. A digital signal only contains a finite number of distinguishable codes, usually a power of 2 (for instance  $2^{10} = 1024$ ).

The analog signal must be converted into a digital signal. This process is known as analog-to-digital conversion or, AD-conversion. Analog-to-digital conversion comprises three main processes, the first of which is sampling where, at discrete time intervals, samples are taken from the analog signal. Each sampled value is maintained for a certain time interval, during which the next processes can take place. The second step is quantization. This is the rounding off of the sampled value to the nearest of a limited number of digital values. Finally, the quantized value is converted into a binary code.

Both sampling and quantization may give rise to loss of information. Under certain conditions, though, such loss can be limited to an acceptable minimum.

The output signal generated by a transducer is seldom suitable for conversion into a digital signal, the converter input should first satisfy certain conditions. The signal processing required to fulfill such conditions is termed signal conditioning. The various processing steps required to achieve the proper signal conditions will be explained in different separate chapters. The main steps, however, will be briefly explained below.

- *Amplification*: in order to increase the signal's magnitude or its power content.

- *Filtering*: to remove non-relevant signal components.

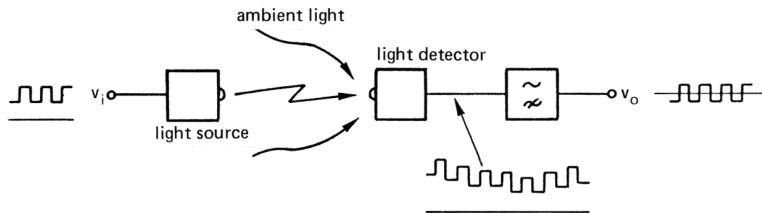

- *Modulation*: modification of the signal shape in order to enable long-distance signal transport or to reduce the sensitivity to interference during transport.

- *Demodulation*: the reverse process operation to modulation.

- *Non-linear and arithmetical operations*: such as logarithmic conversion and the multiplication of two or more signals.

It goes without saying that none of the above operations should affect the information content of the signal.

After having been processed by the (digital) processor, the data are subjected to a reverse operation (Figure 1.2). The digital signal is converted into an analog signal by a digital-to-analog or DA converter. It is then supplied to an actuator (alternative names for this being: effector, excitor and output transducer), which transforms the electrical signal into the desired non-electric form. If the actuator cannot be connected directly to the DA converter, the signal will first be conditioned. This conditioning usually involves signal amplification.

The actuator or output transducer connects the measurement system to the target object, thus becoming the instrument's output port through which the information leaves the system.

Depending on what is the goal of the measurement, the actuator will perform various functions such as, for instance: *indicating* by means of a digital display; *registering* (storing) with such things as a printer, a plotter or a magnetic disk; or *process controlling* with the aid of a valve, a heating element or an electric drive.

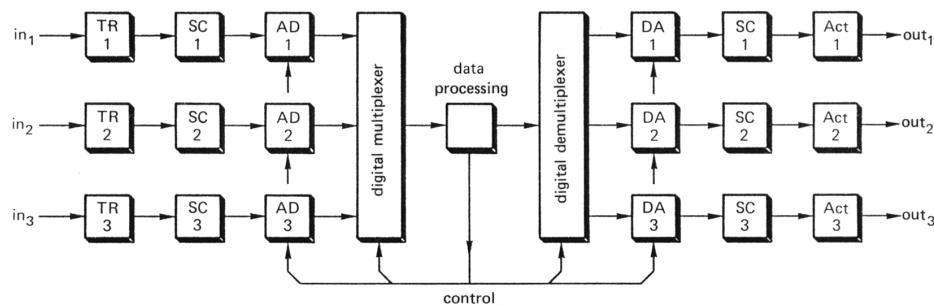

The diagram given in Figure 1.2 refers only to one input variable and one output variable. For the processing of more than one variable, one could take a set of single channel systems. Obviously this is neither efficient nor necessary. The processor shown in Figure 1.2, in particular, is able to handle a large number of signals, thanks to its high data processing speed. Figure 1.3 gives the layout of a multi-channel measuring system that is able to handle multiple inputs and outputs using only one (central) processor.

Central processing of the various digital signals can be effected by means of multiplexing. The digital multiplexer denoted in Figure 1.3 connects the output of each AD converter to the processor in an alternating fashion. The multiplexer may be viewed as an electronically controlled multi-stage switch, controlled by the processor. This type of multiplexing is called time multiplexing because the channels are scanned and their respective signals are successively transferred – in terms of time – to the processor. Another type of multiplexing, frequency multiplexing, will be discussed in a later section.

Figure 1.3. A three-channel measuring system with one central processor.

TR = transduction, SC = signal conditioning.

At first sight it would appear that the concept of time multiplexing has the disadvantage that only the data taken from the selected channel is processed while the information derived from the non-selected channels is blocked. It can be demonstrated that when the

time between two successive selections for a particular channel is made sufficiently short the information loss will be negligible. An explanation of what precisely is meant by “sufficiently short” will be given in Section 2.2.

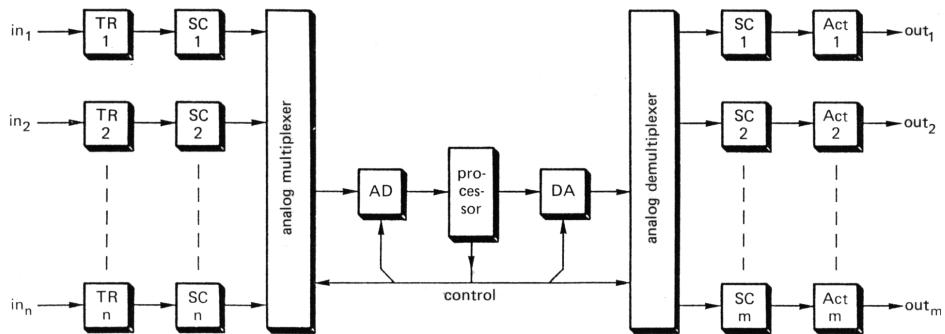

Figure 1.3 clearly shows that a system with many sensors or actuators will also contain large numbers of signal processing units, thus making it expensive. In such cases the principle of multiplexing can also be applied to the AD and DA converters. Figure 1.4 shows the layout of such a measurement system in which all the conditioned signals are supplied to an analog multiplexer. It is even possible to have a central signal conditioner placed behind the multiplexer so as to further reduce the number of system components. It is possible to extend the process of centralizing instrument functions to the data distribution part of the system. An analog multiplexer distributes the converted analog signals over the proper output channels. It is not common practice for output signal conditioners to be multiplexed because multiplexers are not usually designed to deal with large power signals.

Although the functions of analog and digital multiplexers are similar, their design is completely different. Digital multiplexers only deal with digital signals which have better noise and interference immunity than analog signals. Digital multiplexers are therefore far less critical (and less expensive) than analog multiplexers. The same goes for the AD converters. In Figure 1.3 it can be seen that each AD converter has a full multiplexer cycle period in which to perform a conversion. In the system shown in Figure 1.4, the conversion ought to be completed within the very short period of time when a channel is connected to the processor. This system configuration thus requires a high speed (and a higher priced) converter. The centralized system contains a reduced number of more expensive components. Whether one opts for a centralized or a distributed system will depend very much on the number of channels.

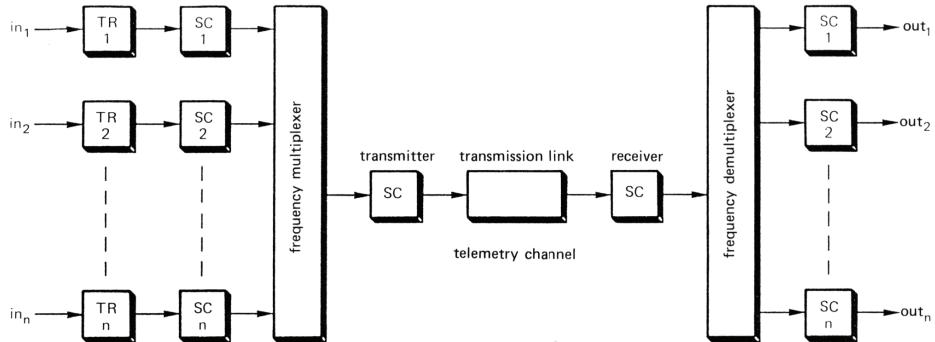

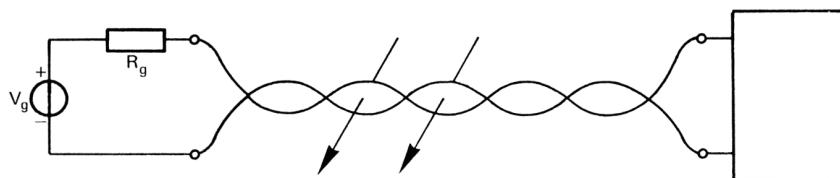

In certain situations the measurement signals and control signals have to be transported over long distances. This instrumentation aspect is known as telemetry. A telemetry channel consists of an electric conductor (for instance a telephone cable), an optical link (like a glass fiber cable) or a radio link (e.g. made via a communication satellite). To reduce the number of lines, which are invariably expensive, the concept of multiplexing is used (Figure 1.5). Instead of time multiplexing, telemetry systems use frequency multiplexing. Each measurement signal is converted to a frequency band assigned to that particular signal. If the bands do not overlap, the converted signals can be transported simultaneously over a single transmission line. When they arrive at the desired destination the signals are demultiplexed and distributed to the proper actuators. More details on this type of multiplexing will be given elsewhere in this book.

Figure 1.4. A multi-channel measuring system with a centralized processor and AD and DA-converters. For an explanation of the abbreviations see Figure 1.3.

Figure 1.5. A multi-channel measuring system with frequency multiplexing.

Signals can be transmitted in analog or digital form. Digital transport is preferable if high noise immunity is required, for instance for very long transport channels or links that pass through a noisy environment.

## 1.2 System specifications

A measurement system is designed to perform measurements according to the relevant specifications. Such specifications convey to the user of the instrument to what degree the output corresponds with the input. The specifications reflect the quality of the system.

The system will function correctly if it meets the specifications given by the manufacturer. If that is not the case it will fail, even if the system is still functioning in the technical sense. Any measuring instrument and any subsystem accessible to the user has to be fully specified. Unfortunately, many specifications lack clarity and completeness.

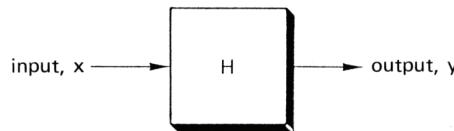

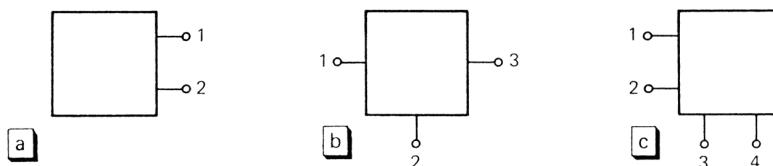

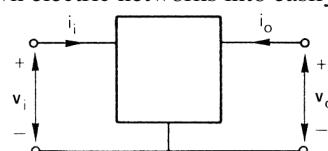

The input signal of the single channel system given in Figure 1.6 is denoted as  $x$  and its output signal as  $y$ . The relationship between  $x$  and  $y$  is called the system transfer.

Figure 1.6. Characterization of a system with input  $x$ , output  $y$  and transfer  $H$ .

By observing the output, the user is able to draw conclusions about the input. The user therefore has to be completely familiar with the system's transfer. Deviations in the transfer may cause uncertainties about the input and so result in measurement errors. Such deviations are permitted, but only within certain limits which are the tolerances of the system. Those tolerances also constitute part of the specifications. In the following pages the main specifications of a measurement system will be discussed. The user should first of all be familiar with the operating range of the system. The operating range includes the measurement range, the required supply voltage, the environmental conditions and possibly other parameters.

**Example 1.1**

*A manufacturer of a digital temperature-measuring instrument gives the following description of the operating range:*

- \* *measuring range:  $-50^{\circ}\text{C}$  to  $200^{\circ}\text{C}$ ;*

- \* *permitted operational temperature:  $-10^{\circ}\text{C}$  to  $40^{\circ}\text{C}$ ;*

- \* *storage temperature:  $-20^{\circ}\text{C}$  to  $85^{\circ}\text{C}$*

- \* *mains voltage:  $220\text{ V} \pm 15\%$ ,  $50\ldots 60\text{ Hz}$ ; can be switched to  $115\text{ V}$ ,  $127\text{ V}$ ,  $240\text{ V} \pm 15\%$ ,  $50\ldots 60\text{ Hz}$ ;*

- \* *analog outputs:  $0\text{-}10\text{ V}$  ( $\text{load} > 2\text{k}\Omega$ ) and  $0\text{-}20\text{ mA}$  or  $4\text{-}20\text{ mA}$  ( $\text{load} < 600\Omega$ ).*

*All other specifications only apply under the condition that the system has never before been taken beyond its permitted operating range.*

The resolution indicates the smallest detectable change in input quantity. Many system parts show limited resolution. A few examples of this are these: a wire-wound potentiometer for the measurement of angles has a resolution set by the windings of the helix – the resistance between the slider and the helix changes leap-wise as it rotates; a display presenting a measurement value in numerals has a resolution equal to the least significant digit.

The resolution is expressed as the smallest detectable change in the input variable:  $\Delta x_{\min}$ . Sometimes this parameter is related to the maximum value  $x_{\max}$  that can be processed, the so-called full-scale value or FS of the instrument, resulting in the resolution expressed as  $\Delta x_{\min}/x_{\max}$  or  $x_{\max}/\Delta x_{\min}$ . This mixed use of definitions seems very confusing. However, it is easy to see from the units or the value itself which definition is used.

**Example 1.2**

*The resolution of a four-digit decimal display with a fixed decimal point in the third position from the left is  $0.1$  units. The maximum indication apparently equals  $999.9$  units, which is about  $1000$ . The resolution of this display is therefore  $0.1$  units or  $10^{-4}$  or  $10^4$ .*

The inaccuracy is a measure of the total uncertainty of the measurement result that may be caused by all kinds of system errors. It comprises calibration errors, long and short-term instability, component tolerances and other uncertainties that are not separately

specified. Two definitions may be distinguished: absolute inaccuracy and relative inaccuracy. Absolute inaccuracy is expressed in terms of units of the measuring quantity concerned, or as a fraction of the full-scale value. Relative inaccuracy relates the error to the actual measuring value.

**Example 1.3**

*The data sheet of a volt meter with a four digit indicator and a full-scale value of 1.999 V specifies the instrument inaccuracy as  $\pm 0.05\% \text{ FS}$   $\pm 0.1\%$  of the indication  $\pm \frac{1}{2}$  digit.*

*The absolute inaccuracy of a voltage of 1.036 V measured with this instrument equals:  $\pm 0.05$  of 2 V (the approximate value of FS) plus  $\pm 0.1\%$  of 1 V (approximate value of the indication) plus  $\pm 0.5$  of 1 mV (the weight of the last digit), which amounts to  $\pm 2.5$  mV in total.*

*The relative inaccuracy is the absolute inaccuracy divided by the indication so it is  $\pm 0.25\%$ .*

Inaccuracy is often confused with accuracy, the latter being complementary to it. When a specification list gives an accuracy of 1%, this hopefully means that there is an inaccuracy of 1% or an accuracy of 99%.

The sensitivity of a measuring system is defined as the ratio between a change in the output value and a change in the input value that causes that same output change. The sensitivity of a current-to-voltage converter is expressed in V/A, that of a linear position sensor in, for instance, mV/ $\mu\text{m}$  and that of an oscilloscope in, for instance, cm/V.

A measuring system is usually also sensitive to changes in quantities other than the intended input quantity, such as the ambient temperature or the supply voltage. These unwelcome sensitivities should be specified as well when this is necessary for a proper interpretation of the measurement result. To gain better insight into the effect of such false sensitivity it will be related to the sensitivity to the measurement quantity itself.

**Example 1.4**

*A displacement sensor with voltage output has a sensitivity of 10 mV/mm. Its temperature sensitivity is  $-0.1 \text{ mV/K}$ . Since  $-0.1 \text{ mV}$  corresponds with a displacement of  $-10 \mu\text{m}$ , the temperature sensitivity can also be expressed as  $-10 \mu\text{m/K}$ . A temperature rise of  $5^\circ\text{C}$  will result in an apparent displacement of  $-50 \mu\text{m}$ .*

**Example 1.5**

*The sensitivity of a temperature sensor including the signal-conditioning unit is 100 mV/K. The signal conditioning part itself is also sensitive to (ambient) temperature and it appears to create an extra output voltage of 0.5 mV for each  $^\circ\text{C}$  rise in ambient temperature (not necessarily the sensor temperature). The undesired temperature sensitivity is thus  $0.5 \text{ mV/K}$  or  $0.5/100 = 5 \text{ mK/K}$ . A change in ambient temperature of  $\pm 10^\circ\text{C}$  gives an apparent change in sensor temperature that is equal to  $\pm 50 \text{ mK}$ .*

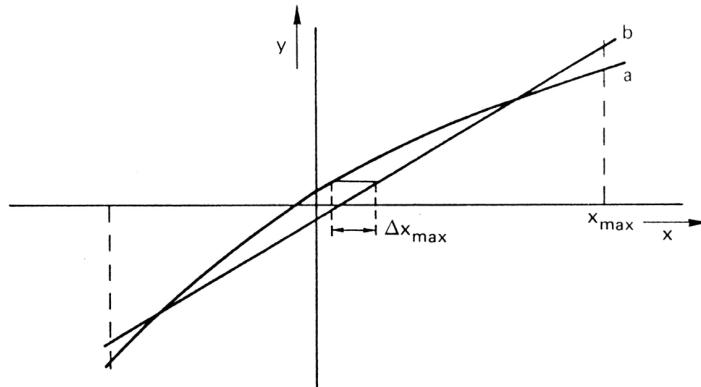

Mathematically, the sensitivity is expressed as  $S = dy/dx$ . If output  $y$  is a linear function of input  $x$  then the sensitivity does not depend on  $x$ . In the case of a non-linear transfer function  $y = f(x)$ ,  $S$  will depend on the input or output value (Figure 1.7). Users of measuring instruments prefer a linear response, because then the sensitivity can be

expressed in terms of a single parameter and the output will not show harmonic distortion. The transfer of a system with slight non-linearity may be approximated by a straight line. The user should still know the deviation from the actual transfer as specified by the non-linearity.

Figure 1.7. Example of a non-linear transfer characteristic,

(a) real transfer, (b) linear approximation.

The non-linearity of a system is the maximum deviation in the actual transfer characteristic from a pre-described straight line. Manufacturers specify non-linearity in various ways, for instance, as the deviation in input or output units:  $\Delta x_{\max}$  or  $\Delta y_{\max}$ , or as a fraction of FS:  $\Delta x_{\max}/x_{\max}$ . They may use different settings for the straight line: by passing through the end points of the characteristic, by taking the tangent through the point  $x = 0$ , or by using the best-fit (least-squares) line, to mention but a few possibilities.

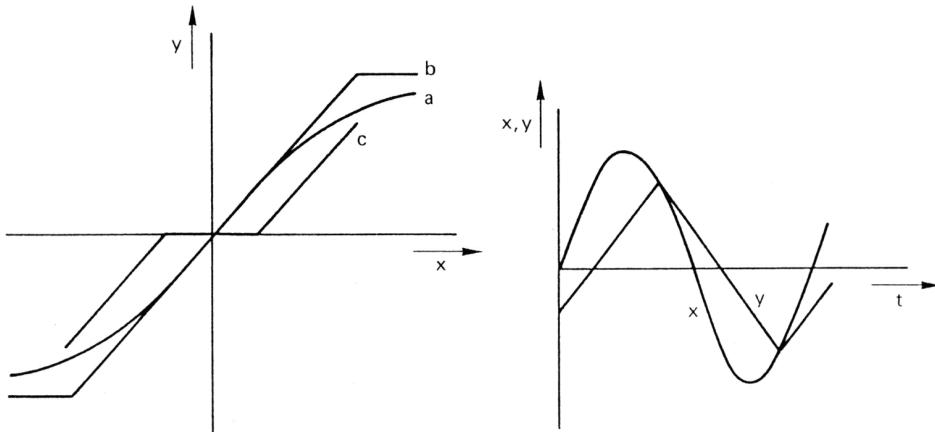

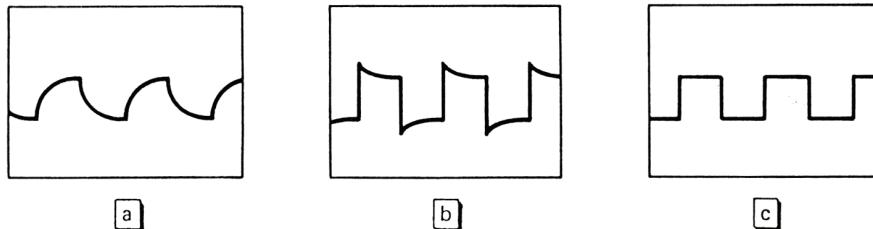

Figure 1.8. Some types of static non-linearity: (a) saturation,

(b) clipping. (c) dead zone

Figure 1.9. The effect of slew rate limitation on the output signal  $y$  at a sinusoidal input  $x$ .

Figure 1.8 depicts some particular types of non-linearity found in measuring systems: saturation, clipping and dead zone (sometimes also called cross-over distortion). These are examples of static non-linearity, appearing even when inputs change slowly. Figure

1.9 shows another type of non-linearity, known as slew rate limitation, which only occurs when the input values change relatively fast. The output which is unable to keep up with the quickly changing input thus results in distortion at the output point. Slew rate is specified as the maximum rate of change in the output of the system.

Most measurement systems are designed in such a way that output is zero when input is zero. If the transfer characteristic does not intersect the origin ( $x = 0, y = 0$ ) the system is said to have offset. Offset is expressed in terms of the input or the output quantity. It is preferable to specify the input offset so that comparisons with the real input quantity can be made. Non-zero offset arises mainly from component tolerances. Most electronic systems make it possible to compensate for the offset, either through manual adjustment or by means of manually or automatically controlled zero-setting facilities. Once adjusted to zero, the offset may still change due to temperature variations, changes in the supply voltage or the effects of ageing. This relatively slow change in the offset is what we call zero drift. It is the temperature-induced drift (the temperature coefficient or t.c of the offset) that is a particularly important item in the specification list.

**Example 1.6**

*A data book on instrumentation amplifiers contains the following specifications for a particular type of amplifier:*

|                                  |                                                      |

|----------------------------------|------------------------------------------------------|

| <i>input offset voltage:</i>     | <i>max. <math>\pm 0.4</math> mV, adjustable to 0</i> |

| <i>t.c. of the input offset:</i> | <i>max. <math>\pm 6</math> <math>\mu</math>V/K</i>   |

| <i>supply voltage coeff.:</i>    | <i>40 <math>\mu</math>V/V</i>                        |

| <i>long-term stability:</i>      | <i>3 <math>\mu</math>V/month</i>                     |

There are two ways to determine the offset of any system. The first method is based on setting the output signal at zero by adjusting the input value. The input value for which the output is zero is the negative value of the input offset. The second method involves measuring the output at zero input value. When the output is still within the allowed range, the input offset simply becomes the measured output divided by the sensitivity. Sometimes a system is deliberately designed with offset. Many industrial transducers have a current output that ranges from 4 to 20 mA (see Example 1.1). This facilitates the detection of cable fractures or a short-circuit so that such a defect is clearly distinguishable from a zero input.

The sensitivity of an electronic system may be increased to almost unlimited levels. There is, however, a limit to the usefulness of doing this. If one increases the sensitivity of the system its output offset will grow as well, to the limits of the output range. Even at zero input voltage, an ever-increasing sensitivity will be of no use, due to the limitations imposed by noise in the system. Electrical noise amounts to a collection of spontaneous fluctuations in the currents and voltages present in any electronic system, all of which arises from the thermal motion of the electrons and from the quantized nature of electric charge. Electrical noise is also specified in terms of input quantity so that its effect can be seen relative to that of the actual input signal.

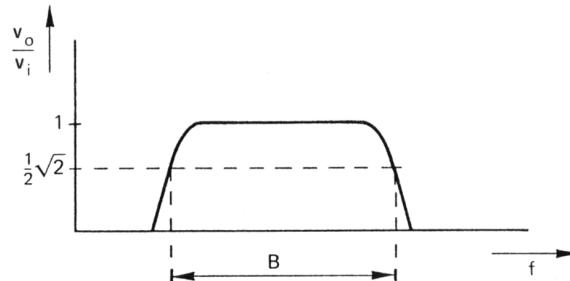

The sensitivity of a system depends on the frequency of the signal to be processed. A measure of the useful frequency range is the frequency band. The upper and lower limits of the frequency band are defined as those frequencies where the power transfer has dropped to half its nominal value. For voltage or current transfer the criterion is

$\frac{1}{2}\sqrt{2}$  of the respective nominal voltage and current transfer (Figure 1.10). The lower limit of the frequency band may be zero; the upper limit always has a finite value. The extent of the frequency band is called the bandwidth of the system expressed in Hz.

Figure 1.10. A voltage transfer characteristic showing the boundaries of the frequency band. The nominal transfer is 1, its bandwidth is B.

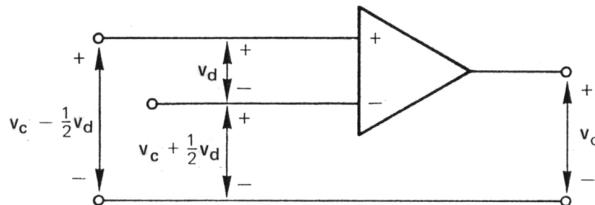

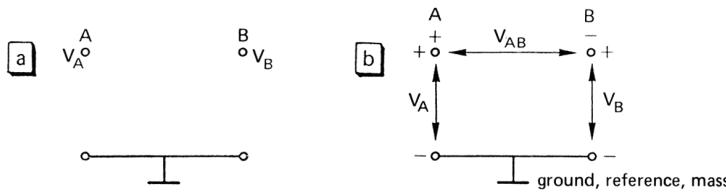

A frequent problem in instrumentation is the problem of how to determine the difference between two almost equal measurement values. Such situations occur when, for instance, big noise or interference signals are superimposed on relatively weak measurement signals. A special amplifier has been developed for these kinds of measurement problems, it is known as the differential amplifier (Figure 1.11). Such an amplifier, which is usually a voltage amplifier, has two inputs and one output. Ideally the amplifier is not sensitive to equal signals on both inputs (common mode signal), only to a difference between the two input signals (differential mode signals). In practice any differential amplifier will exhibit a non-zero transfer for common mode signals. A quality measure that relates to this property is the common mode rejection ratio or CMRR, which is defined as the ratio between the transfer for differential mode signals,  $v_o/v_d$  and common mode signals  $v_o/v_c$ . In other words, the CMRR is the ratio of a common mode input signal and a differential mode input signal, both of which give equal output. An ideal differential amplifier has a CMRR, which is infinite.

Figure 1.11. An ideal differential amplifier is insensitive to common mode signals ( $v_c$ ) and amplifies only the differential signal  $v_d$ .

**Example 1.7**

A system with a CMRR of  $10^5$  is used to determine the difference between two voltages, both about 10 V high. The difference appears to be 5 mV. The inaccuracy of this result, due to the finite CMRR, is  $\pm 2\%$  because the common mode voltage produces an output voltage that is equivalent to that of a differential input voltage of  $10/10^5 = 0.1$  mV.

The final system property to be discussed in this chapter has to do with reliability. There is always a chance that a system will fail after a certain period of time. Such properties should be described according to probability parameters, one of these parameters being the reliability  $R(t)$  of the system. This is defined as the probability that the system will function correctly (in accordance with its specifications) up to the time  $t$  (provided that the system has operated within the permitted range). It should be clear that  $R$  diminishes as time elapses so that the system becomes increasingly less reliable.

The system parameter  $R$  has the disadvantage that it changes over the course of time. Better parameters are the mean-time-to-failure (MTTF) and the failure rate  $\lambda(t)$ . The MTTF is the mean time that passes up until the moment when the system fails; it is its mean lifetime

**Example 1.8**

An incandescent lamp is guaranteed for 1000 burning hours. This means that lamps from the series to which this lamp belongs will burn, on average, for 1000 hours. Some lamps may fail earlier or even much earlier while others may burn longer.

The failure rate  $\lambda(t)$  is defined as the fraction of failing systems per unit of time relative to the total number of systems functioning properly at time  $t$ . The failure rate appears to be constant during a large part of the system's lifetime. If the failure rate is constant in terms of time, it is equal to the inverse of the MTTF.

**Example 1.9**

Suppose an electronic component has an MTTF equal to 10<sup>5</sup> hours. Its failure rate is the inverse,  $10^{-5}$  per hour or 0.024% per day or 0.7% per month. Thus, if one takes a certain collection of correctly functioning components 0.024% will fail daily.

The failure rate of electronic components is extremely low when used under normal conditions. For example, the failure rate of metal film resistors with respect to an open connection is approximately  $5 \times 10^{-9}$  per hour. The reliability of many electronic components is well known. However, it is very difficult to determine the reliability of a complete electronic measurement system from the failure rates of the individual components. This is a reason why the reliability of complex systems is seldom specified.

## SUMMARY

### System functions

- The three main functions of an electronic measurement system are

- data acquisition

- data processing

- data distribution

- The conversion of information of a physical quantity into an electrical signal is known as transduction. Transduction is carried out with an input transducer or sensor. The inverse process is carried out with an output transducer or actuator

- The main operations completed with analog measurement signals are: amplification, filtering, modulation, demodulation and analog-to-digital conversion.

- AD conversion comprises three elements: sampling, quantization and coding.

- Multiplexing is a technique that facilitates the simultaneous transport of various signals through a single channel. There are two different possible ways of doing this: by time multiplexing and by frequency multiplexing. The inverse process is called demultiplexing.

### System specifications

- The main specifications of any measurement system are: operating range (including measuring range), resolution, accuracy, inaccuracy, sensitivity, non-linearity, offset, drift and reliability.

- Some possible types of non-linearity are: saturation, clipping, dead zone, hysteresis and slew rate limitation.

- The bandwidth of a system is the frequency span between frequencies where the power transfer has dropped to half the nominal value or where the voltage or current transfer has dropped to  $\frac{1}{2}\sqrt{2}$  of the nominal value.

- The common-mode rejection ratio is the ratio between the transfer of differential mode signals and common mode signals, or: the ratio between a common mode input and a differential mode input, both producing equal outputs.

- Noise is the phenomenon of spontaneous voltage or current fluctuations occurring in any electronic system. It fundamentally limits the accuracy of a measurement system.

- The reliability of a system can be specified in terms of the reliability  $R(t)$ , the failure rate  $\lambda(t)$  and the mean-time-to-failure MTTF. For systems with constant failure rate,  $\lambda = 1/\text{MTTF}$ .

## EXERCISES

### System functions

- 1.1 What is meant by multiplexing? Describe the process of time multiplexing.

- 1.2 Discuss the difference between the requirements for a multiplexer used for digital signals and one used for analog signals.

- 1.3 Compare an AD converter in a centralized system with that of a distributed system from the point of view of the conversion time.

### System specifications

- 1.4 What would be the reason for putting a factor  $1/\sqrt{2}$  in the definition of the bandwidth for voltage transfer, instead of a factor  $\frac{1}{2}$ ?

- 1.5 What is a differential voltage amplifier? What is meant by the CMRR of such an amplifier?

- 1.6 The CMRR of a differential voltage amplifier is specified as  $\text{CMRR} > 10^3$ , its voltage gain is  $G = 50$ . The two input voltages have values  $V_1 = 10.3 \text{ V}$ ,  $V_2 = 10.1 \text{ V}$ . What is the possible output voltage range?

- 1.7 The slew rate of a voltage amplifier is  $10 \text{ V}/\mu\text{s}$ , its gain is 100. The input is a sinusoidal voltage with amplitude  $A$  and frequency  $f$ .

- a. Suppose  $A = 100 \text{ mV}$ , what would be the upper limit of the frequency where the output would show no distortion?

- b. Suppose  $f = 1 \text{ MHz}$ ; up to what amplitude can the input signal be amplified without introducing distortion?

- 1.8 A voltage amplifier is specified as follows: input offset voltage at  $20^\circ\text{C}$  is  $< 0.5 \text{ mV}$ , the temperature coefficient of the offset is  $< 5 \text{ } \mu\text{V}/\text{K}$ . Calculate the maximum input offset that might occur within a temperature range of 0 to  $80^\circ\text{C}$ .

- 1.9 The relation between the input quantity  $x$  and the output quantity  $y$  of a system is given as:  $y = \alpha x + \beta x^2$ , with  $\alpha = 10$  and  $\beta = 0.2$ . Find the non-linearity relative to the line  $y = \alpha x$ , for the input range  $-10 < x < 10$ .

# 2 Signals

Physical quantities that contain detectable messages are known as signals. The information carrier in any electrical signal is a voltage, a current, a charge or some other kind of electric parameter.

The message contained in such a signal may constitute the result of a measurement but it can also be an instruction or a location code (like, for instance, the address of a memory location). The nature of the message cannot be deduced from its appearance. The processing techniques for electronic signals are as they are, regardless of the contents or nature of the message.

The first part of this chapter will concentrate on the characterization of signals and the various values of signals in terms of time functions. Signals may alternatively be characterized according to their frequency spectrum. In the case of periodic signals, the frequency spectrum is determined by means of Fourier expansion.

The second part of this chapter deals with aperiodic signals, in particular: noise, stochastic and sampled signals.

## 2.1 Periodic signals

### 2.1.1 A classification of signals

There are many ways to classify signals but one way is on the basis of their dynamic properties.

- Static or DC signals (DC = direct current, a term that is also applied to voltages): the signal value remains constant during the measuring time interval.

- Quasi-static signals: the signal value varies just a little, according to a given physical quantity. An example of a quasi-static signal is drift.

- Dynamic signals: the signal value varies significantly during the observation period. Such signals are also termed AC signals (AC = alternating current or alternating voltages).

Another way to distinguish signals is on the basis of the difference between deterministic and stochastic signals. What characterizes a stochastic signal is the fact that its exact value is impossible to predict. Most measurement signals and interference signals, such as noise, belong to this category. Examples of deterministic signals are:

- Periodic signals, characterized as  $x(t) = x(t + nT)$ , in which  $T$  is the time of a signal period and  $n$  the integer.

- Transients, like the response of a system to a pulse-shaped input: the signal can be repeated (in other words predicted) by repeating the experiment under the same conditions.

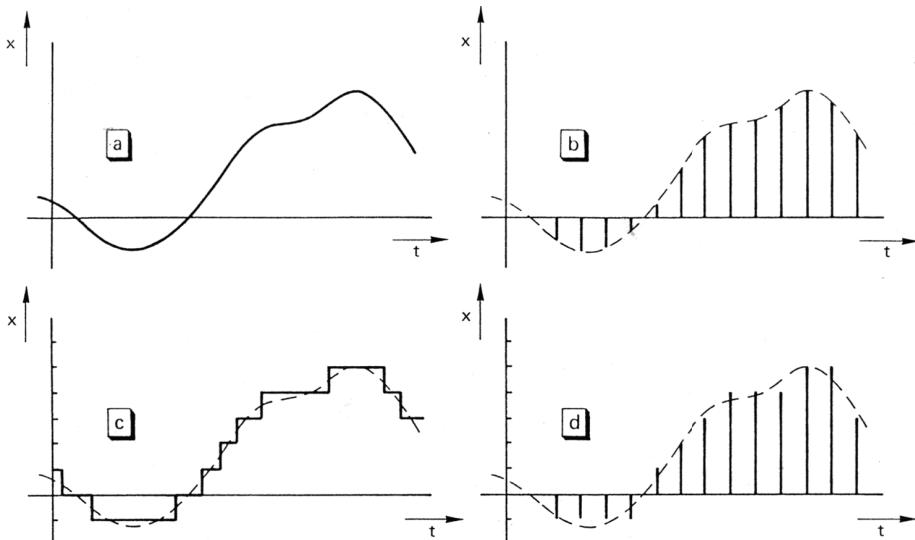

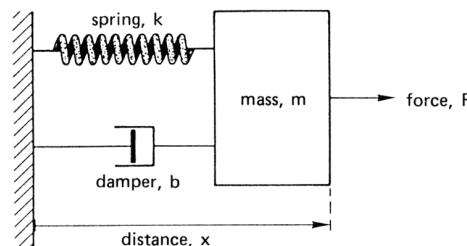

A third possibility is to consider continuous and discrete signals. The continuity may refer both to the time scale and to the amplitude scale (the signal value). Figure 2.1 shows the four possible combinations. Figure 2.1b represents a sampled signal and Figure 2.1c illustrates a quantized signal, as mentioned in Chapter 1. A quantized signal that only has two levels is called a binary signal.

Finally, we shall contemplate the distinction between analog and digital signals. As with many technical terms (especially electronic terms) the meaning here becomes rather fuzzy. In ordinary terms, digital signals are sampled, time-discrete and binary-coded, as in digital processors. Analog signals refer to time-continuous signals that have a continuous or quantized amplitude.

Figure 2.1. Continuous and discrete signals: (a) continuous in time and in amplitude, (b) time discrete, continuous amplitude (sampled signal), (c) discrete amplitude, continuous in time (quantized signal), (d) discrete both in time and amplitude.

### 2.1.2 Signal values

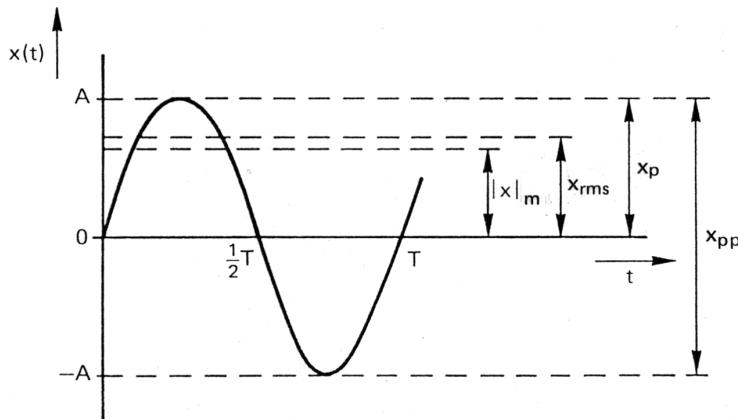

Amplitude-time diagrams of the type given in Figure 2.1, which represent the signal value for each moment within the observation interval, are the most complete kinds of signal descriptions. Invariably it is not necessary to give that much information about the signal; a mere indication of a particular signal property would suffice. Some such simple characteristic signal parameters are listed below. The parameters are valid for an observation interval  $0 < t < \tau$ .

peak value:

$$x_p = \max \{ |x(t)| \}$$

peak-to-peak value:  $x_{pp} = \max\{x(t)\} - \min\{x(t)\}$

mean value:  $x_m = \frac{1}{\tau} \int_0^{\tau} x(t) dt$

mean absolute value:  $|x|_m = \frac{1}{\tau} \int_0^{\tau} |x(t)| dt$

root-mean-square value:  $x_{eff} = \sqrt{\frac{1}{\tau} \int_0^{\tau} x^2(t) dt}$

mean signal power:  $P_m = \frac{1}{\tau} \int_0^{\tau} x^2(t) dt$

The peak and peak-to-peak values are important in relation to the limits of the signal range of an instrument. The mean value is used when it is only the DC or quasi-DC component of a signal that counts. The rms value is a parameter related to the signal power content. An arbitrarily shaped AC current with an rms value of  $I$  (A) which flows through a resistor will produce just as much heat as a DC current with a (DC) value of  $I$  (A). Note that the rms value is the square root of the mean power.

**Example 2.1**

The mathematical description of a sinusoidal signal is:

$$x(t) = A \sin \omega t = A \sin \frac{2\pi}{T} t$$

where  $A$  is the amplitude,  $f = \omega/2\pi$  the frequency and  $T = 1/f$  the period time. Figure 2.2 shows one period of this signal while illustrating the characteristic parameters defined above. If these definitions are applied to the sine wave this will result in the following values:

$$x_p = A$$

$$x_{pp} = 2A$$

$$|x|_m = \frac{2A}{\pi}$$

$$x_{rms} = \frac{1}{2} A \sqrt{2}$$

As the shapes of all periods are equal these values also apply to a full periodical sine wave.

Figure 2.2. Signal values for a sine wave signal.

Many rms voltmeters do not actually measure the rms value of the input signal but rather the mean of the absolute value,  $|x|_m$ , which can be realized with the aid of a very simple electronic circuit. The two values are not, however, the same. To obtain an rms indication such instruments have to be calibrated in terms of rms. Since both signal parameters depend on the signal shape the calibration will only be valid for the particular signal used while calibrating. Generally, rms meters are calibrated for sinusoidal inputs. Example 2.1 shows that the mean absolute value should be multiplied (internally) by  $\frac{1}{4}\pi\sqrt{2}$ , about 1.11, to obtain the rms value. Such instruments only indicate the proper rms value for sine shaped signals.

Some voltmeters indicate the "true rms" value of the input voltage. A true rms meter functions differently from those described above. Some of them use a thermal converter to directly obtain the rms value of the input signal. The indication is true for almost all types of input voltages.

### 2.1.3 Signal spectra

Any periodic signal can be divided into a series of sinusoidal sub-signals. If the time of one period is  $T$ , then the frequencies of all the sub-signals will be multiples of  $1/T$ . There are no components with other frequencies. The lowest frequency which is equal to  $1/T$  is known as the fundamental frequency of the signal.

The subdividing of a periodic signal into its sinusoidal components is known as "Fourier expansion of the signal". The resultant series of sinusoids is thus a Fourier series. Fourier expansion can be described mathematically as follows:

$$\begin{aligned}

x(t) &= a_0 + a_1 \cos \omega_0 t + a_2 \cos 2\omega_0 t + a_3 \cos 3\omega_0 t + \dots \\

&\quad + b_1 \sin \omega_0 t + b_2 \sin 2\omega_0 t + b_3 \sin 3\omega_0 t + \dots \\

&= a_0 + \sum_{n=1}^{\infty} (a_n \cos n\omega_0 t + b_n \sin n\omega_0 t) \\

&= a_0 + \sum_{n=1}^{\infty} c_n \cos(n\omega_0 t + \varphi_n)

\end{aligned} \tag{2.1}$$

These three representations are identical; the second is an abbreviated form of the first. In the third representation the corresponding sine and cosine terms are combined in a single cosine with the new amplitude  $c$  and the phase angle  $\varphi$ , which satisfies the relations:

$$c_n = \sqrt{a_n^2 + b_n^2} \quad \varphi_n = \arctan(b_n/a_n) \quad (2.2)$$

The coefficients  $a_n$ ,  $b_n$  and  $c_n$  are the Fourier coefficients of the signal. Each periodic signal can be written as a collection of sinusoidal signals with amplitudes given by the Fourier coefficients and frequencies that are multiples of the fundamental signal frequency.

The term  $a_0$  in Equation (2.1) is nothing other than the mean value of the signal  $x(t)$ : the mean value must be equal to that of the complete series, and the mean of each sine signal is zero. All sine and cosine terms of the Fourier series have a frequency that is a multiple of the fundamental,  $f_0$ ; they are termed the harmonic components or the signal (i.e. if the signal were made audible by a loudspeaker a perfect "harmonic" sound would be heard). The component with a frequency of  $2f_0$  is the second harmonic,  $3f_0$  is the third harmonic, and so on.

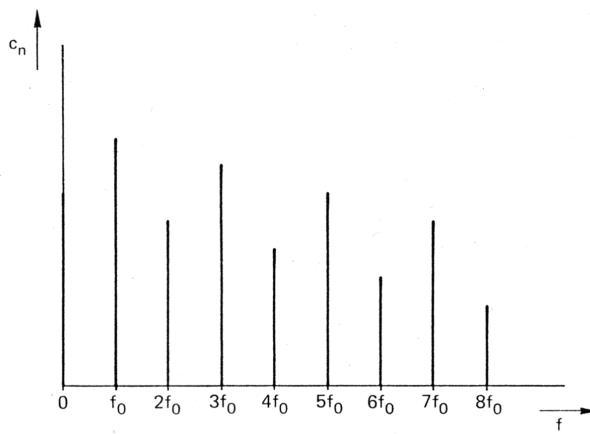

The shape of a periodic signal is reflected in its Fourier coefficients. We can illustrate the Fourier coefficients as a function of the corresponding frequency. Such a diagram is called the frequency spectrum of the signal (Figure 2.3). Usually the amplitude of the combined sine and cosine terms is plotted so that the coefficient is  $c_n$  as in Equation (2.1).

The Fourier coefficients are related to the signal shape. They can be calculated using the transformation formulas given in Equations (2.3):

$$\begin{aligned} a_0 &= \frac{1}{T} \int_{t_0}^{t_0+T} x(t) dt \\ a_n &= \frac{2}{T} \int_{t_0}^{t_0+T} x(t) \cos n\omega_0 t dt \\ b_n &= \frac{2}{T} \int_{t_0}^{t_0+T} x(t) \sin n\omega_0 t dt \end{aligned} \quad (2.3)$$

Figure 2.3. An example of a frequency spectrum of a periodic signal.

These equations present the discrete Fourier transform for real coefficients. In general, the Fourier series has an infinite length. The full description of a signal, according to its spectrum, requires an infinite number of parameters. Fortunately, the coefficients tend to diminish when frequencies increase. One remarkable property of the coefficients is that the first  $N$  elements of the series constitute the best approximation of the signal in  $N$  parameters.

**Example 2.2**

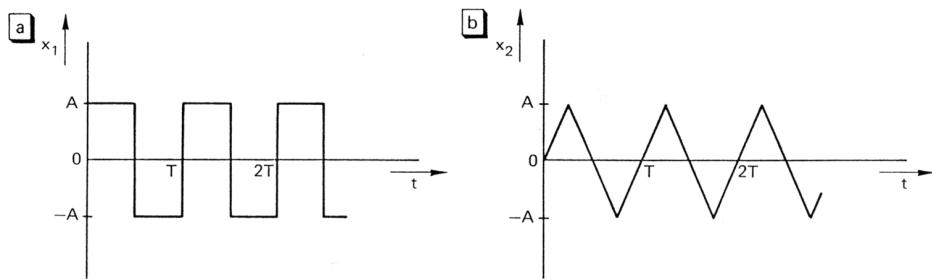

The Fourier coefficients of the square-shaped signal given in Figure 2.4a, calculated with Equations (2.3), are:

$$a_0 = 0$$

$$a_n = 0$$

$$b_n = \frac{2A}{n\pi} (1 - \cos n\pi)$$

Apparently, its Fourier series is described as:

$$x_1(t) = \frac{4A}{\pi} \left( \sin \omega_0 t + \frac{1}{3} \sin 3\omega_0 t + \frac{1}{5} \sin 5\omega_0 t + \dots \right)$$

The signal appears to be composed only of sinusoids with frequencies that are odd multiples of the fundamental frequency.

Figure 2.4. Examples of two periodical signals: (a) a square wave signal, (b) a triangular signal.

**Example 2.3**

Using the same transformation formulas, the frequency spectrum of the triangular signal in Figure 2.4b is calculated as:

$$x_2(t) = \frac{8A}{\pi^2} \left( \sin \omega_0 t - \frac{1}{9} \sin 3\omega_0 t + \frac{1}{25} \sin 5\omega_0 t + \dots \right)$$

and consists of components that have exactly the same frequencies, but different amplitudes.

According to the theory of Fourier, any periodic signal can be split up into sinusoidal components with discrete frequencies. The signal in question has a discrete frequency spectrum or a line spectrum. Obviously, one can also create an arbitrary periodic signal by adding the required sinusoidal signals with the proper frequencies and amplitudes. This particular composition of periodic signals is used in synthesizers.

The Fourier transform is also applicable to aperiodic signals. It appears that such signals have a continuous frequency spectrum. A continuous spectrum does not have any individual components, but the signal is expressed in terms of amplitude density rather than amplitude. A more usual way of presenting a signal is according to its power spectrum, that is, its spectral power (W/Hz) as a function of frequency.

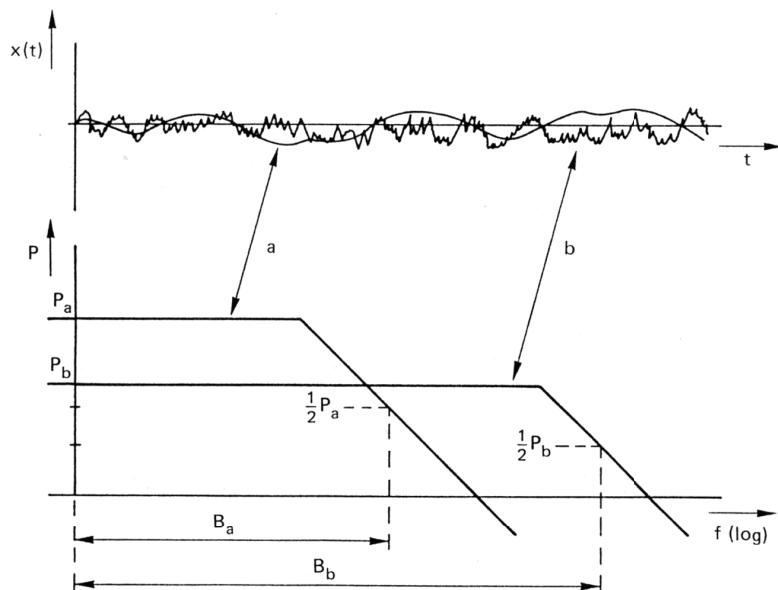

Figure 2.5 shows the power spectra of two different signals. One signal varies gradually over the course of time while the other is much faster. One can imagine the first signal being composed of sinusoidal signals with relatively low frequencies. Signal (b) contains components with frequencies that are higher. This is clearly illustrated in the corresponding frequency spectra of the signals: the spectrum of signal (a) covers a small range of frequency and its bandwidth is low. Signal (b) has a much wider bandwidth.

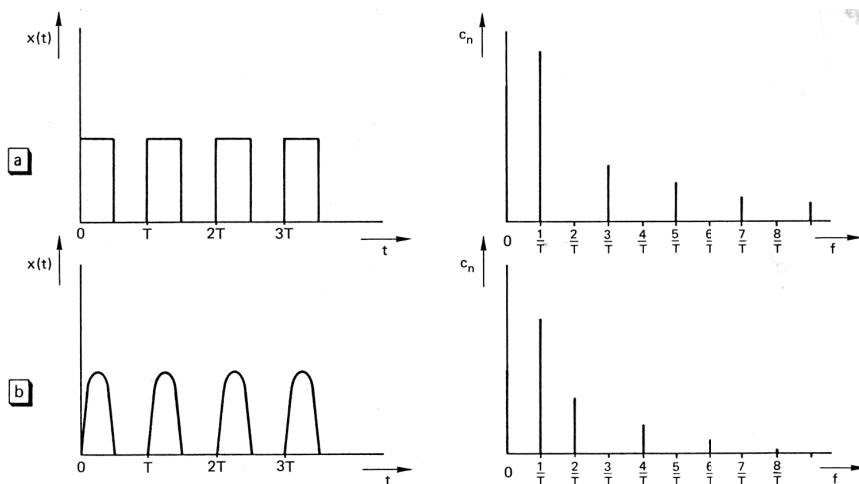

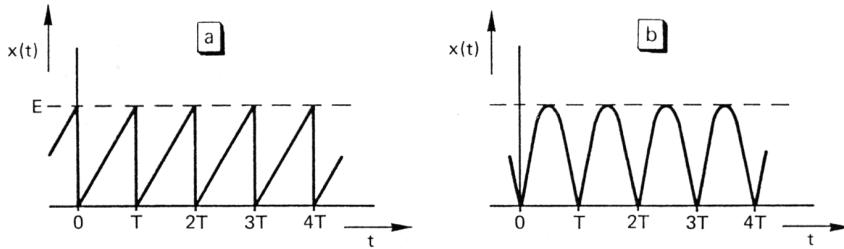

The relationship between the signal shape (time domain) and its spectrum (frequency domain) is also illustrated in Figure 2.6 which shows the spectrum of two periodic signals, one with very sharp edges (the rectangular signal) and another that does not vary so quickly (a rectified sine wave). Clearly the high frequency components of the rectangular wave are much larger than those of the clipped sine wave.

Figure 2.5. The amplitude-time diagram of two signals a and b, and the corresponding power spectra. Signal a varies slowly, and has a narrow bandwidth. Signal b moves quickly; it has a larger bandwidth.

Figure 2.6. The amplitude-time diagram and the frequency spectrum of (a) a rectangular signal, (b) the positive half of a sine wave.

The bandwidth of a signal is defined in a similar way to that for systems. The bandwidth is the part of the signal spectrum found between the frequencies where the power spectrum has dropped to half of its nominal or maximal value. In the case of an amplitude spectrum the boundaries are defined at  $1/\sqrt{2}$  of the nominal amplitude density.

A measurement system can only cope with signals that have a bandwidth up to that of the system itself. Signals with high frequency components require a wideband processing system. The bandwidth of the measuring instrument should correspond to that of the signals being processed.

Randomly varying signals or noise also have continuous frequency spectra. Some types of noise (in particular thermal induced electrical noise) have constant spectral power  $P_n$  (W/Hz) where, up to a certain maximum frequency, the power spectrum is flat. Like white light, such signals are called white noise and contain equal wavelength components (colors) within the visible range. Noise can also be specified as spectral voltage or spectral current, expressed respectively in V/ $\sqrt{\text{Hz}}$  and A/ $\sqrt{\text{Hz}}$ .

**Example 2.4**

Let the respective spectral power, spectral voltage and spectral current density of white noise be  $P_n$  W/Hz,  $V_n$  V/ $\sqrt{\text{Hz}}$  and  $I_n$  A/ $\sqrt{\text{Hz}}$ . The noise power, noise voltage and noise current of this signal, measured within a frequency band of 200 to 300 Hz amount to:  $100 \cdot P_n$  W,  $10 \cdot V_n$  V and  $10 \cdot I_n$  A.

## 2.2 Aperiodic signals

In this section we shall extend the Fourier expansion definition to include aperiodic signals and use the result to deduce the spectrum of sampled signals. Stochastic signals (whether they be continuous or discrete) can be described in three ways: according to their time domain properties (e.g. time average, rms value), their frequency domain properties (amplitude spectrum, power spectrum) or their amplitude properties (expressing the signal value with probability parameters).

### 2.2.1 Complex Fourier series

In the first part of this chapter we showed how the Fourier expansion of a periodic signal can lead to a series of (real) sine and cosine functions. The complex Fourier expansion was established using Euler's relation

$$e^{\pm jz} = \cos z \pm j \sin z \quad (2.4)$$

Solving  $\sin z$  and  $\cos z$ , and replacing the real goniometric functions in (2.1) with their complex counterparts we obtain:

$$x(t) = a_0 + \sum_{n=1}^{\infty} \left[ \frac{a_n}{2} (e^{jn\omega t} + e^{-jn\omega t}) + \frac{b_n}{2j} (e^{jn\omega t} - e^{-jn\omega t}) \right] \quad (2.5)$$

Using the substitutions  $C_0 = a_0$ ,  $C_n = \frac{1}{2}(a_n - jb_n)$  and  $C_{-n} = \frac{1}{2}(a_n + jb_n)$  this can be simplified to

$$x(t) = C_0 + \sum_{n=1}^{\infty} (C_n e^{jn\omega t} + C_{-n} e^{-jn\omega t}) = \sum_{n=-\infty}^{\infty} C_n e^{jn\omega t} \quad (2.6)$$

What this results in is the complex Fourier series. Similarly, the complex form of Equations (2.3) becomes:

$$C_n = \frac{1}{T} \int_{t_0}^{t_0+T} x(t) e^{-jn\omega t} dt \quad n = 0, 1, 2, \dots \quad (2.7)$$

the discrete complex Fourier transform. The complex Fourier coefficients  $C_n$  can easily be derived from the real coefficients using the relations

$$\begin{aligned} |C_n| &= \frac{1}{2} \sqrt{a_n^2 + b_n^2} \quad n \neq 0 \\ \arg C_n &= \arctan \frac{-b_n}{a_n} \end{aligned} \quad (2.8)$$

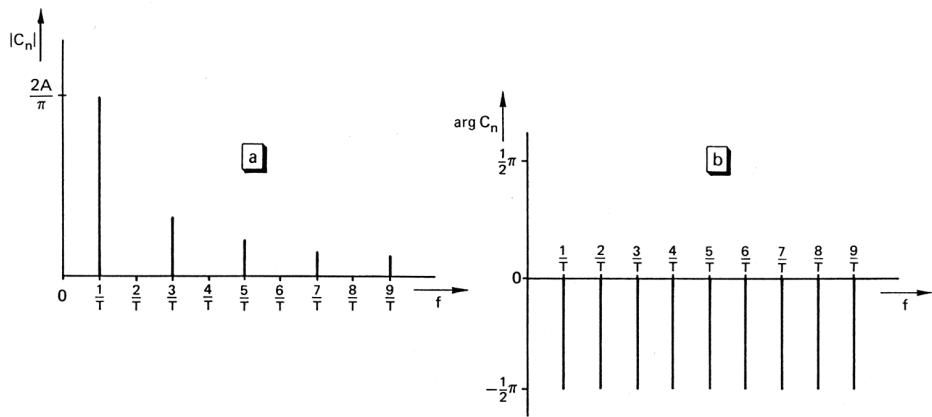

As  $C_n$  is complex, the complex signal spectrum consists of two parts: the amplitude spectrum – a plot of  $|C_n|$  versus frequency and the phase spectrum, a plot of  $\arg C_n$  versus frequency.

**Example 2.5**

The complex Fourier series of the rectangular signal in Figure 2.4a is calculated as follows:  $C_0 = 0$ , so  $|C_0| = 0$  and  $\arg C_0 = 0$ . As  $C_n = \frac{1}{2}(a_n - jb_n)$ , its modulus and argument are:

$$|C_n| = \frac{1}{2} \sqrt{a_n^2 + b_n^2} = \frac{A}{n\pi} (1 - \cos n\pi) \quad n = 1, 2, \dots$$

and

$$\arg C_n = \arctan \frac{-b_n}{a_n} = -\frac{\pi}{2} \quad n = 1, 2, \dots$$

The amplitude and phase spectra are depicted in Figure 2.7.

Figure 2.7. (a) amplitude spectrum and (b) phase spectrum of the rectangular signal from Figure 2.4a.

### 2.2.2 The Fourier integral and the Fourier transform

To obtain the Fourier expansion of a non-periodic signal we start with the discrete complex Fourier series for periodic signals as given in Equations (2.6) and (2.7). Consider one period of this signal. Replace  $t_0$  with  $-\frac{1}{2}T$  and let  $T$  approach infinity. Then:

$$x(t) = \lim_{T \rightarrow \infty} \sum_{n=-\infty}^{\infty} C_n e^{jn\omega t} = \lim_{T \rightarrow \infty} \sum_{n=-\infty}^{\infty} e^{jn\omega t} \left( \frac{1}{T} \int_{-\frac{1}{2}T}^{\frac{1}{2}T} x(t) e^{-j\omega nt} dt \right) \quad (2.9)$$

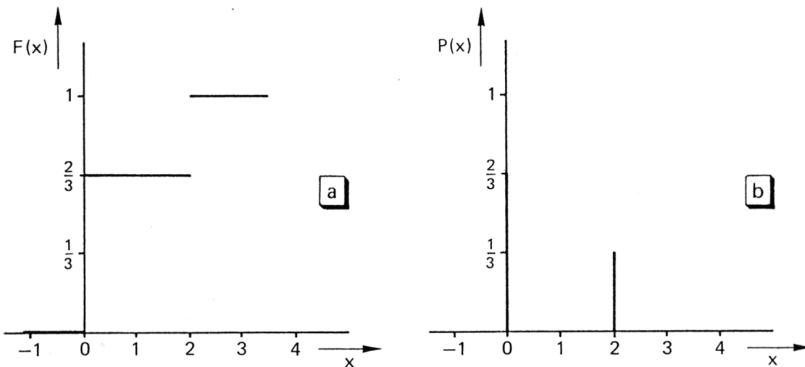

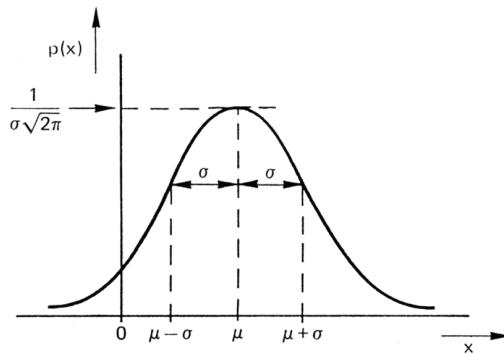

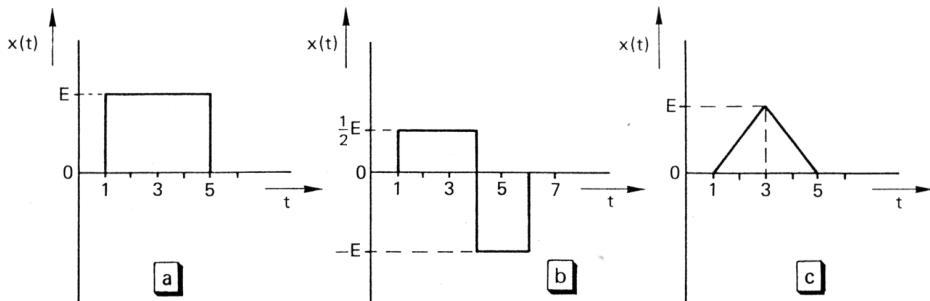

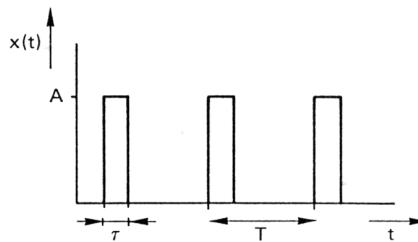

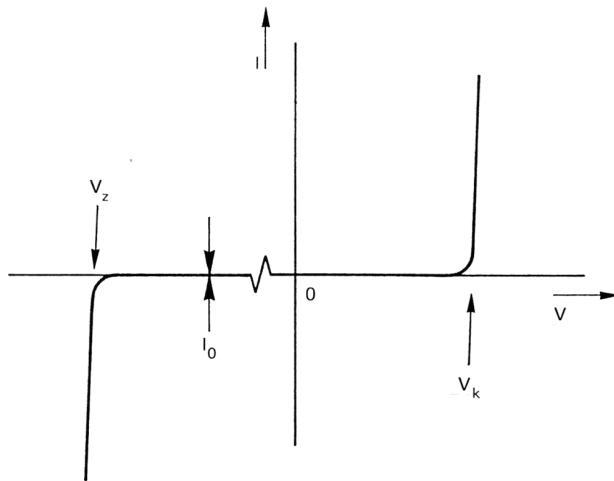

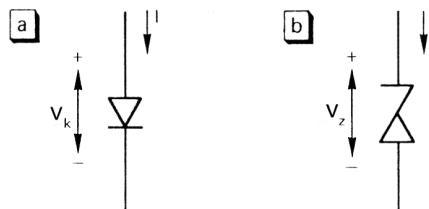

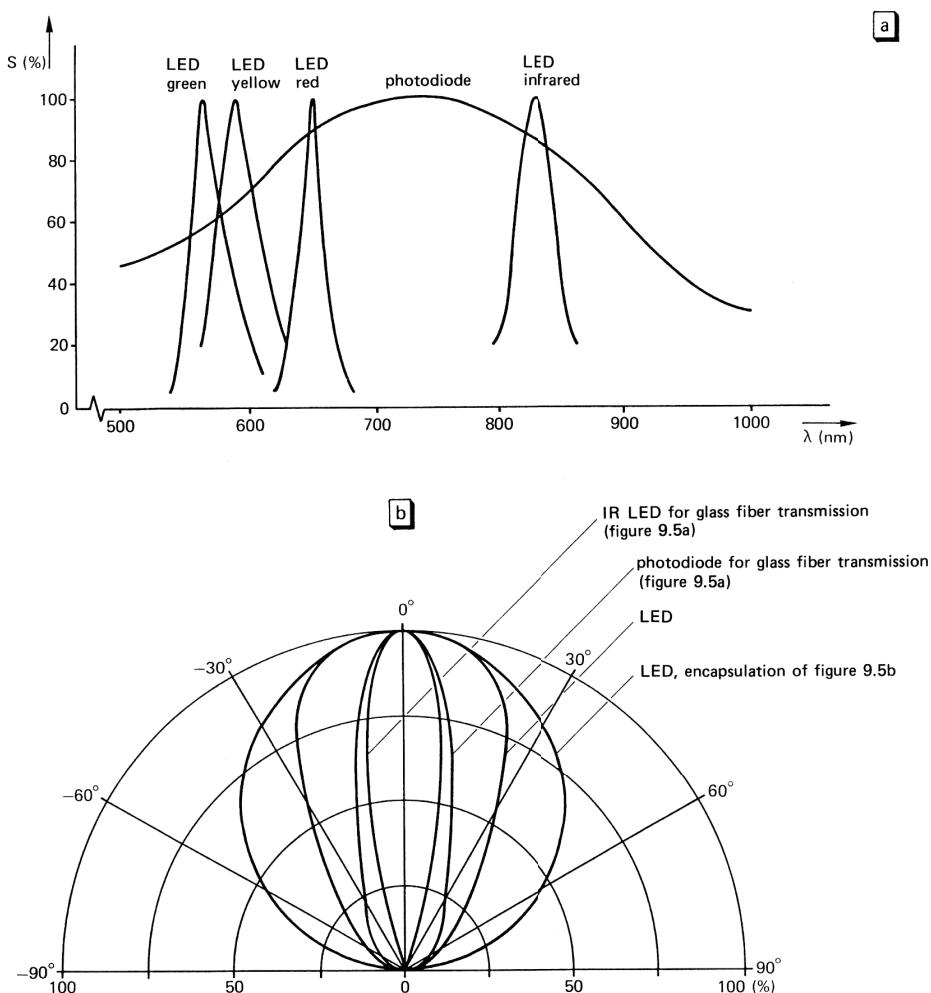

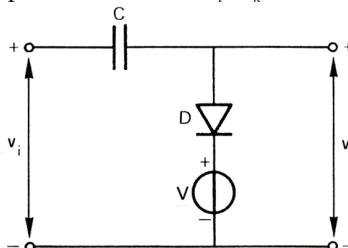

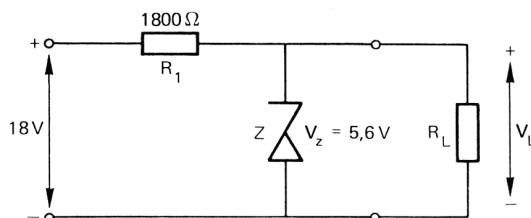

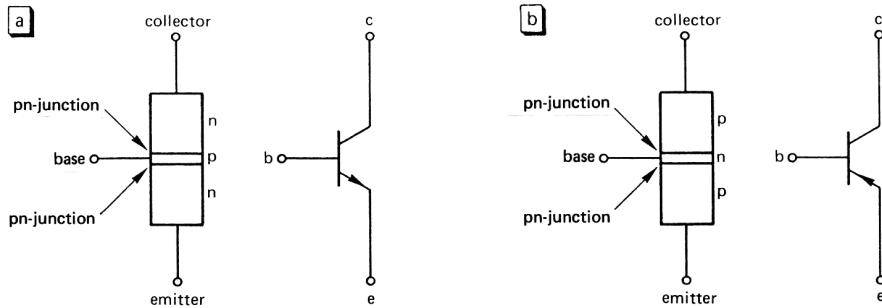

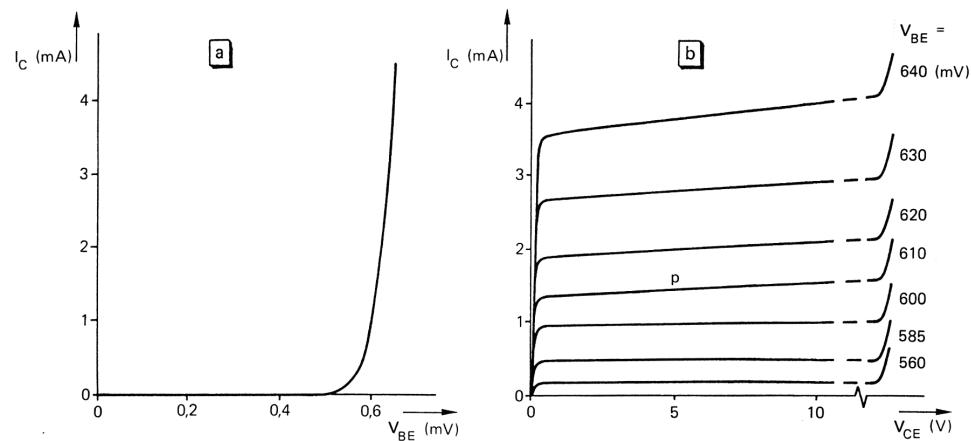

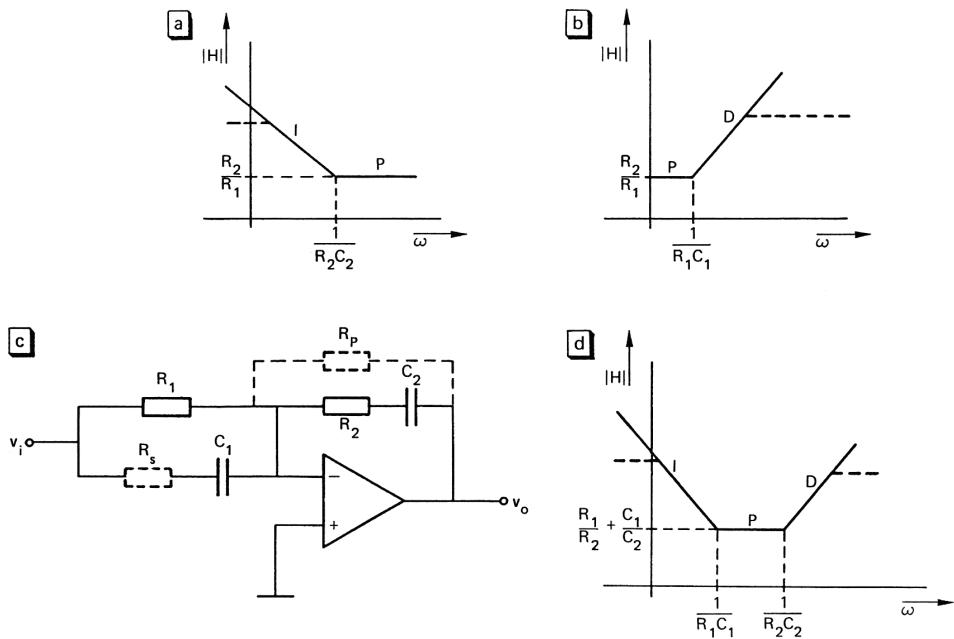

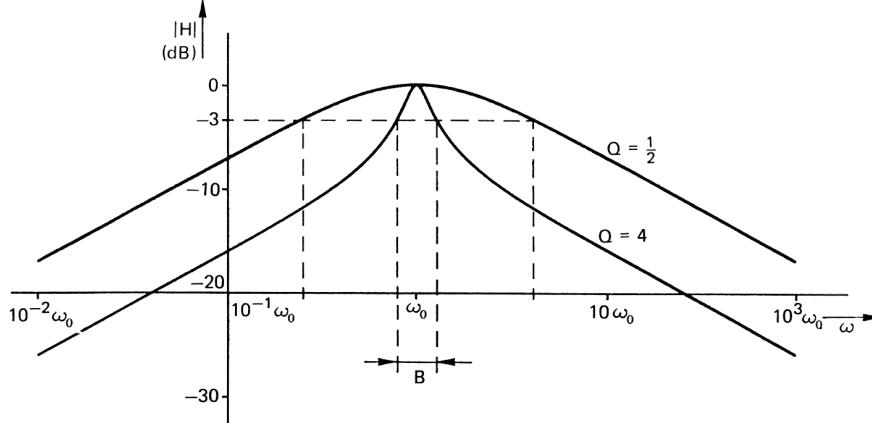

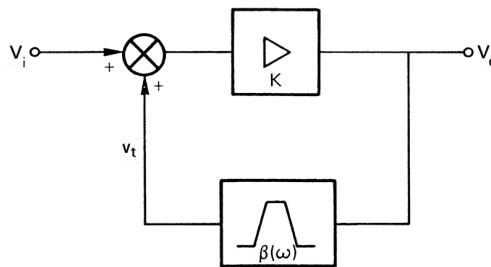

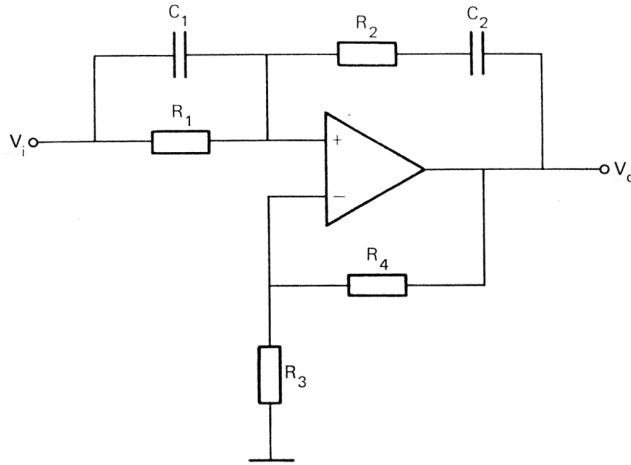

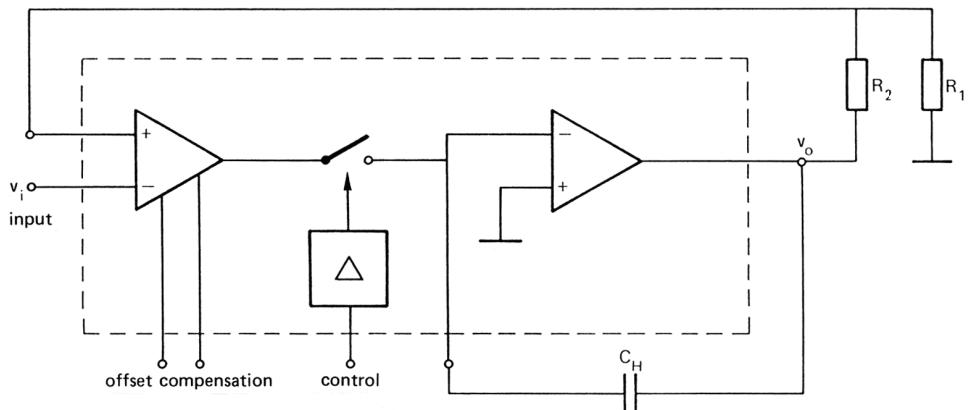

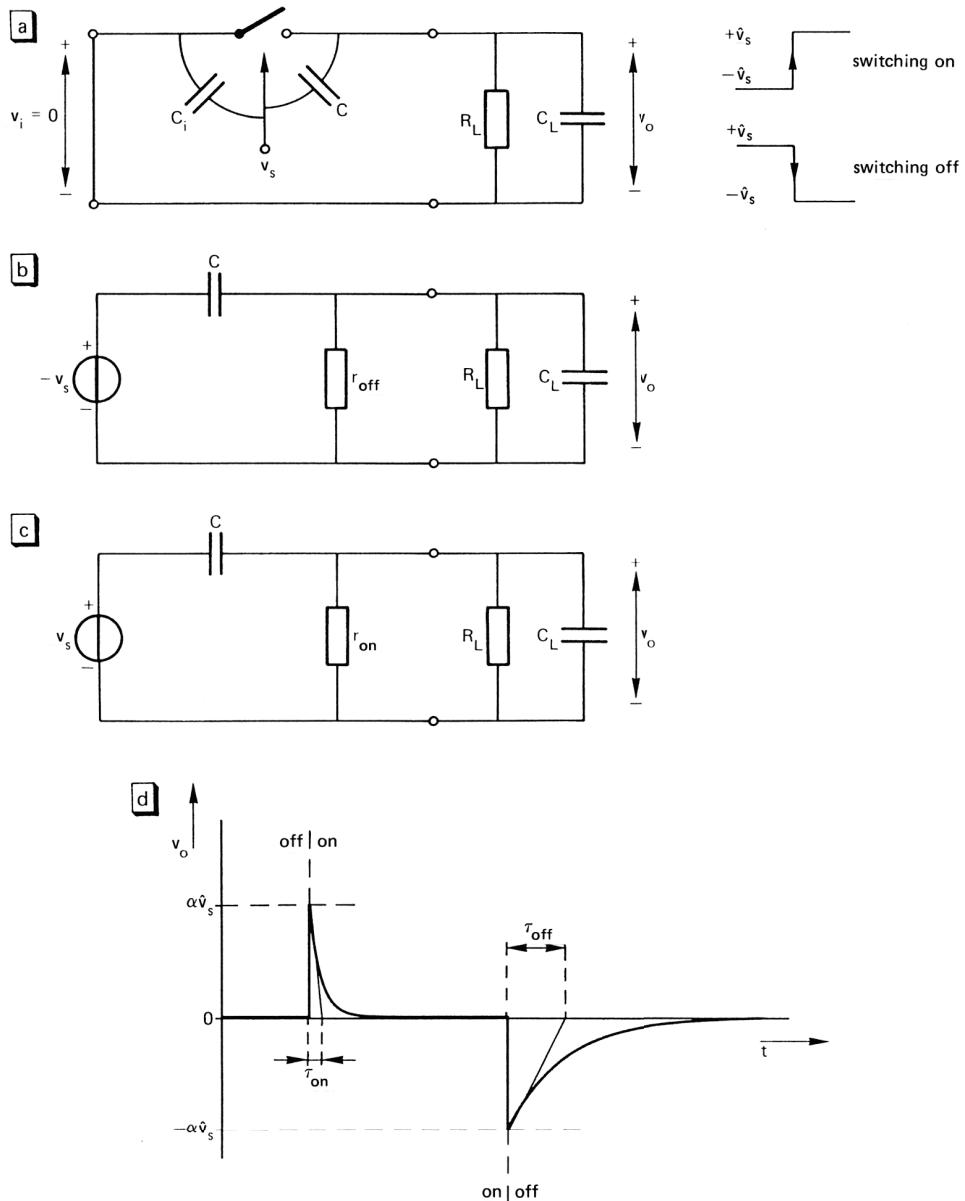

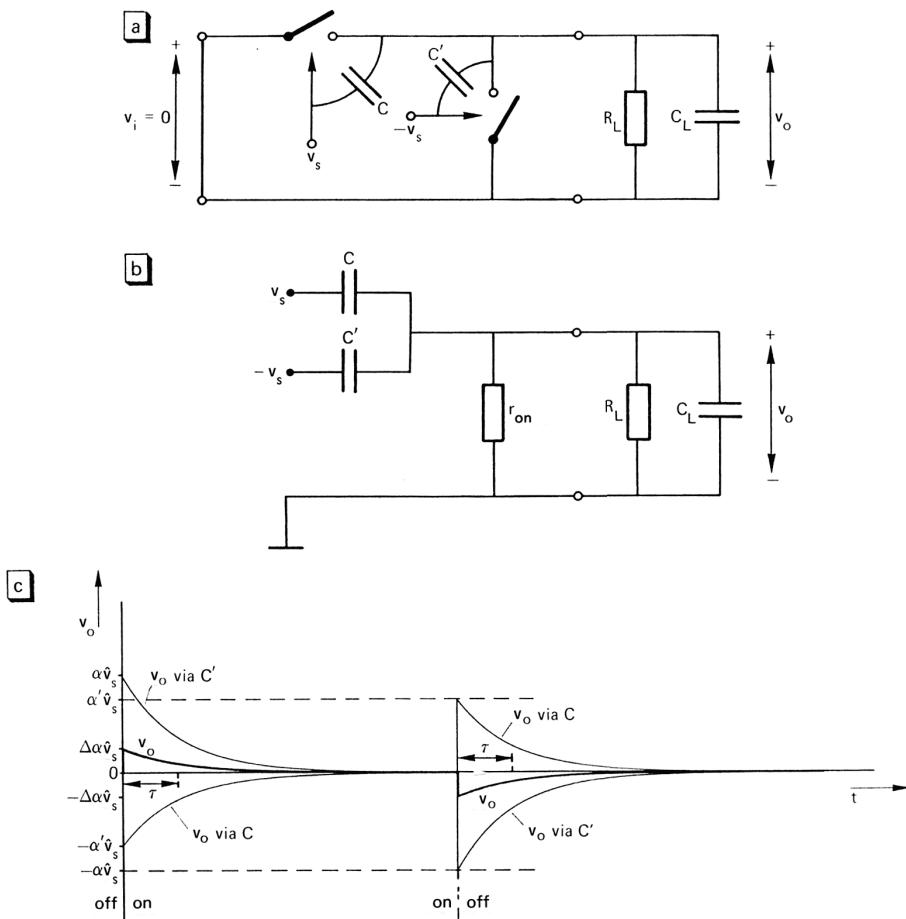

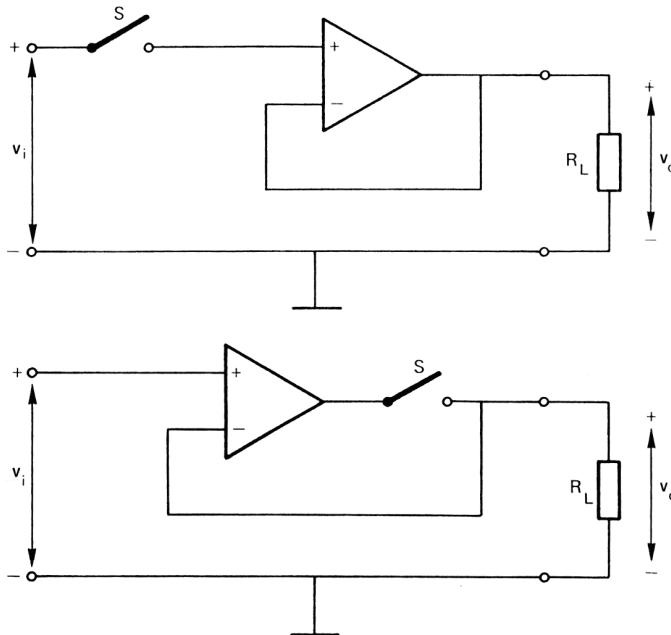

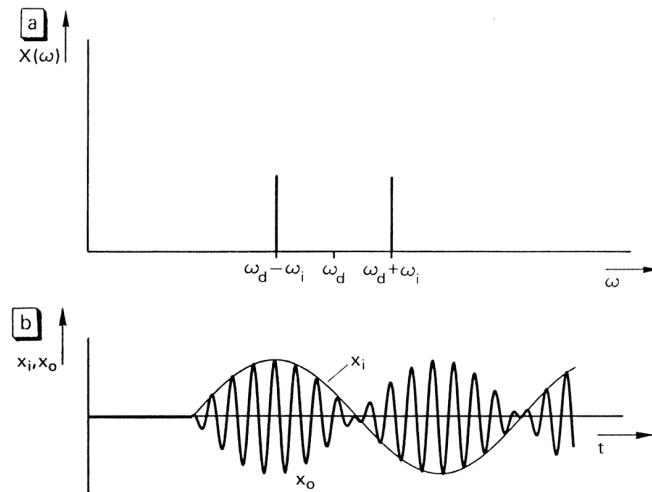

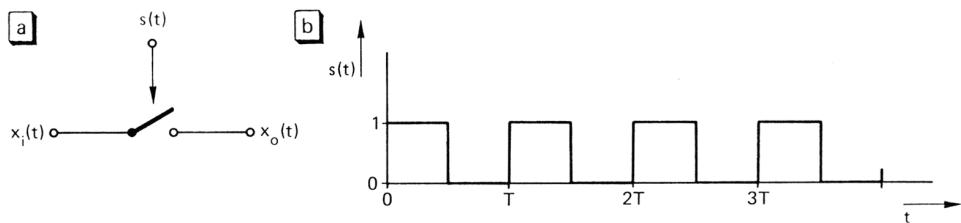

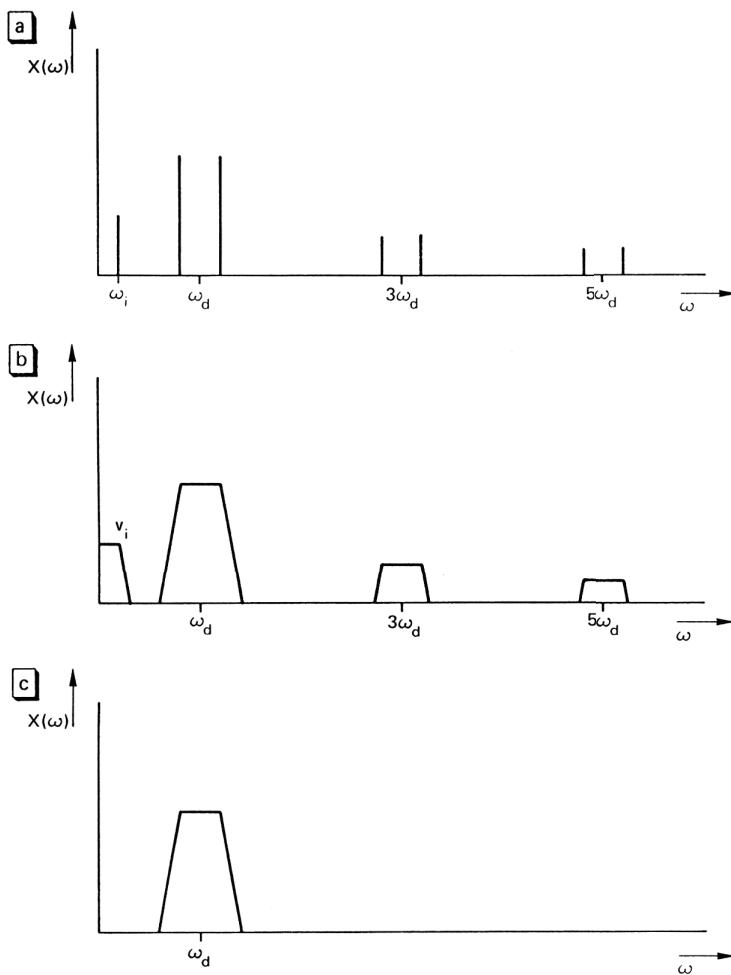

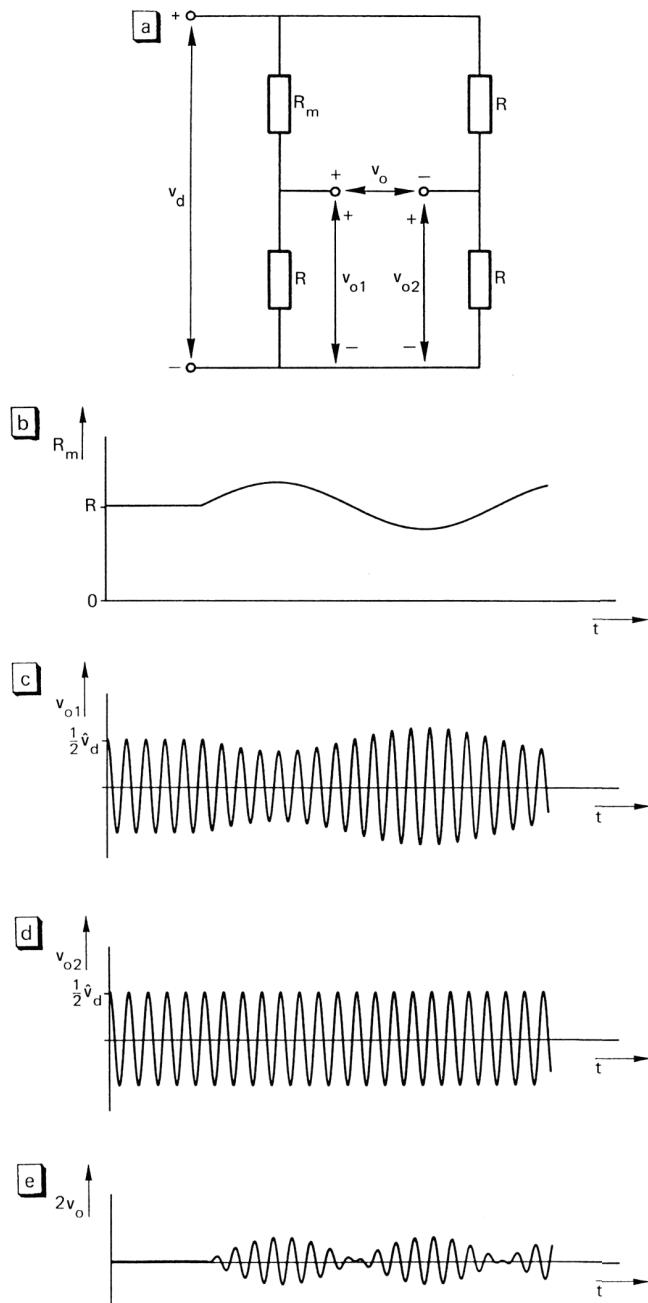

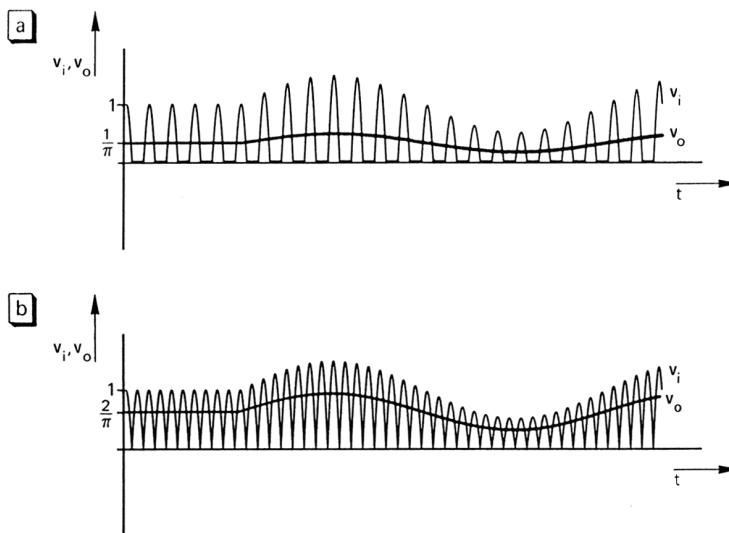

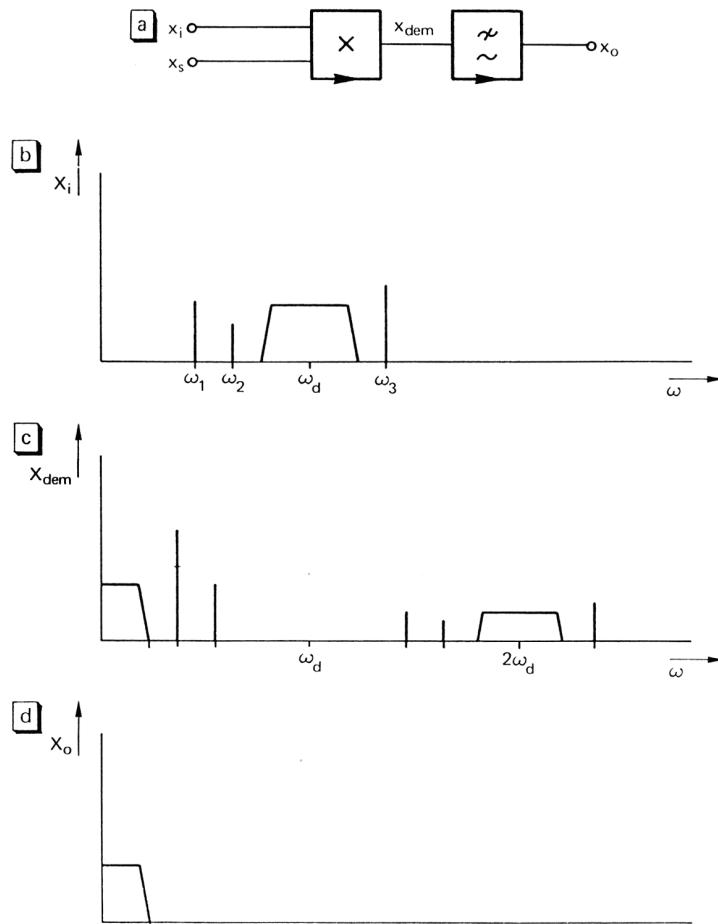

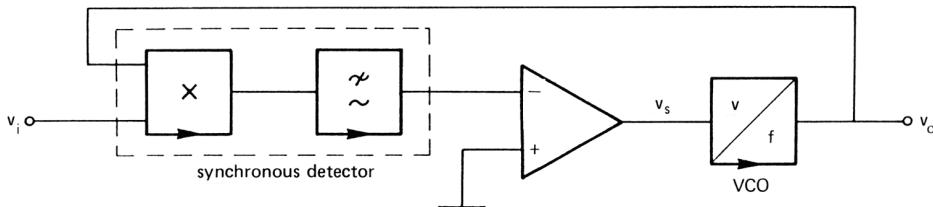

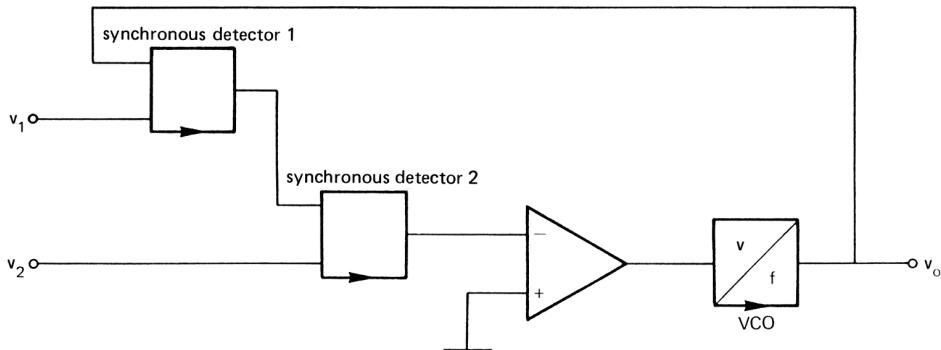

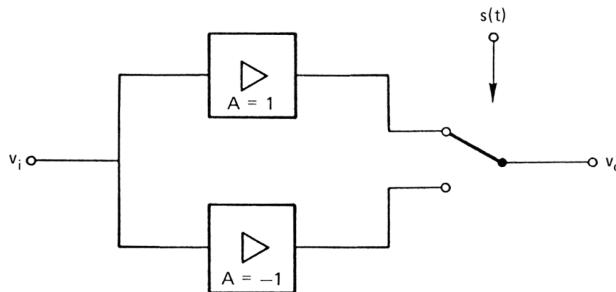

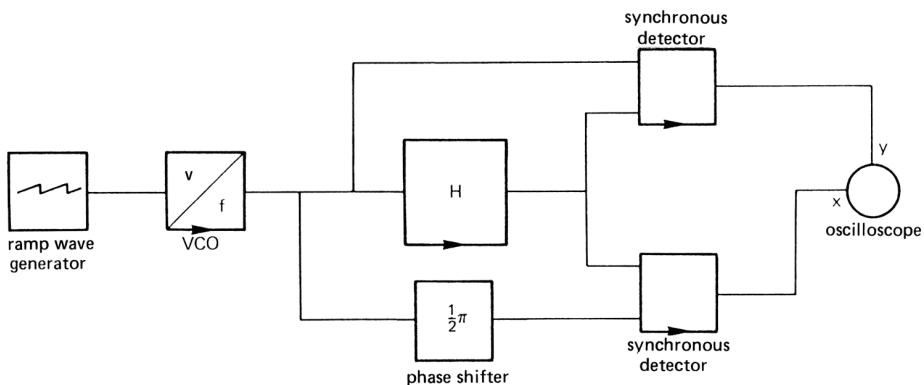

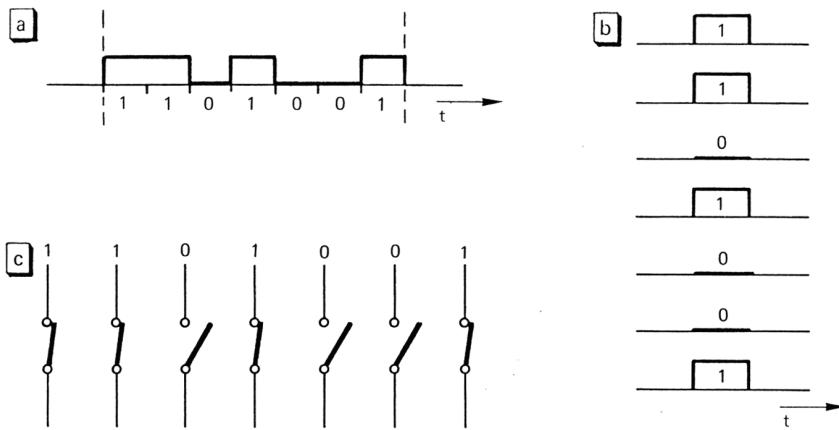

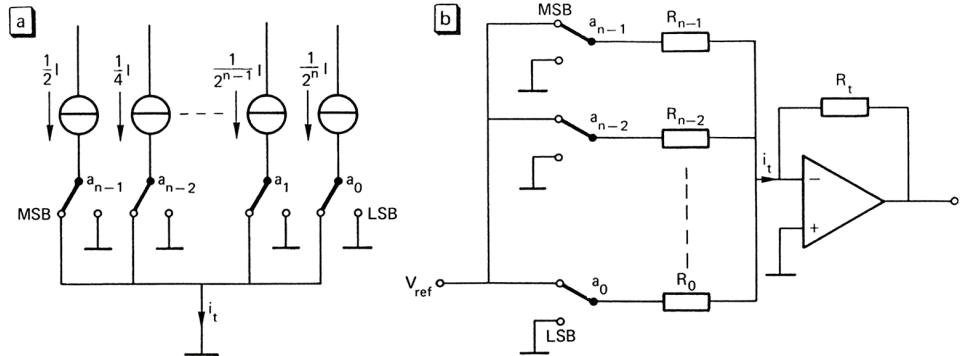

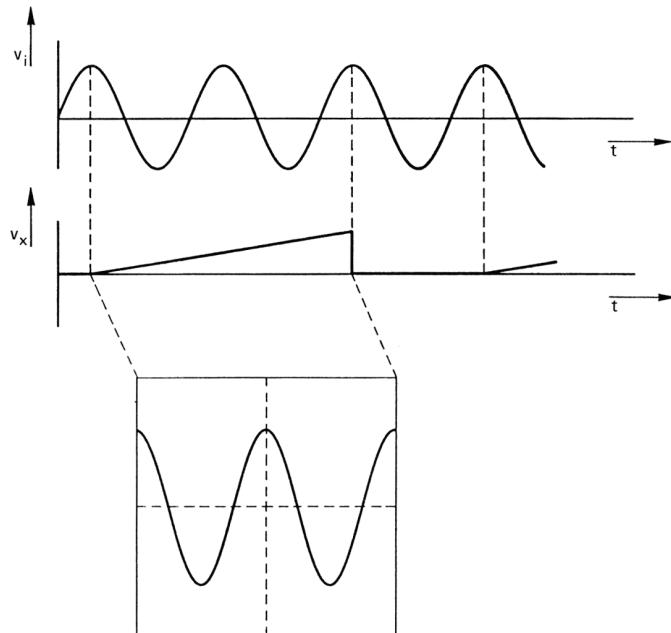

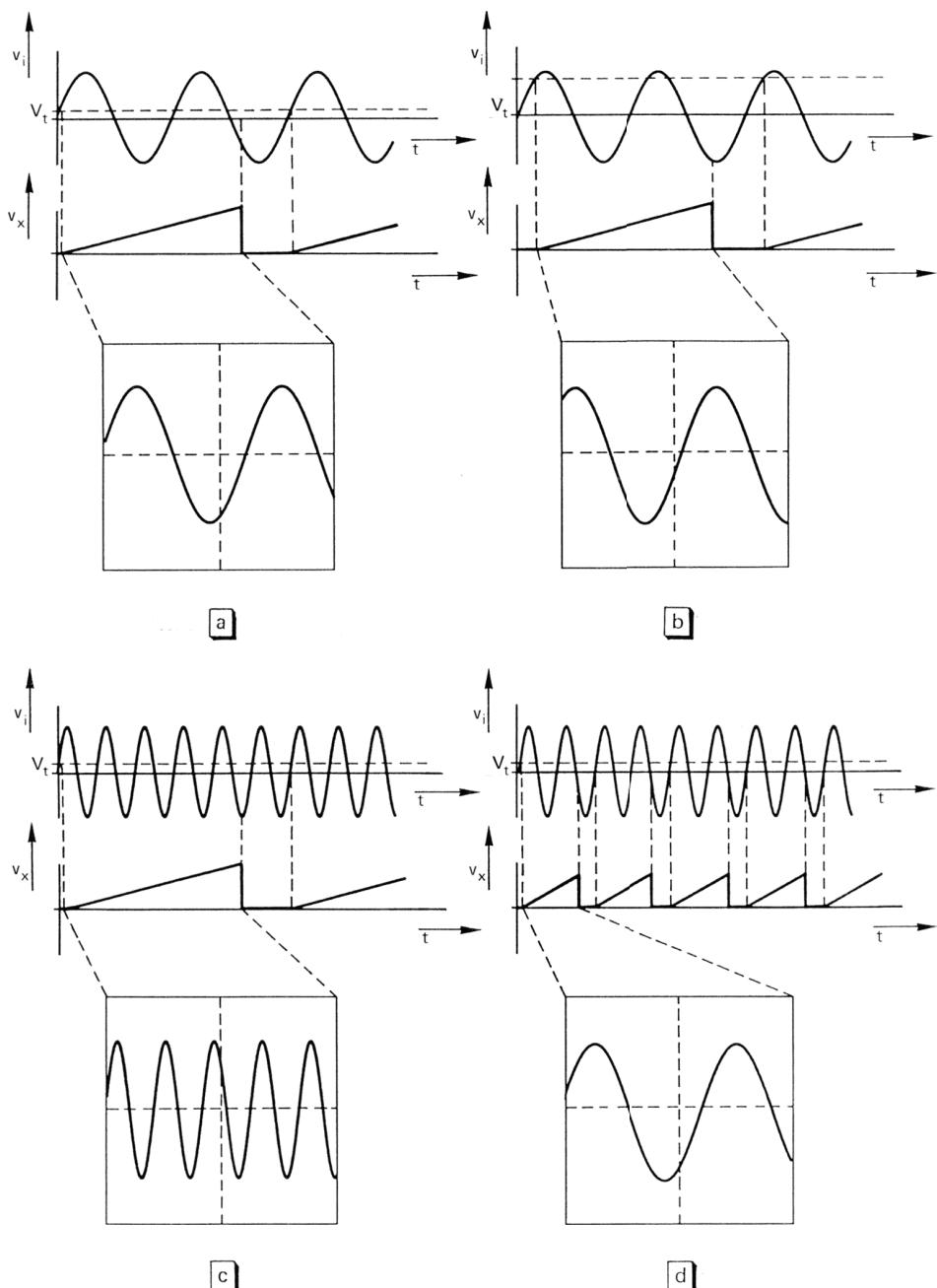

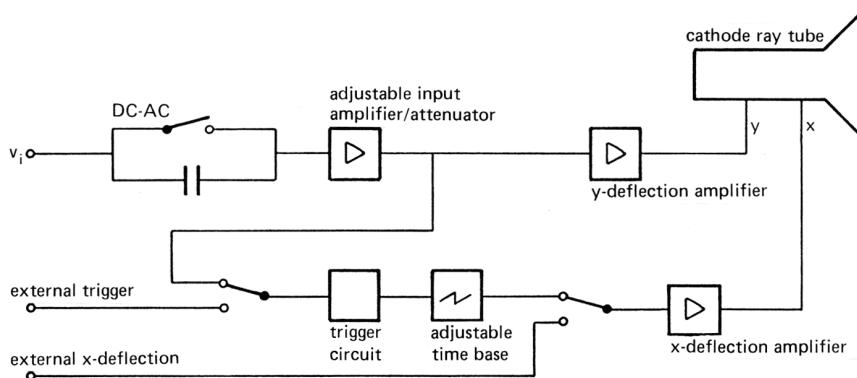

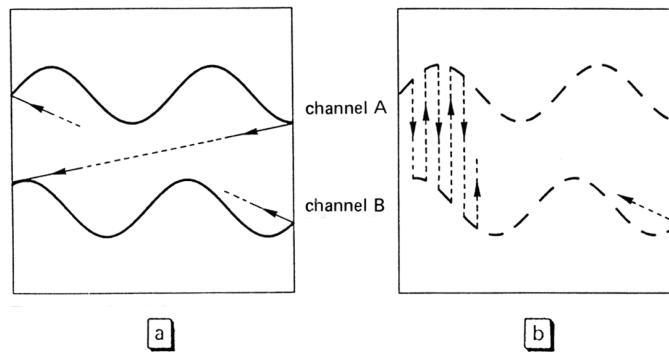

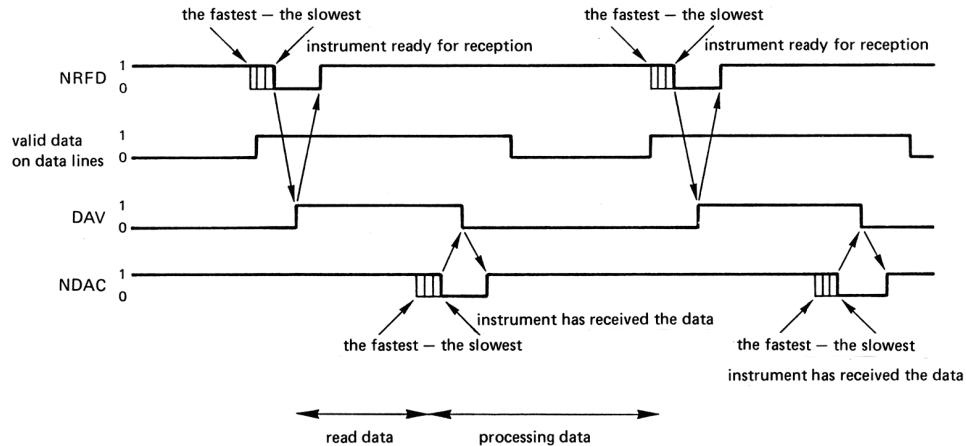

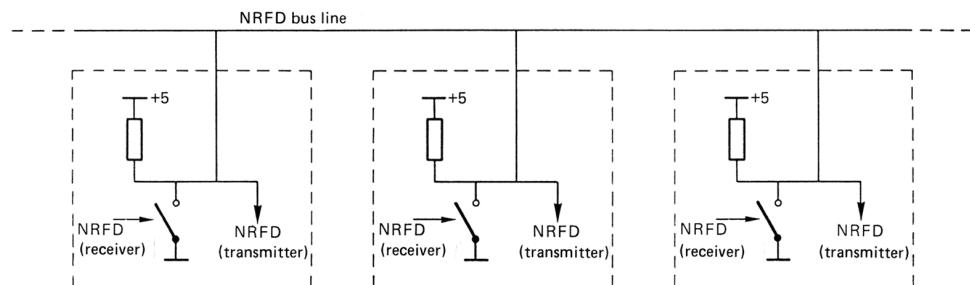

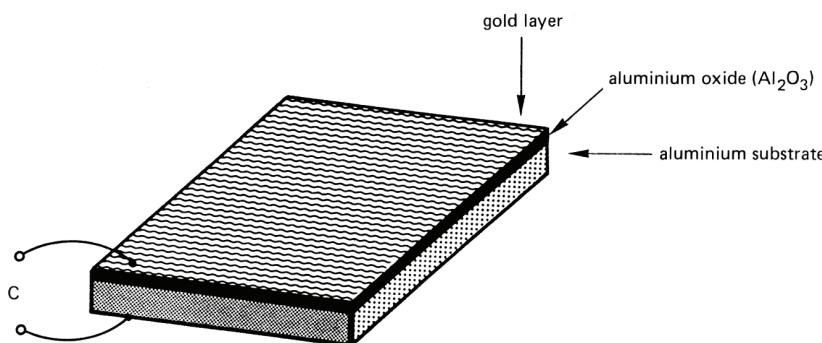

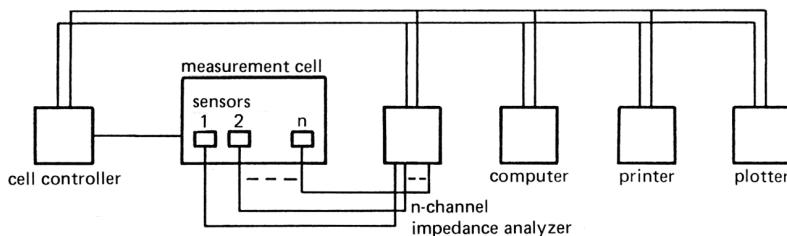

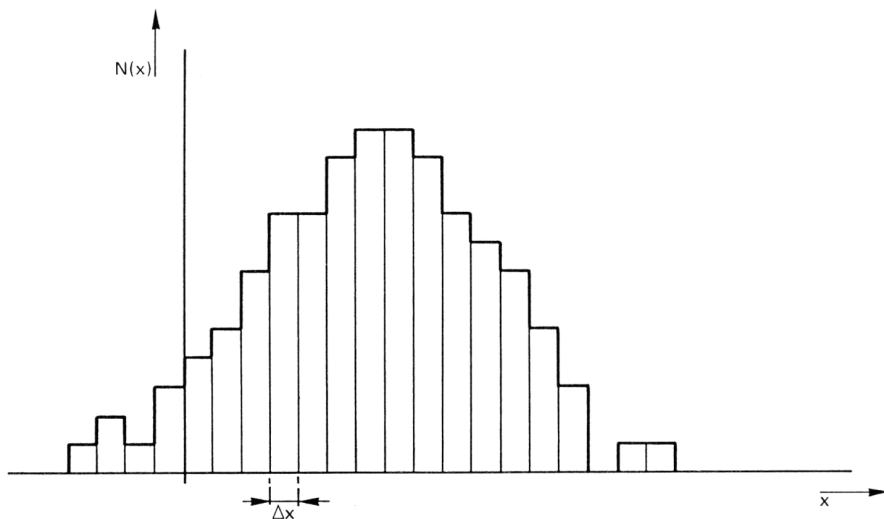

When taking the limit for  $T \rightarrow \infty$ , the summation becomes an integration,  $n\omega$  changes to  $\omega$  and  $T = (1/2\pi)\omega$  becomes  $(1/2\pi)d\omega$ :