# **Yield and Cost Analysis for 3D Stacked ICs**

Mottaqiallah Taouil

# **Yield and Cost Analysis for 3D Stacked ICs**

---

## **Proefschrift**

ter verkrijging van de graad van doctor

aan de Technische Universiteit Delft,

op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben,

voorzitter van het College van Promoties,

in het openbaar te verdedigen op

vrijdag 5 september 2014, om 12:30 uur

door

Mottaqiallah TAOUIL

Master of Science in Computer Engineering

geboren te Al Hoceima, Marokko

Dit proefschrift is goedgekeurd door de promotor:

**Prof. dr. K.L.M. Bertels**

Copromotor:

**Dr. ir. S. Hamdioui**

Samenstelling van de promotiecommissie:

|                              |                                                    |

|------------------------------|----------------------------------------------------|

| Rector Magnificus            | voorzitter                                         |

| Prof. dr. K.L.M. Bertels     | Technische Universiteit Delft, promotor            |

| Dr. ir. S. Hamdioui          | Technische Universiteit Delft, copromotor          |

| Prof. dr. E. Charbon         | Technische Universiteit Delft, The Netherlands     |

| Prof. dr. K. Chakrabarty     | Duke University, USA                               |

| Ir. E.J. Marinissen PDEng    | IMEC, Belgium                                      |

| Dr. ir. H.G. Kerkhoff        | University of Twente, the Netherlands              |

| Prof. dr. J. Pineda de Gyvez | Technische Universiteit Eindhoven, the Netherlands |

| Prof. dr. ir. H.J. Sips      | Technische Universiteit Delft, reserve lid         |

This work has been supported by 3DIM<sup>3</sup> via grants to Delft University of Technology.

ISBN 978-94-6186-331-7

Published and distributed by: Mottaqiallah Taouil

Email: mo\_taouil@hotmail.com

Subject headings: 3D stacked ICs, cost analysis, yield analysis, redundancy, fault coverage, test cost, test analysis, fault coverage, interconnect testing, and interconnect diagnoses

Copyright © 2014 by Mottaqiallah Taouil

mo\_taouil@hotmail.com

All rights reserved. No part of this book may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior permission of the author.

Printed in the Netherlands

*Dedicated to my parents and my wife

for all the support they have been giving me.*

# Summary

3D stacking is an emerging technology promising many benefits such as low latency between stacked dies, reduced power consumption, high bandwidth communication, improved form factor and package volume density, heterogeneous integration, and low-cost manufacturing. However, it requires modification of existing methods and/or introduction of new ones with respect to design, manufacturing, and testing in order to facilitate production. In this thesis three challenges are addressed: one related to manufacturing (i.e., yield improvement) and two related to testing (i.e., cost modeling and interconnect testing).

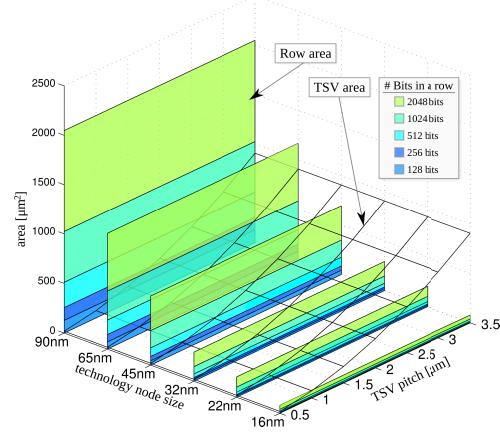

**Yield improvement** - We propose two yield improvement schemes applicable for 3D Stacked-ICs (3D-SICs) with similar die sizes (such as memories and FPGAs): wafer matching and layer redundancy. Wafer matching is based on algorithms that select wafers with identical or similar fault maps for stacking to boost the compound yield. Our algorithms outperform yield-wise previously proposed schemes, and more importantly reduce memory and time complexity significantly. On the other hand, redundancy in 3D memories makes use not only of conventional spare rows and columns, but also of the third dimension to access either spare dies (layer redundancy) or spare cells (inter-layer redundancy). Layer redundancy showed to be effective from a yield point of view, but may seriously affect die area and cost. Inter-layer redundancy realizes even higher yield improvements; however, it requires through-silicon vias (TSVs) to scale down with one order of magnitude for area-efficient implementations.

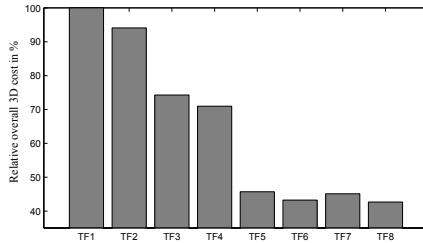

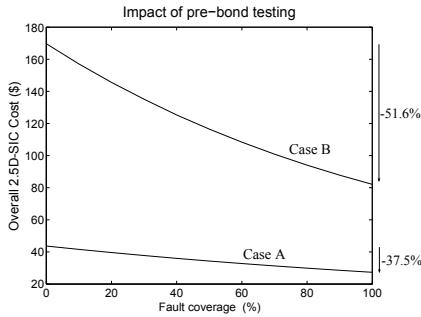

**Cost Modeling** - Selecting an appropriate and efficient test flow for 2.5D/3D SICs is crucial for overall cost optimization. In addition, diverse products and applications require different quality levels resulting in different test flows; these flows may require different design-for-test (DfT) features, which need to be incorporated in the various dies during an early design stage. Therefore, an appropriate cost model used to evaluate test flows with their associated DfT, while taking into account yields and die production costs, is of great importance. A proper cost modeling tool for 2.5D/3D stacked ICs is developed; the tool is referred to as 3D-COSTAR. It considers all costs involved in the whole production chain, including design, manufacturing, test, packaging, and logistics, e.g., related to shipping wafers between a foundry and a test house. 3D-COSTAR provides the estimated overall cost for 2.5D/3D-SICs and its cost breakdown for a given input parameter set, such as test flows, die yield, stack yield etc. The crucial importance of 3D-COSTAR is demonstrated by analyzing trade-offs of different complex optimization test problems such as (a) the impact of test coverage of the pre-bond silicon interposer test, (b) the impact of pre-bond testing of active dies using either dedicated probe-pads or micro-bumps, (c) the impact of mid-bond testing and logistics, and (d) the impact of different test flows on the test escapes.

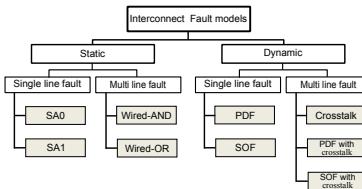

**Interconnect Testing** - A potential application of 3D-SICs is stacking of memory on logic. However, testing the TSV interconnects between such dies is challenging, as the memory and the logic die typically come from different manufacturers. Currently, proposed solutions fail to address dynamic and time-critical faults. In addition, memory vendors have in the past not been in favor to put additional DFT structures such as IEEE 1149.1 for interconnect testing on their memory devices. We propose a new Memory-Based Interconnect Test (MBIT) approach for 3D stacked memories. Our test patterns are applied by using read and write instructions to the memory and are validated by a case study where a 3D memory is assumed to be stacked on a MIPS64 processor. The main benefits of the MBIT approach include zero area overhead, detection of both static and dynamic faults, at-speed testing, flexibility, extremely short test time, and interconnect fault diagnosis.

# Samenvatting

Het 3D stapelen van IC's is een opkomende technologie die vele voordelen met zich mee brengt, zoals een lage latency tussen gestapelde chips, gereduceerde energieverbruik, hoge communicatie bandbreedte, verbeterde form factor en package volume dichtheid, heterogene integratie en lage productiekosten. Echter vereist dit het wijzigingen van bestaande methoden en/of de invoering van nieuwe methoden met betrekking tot het ontwerp, de fabricage en het testen om de commerciële productie te vergemakkelijken. In dit proefschrift worden drie uitdagingen geadresseerd: één ervan verwant aan productie (d.w.z. yield verbetering) en twee verwant aan testen (d.w.z. kostenmodellering en het testen van interconnects).

**Yield verbetering** - Wij stellen twee yield verbeteringsschema's voor die van toepassing zijn op 3D-Stacked IC's (3D-SIC's) met soortgelijke chip oppervlakte (zoals geheugens en FPGAs). Dit zijn wafer matching en layer redundancy. Wafer matching is gebaseerd op algoritmes waarin wafers met identieke of soortgelijke chip defect locaties geselecteerd worden voor het stapelen, dit om de yield te boosten. Onze algoritmes presteren yieldsgewijs beter dan vorige voorgestelde schema's, maar belangrijker nog is de significante reductie in geheugen- en tijds-complexiteit. Anderzijds, redundantie in 3D gestapelde geheugens maakt niet alleen gebruik van de conventionele reserve rijen en kolommen, maar ook van de derde dimensie om ofwel gebruik te maken van reserve chips (layer redundantie) of reserve cellen (inter-layer redundantie). Layer redundantie is vanuit een yield oogpunt effectief, maar kan ernstige gevolgen hebben voor de chip oppervlakte en kosten. Inter-layer redundantie realiseert zelfs een nog hoger rendement; hoewel, dit vereist het neerschalen van through-silicon vias (TSVs) met een orde van grootte voor een area-efficiënte implementatie.

**Kostenmodellering** - Het selecteren van een geschikte en efficiënte test flows voor een 2.5D/3D-SIC is cruciaal voor totale kostenoptimalisatie. Daarnaast vereisen diverse producten en toepassingen verschillende kwaliteitsniveaus wat resulteert in verschillende test flows; deze flows kunnen verschillende design-for-test (DfT) functies vereisen, die in diverse chips moeten worden toegevoegd gedurende de ontwerpfasen. Daarom is een geschikte kostenmodel die gebruikt wordt om test flows met bijbehorende DfT te evalueren, rekening houdend met yield en productiekosten, van groot belang. Een goede kostenmodelleringstool voor 2.5D/3D SIC's is ontwikkeld; de tool wordt aangeduid als 3D-COSTAR. Het beschouwt de kosten van de gehele productieketen, inclusief ontwerp, productie, testen, packaging en logistiek, die bijvoorbeeld betrekking heeft tot de transport van wafers tussen een foundry en een test house. 3D-COSTAR biedt de totale geraamde kosten voor 2.5D/3D-SIC's en de kostenverdeling voor een bepaalde input parameter set, zoals testflows, chip yield, etc. Het cruciale belang van 3D-COSTAR is aangetoond door het analyseren van trade-offs van verschillende complexe testoptimalisatie problemen, zoals (a) de impact van de pre-bond

silicium interposer test, (b) de impact van het pre-bond testen van actieve chips door middel van of probe-pads of micro-bumps, (c) de impact van het mid-bond testen en logistieke kosten en (d) de impact van de verschillende test flows op de test escapes.

**Testen van interconnects** - Een mogelijke toepassing van 3D-SICs is het stapelen van een geheugen op logica. Echter is het testen van de TSV interconnects tussen dergelijke chips moeilijk, omdat de geheugens en logica chips meestal van verschillende fabrikanten komen. Momenteel voldoen de voorgestelde oplossingen voldoen niet aan dynamische en tijdkritieke fouten. Bovendien gaven geheugens leveranciers in het verleden geen voorkeur aan het plaatsen van extra DFT structuren zoals JTAG op hun geheugenapparaten om interconnects te testen. Wij stellen een nieuwe memory Based Interconnect Test (MBIT) aanpak voor 3D gestapelde geheugens. De testpatronen worden uitgevoerd door lees en schrijf instructies naar het geheugen en zijn gevalideerd door een casus waarin verondersteld wordt dat een 3D geheugen wordt gestapeld op een MIPS64 processor. De belangrijkste voordelen van de voorgestelde MBIT aanpak zijn geen extra oppervlakte, detectie van zowel statische als dynamische fouten, testen op normale chip snelheid, flexibiliteit, extreem korte testtijd en de mogelijkheid om interconnect foutdiagnose toe te passen.

# Acknowledgements

After a period of over four years, I can finally say that my Ph.D. dissertation has ended successfully. It has been a unique experience with many ups and downs. Luckily, there has been a great stimulating environment around me (both at home and at work) that facilitated me carrying out this work. I would like to dedicate my acknowledgments to everyone that was part of this environment.

First of all, I would like to thank my co-promotor and daily supervisor Assoc. Prof. dr. ir. S. Hamdioui for providing me the opportunity to pursue my Ph.D. thesis under his guidance. Not only did I learn how to do research and write scientific papers, but also what it means to be a dedicated researcher. Thank you for the continuous motivation and the proper guidance during this work. In addition to properly educating me as an independent researcher, you gave me many opportunities to develop myself further. For instance, the development of lab-courses, giving lectures, organizing IEEE conferences and participating in European Project proposals. Thank you for being my co-promotor! Prof. dr. ir. K.L.M. Bertels, you were more than only a promotor. As main professor and head of our CE laboratory I am very thankful for your efforts in creating a nice atmosphere and working environment in the group. You have always been encouraging us to attend social events, such as Karting, bowling, world cup matches, etc. Further, you always motivated us to maintain a strong network in the group (for example through brainstorm sessions), and not to forget to always provide us with cookies in the coffee room. I would also like to thank the remaining committee members for accepting their role, reading this dissertation, and providing feedback; thank you for all your efforts. Furthermore, I would like to mention several members specifically by name. Ir. E.J. Marinissen PDEng, co-author of many joint publications, I thank you not only for providing constructive feedback for this thesis, but also for the many discussions we had over the years, and not to forget the numerous paper corrections. Your invested time is highly appreciated! Prof. dr. K. Chakrabarty, as part of the same research community I still remember several of our constructive discussions during various conferences regarding 3D, biochips, etc. I really enjoyed them. I am sure that you are very inspiring professor.

I would like to express my gratitude to the Computer Engineering (CE) secretariat and staff for taking care of all the bureaucratic matters related to my day-to-day work. Thank you for always being helpful and for providing the necessary support. Lidwina, thank you for managing all the forms and other secretary-related tasks. Erik and Eef, thank you for creating and keeping the websites updated, managing the servers, fixing computer problems, installing various software, etc.

George, Saleh, Mihai, dr. ir. Demid, Winston, assoc. prof. dr. ir. S. Hamdioui, and assoc. prof. dr. S. Cotofana, thank you for your contributions as member of the CE 3DIM<sup>3</sup> team. The brainstorm sessions have been very fruitful. You have been a great team to work with, always helpful, and open to discussions.

I would like to thank Marius for organizing the CE weekly football matches. These matches provided me very often the right motivation to continue the challenging tasks that laid in front of me. Everyone that participated in these matches, thank you! You are too many to be mentioned by name. Also, special thanks to Andrew, Catalin, Mihai, Mafalda, and Mahroo for organizing various other CE social events. Everyone that participated and contributed to the nice atmosphere, thank you as well. Mihai, in addition to this, I also thank you for designing this thesis cover in such a short time; the cover looks excellent.

I would like to extend my thanks to my previous and current office mates. Christos, Kazeem, Nor Zaidi, Seyab, Mafalda, Innocent, Cristi, Hector and Mahroo. Thank you for the many but sometimes controversial discussions. As some of you are atheists, Christians, Muslims, or ex-Muslims, sometimes the discussions became intense; nevertheless, they always have been fruitful and enjoyable. I would like to address some words regarding Nor Zaidi; he has been a big inspiration and motivation for us. The sad news reached us that he has passed away. إِنَّا لِلَّهِ وَإِنَّا إِلَيْهِ رَاجِعُونَ. All the other CE colleagues, you are too many to be mentioned by name; I thank each of you individually for the pleasant working environment.

I would like to thank Imran, Seyab, Faisal, Fakhar, and Laiq for our close friendship on the campus and in particular for the enjoyable daily lunches we had. Although the food was often too spicy it was very delicious; I really miss these lunches and the dialogues during them. I would like to also thank all the other Islamic community members, especially the ones I met regularly during the prayers. Thank you for always keeping up the spirit high.

Last but not least, I would like to express my deepest thanks to my family for all the support they gave me. In particular my mother and wife! شُكْرًا. My mother, there are no words that can fully express my gratitude towards you. My wife, you have been an excellent support for me and always a reliable source to trust upon. I hope you can guard this distinctive quality of yours for the rest of your life.

Mottaqiallah Taouil

Delft, September, 2014

the Netherlands

# Contents

|                                                      |            |

|------------------------------------------------------|------------|

| <b>Summary</b>                                       | <b>vii</b> |

| <b>Samenvatting</b>                                  | <b>ix</b>  |

| <b>Acknowledgements</b>                              | <b>xi</b>  |

| <b>1 Introduction</b>                                | <b>1</b>   |

| 1.1 Introduction to 3D Stacked ICs . . . . .         | 2          |

| 1.1.1 Past and Future Semiconductor Trends . . . . . | 2          |

| 1.1.2 3D Technology Classification . . . . .         | 3          |

| 1.1.3 Manufacturing . . . . .                        | 6          |

| 1.2 Opportunities and Challenges . . . . .           | 8          |

| 1.2.1 Opportunities and Drivers . . . . .            | 8          |

| 1.2.2 Challenges . . . . .                           | 11         |

| 1.3 Research Topics . . . . .                        | 15         |

| 1.4 Contributions . . . . .                          | 16         |

| 1.4.1 Yield Improvement . . . . .                    | 16         |

| 1.4.2 Cost Modeling . . . . .                        | 17         |

| 1.4.3 Interconnect Testing . . . . .                 | 17         |

| 1.5 Thesis Organization . . . . .                    | 18         |

| <b>2 Yield Improvement</b>                           | <b>19</b>  |

| 2.1 Introduction . . . . .                           | 20         |

| 2.2 Main Contributions . . . . .                     | 20         |

| 2.2.1 Wafer Matching . . . . .                       | 20         |

| 2.2.2 Layer Redundancy . . . . .                     | 21         |

| 2.2.3 Inter-Layer Redundancy . . . . .               | 22         |

| 2.3 Evaluation . . . . .                             | 23         |

| <b>3 Cost Modeling</b>                               | <b>27</b>  |

| 3.1 Introduction . . . . .                           | 28         |

| 3.2 Main Contributions . . . . .                     | 29         |

| 3.3 Evaluation . . . . .                             | 31         |

|                                                            |            |

|------------------------------------------------------------|------------|

| <b>4 Interconnect Testing and Diagnosis</b>                | <b>33</b>  |

| 4.1 Introduction . . . . .                                 | 34         |

| 4.2 Main Contributions . . . . .                           | 35         |

| 4.3 Evaluation . . . . .                                   | 36         |

| <b>5 Conclusion and Future Work</b>                        | <b>37</b>  |

| 5.1 Summary . . . . .                                      | 38         |

| 5.2 Future Research Directions . . . . .                   | 39         |

| <b>Bibliography</b>                                        | <b>41</b>  |

| <b>A Publications - Yield Improvement</b>                  | <b>51</b>  |

| <b>B Publications - Cost Model</b>                         | <b>109</b> |

| <b>C Publications - Interconnect Testing and Diagnosis</b> | <b>185</b> |

| <b>List of Publications</b>                                | <b>211</b> |

| <b>Curriculum Vitae</b>                                    | <b>215</b> |

# Introduction

## **1.1 Introduction to 3D Stacked ICs**

## **1.2 Opportunities and Challenges**

## **1.3 Research Topics**

## **1.4 Contributions**

## **1.5 Thesis Organization**

---

*Transistor scaling slowly reaches physical device limits and goes hand-in-hand with issues pertaining to process variations, power consumption, reliability, yield, cost, etc. Some of these problems could be alleviated by utilizing 3D-Stacked ICs (3D-SICs). The popularity of 3D-SICs is rising among research institutes and industry. 3D-SICs are emerging as one of the main candidates to continue Moore's Law. In this chapter, we first introduce the evolution leading up to 3D-SIC technology. Subsequently, we present the opportunities such a technology offers and discuss its main challenges. Thereafter, we briefly describe the research directions of this dissertation followed by the main contributions. Finally, we provide the outline of the remainder of this dissertation.*

---

## 1.1 Introduction to 3D Stacked ICs

The aim of this section is to get the reader acquainted with 3D Stacked-ICs. Section 1.1.1 describes past and future semiconductor trends. Section 1.1.2 gives a general classification of stacking transistors in the vertical dimension. Section 1.1.3 explains the crucial 3D-SiC manufacturing steps.

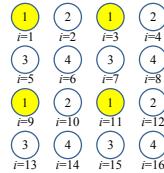

### 1.1.1 Past and Future Semiconductor Trends

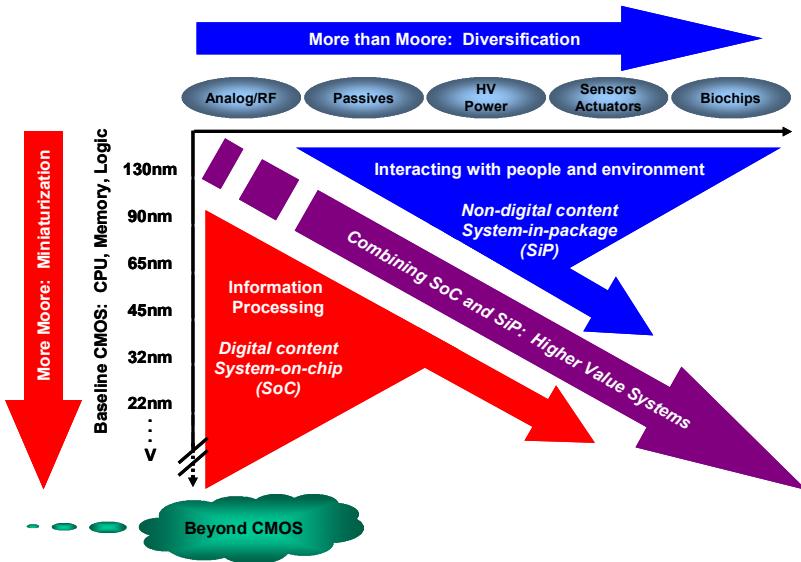

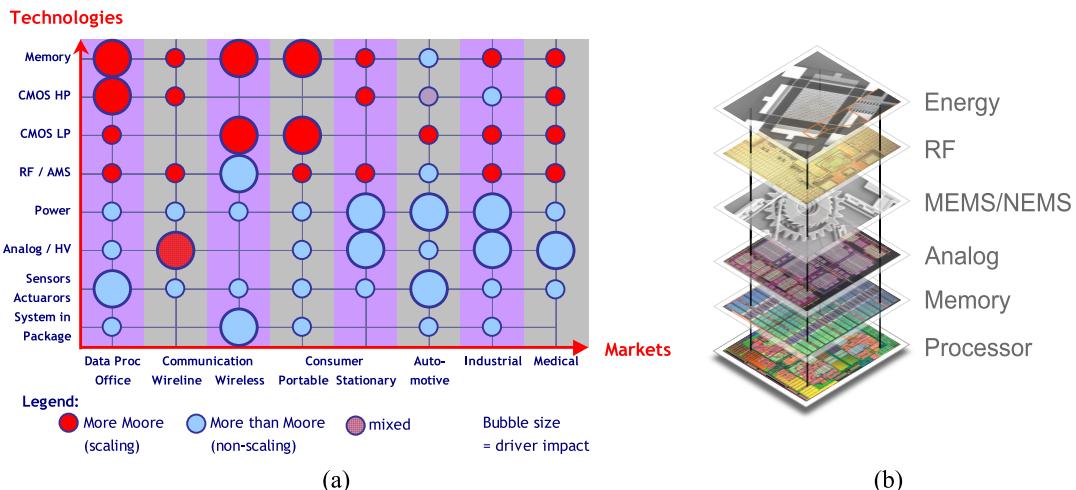

In the past years, the semiconductor industry has fulfilled IC functionality demand by transistor down-scaling adhering to Moore's Law [1]. The associated benefits (such as higher transistor density, higher performance, and reduced cost) of this transistor miniaturization have consistently been emphasized in prior International Technology Roadmap for Semiconductors (ITRS) roadmaps [2]. Although this "More-Moore" trend is still predicted for several future technology nodes, new demands arise concerning computational diversity and functionality in systems that include analog sensors, bio-chips etc. [3]. This diversification is referred to as "More-than-Moore". Figure 1.1 shows a technology roadmap that illustrates the customer need of "More-Moore" and "More-than-Moore", thereby progressing towards more complex and diverse systems.

Figure 1.1: More-than-Moore [3].

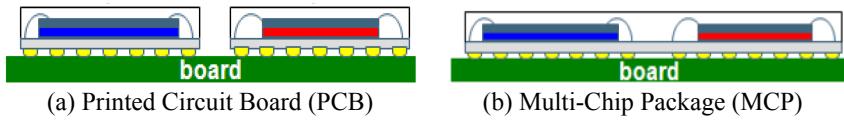

The typical embodiment of such sophisticated and diverse systems predominantly was realized in the past by assembling multiple distinctive components on a printed circuit board (PCB) as depicted in Figure 1.2(a) [4]. Relatively long off-chip wires are used to deliver the communication between ICs, therefore, yielding to relatively low performance and

Figure 1.2: Traditional packaging technologies [4].

power-hungry systems. To shrink the off-chip path length, several heterogeneous chips were brought in closer proximity by integrating them on a single Multi-Chip Package (MCP) as depicted in Figure 1.2(b). This reduces the form factor; however, it still requires off-chip communication between the dies through the package substrate. The need for more complex, faster, more power-efficient and diverse systems led to the utilization of the third dimension.

### 1.1.2 3D Technology Classification

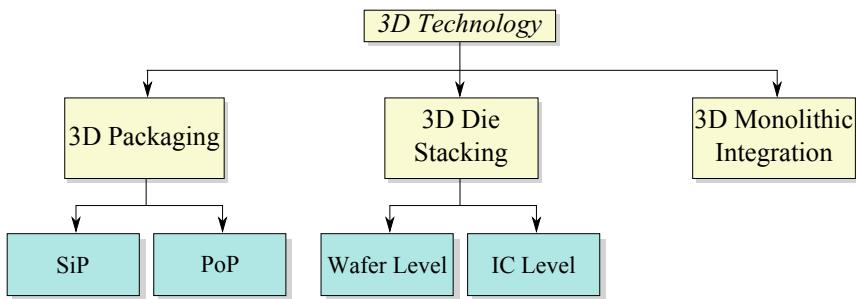

The increasing demand for More-Moore and More-than-Moore has been mostly realized by transistor scaling. A technology that implies further increase in transistor density is the stacking in the vertical dimension; in addition, such technology likely also benefits from more computation diversity due to heterogeneous integration, better performance, and lower power dissipation, all at a smaller footprint. Figure 1.3 shows a general classification of 3D technology consisting of three main classes (i.e., 3D Packaging, 3D Die Stacking and 3D Monolithic) each described next.

Figure 1.3: Classification of 3D systems.

### 3D Packaging

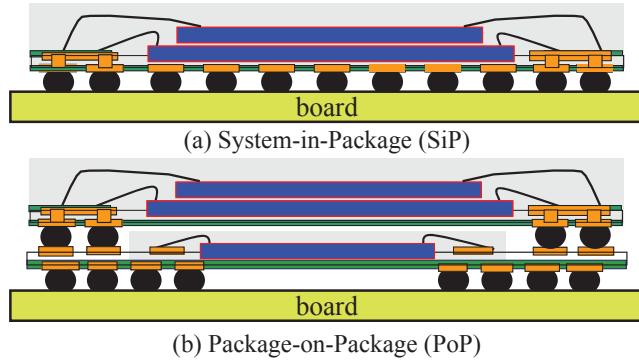

In *3D Packaging*, multiple dies are stacked vertically at the packaging level. Interconnects between the I/Os of the dies are typically formed by wire-bonding, flip-chip, or Ball-Grid-Array (BGA) stacking. This type of 3D stacking provides the lowest interconnect density. An example is a System-in-Package (SiP) depicted in Figure 1.4(a); here the system comprises several naked ICs stacked in the vertical dimension and is packaged in a single chip. The ICs are internally connected by fine wires that are bonded to the substrate. Benefits of

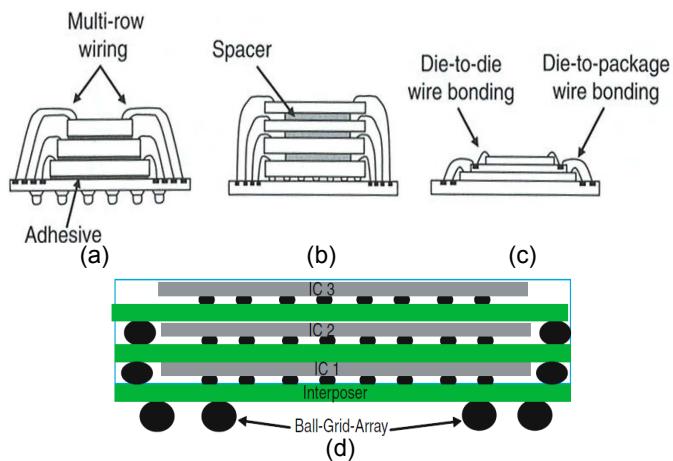

Figure 1.4: 3D packaging technologies.

this system compared to PCBs and MCPs are manifold, such as reduced global wire length (leading to more performance), smaller footprint, increased transistor density, and the elimination of the need to package each die separately. SiPs are, due to these assets, widely used in mobile devices, music players, digital cameras, portable audio players, etc. [5].

Another example that fits into the 3D Packaging class is Package-On-Package (PoP) technology where multiple packaged chips are stacked vertically [8, 9]; an example is depicted in Figure 1.4(b). In this figure, the 3D-SiP package of Figure 1.4(a) is stacked on top of another package. SiPs and PoPs can take many forms as depicted by the examples in Figure 1.5. Figure 1.5(a) shows a SiP with multiple row bonding used to increase the interconnect bandwidth. Figure 1.5(b) shows a SiP delimited by spacers allowing the top dies to form interconnections to the substrate without reducing their die size. Figure 1.5(c) shows a

Figure 1.5: 3D Packaging: (a) Multiple row bonding [6], (b) Dies delimited by spacers [6], (c) Die-to-Die and Die-to-Package wire bonding [6], and (d) BGA-stack [7].

SiP that combines direct die-to-die bonding and die-to-package wire bonding. Figure 1.5(d) shows the interconnection of three dies through a BGA. Generally, communication between stacked ICs in the *3D Packaging* class is performed by off-chip communication by means of wire-bonding through the package substrate or through direct die-to-die communication. However, the wire-bonds in die-to-die communication do not go through the silicon die substrate.

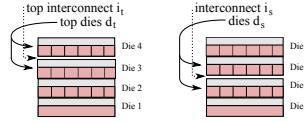

### 3D Die Stacking

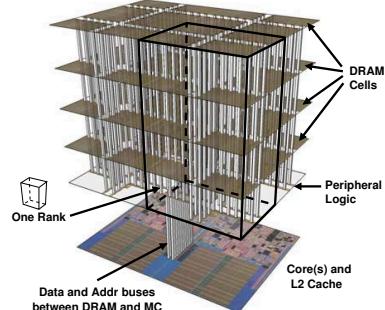

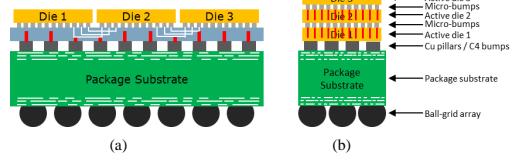

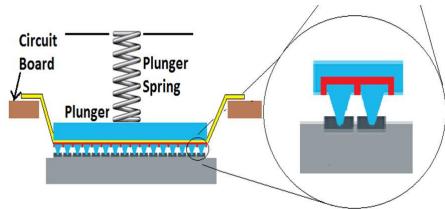

In *3D Die Stacking*, each separately manufactured tier can be stacked and bonded to another tier using a direct communication link between vertically adjacent tiers. A 3D-SIC consists of two or more dies stacked in the vertical direction. The interconnection between the dies can be implemented physically by micro-bumps and/or TSVs, or via contactless communication based on capacitive [10,11] or inductive coupling [12,13]. Among the interconnection schemes, TSVs are the most promising as contactless communication schemes face several challenges such as a stable power delivery [14].

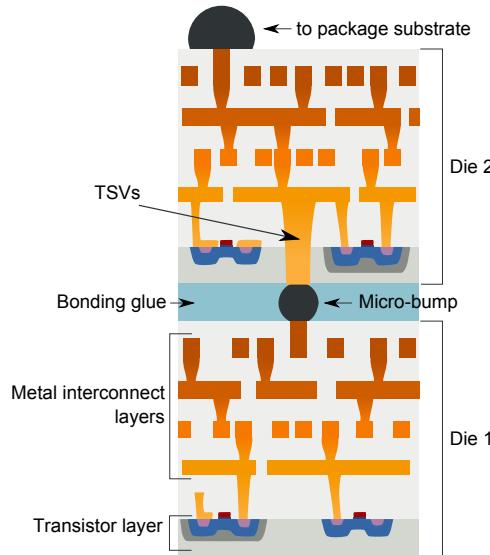

Figure 1.6: TSV-based 3D die stacking.

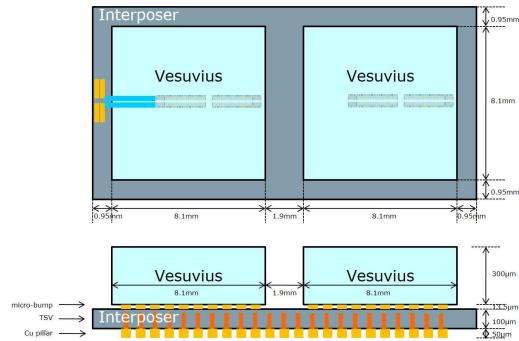

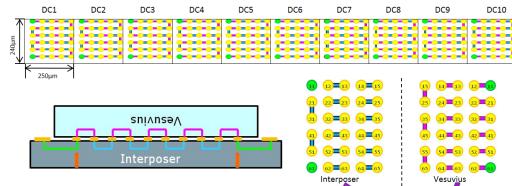

Figure 1.6 depicts a two-layer 3D-SIC with a face-to-back (F2B) stacking configuration. Compared to off-chip wire-bonds, TSVs enable extremely short connections as they go straight through the substrate of the dies. Between the stacked dies, micro-bumps are used to connect the TSVs from Die 2 to Die 1. TSV-based 3D-SICs can be used to empower *More-Moore* and *More-than-Moore* systems and have considerable advantages over planar ICs and SiPs, such as high-speed, less power consumption, small form factor, and heterogeneous integration [15–18]. A special class of *3D Die Stacking* are the 2.5D-Stacked ICs (2.5D-SICs)

in which two or more active dies are stacked side by side Face-to-Face (F2F) on a large passive silicon interposer. The interposer is only used to connect the active dies by means of TSVs and wires. 2.5D-SICs are in general easier to manufacture, but its advantages are typically also less than those of 3D-SICs (for example, power dissipation in interconnects, bandwidth, off-chip I/O density) [19].

### 3D Monolithic Integration

In *3D Monolithic Integration* active devices are created on-chip bottom-up in a single linear process flow; this process does not require bonding materials between the layers. The stacked active silicon areas are isolated from each other by dielectric layers. Among the stacking approaches, monolithic 3D integration provides the highest vertical interconnect density between stacked layers. Currently, the state of this technology is insufficiently enhanced to realize reliable high-performance 3D circuits, primarily due to its complex processing which leads to inferior quality of devices in the upper planes and limited number of layers due to thermal constraints [20].

In this dissertation, we focus on a particular subset of *3D Die Stacking* in which the vertical interconnects are realized by through-silicon vias (TSVs), the TSV-based 3D-SICs. The process to manufacture such ICs is described next.

#### 1.1.3 Manufacturing

Recent enhancements in process development enabled the fabrication of TSV-based 3D-SICs [17]. Critical steps to manufacture such ICs are the formation of TSVs, and the bonding and thinning of dies. They are described next.

#### TSV Manufacturing

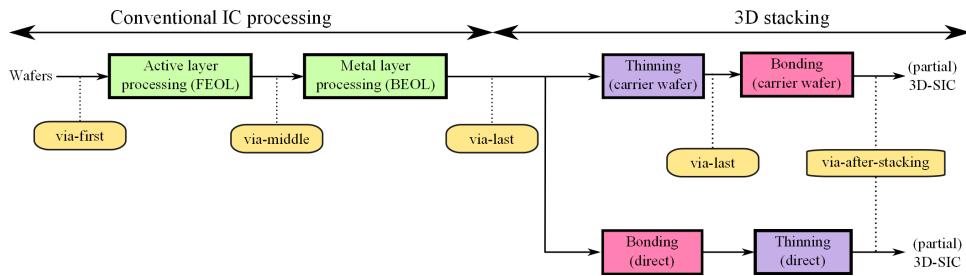

TSVs are holes that go through the silicon substrate filled with a conducting material (e.g., copper or tungsten). These holes are shaped by deep reactive ion etching (DRIE) [21] or laser ablation [17]. The size, pitch, conductivity, and conducting material of TSVs are heavily impacted by the stage they are constructed at [17]; either during the conventional manufacturing of planar ICs (via-first, via-middle, via-last) or during 3D processing steps (via-last, via-after-stacking) as depicted in Figure 1.7. Via-first TSVs are manufactured prior to the front-end of line (FEOL), i.e., before the transistors are fabricated, and must be filled with doped poly-silicon which has a relatively high resistance [17]. A lower-bound temperature constraint, dictated by the FEOL processing, excludes the usage of copper TSVs. Via-middle TSVs are manufactured between the FEOL and back-end of line (BEOL), i.e. before the metal layers are fabricated and typically utilize copper or tungsten as filling material. Via-Last TSVs are manufactured after BEOL either prior or post thinning and have the advantage over via-first and via-middle TSVs that foundries without TSV processing

Figure 1.7: TSV manufacturing stages.

equipment already may manufacture the whole IC. Finally, the option exists to create TSVs (via-after-stacking) as the last 3D processing step.

### Thinning

Thinning of wafers, performed by wet-etching, is required to expose the TSV tips to form electrical contacts; TSVs have limited aspect ratios and therefore, pose a major challenge on the filling processes [4]. A typical thinning process is described in [17]. First, a coarse-grind process removes inaccurately large portions of the back-side of the substrate. As a byproduct, surface and sub-surface damages are created up to a depth of approximately 10-20  $\mu\text{m}$ . A fine-grind process is followed which minimizes surface and subsurface damages typically up to a depth of 2  $\mu\text{m}$ . In the last step, these damages are removed by a stress-relief step to avoid propagation of cracks during bonding and to increase the bonding strength by enlarging the contact area of two bonded dies.

### Bonding

Bonding can be of temporary or permanent type [4]. In temporary bonding, dies are attached to a carrier wafer for TSV or thinning processes only. This type of bonding is used in several 3D process flows (see Figure 1.7) and is commonly realized by polymer adhesive or electrostatic bonding [17].

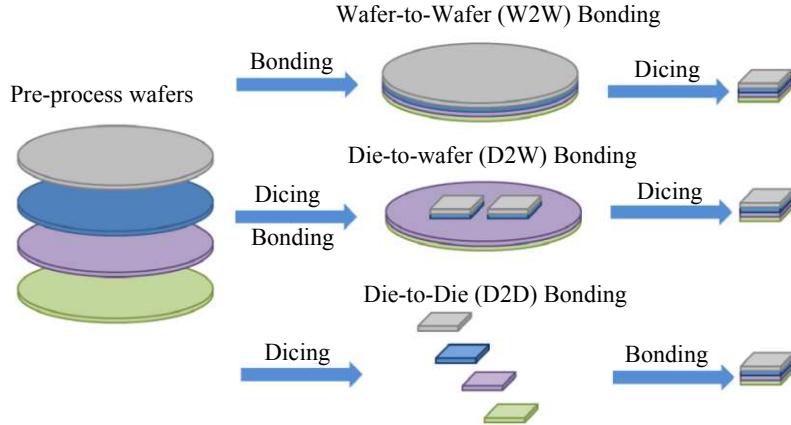

In permanent bonding, the (thinned) die is bonded permanently by using direct Cu-Cu,  $\text{SiO}_2/\text{SiO}_2$ , Au/Au, polymer adhesive, gel adhesive or eutectic bonding [17]. There are three permanent bonding methods, as depicted in Figure 1.8. They are Die-to-Die (D2D), Die-to-Wafer (D2W) and Wafer-to-Wafer (W2W) bonding [17]; each comes with its own merits. Although complex, a high alignment accuracy is feasible in D2D and D2W bonding at the cost of a low throughput. In addition, the handling of very small dies becomes impractical for these bonding methods. Nevertheless, a major benefit of the D2D and D2W bonding methods is the ability to apply pre-bond testing, which may prevent faulty dies from entering the stack [17] leading to improved compound yield. On the other hand, achieving a high alignment accuracy is simpler in W2W bonding, particularly if small dies are used.

Figure 1.8: 3D bonding techniques [22].

However, W2W stacking negatively impacts the compound yield as the stacking of good dies on top of bad dies cannot be prevented. In addition, W2W bonding requires the stacking of dies with same sizes; this makes them suitable for limited applications such as memories and FPGAs. These applications have a high degree of regularity.

## 1.2 Opportunities and Challenges

The previous section introduced briefly 3D-SICs. In this section, the main drivers, advantages and disadvantages of 3D-SIC technology are described.

### 1.2.1 Opportunities and Drivers

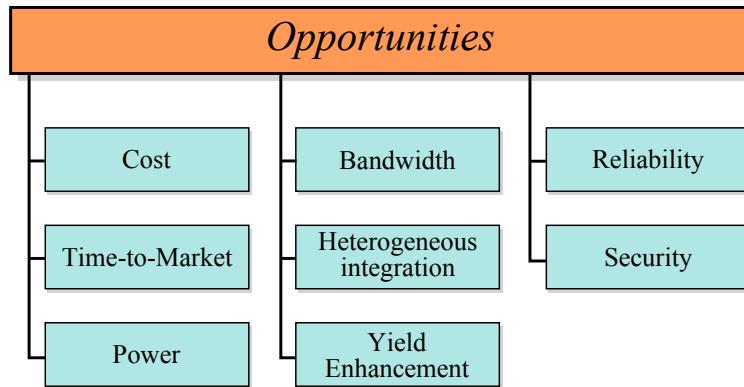

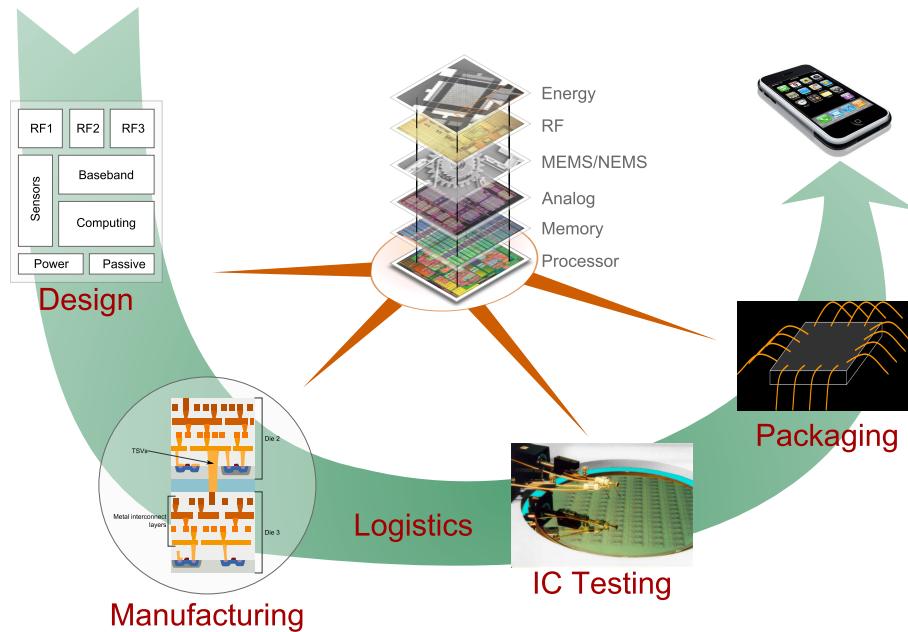

The prospects and potential benefits that 3D-SICs offer is leading to an expansion of research work both in academia and industry [14, 17, 18, 23–26]. However, prior to be accepted as a solid and mature technology, each new technology must demonstrate its market and technological advantages such as the ones depicted in Figure 1.9. They are discussed next.

- **Cost:** A key condition to shift from the design and prototype phase to large-scale production is a manageable cost figure. 3D-SICs are able to reduce cost by splitting up large dies over multiple smaller layers. A benefit of this approach is that the compound yield of the 3D-SIC with smaller die sizes may exceed the yield of the single large die [27]. Another way to reduce cost in 3D-SICs is by integrating multiple stand-alone chips. For example, by stacking DRAM on logic more than a bandwidth improvement is realized. The physical size of vertically pilled-up dies reduces the footprint, volume area, and weight, which in turn increases the package density. Nevertheless, for 3D-SICs to be widely accepted for a wide range of applications cost is still a limiting factor

Figure 1.9: 3D-SIC opportunities.

as the cost depends on the yield learning curve driven by the cumulative produced 3D-SICs.

- **Time-to-Market:** Once the stacking technology matures, time-to-market may be reduced due to die reusability. Figure 1.10(a) shows the technology requirements (such as performance, power, etc.) of several application markets (such as consumer, automotive, medical, etc.). It shows for each market and technology combination the More-Moore and/or More-than-Moore driver impact. The figure illustrates for the different market segments the need for diversification, which may be offered by heterogeneous integration in a modular 3D die design. For example, DRAM, sensors, MEMS, and other analog and RF designs might be reused without a redesign or left

Figure 1.10: (a) Market vs technology requirements [28], (b) Heterogeneous 3D-SIC.

implemented at older and cheaper technology nodes. Therefore, 3D stacking supports an additional level of flexibility in the (re-)design of systems as compared to SoCs.

- **Electrical performance (power, bandwidth, latency, etc.):** For the past couple of decades, performance enhancement of successive transistor generations was carried out by transistor down-scaling leading to increased speed and higher transistor density. Currently, research shows that obtain further scaling benefits beyond 32nm are challenging [29]. In addition, the gained improvements at transistor level did not solve the bandwidth and latency problems at system level, which for example lead to a serious bottleneck between CPU and memory speed referred to as Memory Wall [30]. Utilizing the third dimension, for example by stacking DRAM layers [31], might be the only way to significantly reduce memory latency and power consumption for future generations of multi-core microprocessors [17]. In addition, stacking provides additional benefits such as reduced power consumption (up to 50% and 25% for standby and active power respectively for four stacked memory dies) [32], reduced noise levels due to the shorter global interconnects and the need of smaller I/O drivers [33]. In general, any efficient partitioning of IP cores reduces long global wires and therefore also the delay and power dissipation [14, 34].

- **Heterogeneous integration:** Stacking dies in 3D makes heterogeneous integration possible as depicted in Figure 1.10(b). This is a promising concept for 3D-SICs, since each layer can be manufactured with different technology and optimized for specific needs such as speed, area, power, etc. This affects yield, performance, and lithography cost positively. For example, DRAM, FLASH, sensors, MEMS, etc., could potentially be integrated into a single 3D-SIC. Heterogeneous integration could also make the complete stack more reliable. Traditionally, fault tolerance and fault prevention methods are used to increase system reliability. Fault tolerance focuses on recovering systems in the presence of faults, while fault prevention targets initial reliable systems by using for example reliable materials or designing the chip with extra safety margins. Using the third dimension the reliability may be increased in several ways. For example, (a) functional units may be shared vertically between dies to increase the fault tolerance, and (b) critical system parts may be implemented using more reliable dies (i.e., with larger feature size) to reduce failures, while the less critical cores may use dies with the latest but less-mature technology.

- **Yield improvement:** Traditionally, yield improvement for 2D memories is based on the use of spare rows and/or columns [35–37]. 3D stacked memories provide additional repair features in the vertical dimension as spares can be accessed on neighbor dies. Preliminary research results shows the significant benefits of using this vertical direction [18, 38, 39].

- **Security:** 3D stacking opens new avenues to increase security, such as [40]:

- A Face-to-Face (F2F) stacked IC conceals most of its circuitry making it hard

for attackers to access parts of the chip.

- The 3D structure is inherently resilient against most reverse engineering attacks. De-layering a 3D-SIC is very difficult. Obtaining voltage images of the layers is challenging due to overlap of dies. Moreover, the bonding materials used to attach dies would likely blur and attenuate signals.

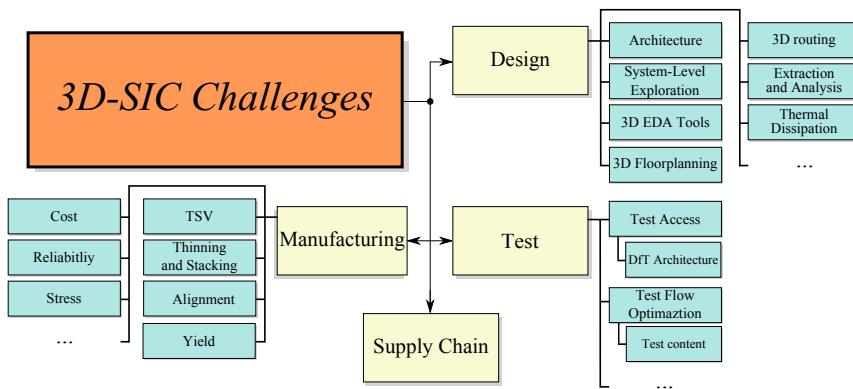

### 1.2.2 Challenges

Although 3D-SICs have a lot of potential due its opportunities, several challenges still need to be addressed. These challenges must be resolved prior to mass production. A list of the most challenging issues is provided in Figure 1.11; they are classified according to design, manufacturing, test, and supply chain. Each class is briefly described next.

Figure 1.11: 3D-SIC challenges.

- **Design:** One of the key design questions is how to map architectures efficiently into the third dimension. It is therefore important to develop tools that support early but sufficiently accurate system-level explorations in terms of electrical performance (power, frequency), area, thermal budget, cost, etc. [33]. This exploration should guide designers to determine the optimal die sequence in the stack, the technology node for each die, and optimize the interconnection between them. Some system-level exploration tools start to appear such as 3D PathFinding [41] but need more features and automation steps. Once the architecture and rough stack layout are determined, tools are required for the floorplanning and routing.

TSVs are relative large objects and their number and placement are decisive, especially as a Keep-Out-Zone (KOZ) must be taken into consideration [42, 43]. This KOZ guarantees safe transistor operation as the mechanically induced TSV stress changes the nearby silicon characteristics. In addition to the TSV placement, floorplanners must not only understand the location of each IP block (on die level), but also its place vertically in the stack. Furthermore, the router should be thermal-aware to reduce

hot spots, for example by moving expected hot areas closer to heat sinks. During the routing phase, specific attention must be attributed to the back-side redistribution layer (RDL), and TSV sizes for optimal area placement. The routing algorithm should minimize wire length by taking connection points on adjacent dies into consideration. Other challenges include the distribution of the power grid and clock tree [26]. Dies that are further from the power source are likely to suffer more from voltage drop, clock skew and jitter, but are also be impacted by process variations between the dies.

Accurate tools must be developed to perform parasitic extraction and analysis after the routing phase [33]. In addition to traditional layout parasitic extraction, tools must recognize and integrate RLC parasitics of TSV and micro-bumps and perform thermal analysis for the whole stack. Thinned dies may lead to lower heat dissipation [17]. As the temperature might raise in the stack special care for heat flux must be taken into account. A challenging task is to remove the heat from the chips. Traditionally, packages remove heat from the chip by placing heat sinks on top and/or on the bottom of the chips. At this moment, the 3D-SIC packaging technology is under intensive development and roadmaps have yet to be defined for it [44]. TSVs could help removing the heat when they are used as heat conductors [45].

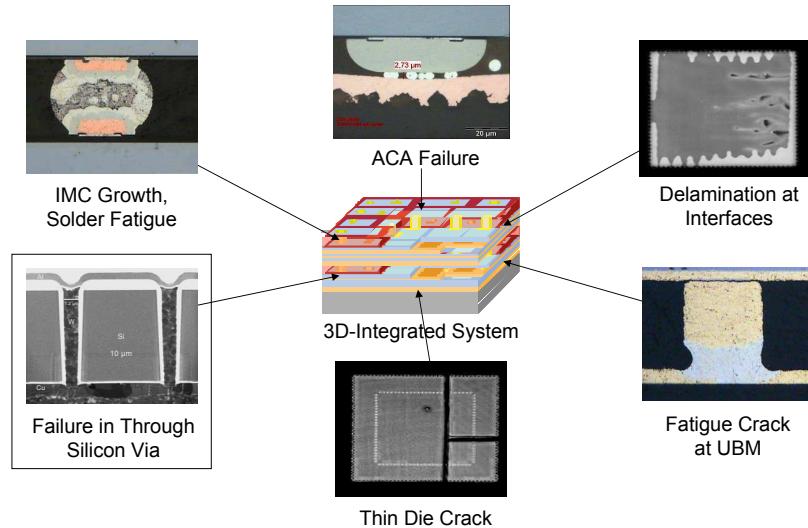

- **Manufacturing:** 3D-SIC manufacturing requires additional processing steps as compared to conventional ICs; these include for example the forming of TSVs, thinning wafers, and stacking and bonding wafers or dies as described in Section 1.1.3. Each of these additional steps may introduce new defects to the system. Figure 1.12 [17] shows examples of defects that may occur in the TSVs, micro-bumps, and thinned dies as a result of the 3D processing. Typical defects related to 3D processing may be summarized as follows.

- Pinhole defects along TSV walls create shorts or low resistance paths between TSVs and the substrate; This causes degradation of the signal quality in terms of strength and speed [4, 46–48].

- An incomplete fill of TSVs (voids) may originate from insufficient wetting during plating. Voids cause partial opens and increase resistance [4, 46–48].

- Coefficient of thermal expansion (CTE) mismatch between TSV metal (e.g., copper) and substrate may lead to TSV cracks and sidewall delamination. Both lead to increased path resistance [47–51].

- Pinch-off of TSVs during plating could lead to increased TSV resistance or partial opens [46].

- Missing contacts between TSVs and transistors or metal layers cause opens [46, 52].

- A misalignment of TSVs and  $\mu$ -bumps increase the resistance and cause (partial) opens [46–48].

- Crosstalk between different TSVs [48, 53].

Figure 1.12: Examples of 3D failure mechanisms [17].

- Damage in underlying BEOL [54].

- Weak bonding due to buckled thinned Si chip [54].

- Variation in TSV heights may cause tin to be squeezed out from  $\mu$ -bump causing shorts between  $\mu$ -bumps [54, 55].

- Electromigration causes voids and cracks in the joints, resulting in higher resistive  $\mu$ -bumps, or opens [56].

- Cracks in  $\mu$ -bumps may be formed due to a CTE mismatch between copper, silicon, and silicon-oxide [46].

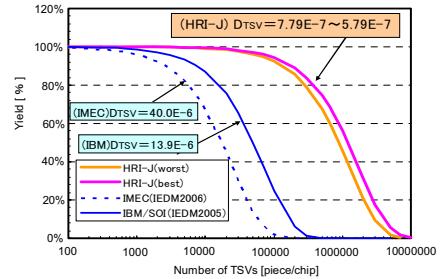

In order for 3D-SICs to be commercially viable, a high-yield manufacturing process is required. To achieve that, defects must be repaired or tolerated as 3D technology is currently in its infant stage. For example, several research publications already analyzed the impact of TSV redundancy schemes [57–59] to increase the TSV interconnect yield. In addition to a satisfactory yield, testing is required to keep defective ICs out from the market; this topic is described next.

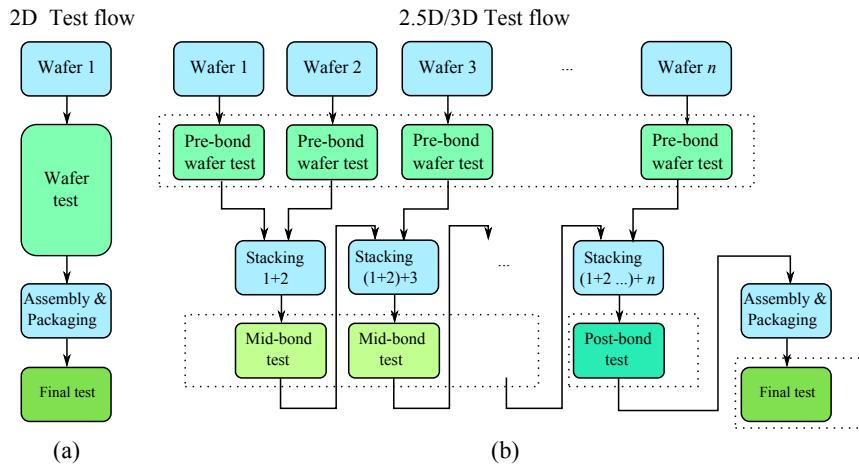

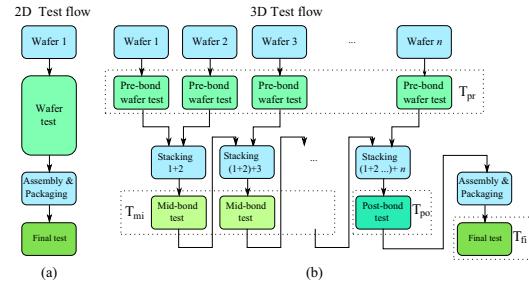

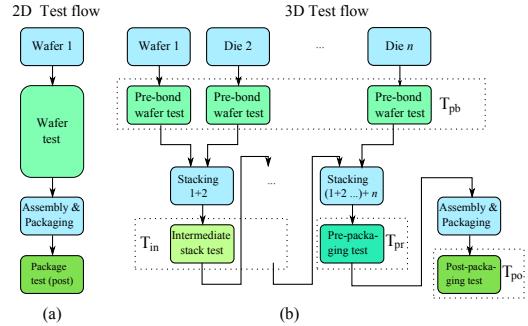

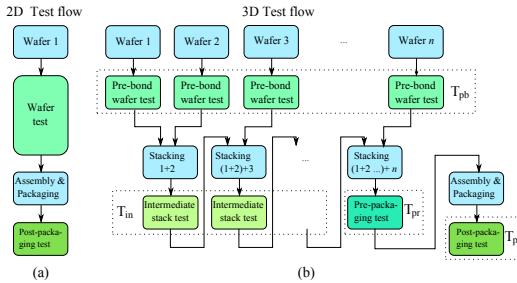

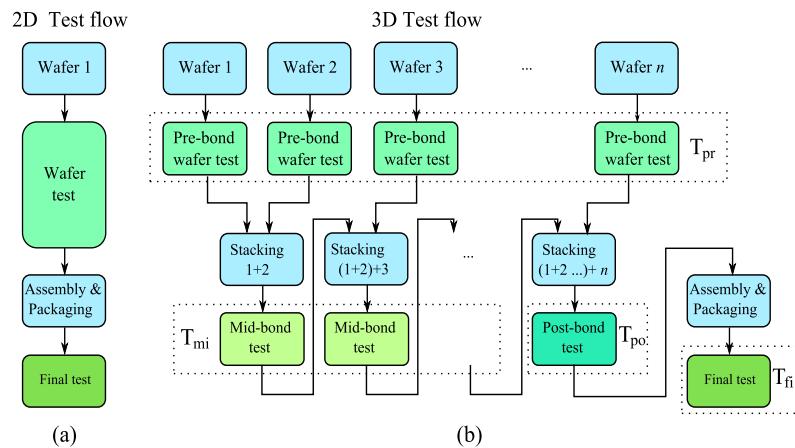

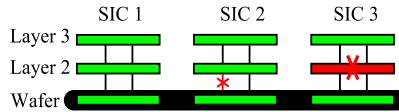

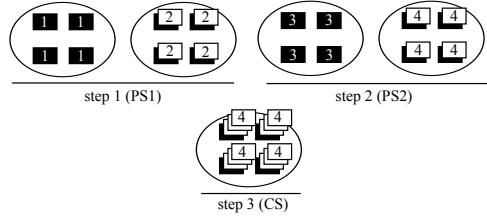

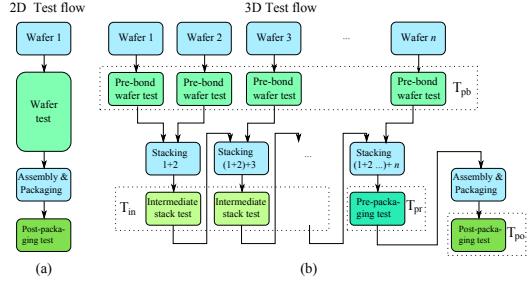

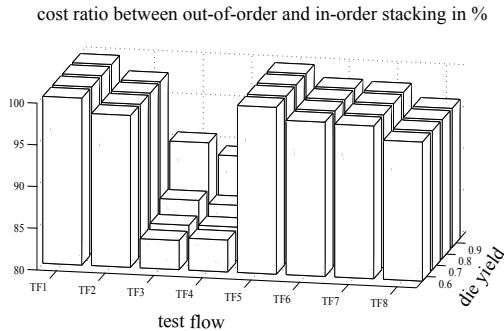

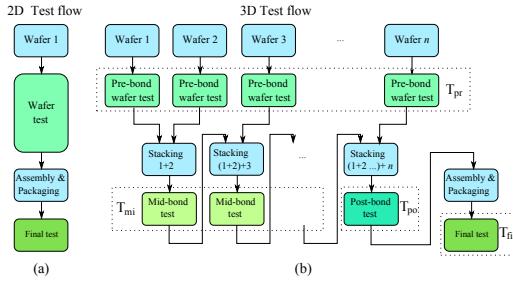

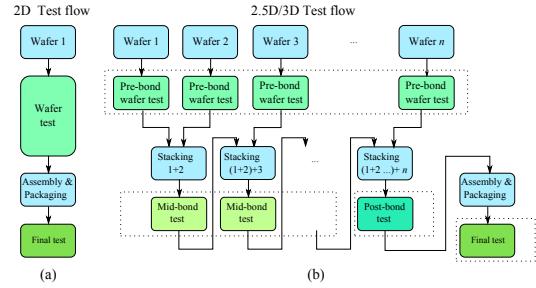

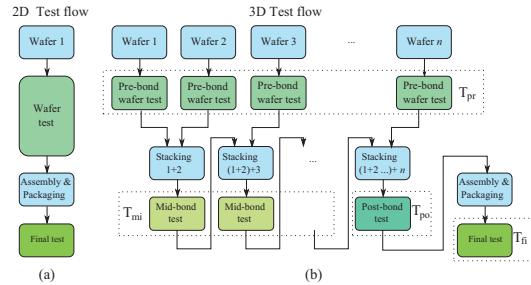

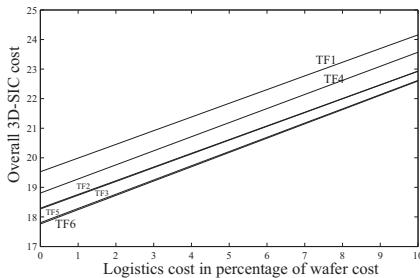

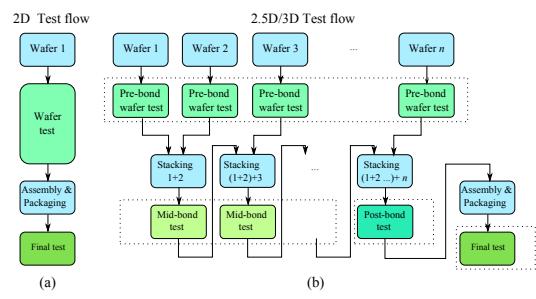

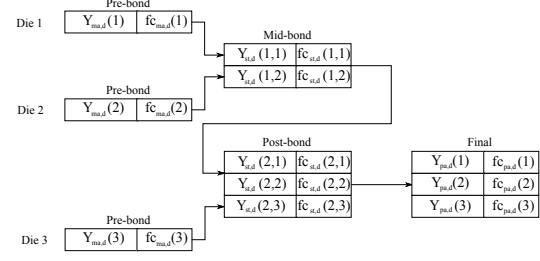

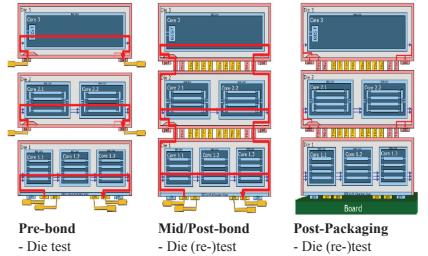

- **Test:** Testing is one of the biggest challenges of 3D-SICs due to its number of potential test moments. Figure 1.13(a) shows the conventional 2D test flow for planar wafers [55, 60]; it consists of two test moments: a wafer test prior to packaging and a final test after packaging. 2.5D/3D-SICs, however, provide additional test moments. In general, four test phases can be distinguished for a 3D-SICs consisting of  $n$  dies as depicted in Figure 1.13(b): (1) *n pre-bond* wafer tests, (2) *n-2 mid-bond* tests, (3) one *post-bond* test prior packaging and (4) one *final* test; resulting into  $2 \cdot n$  test moments.

Figure 1.13: 2D versus 2.5D/3D D2W test flows.

ments [4].

The test challenge can be sub-divided into two main categories: (i) test access and (ii) test flow optimization.

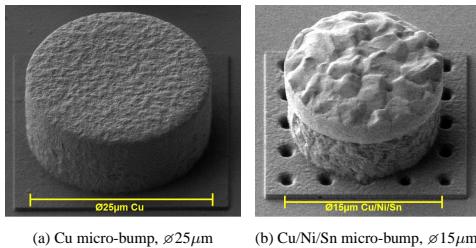

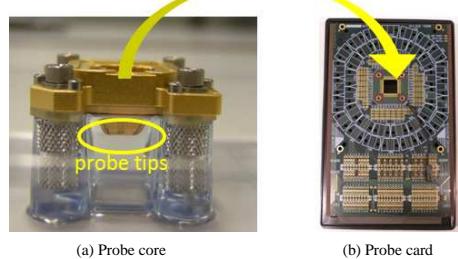

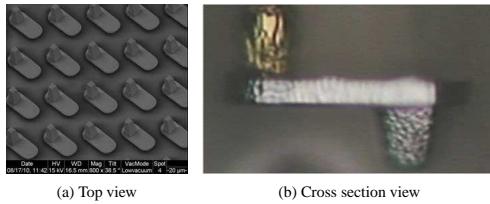

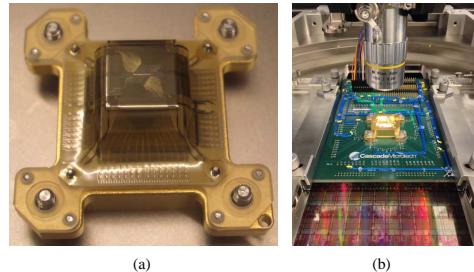

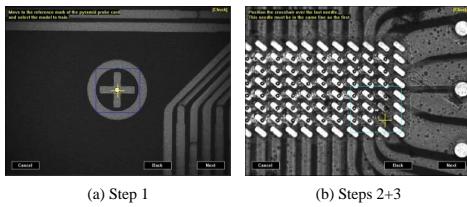

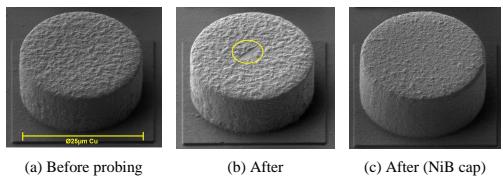

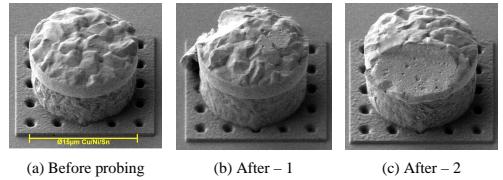

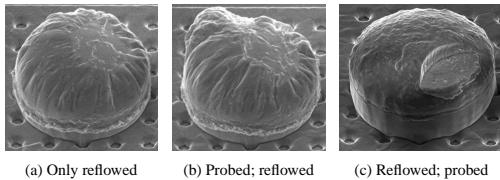

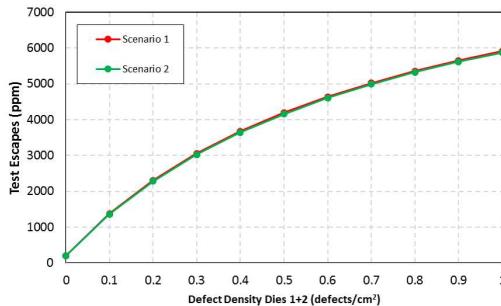

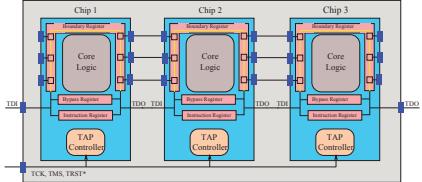

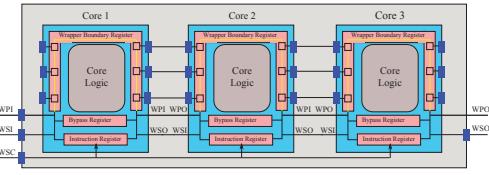

- **Test Access:** The test access can be divided further into two subcategories: external and internal access (or DfT architecture). As non-bottom wafers are not designed with external I/O pins, pre-bond testing of such wafers comes with extra challenges. One option to access these wafers is by using dedicated test pads. The main disadvantages of these pads are their area overhead and undesired load capacitance in the final stack. Efforts are taking place to perform direct probing on the micro-bumps [61] which makes the probe pads superfluous. However, manufacturing a fine pitch probe card is challenging. Probing dies that are already thinned may lead to serious IC damage [62]. Testing the non-bottom dies in the other phases, i.e., during mid-bond, post-bond or the final phase requires proper DfT in the stack to forward test data to the specific die under test. Note that only the bottom die has external I/O pins. IEEE P1838 [63] is currently a DfT standard in development for digital stacked ICs; it is based on the presence of boundary scan cells in all dies.

- **Test Flow Optimization:** Test flow optimization can also be divided into two subcategories: test content and test order. Each test covers a set of faults (which are higher abstract presentations of defects). Generating test patterns for each die in the stack may follow a similar flow as used in traditional 2D. However, new type of defects may arise. For example, the mechanical stress induced by TSVs might impact (negatively or positively) the transistor speed [64]. Thinning of dies leads to shifts in transistor  $I - V$ , impacting both speed and power [65].

In addition, the new introduced components, the TSVs, should be tested. At-speed interconnect testing (for TSVs and micro-bumps) is challenging due to low latency interconnects.

Once the content is defined, the order in which interconnects (e.g., interconnect, die) and dies are tested might impact the overall cost. Testing first for defects that are likely to occur reduces average test time. Early testing might prevent further assembly costs such as the stacking of good dies on defective partial stacks, but may also impact the overall cost negatively. The total number of test moments, equal to twice the number of dies in the stack [4], further complicates finding optimal test flows.

- **Supply Chain:** There are some complex logistic issues that need to be solved for 3D-SIC. For example, responsibility should be taken for yield and inventory risk during the 3D manufacturing process. More precisely, responsibility should be taken for TSV manufacturing, FEOL, BEOL, thinning and bonding, testing (during the different phases), and packaging [66]. Other concerns may be delays between suppliers and transportation of (thinned) non-packaged wafers, as they may affect the yield.

### 1.3 Research Topics

The research that is carried out in this thesis can be divided mainly into three parts.

1. Yield improvement techniques.

2. Cost modeling, mainly focusing on test cost optimization.

3. Interconnect testing and diagnosis for memory stacked on logic.

#### **Yield Improvement**

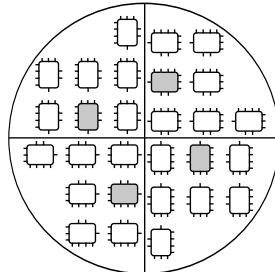

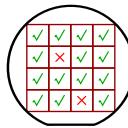

As yield is one of the major concerns for 3D-SICs, yield improvement techniques should be developed from transistor level up to application level. In this dissertation, we focus on yield improvement in W2W stacking as the yield drops quickly with the increasing number of dies. This is a direct consequence of stacking good dies on bad dies and vice versa. Methods to improve this yield are required. Hence, efficient wafer matching algorithms are needed to maximize the compound yield.

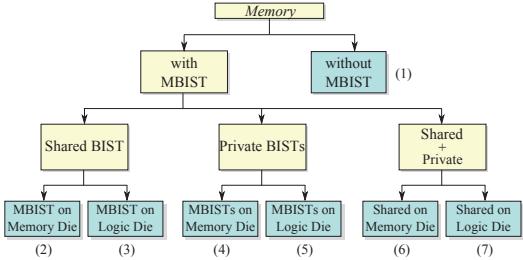

Another interesting research topic is repair for yield improvement. Due to their regular structure, 3D stacked memories are good candidates for such schemes. In 2D memory, each die comes with its own redundant cells typically realized by spare rows and/or columns. In 3D memory, in addition to 2D repair, repair schemes of defective memory cells could utilize the third dimension. This gives defective cells more room for repair and therefore could improve the compound yield.

## Cost Modeling

Each 3D-SIC must be tested as a consequence of many high-precision defect-prone steps. Testing identifies the defective chips and guarantees the end-of-line product quality. There are many possible test moments in the 3D manufacturing flow (see Figure 1.13); they are: pre-bond, mid-bond, post-bond, and final testing. Despite the cost of each test, it may filter defective components in an early stage, which prevents down-stream costs. In particular, each applied test has a particular *value* as it could (a) prevent faulty dies from entering good stacks (pre-bond test), (b) prevent stacking of good dies on faulty partial stacks (mid-bond test), (c) prevent packaging costs (post-bond test), and (d) prevent the shipment of defective parts to customers (final test).

Test flows, which consists of tests applied at some or all test moments, needs to be optimized based on yield and cost parameters of individual products; this is a complex optimization problem due to the various test moments. Once the test flow is determined, proper DfT must be added to the chip at design time. For example, this can be Memory Built-in Self Tests (MBISTs), Boundary Scan, scan chains, etc. This demands a sophisticated tool that is able to evaluate the trade-offs between test cost and test value of all possible test flows, during the early design stage.

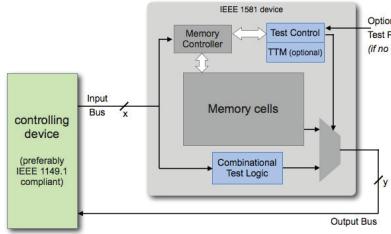

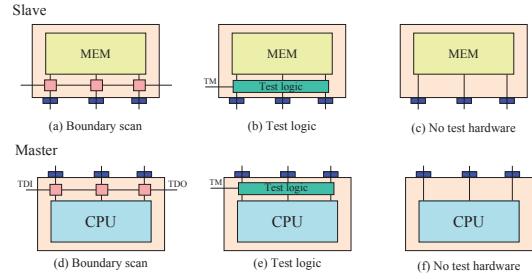

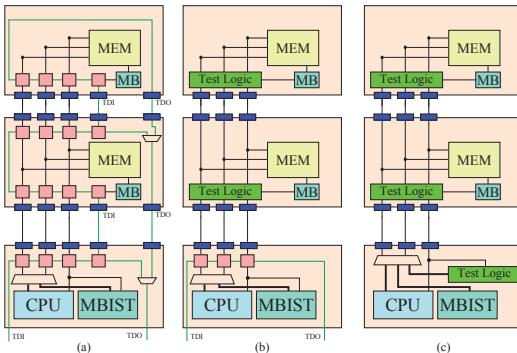

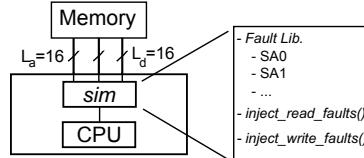

## Interconnect Test and Diagnosis

One of the challenges related to interconnect testing is to perform at-speed post-bond interconnect testing. Prior research publications focused on testing these interconnects using boundary scan. However, at this stage they typically fail to address dynamic faults and at-speed testing. Testing TSV interconnects between the two dies is challenging, as the dies in the stack might come from different manufacturers, which is typically the case for DRAM stacked on logic. In addition, memory vendors have not always been in favor of integrating IEEE 1149.1 on their devices [67].

## 1.4 Contributions

The contributions of this dissertation are directly related to the research topics presented in the previous section.

### 1.4.1 Yield Improvement

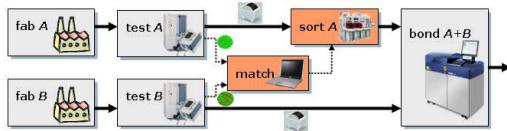

Several methods are deployed to boost the compound yield. We focus on the following methods: (i) wafer matching [68, 69], (ii) layer redundancy [38, 70], and (iii) inter-layer redundancy [71]. The first method, wafer matching, is applicable in the case where entire wafers are stacked using W2W bonding. By using wafer maps with faulty die locations, suitable wafer pairs can be selected for stacking to obtain higher compound yield as compared to blind stacking. Wafer matching does not come for free as it requires pre-bond testing.

Proper cost-trade off analysis are performed that show the added value of wafer matching, i.e., lower 3D-SIC cost. The second and third methods focus in particular on memories and utilize the third dimension to increase the compound yield. Both methods apply repair on different granularities. Layer redundancy focuses on the repair at the die level where complete faulty dies are replaced. However, inter-layer redundancy focuses on repair schemes within the memory array where spares can be accessed on neighbor dies. Both yield repair schemes are presented, analyzed and evaluated.

### 1.4.2 Cost Modeling

We present the tool 3D-COSTAR that is able to perform adequate cost prediction at the early design stage. To our knowledge, we are the first to introduce such a tool that is able to incorporate all test moments of the production cycle. 3D-COSTAR is able to evaluate test flows for 3D-SIC; the tool considers all costs involved in the 3D-SIC production (including design, manufacturing, testing, packaging and logistics) and attributes the cost to end-of-line passing products [72–76]. It is aware of the stack build-up (2.5D, 3D, multiple towers), stacking orientation (face-to-face, back-to-face, or face-to-back), and stacking process (die-to-die, die-to-wafer, or wafer-to-wafer). The tool allows us to evaluate several interesting case studies; some of them are listed next.

1. Trade-off between test quality and area overhead for passive interposers in 2.5D-SICs [77]. Interposers do not contain active logic and therefore, are difficult to test. To facilitate pre-bond testing, additional DfT structures must be embedded into the design. However, this impacts both the yield and die size.

2. Impact of the post-bond test quality for a given packaging cost [78]. The post-bond test is the last test opportunity for testing before the 3D-SIC is packaged.

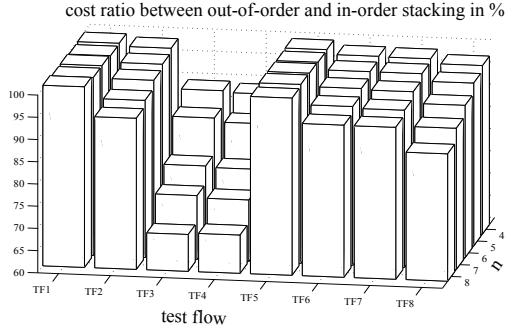

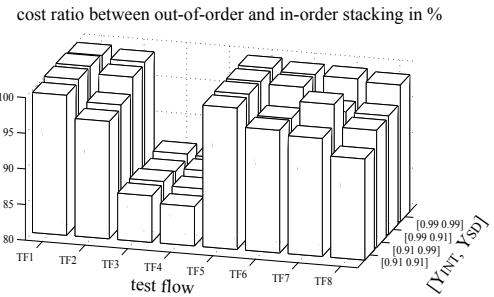

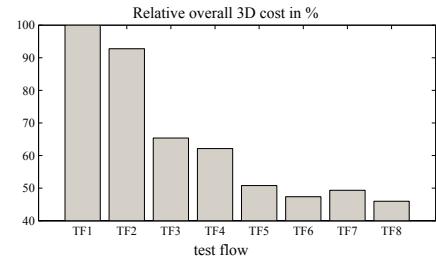

3. Impact of the stacking order [79]. Changing the stacking order impacts the overall 3D-SIC cost in case mid-bond testing is performed.

4. Cost trade-off between testing by means of dedicated pads versus micro-bump probing [77]. Dedicated test pads increase the area (on non-bottom dies), while probing on micro-bumps requires fine-pitch low-force probe cards.

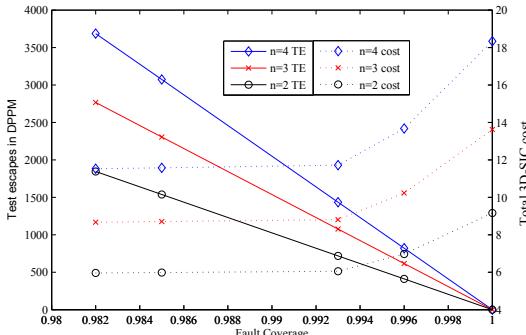

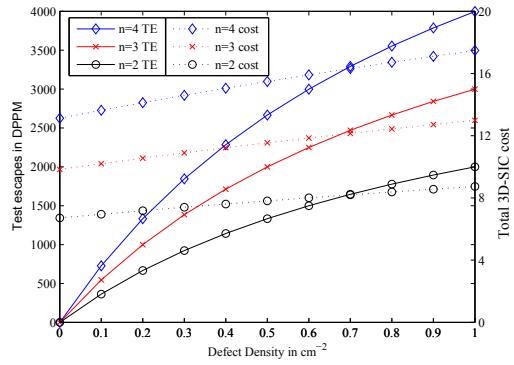

5. Analysis of (test) cost versus product quality (expressed in number of test escapes) [60].

### 1.4.3 Interconnect Testing

We present a methodology to test interconnects in memories-stacked-on-logic without the need for additional DfT [80, 81]. The assumption made here is that the logic die contains a memory controller or CPU such that TSV interconnects are tested by performing appropriate write and read instructions. These instructions function as test patterns that target specific faults. As defects in TSV are primarily timing related (see Section 1.2.2), it is required that dynamic faults have to be covered by the test. We have developed several test sets to detect

all targeted faults both for address and data line TSVs. Control lines have been assumed to be tested implicitly. In addition to testing, also diagnosis algorithms have been presented [82]. These algorithms are able to identify both the fault location and fault type of all targeted faults. We compared our proposed method with general interconnect DfT schemes such as IEEE 1581 and IEEE 1149.1, but also with dedicated Built-in-Self-Test (BIST) architectures.

## 1.5 Thesis Organization

The remainder structure of this dissertation is organized as follows.

Chapter 2 discusses the contributions of this dissertation with respect to yield improvement. It presents the proposed yield improvements techniques by describing their working principles. In addition, it summarizes the state-of-the-art in this field and presents our contributions. The publications accompanying this chapter can be found in Appendix A.

Chapter 3 discusses the contributions of this dissertation with respect to cost modeling. We first argue the need for such a tool followed by previous work in this area. Shortcomings clearly show the uniqueness of our tool. The publications accompanying this chapter can be found in Appendix B.

Chapter 4 presents our test and diagnosis approach for interconnects in memories stacked on logic. It first explains the need for such an approach and presents after that our contributions with respect to the start-of-the-art. The publications accompanying this chapter can be found in Appendix C.

Finally, the conclusions and future work are presented in Chapter 5.

Chapter **2**

## Yield Improvement

---

The content of this chapter is based on the following research articles:

1. **M. Taouil**, S. Hamdioui, J. Verbree, and E.J. Marinissen, “On Maximizing the Compound Yield for 3D Wafer-to-Wafer Stacked ICs,” in *International Test Conference (ITC)*, Austin, TX, USA, Nov. 2010, pp. 1-10.

2. **M. Taouil**, S. Hamdioui and E.J. Marinissen, “Yield Improvement for 3D Wafer-to-Wafer Stacked ICs Using Wafer Matching,” *submitted to ACM Transactions on Design Automation of Electronic Systems (TODAES)*, pp. 1–24, 2014.

3. **M. Taouil** and S. Hamdioui, “Layer Redundancy Based Yield Improvement for 3D Wafer-to-Wafer Stacked Memories,” *European Test Symposium (ETS)*, Trondheim, Norway, May 2011, pp. 45–50.

4. **M. Taouil** and S. Hamdioui, “Yield Improvement for 3D Wafer-to-Wafer Stacked Memories,” *Journal of Electronic Testing: Theory and Applications (JETTA)*, vol. 28, no. 4, pp. 523-534, Aug. 2012.

5. M. Lefter, G.R. Voicu, **M. Taouil**, M. Enachescu, S. Hamdioui, and S.D. Cotofana, “Is TSV-based 3D Integration Suitable for Inter-die Memory Repair?” *Design, Automation & Test in Europe Conference & Exhibition (DATE)*, Grenoble, France, March 2013, pp. 1251-1254.

---

## 2.1 Introduction

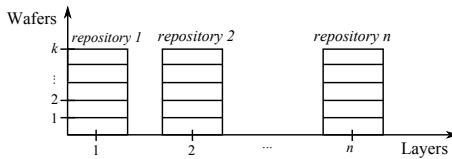

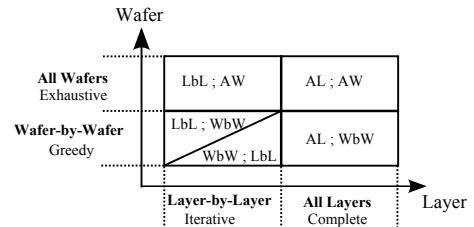

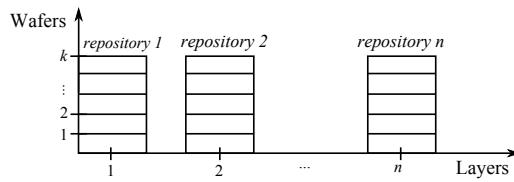

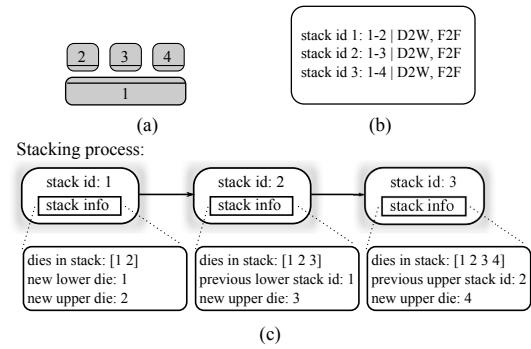

The compound yield of 3D SICs is one of the major challenges as the technology still needs to mature, especially for wafer-to-wafer (W2W) stacked ICs. W2W has several advantages over die-to-wafer (D2W) and die-to-die (D2D) stacking such as a high stacking throughput and the ability to handle thin wafers and small dies. However, it suffers from low compound yield as the stacking of good dies on bad dies and vice versa cannot be prevented. Several methods can be deployed to boost this compound yield. In this chapter, the focus is on three of those methods: (i) *wafer matching*, (ii) *layer redundancy* and (iii) *inter-layer redundancy*.

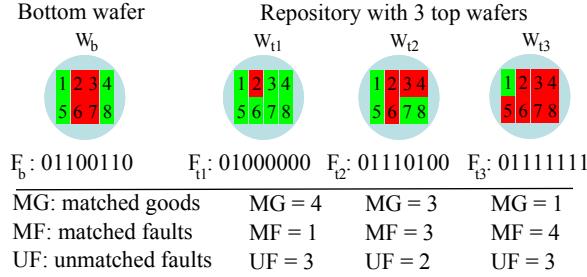

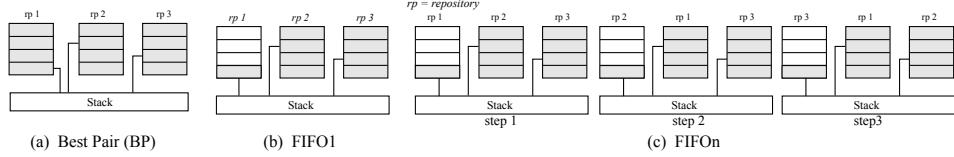

The first method, *wafer matching*, can be generally practiced on all kind of wafers. In wafer matching, a software algorithm keeps track and matches wafer maps; each wafer map contains faulty die locations of a particular wafer. The algorithm matches wafers based on the similarity of fault maps. This increases the compound yield over randomly stacked wafers.

The other methods, *layer redundancy* and *inter-layer redundancy*, are applied in this work only to 3D memory. Nevertheless, they can be applied to any type of 3D-SIC. Traditionally, the memory yield improvement in 2D chips is realized by using spare rows and/or columns to repair defective ones. 3D stacked memories allow the exploration of new repair schemes that take advantage of the vertical dimension. In *layer redundancy*, repair takes place at the wafer level; additional redundant layer(s) are stacked to replace the faulty irreparable memory dies in the stack. In *inter-layer redundancy*, a non-repairable layer (i.e., the number of defective rows and/or columns is more than the available number of spares), borrows additional spares from the neighboring layers. A drawback of this approach, when compared to layer redundancy, is the additional required number of TSVs and the routing complexity to mutually share and access the spare resources among the layers in the stack. Nevertheless, it provides a more effective repair capability.

## 2.2 Main Contributions

This section describes the state-of-the-art and main contributions of the introduced yield improvement techniques.

### 2.2.1 Wafer Matching

The compound yield can be improved by wafer matching, initially introduced by Smith et al. [27]. In [83], Ferri et al. used wafer matching to increase the parametric yield of a two layered D2W stacked 3D-SIC. Only functional dies are considered in this case to produce an optimal binning; i.e., maximize the fastest speed bins and minimize the slowest ones. Wafer matching is then used to combine and improve the 3D parametric yield by including the process variation of both layers in a D2W stacking approach. The authors were able to increase the number of 3D-SICs in the fastest speed bins as well as simultaneously reducing the num-

ber of slow 3D-SICs. More elaborated studies of wafer matching regarding the functional yield are presented in [84, 85], e.g., by considering different die yields, stack and repository sizes, etc. In [86] the author presents wafer rotation; each wafer can be rotated with pre-defined angles before stacking. However, this imposes restrictions on the die orientations. Rotating wafers gives more freedom in stacking and therefore increases the compound yield. In [87, 88] the same author presents a model that also considers radial defect clustering; these publications show that the compound yield is higher than the case where wafers are considered to have a random defect distribution.

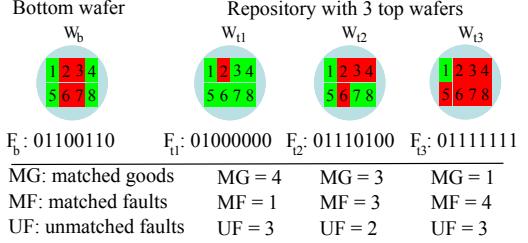

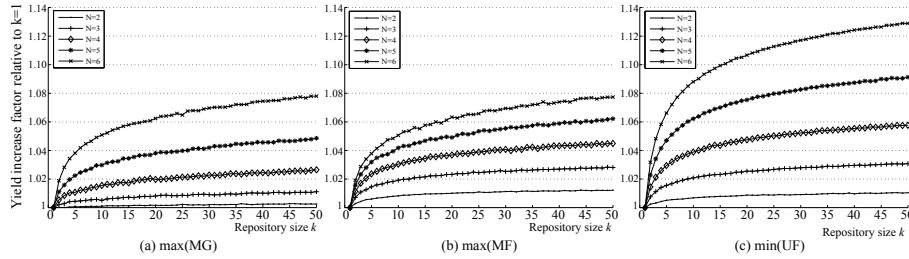

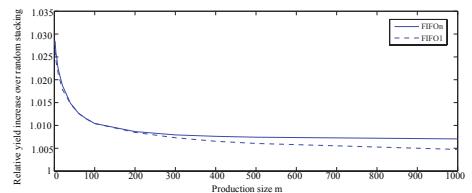

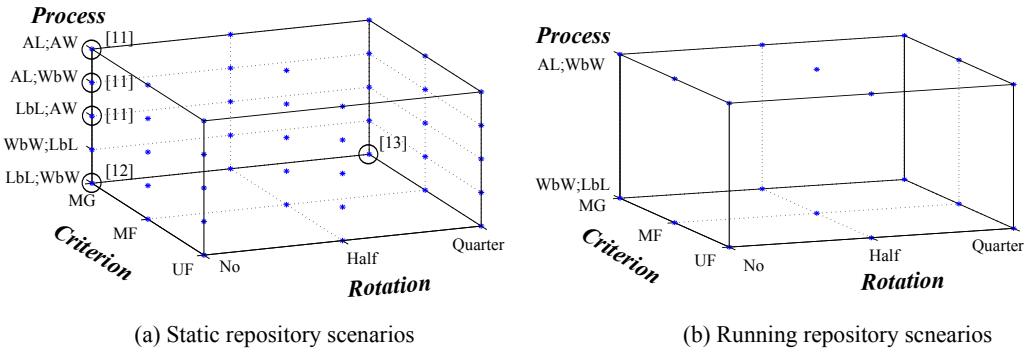

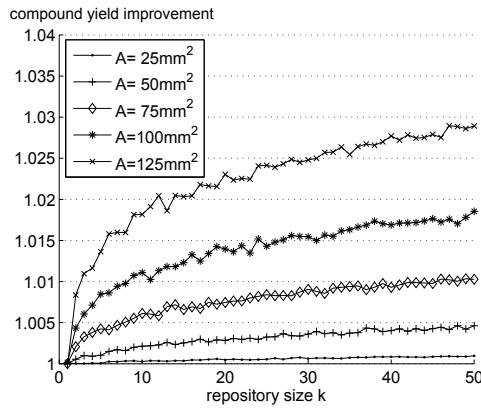

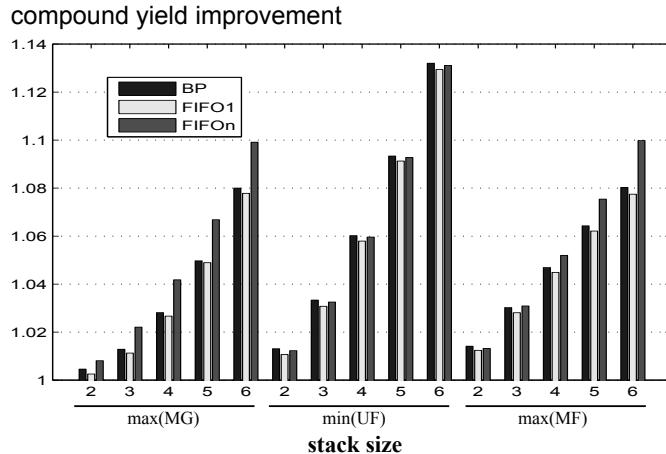

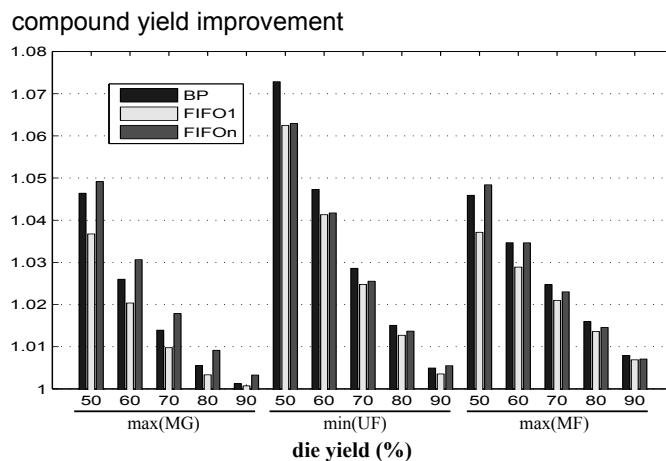

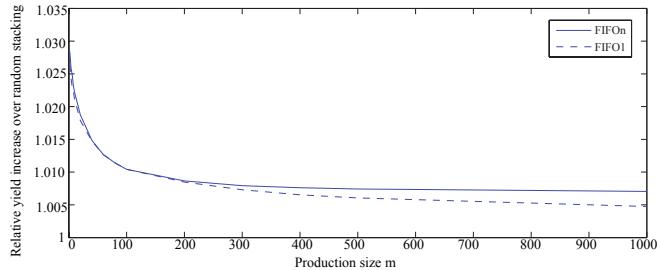

All the related previous work considered static repositories (i.e., the repositories are not replenished unless they are empty) and used a single wafer matching criterion (matching of the good dies from the bottom layer with the good dies from the top layer). However, the matching could also be based on faulty dies instead of good dies. Our contributions [68, 69] are summarized as follows.

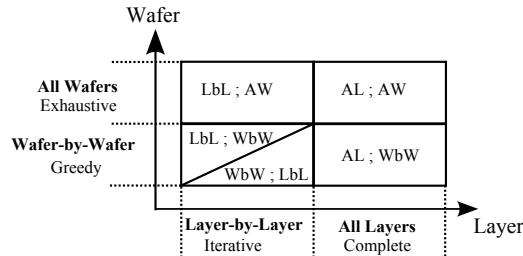

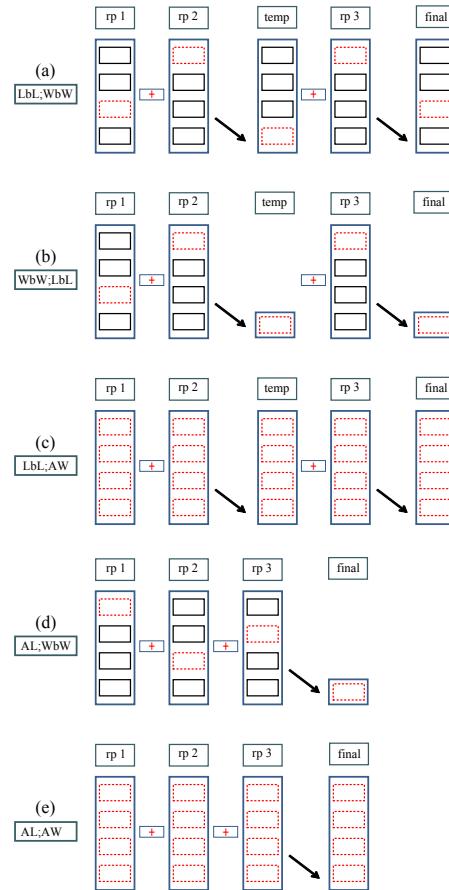

- The introduction of the concepts *matching process*, *matching criterion*, and *matching scenario*. The matching process defines how the repositories are traversed and how many wafers are selected from each repository visit at a time. The matching criterion specifies whether the matching of good or bad dies are maximized or whether the mismatch of good and bad dies are minimized. The matching scenario is defined by its matching process, matching criterion, and whether or not wafer rotation is applied, and its repository type (i.e., static or running repositories). Note that the matching process mainly determines the time and memory complexity of the matching scenario.

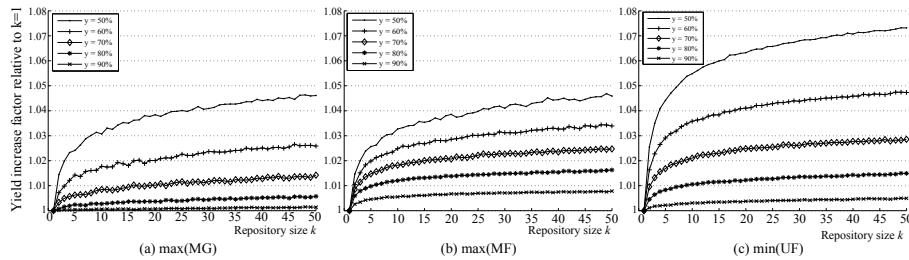

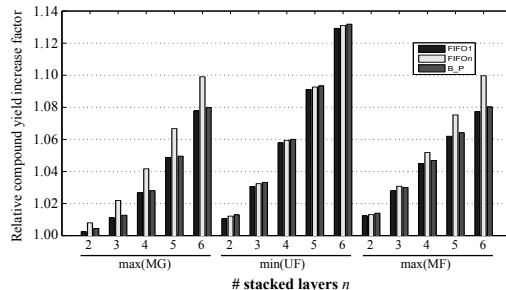

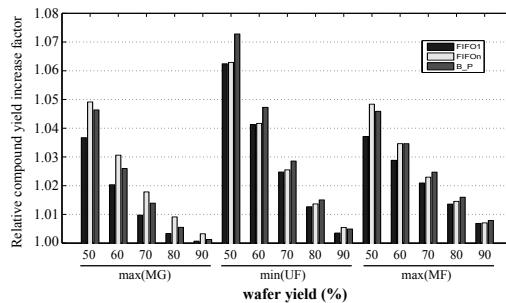

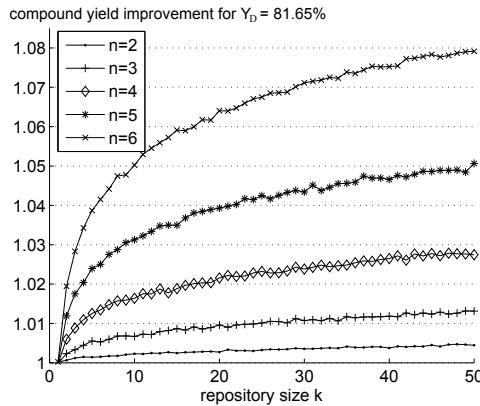

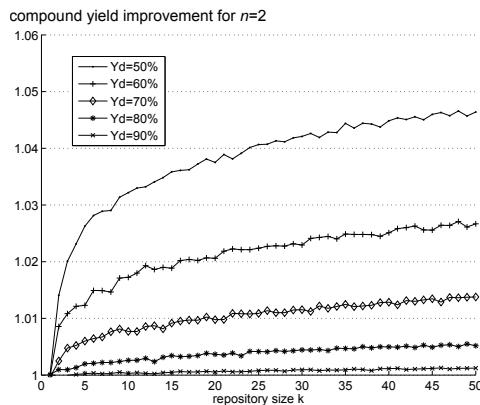

- The impact of several matching processes and matching criteria on the compound yield of 3D-SICs have been analyzed for running repositories. In running repositories, wafers are immediately replenished after matching.

- The optimal matching scenario for running repositories strongly depends on the yield of the stacked dies. We have created a Best Pair scenario that adaptively selects the optimal matching criterion based on given yields.

- Several comparisons are performed between static and running repositories using different matching processes both with and without wafer rotation.

- A new framework is constructed that covers all matching processes and wafer matching criteria for both static and running repositories. The framework does not only allow us to map prior work on it, but it also shows the space of uncovered matching scenarios.

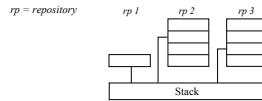

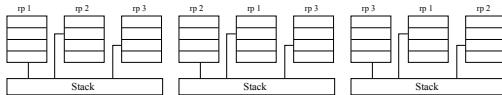

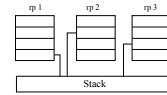

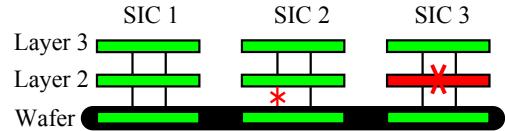

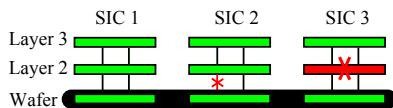

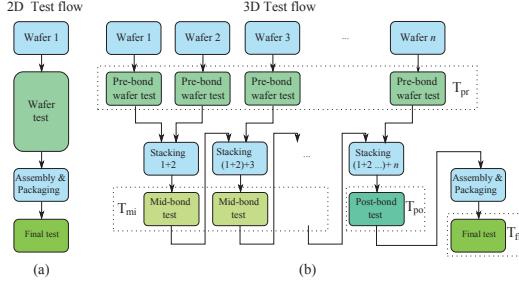

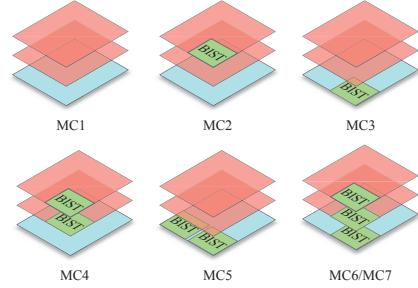

### 2.2.2 Layer Redundancy

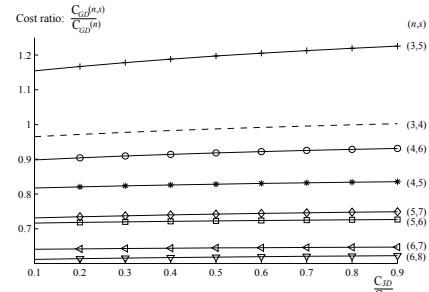

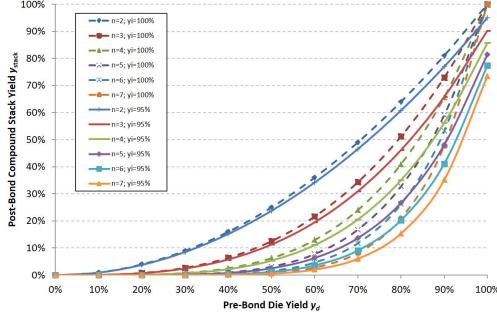

With respect to layer redundancy, the following contributions are made [38, 70].

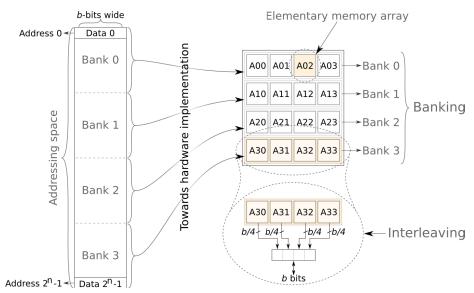

- A classification of 3D memories and 3D memory redundancy repair schemes is provided. The partitioning of memories across multiple device layers can take place at different granularity resulting in different architectures. Our 3D memory classification shows the advantages and disadvantages of each partitioning scheme. The redundancy schemes for 3D stacked memories can be classified into three groups, i.e., intra-layer, inter-layer and layer redundancy. Intra-layer redundancy accesses uses local spares only (located on the same die), inter-layer redundancy may access spares on neighbor dies, and in layer redundancy faulty dies are completely replaced by spare dies.

- An analytical model is presented that formulates the compound yield improvement by using layer redundancy. This model takes into corporation the yields of the pre-bond dies, the die yield of the stacking operations, and the interconnect yield.

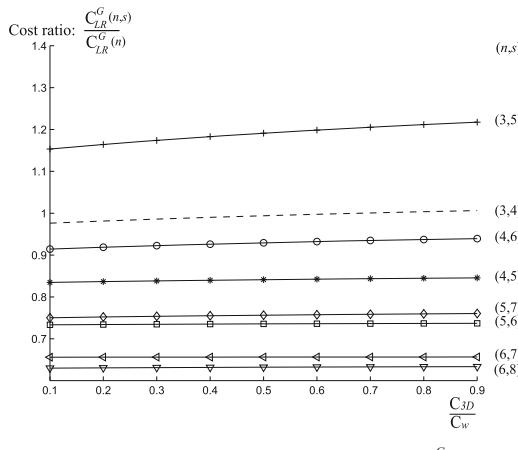

- A comparison of 3D W2W stacked memories with and without layer redundancy is presented in terms of yield and overall cost. The question rises whether it is cost-wise justified to increase the yield by adding more redundant layers. Therefore, the yield comparison is expanded to a cost comparison in which both yield and manufacturing cost are included. The results show huge yield and cost benefits.

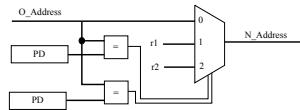

- A memory layer replacement circuit that maps the addresses of faulty memory layer(s) to the spare layer(s) is developed. This circuit converts these addresses at run-time with a minimum timing penalty.

- In addition to the above, we have investigated the merged effect of applying simultaneously wafer matching and layer redundancy. First, a comparison is made between layer redundancy and wafer matching. Thereafter, both methods are merged into a single combined technique. The results typically show that layer redundancy outperforms wafer matching both from yield and cost viewpoint. When both methods are merged, further yield and cost improvements are obtained.

### 2.2.3 Inter-Layer Redundancy

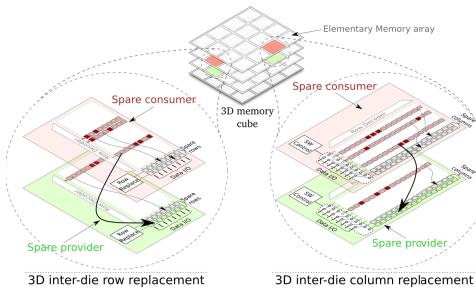

Several authors presented inter-die memory repair as a means to increase the compound memory yield [16, 39, 89–92]. All these publications focused primarily on yield benefits typically evaluated through fault injection simulation. However, the obtained yield improvements form a theoretical upper bound and the challenges of actual silicon implementations have been simply overlooked; examples are the impact on area, layout and latency. Proper infrastructure must be embedded in the 3D memory to allow spares to be shared vertically in the stack. Our contributions are as follows [71].

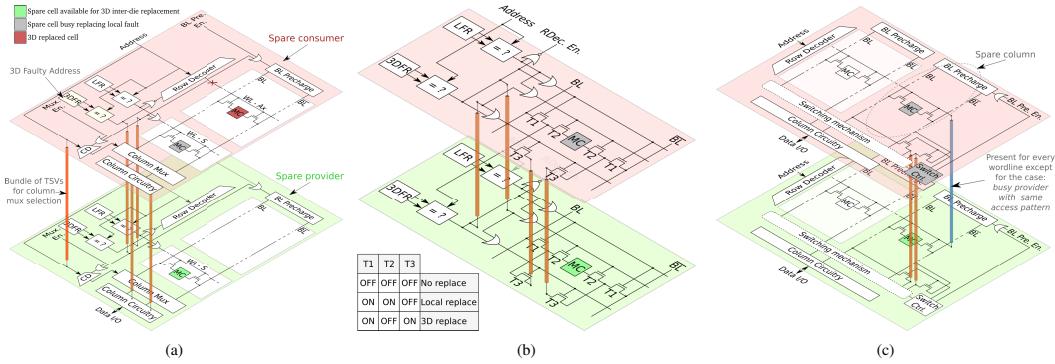

- An overview of possible spare access scenarios in a 3D memory cube based on spare providers and spare consumers is provided. The spare providers have available spare resources and the spare consumers make use of externally available spares of the neighbor dies. Each provider-consumer pair satisfies one of three possible scenario's

[71]: (i) Idle provider - the two stacked arrays of the provider and consumer are part of different banks that are never concurrently accessed; (ii) Busy provider with different access pattern - the two arrays are part of different banks that are concurrently accessed with independent addresses (e.g., by having multiple memory ports); (iii) Busy provider with same access pattern - the two arrays are part of the same interleaved bank; therefore, they have the same address.

- Several implementation schemes are provided both for inter-die row and column repair with detailed circuit infrastructure. Advantages, disadvantages of the impact on memory area and latency are evaluated for each scheme. The results suggest that current state-of-the-art TSV dimensions make inter-die column repair schemes feasible at the expense of reasonable area overhead. However, most row-repair memory configurations require TSV dimensions to scale down at least with one order of magnitude for practical implementations.

- We performed theoretical analysis of the implications of the proposed 3D repair schemes on the memory access time.

## 2.3 Evaluation

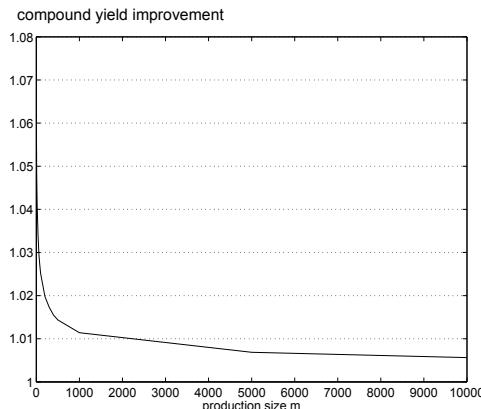

Our results and analysis show that the compound yield can be improved by using wafer matching with running repositories which have a lower time and memory complexity. Compared to the state-of-the-art, running repositories outperform static repositories irrespective of the design and manufacturing parameter values (e.g. stack size, die yield), and by using a relative less complex matching process. The best matching criterion to be used for highest compound yield improvement is strongly stack size and die yield dependent; hence, using adaptive matching criterion selection is the optimal solution.

In addition, it is worth to mention several interesting aspects related to wafer matching.

- The absolute compound yield of W2W stacked 3D-SICs is typically low. Therefore, the applied redundancy schemes presented in this chapter impact the compound yield and reduce the cost significantly. Nevertheless, the absolute yield remains low. Hence, W2W stacking should be considered only out of necessity (like stacking small dies), or when the die yield is high.

- The down-side of the matching process in [85] for static repositories is the forcing of stacking bad wafers when the repositories become emptier. The authors presented a scenario with a greedy matching process; each time the two wafers with the highest yields are selected out of the repositories for stacking. Hence, bad wafers remain in the repositories till the end. To counteract this problem, we have proposed running repositories in which wafers in the repositories are directly replaced after being selected for stacking. This approach does not increase the run-time and memory-complexity of the

algorithm and more importantly, the proposed matching is performed each time using full repositories. However, the authors of [84] presented an optimal algorithm for static repositories based on interlinear programming, which quickly runs out of memory and its execution time is a major bottleneck even for limited number of stacked dies and reasonable repositories sizes.

- In [87] the author introduced wafer rotation where wafers can rotate with angles of 90, 180 or 270 degrees. Obviously, wafer mask designers have to take this into consideration in order to make it feasible, although it may impact the die yield. In addition, stacking equipment need to be modified to support the rotation of wafers. Therefore, rotating is an interesting concept but practically hard, if not impossible, to realize. Moreover, the additional yield benefit due to wafer rotation is marginal [69]. In [93], the authors generalize this concept further by cutting wafers into segments prior to stacking; this leads to a stacking approach between D2D and D2W stacking. This is even more complex to realize as it is very demanding in terms of processing and equipment.

- The impact of wafer matching reduces when the radial clustering defect is considered; the yield benefits in wafer matching are due to random defects. In case the wafers to be stacked are from the same manufacturing line, higher compounds yields are expected as both wafers will most probably suffer from the same systematic defect distribution (e.g., defects at the edge of the wafers); hence, wafer matching is less effective in such cases. In case wafers are coming from different manufacturing lines (e.g., in DRAM stacked on logic), lower compounds yields are expected when the location of the systematic defects on both wafers differs.

- Running repositories may also have practical implementations. One of its concerns is a polluted repository in which bad wafers would remain for a long period in the repository, thereby reducing the effective repository size. Proper filters that force such wafers to be removed from the repository could become necessary. In addition, pre-filters could be set in place to prevent wafers with a very low yield from entering the repository; these wafers need to be processed separately. In particular, the process of replenishing wafers needs attention. One implementation is to consider a secondary repository in which wafers are only used to replace selected wafers from the main repository.

Layer redundancy improves the yield and reduces the cost significantly as the absolute compound yield is low. In inter-layer redundancy, the repair occurs on a much finer granularity (therefore, it is area-wise more effective) and its theoretical yield improvements are even better [16, 39, 89–92]. However, layer redundancy is from a practical point easier to implement. Our preliminary conclusion for inter-layer redundancy shows that only inter-die column redundancy is feasible with current TSV sizes. In addition, more research is required to conclude its practicality. For example, accurate timing analysis need to be performed for a memory layout which includes the redundancy repair logic, the required TSVs to access

the spare cells, and their KOZ. This is important as the timing is very critical in memories [37]. In addition, more research is required for low-cost inter-layer repair schemes for stacks containing more than two dies.

# Chapter 3

## Cost Modeling

The content of this chapter is based on the following research articles:

1. **M. Taouil** and S. Hamdioui, “On Optimizing Test Cost for Wafer-to-Wafer 3D-Stacked ICs,” *7th International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS)*, Tunis, Tunisia, May 2012, pp. 1–6.

2. **M. Taouil**, S. Hamdioui, K. Beenakker, and E.J. Marinissen, “Test Cost Analysis for 3D Die-to-Wafer Stacking,” *19th IEEE Asian Test Symposium (ATS)*, Shanghai, China, Dec. 2010, pp. 435–441.

3. **M. Taouil**, S. Hamdioui, and E.J. Marinissen, “How Significant will be the Test Cost Share for 3D Die-to-Wafer Stacked-ICs?” *6th International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS)*, Athens, Greece, April 2011, pp. 1–6.

4. **M. Taouil**, S. Hamdioui, K. Beenakker, and E.J. Marinissen, “Test Impact on the Overall Die-to-Wafer 3D Stacked IC Cost,” *Journal of Electronic Testing: Theory and Applications (JETTA)*, vol. 28, no. 1, pp. 15–25, Feb. 2012.

5. **M. Taouil** and S. Hamdioui, “Stacking Order Impact on Overall 3D Die-to-Wafer Stacked-IC Cost,” *14th IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS)*, Cottbus, Germany, April 2011, pp. 335–340.

6. **M. Taouil**, S. Hamdioui, and E.J. Marinissen, “On Modeling and Optimizing Cost in 3D Stacked-ICs,” *6th IEEE International Design and Test Workshop (IDT)*, Beirut, Lebanon, Dec. 2011, pp. 24–29.

7. **M. Taouil**, S. Hamdioui, E.J. Marinissen, and S. Bhawmik, “Using 3D-COSTAR for 2.5D Test Cost Optimization,” *IEEE International 3D Systems Integration Conference (3DIC)*, San Fransisco, CA, USA, Oct. 2013, pp. 1–8.

8. **M. Taouil**, S. Hamdioui, E.J. Marinissen, and S. Bhawmik, “Impact of Mid-Bond Testing in 3D Stacked ICs,” *16th IEEE Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT)*, New York, NY, USA, Oct. 2013, pp. 178–183.

9. **M. Taouil**, S. Hamdioui, E.J. Marinissen, and S. Bhawmik, “Quality versus Cost Analysis for 3D Stacked ICs,” *32nd IEEE VLSI Test Symposium (VTS)*, Napa, CA, USA, April 2014, pp. 1–6.

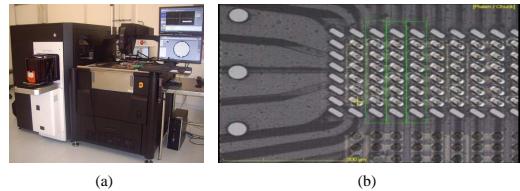

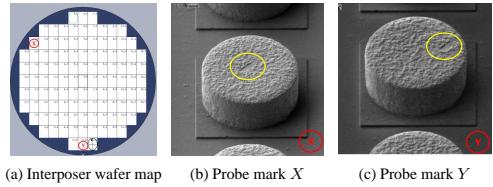

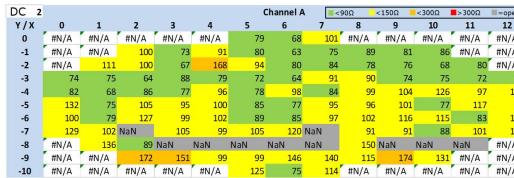

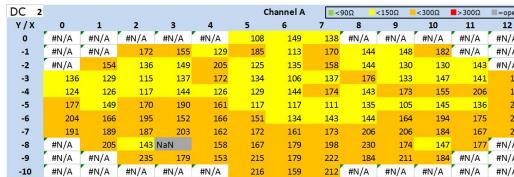

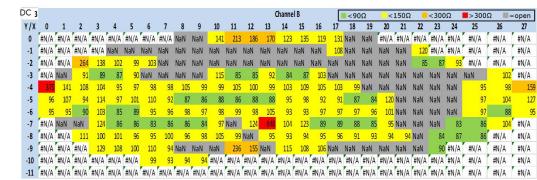

10. E.J. Marinissen, B. de Wachter, K. Smith, J. Kiesewetter, **M. Taouil**, and S. Hamdioui, “Direct Probing on Large-Array Fine-Pitch Micro-Bumps of a Wide-I/O Logic-Memory Interface,” *International Test Conference (ITC)*, Seattle, WA, Oct. 2014, pp. 1–10.

### 3.1 Introduction

ICs are manufactured in highly specialized fabs following a long sequence of defect-prone steps [94]. This makes testing an unavoidable expense as it must identify deficient ICs and prevent them from being shipped to customers. In return, testing adds value as it reduces the number of test escapes which satisfies the customers [95]. In particular markets, such as the automotive, medical, and aerospace industry, extremely low test escape rates are demanded [96]. Therefore, testing is subjected to cost versus quality trade-offs [97].

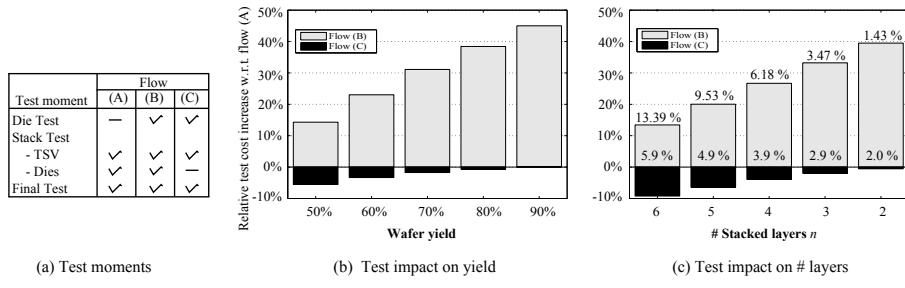

Defining optimal test strategies for 3D-SICs is more challenging as compared to planar ICs due to the significant increase in number of test moments. A planar IC has typically only two test moments; a wafer test prior to packaging and a final test after packaging [98]. The wafer test is cost-effective when the cost of faulty packaged ICs would exceed the test cost. The final test is used to guarantee the final quality of the packaged chips. However, 3D-SICs have many test moments denoted by a pre-bond, mid-bond, post-bond and final test. Pre-bond tests may prevent defective dies from entering the stack, while mid-bond (for partial stacks) and post-bond tests (for the complete stack prior to packaging) are used to verify the dies and interconnects after stacking. In addition, the post-bond test prevents faulty 3D-SICs from being packaged. The final test, applied after packaging, can be used to satisfy the product quality.

Testing dies in all the test phases might lead to test overhead. Therefore, careful analysis must identify in which stage to test. Whether or not to perform a particular test depends primarily on the yield. Even Known Good Dies (KGD) obtained through the pre-bond test are not guaranteed to survive the stacking processing; new defects from the stacking process are unavoidable. Typical sources of failures during stacking include thinning, bonding, as well as TSV failures such as misalignments and opens [62]. Depending on the quality or yield of such a stacking process, retesting of dies in the stack might be cost-wise favorable. If it is known beforehand that a particular stack is malfunctioning, additional silicon, stacking, and bonding costs can be prevented for the successive dies that have to be stacked. Therefore, early testing may prevent further down-stream processing costs.

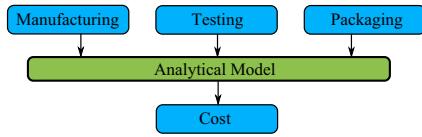

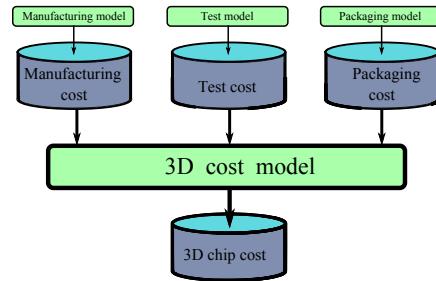

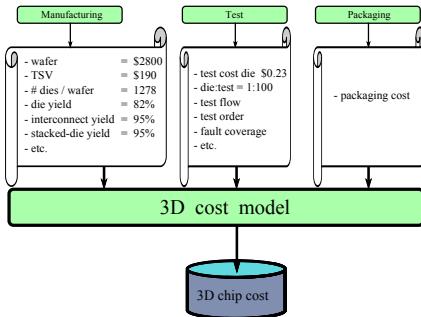

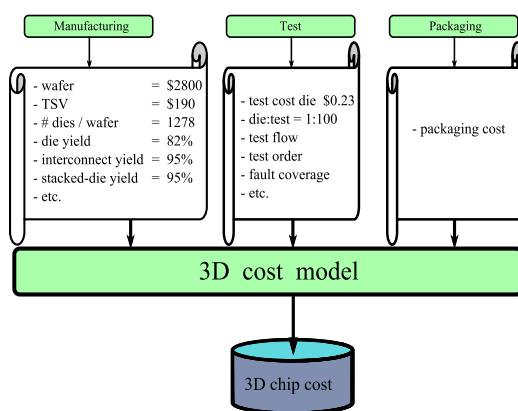

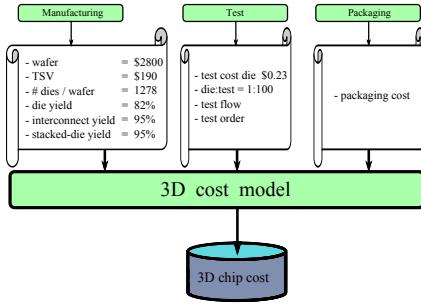

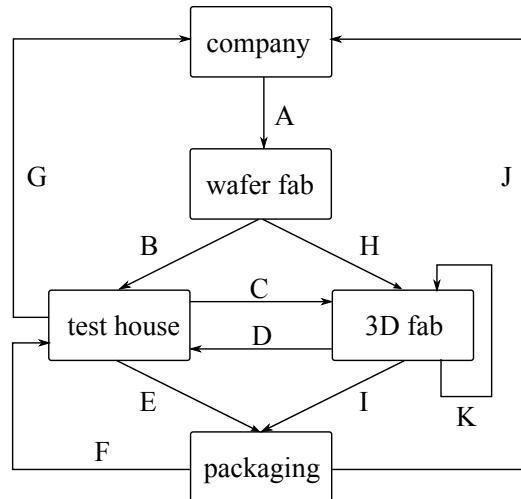

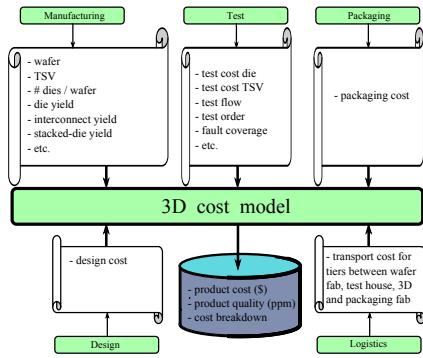

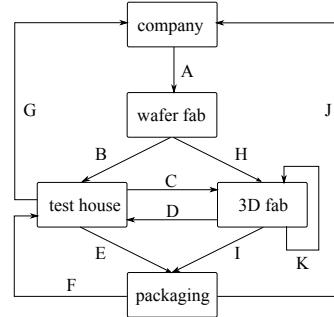

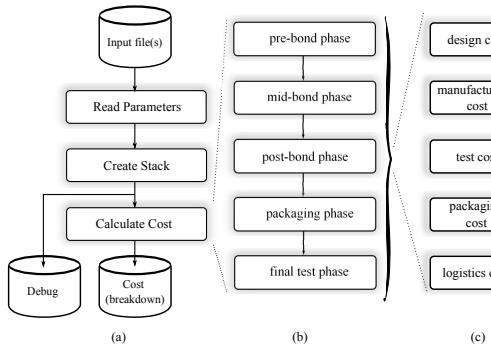

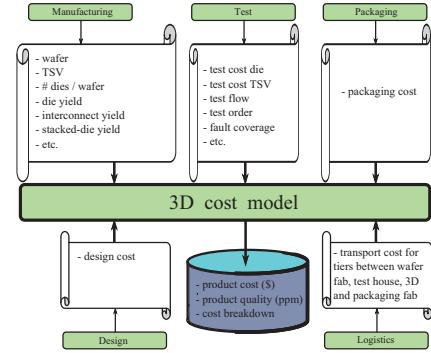

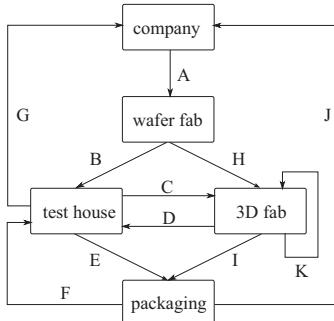

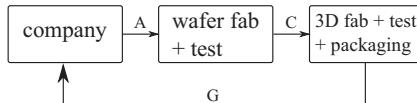

Figure 3.1 shows the typical IC production cycle. There is a design, manufacturing, test, and packaging phase prior to the shipment to the customer. The customer demands products that work during the prescribed life time. This puts certain constraints on the quality of the test. The challenge is to single out proper test flows, i.e., to find out in which test phase to apply tests and to define what exactly to test for. This strongly depends on inputs from design, manufacturing and packaging as well. After the test flow is determined, proper DfT must be added to the chip to support the desired fault coverage, for example by using Memory Built-in Self Tests (MBISTs), Boundary Scan, scan chains etc. This DfT has to be inserted in the netlist at design time. Therefore, a sophisticated cost model must be developed that incorporates not only the test phases (pre-, mid-, post-bond and final testing), but also

manages cost inputs from other classes such as design, manufacturing, etc. In addition, it should be able to estimate the total 3D-SIC cost and its product quality.

Figure 3.1: From design to 3D-SIC.

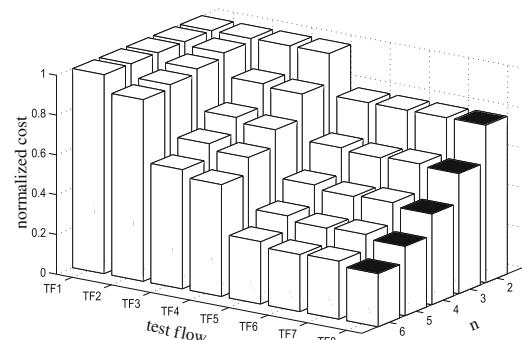

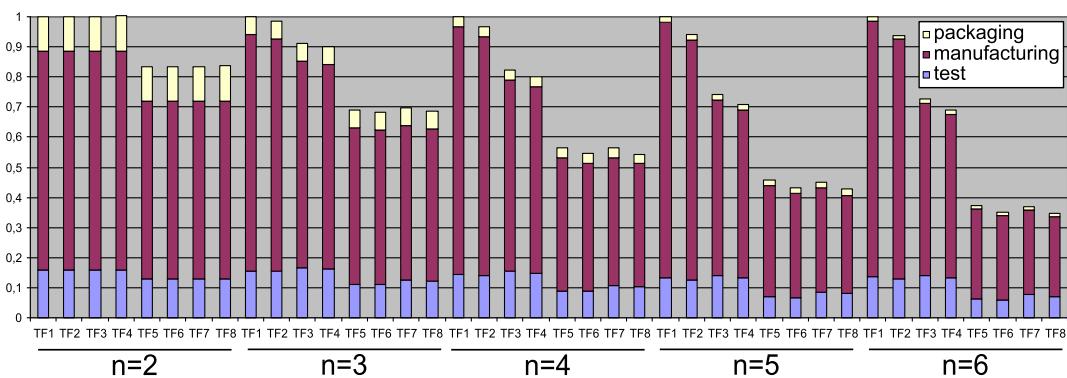

## 3.2 Main Contributions

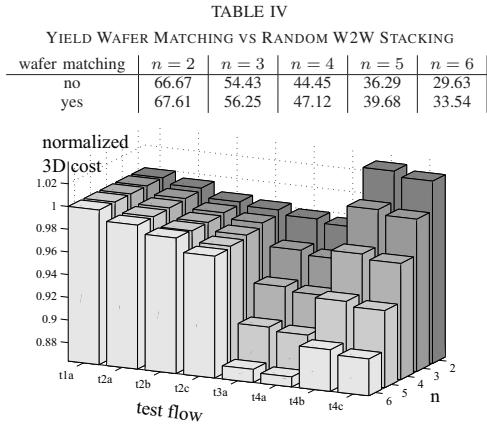

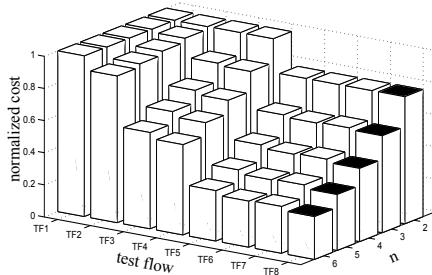

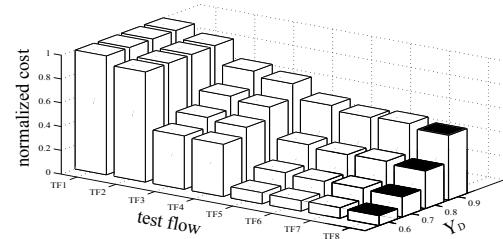

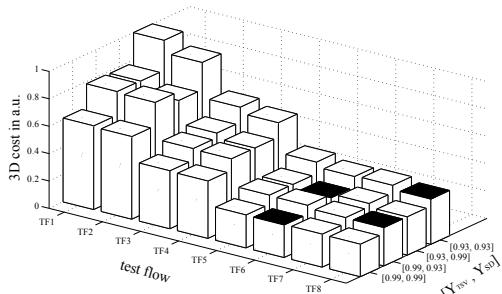

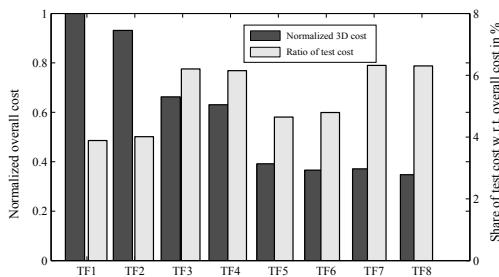

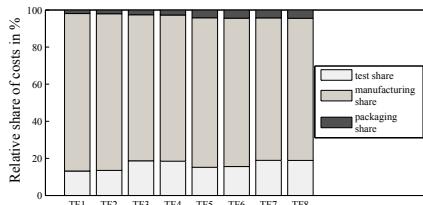

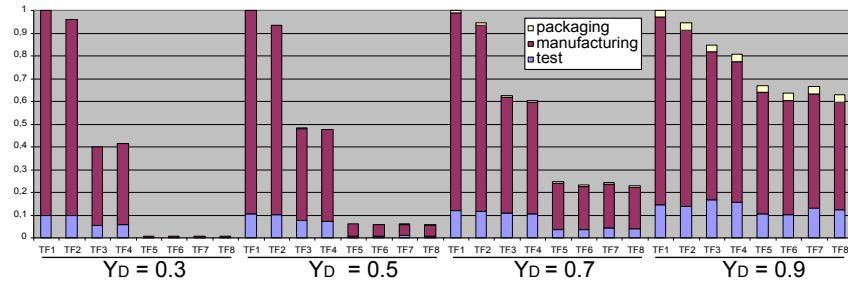

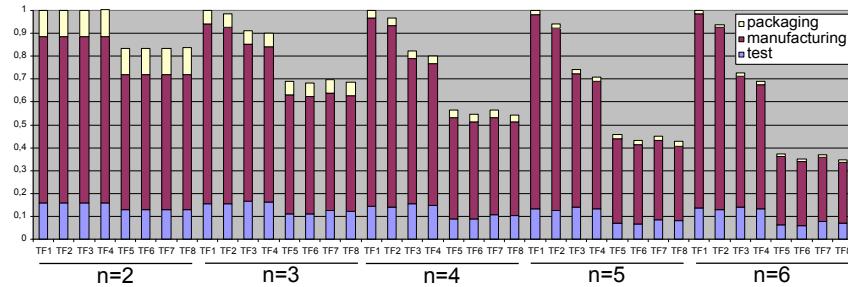

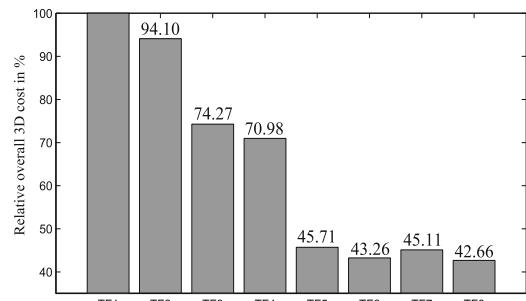

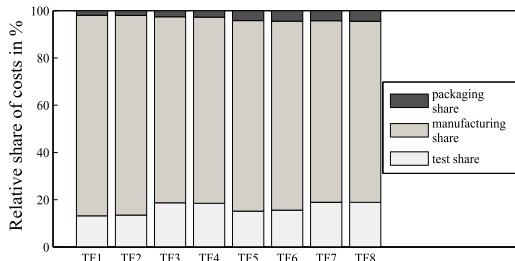

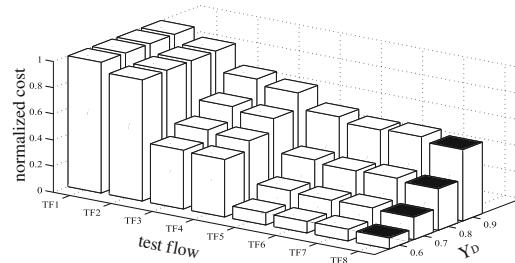

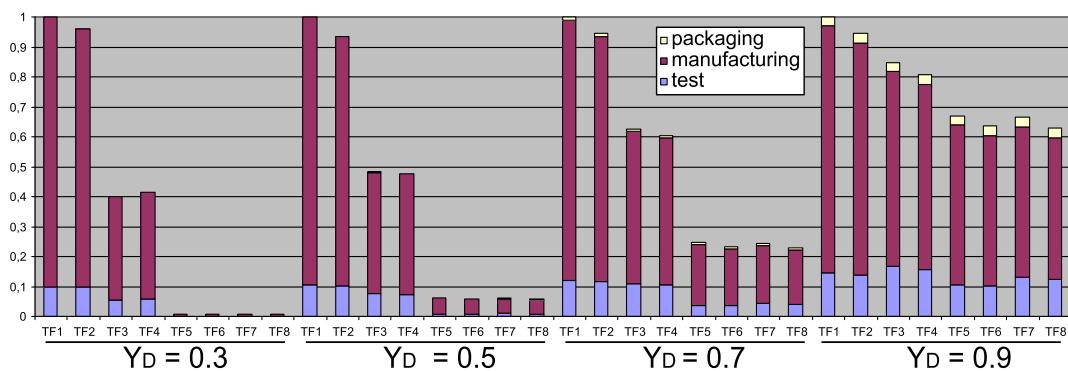

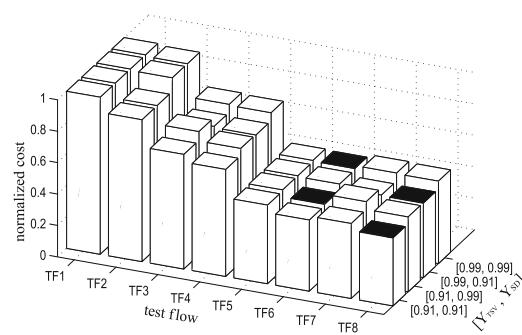

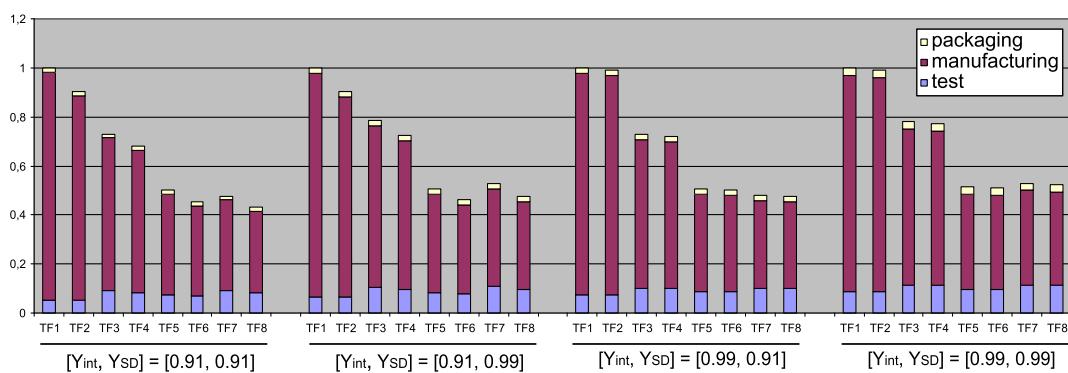

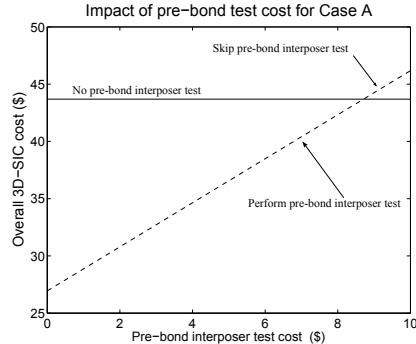

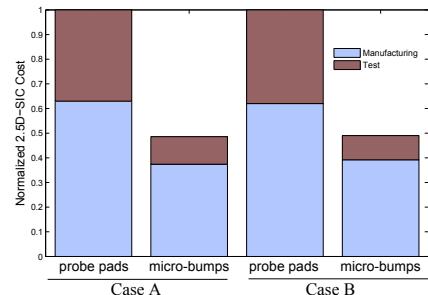

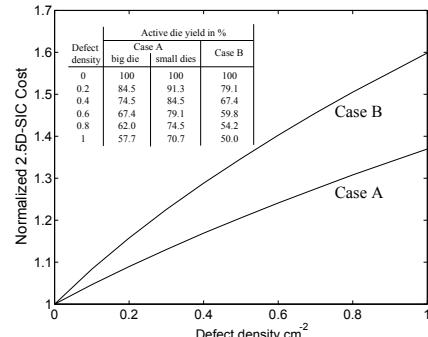

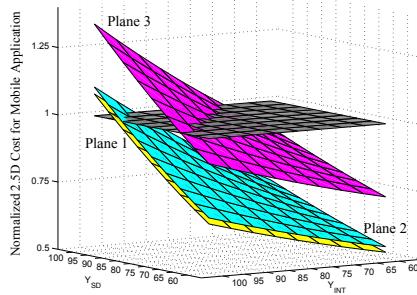

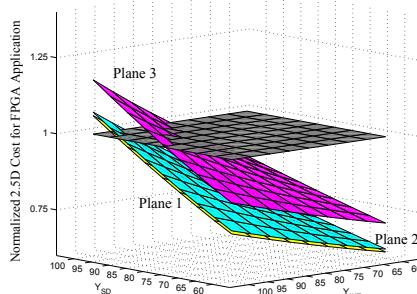

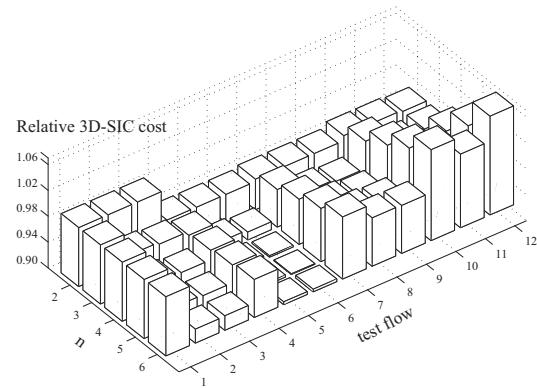

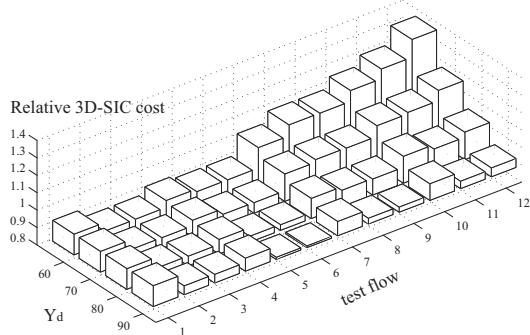

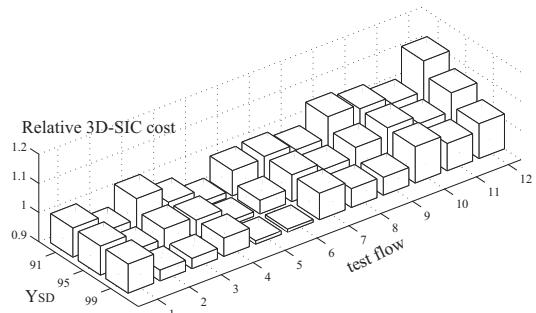

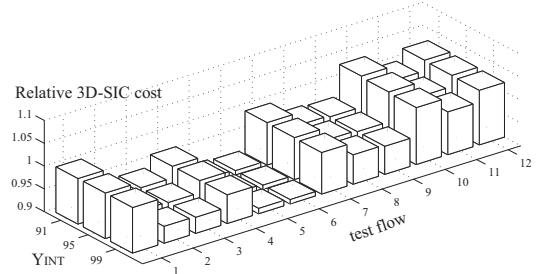

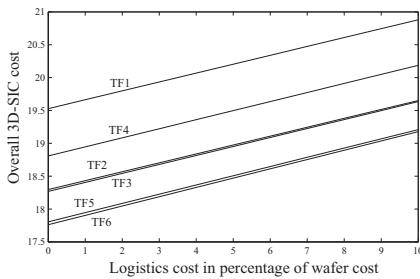

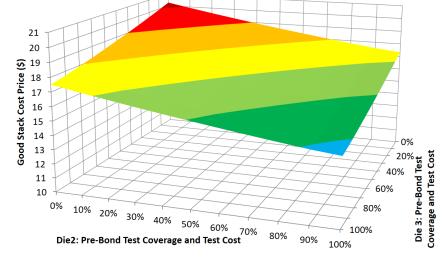

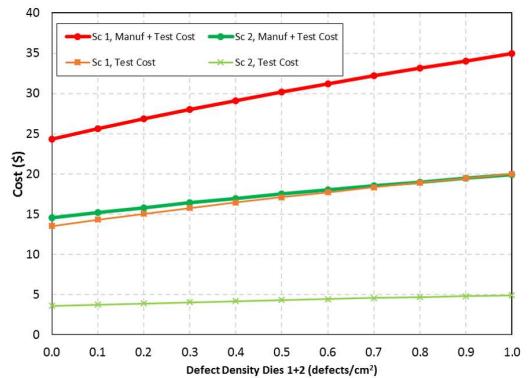

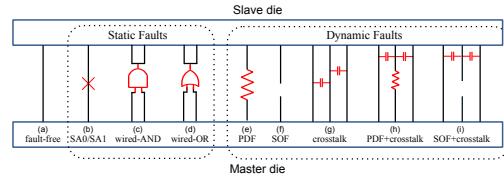

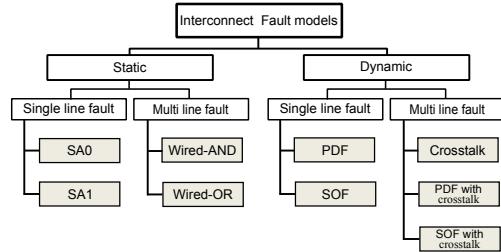

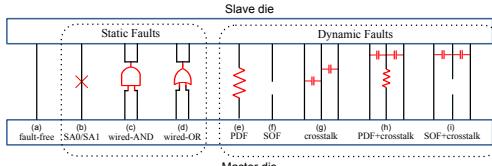

Several cost models have been published in the 2.5D and 3D area. Most of them have focused on cost modeling for 3D manufacturing [99, 100], stacking and integration [101–106], TSV count and die area [107, 108]. However, limited work is published on test cost modeling and its impact on the overall chip quality and cost. In [109], the authors proposed a cost model that emphasizes on manufacturing and test cost; the authors investigated the impact of Die-to-Wafer (D2W) and Wafer-to-Wafer (W2W) stacking on overall cost and determined the lower bound of the yield of the final package level test given the number of stacked dies and the final yield. In [110], the author propose heuristics to find cost-wise optimal test flows that include mid-bond testing. They consider only manufacturing and test cost.