# Software-Enabled Modular Instrumentation Systems

# Software-Enabled Modular Instrumentation Systems

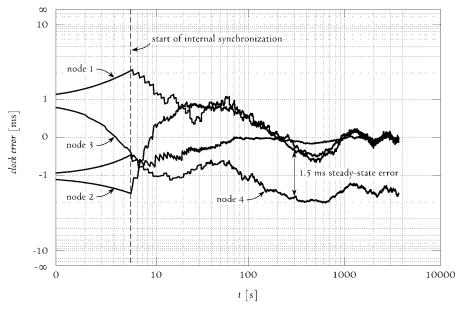

Proefschrift

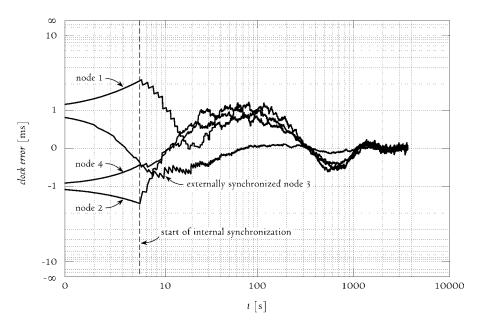

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.dr.ir. J.T. Fokkema, voorzitter van het College voor Promoties, in het openbaar te verdedigen op woensdag 26 november 2003 om 10:30 uur door

> Marco Willem SOIJER ingenieur luchtvaart en ruimtevaart

> > geboren te Nijmegen

Dit proefschrift is goedgekeurd door de promotor: Prof.dr.ir. J.A. Mulder

Samenstelling promotiecommissie:

Rector Magnificus, voorzitter Prof.dr.ir. J.A. Mulder, Technische Universiteit Delft, promotor Prof.ir. B.A.C. Ambrosius, Technische Universiteit Delft Prof.dr. A.J. van der Wal, Universiteit Twente, Enschede Prof.dr. M.H. van Emden, University of Victoria Prof.Dr.-Ing. W. Alles, Rheinisch-Westfälische Technische Hochschule, Aachen Prof.Dr.-Ing. P. Vörsmann, Technische Universität Carolo-Wilhelmina, Braunschweig Dr.ir. M.M. van Paassen, Technische Universiteit Delft

ISBN 90-9017445-1

Published 2003 by Marco W. Soijer Printed in the Netherlands by Ponsen & Looijen, Wageningen Aan mijn Moeder

## Software-gefaciliteerde

## Modulaire Instrumentatiesystemen

Soijer, M.W. (2003). Software-Enabled Modular Instrumentation Systems (Dissertation, Delft University of Technology), ISBN 90-9017445-1.

#### Samenvatting

De snelle ontwikkeling van computersystemen in de jaren 1980 en 1990 leidde tot de mogelijkheid om vliegproefdata-acquisitie en -verwerkingstechniek te integreren. Vliegende simulatoren, het genereren van adaptieve signalen in ware tijd voor experimenten in een gesloten lus en het analyseren van gegevens tijdens de vlucht zijn nieuwe toepassingen in het bereik van vliegproeven die in de afgelopen decennia voor het eerst werden gedemonstreerd. De bijbehorende introductie in vliegende toepassingen van apparatuur die traditioneel op de grond wordt ingezet, heeft tot een stijging van het aantal verschillende computersystemen geleid waarop de vliegproefgegevens worden verwerkt. De betrouwbaarheid en mogelijkheid tot verandering en uitbreiding van instrumentatiesystemen en verwerkingsgereedschappen hebben geleden onder deze paradox van computersysteemdifferentiatie. Om de situatie te verbeteren, is een algemeen toepasbare methodologie voor het ontwikkelen van vliegproefinstrumentatiesystemen voor signaalverwerking in ware tijd ontwikkeld, die zowel simulatie vóór, dataacquisitie tijdens, als gegevensverwerking na de vlucht omvat.

De methodologie gebruikt een object-georiënteerde benadering om het concept van intelligente instrumentatie – waarbij sensoren, actuatoren en signaalvoorbereiders worden geïntegreerd in componenten die via een standaardinterface communiceren – te implementeren in een op software gebaseerde omgeving die met conventionele sensoren en transducers samenwerkt. De omgeving maakt het mogelijk instrumentatiesystemen met een gesloten lus en real-timegedrag modulair te ontwikkelen. De omgeving draagt via de middleware zorg voor het activeren van sensoren, transducers en verwerkingscomponenten op de juiste tijd. Daarnaast stelt de middleware een gesynchroniseerde schatting van de ware tijd ter beschikking op alle locaties in het systeem.

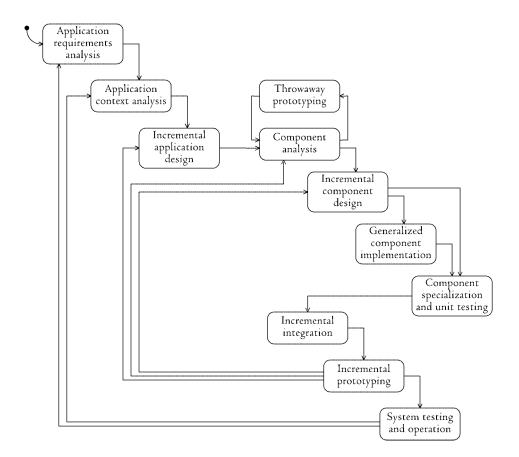

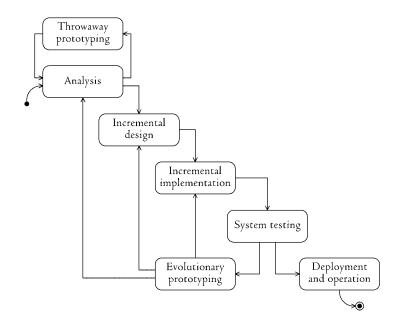

De maatgesneden levenscyclus voor het ontwikkelen van dergelijke vliegproefinstrumentatiesystemen is een combinatie van het evolutionaire-prototypemodel en elementen uit throwaway prototyping en hiërarchisch ontwerpen zoals gebruikelijk in software engineering. De methode legt sterk de nadruk op het ontwikkelen van standaardcomponenten – zowel voor hardware als voor software – die in meer toepassingen zijn te gebruiken. De ontwikkeling van de componenten is daarom in een eigen levenscyclus geplaatst. Standaardcomponenten worden gespecialiseerd voor de specifieke toepassing; de levenscyclus van de toepassing bestaat voornamelijk uit het vastleggen van eisen en het maken van een algemeen ontwerp voordat de componenten worden ontwikkeld en de integratie van het systeem nadat de componentenontwikkeling is afgerond.

Afhankelijk van de wijze waarop verwerkte gegevens worden teruggekoppeld naar het testsignaal van het systeem, wordt een vliegproefsysteem geclassificeerd als een openlussysteem, een adaptief systeem, een ergonomiesysteem, of een vliegende simulator. Als uitbreiding op de verzameling diagrammen die de Unified Modeling Language omvat, is een nieuw type noodzakelijk voor de analyse van een signaalverwerkingsssysteem. Het nieuwe diagram, genaamd signaaldiagram, modelleert de volledige gegevensstroom door het systeem, waarbij de nadruk op de gegevens zelf ligt en niet op de componenten die de gegevens produceren of verwerken. Samen met een contextmodel dat de typische structuur van de vier toepassingstypes reflecteert, vormt het signaaldiagram de basis voor het systeemontwerp.

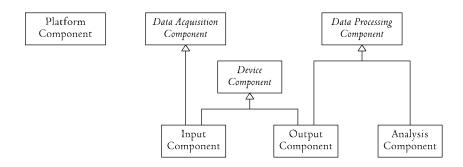

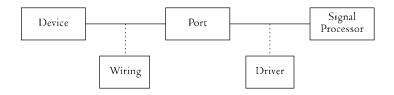

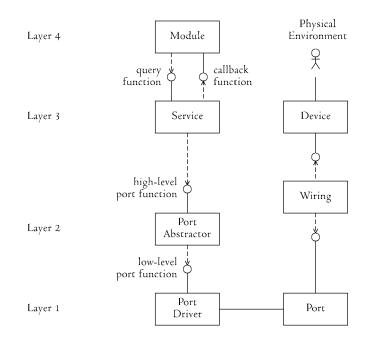

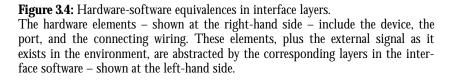

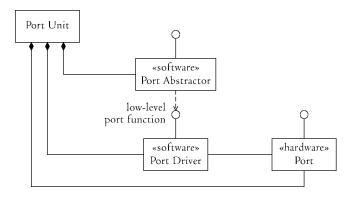

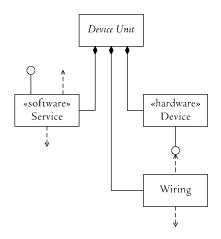

De componenten van een meetsysteem worden onderverdeeld in drie groepen: platform-, acquisitie- en verwerkingscomponenten. Elke groep omvat zowel hardware- als software-elementen. Voor componenten die gegevens in- of uitvoeren, wordt maximale herbruikbaarheid bereikt door het ontwerp te verdelen in hiërarchische lagen. Een vierlagenmodel scheidt de in- en uitvoerhardware van de signaalverwerker, de bijbehorende besturingssoftware en bekabeling, de sensor of actuator en de software die met de andere componenten samenwerkt in gestandaardiseerde abstractieniveau's. Elk element is hierdoor uitwisselbaar zonder dat de andere delen hoeven te worden aangepast.

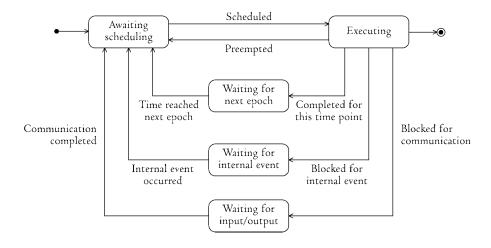

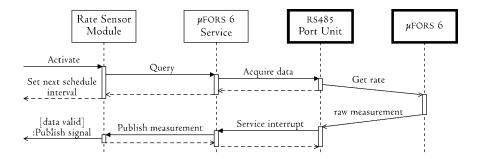

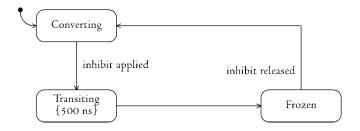

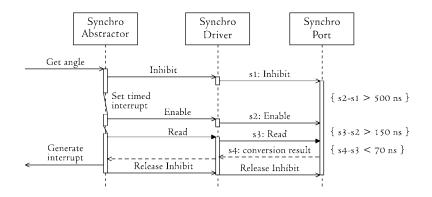

Middleware voor een digitaal signaalverwerkingssysteem dient een aantal extra functionaliteiten te bezitten in vergelijking met algemene middleware-standaards. Naast het verbinden van leveranciers en gebruikers van signalen, moet er een scheduler zijn voor het actieve beheer van de toestanden van de modules en moeten klokken op gedistribueerde locaties nauwkeurig worden gesynchroniseerd. Het concept van unconfined threads modelleert half-actieve modules in een gedistribueerd real-timesysteem. Elke module specificeert een interval dat het venster bepaalt waarin activering moet plaatsvinden. Na afloop van de berekeningen kan de module vrij een nieuw schedule-interval kiezen. Met unconfined threads vervalt de noodzaak voor toegevoegde activeringsmechanismen en worden elegante toestandsovergangen mogelijk gemaakt. De middleware omvat verder een nieuw kloksynchronisatiealgoritme, dat de stochastische informatie in het systeem van klokken optimaal benut om tot een synchronisatie te komen die zowel preciezer als nauwkeuriger is.

De nieuwe methodologie voor het ontwikkelen van modulaire instrumentatiesystemen, maar de geïntegreerde ontwikkeling van data-acquisitie- en data-verwerkingshardware en -software mogelijk voor alle fases van een testprogramma. Dataverwerkingscomponenten die zijn ontwikkeld voor bureausimulaties kunnen zonder aanpassing worden hergebruikt in gesloten-lussimulaties met hardware of een piloot in de lus, voor vliegproeven en voor gegevensanalyse na de vlucht. Bovendien is optimaal hergebruik van de componenten van één project naar het volgende gegarandeerd. De methodologie resulteert op deze manier in afgenomen ontwikkelingstijd en -kosten en in toegenomen betrouwbaarheid van het systeem.

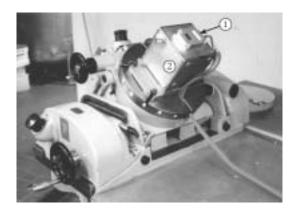

De nieuwe methodologie is ontstaan tijdens de vernieuwing van de instrumentatie in het laboratoriumvliegtuig van de Technische Universiteit Delft. In de zomer van 2001 is aan de Faculteit Luchtvaart- en Ruimtevaarttechniek onderzoek gedaan naar de cybernetica van een tunnel-in-de-sky display tijdens een daadwerkelijke vlucht. In voorbereiding op het vliegproefprogramma is de volledige ontwikkelingsmethodologie voor het eerst toegepast. Gezien de omvang van de nieuwe ontwikkelingen in het systeem en in vergelijking met het tijdschema van eerdere projecten, werd met een looptijd van vier maanden tussen projectbegin en de eerste vliegproeven een significante afname van de ontwikkelingstijd gerealiseerd. Bovendien hielp de test- en systeemintegratiefilosofie van de methodologie bij het voorkomen en verwijderen van implementatiefouten. Als gevolg hiervan heeft de daadwerkelijke looptijd van het project de geplande niet overschreden.

## Software-Enabled

## **Modular Instrumentation Systems**

Soijer, M.W. (2003). Software-Enabled Modular Instrumentation Systems (Dissertation, Delft University of Technology), ISBN 90-9017445-1.

#### Summary

The rapid development of computer systems during the 1980s and 1990s opened the possibility to integrate flight test data acquisition and data processing techniques. Real-time adaptive signal generation for closed-loop experiments, on-line data analysis, and in-flight simulation are new applications in flight test that have been demonstrated in the past decades. The corresponding introduction of traditionally ground-based equipment to airborne applications has increased the number of different computer systems on which data processing tasks are performed. As a consequence of what is referred to as the paradox of computer platform differentiation, reliability and maintainability of the instrumentation systems and processing tools have suffered. In order to improve this situation, a generic methodology is presented for the development of real-time signal processing systems in flight test, covering all of pre-flight simulation, in-flight data acquisition and processing, and post-flight analysis.

The methodology uses an object-oriented approach to implement the concept of intelligent instrumentation – which combines sensors, actuators, and preprocessors into components that communicate through interfaces that are standardized for all – in a software-based environment that is compatible with conventional sensors and transducers. The environment enables modular development of both distributed and real-time applications as they are encountered in closed-loop flight testing. By means of the middleware, it facilitates the activation of sensors, transducers, and processing components at the correct time and provides a synchronized notion of time throughout the nodes in a distributed system.

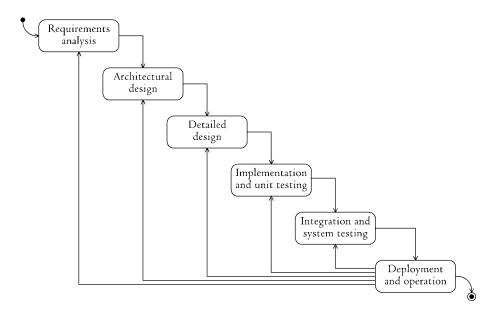

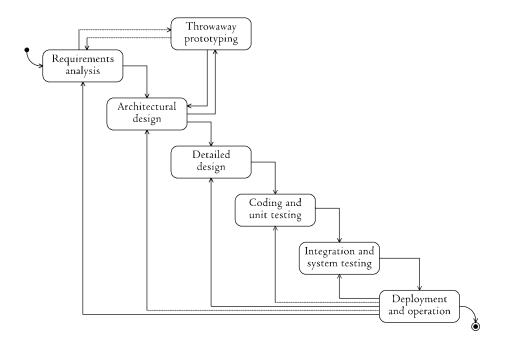

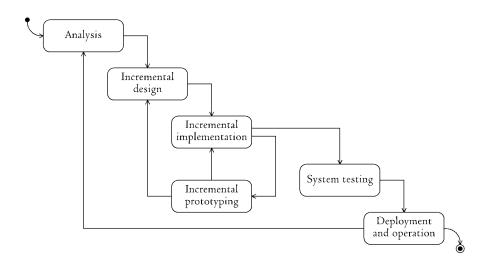

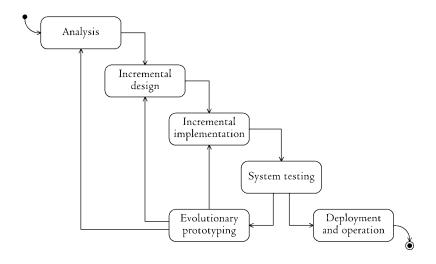

The life cycle model that is tailored to the development of such flight test instrumentation systems is a combination of the evolutionary prototyping model and elements from throwaway prototyping and hierarchical design as they are known from software engineering. The method strongly encourages the development of standardized components – both for hardware and software – that can be used in multiple applications. Component development is therefore placed in a separate life cycle within that of the application. Standardized components are specialized for use in the present application; the application life cycle merely consists of requirement specification and architectural design before, and system integration after component development.

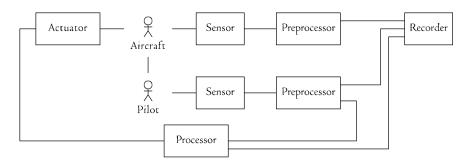

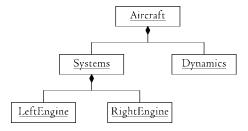

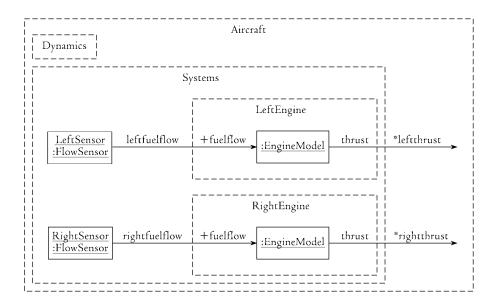

Depending on the way information is fed back from data processing to system excitation, each flight test application is classified as an open-loop testing system, an adaptive testing system, a human-factors testing system, or an in-flight simulation system. A new type of diagram is introduced as an extension to the set of diagrams that are offered by the Unified Modeling Language. The new diagram is referred to as the signal diagram; it models the complete flow of information through the application, while focussing on the information itself rather than on the components by which it is created or processed. Combined with a context model that reflects the characteristic structure of the four application classes, the signal diagram forms the basis for application design. The components in an application are categorized in three groups: platform, data acquisition, and data processing components. Each group covers both hardware and software elements. For data acquisition or publication components, maximum reusability of the hardware and software elements is achieved by applying hierarchical layers to the design. A four-layer model separates the port hardware of the digital signal processor, the corresponding driver software and wiring, the sensor or actuator, and the software that interacts with the other components at standardized levels of abstraction. Each of the elements can therefore be exchanged without affecting the other parts of the component.

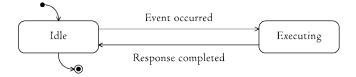

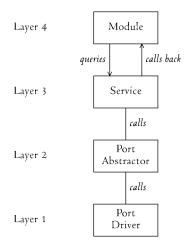

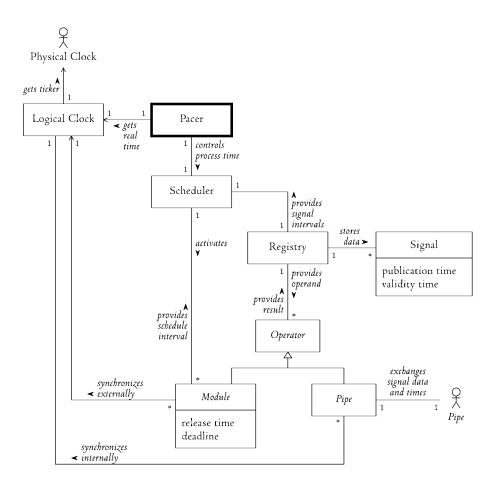

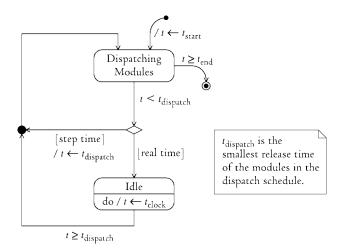

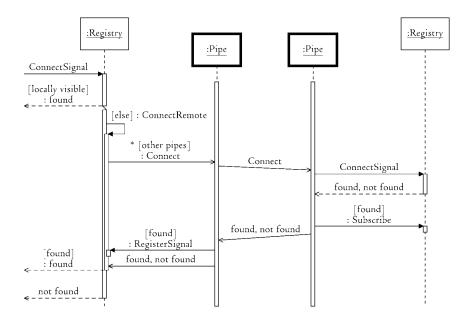

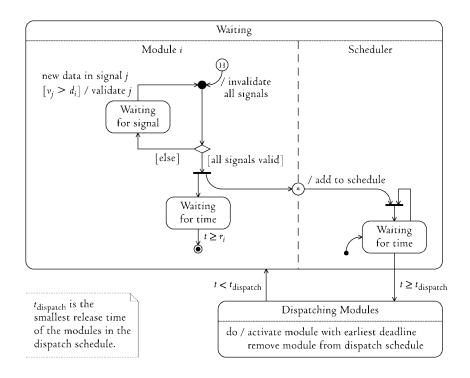

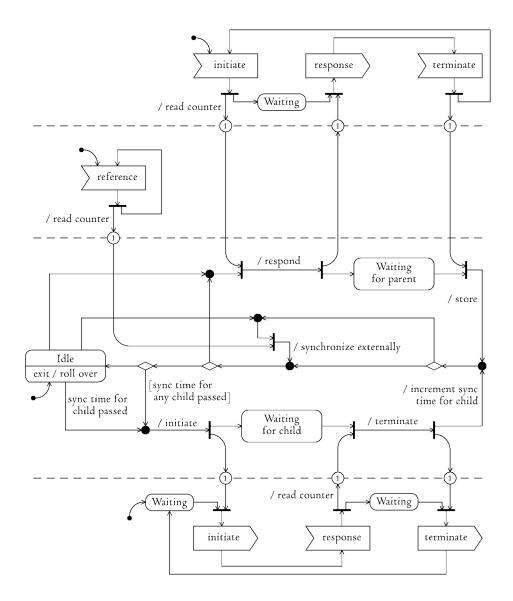

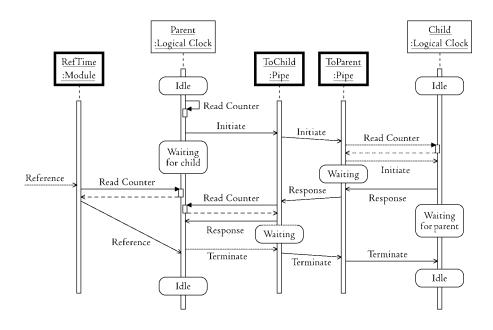

Middleware for a digital signal processing system must provide additional functionality with respect to generic middleware standards. Apart from providing registration services that connect signal producers and consumers, it must include a scheduler that actively manages the states of the application modules, and it must accurately synchronize the real-time clocks of the distributed nodes. The concept of unconfined threads is used to model semi-active modules in a concurrent system. Each module can set an interval that defines the window in which it demands activation. Upon completion of its computation, the module can freely choose the new schedule interval. Unconfined threads remove the need for additional activation mechanisms in the middleware and facilitate graceful mode changes by the modules. The middleware includes a novel clock synchronization algorithm, referred to as the probabilistic peer-to-peer algorithm, which exploits the stochastic information in the system of clocks to yield more accurate and more precise synchronization.

The new methodology for developing modular instrumentation system enables the integrated development of data acquisition and data processing hardware and software for all phases of a test and evaluation program. Data processing components that are developed for desktop simulation can be reused without adaptation in hardware- or pilot-in-the-loop simulation, in flight test, and in post-flight data analysis. Moreover, optimum reusability of the components from one test program to the next is ensured. The methodology thus results in reduced system development time and cost, and improved system reliability.

#### SOFTWARE-ENABLED MODULAR INSTRUMENTATION SYSTEMS

The new methodology for instrumentation system development originated during an upgrade project for the instrumentation of the Delft University laboratory aircraft. Summer 2001, the Faculty of Aerospace Engineering investigated the cybernetics of a tunnel-in-the-sky display in actual flight. In preparation to the flight test program, the fully matured development methodology was applied for the first time. Considering the new developments that were incorporated in the system and comparing the fourmonth time schedule between project initiation and flight test to that of previous projects, a significant reduction in development time was achieved. Moreover, the methodology's testing and system integration philosophy helped to avoid and eliminate implementation flaws. As a result, the project's original time plan was kept.

## Contents

Nomenclature xvii

## Introduction 1

#### 1. Development Philosophy 17

- 1 Life cycle models 18

- 2 Concepts and strategies of object orientation 26

- 3 Concepts and strategies of concurrency 29

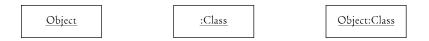

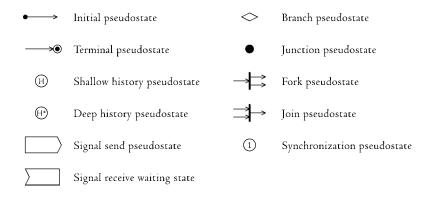

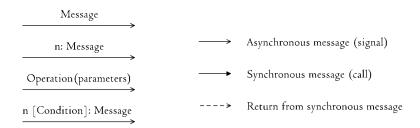

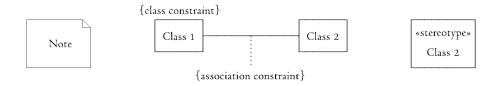

- 4 UML notation for object-oriented modeling 38

- 5 The flight test instrumentation development life cycle 39

### 2. Application Development 45

- 1 Requirements analysis 47

- 2 Context analysis 53

- 3 Design 59

- 4 Synthesis 61

- 5 Documentation and maintenance 65

## 3. Component Development 69

- 1 Analysis and prototyping 72

- 2 Hierarchical layers 75

- 3 Interfaces 77

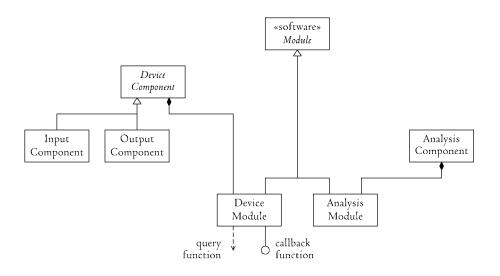

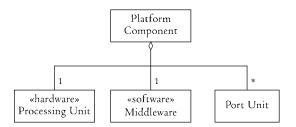

- 4 Modules in data acquisition and processing 83

- 5 Design and implementation 86

## 4. A Middleware Pattern 91

- 1 Requirements 93

- 2 Time 98

- 3 Scheduling policies and performance 105

- 4 Architecture 111

- 5 Application topology 116

- 6 Activities 121

#### CONTENTS

### 5. Clock Synchronization 131

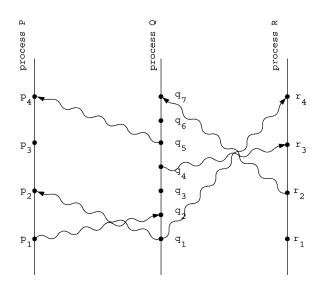

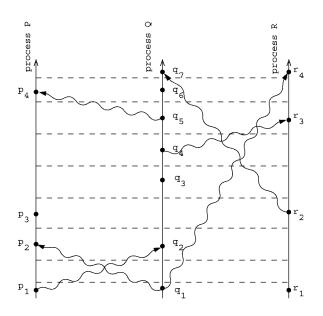

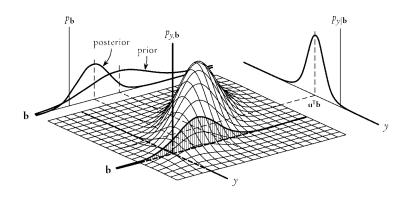

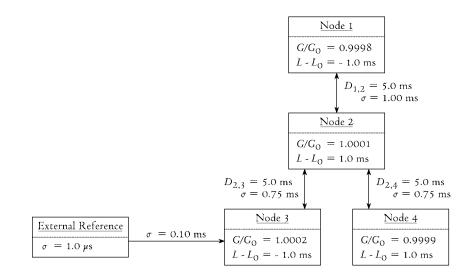

- 1 Probabilistic peer-to-peer synchronization 132

- 2 Practical aspects 143

- 3 Simulations 146

- 4 Activities in the middleware 153

### 6. Case Study in Human-Factors Testing 159

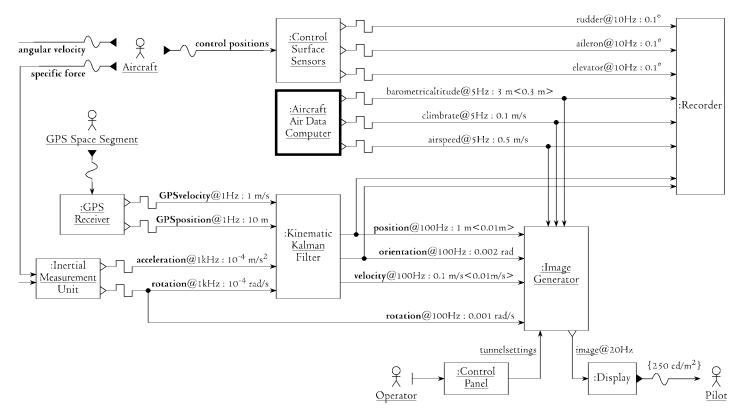

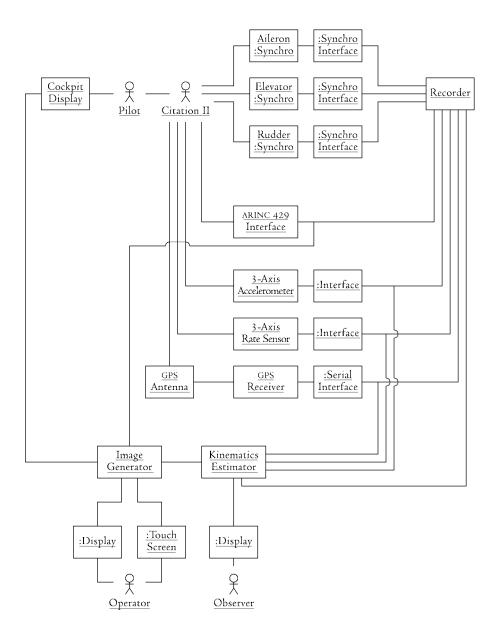

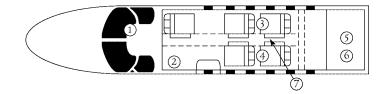

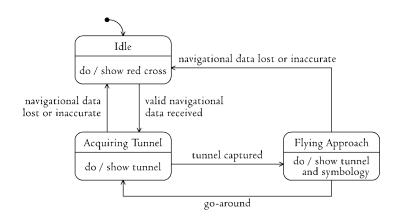

- 1 Application modeling 161

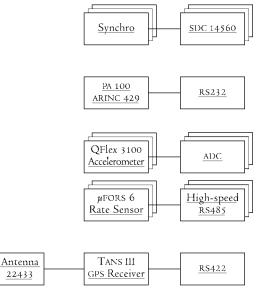

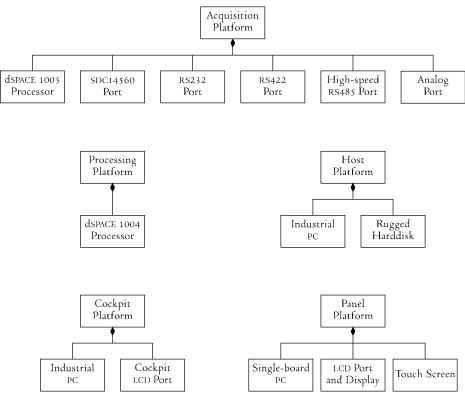

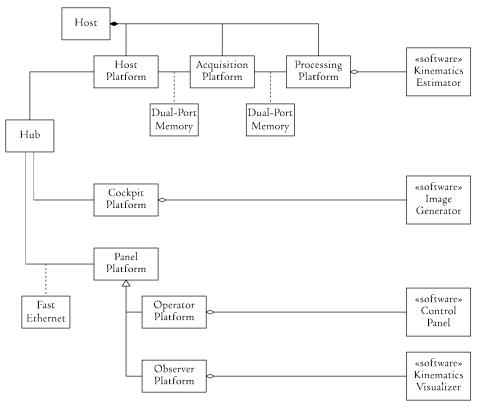

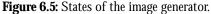

- 2 Component development 176

- 3 Application synthesis 182

#### Discussion 187

Acknowledgments 193 References 195

### Appendix

A Unified Modeling Language 205 B Activities in Instrumentation Development 217 C Bayesian Estimation 223 D Case Study Implementation Details 227

Glossary 229 Index 241

## Nomenclature

| Sets                                   |                                                          |                                                                          |

|----------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------|

| R                                      | all real numbers                                         |                                                                          |

| $\mathbf{R}^n$                         | all <i>n</i> -tuples of real numbers                     | $\{[x_1 \ldots x_n]^{T}\}, x_i \in \mathbb{R}$                           |

| a 1                                    |                                                          |                                                                          |

| Symbo                                  |                                                          |                                                                          |

| B                                      | confidence matrix                                        | (C.12)                                                                   |

| b                                      | parameter vector                                         |                                                                          |

| <b>b</b>   <i>y</i>                    | parameter vector posterior to observation                |                                                                          |

| $C_{\mathbf{x}\mathbf{y}}$             | covariance matrix of $\mathbf{x}$ and $\mathbf{y}$       | $E\{(\mathbf{x} - E\{\mathbf{x}\})(\mathbf{y} - E\{\mathbf{y}\})^{T}\}\$ |

| $C\langle X\rangle$                    | global clock value for event $x$                         |                                                                          |

| $C_{p}\langle x\rangle$                | local clock value for event <i>x</i> in process <i>p</i> |                                                                          |

| $C_i(t)$                               | logical clock value for time $t$ on node $i$             |                                                                          |

| $C_p \langle x \rangle \\ C_i(t) \\ D$ | communication delay                                      |                                                                          |

| $D_{XY}$<br>d                          | average delay between nodes $x$ and $y$                  |                                                                          |

|                                        | zero-mean, random delay                                  |                                                                          |

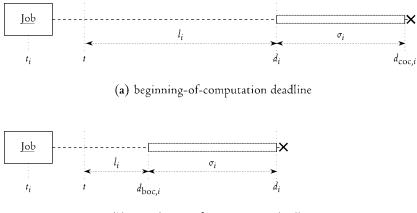

| $d_i$                                  | deadline of job <i>i</i>                                 |                                                                          |

| d <sub>boc, i</sub>                    | beginning-of-computation deadline of                     |                                                                          |

|                                        | job <i>i</i>                                             |                                                                          |

| d <sub>coc, i</sub>                    | completion-of-computation deadline of                    |                                                                          |

| ,                                      | job <i>i</i>                                             |                                                                          |

| $F_{X}(a)$                             | probability distribution function of $x$                 | $P_{X}[-\infty < x \le a]$                                               |

|                                        | granularity of clock on node <i>i</i>                    |                                                                          |

| $G_i$<br>$\hat{G}_i$                   | normalized granularity of clock on node <i>i</i>         |                                                                          |

| $L_i$                                  | logical clock offset on node <i>i</i>                    |                                                                          |

| $\hat{L}_i$                            | normalized logical clock offset on node <i>i</i>         |                                                                          |

| $l_i$                                  | laxity of job <i>i</i>                                   | $d_{\text{coc.}i} - s_i - t$                                             |

| m                                      | measurement noise                                        |                                                                          |

| Ν                                      | counter range                                            |                                                                          |

| $P_{X}[a]$                             | probability of occurrence of event $a(x)$                |                                                                          |

| $p_X$                                  | probability density function of <i>x</i>                 | $\frac{dF_X}{dx}$                                                        |

|                                        | joint probability density function of $x$                | dx                                                                       |

| $p_{X, y}$                             | and y                                                    |                                                                          |

| <i>n</i>                               | conditional probability density function                 |                                                                          |

| $p_{X y}$                              | of x given y                                             |                                                                          |

|                                        |                                                          |                                                                          |

| r <sub>i</sub> | release time | of job <i>i</i> |

|----------------|--------------|-----------------|

|----------------|--------------|-----------------|

- *T* counter base

- $T_e$  external reference time

- *t* time

- $t_i$  arrival time of job *i*

- **u** input vector

- y output vector

- $s_i$  computation time of job *i*

- $s_x$  standard deviation of scalar x

- $t_i(t)$  counter value on node *i* at time *t*

- $t_i$  artificially rolled counter value on node *i*

- $\hat{t}_i$  normalized counter value on node *i*

- *u* output observation

## Delimiters

- $\mathbf{x}_{[i]}$  element *i* of vector  $\mathbf{x}$

- $A_{[ij]}$  element *i*, *j* of matrix A

- $(a_{jj}) \quad \text{matrix } A \in \mathbb{R}^{n \times m} \qquad \begin{bmatrix} a_{11} \ \cdots \ a_{1m} \\ \vdots \\ a_{n1} \ \cdots \ a_{nm} \end{bmatrix}$

- |A|determinant of square matrix A

- $\{x\}_{i}$  set of all elements x

- $\begin{bmatrix} f \end{bmatrix}_a^b$  change of function f over interval  $\begin{bmatrix} a, b \end{bmatrix}$  f(b) f(a)

## Operators

| $E\{x\}$ | expected value of x | $\int_{-\infty}^{\infty} p_{X}(x) x dx$ |

|----------|---------------------|-----------------------------------------|

|----------|---------------------|-----------------------------------------|

$A^{\mathsf{T}}$  transpose of matrix A

$$\frac{@}{@}f$$

Jacobi matrix for function  $f(\mathbf{x})$ : H

$$\mathbf{R}^{m} \rightarrow \mathbf{R}^{n} \left( \frac{\mathscr{A}_{j}}{\mathscr{A}_{j}} \right) \in \mathbf{R}^{n \times m}$$

$\sqrt{C_{xx}}$

## Relations

- $\Leftrightarrow$  entails and is entailed by

## Abbreviations and acronyms

| Abbreviations and acronyms |                                                               |  |

|----------------------------|---------------------------------------------------------------|--|

| ADC                        | analog-digital converter                                      |  |

| AGARD                      | Advisory Group for Aerospace Research and Development         |  |

| AIAA                       | American Institute of Aeronautics and Astronautics            |  |

| COMET                      | Concurrent Object Modeling and Architectural Design Method    |  |

| CORBA                      | Common Object Request Broker Architecture                     |  |

| CPU                        | central processing unit                                       |  |

| DSP                        | digital signal processor                                      |  |

| DUECA                      | Delft University Environment for Communication and Activation |  |

| EDD                        | earliest due date                                             |  |

| EDF                        | earliest deadline first                                       |  |

| ESA                        | European Space Agency                                         |  |

| GMT                        | Greenwich mean time                                           |  |

| GPS                        | Global Positioning System                                     |  |

| HOOD                       | Hierarchical Object-Oriented Design                           |  |

| HUD                        | head-up display                                               |  |

| ICAO                       | International Civil Aviation Organization                     |  |

| IEEE                       | Institute of Electrical and Electronics Engineers             |  |

| ISO                        | International Organization for Standardization                |  |

| LLF                        | least laxity first                                            |  |

| NTP                        | network time protocol                                         |  |

| OMT                        | Object Modeling Technique                                     |  |

| OOM                        | object-oriented modeling                                      |  |

| PCM                        | pulse code modulation                                         |  |

| RMA                        | rate-monotonic analysis                                       |  |

| SDC                        | synchro-digital converter                                     |  |

| SI                         | International System of Units                                 |  |

| SJF                        | shortest job first                                            |  |

| TAI                        | international atomic time                                     |  |

| UML                        | Unified Modeling Language                                     |  |

| USN                        | United States Navy                                            |  |

| UT                         | universal time                                                |  |

| UTC                        | coordinated universal time                                    |  |

| VHF                        | very high frequency                                           |  |

|                            |                                                               |  |

## Introduction

T HE history of flight testing started on Thursday December 17th, 1903, when Orville and Wilbur Wright achieved the very first powered, sustained, and controlled flight. Not only was the flight of the Flyer 1 preceded by several years of careful research and development, including a series of wind tunnel tests, the results of the trial itself were recorded in a way that is typical for the Wright brothers' engineering approach. Flight time and distance were meant to support their claim that they had actually succeeded in conducting a flight with a heavier-than-air machine, but the registration of wind speeds, both from a nearby meteorological station and from personal measurements, was unmistakably meant to provide data for further development of the aircraft (Gibbs-Smith, 1960, pp. 226-227).

Wright Flyer 1, flown by Orville Wright on December 17, 1903. This photograph by John T. Daniels is the only one of what is to be regarded as the first flight test in history. The missing lower left corner is a chip from the glass negative.

There are many aspects in which the achievements of the Wright brothers differ from those of other aeronautical pioneers. Setting the stage for an engineering practice that is now known as flight testing, is certainly one of them. Unlike famous predecessors, among who Lilienthal and Chanute deserve the credit for documenting their contributions to aviation in a scientific manner (Gibbs-Smith, 1960, p. 32), the Wrights were not satisfied by the mere success of performing the world's first flight in the presence of witnesses. In addition, they introduced the practice of measuring physical quantities that are related to the flight, and which are of great importance to assessment of the trials.

Ever since, flight test instrumentation systems and testing techniques have kept pace with the development of aviation technology itself. The continuous increase in airspeed, flight altitude, range, and duration, as well as the growing number of parameters that needed to be monitored, required improved and more powerful data acquisition and data recording systems with every new generation of aircraft. Because of the required capability to withstand the harsh environment in which airborne equipment is to operate, the development of flight test instrumentation systems is an engineering discipline in itself. Yet, instrumentation development has not only been motivated by the continuous progress in aviation and space technology, but has also been among the first to apply new technology arising from it. For example, the development of digital solid-state computers during the Apollo program in the 1960s, provided the world with the hardware to develop the information technology that has found application in both flight test instrumentation and all of society.

The rapid development of computer systems during the 1980s and 1990s opened the possibility to integrate data acquisition practices with flight data processing techniques. On-line parameter estimation, full accuracy quick-look data assessment, and in-flight simulation are a few of the applications of flight test instrumentation and data processing that have become reality. Nevertheless, these applications have so far been cases of pioneering work that remained isolated. Pushing the limits of computer performance, both hardware systems and software environments have been dedicated developments that lacked usability to other applications. A more generic approach to the development of real-time computer systems for flight test data acquisition and processing is desirable, if not necessary.

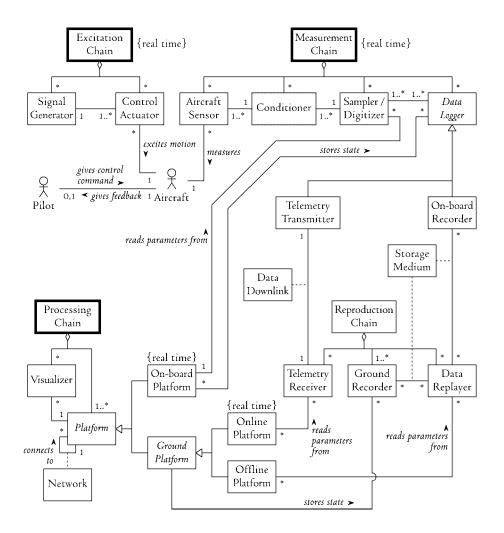

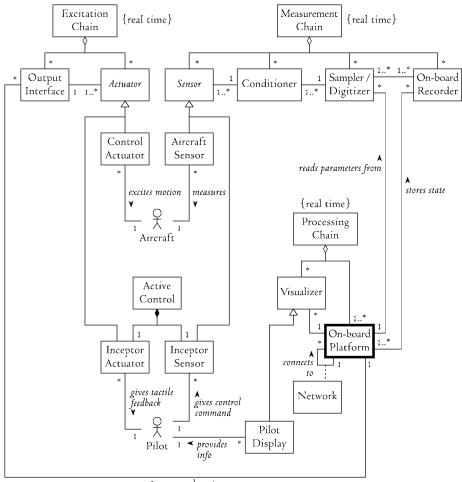

#### Flight test instrumentation

The term *flight test instrumentation* refers to all equipment that is installed on board an aircraft with the purpose to excite, measure, condition, record, process, or display flight data or aircraft parameters, and that is not a part of the aircraft's standard systems. A flight test instrumentation system comprises multiple subsystems, which consist of chains of components. In general, the *excitation chain* contains the equipment that excites the aircraft or system that is to be tested by injecting meaningful test signals; it is connected to the *measurement chain* by means of the system under test itself. The measurement chain covers all the components that convert the physical phenomena that are observed into the numeric data that can be used for processing. Data recording is the final stage in the measurement chain. When data processing is performed on-board, the *processing chain* can be attached directly to the measurement chain. Data replay includes both off-

line data reproduction from a storage medium that was recorded on board, and on-line reproduction through a telemetry downlink. Because the reproduction chain is ground based and not part of the airborne instrumentation, it is traditionally not a part of flight test instrumentation. Likewise, the processing chain is only considered to be a part of flight test instrumentation when the processing is performed on-line. Treatment of instrumentation system design in literature, for example by Borek and Pool (1994), is often limited to the development of the measurement chain.

The measurement chain begins at the physical phenomena that are to be observed, and includes - but is not necessarily limited to - sensors and transducers, signal conditioners, filters, samplers and multiplexers, digitizers, and recorders. When telemetry is used, the data link transmitters and receivers can be inserted anywhere in the measurement chain, although immediately before the recorders is the most common solution. The excitation chain is the smallest of the subsystems in flight test instrumentation and is often not present at all. The excitation chain covers all equipment that is used to excite the aircraft or system under test, in order to obtain meaningful test data. For many performance and handling qualities test flights, system excitation is performed by the test pilot and does not require any additional equipment. For aircraft systems testing, for flight control system testing outside the dynamic range of the pilot, or in cases where optimal input signals need to be reproduced with a level of accuracy that is unobtainable for the human pilot, signal generators and actuators may be used. These excitation chain components are connected to the rest of the flight test instrumentation system via the system under test only, although in some cases a signal generator might be connected to the data recorder. The processing chain begins at the end of the measurement chain, but cannot be defined in terms of equipment as easily as the measurement chain. Data replayers are the starting point for processing, but the rest is highly dependent on the type of application.

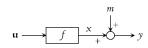

Real-time data processing is defined as the computations or actions for which success or failure not only depends on the correctness of the results, but also on the time at which these results become available (Stankovic and Ramamritham, 1993, p. 1). It is noteworthy that this definition does not specify the size of the time margin that is available for processing, neither in absolute terms nor relative to the operating speed of the system. Systems that exhibit a significant time lag are therefore still regarded as real time, as long as the delay is bounded to a maximum. All components of the excitation and measurement chains typically operate in real time. The recordings that result from the data acquisition processes in the measurement chain, are time traces of the parameters at hand. Data processing can be conducted in real time, but non-real-time processing is more common. When data from time traces is not processed in real time, the computations proceed with the next time point after the completion of the current step. The process clock is thus continuously increased with the step size of the time trace and not linked to the real, wall clock time. To refer to this kind of processes, the term *step-time processing* is introduced.

A traditional flight test instrumentation system consists of the excitation and measurement chains only. The data recording equipment in these systems has gradually been replaced by digital devices, often using solid-state recorders. The rapid development of digital computers in the last few decades has resulted in increased computing power at low cost and with high reliability. Apart from using digital computers for data acquisition and recording tasks, this development led to the introduction of on-line data analysis and visualization. In the old situation, the measurement chain and processing chain would be completely separated. Software components would therefore be developed for either airborne application in the real-time measurement chain, or for step-time application in the processing chain. Powerful digital equipment was introduced to flight test with the purpose the simplify the complete process of data acquisition and analysis. The use of airborne computer equipment – which was initially meant to make data acquisition easier and more robust - for on-line analysis and visualization, transferred part of the data processing software to the measurement chain hardware. However, the same software components are still used for step-time analysis. Not only will raw data recordings have to undergo identical or similar processing for the final analysis as during quick-look analysis, simulated data will be applied to all algorithms before embarking on the flight test program, in order to validate the correctness of both the designed algorithms and their software implementations. The existence of different computer systems, operating systems and software environments for airborne data acquisition, post-flight processing and pre-flight simulation thus requires porting of analysis software from one computer system to another and from one software environment to another. The result is the paradox of computer platform differentiation: the introduction of powerful digital equipment to airborne applications, has increased rather than reduced the number of different computer systems on which certain tasks in the data processing chain are performed. Separate sets of software must be developed, from which maintainability and re-usability of computer code have suffered.

Nevertheless, the possibility for real-time data processing as provided by the replacement of dedicated data recording equipment by generic digital signal processors (DSPs), greatly enhances the process of flight test by presenting data analysis results to the flight test engineer during the execution of the experiment. Present-day computer interfaces allow for interactivity in the data display system, allowing the operator to monitor all of the raw data, generated results and related processes. Malfunctioning sensors or interfaces, inadequate test maneuvers or weather conditions, and other obstacles for meeting the trial's goals can be recognized and possibly obviated during the flight. This can improve both effectiveness and efficiency of a flight test campaign and largely reduce the related costs. An example was presented by Laban (1994), who developed a real-time flight test instrumentation system for on-line estimation of aerodynamic model parameters. For safety critical flight tests, for example envelope expansion for a new type of aircraft, the possibility to identify malfunctions or unexpected system behavior in real time, extends the benefits of on-line data pro-

cessing from economical issues to a matter of improved safety. Yet, without mitigation of the economical and safety-related benefits of real-time data analysis, the single largest change associated with the introduction of digital signal processors is the possibility to attach output interfaces to the system. The system no longer only records and processes the information coming from its environment, but it can also influence that environment by providing new inputs that are based on the outcome of previous measurements and the operator's decisions.

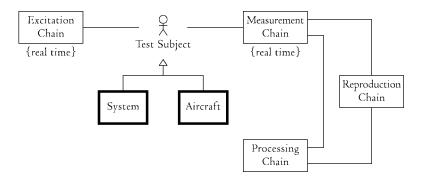

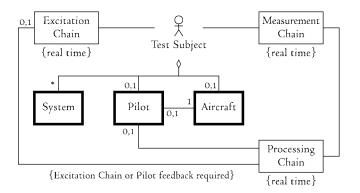

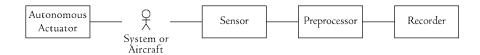

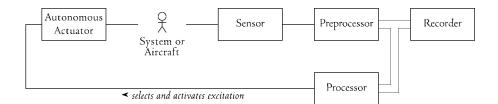

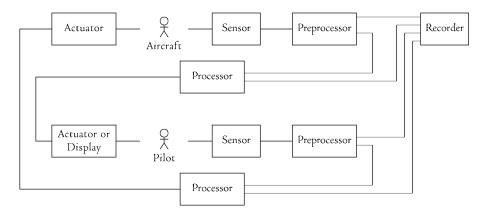

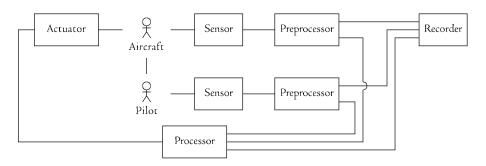

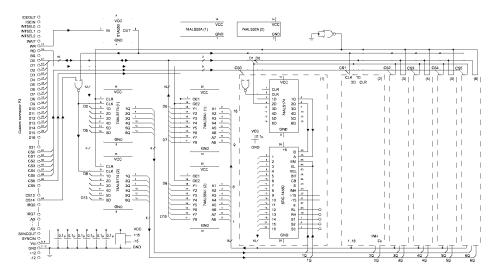

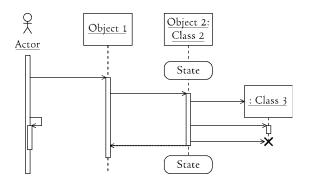

A DSP-based flight test instrumentation system therefore no longer needs to be at the end of a one-way information chain, but can be part of a closed-loop system. For traditional open-loop systems as shown in figure 1, the system being tested is enclosed between the input generators – either an automatic signal generator, autopilot, or the test pilot or flight test engineer who controls the aircraft or system – and the measurement chain. Even when automatic signal generators are used that are considered to be part of the flight test instrumentation system's excitation chain, the only link between the input generators and the data acquisition hardware is the test subject. This is different for the *closed-loop flight test instrumentation systems* as depicted in figure 2. The signal generators are not independent, but connected to the output interfaces of the digital signal processor. The additional link provides a way to feed back the results of the measurements to the system under test.

#### Figure 1: Open-loop flight test instrumentation system.

The diagram shows a static model in conceptual perspective according to the Unified Modeling Language (UML). The system under test, either the aircraft or any (sub)system, is external to the instrumentation system and therefore indicated as an actor. The excitation and the measurement chain are associated directly with the test subject; both must therefore operate in real time. As data processing for openloop systems is not subjected to a time constraint, the processing chain does not necessarily provide real-time delivery of the analysis results.

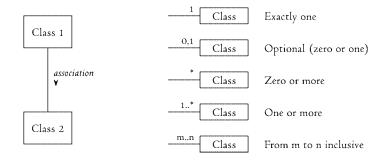

The UML is discussed in section 1.4; an overview of the UML notations that are used in this thesis is presented in appendix A.

Figure 2: Closed-loop flight test instrumentation system.

Like figure 1, the diagram shows a static model in conceptual perspective according to the Unified Modeling Language (UML). The test subject is an arbitrary combination of the aircraft, a pilot, and any number of systems. Excitation of the test subject is controlled from the processing chain. Loop closure is obtained through the excitation chain, addressing any component of the system under test, or through the human pilot directly. An example of the latter is the feedback of analysis results to the pilot by means of a display system. Pilot and excitation chain loop closure are not mutually exclusive.

A closed-loop flight test instrumentation system is a prerequisite for experimental handling qualities flight testing, in which the developmental components are implemented as part of the instrumentation system. For this type of flight tests, the system under test is the combination of a pilot, the aircraft, its flight control system and possibly experimental display or inceptor systems. A digital signal processor can simulate the behavior of the components that need to be evaluated, while recording all the relevant data, including those that are part of the experimental subsystem and that may not be available when the test would be performed in a traditional fashion. Two characteristic examples of experimental handling qualities testing are the assessment of a flight guidance display system, and the evaluation of a fly-by-wire control law. In the first case, the DSP gathers the information that is required for composing the display, creates the image, and presents it to the pilot. The pilot controls the aircraft using the existing control system. The loop closing thus contains the display, the pilot, and the control system respectively. In the case of fly-by-wire control law evaluation, the DSP gathers the pilot's commands from the inceptors and the flight data that serve as input for the flight control laws; it then performs the necessary computations and uses the results to adjust the aircraft's control actuators. In this case, the control laws and the actuators form the closed loop, while the pilot acts as an open-loop input to the flight test instrumentation system. A combination of both typical closed-loop flight tests is

possible as well; the full system then contains two feedback loops, one through the pilot and one through the flight control system.

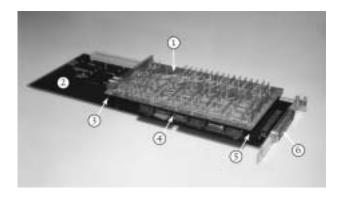

Because of the replacement of conventional data recorders by digital signal processors, the role of instrumentation components like signal conditioners, filters, analogdigital converters and multiplexers, is taken over by data acquisition boards that can be connected to the digital signal processing system. The integration of flight test instrumentation system components into off-the-shelf boards drastically reduces system design and preparation times. As a result, the traditional roles of the flight test engineer and the instrumentation engineer in the system development process are easily obscured. These traditional tasks and responsibilities are outlined by Adolph (1994), Knight and Dove (1994), and Crounse (1995). The instrumentation system design is centered around the composition of a *measurand list*<sup> $\dagger$ </sup>. During the composition of the measurand list, it is the responsibility of the flight test or system engineer to ensure that all parameters that are needed for analyzing the flight test, are recorded with the required accuracy, range, resolution, and data rate. The instrumentation engineer should counterbalance the desires of the flight test or system engineer by proposing adjustments to the measurand list, in order to match the capabilities of commonly supplied or stock sensors and transducers. Thus, the instrumentation engineer prevents the system under design from becoming excessively expensive or from using special case solutions for standard applications.

For traditional flight test instrumentation systems, the development process described above results in the measurand list as the only record of instrumentation characteristics, including the set of measurands and the corresponding ranges, resolutions and accuracies. From an information management point of view, this is a desirable situation. The absence of multiple, local copies of the same information ensures consistency of the data that are being used by the flight test engineer, the instrumentation engineer and all other parties involved. Data redundancy poses a significant threat to the maintenance of the instrumentation system documentation, since data anomalies are easily introduced. An important integrity constraint for any record of information is therefore the uniqueness of data. In information technology theory, this uniqueness is part of the concept of database normalization (O'Neil and O'Neil, 2001, pp. 353-358). However, when a flight test instrumentation system is constructed using off-the-shelf components, extensive sets of documentation for these components are maintained by the instrumentation engineer. These documents contain information on possible measurands, together with the available measurement characteristics. For the preparation of a flight test program, flight test and system engineers still have the responsibility to compose the list of measurands and required characteristics. The different origin of the application and the stock sensor measurand list is easily

<sup>&</sup>lt;sup>†</sup> Although the phrases *measurement list* and *parameter list* are used in the same sense, the term measurand list is preferred, because it refers to the quantities that are to be measured rather than the numbers that result from the measurements.

overlooked, especially when during the negotiation process between the flight test or system engineer and the instrumentation engineer, the specifications of the available instruments are transferred to the required measurand list. Additionally, data redundancies between the instrumentation background documentation and the current flight test measurand list are likely to be introduced. The concept of the measurand list therefore exhibits some inherent disadvantages for instrumentation systems that are composed from off-the-shelf components.

### **Object-oriented modeling and intelligent instrumentation**

Although state-of-the-art computer hardware is well represented in flight test instrumentation systems, modern developments on the more theoretical side of information technology have so far hardly found application in instrumentation design. The most important of these developments, which is also the most promising for contributing to a solution to the problems encountered in flight test instrumentation design, is *objectoriented modeling* (OOM). In the 1970s and 1980s, object-oriented programming arose as a software development paradigm (Parnas, 1972; Parnas, 1979; Meyer, 1987). Afterwards, during the 1990s, the concept of object-oriented design was extended to system design in general (Rumbaugh et al., 1991; Coad and Yourdon, 1991). Recently, object-oriented modeling has been extended with techniques to design *concurrent applications* (Douglass, 1998; Gomaa, 2000).

Concurrent applications are characterized by the simultaneous occurrence of multiple events, which are related to multiple activities that take place in parallel. Concurrency is a typical characteristic of real-time systems and distributed systems. In a realtime system, incoming events occur in an unpredictable manner. The order in which they arrive is arbitrary and one incoming event might overlap the handling of another. Yet, all events must be responded to in a timely manner. A distributed system is a system that consists of multiple nodes, each of which is assigned a part of the activities that make up the full application. These activities run in independent threads of control on the multiple nodes. Flight test instrumentation systems are inevitably at least partly real-time. As will be demonstrated below, they are a natural candidate for implementation as a distributed system as well.

The object-oriented development paradigm is based on the breakdown of a system in a set of cascading subsystems and on separation of interface and implementation. The partitioning of a system into subsystems, referred to as objects, is carried out with a focus on the function of each subsystem, rather than the task. The function of an object is its contribution to the overall system or the environment, and thus the reason for its existence. The task of an object is the collection of actual activities that need to be completed to fulfill its function. The function of an object is therefore the goal of the tasks that are carried out. By focussing on the function of subsystems instead of the tasks, the possibility to separate interface and implementation is cre-

ated. The interface is the boundary between the object and the surrounding systems, through which all communication takes place. As a result, the interface defines the function of the object. To the contrary, the implementation is closely related to the object tasks. It defines how the object perform its task and with that, how it fulfills its functions. The separation of interface and implementation is the rationale for the term object-oriented design; the alternative is procedural design in which the focus is on the tasks and implementation.

Object-oriented design provides a solution to the problems that arise when modern computer equipment is used in a closed-loop flight test instrumentation system. As explained in the previous section, a trade-off exists between flexibility of a system in terms of adjustability, and flexibility in terms of ease-of-use. The assembly of an instrumentation system from integrated off-the-shelf components will greatly reduce costs with respect to a custom-made system, but the flexibility to apply various combinations of sensors, transducers, filters, and converters is lost. With the object-oriented approach, the instrumentation is considered as a system of which the signal processing components are subsystems. By standardizing the interface between each pair of subsystems, any object can be replaced by an equivalent unit without modification of the rest of the system. Separate data paths are modeled by systems at a common level; sensors, actuators, filters, converters, or amplifiers for a single data chain are modeled as cascading subsystems to a single supersystem.

Decentralization of data acquisition components is a natural outcome of the objectoriented separation of interface and implementation for flight test transducers. In a traditional system, only sensors and actuators are located in the vicinity of the physical quantities that are to be measured, or the aircraft systems that are to be excited. All other components are grouped around the core of the instrumentation system. In an object-oriented layout, components which are related to the sensors and actuators, like filters and converters, are relocated with the sensors and actuators. Communication with the core of the instrumentation system takes place through standardized channels, implemented as databuses that interact with the interface of the sensors. This way, remote parts of the system are replaceable as long as the communication protocol remains unchanged. The actual implementation, the way the physical quantity is converted into the standardized data that is handed over through the interface, is hidden from the overall system and thus of no importance to its design. Although the concept of instrumentation decentralization in itself does not require a physically decentralized implementation, it is most easily realized by developing integrated instrumentation components that physically combine sensor or actuator hardware with their corresponding processing components.

Integrated transducers in which the original sensor or actuator, additional signal processing components, and a digital interface are combined, are referred to as *intelligent instruments* (Kopetz, 1997), also known as *smart sensors*. The most important advantage of intelligent instrumentation, is the provision of *agreed data* to the rest of the system. Agreed data is defined by Kopetz (1997) as a data element that has been checked

for plausibility. Thus, agreed data can reach a high level of reliability by identifying and either correcting or disregarding faulty data. As a result, agreed data can be used reliably without additional effort on the receiver side and without relying on implementation-specific characteristics. Because agreed data is expressed in a standardized format and has been checked for plausibility, the use of intelligent instrumentation moves the tasks that are often referred to as *data preprocessing*, for example the removal of spikes or drop-outs, from the processing chain to the measurement chain. Other benefits of intelligent instrumentation are a reduction in instrumentation cabling, because the digital interface for the transducer allows for the use of a single network bus for multiple instruments, and a potential increase of signal fidelity because analog to digital conversion is carried out close to the sensor itself and no additional noise can disturb the signal during transport.

An industrial standard for intelligent instrumentation is currently being developed. The IEEE has so far issued two parts of a standard on smart sensors (Institute of Electrical and Electronics Engineers, 1997; Institute of Electrical and Electronics Engineers, 1999). Application of the standard is not limited to aeronautical or astronautical engineering; the intended audience are measurement and control engineers in general. An additional two parts of the standard are under preparation. Notwithstanding the broad scope of the document being prepared, the working group for part three is dominated by the aerospace industry. It is aimed at the development of a network structure that can be used to provide remote units with both power and a communication bus over a single pair of wires (Eccles, 2000). The result will be a maximum reduction in instrumentation wiring, accompanied by a maximum increase in flexibility. The latter is achieved because additional transducers can simply be directly connected to the network. Eccles (2000) compares the current practice of building a flight test data acquisition system around a pulse code modulation (PCM) encoder, with the proposed solution using intelligent instrumentation. PCM allows for multiplexing of many data channels into a single stream; timing is controlled by the PCM unit using a built-in crystal oscillator. Data skew is therefore unavoidable, but well controllable. Using smart sensors, simultaneous sampling and analog to digital conversion is made possible, but common timing between all nodes in the network is not straightforward. Part three to the IEEE standard on smart sensors aims to develop a network protocol that provides the remote sensors with a common time base.

Although the new IEEE standard for intelligent instrumentation is promising, the lack of a common time base for all components can be a precluding problem for application in flight test systems that require high data fidelity. In addition, the new concept is incompatible with existing instrumentation equipment; many sensors may not be and might never become available as smart instruments. Finally, changes in transducer settings like sample rates or digitization resolutions might necessitate interventions at the transducer's physical location, which is generally more difficult to reach than the location of the core instrumentation system components. Consequently, a solution that allows for object-oriented modeling of a flight test instrumentation sys-

tem, while preserving the centralized layout of existing technology, is desirable. Such a solution can be found by designing the instrumentation system as an object-oriented distributed system. This way, the advantages of intelligent instrumentation can be utilized by implementing the data acquisition components as objects on a series of nodes in the distributed system. The nodes are selected in a way that optimizes the trade-off between flexibility and system simplification of the decentralized approach, and the compatibility and physical accessibility of the centralized approach.

## **Closed-loop flight testing**

The increased possibilities for closed-loop instrumentation systems that have emerged with the availability of digital signal processors, are not only a chance for increased safety and efficiency in flight test, but rather a necessity for the flight testing demands of the future. Modern avionics and flight control systems are dominated by digital computers. Their importance, including their influence on operating procedures and handling qualities of the aircraft, is likely to increase further. Design of higher-order flight control systems using digital computers is still subject to investigation. In fact, the potential for designing aerodynamically unstable aircraft, combined with the desire to design for *carefree handling* or *flight envelope protection* – the respective military and civil terms for a flight control system that protects the pilot from leaving the flight envelope - has put back the existing knowledge on design for handling qualities with respect to the possibilities for implementing the resulting control laws as offered by the airframe and the flight control system. To be able to flight test experimental higher-order control systems in a safe and cost-effective way, a closed-loop instrumentation system is required. By means of *in-flight simulation*, control laws can be evaluated in real flight before the aircraft for which they are designed is available, and with the increased safety of being able to revert to the original control system of the simulating aircraft. As described by Gibson (1999), in-flight simulation is an excellent way to gain knowledge on new fly-by-wire control laws and its appropriate use might prevent accidents during flight test. The equipment used for in-flight simulation, is in fact a closed-loop instrumentation system as previously shown in figure 2.

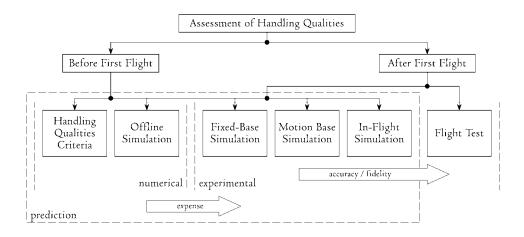

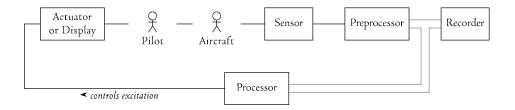

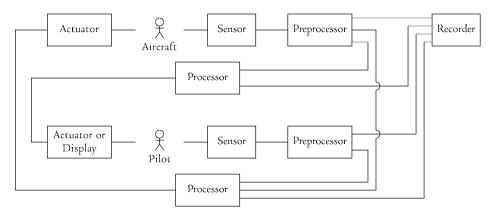

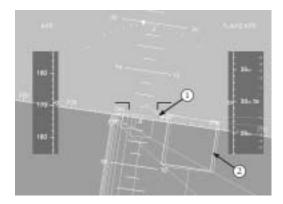

An overview of various possibilities to assess aircraft handling qualities is given in figure 3, which was adapted from Höhne (2001). In-flight simulation is an element in a continuous range of testing methods that starts with off-line simulation and ends with flight test of the flight control system that is being evaluated. The existence of four different experimental concepts, completed with off-line simulation in which the test pilot is replaced by a pilot model, underlines the resolving distinction between tools and methods for data acquisition, simulation, and processing that was noted earlier as part of the paradox of computer platform differentiation. Another sign for this is the separate classification of flight test and in-flight simulation, where the latter is a type of flight test in itself. This distinction is correct when regarded from the view-

point of categorizing possibilities for handling qualities assessment, but from an instrumentation point of view, in-flight simulation is more closely related to flight test than to fixed-base or motion base simulation.

Figure 3: Possibilities of handling qualities assessment (adapted from Höhne, 2001, p. 6).

Apart from the application of design criteria, flight test and four classes of simulation form a continuous range of testing resources to analyze handling qualities with increasing fidelity at the cost of increasing expenses.

Further research on higher-order flight control systems is not the only reason for the growing demand for closed-loop flight testing in the area of handling qualities. Aircraft navigation systems have developed from stand-alone devices to sources of navigation information that are connected to a central processor. In the traditional situation, a typical navigation aid consists of an antenna, a receiver with a processing unit, and an indicator. All civil aeronautical radio navigation systems that are currently in use adhere to this principle, including automatic direction finders (ADFs), VHF omnidirectional radio range receivers (VORs), distance measuring equipment (DMEs), and instrument and microwave landing systems (ILSs and MLSs). The International Civil Aviation Organization (ICAO) regulates the use of radio navigation aids on board of civil aircraft, by demanding certain systems to be installed and by specifying the navigation accuracy that must be achieved with each of these (International Civil Aviation Organization, 1996). However, these requirements do not suit the recent development towards integrated avionics and hybrid navigation systems. In these systems, the navigation information from at least two types of equipment is fused to yield an optimal estimate of the aircraft's position. The navigation equipment that can be used in a hybrid system, is not limited to ground-based radio navigation aids, but can also include inertial or satellite navigation systems. A central processor, for example a flight

management system or flight control computer, now delivers the combined navigation solution for use by the autopilot, or for presentation on a single display. Alternatively, many satellite navigation systems accept supporting information from an inertial or radio navigation system, in order to provide a hybrid navigation solution directly. For all of these systems, the combined navigation accuracy and reliability are more important than the characteristics of the individual sensors.

To address the problem of inappropriate requirements for aeronautical navigation aids, Kelly and Davis (1994) introduced the concept of required navigation performance (RNP). It relates the accuracy of a navigation system to the required performance that ensures safe aircraft guidance during all-weather operations, without referring to the specific characteristics of the navigation system at hand. The requirements, characterizing the navigation system performance in terms of accuracy, integrity, continuity and availability, are defined for each type of airspace in which the aircraft is operated. To satisfy required navigation performance, an aircraft's total system error (TSE) must exceed certain deviations from a nominal flight path with sufficiently small probability only. Total system error is the sum of navigation sensor error and flight technical error. The first is the discrepancy between the aircraft's actual position, and the position indicated by the navigation system; the latter is the error between the position that is indicated by the navigation system, and the desired position of the aircraft. Because flight technical error is a part of total system error, the accuracy at which an aircraft's position as it is known can be controlled to equal the desired position, plays an important role in achieving required navigation performance. Thus, the aircraft's handling qualities affect the overall navigation performance. Their influence may become significant during manually controlled phases of flight with tight navigation requirements. It is noteworthy in this respect that manual control and the most stringent navigational requirements for civil air traffic coincide during final approach and landing.

ICAO is in the process of accepting required navigation performance as a replacement for the existing radio aids specifications, in which only the performance of the navigation equipment is regulated. Once RNP has been accepted as an ICAO requirement, the concept of total system error effectively forces all future certification flight tests for navigation and flight control systems to be a combination of an aircraft systems flight test, in which the navigation sensor error is assessed, and a human-factors or automatic flight controls test, in which the flight technical error is assessed. During the development phase that precedes the certification, a closed-loop instrumentation system can be used to assess adjusted flight control system or pilot display characteristics. If the instrumentation system is equipped with its own high-accuracy navigation sensors, it can be used to insert known errors in the navigation solution, in order to investigate the effect of navigation sensor error. Additionally, a navigation solution can be obtained that can be used as a reference for validating navigation sensor error during both development and certification.

### Motivation and project scope

Since the inception of flight testing in 1903, data acquisition and data processing equipment have matured with both aircraft and signal processing technology. In the last three decades of the 20th century, developments in digital computer hardware found their way to flight test instrumentation. Nowadays, all of data processing and most data acquisition systems are completely digital. Measurement chains are controlled by microprocessors throughout and data storage is carried out using solid-state recorders. Yet, the practice of instrumentation system design and maintenance has hardly changed since the beginning of flight test.

Consequently, flight test data acquisition systems and data processing equipment do not form an integrated environment for system analysis, although both are now largely based on the same equipment. Software for data processing thus has to be redeveloped for simulation purposes, on-line application purposes, and post-flight analysis purposes. Digital signal processors allow for rapid assembly of an instrumentation system with standard components, but pose a threat to instrumentation suitability for a specific application, and may endanger documentation reliability by obscuring the importance of a measurand list. Recent developments in intelligent instrumentation may offer a solution to the latter problems, but are far from being available as stock products and are not easily combined with existing instrumentation. A gradual transition to smart sensors, or application of smart sensors in combination with custommade instruments, is therefore difficult to accomplish. Finally, intelligent instrumentation as currently being developed will not solve the problem of computer platform differentiation between airborne and post-flight applications, nor does it provide a solution for other problems in real-time data processing, like clock drift in distributed applications.

In this thesis, a new methodology for instrumentation system development is presented with the objective to address the issues that are mentioned above. A system that has been developed according to this methodology, provides a data acquisition and processing environment in which software can be reused throughout all stages of a development program and in which hardware components are both reusable and replaceable. The software for data processing can be applied to both off-line data analysis and stringent real-time applications, without the need for programmatic changes. Application of the methodology – which in itself is not limited to flight test – lifts the traditional restriction that flight test instrumentation consists of only airborne equipment. Instead, the previously separate developments of simulators, airborne instrumentation hardware, and data processing tools are fully integrated. In order to yield an instrumentation system maximum flexibility while ensuring reliability of the system and its documentation, the methodology follows the object-oriented analysis and design paradigm. The concept of intelligent instrumentation is implemented in a distributed realtime environment that is compatible with conventional sensors and transducers. The software-based environment enables the development of the modular instrumentation

system by providing mechanisms for scheduling and activation of acquisition and processing objects, by managing data exchange between the nodes of a distributed system and between individual objects, and by synchronizing the clocks in a distributed system. Finally, the environment supports different computer platforms, while maintaining computational performance with respect to dedicated software developments on each of these.

The methodology is applied in a case study in human-factors flight test. An instrumentation system was analyzed, designed, and implemented in accordance with the new approach and has been used in a series of flight tests. During these experiments, the use of a perspective flight path display for aircraft guidance was investigated in flight. The experiment is a typical example of the closed-loop handling qualities flight tests that have been described in the previous sections. The presence of the pilot in the loop and the desire to evaluate handling qualities with the perspective display, pose the most stringent real-time requirements for the whole of the instrumentation system.

This thesis comprises six chapters, each of which starts with an abstract that summarizes the original contributions of the work that is presented. Chapter 1 enumerates the philosophies and concepts that are behind the methodology and introduces the development life cycle for an instrumentation system. Chapter 2 elaborates the analysis, design, and implementation of a flight test instrumentation application. It identifies the primary subsystems and explores their role in various typical open-loop and closed-loop applications. The synthesis and maintenance of an instrumentation system from existing and customized components is discussed, without going into the details of component development. Chapter 3 then describes the development method for the components that make up the instrumentation system, including platforms, sensors and signal conditioners, actuators, and processing software. Chapter 4 presents the exemplary design for the software environment that is required for implementing an instrumentation system according to the methodology. Special emphasis is placed on the features that support distribution of the application over multiple computer platforms, and the activation and interaction of the object-oriented instrumentation components. Chapter 5 introduces a novel clock synchronization algorithm. The algorithm allows local clocks in a distributed system to be synchronized mutually and to an external reference time, thus forming the enabling technology for real-time applications in a distributed system. Finally, chapter 6 describes the case study in a representative closed-loop flight test program. It shows the application of the new design methodology during each of the analysis, design, and implementation activities.

1

# **Development Philosophy**

A development methodology is shaped by a collection of concepts. The instrumentation system development methodology that is presented in this thesis primarily relies on a life cycle model and the concepts of object orientation and concurrency. Object orientation, concurrency, and development life cycles stem for software engineering. Their applicability is based on the strong similarities from a development point of view between flight test instrumentation systems and software packages. In both cases, maintenance does not consist of examination and repair of the finished product, but to extension and adaptation to continuously changing requirements over a comparatively long period of time. This requires improved flexibility of the development life cycle in comparison with more traditional methods.

This chapter presents a new life cycle model that is tailored to the development of flight test instrumentation systems. It is a combination of the evolutionary prototyping model with elements from throwaway prototyping and hierarchical design. The new method strongly encourages the development of standardized components – both for hardware and software – that can be reused in future applications. Component development is therefore placed in a separate life cycle within that of the application. Standardized components are specialized for use in each application; the application life cycle merely consists of requirement specification and architectural design before component development, and system integration afterwards. A development method prescribes the designer a series of steps that lead from the requirements for a product to its design and implementation. A method covers a description of each step, and the sequence in which they should be undertaken. As such, the development method helps the designer in making the right design decisions by offering both the criteria and the appropriate context, whenever the development process arrives at a point where a decision must be made.

Development methods rely on design concepts, which are the fundamental ideas on which a design can be based. A successful – or even correct – design in terms of the development method, is a design that incorporates the design concepts. As such, design concepts can be seen as requirements for the final design; the development method is a procedure that ensures satisfaction of these requirements. The key activities that make up the analysis and design procedures, are referred to as modeling strategies. A modeling strategy provides a specific approach to complete a single step in the development method.

The complete development method is based on a collection of design concepts, applies a collection of modeling strategies and documents the results using a design notation. Although the latter is no part of the development method, the notation must be closely related to the method's underlying design concepts. The design notation must allow for a graphical or textual description of the design in a way, that all characteristics of the design are documented. A design notation that has not been developed with the appropriate design concepts in mind, will generally not meet this requirement. The development methodology that is presented in this thesis, uses the Unified Modeling Language (UML) as its design notation. The Unified Modeling Language is introduced in section 1.4; the UML diagrams that are used in this thesis and their graphical appearances are summarized in appendix A.

# 1.1 Life cycle models

While design concepts and modeling strategies are the building blocks of a development method, the method itself is embedded in the development life cycle. The term life cycle as it used in this thesis stems from software engineering; it indicates a phased approach to the development of an application (Gomaa, 2000, p. 92). Software engineering was developed in the late 1960s as a solution to the problems of ineffectiveness and inefficiency that haunted large-scale software projects. Life cycle models are an important product of the software engineering discipline. They designate the various phases of software development and define how and when each phase goes over in the next, and which iterations can be made. This way, they help the designers to plan the project with respect to time and to avoid confusion of design activities from different phases.

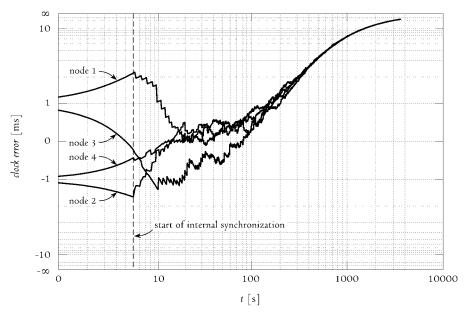

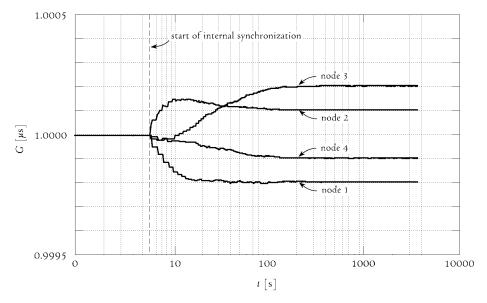

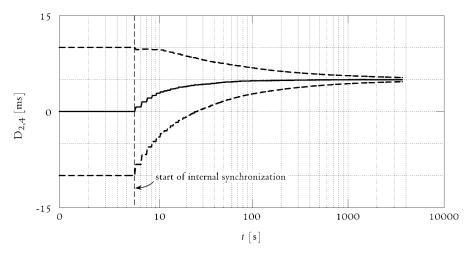

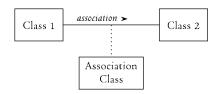

For the development of hardware, the term life cycle refers to the lifetime of the physical machinery. Although the life cycle includes its production, the cycle as a concept focusses on the product's maintainability. The ease at which correct functioning of the hardware can be supported and the ease at which repairs can be carried out, determine the success of the design in terms of the product's maintainability. Although the term maintenance is used in software engineering as well, it relates to a concept completely different from the one in hardware development. Software does not wear down; it requires no attention or repairs to preserve its functionality. For software systems, the term maintenance actually refers to redesign and reimplementation. Software maintenance covers the extension or improvement of the system, in order to make it more suitable for its existing application or to extend its applicability. In conjunction with software development, the term maintenance therefore indicates a new iteration through the design and implementation process. In the same context, it is exactly this repeated sequence of development phases for which the term life cycle is used.