# Design and Integration of Graphene Sensors with Read-Out Electronics

# A Graphene-Based Pirani Pressure Sensor Integrated with the BICMOS Process

by

#### Joost Romijn

in partial fulfillment of the requirements for the degree of

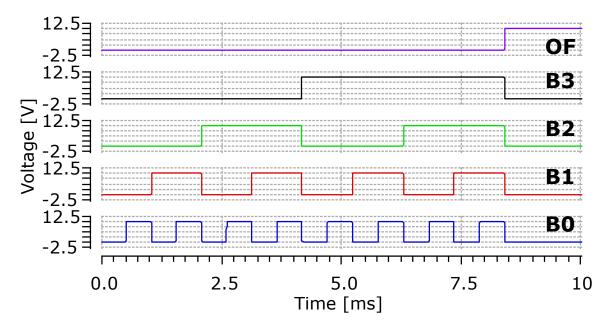

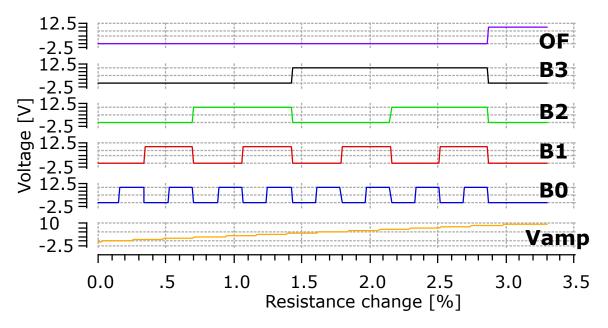

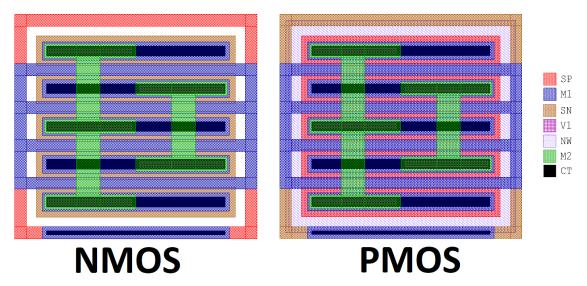

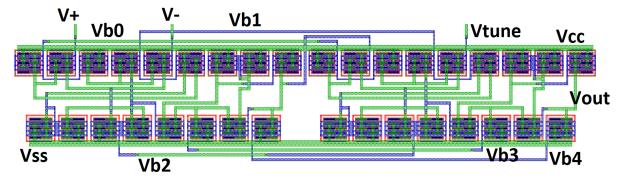

#### **Master of Science**

in Electrical Engineering

at the Delft University of Technology, to be defended publicly on March 2, 2018 at 14:00.

Student number: 4223802

Project duration: November 14, 2016 – March 2, 2018

Responsible professor: Prof. dr. P. M. Sarro Daily supervisor: Dr. ir. S. Vollebregt

Thesis committee: Prof. dr. P. M. (Lina) Sarro, Professor/Chairman at ECTM in EEMCS, TU Delft

Dr. ir. S. (Sten) Vollebregt, Assistant professor at ECTM in EEMCS, TU Delft

Prof. dr. P. G. (Peter) Steeneken, Ir. R. J. (Robin) Dolleman, Professor at PME in 3mE, TU Delft PhD candidate at QN in AS, TU Delft

An electronic version of this thesis is available at http://repository.tudelft.nl/.

# **Abstract**

In this research work, efforts have been made to successfully integrate graphene in a standard CMOS fabrication process without the need for wafer-to-wafer transferring. For this purpose, a graphene-based Pirani sensor is integrated in the BICMOS process. Two batches of graphene-based Pirani sensors are characterized, resulting in world's first operating graphene-based Pirani pressures sensors. The maximum measured resistance change is 2.8 % which is comparable to current state-of-the-art implementations using other materials. The graphene-based implementation allowed for miniaturization of the devices with low power consumption design possibilities.

The BICMOS technology used at EKL at the Delft University of Technology is characterized and effects of graphene growth are investigated. This led to an electrical read-out design in CMOS technology of which the digital circuits performed as designed. Operational digital logic gates were measured alongside grafeen, but with a reduced yield. The analog circuits proved to be challenging in the BICMOS technology and did therefore not operate as intended. From this it is concluded that it is indeed possible to integrate grafeen with a CMOS process.

Future research work that focuses on the details of the fabrication process flow should result in higher fabrication yields and better reproducibility. Additional measurements on the grafeen structures will help to characterize the graphene-based Pirani better and allow for attempts to fit an analytical model to the measurement data.

## Preface

This thesis is part of the Master graduation project that is conducted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering. The project is conducted over a period of fifteen months. During this project, a graphene-based Pirani pressure sensor is integrated in the BICMOS process of the TU Delft to demonstrate that graphene is compatible with standard CMOS processing.

In the first stage of this project, the focus lay on characterization of the Pirani pressure sensor. Earlier attempts of fabricating such a device were already contucted by Sten and Robin. I observed how the most recent batch was fabricated by Sten at Kavli, which I could then start to characterize in a controlled pressure measurement setup. This setup was build by Robin, who then showed me how to use it. The results were good and the first working devices were a fact. A second batch was made and characterized after that to acquire more data. Not all parameters of the existing analytical model for Pirani pressure sensors in literature could be determined beforehand. Therefore, the electrical read-out design was based purely on the measurement results.

The second stage involved clean room training and characterization of the CMOS devices before and after a graphene growth process. The training was given mainly by Sten and discussions on the characterization were often with Henk van Zeijl. The graphene growth step effects on the CMOS devices are clear, but the causes are left open to discussion as this would involve too much time to fully investigate.

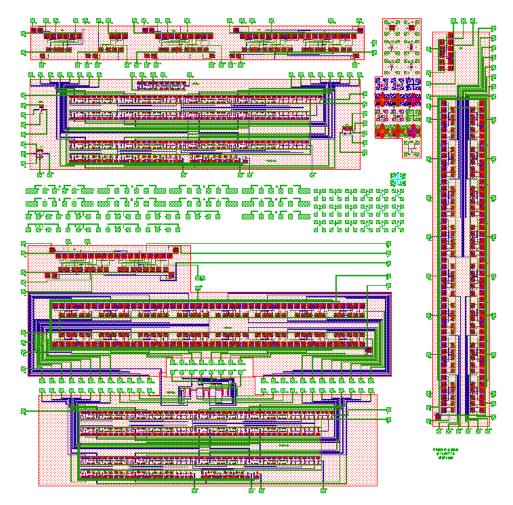

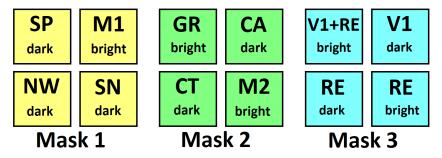

During the third stage of the project, the electrical design of the read-out electronics was performed. This involved both analog and digital design in Cadence Virtuoso. Instructions on the software and discussions on the design with Ronaldo Martins da Ponte were very valuable. After extensive simulations, the layout was made also in Cadence. This layout was exported to L-Edit, were the final layers involving the graphene-based Pirani pressure sensor were created. In total three masks with each four images were ordered and used in the fabrication process.

In the fourth stage the fabrication process was performed, which involved many trial and error steps in the process to achieve the desired result. The preservation of the graphene and molybdenum until the final process steps, proved to be the largest challenge in fabrication. Many discussions with Sten on the results eventually led to the working process that is presented.

The final stage of this project was the characterization and verification of the fabricated devices. Simple circuit measurements could be performed in a probe station. The larger circuits were measured in a wire bonded package on a bread board. The measurement equipment in the Tellegen Hall at EEMCS was used for these electrical measurements. Finally, the pressure controlled measurement setup build by Robin was used to perform pressure dependency measurements. The result is a successful integration of a graphene-based Pirani pressure sensor with CMOS electronics, even though not all designed read-out electronics are operational.

The thesis committee consists of professor Lina Sarro, the head of the ECTM laboratory, my daily supervisor Sten Vollebregt, highly involved PhD candidate Robin Dolleman at Quantum Nanoscience at Applied Sciences and professor Peter Steeneken at PME at Mechanical Engineering.

Joost Romijn Delft, February 2018

## Acknowledgments

There were many people involved in this project and together we achieved the successes presented in this thesis work. First of all, I thank my daily supervisor Sten. His enthusiasm, creativity and commitment inspired me to strive for the best results in each stage. He is always prepared to discuss problems or provide help. Secondly, I thank Robin for his work and help regarding the pressure dependency measurements and Pirani pressure sensor characterization. I thank Henk for discussions and help on fabrication in the clean room, Ronaldo for discussions on measurements results and help in designing, Manju for help on MEDICI and TSUPREM simulations, Zahra for providing a starting point in my design and Laurens for his work on a visualization program for wafermaps. Furthermore, I thank all people involved at the clean room for their help and hard work and my office mates Levar, Thijs, Ziqiao and the other master students for their support and cheerful company. I thank all people who took the time to read the draft versions of this thesis and provided critical feedback to improve it. Finally, I thank my parents for their support, patience and understanding throughout my entire studies.

# Contents

| Al | abstract                                                                                                                                                                                                                                                                                                                                                                                                                                        | iii                                            |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Pr | Preface                                                                                                                                                                                                                                                                                                                                                                                                                                         | v                                              |

|    | Acknowledgments                                                                                                                                                                                                                                                                                                                                                                                                                                 | v                                              |

| 1  | Introduction       1.1 Problem Formulation       1.2 Proposed Solution       1.3 Research Goals                                                                                                                                                                                                                                                                                                                                                 | 2                                              |

| 2  | Background Theory                                                                                                                                                                                                                                                                                                                                                                                                                               | 5                                              |

|    | 2.1 Pirani Pressure Sensor 2.1.1 Theory and Architecture of the Pirani Pressure Sensor. 2.1.2 Analytical Model of a Pirani Pressure Sensor 2.1.3 Graphene-Based Pirani Pressure Sensor Fabrication. 2.2 Graphene Growth and Characterization 2.2.1 Selective CVD of Graphene on Molybdenum 2.2.2 Graphene Characterization Technique 2.3 BICMOS Process 2.3.1 BICMOS Core Fabrication Steps 2.3.2 Threshold Voltage Adjustment. 2.4 Conclusions | 5<br>5<br>7<br>9<br>10<br>11<br>12<br>13<br>13 |

| _  |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                |

| 3  | Graphene-Based Pirani Pressure Sensor Characterization 3.1 First Batch Graphene-Based Pirani Sensor Results 3.2 Second Batch Graphene-Based Pirani Sensor Results 3.3 Pirani Pressure Sensor Design Choices 3.4 Bridge Material Parameter Measurements 3.5 Conclusions                                                                                                                                                                          | 19<br>21<br>23                                 |

| 4  | BICMOS Characterization                                                                                                                                                                                                                                                                                                                                                                                                                         | 25                                             |

| •  | 4.1 Training Run Reference Wafer 4.2 Different Interconnect Materials and Processes 4.3 Effect of Graphene Growth on BICMOS Characteristics 4.4 Analysis of the Effects of Graphene Growth on the Threshold Voltage 4.5 Conclusions                                                                                                                                                                                                             | 26<br>27<br>29<br>30                           |

| 5  | Read-Out Electronics and Complete Layout Design                                                                                                                                                                                                                                                                                                                                                                                                 | 33                                             |

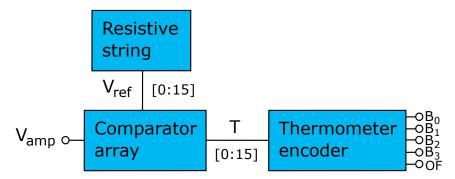

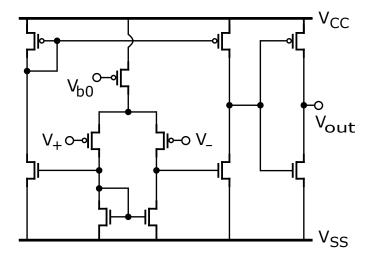

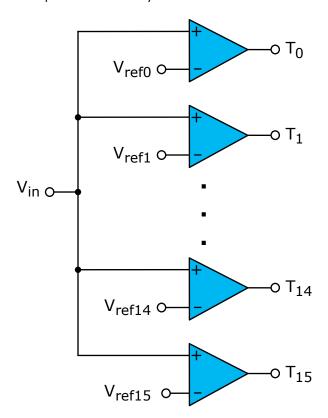

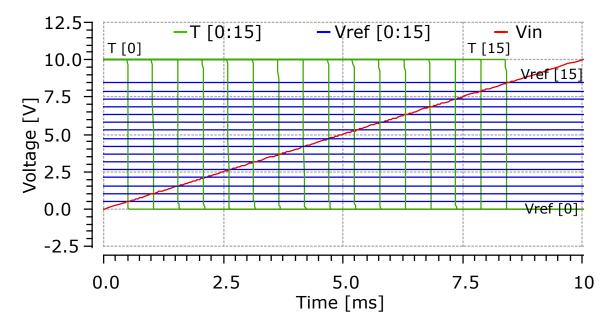

|    | 5.1 Sensor Read-Out Topology 5.2 Amplifier Circuit Design 5.3 Analog-to-Digital Converter Design 5.4 Complete Circuit Design Simulation 5.5 Layout Design of the Complete Circuit 5.6 Conclusions                                                                                                                                                                                                                                               | 35<br>40<br>43<br>44                           |

| 6  | Fabrication Results and Discussion                                                                                                                                                                                                                                                                                                                                                                                                              | 51                                             |

|    | 6.1 Fabrication Run Reference Batch. 6.2 Graphene Implementation in the Fabrication Process. 6.3 Graphene Protection During First Metallization 6.4 Dielectric and Second Metallization Implementation 6.5 Pirani Pressure Sensor Cavity Etch and Release. 6.6 Conclusions                                                                                                                                                                      | 53<br>54<br>55<br>57                           |

| 7  | Implemented Design Characterization and Verification                                                                                                                                                                                                                                                                                                                                                                                            | 61                                             |

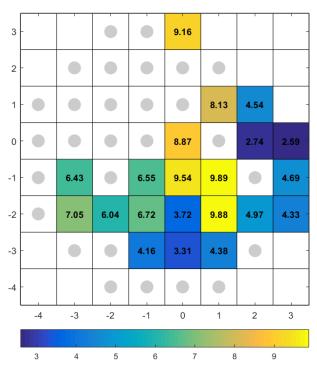

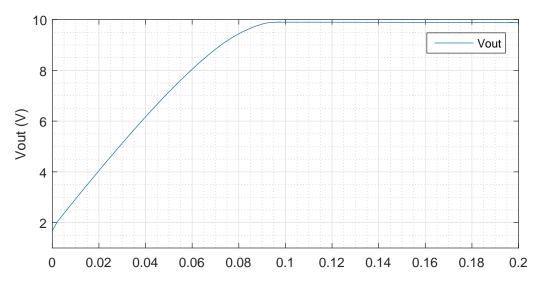

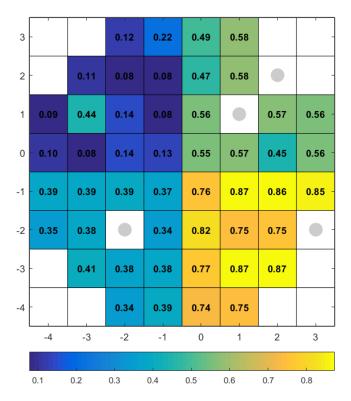

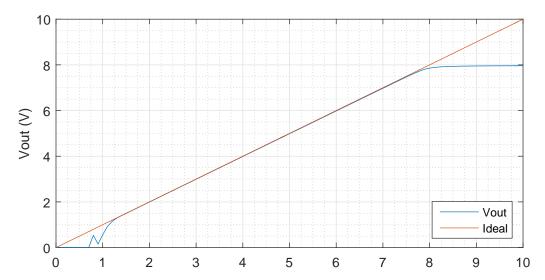

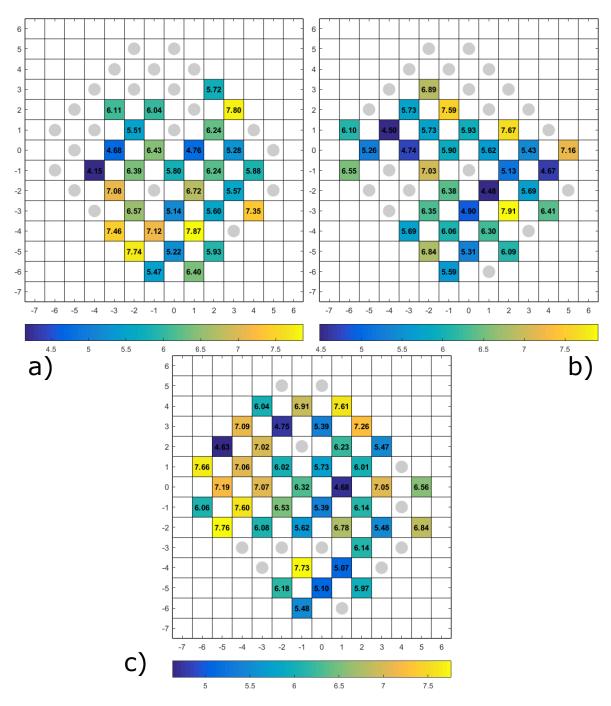

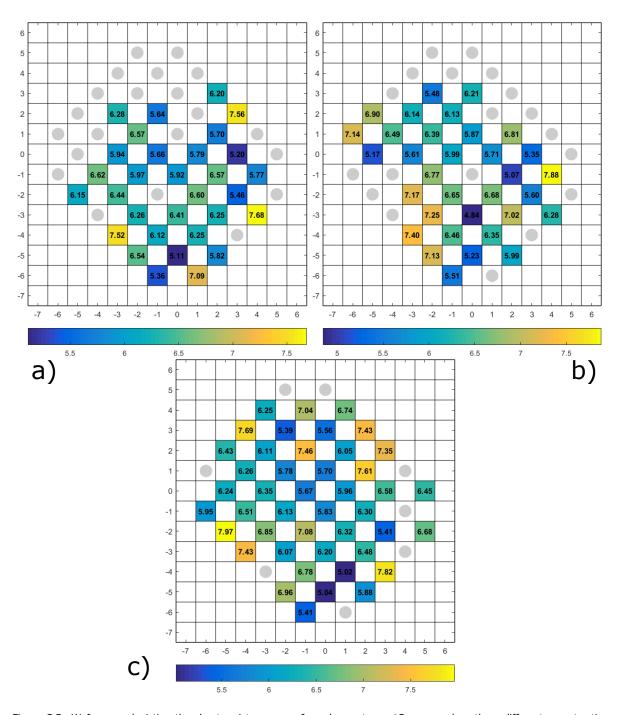

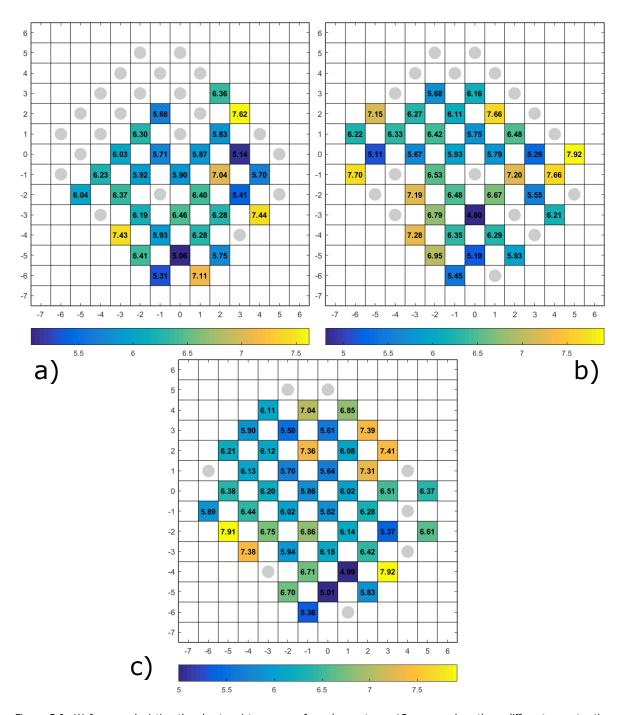

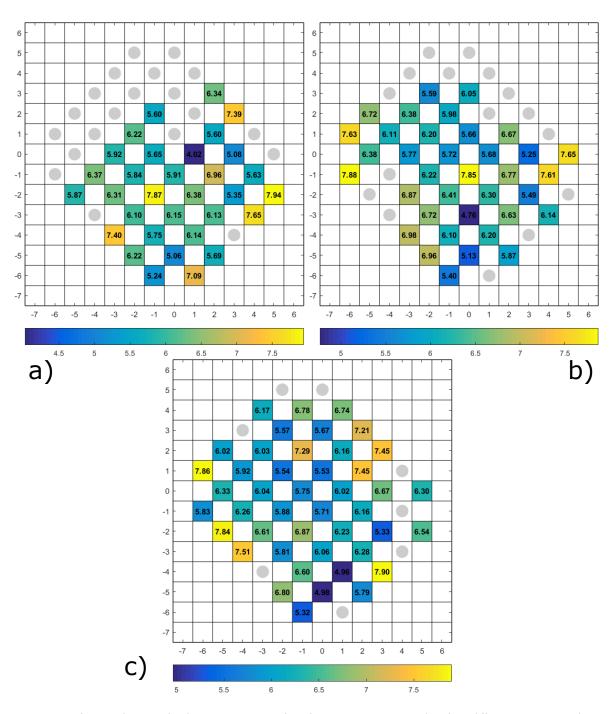

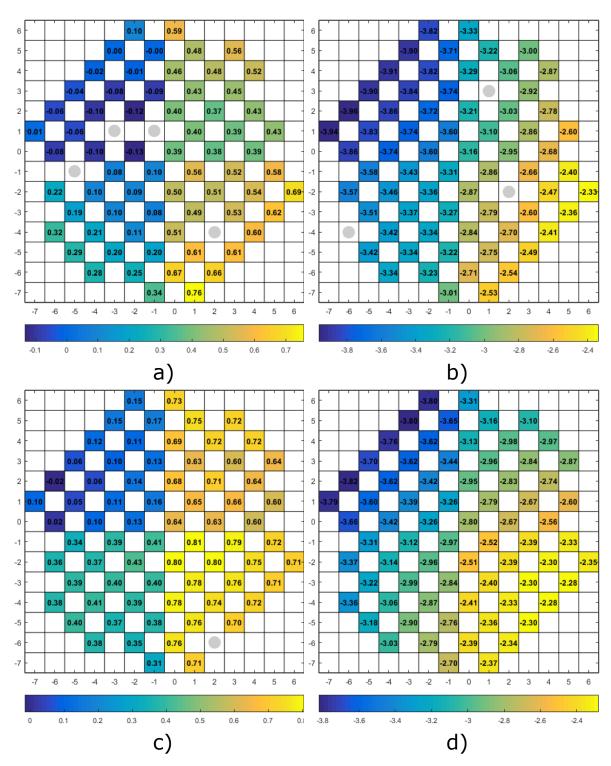

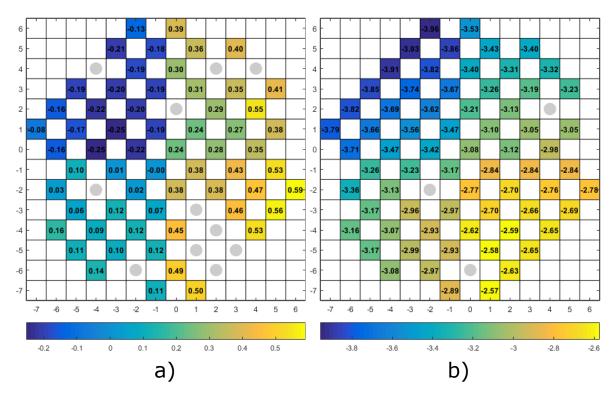

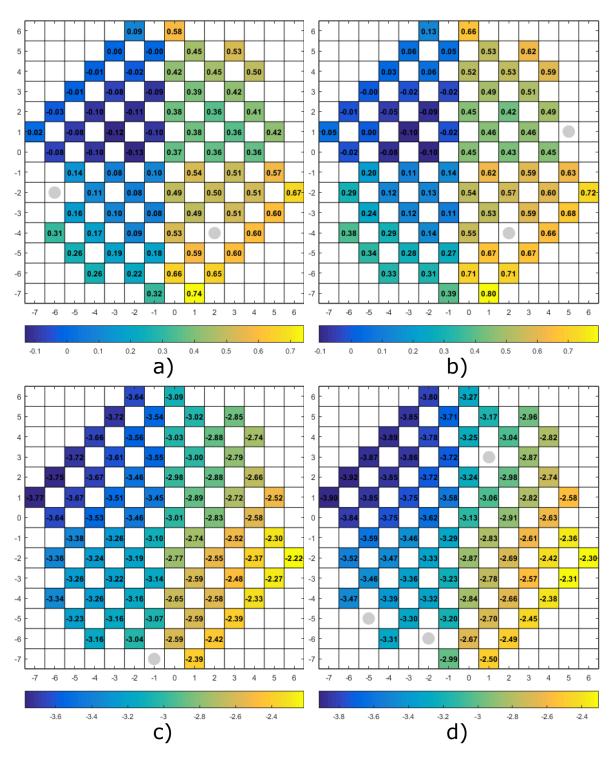

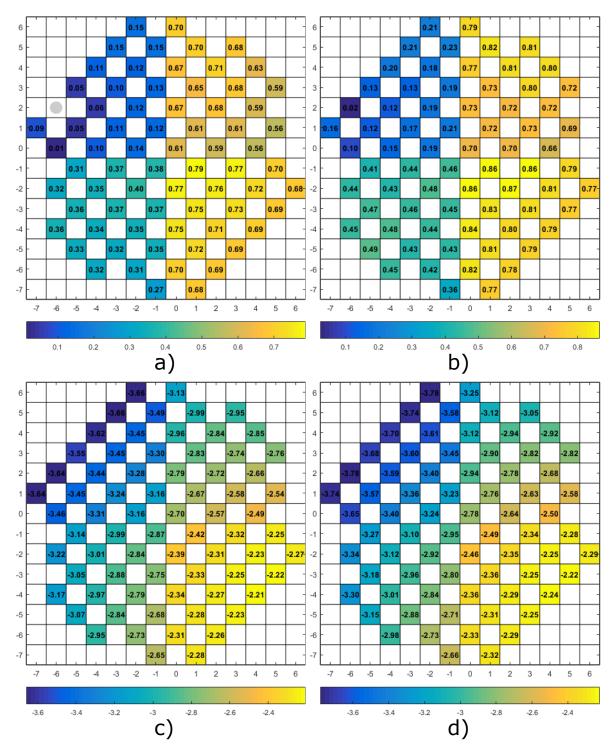

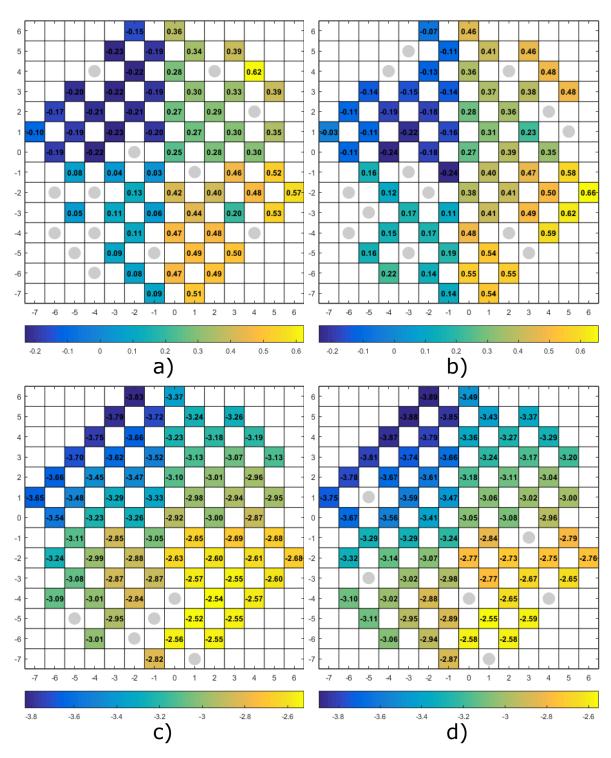

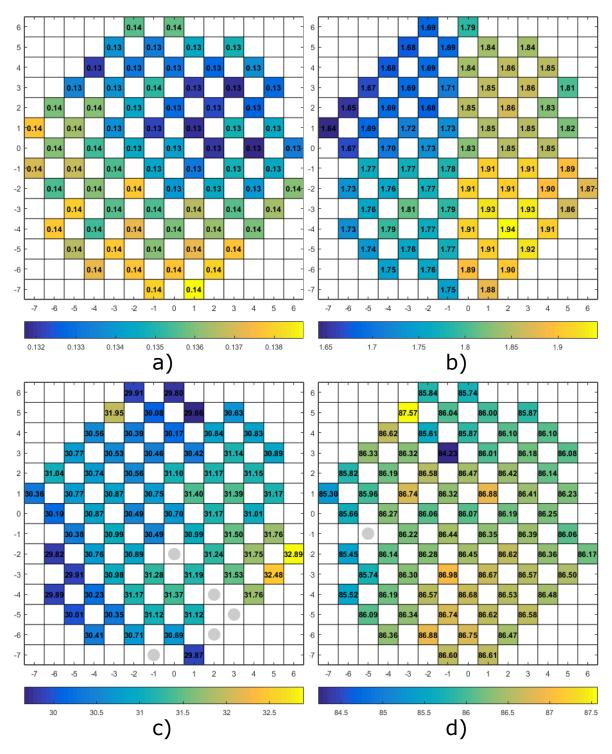

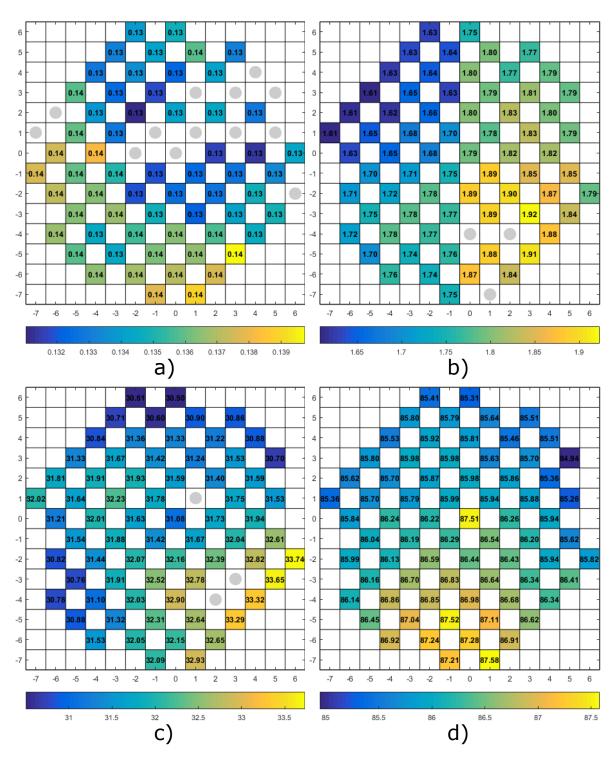

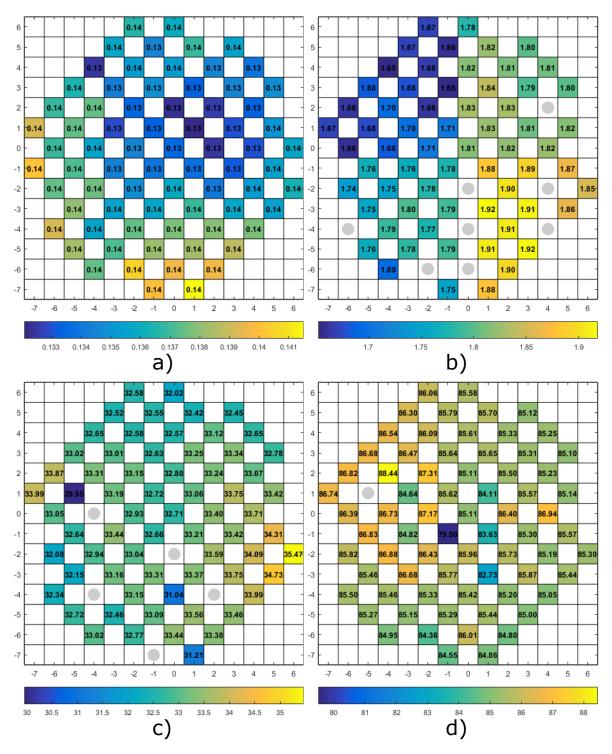

|    | 7.1 Wafer-Scale Measurement Results                                                                                                                                                                                                                                                                                                                                                                                                             | 67                                             |

viii Contents

| 8  | Conclusions and Recommendations 8.1 Summary of Research Conclusions | 70  |

|----|---------------------------------------------------------------------|-----|

| A  | List of Acronyms                                                    | 71  |

| В  | Background Theory                                                   | 73  |

| C  | Graphene-Based Pirani Pressure Sensor Characterization              | 75  |

| D  | BICMOS Characterization                                             | 83  |

| E  | Read-Out Electronics and Complete Layout Design                     | 99  |

| F  | Fabrication Results                                                 | 105 |

| G  | Design Characterization                                             | 119 |

| Bi | bliography                                                          | 125 |

1

# Introduction

Nowadays, many regular kinds of electronics are upgraded to a smart variant of that particular electronic device, which results in smart homes, smart phones, smart sensors, smart cars, etc. This 'More than Moore' trend requires an increased functionality of the existing electronic designs. For this purpose, integrated sensors with improved sensitivity, lower power consumption and smaller footprint are required. This is achieved by introducing new materials with favorable properties for sensing applications. The integration of these new materials in standard CMOS processes, allows for sensor signal read-out and conditioning on chip in favor of the smart sensors.

For successful integration of new materials in the CMOS process it is important that the yield is high and that they can be patterned by lithography. So far the integration of graphene with CMOS electronics is only achieved by wafer-to-wafer transferring. Such transfer steps induce wrinkles and defects in the transferred material, which impacts the yield and reproducibility. Furthermore, the alignment is not guaranteed and therefore no small structures are transferred, which poses difficulties during the patterning after transfer. Successful integration therefore demands that the new material and the CMOS devices are fabricated without a wafer-to-wafer transfer step.

A novel material with promising properties for sensor applications is graphene. Graphene is a two dimensional sheet of carbon atoms that has a thickness of a single atom and is ordered in a hexagonal structure, as illustrated in Figure 1.1. Several layers of graphene on top of each other is called multi-layer graphene, while the single layer is often called mono-layer graphene. It was first created using scotch-tape exfoliation from a graphite crystal for which the discoverers received the Nobel prize in 2010 in Physics [1]. Graphene has several remarkable properties such as high area to thickness ratio, high elasticity, high mechanical strength, high carrier mobility and high thermal conductivity [2–4]. There are no other known materials that possess these properties, which is why graphene is called the first super material.

These properties make graphene a promising material for applications involving flexible, transparent and conductive thin films [5] and high frequency transistors exceeding state-of-the art silicon transistors performance [6]. Recent developments in synthesis of large area mono-layer graphene films has enabled studies of various potential sensor types based on graphene [7, 8]. This includes chemical, electrochemical, photoelectric, electric field, magnetic field and mechanical sensors [9, 10].

However, so far this material has not yet been integrated without wafer-to-wafer transfer with CMOS electronics, which renders its full potential unused in the trend towards a world with smarter devices. To open possibilities for integrated graphene sensors in smart devices in the future, the challenge of integration without wafer-to-wafer transfer in a standard electronics fabrication process has to be overcome. This is the main driving force behind this thesis research work. This work aims on introducing world's first integration of graphene with CMOS electronics, without a wafer-to-wafer transfer step. This opens the door to graphene-based sensors integration with read-out electronics with a high yield and satisfies the 'More than Moore' trend in pursuit of a world with smarter devices.

This research work is considered successful when working CMOS circuits as well as an operating graphene-based structure are implemented alongside each other without a transfer step. The success is arguably already achieved if single CMOS devices are found to be operating, but working circuits demonstrate that the process allows for designing circuits as well. The best expected result is an integration in which the graphene-based structure is connected to CMOS electronics successfully.

2 1. Introduction

Figure 1.1: Illustration of a mono-layer graphene film [11].

#### **1.1.** Problem Formulation

The potential of graphene as a material for various applications is not incorporated in electronics, as no fabrication process without wafer-to-wafer transfer currently exists. It is therefore of great value to investigate the feasibility of such a process with the current technology to allow for further advances in the trend of smart devices that require improved integrated sensors. In this research it is important to asses the implications on the already existing fabrication process of single graphene devices and standard electronics. As a result, the central research question that drives this research work is:

"Can graphene synthesis be integrated in a standard CMOS process, without wafer-to-wafer transfer?"

Additionally, the research project is given a more concrete goal by defining the application in which graphene is to be incorporated. This is done by choosing a graphene-based sensor on which promising efforts were already made by Sten Vollebregt and Robin Dolleman, which is the Pirani pressure sensor. The architecture, properties and advantages of a graphene-based variant of this sensor are discussed in the background theory in Section 2.1.1. However, a graphene-based Pirani pressure sensor has not been reported yet. It is therefore required to first investigate the feasibility and advantages of such a device. The additional research question is:

"Can a Pirani pressure sensor be based on graphene and what are the advantages?"

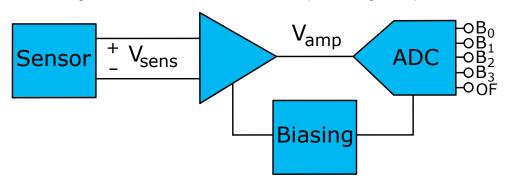

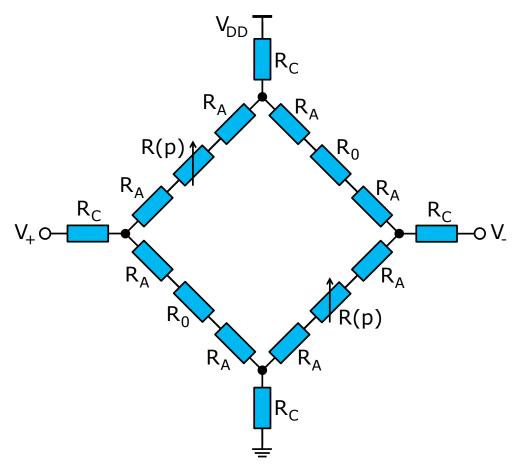

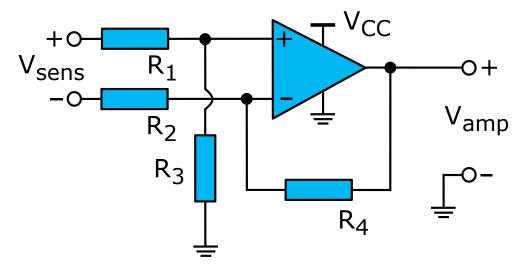

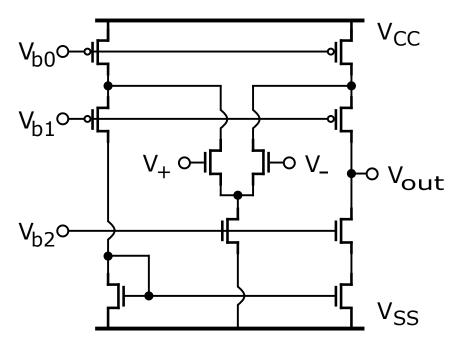

Although the main research question can also be answered by implementing a graphene device and some generic electronics on the same die without wafer-to-wafer transfer that are not connected, the ultimate application is a fully interconnected design. To integrate the graphene-based Pirani pressure sensor with standard electronics, read-out electronics are to be designed that interface with the sensor. These read-out electronics consist of a graphene-based sensor topology, signal amplifier and analog-to-digital converter. No specific requirements for the read-out electronics such as amplifier gain or analog-to-digital converter resolution are given, as it is pure proof of principle.

## 1.2. Proposed Solution

The additional research question is to be answered first. For the implementation of the graphene-based Pirani pressure sensor, the fabrication method that results from the efforts made by Sten Vollebregt and Robin Dolleman is used as a starting point. This fabrication method is described in detail in the background theory in Section 2.1. This method does not require wafer-to-wafer transfer, which is a requirement for the main research question. If a graphene-based Pirani pressure sensor is fabricated successfully, it is to be characterized to provide a starting point for the design. Therefore, it is investigated which sensor dimensions produce good results and the device is characterized electrically.

After successful results in the implementation of the graphene-based sensor, attempts can be made to integrate it in the standard electronics fabrication process developed at the Else Kooi Laboratory to answer the main research question. Since the implementation of graphene used in the graphene-based Pirani sensor is at high temperature, most metals used conventionally for the device interconnect material will melt during that process step. The

1.3. Research Goals 3

graphene implementation is therefore performed before the metal interconnect implementation. Furthermore, the graphene implementation is performed in a potentially copper contaminated environment, which poses restrictions on allowed processes after that step. It is therefore desired to postpone the graphene implementation towards the end of the fabrication process. The graphene implementation process is therefore integrated with the standard electronics fabrication process by placing the required steps between the front-end and back-end of line (BEOL) of the fabrication process.

#### 1.3. Research Goals

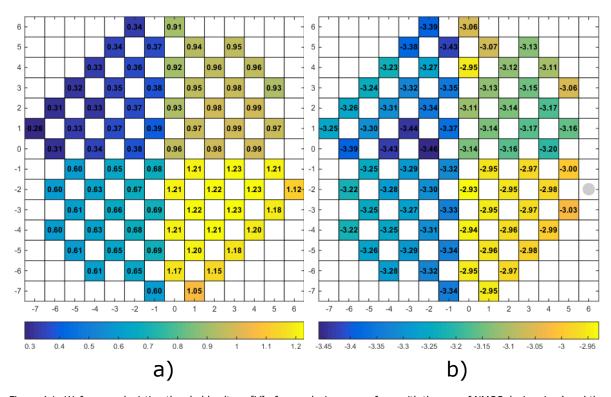

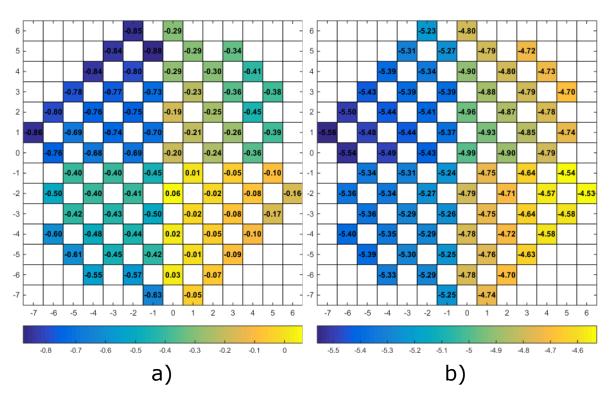

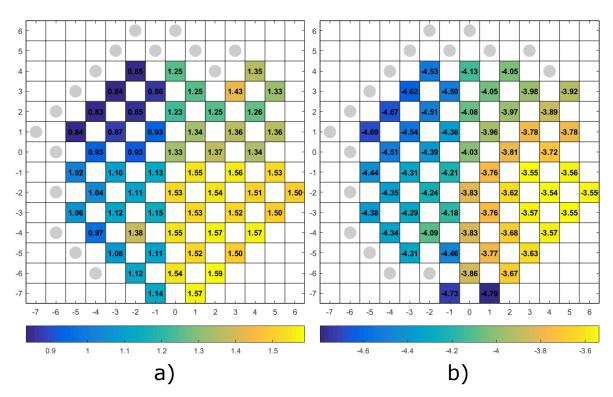

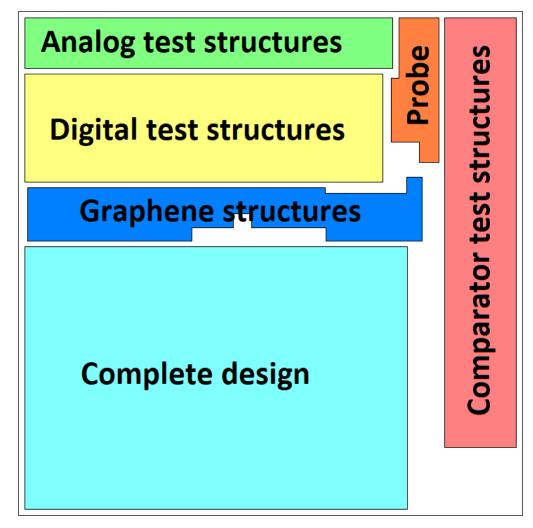

To achieve the proposed solutions, several research goals are formulated and listed below. Each individual research goal is equally important in answering the research question. Therefore, each research goal is defined as a research stage and has its own chapter in this thesis. Prior to the chapters that each house a research goal, the required background theory is given in Chapter 2. The thesis is concluded and recommendations for future work are given in Chapter 8. The Appendix lists additional figures and measurement results as well as a list of used acronyms. The listed probe station measurement results could be visualized in colorful wafermaps due to the results of a case study by Laurens van Dam.

- 1. **Implementation and characterization of the graphene-based Pirani sensor**In this stage the implementation of the graphene-based Pirani sensor is investigated and characterized. The

- results are given in Chapter 3.

- 2. Characterization of the standard electronics and the effect of the graphene implementation at high temperature

During this stage clean room training is followed during which the standard electronics are fabricated and characterized. This is followed by a run that incorporates the graphene growth step to investigate the effects on the devices. The results are discussed in Chapter 4.

- 3. **Electrical design of the read-out electronics and mask design of the complete design**The read-out electronics are designed and simulated during this stage accordingly to measurement results obtained in the previous stages. The layout is then designed and completed by adding the graphene-based sensor layers. The results are elaborated in Chapter 5.

- 4. **Defining the details of a suitable integrated fabrication process**In this stage the fabrication of the design is performed. To find a suitable fabrication process, different approaches are investigated to find the most suitable solution. The results are given in Chapter 6.

- 5. **Characterization and verification of the fabricated devices**In this final stage measurements are performed to test the success of integrating the graphene-based sensor in the standard electronics fabrication process. The results are discussed in Chapter 7.

# **Background Theory**

This chapter addresses the research topics with corresponding studies that are relevant to this research. The theory, architecture, fabrication and analytical model of the Pirani pressure sensor is discussed in Section 2.1. The graphene synthesis and characterization are then discussed in Section 2.2. This is followed by the description of the BICMOS process and a model for the device threshold voltage. Finally, the chapter is concluded by a short summary of the findings.

#### 2.1. Pirani Pressure Sensor

Pirani pressure sensors are an attractive and often used sensor due to their simplicity and robustness as no hermetic cavity, moving parts or accurate deflection measurement methods are required. However, current Pirani implementations are bulky and not suitable for low power applications. Typical dimensions are 100  $\mu$ m x 200  $\mu$ m or larger, with power consumption of 1 mW or more and operating range of 10<sup>-3</sup> mbar to 10<sup>3</sup> mbar [12–15]. An implementation with much smaller footprint, lower power consumption and higher operating range has been achieved by using CNTs, but the reported fabrication process gives unpredictable results and low yield [16].

#### **2.1.1.** Theory and Architecture of the Pirani Pressure Sensor

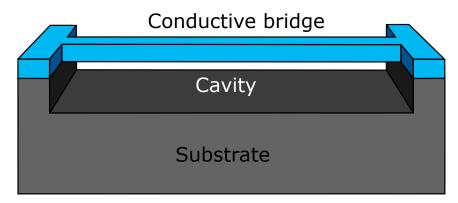

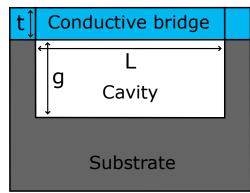

The Pirani pressure sensor is based on the principles of resistive heating and heat conduction. The standard Pirani sensor architecture is illustrated in Figure 2.1 where an electrically conductive bridge is implemented over a cavity in the wafer substrate. Alternative Pirani architectures exist such as a buried architecture [15]. The device is placed in a gas mixture and an electrical current is forced through the bridge. The forced current generates heat in the bridge, which is partially absorbed by colliding particles in the gas mixture. The final increase of the bridge temperature is therefore dependent on the composition and pressure of the gas mixture. The electrical resistance of the bridge material changes as a result of the temperature increase. This resistance is therefore also dependent on the gas mixture composition and pressure. The boundary conditions for this principle to work, are discussed next.

Figure 2.1: Pirani pressure sensor architecture [15] with the conductive bridge marked in blue over a cavity in the substrate.

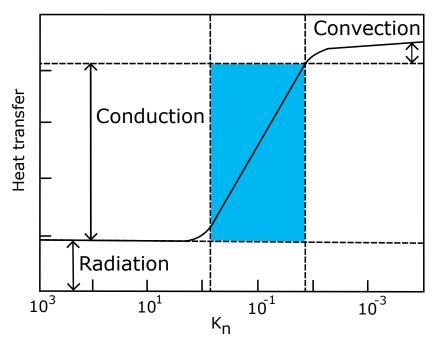

The first boundary condition affects the used substrate material. For the Pirani sensor to operate effectively, the substrate should not conduct a significant amount of electrical current compared to the bridge. Secondly, the gas mixture composition and pressure need to be in a specific range for the principle of heat conduction to be dominant. This specific range is related to Knudsen's number. The relation between Knudsen's number and the heat transfer is depicted in Figure 2.2. There are three different types of heat transfer, each of which is dominant in a specific range of Knudsen's number. These heat transfer types are radiation, conduction and convection and are marked in the graph. The boundary condition for the Pirani sensor requires that the heat transfer is dominated by conduction as in that case the gas composition and pressure influence the cooling. This desired range is marked with blue in the graph. The corresponding range of Knudsen's number is roughly 0.01 to 1. These limits are later used in combination with the value of the cavity depth to find the pressure range.

Figure 2.2: Relation between the heat transfer and Knudsen's number. The three heat transfer types are indicated and the desired heat transfer range for the Pirani sensor is marked in blue [17].

Knudsen's number  $K_n$  is calculated by Equation 2.1 where  $\lambda$  is the average free molecular path of the gas surrounding the bridge and g the characteristic length of the device, which is equal to the cavity depth of the Pirani sensor. Note that Knudsen's number is dimensionless.

$$K_n = \frac{\lambda}{g} \tag{2.1}$$

The average free path is calculated by Equation 2.2 where  $d_0$  is the average molecular diameter and n the density in atoms per volume of the gas mixture surrounding the conductive bridge [17]. In this research, the gas mixture is regular air, which has an average molecular diameter of  $9.7 \cdot 10^{-10}$  m [18].

$$\lambda = \frac{1}{\sqrt{2}\pi d_0^2 n} \tag{2.2}$$

The pressure is calculated by Equation 2.3, which gives the ideal gas law. Here, T is the gas temperature,  $\rho$  the density in mass per volume and  $R_d$  the gas constant for dry air which is 287 J·kg<sup>-1</sup>·K<sup>-1</sup> [19].

$$P = \rho R_d T \tag{2.3}$$

Finally, the two densities n and  $\rho$  are related by Equation 2.4 where  $M_d$  is the molar mass of dry air and  $N_A$  the Avogadro constant, which equal  $2.896 \cdot 10^{-2}$  kg·mole<sup>-1</sup> [20] and  $6.022 \cdot 10^{23}$  mole<sup>-1</sup> respectively.

$$\rho = n \frac{M_d}{N_A} \tag{2.4}$$

Equations 2.1-2.4 are combined and solved in Equation 2.5 for the pressure in terms of the cavity depth, as this is the only undetermined parameter left. The operational pressure range is found by filling in the limits of Knudsen's number. The result dictates that the operational pressure range scales inversely proportional with respect to the cavity depth and no other geometry parameters have any influence on the pressure range.

$$P = \frac{R_d M_d T}{\sqrt{2} \pi d_0^2 N_A K_n} \frac{1}{g}$$

(2.5)

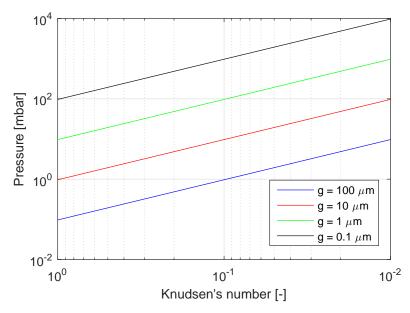

Equation 2.5 is now used to obtain the pressure range corresponding to the found Knudsen's number range for different values for the cavity depth. The investigated cavity depth values are 100  $\mu$ m, 10  $\mu$ m, 10  $\mu$ m, 10  $\mu$ m, and 0.1  $\mu$ m, which are considered typical values. The result is depicted in Figure 2.3. The pressure range clearly scales inversely proportional with respect to the cavity depth. Atmospheric pressure is at approximately 10³ mbar, which implies that the pressure range results are generally for low pressures. The exception is a cavity depth of 0.1  $\mu$ m, which results in a pressure range of 10² mbar to 10⁴ mbar.

Figure 2.3: Pressure ranges of Pirani sensors with four different values for the cavity depth in the found Knudsen' number range.

#### 2.1.2. Analytical Model of a Pirani Pressure Sensor

A widely used and confirmed analytical model of the Pirani pressure sensor is presented below [15, 21]. The Pirani sensor geometry parameters bridge length L, thickness t and width w and the cavity depth g are depicted in Figure 2.4, which depicts the top and side view of the Pirani sensor architecture of Figure 2.1.

The conductive bridge pressure dependent resistance R(p) is calculated by Equation 2.6 where  $R_{\square}$  is the sheet resistance of the bridge material measured at room temperature and ambient pressure,  $\xi$  the temperature coefficient of resistance (TCR) of the bridge material and  $\bar{u}(p)$  the pressure dependent average temperature rise of the conductive bridge as a result of resistive heating caused by an electric current.

$$R(p) = R_{\Box} \frac{L}{w} (1 + \xi \bar{u}(p))$$

(2.6)

The pressure dependent average temperature rise of the conductive bridge  $\bar{u}(p)$  is calculated by Equation 2.7 where  $\delta$  represents the ohmic heat generation and  $\epsilon(p)$  the pressure dependent heat conduction to the gas surrounding the conductive bridge.

$$\bar{u}(p) = \frac{\delta}{\epsilon(p)} \left( 1 - \frac{\tanh(\sqrt{\epsilon(p)}L/2)}{\sqrt{\epsilon(p)}L/2} \right) \tag{2.7}$$

# Substrate L w Conductive bridge Substrate

## Side view

Figure 2.4: The Pirani pressure sensor top and side view with the conductive bridge marked in blue. The bridge length L, thickness t and width w and the cavity depth g are indicated.

The pressure dependent heat loss through the gas  $\epsilon(p)$  is calculated by Equation 2.8 where  $\eta$  is the correction factor for the fringing of the heat flux through the cavity that is typically equal to 1,  $\kappa_g(p)$  the pressure dependent thermal conductivity of the surrounding gas mixture and  $\kappa_b$  the thermal conductivity of the bridge.

$$\epsilon(p) = \frac{\eta \kappa_g(p)}{\kappa_h g t} - \delta \xi \tag{2.8}$$

The ohmic heat generation  $\delta$  is calculated by Equation 2.9 where I is the electric current forced through the conductive bridge.

$$\delta = \frac{I^2 R_{\square}}{\kappa_b w^2 t} \tag{2.9}$$

The pressure dependent thermal conductivity of the surrounding gas mixture  $\kappa_g(p)$  is now approximated by Equation 2.10 where  $p_0$  is the transition pressure and  $\kappa_c$  the continuum limit of thermal conductivity, which equals  $2.2 \cdot 10^{-2} \text{ W·m}^{-1} \cdot \text{K}^{-1}$  [15].

$$\kappa_g(p) \approx \kappa_c \left(\frac{p}{p+p_0}\right)$$

(2.10)

The transition pressure  $p_0$  is approximated by Equation 2.11 where  $T_s$  is the substrate temperature and  $\bar{v}$  the average molecular velocity. In this approximation, it is assumed that the substrate temperature is equal to the surrounding gas temperature and that the width of the conductive bridge is several orders of magnitude higher than the thickness  $(w \gg t)$ .

$$p_0 \approx \frac{\eta \kappa_c T_s}{g \bar{v}} \tag{2.11}$$

The average molecular velocity is calculated by Equation 2.12 where  $m_d$  is the average mass of a dry air molecule and  $k_B$  the Boltzmann constant, which equals  $1.381 \cdot 10^{-23} \text{ m}^2 \cdot \text{kg} \cdot \text{s}^{-2} \cdot \text{K}^{-1}$ .

$$\bar{v} = \sqrt{\frac{8k_B T_s}{\pi m_d}} \tag{2.12}$$

Finally, the average mass of a dry air molecule is calculated by Equation 2.13 where  $M_d$  and  $N_A$  represent the previously given molar mass of dry air and the Avogadro constant respectively.

$$m_d = \frac{M_d}{N_A} \tag{2.13}$$

Note that the given analytical model in Equations 2.6-2.13 is to be solved for the pressure dependent resistance R(p) with the pressure p as the single free variable to simulate the electrical graphene-based Pirani pressure sensor behavior. This implies that all other variables need to be determined by literature research, measurements or estimation. These variables can be grouped as physical constants, gas mixture parameters, geometry parameters, bridge material parameters and measurement parameters. For convenience, these groups with corresponding variables are listed in Table 2.1.

Table 2.1: List of grouped variables used in the analytical model for the Pirani pressure sensor.

| Group                      | Variables                            |

|----------------------------|--------------------------------------|

| Physical constants         | $N_A$ , $k_B$ and $\kappa_c$         |

| Gas mixture parameters     | $M_d$ and $T_s$                      |

| Geometry parameters        | $L, w, g, t \text{ and } \eta$       |

| Bridge material parameters | $\xi$ , $\kappa_b$ and $R_{\square}$ |

| Measurement parameters     | I                                    |

The physical constant values are previously given and the gas mixture parameters are determined by assuming dry air at room temperature. Therefore the previously given molar mass of dry air  $M_d$  and substrate temperature  $T_s$  of 293 K are used. The geometry parameters depend on the device implementation and are determined in Section 3.3. The bridge material parameters for graphene are not taken from literature as they depend strongly on the fabrication process and the quality of the graphene. Instead, they are measured on an implemented device in Section 3.4. Finally, the measurement parameter I is given for each measurement, unless it is a voltage controlled measurement. In that case, the analytical model can not be rewritten for a forced voltage due to the hyperbolic function in Equation 2.7, which implies that the current has to be measured or determined quantitatively from the measurement results.

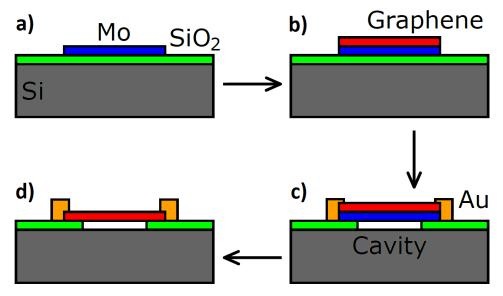

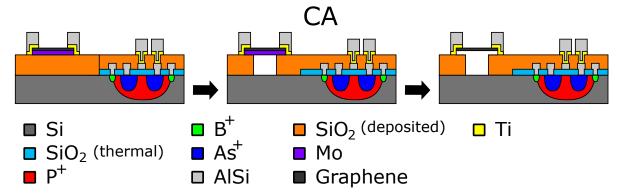

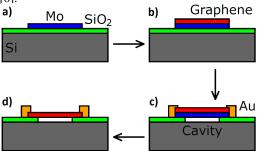

#### 2.1.3. Graphene-Based Pirani Pressure Sensor Fabrication

An overview of the fabrication method that resulted from the efforts made by Sten Vollebregt and Robin Dolleman is schematically illustrated in Figure 2.5. The first step in Figure 2.5a consists of the deposition and patterning of a 50 nm thick molybdenum (Mo) layer on a 600 nm thick silicon dioxide ( $SiO_2$ ) layer on a silicon (Si) substrate. This is followed by the selective chemical vapor deposition (CVD) of graphene on Mo in Figure 2.5b. The details of the graphene growth step are discussed in Section 2.2.1. The metal contacts to the graphene are then implemented by the deposition and patterning of gold (Au) in a lift-off process, followed by the etching of a cavity defined by photoresist under the Mo in the  $SiO_2$  using buffered hydrofluoric acid (BHF) in Figure 2.5c. Finally, the photoresist is removed and the Mo is etched in hydrogen peroxide ( $H_2O_2$ ) in Figure 2.5d followed by critical point drying (CPD) which results in a suspended graphene bridge.

Figure 2.5: Overview of the Pirani sensor fabrication process. In a) the patterning and deposition of Mo on a  $SiO_2$  layer is performed, in b) the selective CVD of graphene on Mo, in c) the metal contact cavity implementation and in d) the Mo etching which result in a suspended graphene bridge.

The proposed Pirani sensor fabrication method as well as the incorporation of graphene as the Pirani bridge material have significant advantages. Firstly, the proposed Pirani fabrication method does not require a wafer-to-wafer transfer step. Secondly, due to the high area-to-thickness ratio, graphene-based Pirani devices can be much smaller than implementations with other materials as these materials would break for such area-to-thickness ratios. This reduces the device footprint which reduces the average fabrication cost and opens possibilities for in

situ pressure monitoring inside sealed MEMS. Thirdly, the fabrication process with tuned cavity depth benefits the design of pressure sensors for specific ranges. Finally, a Pirani sensor can also be used as a gas sensor, as it is dependent on the composition of the gas mixture surrounding the conductive bridge. A graphene-based Pirani sensor therefore offers miniaturization to the field of thermal conductivity detectors (TCD).

A graphene-based Pirani pressure sensor has the advantage that it can be made smaller than current implementations. A smaller value for the bridge width w results in an inversely quadratic increase of the ohmic heat generation  $\delta$ , according to Equation 2.9. The increase of  $\delta$  in turn decreases the pressure dependent heat loss through the gas  $\epsilon(p)$ , according to Equation 2.8. The combination of increasing  $\delta$  and decreasing  $\epsilon(p)$  and  $\epsilon$  results in a strong increase of the pressure dependent average temperature rise of the conductive bridge  $\epsilon(p)$ , according to Equation 2.7. This results in an increase of the pressure dependent resistance  $\epsilon(p)$ , according to Equation 2.6. Therefore, decreased  $\epsilon(p)$  and  $\epsilon(p)$  result in a stronger pressure dependency of  $\epsilon(p)$ , which implies that graphene-based Pirani pressure sensors allow a higher sensitivity compared to existing implementations. Furthermore, the low thickness of graphene increases  $\epsilon(p)$  inversely proportional as well.

#### **2.2.** Graphene Growth and Characterization

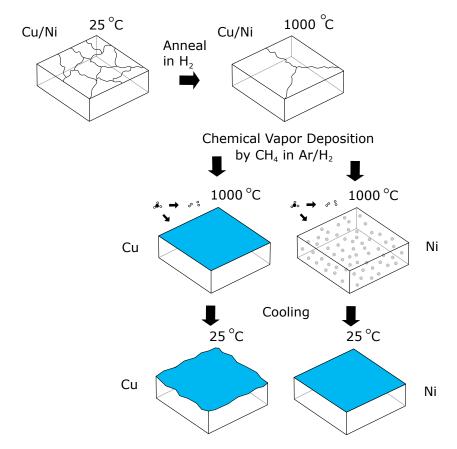

In recent years the production of high quality graphene films has been achieved. This includes the synthesis of both mono- and multi-layer graphene. There are various methods to synthesize graphene [2, 3], which include mechanical exfoliation of graphite [1], annealing of silicon carbide (SiC) [22], unzipping of carbon nanotubes (CNT) [23] and CVD growth on transition metals [24, 25]. Mechanical exfoliation, annealing of SiC and the unzipping of CNT can not be integrated with a standard electronics fabrication process without a wafer-to-wafer transfer step. This renders these methods insufficient with regard to the main research question. However, the CVD growth on transition metals does not require a (wafer-to-wafer) transfer step and is furthermore an efficient and inexpensive method for graphene synthesis [26]. Commonly used transition metals are copper (Cu) foils [24] and nickel (Ni) foils [25]. This method of graphene synthesis is also used in the proposed graphene-based Pirani sensor fabrication in Section 2.1.3, but with the use of Mo as catalyst.

Figure 2.6: CVD growth process of graphene on transition metals Cu and Ni. The thin films are first annealed followed by the CVD step with methane. The wafers are cooled down to room temperature. The graphene layer is depicted in blue.

#### **2.2.1.** Selective CVD of Graphene on Molybdenum

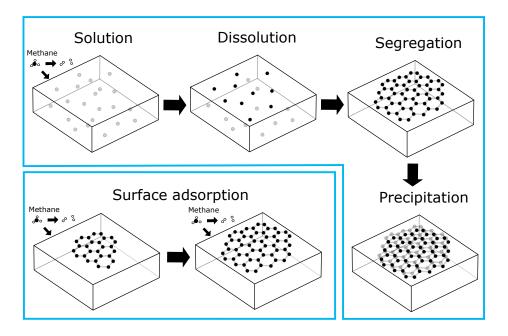

The CVD growth process consists of several steps, for which the details differ between the different transition metals. Figure 2.6 shows the CVD growth process steps and differences between the commonly used transition metals Cu and Ni. The process starts with a thin film of poly crystalline Cu or Ni on top of the Si bulk at room temperature. Generally there is a  $SiO_2$  layer between the metal thin-film and Si bulk to prevent diffusion of the metal atoms into the Si bulk. The poly crystalline Cu or Ni thin films are first annealed at at 900 °C to 1000 °C to increase the thin film grain size and reduce the metal oxide to metallic state, which allows for higher quality graphene films as the grain boundaries result in defects in the graphene formation. Secondly, the CVD growth step is performed at high temperature with methane, that acts as the carbon source. Finally, the wafers are cooled down to room temperature. Note that the actual growth process is different for Cu and Ni due to different carbon solubilities.

The thin film transition metals are exposed to methane during the CVD growth step. The methane molecules decompose in carbon and hydrogen at the surface of the transition metals, which function as a catalyst that lowers the energy barrier for this decomposition. The carbon atoms then dissolve in the Ni thin film while they adsorb to the Cu surface, due to the difference in carbon solubility. This solubility is low for Cu, while it is high enough for carbon atoms to diffuse in Ni. The difference in physical process is illustrated in Figure 2.7. Before cooling, graphene has already formed on the Cu thin film while this is not the case for Ni. The different thermal expansion coefficients of graphene and Cu result in wrinkles in the formed graphene film when the wafer is cooled. These wrinkles can form across grain boundaries which indicates that the graphene film is continuous. In the case of Ni, the carbon atoms diffuse in the thin film during the CVD growth and then segregate to the Ni thin film surface during cooling, which is due to the carbon solubility decreasing as temperature decreases. Depending on the amount of carbon atoms in the Ni thin film, the amount of layers of graphene formed on the surface is different. The lattice of Ni(111) is similar to that of the hexagonal lattice of graphene, which allows for excellent graphene growth without wrinkles on Ni(111). The graphene film uniformity is limited by the Ni thin film grain size as the diffusion rates are different at the grain edges [27]. Multi-layers on Ni therefore tend to be non-uniform.

Figure 2.7: Graphene formation by either the surface adsorption or dissolution and segregation process [3].

The transition metals Ni and Cu are difficult to work with in terms of patterning, as the growth temperature is close to the melting temperature of these metals. Furthermore, these Cu poses contamination issues in the front-end fabrication. To use the grown graphene on Ni or Cu films in applications using standard CMOS processing, a wafer-to-wafer transfer step is required [28]. This implies that these transition metals can not be used in this research. Fortunately, a transfer free CVD process developed by our group that uses Mo as transition metal exists [29] after the feasibility for CNT growth on Mo was already reported [30]. The CVD process for Mo is similar to that of Ni, but the carbon solubility of Mo is lower and it has a larger range of optimal cooling rates which additionally allows for a more controllable and uniform multi-layer graphene growth [28, 31–33]. Furthermore, the methane flow rate and

growth time do not affect the graphene formation on Mo, with exception of the amount of multi-layers, while this may affect graphene growth on Ni. The advantages of Mo over Cu and Ni is that it is front-end compatible with the fabrication process, it has a much higher melting temperature than the graphene growth step and it forms uniform multi-layer graphene.

#### 2.2.2. Graphene Characterization Technique

There are various different tools that can be used to characterize aspects of the fabricated graphene [2]. Some effective methods are optical contrast [34], scanning electron microscopy (SEM) [35], electron diffraction [36] and Raman spectroscopy [37]. Even individual atoms in the graphene film can be observed by using High-Angle Annular Dark-Field Scanning Transmission Electron Microscopy, which visualizes single defects in the graphene lattice [38]. The method used in this research project is Raman spectroscopy, as these the most widely used method and equipment is available at the university faculty. Additionally, SEM is used for visualization and evaluation of various samples at different stages of the fabrication process.

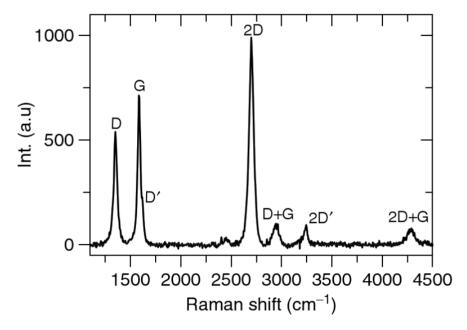

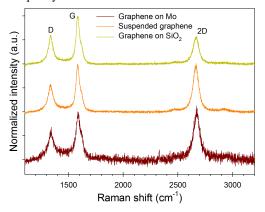

Raman spectroscopy is a measurement technique that measures the frequency shift of reflective light by exposing the sample to a laser with a known wavelength. This technique is primarily used to characterize the amount of layers and defects in the graphene film, but more properties can be probed. It is a powerful tool when comparing slightly different graphene synthesis processes [2, 37, 39]. The graphene Raman spectrum consists of various peaks which are depicted in Figure 2.8. The intensity is in is arbitrary units (a.u.) as this is related to the counts of a detector that will vary for different setups and over time. To compare Raman spectra, the ratio between peaks is therefore used. Note that the location of the peaks depends on the laser wavelength used to probe the graphene film.

The three most important bands are the G-, D- and 2D-peaks. The G-peak is located at approximately 1580 cm<sup>-1</sup> and it is induced by in-plane vibrations of the sp² hybridized carbon atoms. The intensity increases linearly for an increasing amount of layers when compared to the other bands [40]. The D-peak is located at approximately 1350 cm<sup>-1</sup> and it is induced by all kinds of defects in the graphene film. This includes the amount of layers [2] and wrinkles [28]. Its shape, width and position change for increasing amount of layers in the graphene film [41]. The D'-peak is induced by similar processes as the D-peak and becomes observable when the D-peak is of significant intensity which can cause an apparent shift in the G-peak. The 2D-peak is located at approximately 2700 cm<sup>-1</sup> and is the overtone of the D-peak as result of the double resonance Raman scattering process and appears even without defects in the graphene film [37]. Note that this peak will therefore be present even if the D-peak is absent. This peak is directly dependent on the amount of layers in the graphene film and is hence the most reliable peak when determining the amount of layers [41]. However, this dependency is only strong for few-layer graphene. For a mono-layer graphene film, the full width at half maximum (FWHM) is approximately 25 cm<sup>-1</sup> [2].

Figure 2.8: Example of a Raman spectrum of a mono-layer graphene film probed with a 514.5 nm laser [2].

2.3. BICMOS Process 13

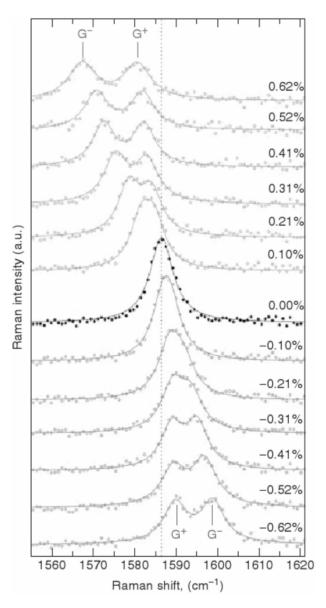

The G-peak is shifted due to induced strain [42], orientation [43] or other environmental effects. The strain and orientation affect the phonon behavior in the graphene film, which causes the shift of the peak. Moreover, significant amount of induced strain splits the G-peak in two peaks [2]. This phenomenon is depicted in appendix Figure B.1. The 2D-peak is similarly dependent on induced strain.

#### 2.3. BICMOS Process

The BICMOS process of the Else Kooi Laboratory (EKL) at the Delft University of Technology is used primarily for educational purposes [44]. It can be used to fabricate both bipolar and CMOS devices, while it only requires five masks. This research work only focuses on CMOS electronics as these are most popular nowadays. The simplicity of the BICMOS process makes it a suitable process to experiment with and is therefore adopted in this work. Unfortunately, no full design kit is available for this process nor has it been properly characterized in circuit design. The work in the process of Zahra Kolahdouz Esfahani [45] is used as a starting point in this research work.

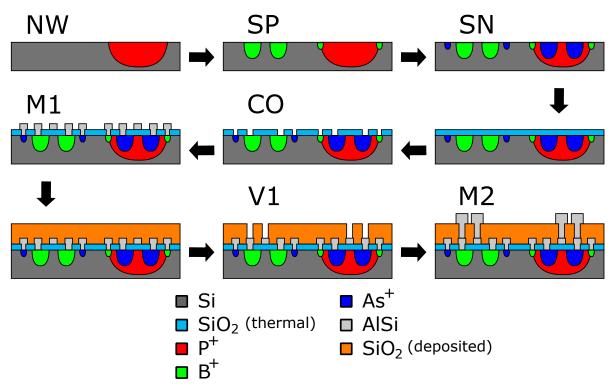

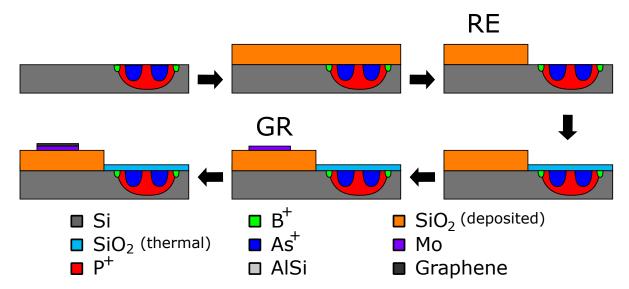

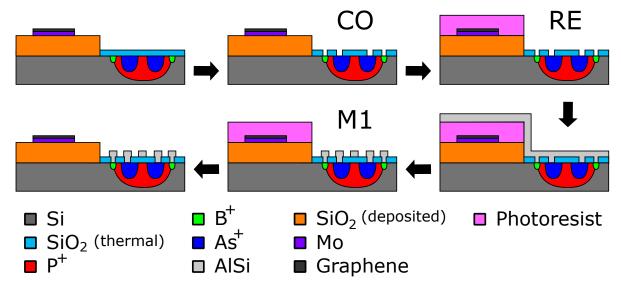

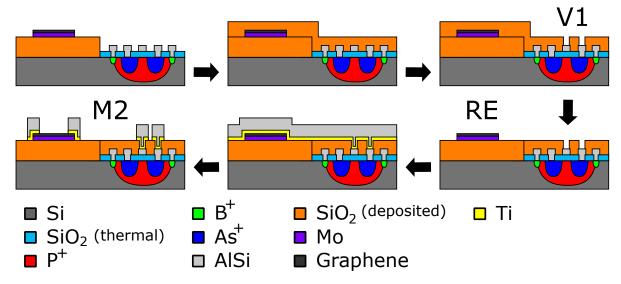

#### 2.3.1. BICMOS Core Fabrication Steps

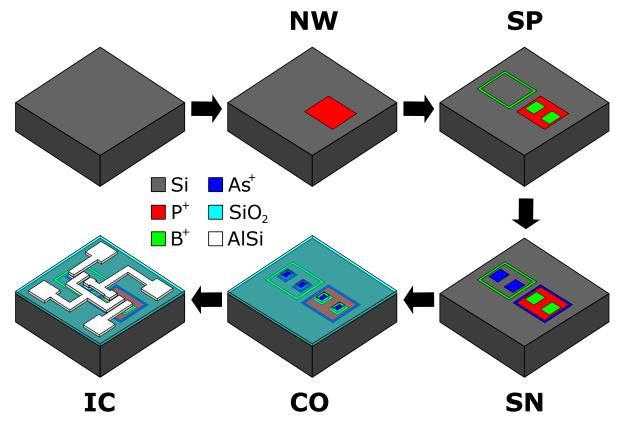

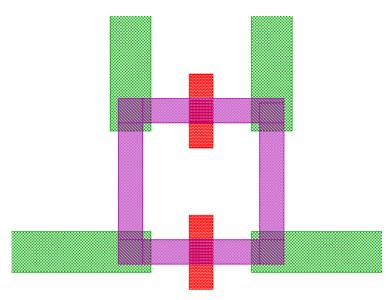

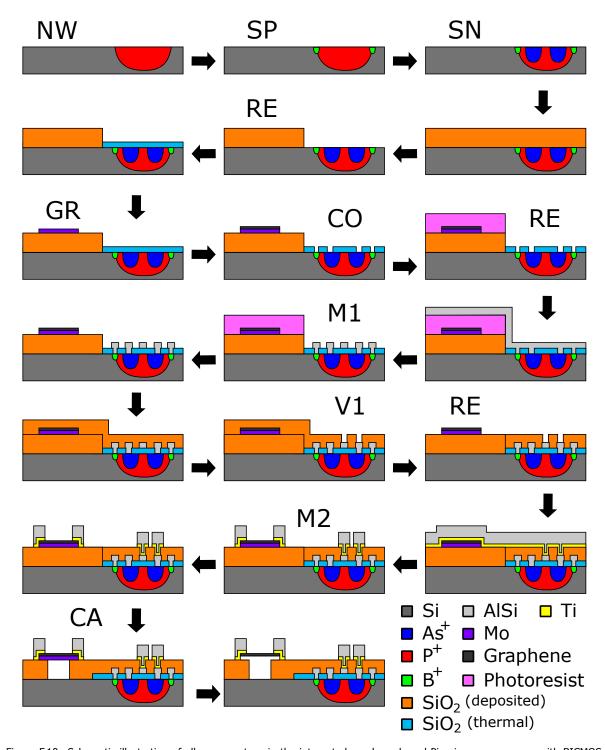

The five core fabrication steps of the BICMOS process are schematically illustrated in Figure 2.9, which are the N-well (NW), shallow p-type (SP), shallow n-type (SN), contact openings (CO) and metal interconnect (IC). The process starts with bare p-type silicon with a highly uniform background dopant concentration epi-layer. The NW step then implements the n-type doped N-well that is required for a PMOS device. Phosphorus ions (P+) are implanted and diffused deep in the silicon bulk to form a well. This is followed by the SP step that implements the highly doped shallow p-type regions. These consist of source and drain of the PMOS and the guard ring of the NMOS and are implemented by boron ions (B+) implantation. The third step is the SN step that complements the doped regions by arsenic (As+) implantation to form the source and drain of the NMOS and the guard ring of the PMOS. In the fourth step the gate material is formed by wet thermal oxidation and contacts to the doped regions in the silicon bulk are etched through the  $SiO_2$ . The final step implements the metal interconnect which is often 99% aluminum and 1% silicon (AlSi) as this material does not diffuse in the Si bulk and has a low contact resistance. Each core processing step requires a mask to define the respective regions.

Figure 2.9: The five core fabrication steps of the BICMOS process, depicting the implementation of a single inverter. The legend shows the corresponding materials of each color used in the schematic illustration.

The implanted dopant atoms are activated by annealing the wafer at high temperature. This activation is the process of placing the dopant atoms in the damaged silicon lattice. A long anneal is performed after the NW step to activate and diffuse the dopant atoms in the lattice. Another anneal is performed during the wet thermal oxidation of the gate material, which activates the SN and SP regions. Contrary to the illustration in Figure 2.9, the doped regions have no color difference compared to the silicon bulk. Prior to the ion implantation a dirt barrier on the wafer is created by thermal oxidation. This layer captures dirt particles that may hit the wafer during the ion implantation and act as a scatter layer for the implantation ions to prevent channeling effects.

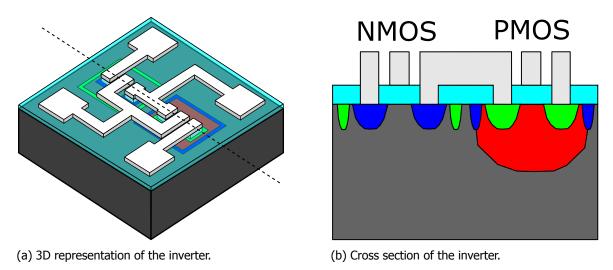

A cross section of the single inverter is schematically illustrated in Figure 2.10. Note that the N-well is much deeper than the SN and SP regions. Furthermore, in the source and drain of the PMOS are both P<sup>+</sup> and B<sup>+</sup> present although the concentration of the latter is several order of magnitude higher. The guard rings are left unconnected in this illustration in favor of simplicity. In reality, these need to be connected and correctly biased to be effective. It is common practice to connect the NMOS and PMOS guard ring to ground and supply voltage respectively.

Figure 2.10: Schematic illustration of the inverter with in a) the 3D representation and in b) the cross section at the dotted line. The used colors match those used in Figure 2.9.

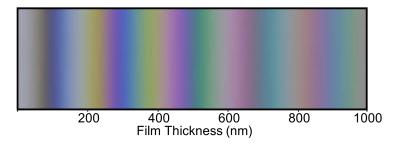

There are oxide formation or depostion methods available at EKL of which two are used in this work. The first is the mentioned wet thermal oxidation used for the gate material implementation. This method grows highly uniform  $SiO_2$  on the silicon bulk at a high temperature of approximately 1100 °C by providing a water vapor flow in the furnace. At this temperature the water molecules diffuse through the  $SiO_2$  and react with the silicon, resulting in  $SiO_2$  growth on both sides of the wafer by consuming silicon. The growth rate is predicted with the Deal-Grove model [46]. The growth rate is different for the doped regions by approximately 2x and 1.5x for the SN and SP regions respectively. Since the  $SiO_2$  color is highly dependent on the layer thickness, there is a distinct color difference between the SN, SP and field oxide. This dependency is depicted in Figure 2.11, resulting in metallic blue, light blue and yellow for the field, SP and SN oxide respectively in this process. The second method is tetraethylorthosilicate (TEOS) plasma-enhanced chemical vapor deposition (PECVD) at approximately 350 °C. The TEOS plasma reacts at the exposed wafer surface and forms  $SiO_2$  directly, without consuming silicon. It can therefore be deposited on other materials than silicon and is a faster process although the  $SiO_2$  is less uniform compared to wet thermal oxidation.

Figure 2.11: Color dependency on thickness of a thermal  ${\rm SiO}_2$  layer [47].

2.3. BICMOS Process 15

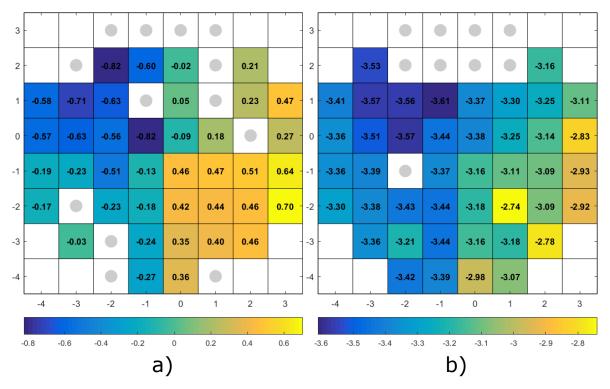

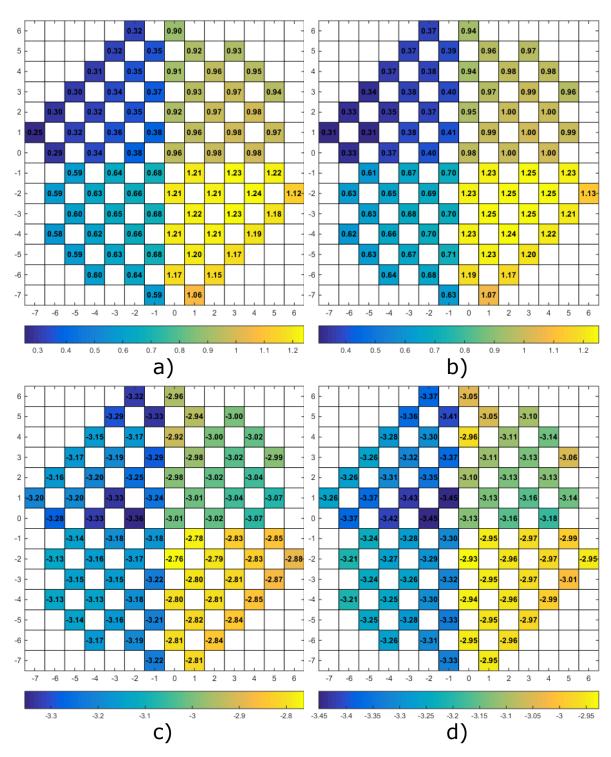

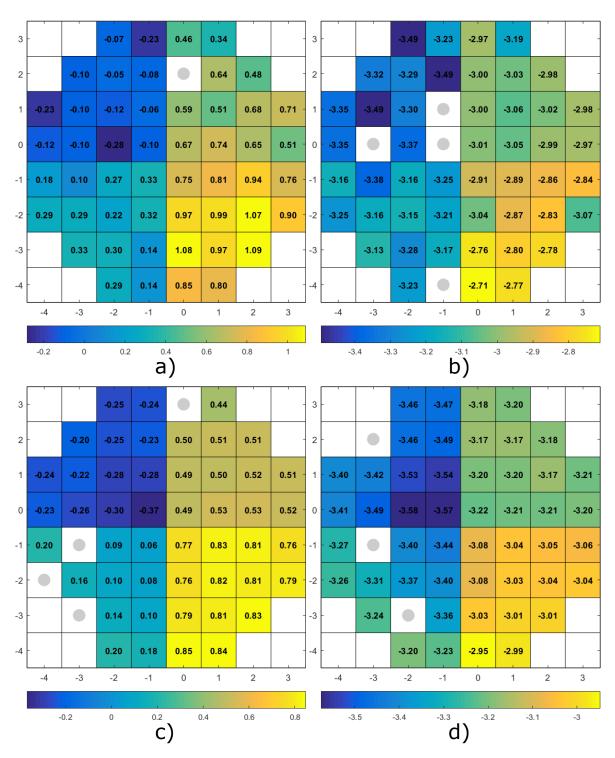

#### 2.3.2. Threshold Voltage Adjustment

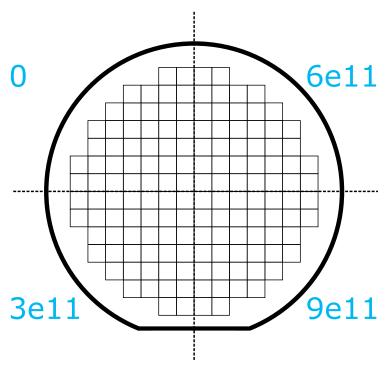

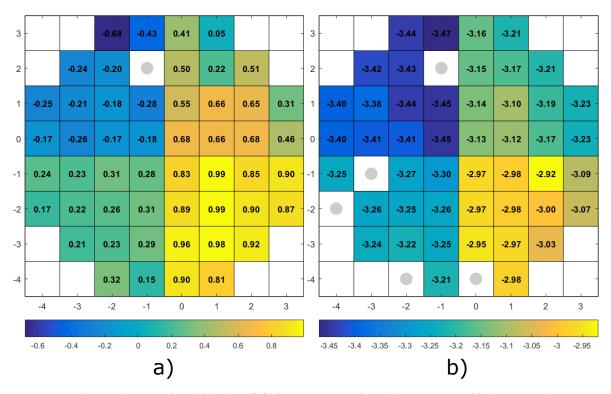

The threshold voltage of the NMOS and PMOS devices is influenced by adding a blanked of B<sup>+</sup> after the SN step and before the gate oxidation step. In this educational process, it is common practice to vary the blanket dose in each wafer quadrant to pursuit symmetry in threshold voltage of the NMOS and PMOS. This concept with corresponding adjustment doses is illustrated in Figure 2.12. A higher voltage adjustment dose increases the threshold voltage of all devices as it increases the p-type concentration in the channels. The threshold voltage is an important characteristic of CMOS devices and information on it is required during the design stage. The mathematical model for the threshold voltage of CMOS devices is given below [48].

Figure 2.12: Threshold voltage adjustment doses of  $B^+$  implantation for each wafer quadrant. Note that the unit of the doses is atoms·cm $^{-2}$ .

The threshold voltage of an NMOS device is calculated by Equation 2.14 where  $\phi_{ms}$  is the metal-semiconductor work function difference,  $\phi_{fp}$  the fixed work function of a p-type channel,  $|Q'_{SD}(max)|$  the magnitude of the maximum space charge density per unit area of the depletion region,  $Q'_{SS}$  the oxide charge,  $t_{ox}$  the oxide thickness and  $\epsilon_{ox}$  the permittivity of SiO<sub>2</sub>, which equals  $3.45 \cdot 10^{-13}$ . The the metal-semiconductor work function difference  $\phi_{ms}$  is estimated using the channel doping and gate material in literature [48].

$$V_{Tn} = (|Q'_{SD}(max)| - Q'_{SS}) \left(\frac{t_{ox}}{\epsilon_{ox}}\right) + \phi_{ms} + 2\phi_{fp}$$

(2.14)

The fixed work function of a p-type channel  $\phi_{fp}$  is calculated by Equation 2.15 where  $N_a$  is the acceptor doping concentration,  $n_i$  the intrinsic carrier concentration and  $V_t$  the thermal voltage. Constants  $n_i$  and  $V_t$  equal 1.45 ·  $10^{10}$  cm<sup>-3</sup> and  $2.26 \cdot 10^{-2}$  at 300 K respectively.

$$\phi_{fp} = V_t \ln\left(\frac{N_a}{n_i}\right) \tag{2.15}$$

The magnitude of the maximum space charge density per unit area of the depletion region  $|Q'_{SD}(max)|$  is calculated by Equation 2.16 where  $x_{dT}$  is the maximum space charge width for a given doping concentration and q the electron charge, which equals  $1.60 \cdot 10^{-19}$  C.

$$|Q'_{SD}(max)| = qN_a x_{dT} \tag{2.16}$$

The maximum space charge width for a given doping concentration  $x_{dT}$  is calculated by Equation 2.17 where  $\epsilon_s$  is the permittivity of Si, which equals  $1.04 \cdot 10^{-12}$ .

$$x_{dT} = \sqrt{\frac{4\epsilon_s \phi_{fp}}{q N_a}} \tag{2.17}$$

Similarly, the threshold voltage of a PMOS device calculated by Equation 2.18, where  $\phi_{fn}$  is the fixed work function of an n-type channel that is calculated using Equation 2.15 by substituting  $N_a$  by  $N_d$  that represents the donor doping concentration. Furthermore,  $x_{dT}$  is calculated by Equation 2.16 using the same substitution.

$$V_{Tp} = (-|Q'_{SD}(max)| - Q'_{SS}) \left(\frac{t_{ox}}{\epsilon_{ox}}\right) + \phi_{ms} - 2\phi_{fn}$$

(2.18)

Note that there are still three undetermined parameters in the model that are determined by the process, when considering a fixed gate material. These are the density of doped carriers  $N_a$  or  $N_d$  in [cm<sup>-3</sup>], the gate material thickness  $t_{ox}$  in [cm] and the fixed charge for surface states  $Q_{SS}'$  in [C·cm<sup>-2</sup>].

#### 2.4. Conclusions

The proposed Pirani sensor fabrication method does not require a wafer-to-wafer transfer step and will be used to experimentally integrate in the BICMOS process. Furthermore, it offers the ability of tuning the gap depth which determines the operating range. Graphene-based Pirani devices can be smaller than current implementations due the high area-to-mass ratio. An analytical model for the Pirani pressure sensor is defined and its parameters are grouped of which most are to be determined later. The graphene is implemented through CVD on Mo as this is compatible with the front-end fabrication and can be patterned before graphene growth. The educational BICMOS process is a simple five step process and is therefore used in this work. An analytical model for the device threshold voltages is defined and three parameters are pointed out as to be determined by the fabrication process.

# Graphene-Based Pirani Pressure Sensor Characterization

This chapter investigates the properties of a Pirani pressure sensor. Two batches of devices are fabricated and released. The pressure dependency of the resistance is measured in a pressure controlled experimental setup. All fabricated devices have an etched cavity depth of 0.6  $\mu$ m and multi-layer graphene bridge thickness of ~ 7 nm, which are two of the geometry parameters. Equation 2.5 results in an operational pressure range of approximately  $1.5 \cdot 10^1$  mbar to  $1.5 \cdot 10^3$  mbar. Furthermore, the other geometry parameters and design aspects are chosen based on the measurement results. This is followed by the determination of the bridge material parameters from measurements. Finally, the chapter is concluded by listing the important findings.

#### 3.1. First Batch Graphene-Based Pirani Sensor Results

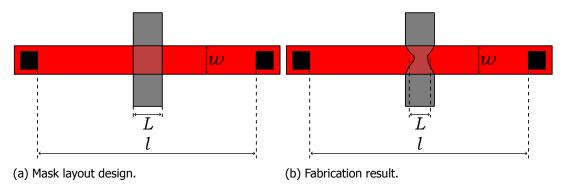

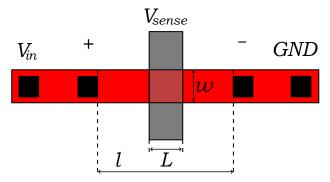

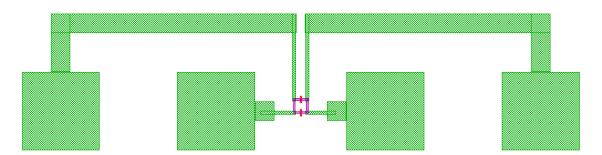

The Pirani sensors of the first batch are fabricated according to the mask layout design that is schematically illustrated in Figure 3.1a. The red rectangle marks the graphene film, the grey rectangle the window used to etch the cavity and the black squares the metal contacts to the metal IC layer. Note that no IC is illustrated apart from the contacting points in favor of simplicity. Furthermore, the figure depicts the total graphene film length l, conductive bridge length l and width l and wi

Figure 3.1: Top view of the Pirani sensor layout of the first batch with in (a) the used mask layout design and in (b) the fabrication result according to this mask layout design. Red marks the graphene, grey the cavity and black the metal.

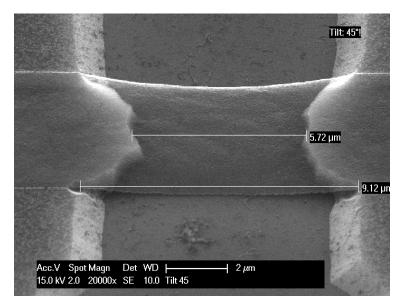

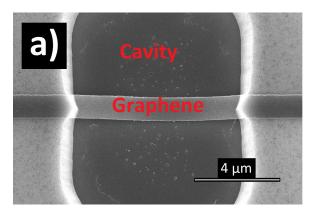

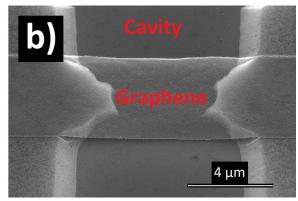

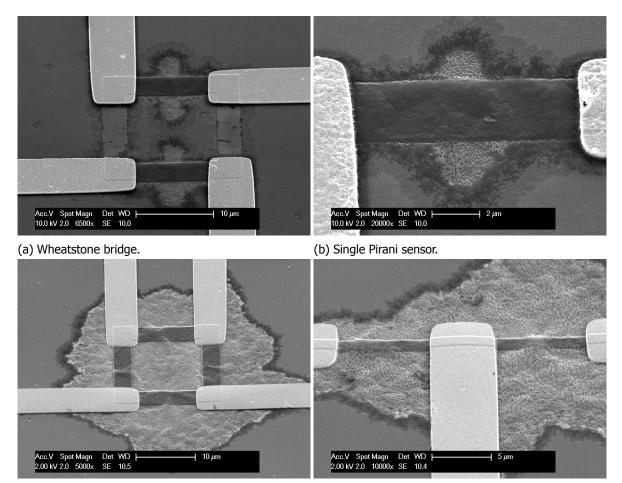

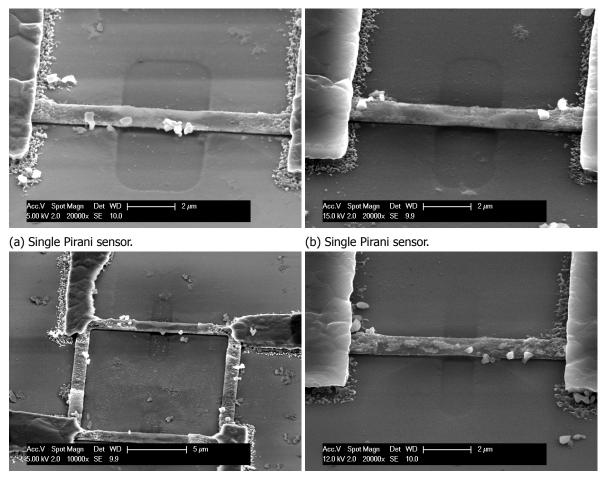

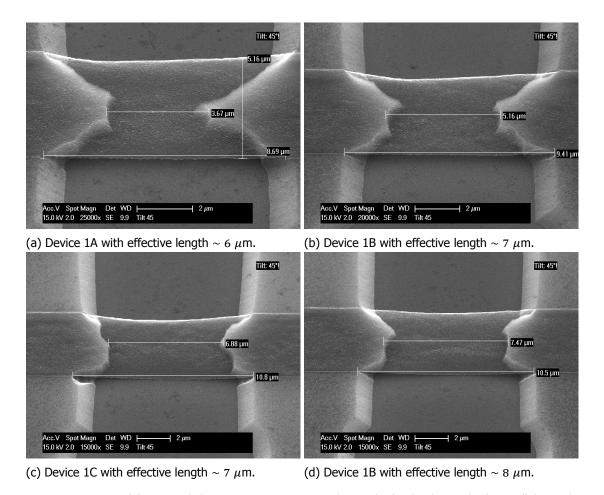

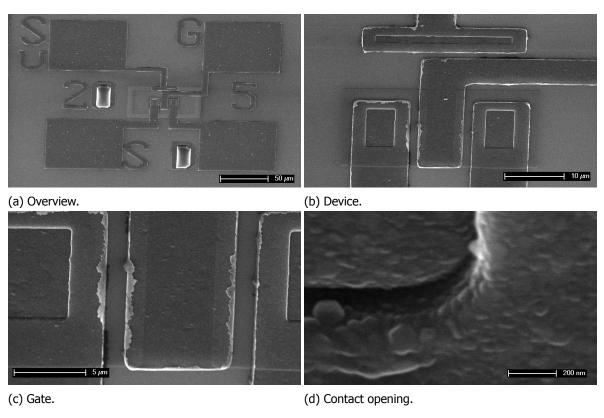

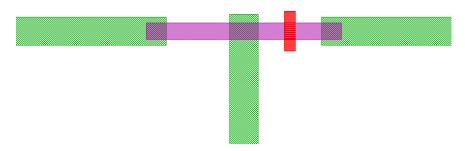

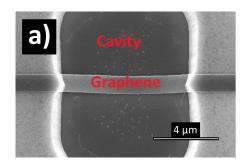

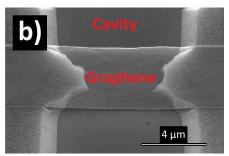

The SEM image in Figure 3.2 depicts the typical fabrication result of the first batch. Two dies were released in the first batch, of which a complete set of suspended Pirani sensor SEM images is listed in appendix Figure C.1 and Figure C.2. Four and six suspended Pirani sensors were observed on the first and second die respectively. The typical aspect ratio is  $\sim 1.4$  and the graphene bridge typically sags towards the substrate, causing the effective gap depth to decrease.

Figure 3.2: SEM image of the typical fabrication result of a Pirani pressure sensor in the first batch at a tilt of  $45^{\circ}$ . It has a width of 5  $\mu$ m and effective length of  $\sim$  7  $\mu$ m.

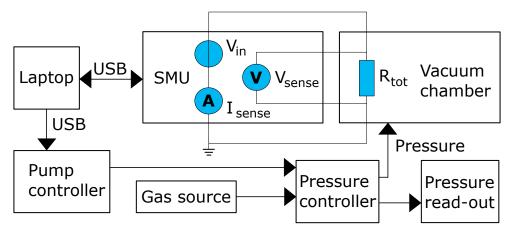

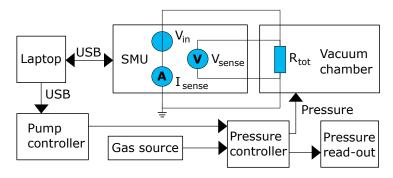

The pressure dependency measurement setup is schematically illustrated in Figure 3.3 and is capable of automated measurements. A *Matlab* script running on a laptop communicates through USB with the source-and-measurement unit (SMU) and pump controller. The SMU is capable of performing both 2- and 4-wire measurements. Note that in the first batch, only 2-wire measurements are possible due to its layout design. The pump controller is a controlled voltage source that controls the pressure controller with an analog signal. The pressure controller regulates the pressure in the vacuum chamber using a gas source and is read out by a multimeter. The gas source used is nitrogen  $(N_2)$ , whose properties are similar to dry air. An upward and downward pressure sweep is performed to monitor drift and hysteresis of the resistance. Neither is observed in the reported measurement results.

Figure 3.3: Schematic illustration of the automated pressure dependency measurement setup. A Keysight B2901A SMU, Rigol DP832A voltage source pump controller, Proportionair PA2254 dual-valve pressure controller and Keithey 199 pump read-out are used in the setup.

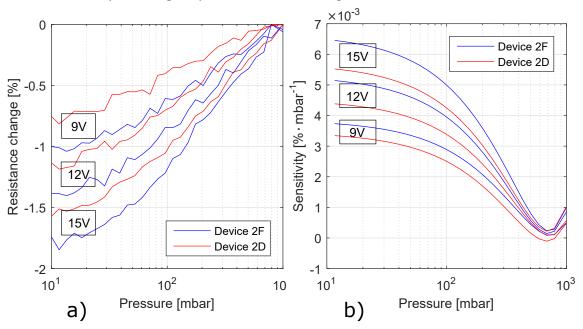

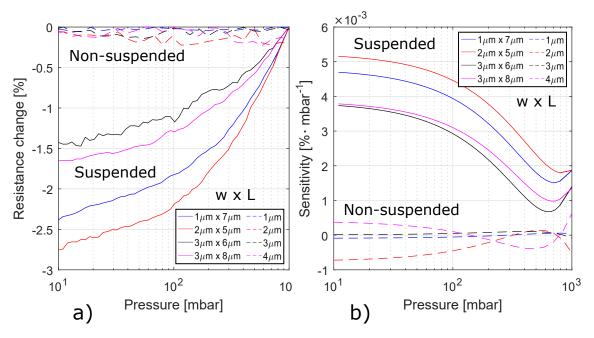

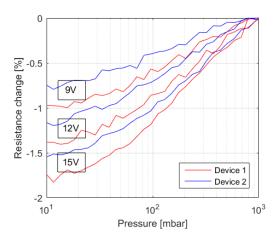

The results of the pressure dependency of the conductive bridge resistance of the first batch are depicted in Figure 3.4a. The measured pressure range corresponds well with the predicted operating range of  $1.5 \cdot 10^1$  mbar to  $1.5 \cdot 10^3$  mbar. Unfortunately, just two devices are found to operate, which are both on the second die and is likely due to wire bonding issues. The resistance change is defined as the ratio in Equation 3.1 where R is the measured resistance dataset and  $R_{max}$  the maximum value in that dataset. There is a definite pressure dependency where magnitude is dependent on the bias voltage, which makes this batch world's first graphene-based Pirani pressure sensors. A larger bias voltage implies a larger current I, which results in more ohmic heat generation. The largest maximum resistance change is 2.8% observed on device 2F for a bias voltage of 9 V with maximum resistance change of 0.8% at 0.9 mW observed on device 2D. The sheet resistance is determined in Section 3.4.

Resistance change =

$$\frac{R}{R_{max}} * 100$$

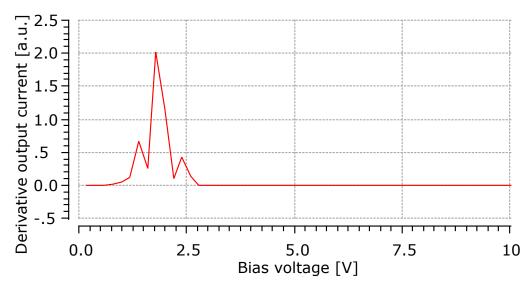

(3.1)

The sensitivity to pressure is depicted in Figure 3.4b, which is derived by fitting a third order polynomial to the measurement data and calculating the derivative with respect to the pressure. The sensitivity maximum is not included in the measured pressure range and appears to be at lower pressure. The sagging of the conductive bridges gives a smaller cavity depth, which results in a higher pressure range according to Equation 2.5. The shift towards a lower pressure range suggests that a dominant factor other than cavity depth is left out. The gentle increase of sensitivity for the highest pressures is due to a fitting artifact.

Figure 3.4: Measurement results of the pressure dependency of the Pirani sensor conductive bridge resistance in a) and the found device sensitivity in b). Three different bias voltages are applied and two devices are found to operate. The sensitivity is derived by the derivative of a third order polynomial fit to the data. The device labels correspond with the listing in appendix Figure C.2.

## 3.2. Second Batch Graphene-Based Pirani Sensor Results

The second batch of Pirani sensors is fabricated according to the mask layout design that is schematically illustrated in Figure 3.5. The incomplete under etching is still inevitable and the used colors match the layout design given before. This design opens the possibility of 4-wire measurements as it has two extra contacts. The force pair is  $V_{in}$  and  $C_{in}$  and the sense pair is marked by  $V_{sense}$ . Note that the total length  $C_{in}$  is reduced significantly, which reduces the impact of the non-suspended graphene film caused by ohmic heating.

Figure 3.5: Top view of the Pirani sensor layout of the second batch. Red marks the graphene, grey the cavity and black the metal

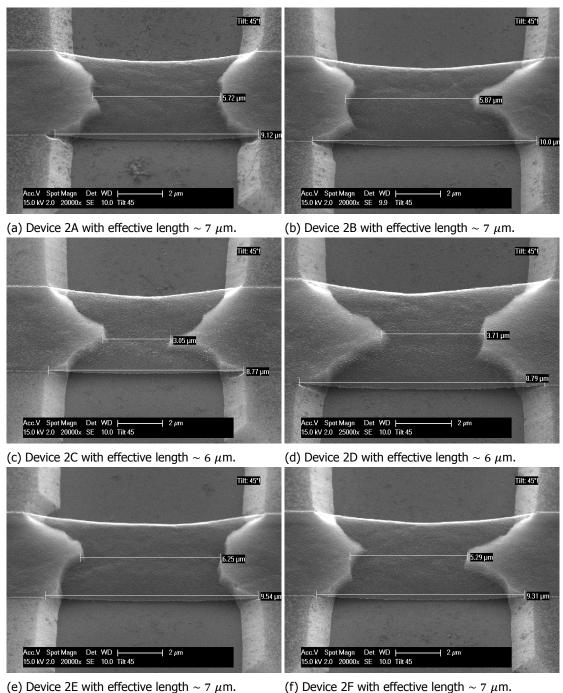

The SEM images in Figure 3.6 depicts the fabrication results of different aspect ratios in the second batch. One die was released in the first batch with device aspect ratios up to 8. On this die, the yield of suspended Pirani sensors is  $\sim 75$  %. The SEM images reveal that devices with a longer bridge length tend to contact the Si substrate.

Figure 3.6: SEM images of suspended Pirani sensors in the second batch with a) high aspect ratio (width of 1  $\mu$ m and length of  $\sim 8\mu$ m) and b) with low aspect ratio (width of 5  $\mu$ m and length of  $\sim 6\mu$ m). Images taken under a 45° angle.

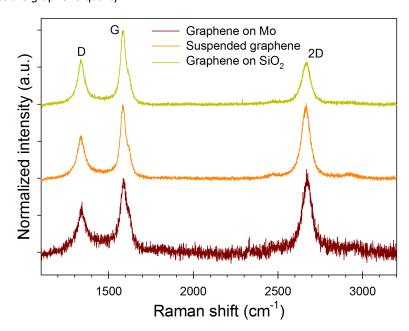

Additionally, Raman spectroscopy is performed on the devices in the second batch during different stages in the process. This includes on Mo before release and after release on  $SiO_2$  and when suspended. The results are given in Figure 3.7. The D/G ratios are similar in all monitored process stages, from which is concluded that the process steps do not affect the graphene quality.

Figure 3.7: Raman spectroscopy of graphene strips in the second batch at different stages of the process. This includes before release on Mo, after release on SiO<sub>2</sub> and suspended. Identical D/G ratios indicate no change in defect density.

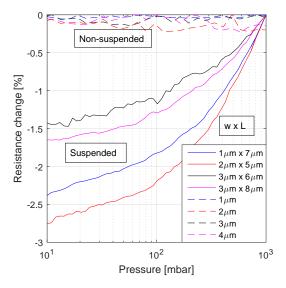

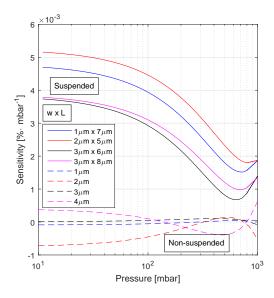

The results of the pressure dependency of the conductive bridge resistance of the second batch are depicted in Figure 3.8a. At least five devices with different geometries are found to be operating. The reason for leaving out the results of other devices is due to drift in the measurement results, which causes the devices to give irreproducible results. Additionally, the pressure dependency of non-suspended graphene strips is measured and depicted in Figure 3.8a. It is concluded that non-suspended strips show no pressure dependent resistance while the suspended strips do. All measurements were done at a 7.5 V bias.

The sensitivity to pressure is depicted in Figure 3.8b, which is derived by fitting a third order polynomial to the measurement data and calculating the derivative with respect to the pressure. The sensitivity maximum is again not included in the measured pressure range and appears to be at lower pressure. The gentle increase of sensitivity for the highest pressures is due to a fitting artifact. Equation 2.9 in the analytical model of the Pirani pressure sensor states that the ohmic heat generation increases inversely quadratic for decreasing bridge width, which in turn increases the maximum resistance change. Figure 3.8b complies with this statement as the narrower bridges generally have a larger sensitivity. Although the 2  $\mu$ m narrow bridge has a larger sensitivity than the 1  $\mu$ m narrow bridge, but this could be related to effects like the sagging. Equation 2.6 states that the pressure dependent temperature rise is dependent on the bridge length, but no quantitative relation of the bridge length is derived from Figure 3.8b. The shortest bridge has the highest sensitivity in the measurement results. For equal sensitivity a decreased geometry results in a decreased power consumption.

Figure 3.8: Measurement results of the pressure dependency of the Pirani sensor conductive bridge resistance in a) and the found device sensitivity in b). The devices were biased at 7.5 V and five devices were found to be operational. The pressure dependency of non-suspended graphene strips is included as reference. The sensitivity is derived by the derivative of a third order polynomial fit to the data.

#### 3.3. Pirani Pressure Sensor Design Choices

The gap depth and bridge thickness were already mentioned and are kept the same in favor of future comparisons. Multiple combinations of the bridge width and length are incorporated in the design to better characterize the relation between width, length and sensitivity in the future. The bridge width should be kept as low as possible to increase the sensitivity and is therefore chosen to be 1  $\mu$ m, 2  $\mu$ m and 3  $\mu$ m. The bridge length is kept to a minimum to reduce the observed sagging effects. The cavity width is therefore chosen to be 1  $\mu$ m, 2  $\mu$ m and 3  $\mu$ m. This geometry allows for the miniaturization with a factor of at least 100x compared to state-of-the-art implementations [12–15]. Note that different etch times are required to fully etch the cavities under the bridge, which in turn results in different bridge lengths. This is summed up in Table 3.1 where etch times A, B and C correspond with the time required to fully etch under the corresponding bridge width. These etch times are determined by dividing the oxide layer thickness by the etch rate. To characterize all devices, it is therefore required to release three different dies with each a different etch time.

Furthermore, the metal contacts to the graphene bridge can not be placed directly at the edge of the cavity due to the risk of under etching the metal contact when etching the cavity. The distance was  $\sim 14~\mu m$  and  $\sim 3~\mu m$  in the first batch and second batch respectively. It is chosen that a minimal distance of 3  $\mu m$  is required between cavity edge and metal contact. The total graphene strip length l between metal contacts is also listed in Table 3.1. The non-suspended part of the graphene strip reduces the sensitivity of the device significantly as it is responsible for at least half of the total graphene strip resistance.

Table 3.1: Design geometry parameters with minimum widths and length. The edge time is dependent on the bridge width and is marked with A, B or C.

| Width $w$      | Cavity width | Etch time | Length $L$ | Total length $l$    |

|----------------|--------------|-----------|------------|---------------------|

| $1~\mu{\sf m}$ | $1  \mu$ m   | Α         | 2 μm       | 8 μ <b>m</b>        |

| $1~\mu{\sf m}$ | 2 μ <b>m</b> | Α         | 3 μm       | 9 μ <b>m</b>        |

| $1~\mu{\sf m}$ | 3 μ <b>m</b> | Α         | 4 μm       | $10~\mu \mathrm{m}$ |

| $2~\mu m$      | 1 μ <b>m</b> | В         | 3 μm       | 9 μ <b>m</b>        |

| $2~\mu m$      | 2 μ <b>m</b> | В         | 4 μm       | 10 μm               |

| $2~\mu m$      | 3 μ <b>m</b> | В         | 5 μm       | 11 μm               |

| $3~\mu m$      | $1  \mu$ m   | С         | 4 μm       | 10 μm               |

| $3~\mu m$      | 2 μ <b>m</b> | С         | 5 μm       | 11 μm               |

| $3~\mu m$      | 3 μ <b>m</b> | С         | 6 μm       | 12 μm               |

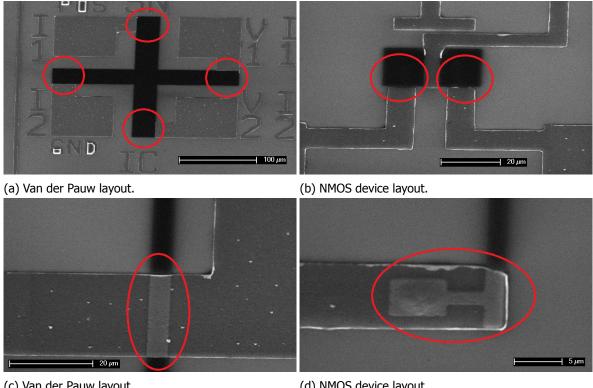

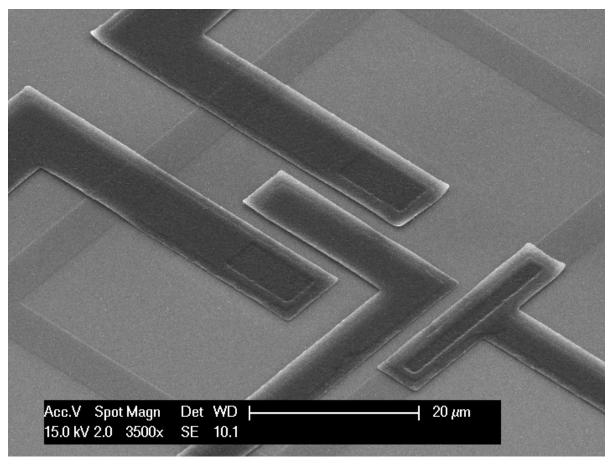

The contact between AlSi and graphene is investigated on a test wafer. The AlSi did not adhere well to the graphene, which results in missing AlSi at large contact areas with graphene. The SEM images in Figure 3.9a and Figure 3.9b show these areas and mark missing AlSi with red circles. Fortunately, the AlSi does adhere to the graphene at smaller contact areas with overlap on two sides of the graphene strip. These areas are depicted in Figure 3.9c and Figure 3.9d.

(c) Van der Pauw layout.

(d) NMOS device layout.

Figure 3.9: SEM images of large contact areas between graphene and AlSi with in (a) a Van der Pauw layout and in (b) a zoomed view of an NMOS layout and small contact areas between graphene and AlSi with overlap on two sides of the graphene strip with in (c) a guard ring crossing and in (d) a contact to an electric linewidth structure. All images are taken on a test wafer at an angle of 45° where graphene is implemented as the SN layer.

All the pressure dependency measurements were performed by forcing a voltage over the Pirani sensor in contrast to the forced current in the analytical model. This is done since a voltage supply is more common as well as to reduce the risk of damaging the devices. The analytical model can not be rewritten analytically for a forced voltage due to the hyperbolic function in Equation 2.7. Therefore, the forced current is to be quantitatively derived from the measured resistance to verify the analytical model.

#### 3.4. Bridge Material Parameter Measurements

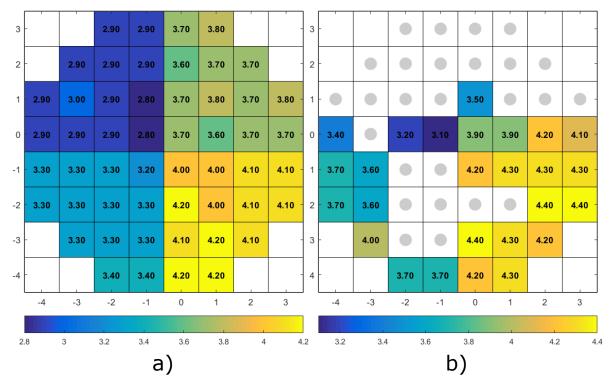

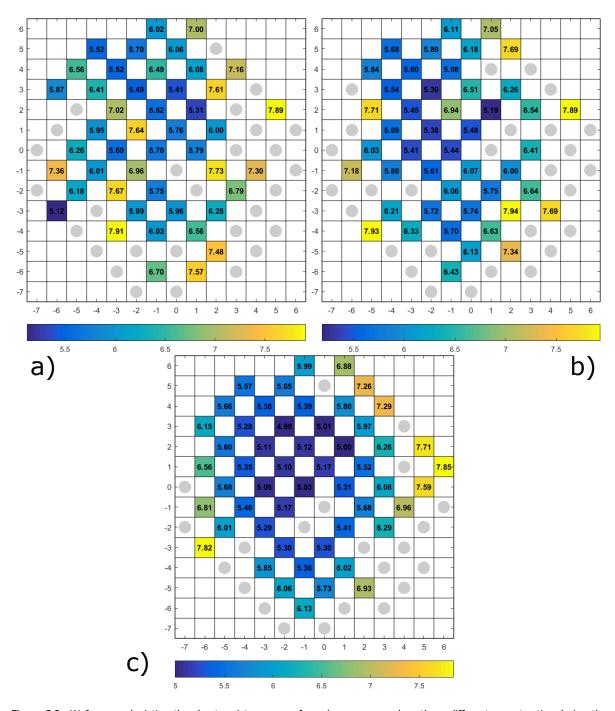

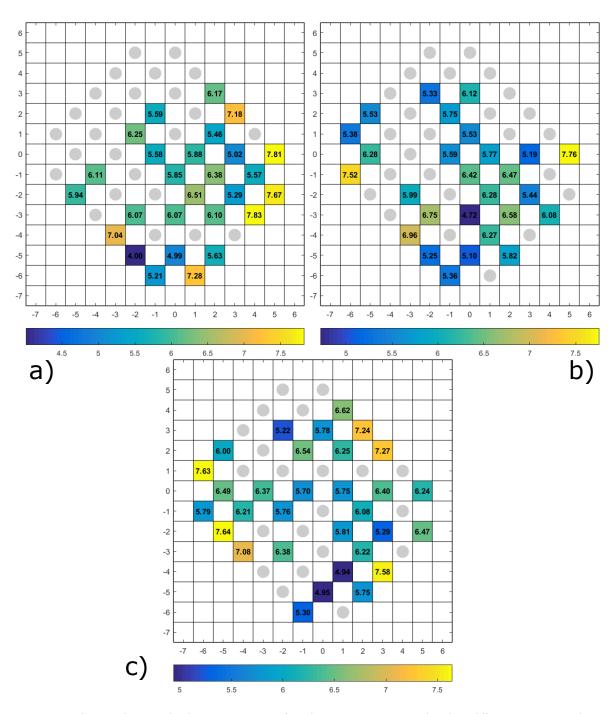

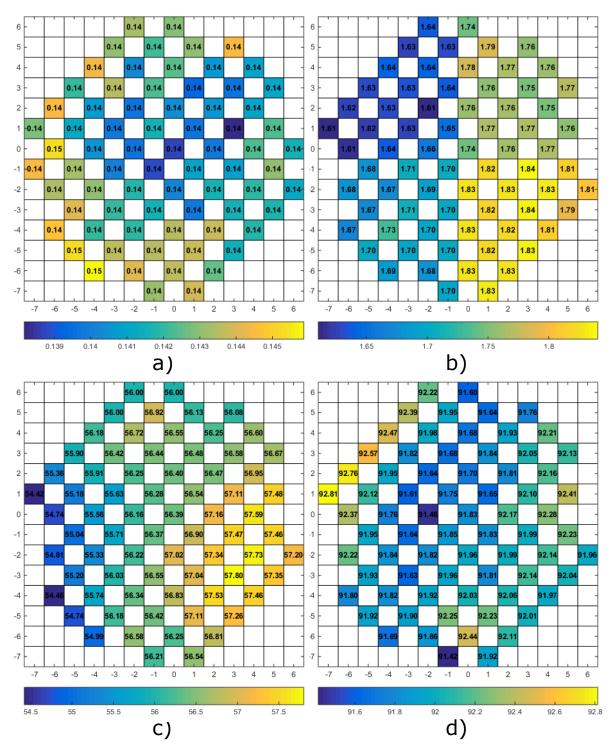

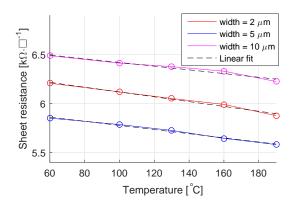

The average sheet resistance  $R_\square$  is determined by measuring the resistance of graphene strips and dividing by the aspect ratio of the strip. This results in 10.6 k $\Omega$  and 0.8 k $\Omega$  for the first and second batch respectively. This large difference of  $\sim$  13x has not been further investigated. It is assumed that it is caused by differences or variations in the fabrication process. It should therefore be checked after fabrication. Although the resistance of the graphene strips in the first and second batch is different, the sensitivity is comparable. However, the power consumption is  $\sim$  0.9mW and  $\sim$  8.5mW in the first and second batch respectively. This is significantly different and implies that the higher sheet resistance strips of the first batch are desirable in applications where power consumption is a constraint, as the power relates to  $I^2R$ . Wafer-scale measurements on three different structures on the mentioned test wafer result in a sheet resistance of 6.2  $\pm$  0.8 k $\Omega$ . The measurement results of each die are depicted in appendix Figure C.3.

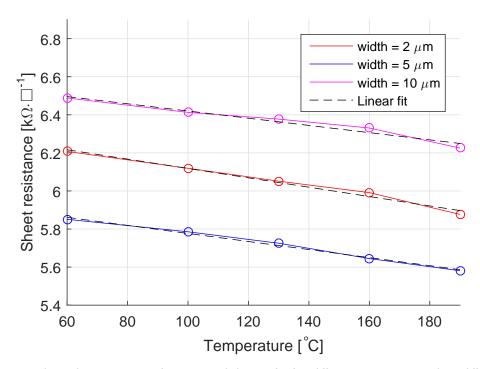

Figure 3.10: Graphene sheet resistance of non-suspended strips for five different temperatures. Three different strips are measured with variable width and length 206  $\mu$ m. The difference between strips is  $\sim$  5 % and is considered due to process variations. A linear fit is included to determine the TCR.

The TCR  $\xi$  of graphene is determined on the aforementioned test wafer devices. The average sheet resistance is measured for five different temperatures and the results are depicted in Figure 3.10. The measurement results of each die and temperature are depicted in appendix Figure C.4-C.8. The devices are measured at low bias to minimize the effect of ohmic heating. The figure includes linear fits of which the largest fit error is 0.5 %. The TCR is therefore concluded to be constant for this temperature range. An average TCR value of  $(-3.6 \cdot 0.5) \cdot 10^{-4} \text{ K}^{-1}$  is found for the graphene strip, which matches values from literature [49].

The direct measurement of the thermal conductivity  $\kappa_b$  is considered out of the scope of this project. Unfortunately, no fit of the analytical model to the data is achieved. A larger data set with different geometries could provide a solution. The value of  $\kappa_b$  is therefore left undetermined for now, but literature suggests a  $\kappa_b$  of 1000 W·m<sup>-1</sup>·K<sup>-1</sup> for multi-layer graphene [49]. The analytical model can not be used to make predictions, due to the many uncertainties.

#### 3.5. Conclusions

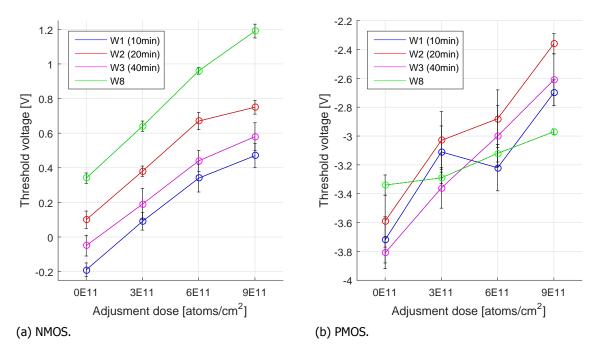

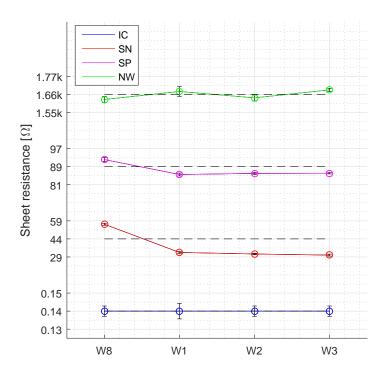

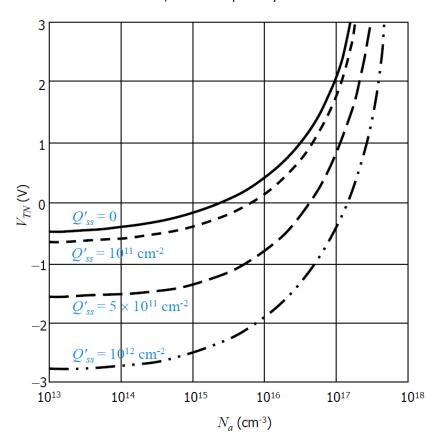

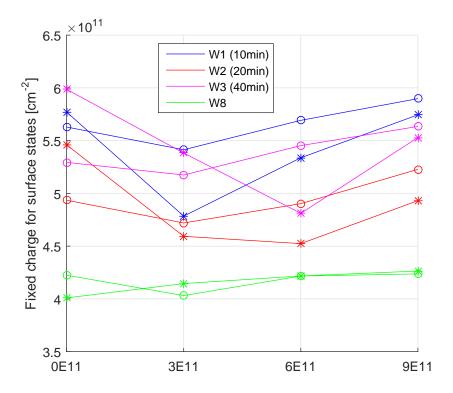

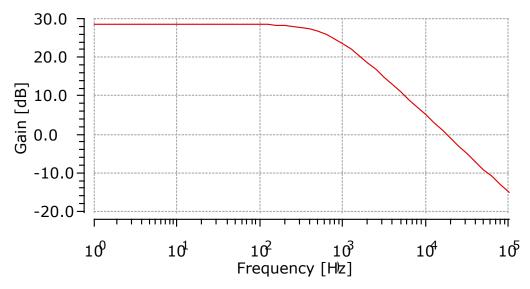

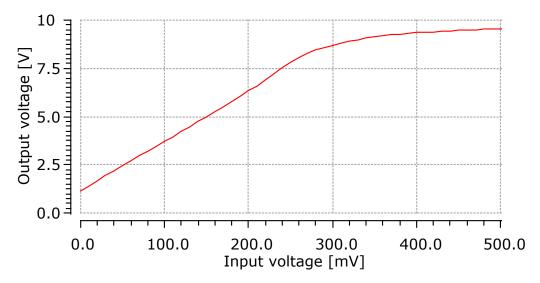

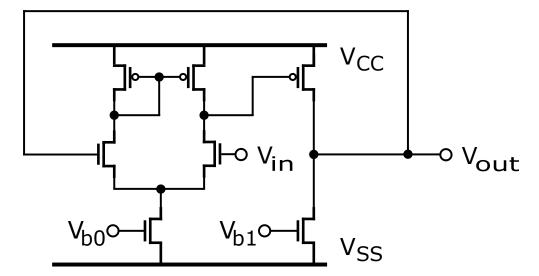

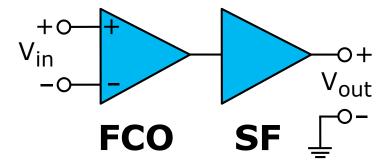

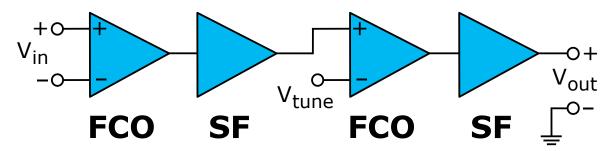

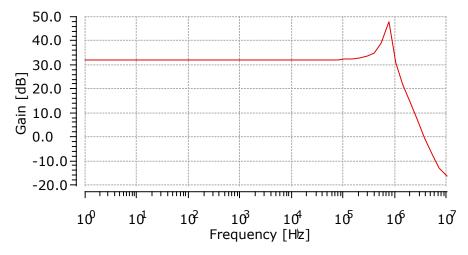

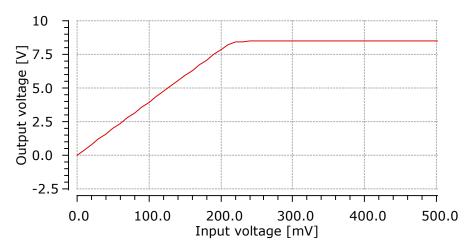

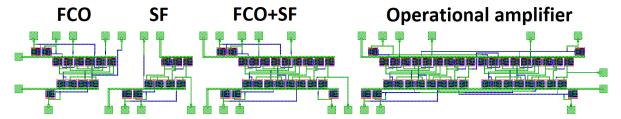

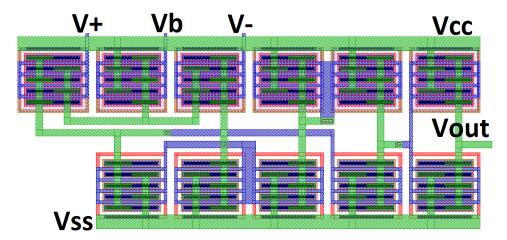

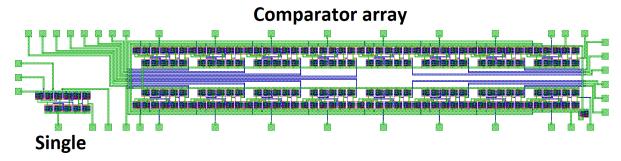

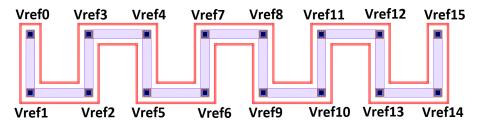

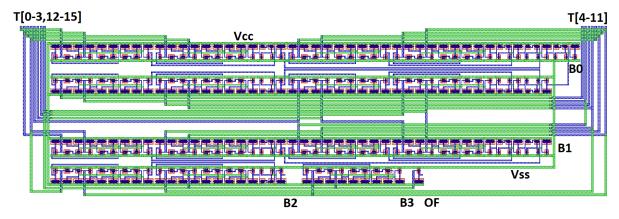

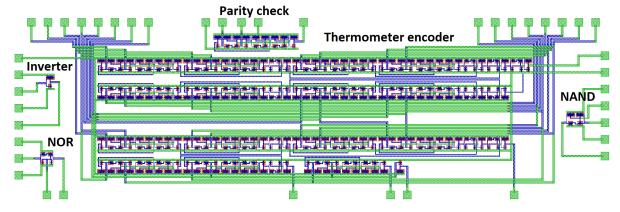

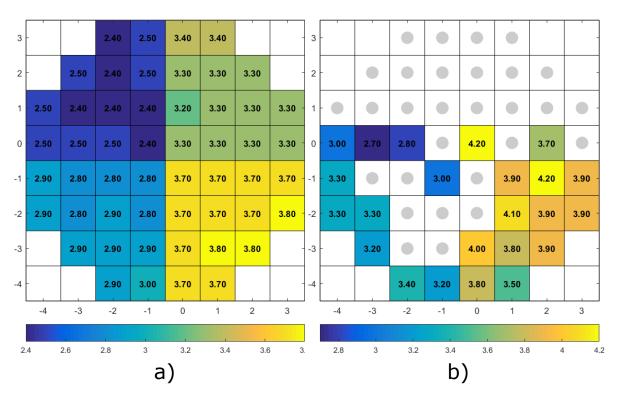

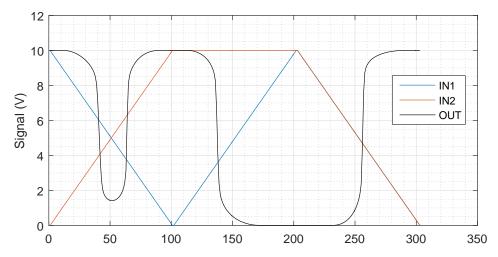

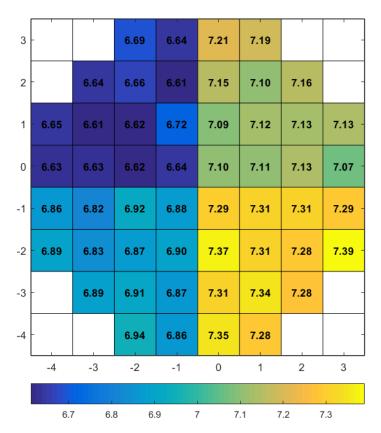

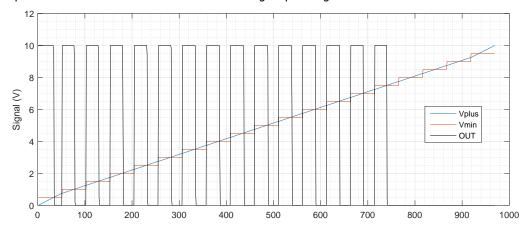

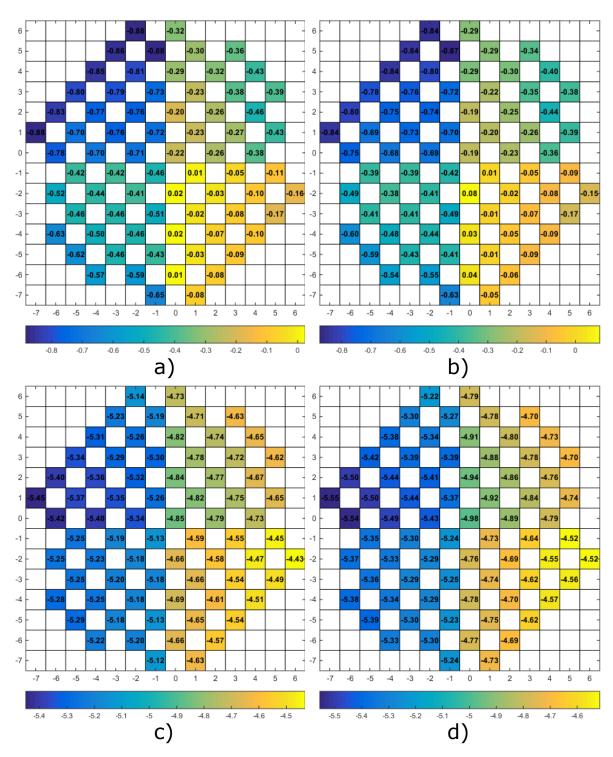

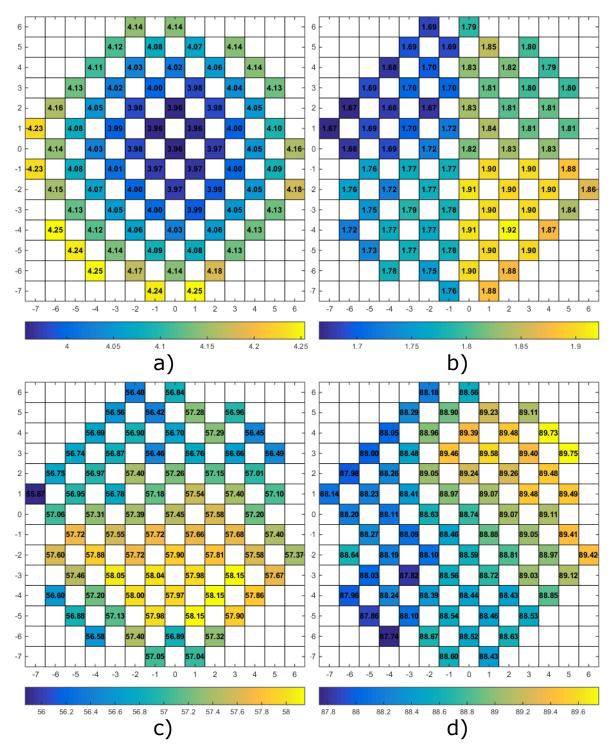

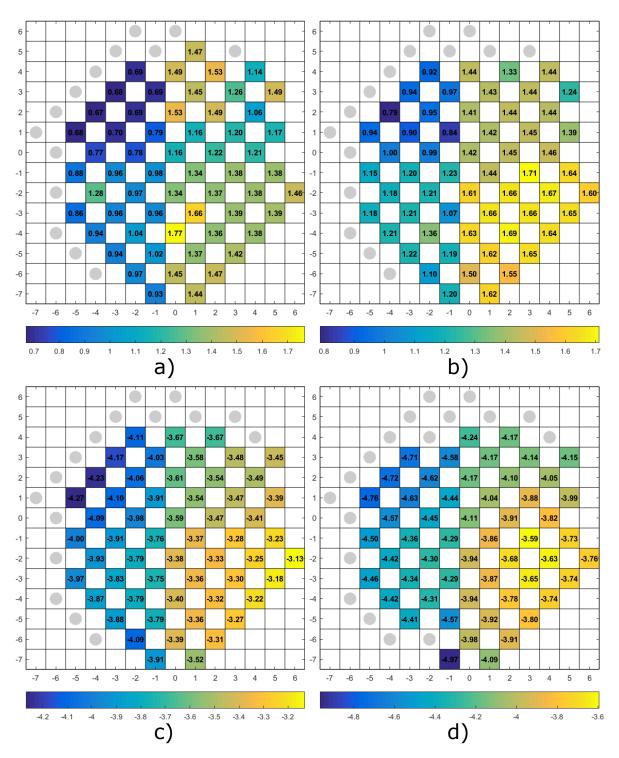

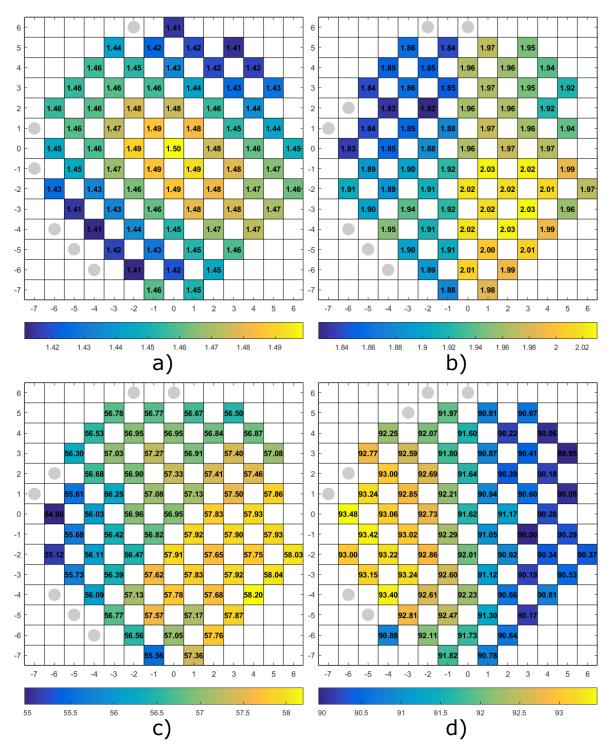

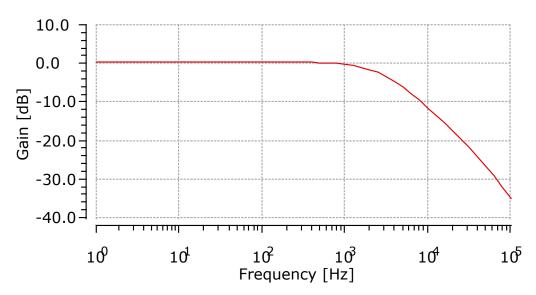

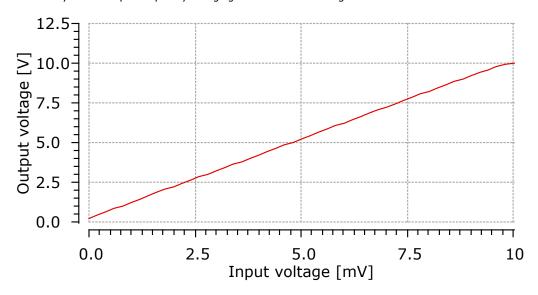

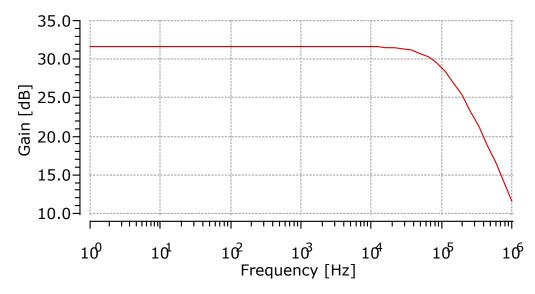

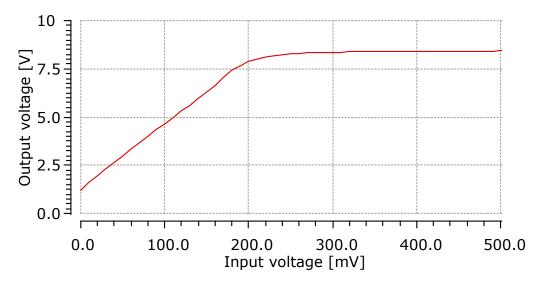

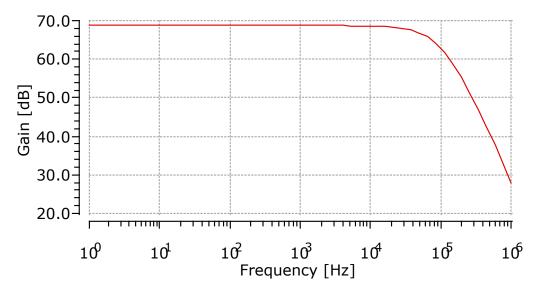

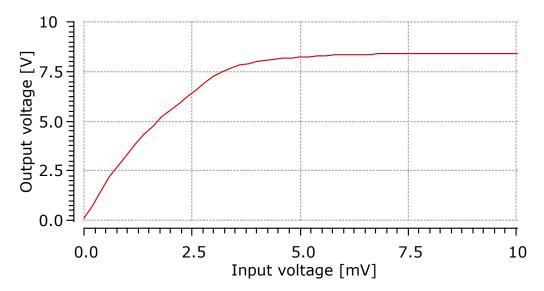

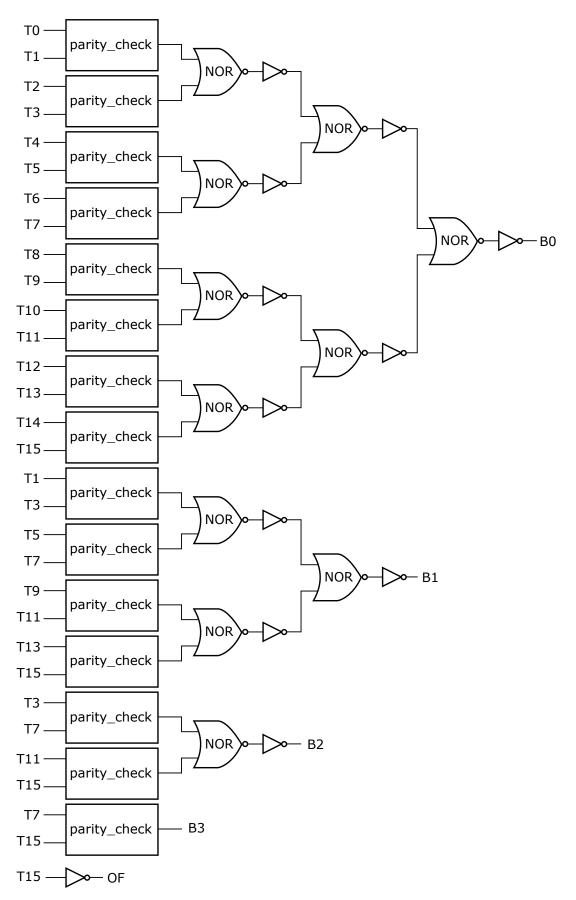

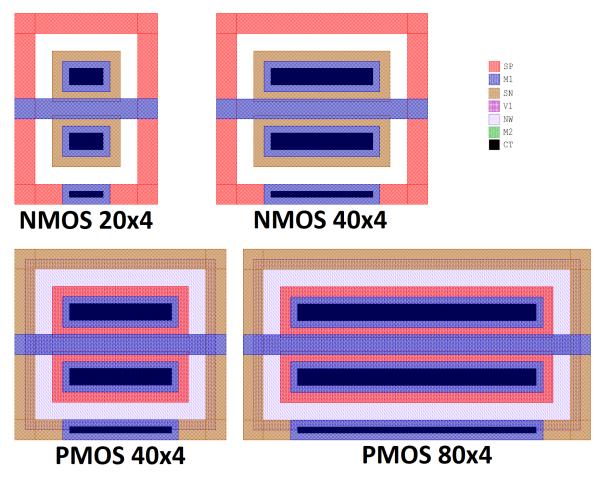

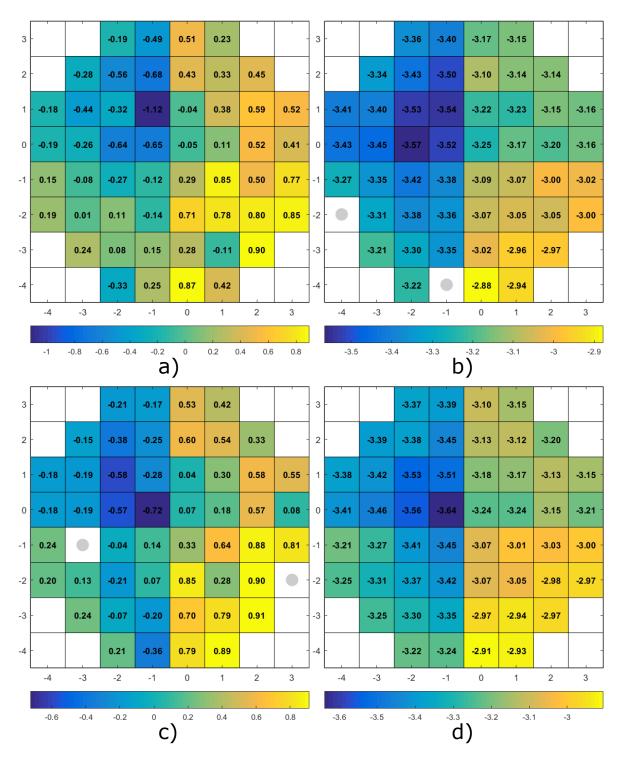

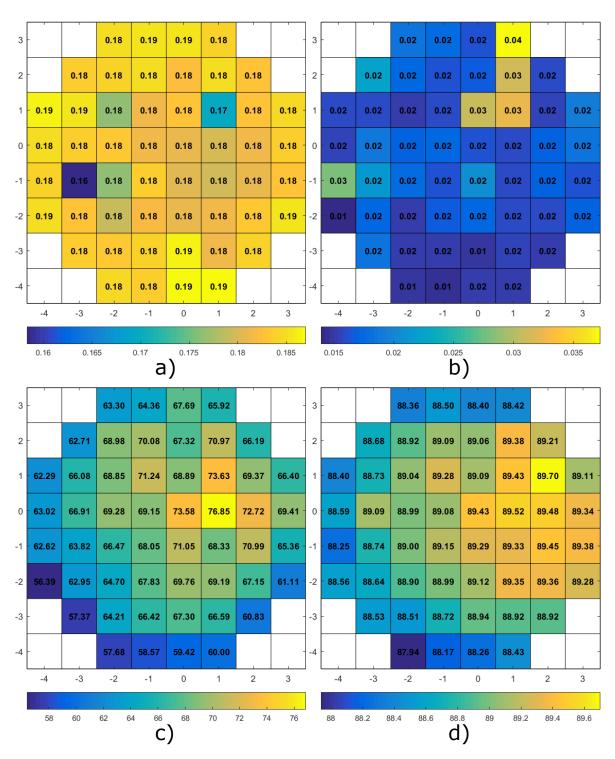

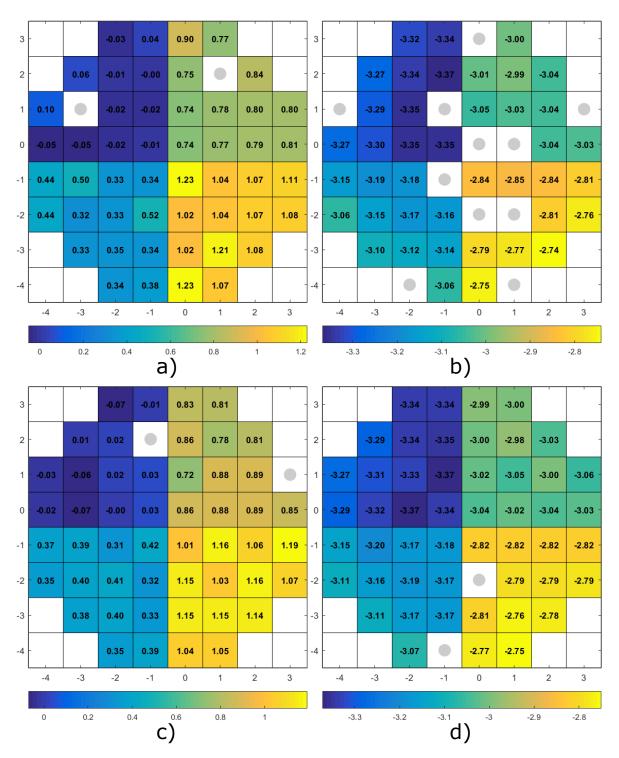

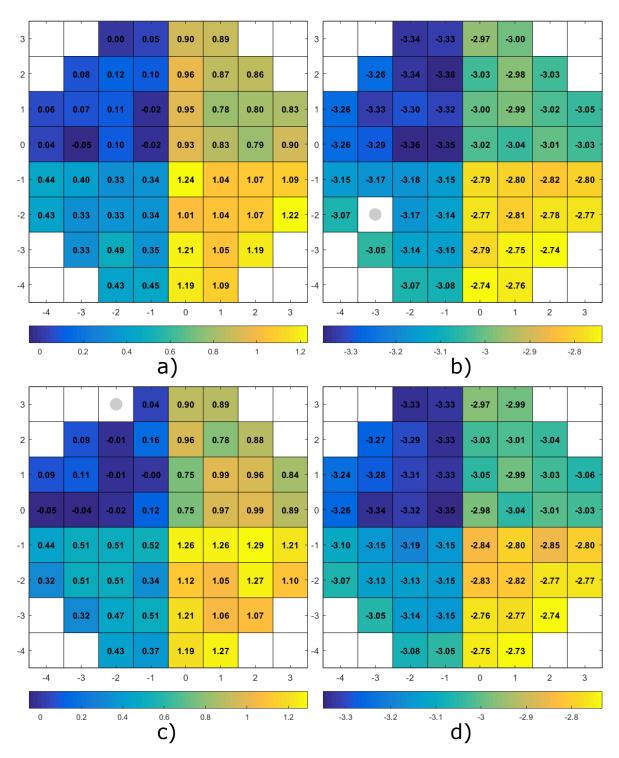

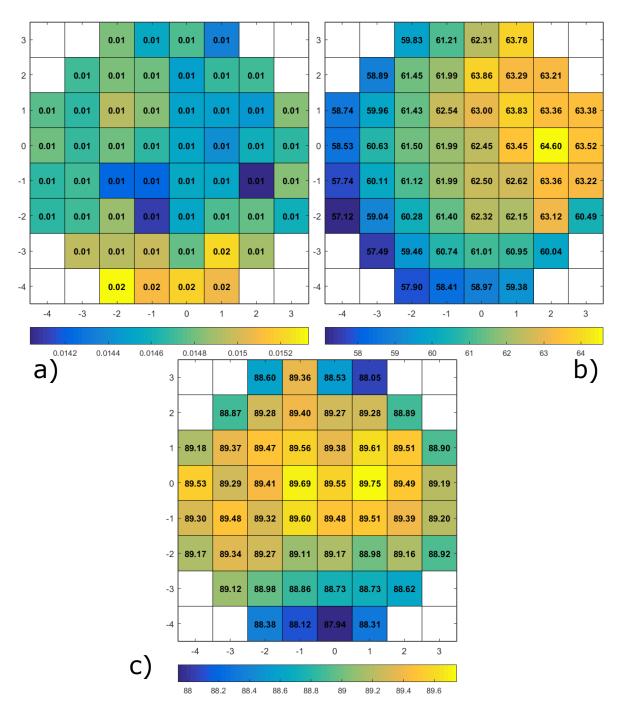

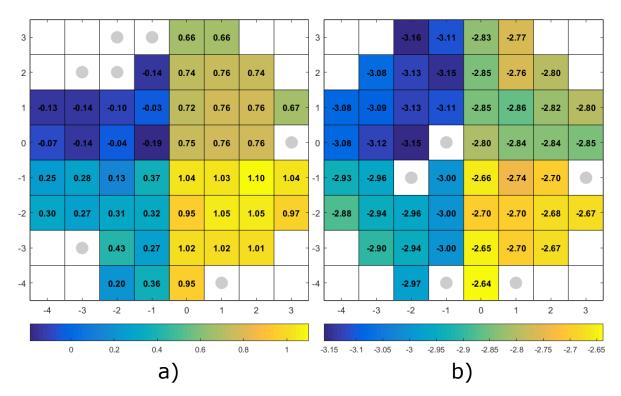

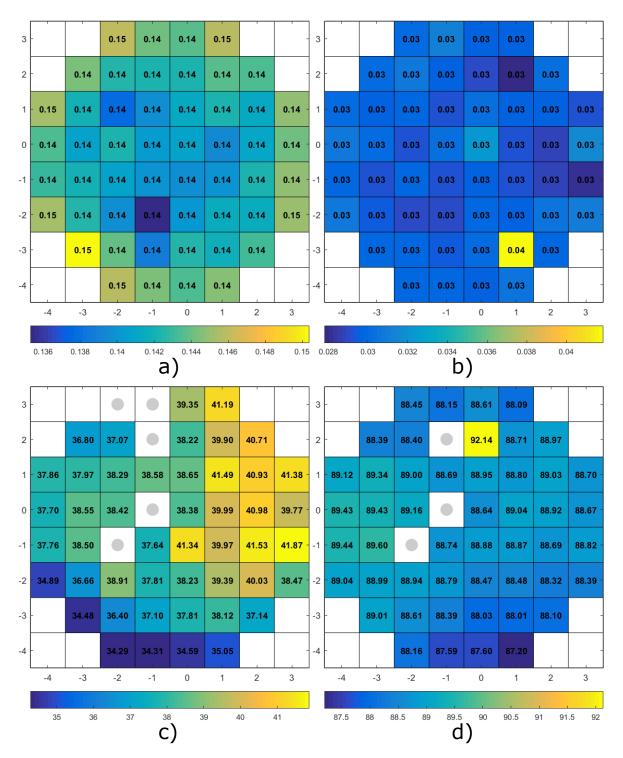

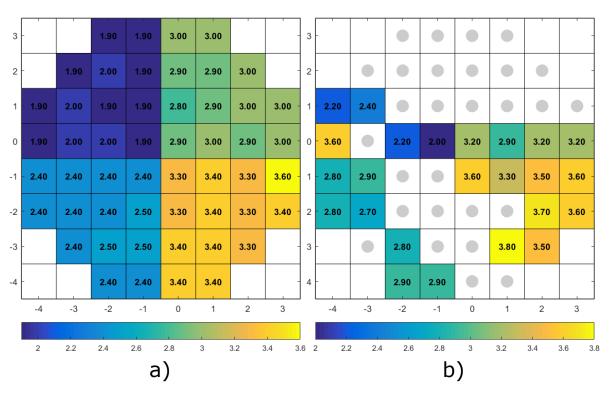

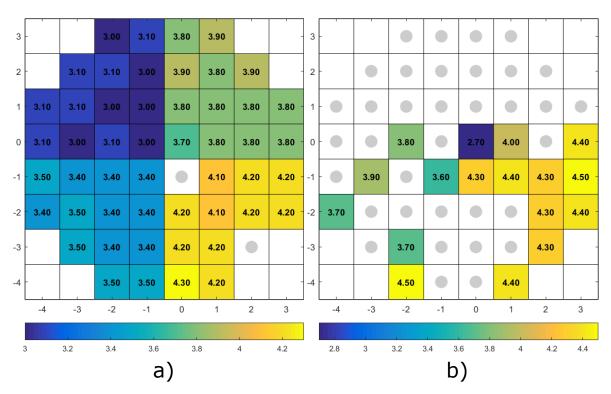

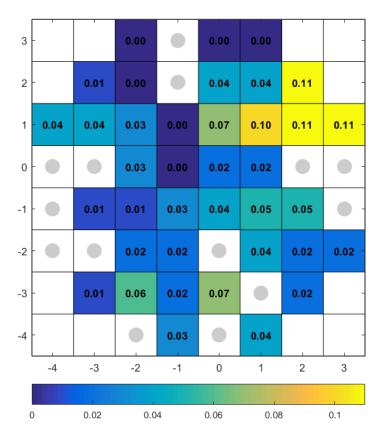

Two batches of graphene-based Pirani pressure sensors were released and characterized, leading to world's first graphene-based Pirani pressure sensors. The largest maximum resistance change observed was 2.8 % at a bias voltage of 15 V and a low power of 0.9 mW was achieved at a bias voltage of 9 V with maximum resistance change of 0.8 %. The second batch provided several different aspect ratio devices, with similar performance as the first