A Digital-Intensive Wakeup Timer based on an RC Frequency-Locked Loop for Internet-of-Things Applications

Zhihao Zhou

# A Digital-Intensive Wakeup Timer based on an RC Frequency-Locked Loop for Internet-of-Things Applications

by

#### Zhihao Zhou

in partial fulfillment of the requirements for the degree of

#### **Master of Science**

in Microelectronics

at the Delft University of Technology, to be defended publicly on Monday, November 27, 2017.

Supervisors: Prof. dr. Fabio Sebastiano, TU Delft

Dr. Yao-Hong Liu, IMEC/Holst Centre Ir. Ming Ding, IMEC/Holst Centre

Thesis committee: Prof. dr. Michiel Pertijs, TU Delft

Prof. dr. Masoud Babaie, TU Delft

This thesis is confidential and cannot be made public until December 1, 2018.

An electronic version of this thesis is available at http://repository.tudelft.nl/.

# **Abstract**

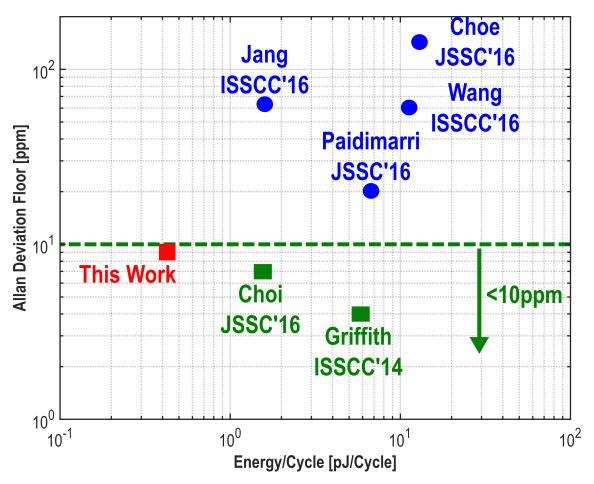

This thesis presents an ultra-low power wakeup timer locked to an RC time constant that can meet the stringent power requirements of the nodes for Internet-of-Things (IoT) applications. The wakeup timer, fabricated in a 40-nm CMOS process, employs a bang-bang digital-intensive frequency-locked loop (DFLL). A self-biased  $\Sigma\Delta$  digitally controlled oscillator (DCO) is locked to an RC time constant via a chopped dynamic comparator and a digital loop filter, enabling an operation down to 0.65 V and a small area of 0.07 mm<sup>2</sup>. The digital-intensive design consumes 181 nW with an output frequency of 417 kHz. Thus, it achieves the best power efficiency (0.43 pJ/Cycle) at the lowest supply voltage (0.7 V nominal) over the state-of-the-art for ultra-low-power timers, while keeping on-par long-term stability (Allan deviation floor below 10 ppm) and temperature stability (106 ppm/°C).

# Contents

| Li | st of                                  | Figures                                                                                                                                                                                                                                                        | vii                                          |

|----|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Li | st of                                  | Tables                                                                                                                                                                                                                                                         | хi                                           |

| 1  | 1.1                                    | Internet-of-Tings and wireless sensor networks                                                                                                                                                                                                                 |                                              |

|    | 1.3                                    | Motivation and objectives                                                                                                                                                                                                                                      | 4                                            |

| 2  | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | y Integrated Time References  RC-based references  LC-based references  TD-based references  MOS-based references  MEMS-based references  State-of-the-art low-power references  2.6.1 Relaxation oscillators  2.6.2 FLL oscillators  Benchmark and conclusion | 10<br>11<br>12<br>13<br>14<br>14<br>15       |

| 3  | A D: 3.1 3.2 3.3                       | igital-Intensive FLL based RC Oscillator Specifications. Proposed architecture 3.2.1 Small signal model. System-level considerations 3.3.1 RC network. 3.3.2 Comparator 3.3.3 Digital loop filter 3.3.4 Multi-phase clock generator 3.3.5 DCO Conclusion       | 19<br>20<br>22<br>26<br>26<br>28<br>29<br>29 |

| 4  | 4.1<br>4.2<br>4.3                      | System overview RC network 4.2.1 Characteristics of integrated resistors and capacitors 4.2.2 Trimming network 4.2.3 Switches Dynamic comparator DCO 4.4.1 Leakage based delay cell 4.2 Subthreshold PTAT bias circuit                                         | 34<br>36<br>37<br>39<br>42<br>44             |

vi

| 4.4.3 Sigma-Delta modulator 4.5 Digital Loop Filter 4.6 Clock divider 4.7 Layout overview  5 Measurement Results 5.1 Chip micrograph 5.2 Measurement setup 5.3 Measurement results 5.3.1 Frequency accuracy vs. temperature variation 5.3.2 Frequency accuracy vs. supply variation 5.3.3 Allan deviation 5.3.4 Power consumption 5.3.5 Other results 5.4 Conclusion and summary  6 Conclusion and Future Work 6.1 Conclusion 6.2 Future work  A Phase Noise, Period Jitter and Allan Deviation Conversions A.1 Phase noise and Allan deviation conversion A.2 Phase noise and period jitter conversion  B MATLAB behavior model of the DFLL | 75                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 4.5 Digital Loop Filter 4.6 Clock divider 4.7 Layout overview  5 Measurement Results 5.1 Chip micrograph 5.2 Measurement setup 5.3 Measurement results 5.3.1 Frequency accuracy vs. temperature variation 5.3.2 Frequency accuracy vs. supply variation 5.3.3 Allan deviation 5.3.4 Power consumption 5.3.5 Other results 5.4 Conclusion and summary  6 Conclusion and Future Work 6.1 Conclusion 6.2 Future work  A Phase Noise, Period Jitter and Allan Deviation Conversions A.1 Phase noise and Allan deviation conversion                                                                                                               | 73                               |

| 4.5 Digital Loop Filter 4.6 Clock divider 4.7 Layout overview  5 Measurement Results 5.1 Chip micrograph 5.2 Measurement setup 5.3 Measurement results 5.4 Power consumption 5.5 A Power consumption 5.5 Chip micrograph 5.5 Measurement results 5.6 Conclusion and Future Work 6.1 Conclusion                                                                                                                                                                                                                                                                                                                                               |                                  |

| 4.5 Digital Loop Filter 4.6 Clock divider 4.7 Layout overview  5 Measurement Results 5.1 Chip micrograph 5.2 Measurement setup. 5.3 Measurement results 5.3.1 Frequency accuracy vs. temperature variation. 5.3.2 Frequency accuracy vs. supply variation 5.3.3 Allan deviation. 5.3.4 Power consumption 5.3.5 Other results.                                                                                                                                                                                                                                                                                                                |                                  |

| 4.5 Digital Loop Filter4.6 Clock divider4.7 Layout overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 58<br>59<br>59<br>60<br>61<br>62 |

| 4.4.2 Sigma Dalta madulatar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50<br>51                         |

# List of Figures

| 1.1  | Conceptual framework of future IoT                                                                                                                                            |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2  | (a) A fully integrated IoT node. (b) The smallest crystal.                                                                                                                    |

| 1.3  | (a) Generalized block diagram of a duty-cycled IoT node. (b) Example timing profile of a duty-cycled IoT node that includes guard bands to compensate for timing uncertainty. |

| 1.4  | Power consumption in a duty-cycled wireless system                                                                                                                            |

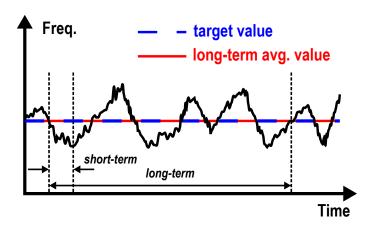

| 1.5  | Illustration of a long-term stable noisy frequency signal.                                                                                                                    |

| 1.6  | Lifetime voltage of Duracell CR1220 button battery.                                                                                                                           |

| 2.1  | Generalized block diagram of a Wienbridge oscillator.                                                                                                                         |

| 2.2  | Generalized block diagram of an LC oscillator.                                                                                                                                |

| 2.3  | Block diagram of the TD-based frequency reference.                                                                                                                            |

| 2.4  | (a) Block diagram of the MEMS-based frequency reference. (b) Die micrograph of the MEMS-based frequency reference.                                                            |

| 2.5  | Block diagram of a conventional relaxation oscillator                                                                                                                         |

| 2.6  | Generalized block diagram of an FLL RC oscillator.                                                                                                                            |

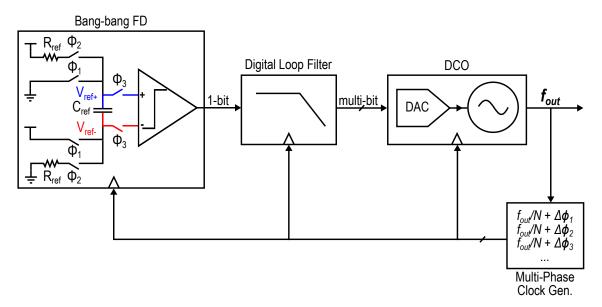

| 3.1  | Block diagram of the proposed DFLL based RC oscillator.                                                                                                                       |

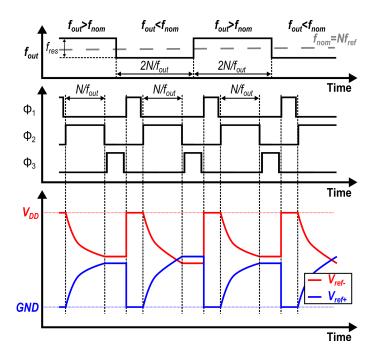

| 3.2  | Waveforms of DCO output frequency, RC network timing, and $C_{ref}$ voltages of the DFLL under ideal steady state operation.                                                  |

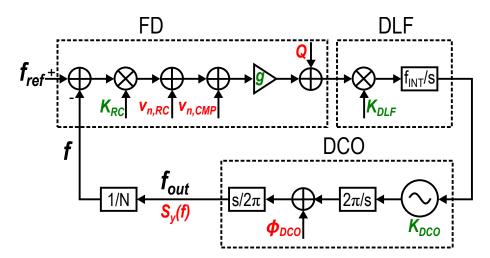

| 3.3  | Small signal model of the proposed oscillator.                                                                                                                                |

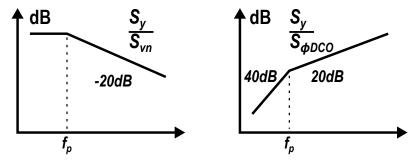

| 3.4  | Gain plots of the noise transfer functions.                                                                                                                                   |

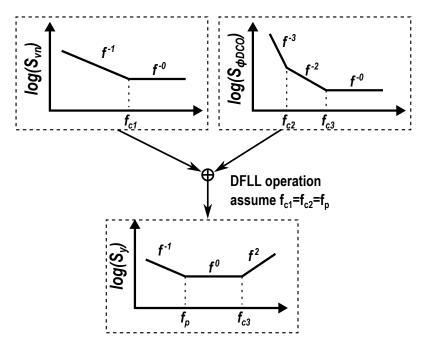

| 3.5  | Typical spectrums of $v_n$ and $\phi_{DCO}$ , and their responses on $S_y$ with the DFLL operation.                                                                           |

| 3.6  | Allan deviation simulations with different comparator flicker noise and the same DCO flicker FM.                                                                              |

| 3.7  | Allan deviation simulations with different DCO flicker FM and the same comparator flicker noise                                                                               |

| 3.8  | Allan deviation simulations with different DCO resolutions and comparator flicker noise of 1 $\mu$ V/ $\sqrt{\rm Hz}$ at 10 Hz.                                               |

| 3.9  | Illustration of the RC trimming strategy using a 12-bit coarse-fine overlapped network.                                                                                       |

| 3.10 | Topology of a resistor using first-order temperature compensation and illustration of the TCs of the resistors before and after compensation.                                 |

| 3.11 |                                                                                                                                                                               |

| 3.12 | Illustration of the frequency offset due to the DCO finite resolution.                                                                                                        |

|      | Simulation showing reduced frequency offset due the DCO finite resolution thanks                                                                                              |

|      | to noise.                                                                                                                                                                     |

viii List of Figures

| 4.1         | Architecture of the proposed oscillator, the clocks driving each block are marked                |

|-------------|--------------------------------------------------------------------------------------------------|

|             | in purple.                                                                                       |

| 4.2         | Temperature dependencies of the compensated and uncompensated resistors                          |

| 4.3         | Monte Carlo simulations showing (a) first-order TC variation, and (b) resistance                 |

|             | variation of the compensated resistor.                                                           |

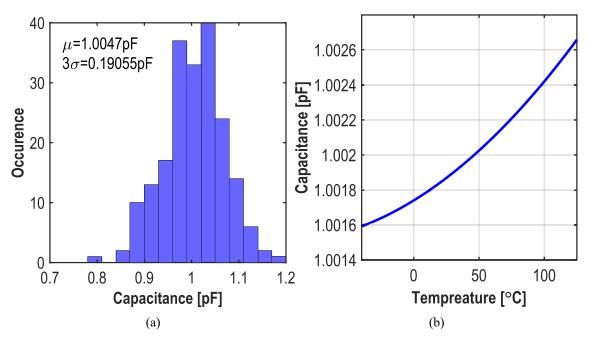

| 4.4         | (a) Process variation of a 1 pF fringe MOM capacitor. (b) Temperature dependency                 |

|             | of the MOM capacitor.                                                                            |

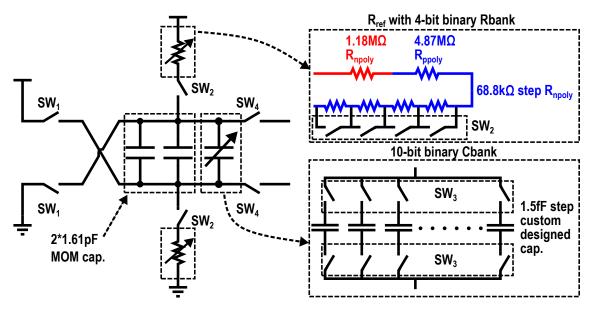

| 4.5         | RC network with trimming capabilities                                                            |

| 4.6         | Schematic of the switches used in the RC network.                                                |

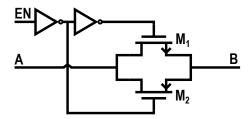

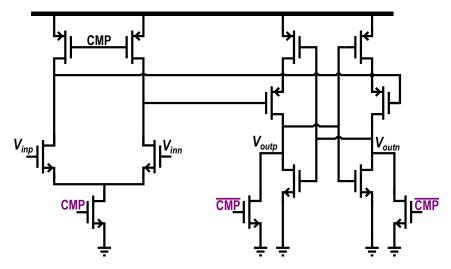

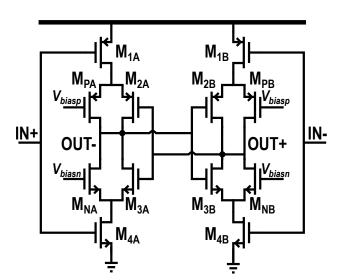

| 1.7         | Schematic of the dynamic comparator                                                              |

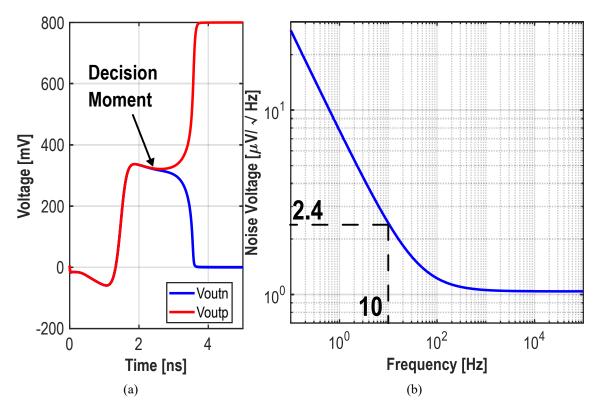

| 4.8         | (a) Comparator output voltages showing the decision moment at around 2.5 ns. (b)                 |

|             | Input referred noise of the comparator                                                           |

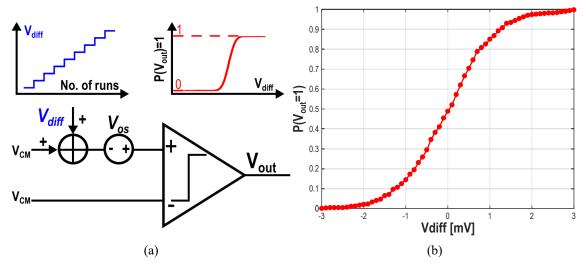

| 4.9         | (a) Illustration of the comparator offset simulation testbench. (b) Statistical simu-            |

|             | lation result of the comparator offset voltage.                                                  |

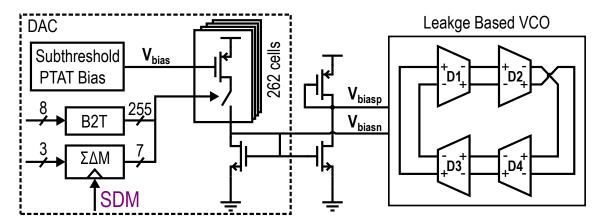

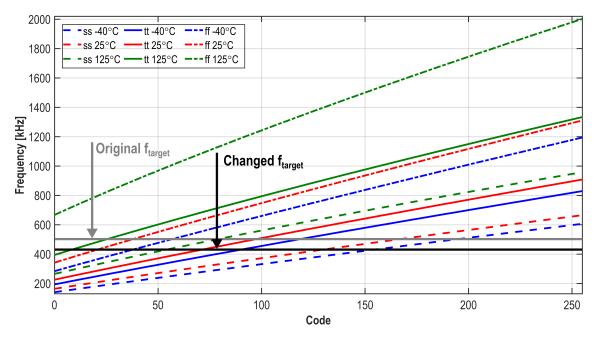

|             | Block diagram of the DCO with $\Sigma\Delta$ dithered input.                                     |

|             | DCO tuning range under temperature and process corners                                           |

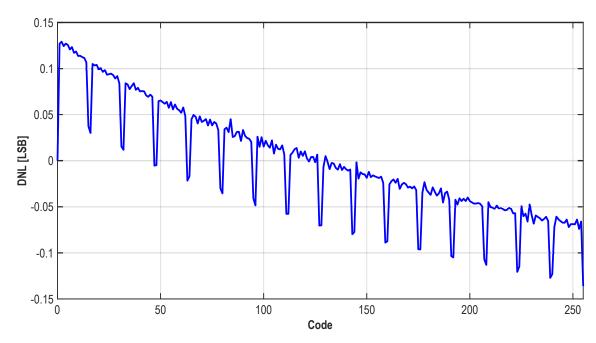

| 1.12        | DNL of the DCO integer bits                                                                      |

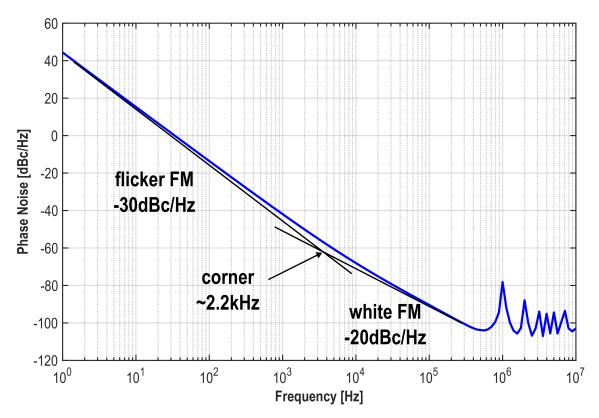

| 4.13        | DCO phase noise performance at the center frequency of 512 kHz                                   |

|             | Schematic of the leakage based delay cell                                                        |

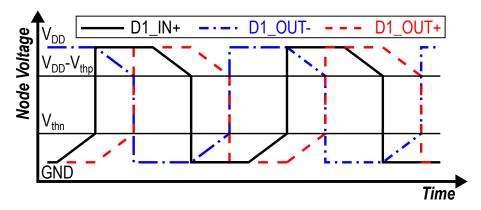

|             | Transient voltages of the internal nodes in one delay cell                                       |

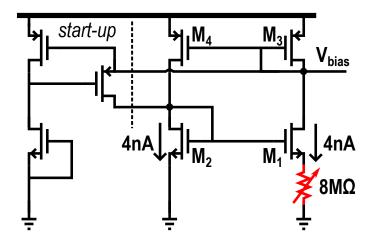

| 1.16        | Schematic of the subthreshold PTAT bias circuit.                                                 |

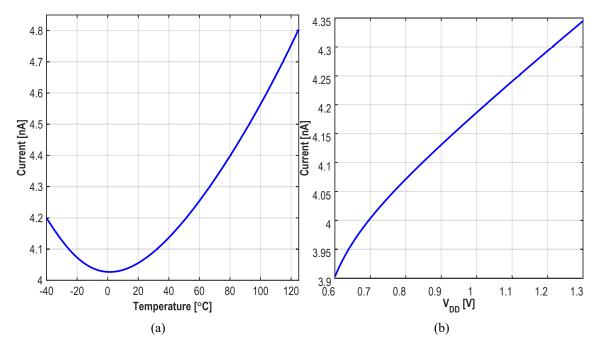

| 1.17        | (a) Temperature dependency of the PTAT bias current. (b) Supply voltage depen-                   |

|             | dency of the PTAT bias current.                                                                  |

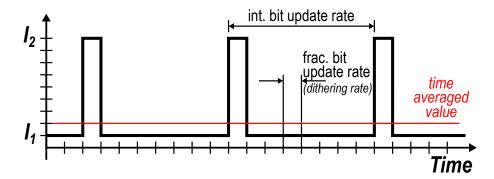

| 1.18        | Illustration of the DCO high rate dithering.                                                     |

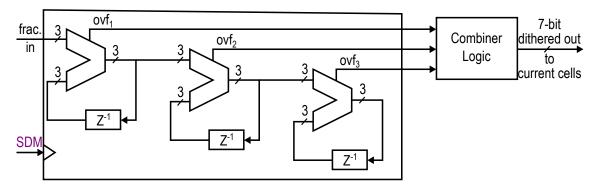

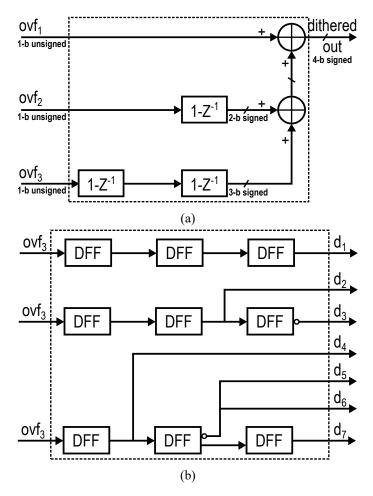

|             | Block diagram of the third-order MASH $\Sigma\Delta$ modulator                                   |

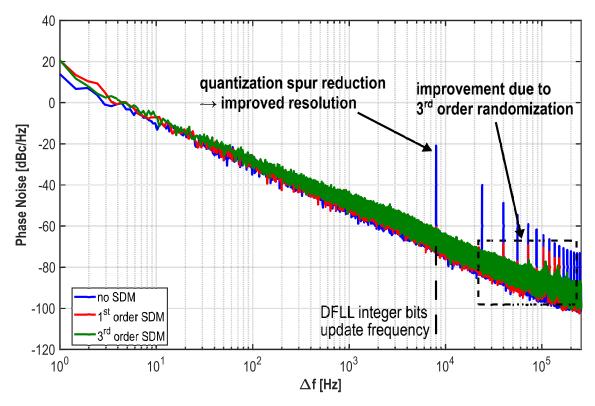

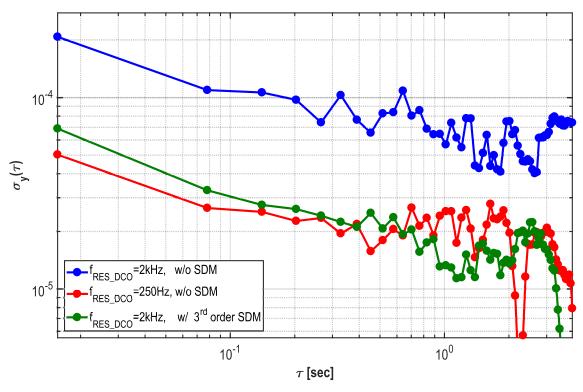

|             | Phase noise plot showing the effect of the first-order and third-order $\Sigma\Delta$ modulators |

| 4.21        | Allan deviation plot showing the effect of the third-order $\Sigma\Delta$ modulator              |

| 1.22        | (a) Original combiner logic with signed summation. (b) Improved combiner with                    |

|             | D flip-flops only.                                                                               |

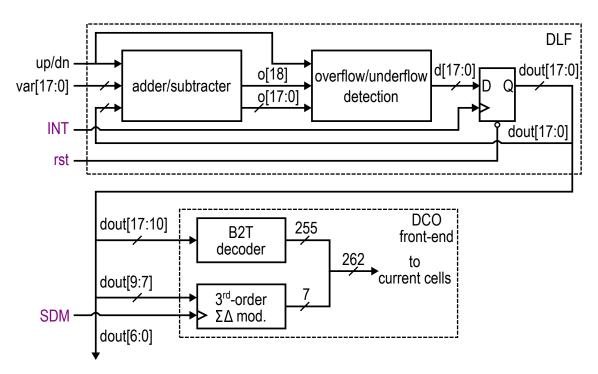

| 1.23        | Block diagram of the DLF and its connection with the DCO                                         |

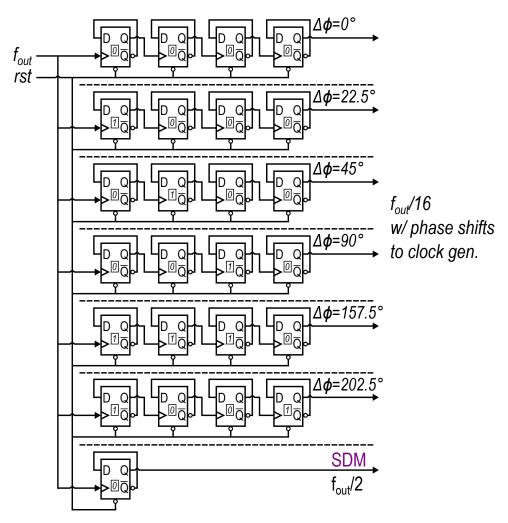

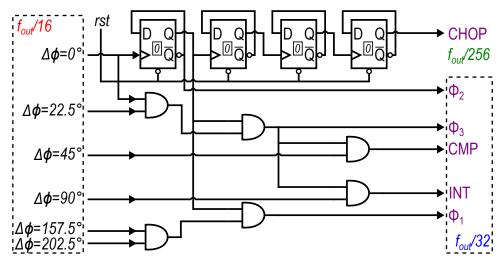

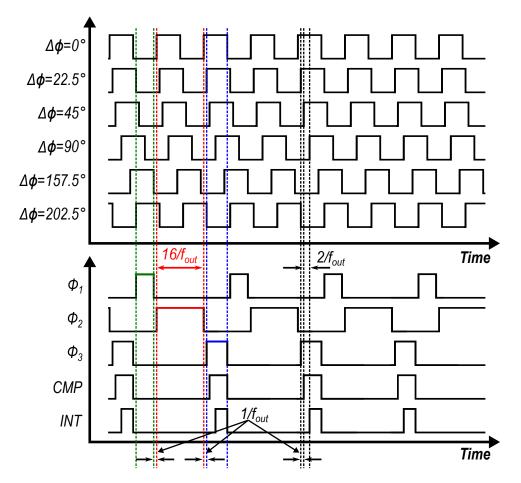

|             | Block diagram of multi-phase divider                                                             |

|             | Block diagram of the non-overlap clock generator.                                                |

| 1.26        | Waveforms of the timing of the multi-phase divider and the non-overlap clock                     |

|             | generator                                                                                        |

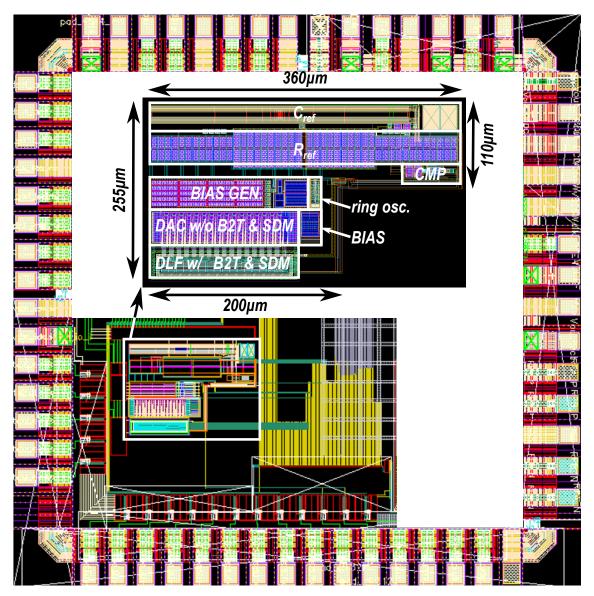

| 1.27        | Layout of the chip.                                                                              |

|             |                                                                                                  |

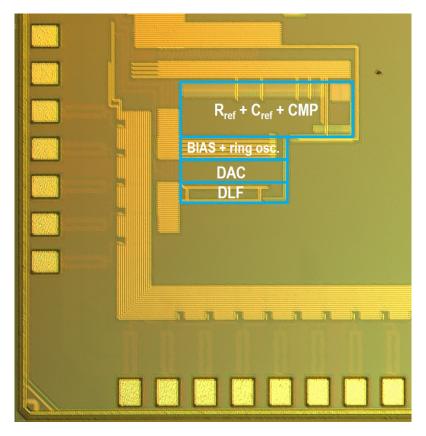

| 5.1         | Die micrograph of the fabricated chip in the 40-nm process                                       |

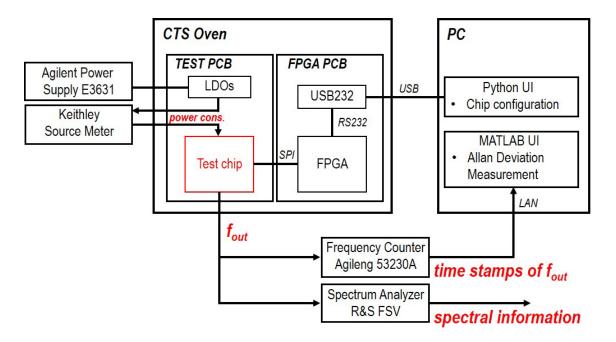

| 5.2         | Block diagram of the measurement setup.                                                          |

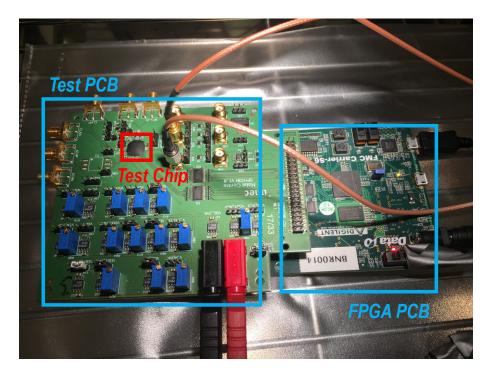

| 5.3         | PCBs used for measurement                                                                        |

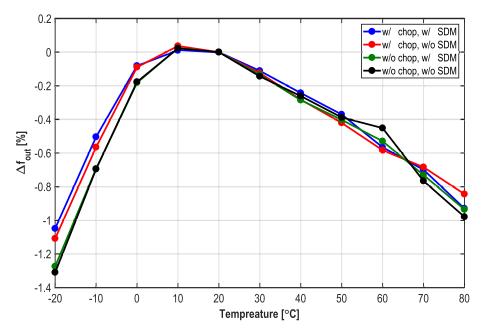

| 5.4         | Frequency accuracy vs. temperature variation                                                     |

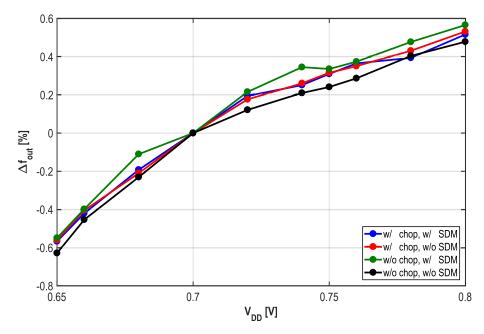

| 5.5         | Frequency accuracy vs. supply variation.                                                         |

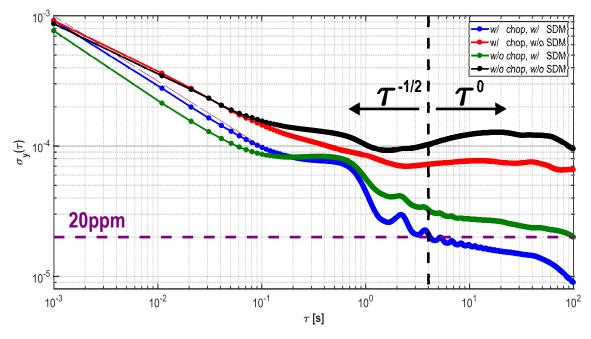

| 5.6         | Allan deviation measurement results.                                                             |

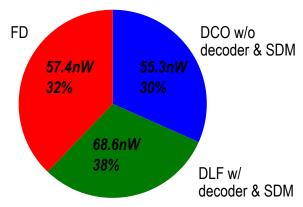

| 5.7         | Oscillator power breakdown.                                                                      |

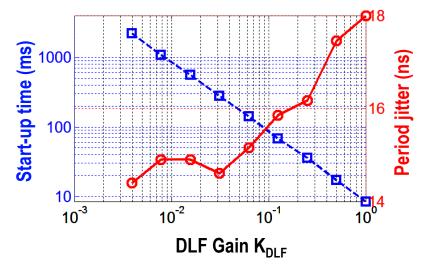

| 5.8         | Period jitter and start-up time with different DLF gain.                                         |

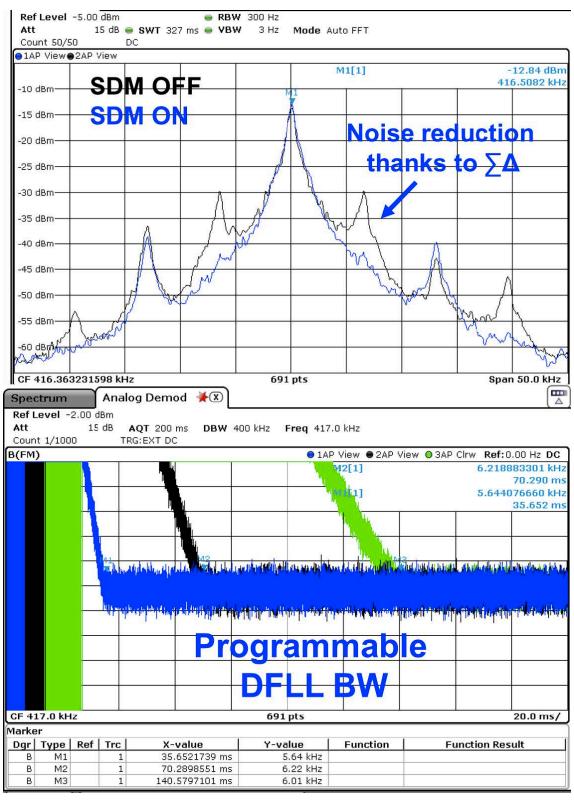

| 5.9         | Output spectrum and settling behavior.                                                           |

| 5.10        |                                                                                                  |

|             |                                                                                                  |

| <b>A</b> .1 | Characteristics of the noise processes in spectral density of phase fluctuations.                |

| r' CD'          | •  |

|-----------------|----|

| List of Figures | 10 |

| List of Figures | 12 |

|                 |    |

| A.2 | Characteristics of the noise processes in spectral density of fractional frequency |    |

|-----|------------------------------------------------------------------------------------|----|

| A.3 | fluctuations                                                                       |    |

| B.1 | Pseudo code of the discrete time MATLAB behavior model.                            | 74 |

# List of Tables

| 2.1         | Benchmark table of the integrated oscillators                                                                          | 17 |

|-------------|------------------------------------------------------------------------------------------------------------------------|----|

| 3.1         | Target specifications of the proposed oscillator                                                                       | 19 |

| 3.2         | Design specifications for the major building blocks                                                                    | 31 |

| 4.1         | Characteristics of the available non-silicide poly resistors in the 40-nm process.                                     | 34 |

| 4.2         | Worst-case $R_{on}$ and $I_{leak}$ of the switches at 25 °C and tt corner.                                             | 38 |

| 4.3         | Start up time of the current reference in millisecond across corners                                                   | 47 |

| 4.4         | Summary of the configurable functions in the DFLL                                                                      | 55 |

| 5.1         | Performance summary and comparison with state-of-the-art.                                                              | 66 |

| <b>A.</b> 1 | Translation of frequency instability measures from spectral densities in frequency domain to variances in time domain. | 71 |

|             | domain to variances in time domain.                                                                                    | /  |

1

# Introduction

## 1.1. Internet-of-Tings and wireless sensor networks

Communication and networking technologies have enabled people to connect with each other everywhere at any time. In the meantime, there is a growing demand for networks which can facilitate the communication between human and environment, human and machines, and even machine and machines. The key technology fulfilling this demand is the *Internet-of-Things (IoT)*, which is a framework comprising physical objects equipped with limited hardware to provide computation and networking support.

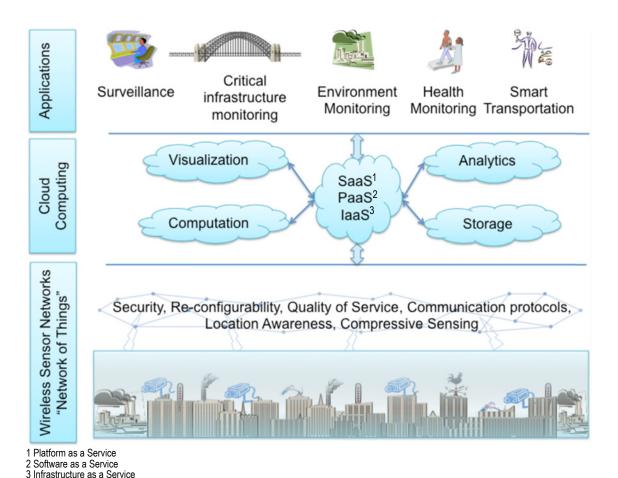

The first IoT device (a coke machine) was implemented in 1982<sup>1</sup>. From that time on, Internet-connected devices have been around us for decades. However, only recently these devices have permeated our lives and are popularly conceptualized as IoT. The IoT is now regarded as the next revolutionizing technology and economic worldwide after the Internet. In its paradigm, many objects will be connected to networks and embedded into our surroundings ubiquitously and seamlessly. A conceptual framework of future IoT is shown in figure 1.1 below.

As depicted in the figure, the basement of IoT is composed by the *Wireless sensor networks (WSNs)*. In WSNs, distributed autonomous sensor nodes monitor physical conditions such as temperature, humidity, pressure, etc. The acquired raw data is collected and propagated to the cloud for computational purposes. After being processed in the cloud, the raw data becomes useful information and then available to users in different kinds of applications.

Typical WSN applications, e.g., environmental monitoring, require hundreds or even thousands of nodes in the network. In addition to the sensor, each node must also be equipped with other circuitry for wireless communication, such as a micro-controller and a radio transceiver. Considering the functionalities of the node, there are several constraints it should satisfy [1].

- The cost of each node should be low (cheaper than 1 €), so that the entire WSN comprising thousands of nodes is economically viable;

- Small form factor is preferred since the nodes must be seamlessly integrated into the environment;

<sup>1</sup>https://www.cs.cmu.edu/~coke/history long.txt

2 1. Introduction

Figure 1.1: Conceptual framework of future IoT (reproduced from [2]).

• Low-power consumption is required for energy-autonomous operation and long lifetime in battery powered systems.

#### **1.2.** Time reference for IoT node

As mentioned in the previous section, the IoT node in WSNs must be cheap, small, and power efficient. Conventional solutions for IoT nodes may need many discrete ICs and a custom designed printed circuit board (PCB) for assembly. However, this solution is not efficient in either cost or size. One way to solve these problems is integrating the components together. If all of the discrete components are combined into one, the cost of PCB making and chip packaging can be cut off, and the resulting size is also much smaller.

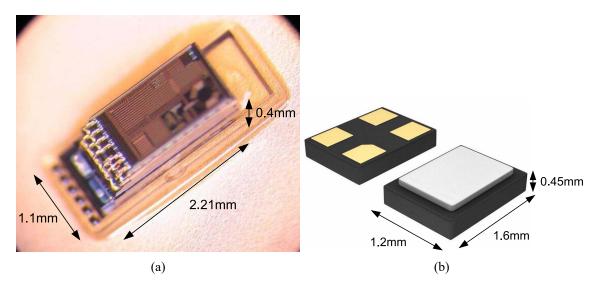

Modern wireless communication protocols require either time or frequency information for synchronization. Thus, the IoT node in WSNs should contain at least one time/frequency reference<sup>1</sup>. Crystal oscillators are most widely used for frequency generation in wireless applications. However, it is bulky and cannot be integrated into an integrated circuit (IC) using standard CMOS technology. In figure 1.2, the smallest crystal is shown next to a fully functional IoT node for size comparison, and thus the limit in size is clearly illustrated.

<sup>&</sup>lt;sup>1</sup>Expressions "oscillator" and "time/frequency reference" are interchangeable

Figure 1.2: (a) A fully integrated IoT node. (b) The smallest crystal. (both reproduced from [3])

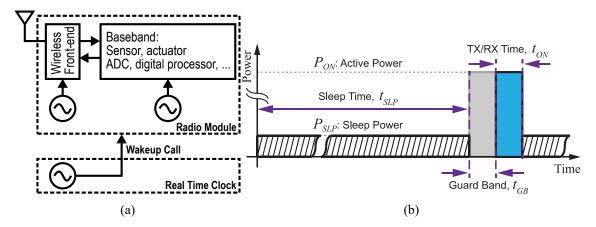

Figure 1.3: (a) Generalized block diagram of a duty-cycled IoT node. (b) Example timing profile of a duty-cycled IoT node that includes guard bands to compensate for timing uncertainty (reproduced from [4]).

Moreover, a time reference is also needed to meet the very tight power requirements for IoT applications. Taking advantage of the small average rate required by WSN for IoT, the wireless radio module can be duty-cycled, and power is only dissipated during data transmission. One of the most widely accepted duty-cycled node architectures is shown in figure 1.3a, consisting a radio module for communication and a real-time clock (RTC)<sup>2</sup> for time synchronization [5]. The main radio is not active (i.e., in low-power sleep mode) until the RTC wakeup call arrives. Power consumption in these systems is averaged down. As shown in figure 1.3b (b), the average system power consumption can be expressed as

$$P_{avg} = \frac{P_{SLP}t_{SLP} + P_{ON}(t_{ON} + t_{GB})}{t_{SLP} + t_{ON} + t_{GB}},$$

(1.1)

where  $t_{SLP}$  is the sleep time,  $P_{SLP}$  is the sleep power,  $t_{ON}$  is the active TX/RX time,  $P_{ON}$  is the active power,  $t_{GB}$  is the guard band time, and  $P_{avg}$  is the average IoT node total power over time.

<sup>&</sup>lt;sup>2</sup>Expressions "RTC" and "wakeup timer" are interchangeable

4 1. Introduction

The guard band time is defined as

$$t_{GB} = C_U \cdot t_{SLP} \tag{1.2}$$

where  $C_U$  is the RTC inaccuracy. When the system is aggressively duty-cycled, i.e.,  $t_{SLP} >> (t_{GB} + t_{ON})$ ,  $P_{SLP} \cdot t_{SLP}$  becomes comparable to  $P_{ON}(t_{ON} + t_{GB})$ . Thus, the total power is dominated not by the active mode power of radio front-end and baseband, but instead by a mix of duty-cycled active mode power and the static power of always-on modules, such as bias generators and the RTC.

In the duty-cycled node architecture shown in figure 1.3a, there are three types of frequency references needed [5]:

- RTC: it generates the wakeup calls for all other modules;

- Reference for baseband: clock for digital circuits, ADC, sensors, etc.;

- Reference for wireless front-end: it generates the carrier for radio frequency (RF).

Depending on the application, the baseband reference may have different specifications. Digital circuits can tolerate inaccurate clocks, while the performance of analog circuit such as ADC/DAC may suffer from low-quality clocks. However, it can be combined with the wireless front-end frequency reference which also must show high accuracy and low noise to meet the RF modulation specifications. Although stringent performances are required for the frequency references for the baseband and wireless transmission, they do not have very tight power budget since they are not continuously required and thus can be duty-cycled.

The requirement for the RTC, which is the object of this thesis, will be discussed in the following section.

## 1.3. Motivation and objectives

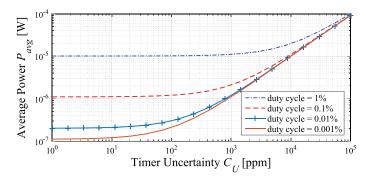

Recently, several attempts have been made to integrate oscillators on-chip, with the focus on RC-based oscillators, LC-based oscillators, MEMS (microelectromechanical systems) -based oscillators, and thermal-diffusivity (TD) -based oscillators. The ultimate goal of the integrated timing circuits is to replace crystal oscillators with integrated alternatives showing the same accuracy. However, since there is always a power-accuracy trade-off in circuit design, this may not be true for the RTC in duty-cycled IoT applications. In equation 1.1, assuming  $P_{ON} = 1$  mW,  $P_{SLP} = 100$  nW, and  $t_{ON} = 100$   $\mu$ s, figure 1.4 can be plotted showing the average IoT node power versus varying wakeup timer inaccuracy and duty cycles. As depicted in the plot, enough timer accuracy is required to reduce average power. However, for aggressive duty-cycling, the averaged system power is limited by the timer power. Therefore, it is important to find a low-power and standard CMOS compatible RTC solution with an accuracy high enough for the duty-cycling synchronization.

High timing accuracy of an RTC includes two aspects: low sensitivity to internal (i.e., process variation) and external (i.e., temperature and supply variations) changes and high long-term stability. The long-term stability indicates the performance of an oscillator due to noise over time. As an example, the frequency signal of an oscillator plotted in figure 1.5 may be considered unstable in short-term because of the noise. However, when it is used as a wakeup timer, the noise is averaged and filtered, and the resulting average value is very close to the target value. This means it shows a good long-term stability. Since the wakeup signal required by the duty-cycled node occurs with a

Figure 1.4: Average power of a duty-cycled IoT node under varying timer inaccuracy and duty cycles (reproduced from [4]).

Figure 1.5: Illustration of a long-term stable noisy frequency signal.

very long period (from several minutes up to hours or even days), the long-term stability is a more important performance metric over the short-term one.

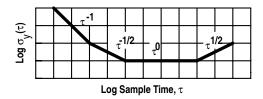

There are many figure-of-merits (FOMs) that quantify noise in oscillators, and the popular ones are phase noise, period jitter, and Allan deviation. Proposed in [6], Allan deviation is a time-domain measure of frequency instability, and its mathematical representation is given by

$$\sigma_{y}(\tau) = \sqrt{\frac{1}{2} \langle (\overline{y}_{n+1} - \overline{y}_{n})^{2} \rangle}, \tag{1.3}$$

where  $\langle \rangle$  denotes the expectation operator,  $\tau$  is the sample period, and  $\overline{y}_n$  is the *n*th fractional frequency average over  $\tau$ . An Allan deviation of  $\alpha$  over  $\tau = \beta$  should be interpreted as there being an instability in frequency between two samples  $\beta$  apart in time with a relative root mean square (rms) value of  $\alpha$ . For a good oscillator, its  $\sigma_y(\tau)$  converges to a minimum value (floor) over long enough  $\tau$ 's, and this floor indicates the long-term stability of such oscillator. Period jitter shows the deviation of a single clock period (i.e., short-term). Moreover, both period jitter and Allan deviation can be derived from phase noise, and the derivation is elaborated in appendix a. However, only the short-term stability can be evaluated from typical phase noise measurements. Since the long-term stability is important to an RTC, it is reasonable to use the Allan deviation floor as a performance metric.

Apart from the power and accuracy perspectives, RTCs with small size are preferred for cost

6 1. Introduction

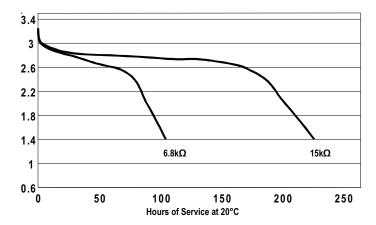

Figure 1.6: Lifetime voltage of Duracell CR1220 button battery<sup>1</sup>.

consideration. Low voltage operation is needed for interfacing with various types of energy harvesters/scavengers. In addition, as an example shown in figure 1.6, a low supply voltage also helps prolong the lifetime of battery-powered IoT nodes.

In conclusion, the RTC of the IoT node should have the following general characteristics:

- Compatible with standard CMOS processes;

- · Low-power;

- High timing accuracy;

- Able to handle low supply voltage;

- Small in chip area.

Several state-of-the-art oscillator designs will be discussed and compared in chapter 2, and the quantities of these specifications will be given in chapter 3 based on the comparison.

## **1.4.** Thesis organization

This thesis consists of six chapters. The organization of the following chapters is:

Chapter 2 reviews various fully integrated oscillator designs. Their principles and accuracies are discussed in detail. The adaptability of these approaches into an RTC is analyzed.

**Chapter 3** proposes a novel digital-intensive oscillator, which is suitable as an RTC for IoT applications. The sources of frequency inaccuracy are modeled, and methods are investigated to reduce them. With the help of the analysis, specifications of basic building blocks are derived. Circuit implementation of the proposed structure in an advanced CMOS process (TSMC 40-nm) is presented in **chapter 4**. The layout of this design is also shown at the end of the chapter.

**Chapter 5** describes the PCB of the test chip and the measurement setup. Voltage and temperature stabilities along with long-term stability are measured under different settings. The results are compared with state-of-the-art designs.

<sup>&</sup>lt;sup>1</sup>The data used in the plot is retrieved from https://www.duracell.com/en-us/techlibrary/product-technical-data-sheets?region=262&type=270.

Chapter 6 presents conclusions of the thesis and recommendations for the future work.

# Fully Integrated Time References

As mentioned in chapter 1, a fully integrated time reference required by an IoT node needs to be low-power and moderately accurate. A repetitive and regular physical phenomenon is needed in building any time reference. In the following sections, different types of integrated time references will be discussed based on their physical reference principles. Furthermore, their advantages and disadvantages for the targeted IoT application will be analyzed. In addition, several state-of-the-art low-power sleep timer designs will be reviewed.

#### 2.1. RC-based references

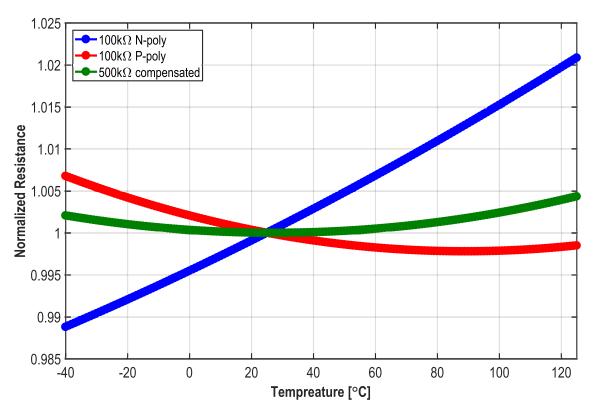

RC oscillators can be implemented as fully integrated time references. The frequency generated by such kind of references is proportional to 1/RC, which can be as low as a few kilohertz. Therefore, it is possible to achieve low power consumption. However, the frequency accuracy is limited by both the passive components and the active circuit implementation. Usually, integrated resistors and capacitors have large process variations of over 10 %, which require trimming to achieve the target frequency accuracy. Regarding the temperature stability, integrated capacitors have negligible temperature dependencies compared to those of integrated resistors. Therefore, the final temperature coefficient (TC) of the generated frequency is determined by the resistor. Luckily, resistors with both positive and negative TCs are available in most CMOS processes, which makes it possible to make first-order temperature compensated resistors by properly combining resistors with positive and negative TCs.

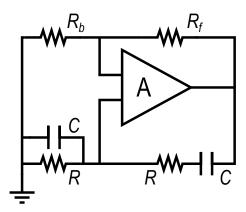

Both linear and nonlinear oscillators can be implemented as RC-based references. Linear oscillators fulfill the Barkhausen criteria for oscillation. One of the popular linear RC oscillators is the Wien-bridge oscillator shown in figure 2.1. By calculating the phase shift of the feedback network, its output frequency  $f_{out}$  can be derived as

$$f_{out} = \frac{1}{2\pi RC'},\tag{2.1}$$

where R and C are the values of the resistors and capacitors in the figure. In equation 2.1, the  $f_{out}$  is determined only by the passive components. However, the amplifier usually consumes high power. In [7], a Wien bridge oscillator is reported with a TC of 86 ppm/°C from 0 °C to 100 °C, but it also has a power consumption of 66  $\mu$ W.

Figure 2.1: Generalized block diagram of a Wienbridge oscillator.

Recently, many nonlinear RC oscillators, such as frequency-locked loop (FLL) based and relaxation oscillators, with ultra-low power consumption (smaller than 1  $\mu$ W) have been introduced [3, 4, 8–12]. Unlike their linear counterpart, the non-linear oscillators do not have to meet specific gain and phase requirements, which allows low-power design. Even though the non-sinusoidal output may limit their usage, they are still suitable as RTC in IoT. Because of such attractive characteristics, low-power designs of nonlinear RC-based oscillators will be described in details in section 2.6.

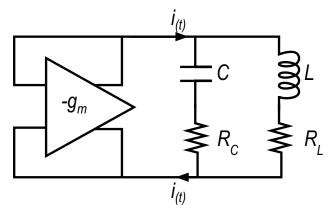

#### 2.2. LC-based references

LC oscillators are widely used in RF circuits like phase-locked loops (PLLs). A block diagram of a typical CMOS LC oscillator is shown in figure 2.2. It consists of an LC resonator tank and an active circuit, where  $R_L$  and  $R_C$  are the resistive losses of the inductor and capacitor respectively. By calculating the phase shift of the LC tank, the output frequency can be derived as

$$f = f_0 \sqrt{\frac{1 - \frac{CR_L^2}{L}}{1 - \frac{CR_C^2}{L}}} \approx f_0 \sqrt{\frac{1 - \frac{1}{Q_L^2}}{1 - \frac{1}{Q_C^2}}}.$$

(2.2)

In equation 2.2,  $f_0 = 1/(2\pi\sqrt{LC})$  is the natural frequency of the LC tank. In addition,  $Q_L = 2\pi f L/R_L$  and  $Q_C = 1/(2\pi f CR_C)$  are the quality factors of the inductor and capacitor respectively. Therefore, f only relies on the properties of passive components.

Integrated inductors have much smaller process variations compared to those of integrated capacitors, due to their large dimensions on silicon. As a result, trimming banks are usually implemented along with the capacitors. Regarding the temperature stability, both of the passive components have small TCs. However, the resistive losses show strong dependencies with temperature [1]. For most LC oscillators, the condition  $Q_C >> Q_L$  holds due to their low-enough oscillation frequencies. Thus, the losses of the inductor  $R_L$ , which determines  $Q_L$ , becomes the major source of temperature-dependent frequency drift.

In order to compensate the poor quality factor of the inductor,  $Q_L$ , a large  $g_m$  is required. Consequently, a high power consumption is needed for the active circuit. Furthermore, the temperature dependency of  $R_L$  can be compensated using various circuit techniques. In [13], an LC oscillator is proposed with constant-biased varactors to nullify the overall TC, which is reported to be

Figure 2.2: Generalized block diagram of an LC oscillator.

1.5 ppm/°C from -20 °C to 120 °C. In [14], complex trimming methods are employed to achieve a total inaccuracy of ±400 ppm over temperature (-10 °C to 85 °C) and supply changes (5 V, ±10 %). In [15], a phase shift technique is proposed, which adjusts the phase of the LC tank at a specific temperature null phase to achieve a minimized TC in the frequency. With this technique, the oscillator shows a total frequency inaccuracy of ±100 ppm across temperature (-40 °C to 85 °C), supply (3.0 V to 3.6 V) and load (0 to 15 pF) changes. Despite the high accuracy, the power of LC oscillators have is limited at the milliwatt level by the active circuit required to compensate for the lossy tank, and for the high GHz-range frequency resulting in a high power of the cascaded circuits. The high power consumption of the LC-based references makes them unsuitable as the RTC for IoT applications.

#### 2.3. TD-based references

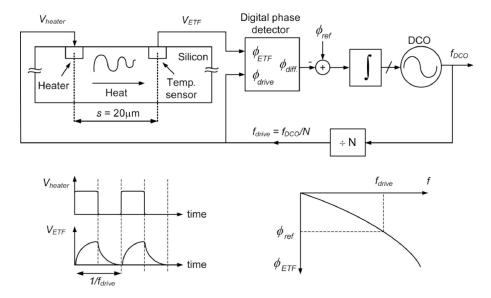

The time references mentioned earlier are all based on passive electrical components. However, the well-defined TD of IC grade silicon can also be used for frequency generation. Figure 2.3 shows a thermal-diffusivity based frequency reference, in which an FLL locks the frequency of a digitally controlled oscillator (DCO) to the process-insensitive phase shift of an electrothermal filter (ETF). The ETF consists a heater and a temperature sensor, which are close to each other (s≈20  $\mu$ m) in the same silicon substrate [16]. Driven by the DCO output signal,  $V_{heater}$ , an AC temperature variation is generated by the heater and propagate through the substrate. Sensed by the temperature sensor, the temperature gradients are converted back to an electrical signal,  $V_{ETF}$ . The digital phase detector processes the delay between  $\phi_{ETF}$  and  $\phi_{drive}$  and generates a phase delay  $\phi_{diff}$ . The delay is then compared to a phase reference  $\phi_{ref}$ , and the resulting error signal will be integrated to drive the DCO.

The FLL forces the DCO to oscillate at a frequency  $f_{DCO}$ , where  $\phi_{diff} = \phi_{ref}$ . The DCO output frequency depends on the phase-frequency characteristic of the ETF, which can be written as

$$\phi_{diff} \propto s \sqrt{\frac{f_{DCO}}{D}},$$

(2.3)

where D in the equation is the temperature-dependent thermal-diffusivity of the bulk silicon. Since the D is process-independent at typical substrate doping levels, the accuracy of  $f_{DCO}$  is mainly

Figure 2.3: Block diagram of the TD-based frequency reference (reproduced from [16]).

determined by the accuracy of lithography, which improves with scaling. The temperature dependency of  $f_{DCO}$  is set by the that of D, which is

$$D \propto \frac{1}{T^{1.8}}.\tag{2.4}$$

By substituting equation 2.4 into equation 2.3, the following equation can be derived

$$f_{DCO} \propto \frac{\phi_{ref}^2}{T^{1.8}}. (2.5)$$

Thus, for fixed values of  $\phi_{ref}$ , the resulting output frequencies are highly temperature dependent. However, since  $\phi_{ref}$  can be programmed, compensation on the output frequency can be performed by using a temperature sensor.

In [16], a temperature compensated TD-based frequency reference is proposed. It uses a temperature sensor to generate a temperature-dependent  $\phi_{ref}$ . An absolute inaccuracy of  $\pm 0.1$  % is reported for 16 samples over the military temperature range (-55 °C to 125 °C), which is good enough for demanding applications like USB. However, it draws 7.8 mW power from a 5 V supply. Even though the power can be scaled down with in more processes by reducing the ETF size, a considerable amount of power is still needed for heating up the ETF. Thus, this type of reference is not suitable for as RTC for IoT applications.

#### **2.4.** MOS-based references

It is possible to build frequency references using only MOS transistors and capacitors, such as stabilized ring oscillator [17] and mobility-based references [18, 19]. The periodic phenomenon of these references is the process of charging and discharging a capacitor between two voltages, which is similar to that of relaxation oscillators. Thus, the frequency is set by the reference voltages, the MOS current, and the capacitor value.

In [17], by adapting the bias voltages of a ring oscillator as a function of temperature, an inaccuracy of  $\pm 0.84$  % is achieved from -55 °C to 125 °C. Additional stabilization circuitry is implemented to handle process and supply voltage variations. A high power consumption of 1.5 mW is reported due to the complex biasing. The uncompensated mobility-based relaxation oscillator [18] has an output frequency proportional to  $T^{-1.6}$  with a spread in the order of 1 % after a single-point trimming. By adapting temperature compensation, an inaccuracy of  $\pm 0.5$  % over a temperature range from -55 °C to 125 °C is achieved after a two-point trim, while consuming a power of 51  $\mu$ W. Although they are low-power and show moderate accuracy, MOS-based references suffer from large temperature variations that require complex and accurate temperature compensation circuitry. Therefore, they are not suitable for ultra-low-power applications.

#### 2.5. MEMS-based references

Mechanical properties can also be used as frequency reference thanks to MEMS technology, which enables the fabrication of attaining on-chip microscale mechanical structures. Conventional high Q passives, like film bulk acoustic resonator (FBAR) filters, are not typically used due to their big sizes, but can now be integrated on-chip by micromachining. These high-Q components allow the timing and frequency generation circuit to achieve both good performance and low power consumption at the same time.

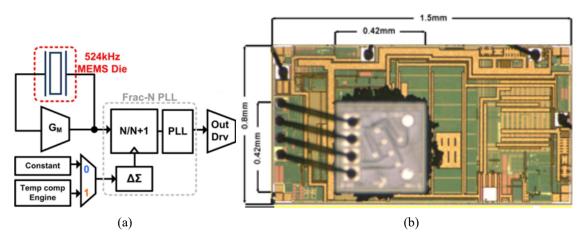

In [20], a MEMS oscillator is proposed with an H-style capacitively-transduced tuning-fork resonator and a sustaining circuit ( $G_M$ ). The MEMS resonator has a nominal Q of 52,000, which is comparable to those of crystals. Figure 2.4a shows the system level block diagram of the MEMS oscillator. A PLL is employed in the design to compensate the process variations. The MEMS oscillator itself is temperature stable thanks to the stable elastic property of the silicon. Additional temperature compensation is applied using a temperature sensor to achieve better performance at the cost of higher power. The uncompensated oscillator shows an inaccuracy of  $\pm 3$  ppm over a temperature range from -40 °C to 85 °C, consuming 1  $\mu$ A in a supply voltage rage from 1.4 V to 4.5 V.

Even though MEMS oscillators have overall the best accuracy and the lowest power consumption over integrated time references, they can only be manufactured in dedicated processes or require

Figure 2.4: (a) Block diagram of the MEMS-based frequency reference. (b) Die micrograph of the MEMS-based frequency reference. (both reproduced from [20])

special packaging techniques. Figure 2.4b shows the die micrograph of the previously mentioned MEMS oscillator. The MEMS die is flip-chip bonded to the CMOS die, and this more complex packaging with respect to traditional ICs increases both cost and production time requests in the final product. Considering that a standard CMOS compatible solution is the target of this thesis, this type of references is considered out of the scope of this work.

## **2.6.** State-of-the-art low-power references

Most of the previously discussed frequency references are characterized either by high power consumption (LC and TD) or they are not compatible with standard CMOS process (MEMS). Among the remaining references, MOS-based references suffer from large temperature variations. For those reasons, in the following, the focus will be on RC-based references. In this section, several standard CMOS compatible state-of-the-art low-power (<1  $\mu$ W) RC-based references will be described.

#### 2.6.1. Relaxation oscillators

Figure 2.5: Block diagram of a conventional relaxation oscillator.

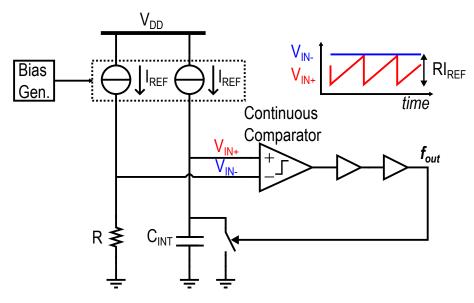

RC-based relaxation oscillators are nonlinear oscillators. Figure 2.5 shows the block diagram of a conventional relaxation oscillator. A current source constantly charges a capacitor, and a continuous comparator resets the capacitor when its voltage exceeds the reference voltage  $R \cdot I_{REF}$ . A periodic signal  $(f_{out})$  is then generated based on the capacitor charging and reset iteration, and can be expressed as

$$f_{out} = \frac{1}{RC + 2t_{delay}},\tag{2.6}$$

where  $t_{delay}$  is the delay of the comparator. In most cases, the comparator also has an input offset voltage  $V_{os}$ . Assuming  $V_{os}$  is at the negative input, the output frequency now becomes

$$f_{out} = \frac{1}{RC + V_{os}C/I + 2t_{delay}}. (2.7)$$

Besides the flaws common to all RC oscillators (described in section 2.1), the existence of the continuous comparator gives two additional problems. First, its offset voltage and delay are vulnerable to PVT changes, which may affect the frequency accuracy. Second, the flicker noise of the comparator translates into worse long-term stability [8].

To address the offset/flicker noise of the comparator, an RC relaxation oscillator using chopping technique is reported in [8]. Since the offset is sensitive to voltage and temperature changes, chopping effectively improves the TC of the output frequency. Measurement results also show lower Allan deviation floor (better long-term stability) with respect to the results without chopping. However, the delay problem cannot be solved by this technique. The conventional way to reduce the effect of the delay is to make it small enough by increasing the power consumption of the comparator and an example can be found in the oversampled comparator presented in [1]. Feed-forward frequency control scheme [9] has been introduced to address this problem. However, this architecture requires approximately two times the power and area of the original uncompensated oscillator.

The two current sources of the relaxation oscillator require extra bias generation circuitry, which increases power area overhead. Wang and Mercier [4] proposed a reference free oscillator by using the capacitive discharging process as a relative voltage reference. However, the comparator delay problem is unsolved.

Typically, the continuous comparator is the most power hungry component in the relaxation oscillator. A duty-cycling technique is introduced in [11] to save power from the comparator. It achieves an efficiency of 0.68 pJ/Cycle, while keeping good temperature and voltage stabilities. However, since its core circuit is similar to the conventional ones, it also suffers from disadvantages caused by the comparator offset/flicker noise and delay.

#### 2.6.2. FLL oscillators

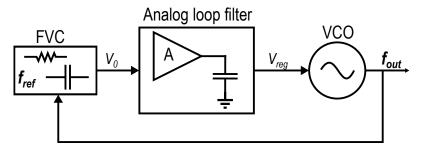

Since the accuracy of the relaxation oscillator is limited by the comparator, it is interesting to look for alternative architectures that do not suffer from this limitation. In [3, 12], low-power FLL oscillators based on the RC time constant are introduced. A general block diagram of such references is shown in figure 2.6. Instead of using a comparator to generate the periodic signal, the FLL locks its output of a voltage controlled oscillator (VCO),  $f_{out}$ , to a target frequency,  $f_{ref}$  set by the RC time constant inside a frequency-to-voltage converter (FVC). In the locking process, the analog loop filter integrates the error voltage  $V_0$  generated by the FVC, and provides the regulation voltage  $V_{reg}$  to bias the VCO. The VCO changes its  $f_{out}$  according to  $V_{reg}$  until the  $V_0$  becomes zero eventually.

Figure 2.6: Generalized block diagram of an FLL RC oscillator.

Theoretically, the  $f_{out}$  depends solely on the RC time constant  $(1/f_{ref})$ . However, any offset of the amplifier within the analog loop filter will cause  $f_{out}$  to deviate from  $f_{ref}$ . In addition to the offset, the large flicker noise of the amplifier will degrade the long-term stability. In [3], an FLL oscillator is designed with the chopping technique, which reduces the offset/flicker noise of the amplifier and improves the frequency stability consequently.

With respect to the relaxation oscillators, a bigger chip area is needed due to the loop structure compared to that of the relaxation oscillator. In [12], a switched resistor scheme is implemented in the FVC to boost the resistance, which in turn reduces the overall power consumption and chip area.

#### **2.7.** Benchmark and conclusion

The benchmark of the oscillators based on different principles [3, 4, 7, 13, 16, 19, 20] is in table 2.1.

According to the table, the MEMS oscillator has the best accuracy. However, it is not compatible with standard CMOS processes. The oscillators with low power consumption ( $<1~\mu W$ ) are RC-based. Despite the fact that the accuracies are not as good as those of the LC-based and the TD-based ones, they are still in an acceptable level [1].

Thanks to the elimination of comparator errors, the FLL-based RC oscillator [3] shows better performance than the relaxation one [4]. However, its analog-intensive circuitry requires high supply voltage. Moreover, they are not friendly to process scaling in terms of both area and required supply voltage. In the following chapter, an RC oscillator based on a digital-intensive FLL, which is able to handle low voltage operation and fully exploit the advantages of advanced CMOS processes will be introduced.

Table 2.1: Benchmark table of the integrated oscillators

| Ref. No.                                    | [3]         | [4]         | [7]        | [13]         | [16]         | [19]                 | $[20]^a$             |

|---------------------------------------------|-------------|-------------|------------|--------------|--------------|----------------------|----------------------|

| Principle                                   | RC          | RC          | RC         | ГС           | TD           | MOS                  | MEMS                 |

| Process [nm]                                | 180         | 250         | 65         | 180          | 700          | 65                   | 1                    |

| Frequency [Hz]                              | 70.4 k      | 6.4 k       | 9 W        | 2.09 G       | 1.6 M        | 20                   | 32.768 k             |

| VDD [V]                                     | 1.3         | 8.0         | 1.2        | 1.4          | 5            | 1.2                  | 1.5 - 4.5            |

| Power [W]                                   | 110 n       | 75.6 n      | п 99       | 10.9 m       | 7.8 m        | 51 µ                 | 1.5 - 4.5 μ          |

| Energy/Cycle [pJ/Cycle]                     | 1.56        | 11.81       | 11         | 5.22         | 4875         | $2.55 \times 10^{6}$ | 137.33 <sup>b</sup>  |

| Variation with                              | ±0.23       | ±0.27       |            |              |              |                      | $7.5 \times 10^{-5}$ |

| VDD [%]                                     | 1.2 - 1.8 V | V 6.0 - 9.0 | ı          | ı            | ı            | ı                    | 1.5 - 4.5 V          |

| LJ0/2007                                    | 34.3        | 148         | 98         | 1.5          | 11.2         | 55.6                 | 0.05                 |

|                                             | -40 - 80 °C | -20 - 80 °C | 0 - 100 °C | -20 - 120 °C | -55 - 125 °C | -55 - 125 °C         | -55 - 125 °C         |

| Phase Noise                                 |             |             | -94.6      | -119.4       |              |                      |                      |

| [dBc/Hz]                                    | ı           | ı           | @ 100 kHz  | @ 1M Hz      | ı            | •                    | ı                    |

| Period Jitter [s]                           | ı           | ı           | ı          | ı            | 312 p        | ı                    | ı                    |

| Allan Deviation <sup>c</sup><br>Floor [ppm] | 7 (>12 s)   | 60 (>100 s) | 1          | 1            | ı            | ~1000                | ı                    |

| Area [mm <sup>2</sup> ]                     | 0.26        | 1.08        | 0.03       | 0.158        | 6.75         | 0.2                  | 1                    |

<sup>&</sup>lt;sup>a</sup>The performance of TCXO mode is chosen.

<sup>b</sup>Worst-case value is calculated.

<sup>c</sup>A smaller Allan deviation floor indicates a better long-term stability.

# A Digital-Intensive FLL based RC Oscillator

In this chapter, the specifications on the RTC required by IoT applications will be given, based on the discussion in the previous chapters. A new digital-intensive FLL based RC oscillator which fulfills such specifications will be proposed. Its operating principle will be described, and the analysis of its frequency accuracy will be given.

## 3.1. Specifications

The target specifications of the wakeup timer are shown in table 3.1, and these specifications are derived based on the following reasons.

A 40-nm CMOS process is chosen for the timer because the other parts of the IoT node are implemented in the same technology. Although the wakeup signal usually occurs at a low frequency, the target is set to be higher than 100 kHz because it could also be used for some other blocks in the node. In addition, a supply voltage (0.8 V) lower than the nominal value (1.1 V) in the

| Specification               | Value      |

|-----------------------------|------------|

| Process [nm]                | 40         |

| Frequency [kHz]             | >100       |

| Nominal VDD [V]             | 1.1        |

| Target VDD [V]              | 0.8        |

| Line Regulation [%/V]       | ±2.5       |

| Supply Range [V]            | 0.7 - 0.9  |

| Power [µW]                  | <1         |

| TC [ppm/°C]                 | <100       |

| Temp. range [°C]            | -40 - 125  |

| Allan deviation Floor [ppm] | 20 (>100s) |

| Area [mm <sup>2</sup> ]     | < 0.1      |

Table 3.1: Target specifications of the proposed oscillator

chosen process is targeted to simplify the power management. As a low-power design, the timer should consume less than 1  $\mu$ W power. After comparing the references with different principles in the previous chapter, RC is selected as the frequency defining element to fulfill the power budget. Finally, based on the discussion of the state-of-the-art low-power designs, which is also in the previous chapter, the accuracy and area requirements are derived.

## **3.2.** Proposed architecture

With reference to the discussion in the previous chapter about the state-of-the-art low-power oscillators, it is clear that

- RC-based oscillators are preferred due to their low power consumption and capability with standard CMOS processes;

- The performance of relaxation oscillators is limited by the variations of the comparator delay due to PVT and its offset;

- FLL-based references solve the comparator issues, but they typically require analog-intensive circuitry which is not friendly to scaling and require high supply voltages.

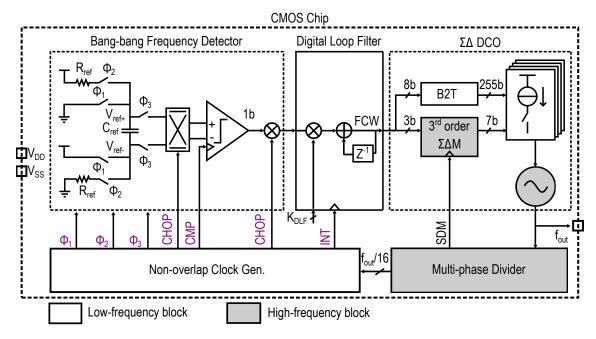

A new digital-intensive FLL based RC oscillator is proposed in figure 3.1 to handle low supply voltages and fully exploit the advantages of advanced CMOS processes. It comprises a bang-bang frequency detector (FD), a digital loop filter (DLF), a DCO and a multi-phase clock generator. Similar to the conventional FLL based RC oscillators [3, 12], the output frequency of the DCO,  $f_{out}$ , is locked to a reference frequency,  $f_{ref}$ , defined by the RC network in the FD. However, after being compared to the  $f_{ref}$ , the error ( $f_{ref} - f_{out}/n$ ) is directly converted into the digital domain, while in traditional FLL-based designs an analog loop filter processes such error. The resulting 1-bit error signal is then filtered by the low-pass function in the DLF, which generates a multi-bit frequency control word (FCW). Finally, the DCO changes its  $f_{out}$  according to the FCW until the FLL reaches its steady state.

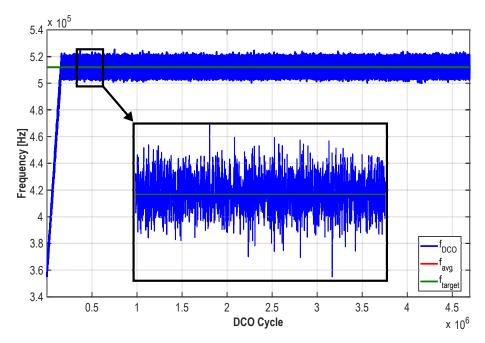

Figure 3.1: Block diagram of the proposed DFLL based RC oscillator.

Figure 3.2: Waveforms of DCO output frequency, RC network timing, and  $C_{ref}$  voltages of the DFLL under ideal steady state operation.

As illustrated in figure 3.2, under ideal DFLL steady state operation,  $f_{out}$  toggles between two least significant bits (LSBs) of the DCO (fres indicates its resolution) with a 50 % duty cycle, where its average value,  $f_{nom}$ , satisfies  $f_{nom} = N \cdot f_{ref}$ . The RC network in figure 3.1 is based on the one proposed by Lee in [21]. It consists of a floating capacitor,  $C_{ref}$ , two resistors,  $R_{ref}$ s, and three switch pairs. In order to explain its operation principle, the non-overlapping clocks  $\Phi_{1-3}$ and the voltages on  $C_{ref}$ ,  $V_{ref+}$  and  $V_{ref-}$ , are also plotted in figure 3.2. When  $\Phi_1 = 1$ ,  $C_{ref}$  is reset with  $V_{ref+} - V_{ref-} = -V_{DD}$ . During  $\Phi_2 = 1$ ,  $C_{ref}$  is discharged to  $V_{ref+} - V_{ref-} = V_{DD}$ through  $R_{ref}$ s. The final voltages on  $C_{ref}$  can be expressed as

$$V_{ref+} = V_{DD} \cdot (1 - e^{\frac{-t_{\Phi_2}}{2R_{ref}C_{ref}}}),$$

$$V_{ref-} = V_{DD} \cdot e^{\frac{-t_{\Phi_2}}{R_{ref}C_{ref}}},$$

(3.1)

$$V_{ref-} = V_{DD} \cdot e^{\frac{-t_{\Phi_2}}{R_{ref}c_{ref}}},\tag{3.2}$$

where  $t_{\Phi_2}$  is the positive half of the period of  $\Phi_2$ . When  $\Phi_3 = 1$ ,  $C_{ref}$  is connected to the comparator, and voltage difference between  $V_{ref+}$  and  $V_{ref-}$  is quantized:

$$V_{ref} = V_{ref+} - V_{ref-}$$

$$= V_{DD} \cdot (1 - 2 \cdot e^{\frac{-t_{\Phi_2}}{2R_{ref}C_{ref}}}).$$

(3.3)

With the help of the DLF, the average frequency,  $f_{nom}$ , ensures  $V_{ref} = 0$ , which means that the average value of  $t_{\Phi_2}$  is the zero-crossing time of the differential voltage  $V_{ref}$ . By solving equation 3.3 with  $V_{ref} = 0$ , this average value is given by

$$\overline{t_{\Phi_2}} = 2\ln(2)R_{ref}C_{ref}. \tag{3.4}$$

Since the condition  $t_{\Phi_2} = N/f_{out}$  is ensured by the clock generator, the average output frequency  $f_{nom}$  of the DCO will be

$$f_{nom} = \overline{f_{out}} = \frac{N}{\overline{t_{\Phi_2}}} = \frac{N}{2\ln(2)R_{ref}C_{ref}},$$

(3.5)

and thus the reference frequency defined by the network is considered to be

$$f_{ref} = \frac{1}{\overline{t_{\Phi_2}}} = \frac{1}{2\ln(2)R_{ref}C_{ref}}.$$

(3.6)

There are three main advantages of the proposed architecture over the conventional ones. First, by replacing the traditional analog loop filter with the dynamic comparator and DLF, it can handle low supply voltages. Second, implementing a large part of the system in the digital domain, this architecture can exploit the energy efficiency of digital circuits in nanometer CMOS processes. Last but not least, being a highly digital-intensive architecture, this design is intrinsically amenable to the CMOS process scaling in terms of both chip area and supply voltage.

#### 3.2.1. Small signal model

The ideal output frequency of the oscillator is described in equation 3.5. However, non-idealities such as PVT variation and noise will make the oscillation deviate from this frequency. In order to investigate the effect of noise on the long-term stability (Allan deviation floor), an s-domain linearized small signal model is described in figure 3.3 for steady state FLL operation.

In the model, the RC network is treated as a linear gain,  $K_{RC}$ . Considering the feedback frequency to the RC network,  $f = f_{out}/N$ , is in the vicinity of  $f_{ref}$  in the DFLL steady state, by calculating

Figure 3.3: Small signal model of the proposed oscillator.

the derivative of  $V_{ref}$  in equation 3.3 with respect to f,  $K_{RC}$  is given by

$$K_{RC} = \frac{dV_{ref}}{df} \bigg|_{f = f_{ref}}$$

$$= \frac{d(V_{DD} \cdot (1 - 2 \cdot e^{\frac{-t_{\Phi_2}}{2R_{ref}C_{ref}}}))}{df} \bigg|_{f = f_{ref}}$$

$$= \frac{d(V_{DD} \cdot (1 - 2 \cdot e^{\frac{-1}{2fR_{ref}C_{ref}}}))}{df} \bigg|_{f = f_{ref}}$$

$$= -\frac{\ln(2)V_{DD}}{f_{ref}}.$$

(3.7)

The comparator is replaced by a gain factor, g. For simplicity, the low-pass DLF is assumed to be an integrator, whose s-domain model is given as  $K_{DLF} \cdot f_{INT}/s$ , where  $K_{DLF}$  is the gain factor of the DLF and  $f_{INT}$  is the integration frequency. The DCO is characterized as a gain factor,  $K_{DCO}$ , and the factors  $2\pi/s$  and  $s/(2\pi)$  are used for adding the phase noise  $\phi_{DCO}$  and related frequency-to-phase and phase-to-frequency domain transfers. In addition, due to the quantization effect of the comparator, an error Q is added, and it is also related to the quantization effect of the DCO [22].

There are three main noise sources in the proposed oscillator:

- $v_{n,RC}$ , the noise of the RC network;

- $v_{n,CMP}$ , the noise of the comparator;

- $\phi_{DCO}$ , the phase noise of the DCO.

Using the model, one can calculate the transfer functions from the spectral densities of these sources to the spectral density of the output fractional frequency fluctuation,  $S_{\nu}$ , which are given by

$$v_{n,RC}$$

and  $v_{n,CMP}$ :  $\frac{S_y}{S_{v_n}} = \frac{NK_{DLF}K_{DCO}f_{INT}}{Ns + gK_{RC}K_{DLF}K_{DCO}f_{INT}};$  (3.8)

$\phi_{DCO}$ :  $\frac{S_y}{S_{\phi_{DCO}}} = \frac{Ns^2}{2\pi(Ns + gK_{RC}K_{DLF}K_{DCO}f_{INT})}.$  (3.9)

Figure 3.4: Gain plots of the noise transfer functions.

Figure 3.5: Typical spectrums of  $v_n$  and  $\phi_{DCO}$ , and their responses on  $S_y$  with the DFLL operation.

By plotting the gain of transfer functions in figure 3.4, it is clear that, for  $v_{n,RC}$  and  $v_{n,CMP}$ , they are first-order low pass filtered, whereas  $\phi_{DCO}$  is second-order high-passed filtered. Typical spectrums of  $v_n$  (including  $v_{n,RC}$  and  $v_{n,CMP}$ ) and  $\phi_{DCO}$ , and the resulting  $S_y$  with these noise spectrums under the DFLL operation is plotted in figure 3.5 using the transfer functions.

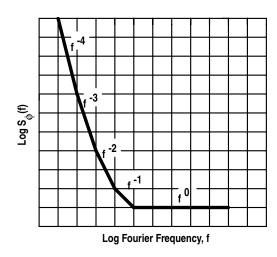

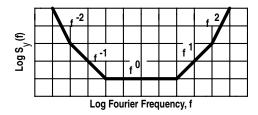

According to appendix a, only the flicker frequency modulation (FM) ( $f^{-1}$  noise process) in  $S_y$  contributes to the Allan deviation floor. In figure 3.5, this flicker FM is caused by the flicker noise ( $f^{-1}$  noise process) in the  $S_{vn}$ , and the flicker FM ( $f^{-3}$  noise process) in the  $S_{\phi DCO}$ . Since differential voltage seen by the comparator is the voltage,  $V_{ref}$ , on floating capacitor,  $C_{ref}$ , the  $v_{n,RC}$  is then given by

$$v_{n,RC} = \sqrt{\frac{kT}{C_{ref}}},\tag{3.10}$$

and it does not contribute to the flicker noise of  $S_{vn}$ . As a result, the Allan deviation floor is determined by a mix of the flicker noise of the comparator and the flicker noise of the DCO. However, this conclusion is made with the assumption that the DFLL bandwidth,  $f_p$ , equals to both the corner frequency of the  $S_{vn}$ ,  $f_{c1}$ , and the  $f^{-3}$  corner of the  $S_{\phi DCO}$ ,  $f_{c2}$ , which may not be true in real world. Moreover, the comparator gain factor in the transfer functions, g, is related to its input and output power and thus hard to estimate [23], and consequently the estimation of  $f_p$  becomes complicated. In order to investigate the contribution of the comparator and the DCO to the Allan deviation floor quantitatively, simulations are performed using a z-domain MATLAB behavior model of the DFLL (a brief description of this model can be found in appendix b).

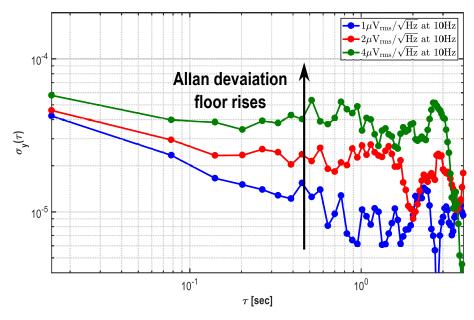

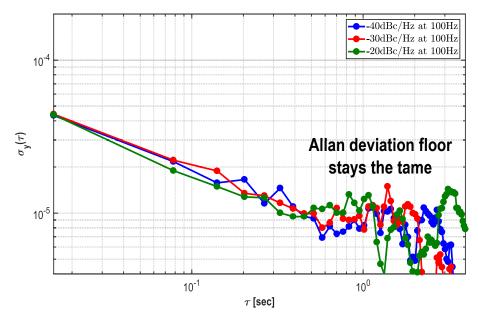

Although theoretically, the DCO flicker FM will contribute to the Allan deviation floor, MATLAB simulations in figure 3.6 and figure 3.7 show that the Allan deviation floor is dominant by the comparator flicker noise. Except the flicker noise and flicker FM, the other settings of the two simulations are the same, and they are  $V_{DD} = 0.8 \text{ V}$ ,  $R_{ref} = 5.5 \text{ M}\Omega$ ,  $C_{ref} = 4 \text{ pF}$ ,  $K_{DLF} = 1/8$ ,  $K_{DCO} = 250 \text{ Hz}$ , N = 16, and the choices of noise values of the comparator and DCO are based

Figure 3.6: Allan deviation simulations with different comparator flicker noise and the same DCO flicker FM.

Figure 3.7: Allan deviation simulations with different DCO flicker FM and the same comparator flicker noise.

on the simulated value, which will be covered in the next chapter. According to figure 3.6, the designed comparator should have a flicker noise with a value smaller than 1  $\mu$ V/ $\sqrt{\rm Hz}$  at 10 Hz to achieve the long-term stability specification (Allan deviation floor better than 20 ppm).

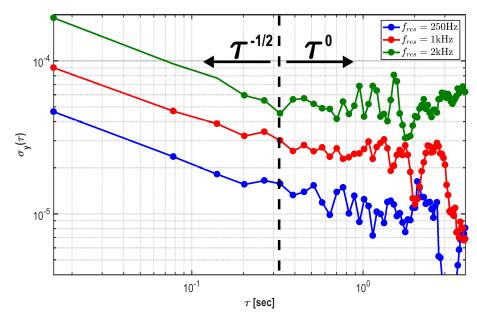

The quantization error, Q, may also affect the Allan deviation floor. Since Q is related to the DCO resolution,  $f_{res}$ , Allan deviation is simulated with varying  $f_{res}$  using the MATLAB model to show the effect of Q. Figure 3.8 shows the result, where smaller Allan deviations are achieved with finer  $f_{res}$ s. When fully randomized, the quantization energy is similar to thermal noise, and thus a finer  $f_{res}$  will result in less thermal noise energy in the output frequency. Consequently, the  $\tau^{-1/2}$  thermal noise process Allan deviation is reduced. Due to the reduced thermal noise energy,

Figure 3.8: Allan deviation simulations with different DCO resolutions and comparator flicker noise of 1  $\mu$ V/ $\sqrt{\rm Hz}$  at 10 Hz.

the input power of the comparator is also reduced. With DFLL locking, the output power of the comparator is expected to be the same, and thus g becomes larger with a smaller  $f_{res}$ . A larger g makes the low-frequency gain smaller in equation 3.8 and equation 3.9, and consequently, less flicker noise is transferred from the comparator and DCO to the output. In such a way, the Allan deviation floor also gets improved with smaller  $f_{res}$ . In order to achieve the Allan deviation floor specification (better than 20 ppm), a  $f_{res}$  of 250 Hz is required.

## **3.3.** System-level considerations

In this section, the system-level considerations for each building block are described. Specifically, the impacts of inaccuracy sources (i.e., PVT variations and noise) within each building blocks on the output frequency accuracy will be analyzed, and their solutions will be proposed.

### **3.3.1.** RC network

As mentioned in the previous chapter, both integrated resistors and integrated capacitors have large process variations. At least a one-point trim is needed at room temperature to ensure the same oscillation frequency among different samples. The range of the trimming network should be large enough to cover the variations of the RC. Meanwhile, the accuracy of the frequency after trimming depends on the resolution of the trimming network, and thus the trimming step should be small enough to achieve a high frequency accuracy.

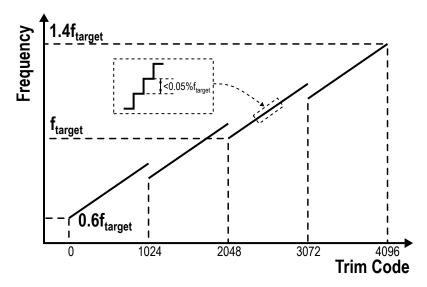

Assuming a trimming range of  $\pm 40$  % with a resolution of better than  $\pm 0.05$  % with respect to the target reference frequency is needed, building a monotonic DAC to realize such trimming network can be trivial. Therefore, as shown in figure 3.9, a 12-bit coarse-fine overlapped network can be adopted, where 10 bits are in the fine bank, and 2 bits are the in coarse bank.

After trimming, the frequency inaccuracy due to the RC network depends only on the TC. Usually,

Figure 3.9: Illustration of the RC trimming strategy using a 12-bit coarse-fine overlapped network.

Figure 3.10: Topology of a resistor using first-order temperature compensation and illustration of the TCs of the resistors before and after compensation.

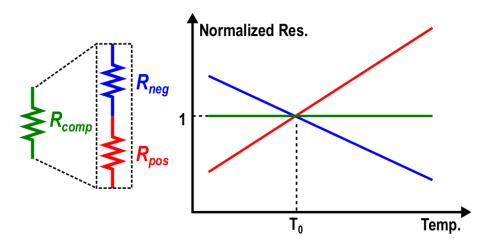

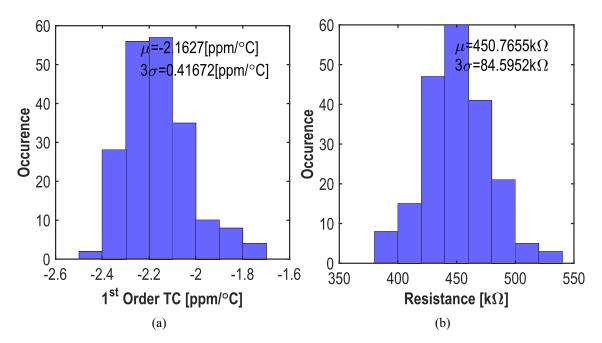

the TC of the integrated resistor is the major contributor [1]. A popular first-order temperature compensated resistor topology can be used to cancel such TC, as shown in figure 3.10. By modeling the resistance as

$$R = R_0(\alpha(T - T_0) + 1), \tag{3.11}$$

where T is the absolute temperature,  $R_0$  is the resistance at  $T_0$ , and  $\alpha$  is the TC of R. The compensated resistor can be expressed as

$$\begin{split} R_{comp} &= R_{pos} + R_{neg} \\ &= R_{pos0} (\alpha_{pos} (T - T_0) + 1) + R_{neg0} (\alpha_{neg} (T - T_0) + 1) \\ &= (R_{pos0} + R_{neg0}) (\alpha_{comp} (T - T_0) + 1). \end{split} \tag{3.12}$$

Ideally,  $\alpha_{comp}$  should be 0. However, integrated resistors have higher-order temperature dependencies, which add to the final compensated TC. Moreover, the process variations of  $R_{pos0}$  and

$\alpha_{neg}$  also make the compensation inaccurate (same conditions apply to  $R_{neg0}$  and  $\alpha_{neg}$ ) [1]:

$$|\Delta\alpha_{comp,\Delta R_{poso}}| < \frac{|\alpha_{pos}| + |\alpha_{neg}|}{2} \left| \frac{\Delta R_{poso}}{R_{poso}} \right|, \tag{3.13}$$

$$|\Delta\alpha_{comp,\Delta\alpha_{pos}}| < \frac{|\alpha_{pos}| + |\alpha_{neg}|}{2} \left| \frac{\Delta\alpha_{pos}}{\alpha_{pos}} \right|, \tag{3.14}$$

$$|\Delta \alpha_{comp,\Delta \alpha_{pos}}| < \frac{|\alpha_{pos}| + |\alpha_{neg}|}{2} \left| \frac{\Delta \alpha_{pos}}{\alpha_{pos}} \right|, \tag{3.14}$$

where  $\Delta \alpha_{comp}$  is the residual TC,  $\Delta R$  is the spread in the resistance, and  $\Delta \alpha_{pos}$  the spread in the TC. Taking into account the effect of the higher-order dependencies and the process variations, a residual TC of approximately 100 ppm/°C is expected [1].

Regarding the switches, they should have small on-state resistance and small off-state leakage, because the resistance and the current are vulnerable to PVT changes. Since these two terms are dependent on the circuit implementation, they will be covered in details in the next chapter. On the other hand, since the value of  $C_{ref}$  relatively large for kilohertz range oscillators, the charge injection of those switches is less important compared to their resistance and leakage.

### 3.3.2. Comparator

The error sources of the comparator are its offset voltage,  $V_{os}$ , and noise,  $v_{n,CMP}$ .

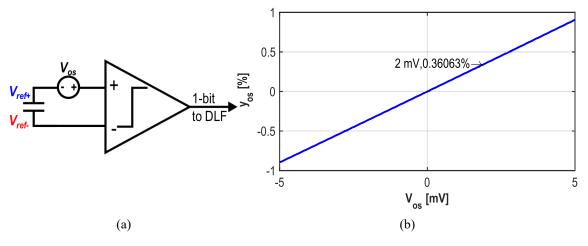

The model of the comparator with a offset voltage,  $V_{os}$ , during  $\Phi_2$  of the RC network is shown in figure 3.11a. Since  $V_{os}$  is directly added to  $V_{ref}$ , the original zero-crossing time of the differential voltage  $V_{ref}$  time will deviate. As a result, a DC frequency offset will be present on the nominal output frequency  $f_{nom}$ . The deviation and resulting frequency offset are given by

$$\overline{t_{\Phi_2, V_{os}}} = 2(\ln(2) - \ln(1 + \frac{V_{os}}{V_{DD}}))R_{ref}C_{ref}$$

(3.15)

$$\overline{t_{\Phi_2,V_{os}}} = 2(\ln(2) - \ln(1 + \frac{V_{os}}{V_{DD}}))R_{ref}C_{ref}$$

$$f_{nom,V_{os}} = \frac{N}{2(\ln(2) - \ln(1 + \frac{V_{os}}{V_{DD}}))R_{ref}C_{ref}}.$$

(3.15)

Figure 3.11: (a) Model of the comparator with a offset voltage,  $V_{os}$ , during  $\Phi_2$  of the RC network. (b) Frequency offset with varying  $V_{os}$  under ideal DFLL steady state.

Using equation 3.5 and equation 3.16, the fractional frequency offset due to  $V_{os}$  can be calculate as

$$y_{os} = \frac{f_{nom,V_{os}} - f_{nom}}{f_{nom}}$$

$$= \frac{\ln(1 + \frac{V_{os}}{V_{DD}})}{\ln(2) - \ln(1 + \frac{V_{os}}{V_{DD}})}.$$

(3.17)

With the  $V_{DD} = 0.8$  V, a  $V_{os}$  of 2 mV will cause a fractional frequency offset of 0.36 % on  $f_{nom}$ . This result also agrees with the result generated by the MATLAB behavior model shown in figure 3.11b.

In order to achieve a ensure the offset frequency due to  $V_{os}$  is better than 0.1 %, an  $V_{os}$  of better than 0.5 mV is expected. This  $V_{os}$  may not be easy to achieve. Therefore, chopping technique could be used for the comparator. By using chopping,  $V_{os}$  along with the low-frequency flicker noise is modulated to the chopping frequency and then suppressed by the low-pass dynamics of the DFLL. As a result, the frequency error due to  $V_{os}$  and the flicker noise is reduced, and the specifications on the  $V_{os}$  and the flicker noise can be lowered.

### 3.3.3. Digital loop filter

As a digital circuit, the DLF provides a low-pass function, which does not affect the frequency accuracy against PVT variations. However, the long-term stability could be changed with different gain factors,  $K_{DLF}$ s. From equation 3.8 and equation 3.9, it can be derived that a larger  $K_{DLF}$  means the more noise from the FD and less noise from the DCO will be transferred to the output, and vice versa. Although, the  $K_{DLF} = 1/8$  used in the MATLAB simulation in section 3.2.1 ensures the best Allan deviation floor with the given flicker noise sources (comparator and DCO). However, FLL-based oscillators generally have longer start-up time with respect to the relaxation ones. Such startup time can be reduced with a larger  $K_{DLF}$ . Therefore, it is good to have a configurable  $K_{DLF}$  which can be set to a large value for fast start-up and tuned for a better long-term stability when the DFLL is locked.

### **3.3.4.** Multi-phase clock generator

The clock generator divides the  $f_{out}$  by a factor of N, and feedback this frequency,  $f_{out}/N$ , to the FD. In addition, it also provides the clocks to drive other blocks, such as  $f_{INT}$ .

According to equation 3.5, any instability in *N* will make the output frequency to change proportionally. Therefore, a stable *N* is required to make the output frequency accurate against PVT changes. In reality, the clock generator can be implemented with fast digital cells, and hence it had negligible influence on the frequency accuracy.

#### 3.3.5. DCO

The frequency of a free running oscillator will deviate from its steady-state value due to PVT variations. The DFLL counteracts this effect by properly adapting the FCW of the DCO. In order to ensure locking, the frequency range of the DCO should be large enough to cover its own PVT changes.

Figure 3.12: Illustration of the frequency offset due to the DCO finite resolution.

Figure 3.13: Simulation showing reduced frequency offset due the DCO finite resolution thanks to noise.

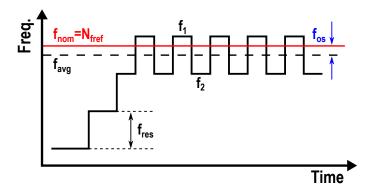

As shown in figure 3.2, the DCO toggles between its two LSBs with an average value that gives no locking error in the ideal DFLL locking case. However, in reality, there is a possibility that the DCO locks to a point where its average output frequency,  $f_{avg}$ , does not equal to the target nominal value,  $f_{nom}$ . As explained in figure 3.12, the frequency offset between the average frequency and the nominal frequency is given by

$$f_{os} = f_{nom} - f_{avg}$$

$$= Nf_{ref} - \frac{f_1 + f_2}{2}$$

$$= Nf_{ref} - f_2 - \frac{f_{res}}{2},$$

(3.18)