# Computer Engineering Mekelweg 4, 2628 CD Delft The Netherlands

The Netherlands http://ce.et.tudelft.nl/

### MSc. THESIS

## Operating system support for a dynamically reconfigurable VLIW processor

Anurag Kulkarni

#### Abstract

CE-MS-2018-21

The  $\rho$ -VEX is a dynamically reconfigurable VLIW processor, developed at TU Delft, which is capable of extracting large amounts of parallelism from applications running on it. However, without a dedicated software layer to dictate the reconfigurations, the  $\rho$ -VEX has to depend on another processor to carry out its reconfigurations meaningfully. Otherwise, this task can be left to the applications themselves, which would increase their complexity. In order to make the  $\rho$ -VEX capable of behaving as a stand-alone processor, with complex real-world applications running on it benefiting from its dynamic properties, while remaining abstract from the hardware changes, such a dedicated piece of software is needed. An operating system can equip the  $\rho$ -VEX with such functionality, as well as with other desired features like memory management support. Running applications in virtual memory is an important step towards multitasking. Therefore, the envisioned goal of this project is to make the  $\rho$ -VEX processor a truly independent and dynamic environment, capable of extracting large amounts of thread-level as well as instruction-level parallelism from programs running on it.

In this project, the Linux kernel 2.6.32 has been ported on simrvex: a cycle-accurate architectural simulator for the  $\rho$ -VEX pro-

cessor. To test the port, three benchmarks from the Powerstone benchmark suite, crc, ucbqsort and jpeg, have been chosen to run as user programs on the ported Linux kernel. The timing performance of these benchmarks for the 2-issue, 4-issue and 8-issue configurations of the  $\rho$ -VEX is also presented.

## Operating system support for a dynamically reconfigurable VLIW processor

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

EMBEDDED SYSTEMS

by

Anurag Kulkarni born in Pune, India

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

## Operating system support for a dynamically reconfigurable VLIW processor

#### by Anurag Kulkarni

#### Abstract

The  $\rho$ -VEX is a dynamically reconfigurable VLIW processor, developed at TU Delft, which is capable of extracting large amounts of parallelism from applications running on it. However, without a dedicated software layer to dictate the reconfigurations, the  $\rho$ -VEX has to depend on another processor to carry out its reconfigurations meaningfully. Otherwise, this task can be left to the applications themselves, which would increase their complexity. In order to make the  $\rho$ -VEX capable of behaving as a stand-alone processor, with complex real-world applications running on it benefiting from its dynamic properties, while remaining abstract from the hardware changes, such a dedicated piece of software is needed. An operating system can equip the  $\rho$ -VEX with such functionality, as well as with other desired features like memory management support. Running applications in virtual memory is an important step towards multitasking. Therefore, the envisioned goal of this project is to make the  $\rho$ -VEX processor a truly independent and dynamic environment, capable of extracting large amounts of thread-level as well as instruction-level parallelism from programs running on it.

In this project, the Linux kernel 2.6.32 has been ported on simrvex: a cycle-accurate architectural simulator for the  $\rho$ -VEX processor. To test the port, three benchmarks from the Powerstone benchmark suite, crc, ucbqsort and jpeg, have been chosen to run as user programs on the ported Linux kernel. The timing performance of these benchmarks for the 2-issue, 4-issue and 8-issue configurations of the  $\rho$ -VEX is also presented.

**Laboratory** : Computer Engineering

Codenumber : CE-MS-2018-21

Committee Members :

Advisor: Dr. ir. Stephan Wong, CE, TU Delft

Chairperson: Dr. ir. Stephan Wong, CE, TU Delft

Member: Dr. ir. Mottaqiallah Taouil, CE, TU Delft

Member: Dr. ir. Ioan Lager, Microelectronics, TU Delft

Dedicated to my family and friends

## Contents

| Li            | st of           | Figure       | es                                                                | vii  |

|---------------|-----------------|--------------|-------------------------------------------------------------------|------|

| $\mathbf{Li}$ | st of           | Tables       | 3                                                                 | ix   |

| $\mathbf{Li}$ | st of           | Acron        | yms                                                               | xi   |

| A             | cknov           | wledge       | ments                                                             | xiii |

|               |                 |              |                                                                   |      |

| 1             | $\mathbf{Intr}$ | oducti       | on                                                                | 1    |

|               | 1.1             | Contex       | kt                                                                | 1    |

|               |                 | 1.1.1        | Modern age computing trends                                       | 1    |

|               |                 | 1.1.2        | Multicore architectures and TLP                                   | 3    |

|               |                 | 1.1.3        | Reconfigurable Computing                                          | 4    |

|               |                 | 1.1.4        | VLIW and ILP                                                      | 4    |

|               |                 | 1.1.5        | Advantages of the $\rho$ -VEX processor                           | 5    |

|               |                 | 1.1.6        | Current trends in operating systems supporting dynamic processors | 6    |

|               | 1.2             | Motiva       | ation                                                             | 7    |

|               | 1.3             |              | ch Question, Goals and Methodology                                | 9    |

|               | 1.4             | Overvi       | ew                                                                | 10   |

| 2             | Bac             | kgrour       | nd                                                                | 13   |

|               | 2.1             | The $\rho$ - | VEX toolchain                                                     | 13   |

|               | 2.2             | The $\rho$ - | VEX processor                                                     | 14   |

|               |                 | 2.2.1        | Reconfiguration in the $\rho$ -VEX                                | 15   |

|               |                 | 2.2.2        | Configuration word encoding                                       | 16   |

|               |                 | 2.2.3        | Requesting a reconfiguration to the $\rho$ -VEX processor         | 18   |

|               |                 | 2.2.4        | The $\rho$ -VEX Instruction Set Architecture                      | 18   |

|               |                 | 2.2.5        | The concept of generic binary                                     | 20   |

|               |                 | 2.2.6        | Trap handler in the $\rho$ -VEX                                   | 20   |

|               | 2.3             |              | ex: The architectural simulator for the $\rho$ -VEX               | 22   |

|               |                 | 2.3.1        | TLB in simrvex                                                    | 23   |

|               | 2.4             |              |                                                                   | 25   |

|               |                 | 2.4.1        | The Linux kernel structure                                        | 25   |

|               |                 | 2.4.2        | Processes and threads in Linux                                    | 27   |

|               |                 | 2.4.3        | Scheduling in Linux                                               | 28   |

|               |                 | 2.4.4        | The Linux kernel's notion of time                                 | 29   |

|               |                 | 2.4.5        | The Linux boot process                                            | 29   |

|               | ~ ~             | 2.4.6        | Memory management in Linux                                        | 30   |

|               | 2.5             |              | d Work                                                            | 31   |

|               | 2.6             | Conclu       | asion                                                             | 32   |

| 3  | Por    | ting Linux to $\rho$ -VEX                                             | 35 |  |  |  |

|----|--------|-----------------------------------------------------------------------|----|--|--|--|

|    | 3.1    | Choosing the $\rho$ -VEX platform                                     | 35 |  |  |  |

|    | 3.2    | Choosing the operating system kernel for the port                     | 36 |  |  |  |

|    | 3.3    | Porting Linux on simrvex                                              | 37 |  |  |  |

|    |        | 3.3.1 Modifications to the architecture-independent part of the Linux |    |  |  |  |

|    |        | kernel                                                                | 38 |  |  |  |

|    |        | 3.3.2 The architecture-specific kernel code                           | 40 |  |  |  |

|    | 3.4    | Conclusion                                                            | 46 |  |  |  |

| 4  | Exp    | Experimentation and Results                                           |    |  |  |  |

|    | 4.1    | The Linux kernel image                                                | 47 |  |  |  |

|    |        | 4.1.1 Compressed kernel image                                         | 49 |  |  |  |

|    | 4.2    | Booting                                                               | 49 |  |  |  |

|    | 4.3    | Evaluating timing performance of benchmarks from the Powerstone       |    |  |  |  |

|    |        | benchmark suite                                                       | 53 |  |  |  |

|    | 4.4    | Thread switch latency                                                 | 57 |  |  |  |

|    | 4.5    | Conclusion                                                            | 59 |  |  |  |

| 5  | Cor    | Conclusion                                                            |    |  |  |  |

|    | 5.1    | Summary                                                               | 61 |  |  |  |

|    | 5.2    | Main contributions                                                    | 63 |  |  |  |

|    | 5.3    | Future work                                                           | 65 |  |  |  |

| Bi | ibliog | graphy                                                                | 69 |  |  |  |

## List of Figures

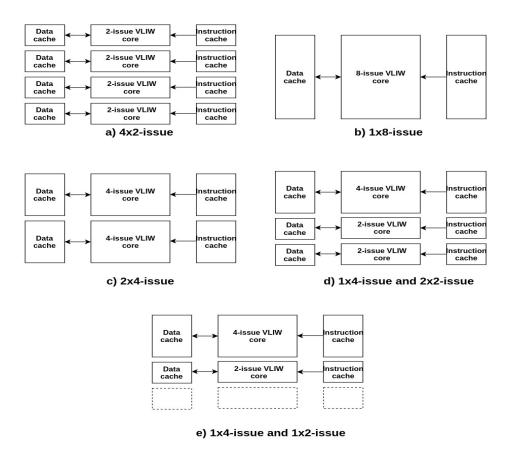

| 2.1 | Some configurations of the $\rho$ -VEX processor <sup>[1]</sup>                             | 16 |

|-----|---------------------------------------------------------------------------------------------|----|

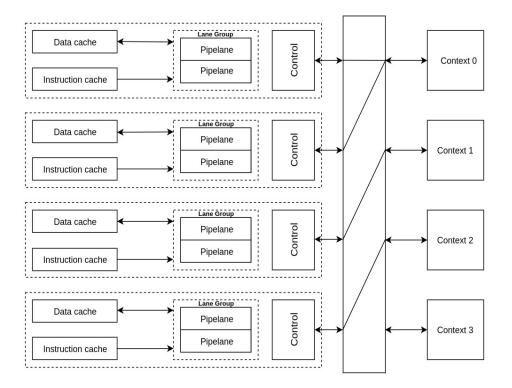

| 2.2 | A 1x4-issue and 2x2-issue configuration of the $\rho$ -VEX processor <sup>[2]</sup>         |    |

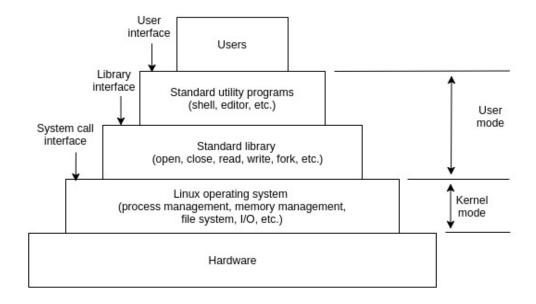

| 2.3 | The different layers of operation in a Linux-based system <sup>[3]</sup> $\dots \dots$      |    |

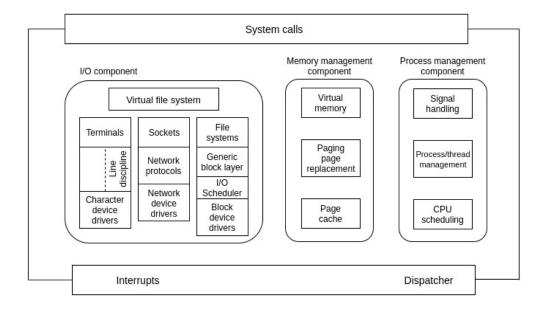

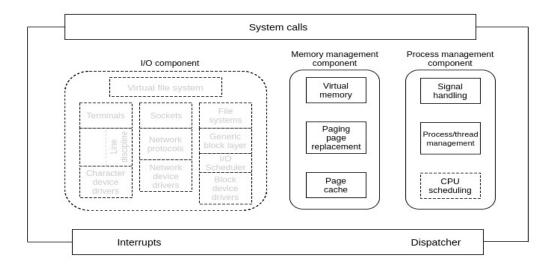

| 2.4 | The Linux kernel structure <sup>[3]</sup> $\dots \dots \dots \dots \dots \dots \dots \dots$ | 26 |

| 3.1 | Components of the Linux kernel structure that were $\mathrm{ported}^{[3]}$                  | 44 |

| 4.1 | The ELF header information for the vmlinux                                                  | 48 |

| 4.2 | The section headers inside vmlinux                                                          | 48 |

| 4.3 | The program headers inside vmlinux                                                          | 49 |

| 4.4 | The directory structure of the simple initramfs created to test the boot .                  | 51 |

| 4.5 | The Linux kernel boot logs observed on passing the kernel image to simrvex                  | 52 |

| 4.6 | Some of the kernel boot logs to show a shell can be started                                 | 53 |

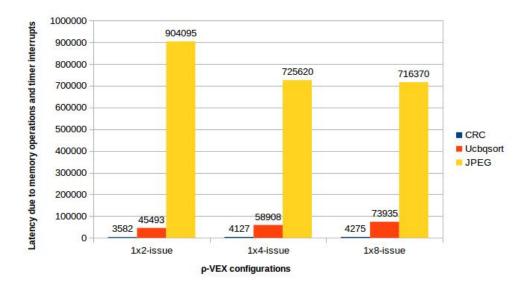

| 4.7 | Latency due to the use of Linux kernel code and virtual memory for the                      |    |

|     | three benchmarks                                                                            | 56 |

| 4.8 | Logs indicating constant thread switching between the two kernel                            |    |

|     | threads created, along with the cycle counter register values                               | 58 |

## List of Tables

| 2.1 | TLB configuration for simrvex                                                                                                        | 24 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Register translation scheme for st200 to $\rho$ -VEX <sup>[4]</sup>                                                                  | 40 |

| 4.1 | Execution cycles consumed by the benchmarks when run on Linux ported on simryex, for different configurations of simryex             | 56 |

| 4.2 | Execution cycles consumed by the benchmarks when run bare-metal on simrvex, for different configurations of simrvex                  |    |

| 4.3 | Latency in terms of percentage of increase in the execution cycle count for the three benchmarks when run on Linux ported on simrvex | 57 |

### List of Acronyms

ASIC Application Specific Integrated Circuit

BSS Block Started by Symbol

CPU Central Processing Unit

CRC Cyclic Redundancy Check

DTLB Data Translation Lookaside Buffer

**ELF** Executable and Linkable Format

FPGA Field Programmable Gate Array

**GNU** GNU's Not Unix

**GDB** GNU Debugger

**HP** Hewlett-Packard

ILP Instruction-level Parallelism

ISA Instruction Set Architecture

ITLB Instruction Translation Lookaside Buffer

JPEG Joint Photographic Experts Group

MMU Memory Management Unit

**OS** Operating System

RTOS Real-time Operating System

SASH Stand-alone Shell

**SMP** Symmetric Multiprocessing

TLB Translation Lookaside Buffer

TLP Task-level Parallelism

UTLB Unified Translation Lookaside Buffer

UNIX UNiplexed Information and Computing System

**VEX** VLIW Example

VLIW Very Long Instruction Word

### Acknowledgements

Firstly, I would like to thank my MSc. thesis supervisor, Dr. Stephan Wong, for this project opportunity, as well as for guiding me throughout the project. I would also like to thank the thesis committee members, Dr. Ioan Lager and Dr. Mottaqialla Taouil, for agreeing to invest their valuable time on the evaluation of my work.

A very special thanks to Dr. Joost Hoozemans, my guide, for his support throughout the project. I could receive his support irrespective of his work location, and I consider myself fortunate for having gained so much through his intelligence and experience. I would also like to thank Jeroen van Straten from the Computer Engineering department at TU Delft for some important  $\rho$ -VEX toolchain fixes that he provided which were required for this project.

I would like to extend my thanks to all the EWI staff members involved in conducting the thesis formalities. My friends played a very important role in keeping my motivation high, for which I would like to thank them all from the bottom of my heart.

Most importantly, I would like to thank my parents, without whose emotional and financial support I would not have been able to reach this stage, and also my brother, Aditya, for taking care of things at home while I was away.

Anurag Kulkarni Delft, The Netherlands November 12, 2018

Introduction

This thesis documents the software implementation towards providing operating system support to the  $\rho$ -VEX processor. The intention of such an implementation is to make the  $\rho$ -VEX capable of behaving as a stand-alone system running complex, real-world applications which can benefit from its dynamic reconfigurability.

While the work involved (as would be described in detail in the following chapters) would appeal most to operating system and computer architecture enthusiasts, this chapter assumes a general computer engineering target audience. It focuses on providing an overview of the topics needed to understand the project, along with the motivation behind it, and also, the research question and the ultimate goals of this graduation project.

#### 1.1 Context

The context of this project revolves around the advantages the  $\rho$ -VEX processor brings and the importance of porting an operating system to it, and will be discussed in detail in this section. We begin by discussing some modern age computing trends and a few techniques to exploit parallelism. These topics help understand the characteristics of the  $\rho$ -VEX processor that prove to be advantageous, which is discussed thereafter. Some modern operating systems which support dynamic processors will be discussed next. Together, the contents of this section would lead to understanding the motivation behind this project, discussed in Section 1.2.

#### 1.1.1 Modern age computing trends

The ever-increasing demand for computing power and reduced system size and power consumption has lead to the evolution of modern computing. Improvements that have led to such an evolution can be broadly seen targeted to the following three aspects associated with a computer design<sup>[5]</sup>:

- Computer Architecture

- Computer Organization

- Computer Realization

Computer architecture refers to the conceptual structure and behaviour of a computer system as observed by its immediate user. It deals with, for example, the instructions and arithmetic a computing system is capable of executing. The logical organization of the dataflows and controls of a computer design is called computer organization, which is also its microarchitecture. Examples can include the different types of adder

units like the Manchester Carry Chain adder, for instance. Some texts use the term computer implementation for computer organization. Basically, computer organization establishes a method to achieve a desired functionality (architecture). Computer realization is the physical structure embodying the organization or implementation. It refers to the underlying technology, e.g., CMOS. Even FPGAs are computer realizations, as after manufacture (i.e., before any functionality is implemented on them), they merely exist as configurable blocks of logic gates.

Examples of improvements targeted towards computer realization or technology may include:

- 1. Technology scaling, which enables an increase in transistor density and speed

- 2. 3D-stacked memory, which reduces wire delays and maximizes throughput, and hence speeds up memory accesses multifold

Improvements in computer organization can be brought about by implementing techniques like pipelining and multi-level caches. However, the discussion which lies under the scope of this project pertains to an improvement in computer architecture.

We are, therefore, left with considering one of the most interesting themes of research in computer engineering: exploiting parallelism in all its forms. At the application level, parallelism can exist by virtue of multiple independent data or independent tasks. Computer organization and architecture styles can exploit these two types of parallelism in the following ways<sup>[6]</sup>:

- 1. Instruction-Level Parallelism  $(ILP)^1$  deals with compile-time scheduling of instructions such that data-level parallelism is exploited. It is concerned with aspects such as pipelining, speculative execution, etc.

- 2. Vector Architectures and Graphic Processor Units (GPUs) use the single instruction multiple data (SIMD) concept, and find applications in areas like Digital Image Processing.

- 3. Thread-Level Parallelism (TLP) seeks to exploit either Task-Level or Instruction-Level Parallelism primarily through the Multiple Instructions Multiple Data (MIMD) concept. It involves identifying and executing independent "tasks" over multiple processing units. It is, hence, implied that Thread-Level Parallelism primarily focuses on multiprocessor and multicore architectures.

- 4. Request-Level Parallelism (RLP) deals with Distributed Computing which involves executing largely decoupled tasks over computer clusters with multiple servers connected to a network.

Only ILP and TLP lie within the scope of discussion of this project. The means through which they are exploited are discussed next. It should be noted here that limitations of ILP approaches directly led to the rise of multicore architectures<sup>[6]</sup>.

<sup>&</sup>lt;sup>1</sup>ILP is the potential overlap between instructions

<u>1.1. CONTEXT</u> 3

#### 1.1.2 Multicore architectures and TLP

The notion of (truly) parallel processing is not new. It is a logical solution to physically running multiple threads (tasks<sup>2</sup>) in parallel, and thus exploiting thread-level parallelism. In fact, the first parallel computers were developed in the 1960s, e.g., ILLIAC IV<sup>[7]</sup>. These were, however, difficult to program and were expensive, which limited their use to supercomputers. The 1990s saw the rise of multiprocessor systems, but these also suffered from the drawbacks of programming difficulties, cache consistency maintenance difficulties<sup>[8]</sup>, and size. The computer industry then shifted to multicore architectures. The first non-embedded multicore processor was IBM's POWER 4, which was released in 2001<sup>[9]</sup>. It featured two processor cores on a single chip, 4-bit PowerPC architecture and two cache levels.

Some of the reasons as to why multicore architectures became popular quickly were<sup>3</sup>:

- 1. The operating systems now had to manage a single memory hierarchy as the processor cores on the chip shared caches and MMUs.

- 2. Thread management was easier and so was cache synchronization.

- 3. Lesser inter-processor communication latency.

- 4. Better power performance as they can run on lower clock frequencies than a single processor, to achieve the same performance.

Of course, they are still popular in the market, with their areas of application ranging from handheld devices to super computers. The number of processor cores is often used as a selling point.

While designing a multicore processor chip, the area of application dictates the number of cores to exist on the chip and their size. According to [10], general-purpose computers benefit from a small number of large computing cores, as they have course-grained threads which depend on the instruction-level parallelism for performance. A larger number of small processors is suited for applications which exhibit a lot of thread-level parallelism<sup>4</sup>. Architectures lying in between these extremes are suited only for specific workloads for which there is a granularity match.

Another point to be considered here is that the growing popularity of multicore processors has caused a focus shift towards parallelizing programs. However, sequential (single-threaded) code still remains important, and may often be difficult to parallelize. It can be argued that asymmetric multicore processors may attempt to solve this issue by dedicating a (more) powerful core to the sequential program, but the parallel applications' performance often suffers due to this: the resources dedicated to powerful cores could be used instead for more simple (small) cores for parallel execution.

It is, therefore, desirable to have a *dynamic reconfiguration* of processor cores based on the nature of the task(s) being executed. For example, Core Fusion<sup>[11]</sup> is capable of fusing multiple cores into a larger one dynamically through reconfiguring caches and

$<sup>^2</sup>$ Tightly-coupled tasks implied here

<sup>&</sup>lt;sup>3</sup>ET4C07 Advanced Computing Systems 2017, TU Delft, Lecture 2 - Cores

<sup>&</sup>lt;sup>4</sup>Popular terminology: Bulldozers, Chainsaws and Termites

other resources. Speculative multi-threading executes different portions of a single thread in parallel on different cores<sup>[12]</sup>, and Intel's Turbo boost can dynamically change the frequency of processor cores based on their temperature<sup>[13]</sup>. Such reconfigurations can take place in microseconds<sup>[12]</sup>.

#### 1.1.3 Reconfigurable Computing

Reconfigurable computing aims to provide a balance between the flexibility of General Purpose Processors (GPPs) and the performance of ASICs. ASICs have the highest performance and consume the least power and area among the three, but they are not flexible. GPPs, on the other hand, are the most flexible due to their versatile instruction sets, but are not optimized for a particular application<sup>[14]</sup>. In the words of Andre DeHon, "Reconfigurable Computing is computing via post-fabrication, spatially programmed connection of processing element." Field-Programmable gate Arrays (FPGAs) are a popular choice for the high-speed flexible computing fabric needed to implement reconfigurable hardware. It is to be noted here that reconfigurable architecture refers to the changing functionality, and not the technology (like FPGAs).

In a way, reconfigurable computing enables controlling the underlying microarchitecture through software<sup>[5]</sup>. Reconfigurable computing itself is a vast space of computer designs with the  $\rho$ -VEX falling in the category of dynamic processors, with software being required to run on top of it. Reconfigurable hardware implementations are not discussed here. These implementations are suitable for a specific type of applications like streaming applications.

#### 1.1.4 VLIW and ILP

Another way of looking at exploiting ILP is decreasing CPI (Cycles Per Instruction), or effectively, increasing IPC (Instructions per cycle). According to [6], the CPI value for a pipelined processor can be given by:

```

Pipeline CPI = Ideal pipeline CPI + Structural stalls + Data hazard stalls + Control stalls (1)

```

The ideal pipeline CPI is a measure of the maximum performance attainable by the implementation<sup>[6]</sup>. Ideal pipeline CPI is the only relevant parameter (among those in the R.H.S. of the above equation) for discussion from a computer architecture point of view. One of the ways to decrease the ideal pipeline CPI is issuing multiple instructions per cycle. Such *multiple-issue processors* can be of the following types:

- 1. Superscalar Processors These issue varying number of instructions per cycle.

- 2. VLIW (Very Long Instruction Word) Processors These issue fixed number of instructions per cycle.

Superscalar processors can in turn be statically scheduled (compiler intelligence required) or dynamically scheduled (reliance on hardware to discover and exploit parallelism dynamically). An example of a statically scheduled superscalar processor can be ARM

Cortex A8 while Intel Core series and ARM Cortex A9 are dynamically scheduled superscalar processors<sup>[6]</sup>. VLIW processors are inherently statically scheduled.

Statically scheduled superscalar processors witness diminishing returns with increase in issue width (above  $2)^{[6]}$  and dynamically scheduled superscalar processors require complex hardware circuitry<sup>5</sup>. VLIW processors, therefore, tend to be more area and power efficient than superscalar processors<sup>6</sup>. The simplicity and mutability<sup>7</sup> of VLIW processors work in their favour to be considered for exploiting ILP over superscalars.

#### 1.1.5 Advantages of the $\rho$ -VEX processor

As discussed in Section 1.1.2, it is advantageous to have processors which can be reconfigured to change their behaviour as per the nature of the application(s) executing on them. The  $\rho$ -VEX itself is a reconfigurable processor, and exists as a softcore, but it does not involve an FPGA reconfiguration<sup>8</sup>. This means that there is no loading of a bitstream to perform partial or full reconfiguration, as is common with FPGAs. The overhead of a reconfiguration is thus equivalent to that of a pipeline flush and is of the order of 5 cycles<sup>[15]</sup>. This proves to be an advantage as FPGA reconfiguration time can be of the order of  $100 \text{ms}^{[16]}$ .

Also, the  $\rho$ -VEX is a dynamic VLIW processor, meaning, it can execute a variable number of instructions per cycle<sup>9</sup>, and this number can be decided runtime. Therefore, it combines the simplicity of VLIWs with the dynamism of superscalars. As per [8], the dynamic nature of the  $\rho$ -VEX can ease the implementation of hyperthreading. (Dynamic) Superscalars use this feature to save resources in case the program under execution has a lower ILP than predicted. For more information on hyperthreading, [17] can be referred. Specifically, the  $\rho$ -VEX processor is a (reconfigurable) VEX implementation [8]. VEX stands for VLIW Example and is a system comprising of a flexible ISA, a C compiler and a simulation system. It is introduced in [18] for the purpose of experimental use.

As per [15], the  $\rho$ -VEX can constantly adapt to the available ILP and TLP by dynamically changing the mapping between the available threads and issue slots. Thus, it can dynamically reconfigure between many small processors<sup>10</sup> (when more TLP is available), and one large processor (when more ILP is available). Such characteristics of the  $\rho$ -VEX make it a suitable candidate for research to further obtain performance gains for tasks running on it. The idea of adding an operating support to the  $\rho$ -VEX stems from the need to abstract "how and when the  $\rho$ -VEX is reconfigured to maximally exploit available parallelism, while saving resources" from the applications running on top of it. Section 1.2 describes in detail the motivation behind the OS support and the choice of the OS.

$<sup>^5</sup>$ Although the advantage is that programs need not be recompiled for processors with different degrees of parallelism

$<sup>^6{</sup>m The}$  disadvantage being recompilation requirement for processors with different instruction issue widths

<sup>&</sup>lt;sup>7</sup>The ease of morphing an existing VLIW design to a similar design

$<sup>^8\</sup>mathrm{Reconfiguration}$  mechanism is discussed in detail in Chapter 2

<sup>&</sup>lt;sup>9</sup>Number of instructions (issued) per cycle can be 2, 4 or 8; to be discussed in detail in Chapter 2

<sup>&</sup>lt;sup>10</sup>Actually, virtual cores - to be discussed in Chapter 2

### 1.1.6 Current trends in operating systems supporting dynamic processors

As discussed in Section 1.1.3, the  $\rho$ -VEX falls under the category of dynamic processors, i.e, it can change some of its properties runtime. There exist other such dynamic processors, e.g., CoreFusion<sup>[12]</sup>, which can do this. Often, it is the cores and the caches that are considered for reconfiguration. It is important that an operating system maintains its state during the reconfigurations of the processor hardware, and also is able to control such reconfigurations, for multiple reasons. Some examples of modern operating systems<sup>11</sup>, and their mechanisms, supporting such dynamic processor reconfigurations and environments are as follows:

#### 1. The Linux hotplug mechanism

Hotplugging became a standard feature in the Linux kernel from version 2.4<sup>[19]</sup>. Through the hotplug mechanism, the Linux kernel can update itself when devices are added to the processor system or removed. A classic example of such a device-level hotplug support by the Linux kernel is for USB devices. In a similar manner, Linux also supports CPU hotplugging. This means that one or more cores can be selectively disabled by the kernel, which helps in removing a dysfunctional processor or allocating processor cores from virtual machines to the host machine<sup>[12]</sup>. Hotplugging mechanisms, however, suffer from a delay of the order of 200ms while performing the activation or deactivation of a core<sup>[12]</sup>.

#### 2. The Barrelfish OS

The Barrelfish is an operating system developed from scratch at ETH Zurich, for research purposes<sup>[20]</sup>. Its development is motivated by the scalability issue faced due to the rapid increase in the number of cores, and also, the need to manage the increasing heterogeneity in computer hardware resources<sup>[21]</sup>. The Barrelfish is capable of fast coupling and decoupling of the kernel state to and from the cores, thereby resulting in a highly dynamic environment. Essentially, a lot of low-level code is populated in databases, thereby doing away with driver software, which aids in fast device interrupt rerouting and thereby resulting in fast kernel decoupling<sup>[22]</sup>. Kernel coupling and decoupling happens through dynamic booting and shutdown of cores<sup>[22]</sup>. [22] reports a 2x decrease in boot time and a 57,500x decrease in the shutdown time of a core<sup>12</sup> when compared to the hotplug mechanism in Linux kernel version 3.13.

#### 3. The Chameleon OS

An operating system support for dynamic processors is presented in [12]. The work results in an an extension to the Linux kernel which supports rapid dynamic processor reconfigurations, called Chameleon, and basically involves the following:

(a) Providing *processor proxies*, which are abstraction structures running on active processor cores, and representing offline processors. When the kernel

<sup>&</sup>lt;sup>11</sup>Kernels mostly

<sup>&</sup>lt;sup>12</sup>No load conditions

requires the presence of the processor cores for certain operations, these proxies can be helpful. The kernel, therefore, need not wait for the offline processor(s) to become active (through reconfiguration) for performing certain core-specific operations, thereby enabling fast reconfiguration.

7

- (b) Abstracting the cores through kernel structures called *execution objects*, which act as representatives of the active cores. Basically, during scheduling, these objects can be assigned to threads, while the actual dispatching to the real hardware can be done after the assignment.

- (c) Implementing a gang scheduling based technique called *cluster scheduling* in order to balance the needs of the sequential and parallel programs. Chameleons scheduler can use intelligence to decide whether to execute a thread on a single core or multiple cores via selective activation of an execution object.

[12] reports a speedup of upto 75,000 times for fusing cores (hot unplugging a CPU) and upto 160,000 times for splitting an execution object of two CPUs (hot plugging a CPU).

The  $\rho$ -VEX is a dynamic processor capable of rapid reconfigurations. Therefore, the supporting operating system should also be able to control such reconfigurations through minimum latency. Out of the kernel mechanisms discussed above, the features of the Chameleon OS are the most desirable to have as it provides the fastest reconfiguration support. Besides, it is an extension of the standard operating system kernel, Linux, which itself is modular and portable. This increases the chances of resulting in a successful port to the  $\rho$ -VEX. The Linux hotplug mechanism is too slow for the rapid runtime reconfiguration capabilities of the  $\rho$ -VEX. The Barrelfish OS is also a good option, though not as suitable as the Chameleon OS. Besides, it is an experimental operating system as of now. Also, it mainly targets heterogeneous multicore systems<sup>[21]</sup>. With these parameters taken into account, the Barrelfish OS is not the best choice for porting to the  $\rho$ -VEX processor.

#### 1.2 Motivation

An operating system running on top of the  $\rho$ -VEX processor can provide the necessary abstraction of the reconfiguration mechanism to the applications it runs. It can take care of the software state while performing configuration changes in the  $\rho$ -VEX, dynamically, to maximize parallelism exploitation. Due to this, applications meant to run on static processors can also run on the  $\rho$ -VEX, which is not possible now in case of a reconfiguration requirement. A program running on the  $\rho$ -VEX core can indeed request a reconfiguration, but in order to decide upon a suitable configuration, a lot of efforts would be required during the development of its code. Instead, intelligent algorithms can be embed into another software layer, running on the  $\rho$ -VEX, which is capable of scheduling such programs or tasks. The algorithms, for example, can monitor

the execution cycles consumed by a running task and also the NOP<sup>13</sup> instructions in its instruction stream to determine whether a task indeed benefits from a configuration. An operating system can act as this intermediate layer, and can control the reconfiguration by, for example, scheduling a reconfiguration request (as a task) after identifying the suitable configuration for a task running on the operating system. Such a mechanism can abstract:

- 1. The algorithm to determine a suitable configuration for a task running on the  $\rho$ -VEX processor.

- 2. The reconfiguration request 14 procedure.

- 3. The saving of the (software) context of a task before a reconfiguration.

- 4. Restoring the software context after the reconfiguration.

The general functions of an operating system like memory management, file system management, input/output device handling, etc. are also desirable to have. If all these functions are not provided, either the applications themselves have to take care of the hardware control and finding out a suitable configuration for themselves, or the  $\rho$ -VEX needs to behave as a co-processor, with another processor, running an OS, controlling its configurations as suited for the applications meant to run on the  $\rho$ -VEX core. In the former situation, programs meant to run on the  $\rho$ -VEX processor need to include the necessary code for hardware control, and configuration determination and reconfiguration request if runtime reconfiguration is to happen, which is not logical at all. In the latter situation, the communication latency between the main processor and the co-processor or the accelerator (here, the  $\rho$ -VEX) will affect performance of applications to a great extent.

[23] also mentions the desirability of an operating system for the  $\rho$ -VEX. While [23] reports a uCLinux variant ported on the  $\rho$ -VEX softcore, this variant of Linux is without an MMU (Memory Management Unit) support. During the time of implementation of [23], the  $\rho$ -VEX did not have an MMU. It still does not have it, but its simulator, simrvex, has this unit included. Basically, an MMU allows programs to use virtual memories and serves as a translator between virtual and physical memories. An MMU support is important for paging and preventing illegal memory accesses by processes. Every process is given its own address space, therefore, there is a protection from accesses of address spaces/secure data between processes. Each such address space is broken into fragments called pages, which give the illusion of contiguous memory. Not all the pages have to be mapped to physical memory. If a process accesses a page which is mapped to physical memory, a direct translation is provided by the MMU. However, if the page does not lie in the physical memory, an exception is triggered by the operating system, which fetches the corresponding page by evicting some other, and re-executes the failed instruction. It is also very important that the kernel address space and the user address space is maintained (and mapped) separately, which can be achieved effectively by using virtual memory. Virtual memory also allows for memory

<sup>&</sup>lt;sup>13</sup>No Operation

$<sup>^{14}</sup>$ Reconfiguration request to the  $\rho$ -VEX processor

to be swapped to an external storage, such as a disk, or a memory mapped file, thereby creating an illusion of sufficient physical memory (RAM). This is not a problem nowadays as it is common to have physical memories larger than 4GB (for systems with 32-bit address spaces, for instance) but virtual memory still makes it effective to run multiple processes simultaneously. With these advantages of using virtual memory, it becomes very much desirable to have an operating system for the  $\rho$ -VEX which supports memory management.

#### 1.3 Research Question, Goals and Methodology

The facts discussed earlier provide a good motivation to move ahead with the project implementation. However, as with any project, the goals need to be clearly defined and as this is a research-based project, a research question needs to be formulated. Our entire discussion will therefore be along the lines of the answer to this question. The long term goal of this project is:

To make the  $\rho$ -VEX capable of behaving as a stand-alone processor, with the applications running on it benefiting from its dynamic properties, while remaining abstract from the hardware changes.

However, to limit the scope of the project to that of a graduation project, the research question which this thesis intends to answer is:

How to provide operating system support to the  $\rho$ -VEX?

With an operating system support, the  $\rho$ -VEX can result in a stand-alone dynamic environment, which can maximally exploit parallelism in applications running on it. At the same time, the necessary abstraction with regard to the (dynamic) core reconfiguration mechanism can be achieved. As we already know, without an operating system, the  $\rho$ -VEX would have to depend on the programs to take care of their contexts themselves while performing core reconfigurations, or an external processor which would decide upon the reconfigurations of the  $\rho$ -VEX and run programs on it. In the latter case, the  $\rho$ -VEX would behave as a co-processor or an accelerator.

The answer to the above-stated research question involves many considerations ranging from the choice of the OS, to ensuring whether the  $\rho$ -VEX processor and the associated toolchain support it, and also the modifications in the chosen OS to make it "fit" for the  $\rho$ -VEX. Testing the implementation for the port is implicit.

It can be realized that the task requires a thorough knowledge of the  $\rho$ -VEX architecture, functionality of the chosen microarchitecture, toolchain functionality and limitations, operating system internals, boot sequence and thread creation in the  $\rho$ -VEX. Now that the focus of this project has been identified, the following project goals, along with the methodologies to achieve them, can be demarcated:

1. Porting an operating system to the  $\rho$ -VEX.

The approach to be considered to accomplish this goal would be of a multifaceted nature, and can be said to consist of the following:

- i) Choose an appropriate microarchitecture of the  $\rho$ -VEX which would act as the platform upon which the operating system will be ported.

- ii) Ensure that the toolchain is capable of supporting an operating system port.

- iii) Choose the right operating system for porting.

- iv) Implement the changes in the chosen operating system's kernel code in order to accomplish the port.

What is also desirable to achieve under this goal is the compression of the end product of the operating system kernel compilation. This would help achieve faster startup time<sup>15</sup>, apart from the reduction in the requirement of external memory for storing the kernel.

2. Evaluating performance of applications run by the operating system ported to the  $\rho$ -VEX.

The performance of applications can be evaluated by measuring the execution time taken by them while running on the OS running on the  $\rho$ -VEX processor. Appropriate infrastructure needs to be implemented to read (and naturally, output) the count of execution cycles consumed by a running application.

In order to limit the scope of this project to that of an MSc. graduation project, the above two goals have been set for the same. However, in the event of availability of further time, the following goal is highly desirable to be pursued.

Implementing modifications in the kernel as mentioned in [12] to support fast runtime reconfiguration in the  $\rho$ -VEX, thereby creating a truly dynamic environment.

The implementation for this goal together with that for the first two will help accomplish the long term goal of this project. The third goal stated above gives rise to interesting research opportunities towards development of the  $\rho$ -VEX project. Even in case of no implementation towards it, a superficial discussion alone would provide useful insights for the next project which aims to implement it.

#### 1.4 Overview

So far, the relevance of the project work has been discussed with an introductory flavour. Chapter 2 provides a detailed background of the  $\rho$ -VEX system essential to proceed

$<sup>^{15}\</sup>mathrm{In}$  most processors, the total time required to read a compressed kernel image from an external storage, decompress it and then boot it, is often less than the total time required to read the uncompressed kernel from an external storage and then boot it  $^{[24]}$ . In other words, in most processors, decompression is faster than I/O operations.

1.4. OVERVIEW

with the implementation. It discusses the study of the compiler, linker, the  $\rho$ -VEX architecture, as well as *simrvex*. Work related to this project and already been done is also discussed in Chapter 2.

Chapter 3 details the implementation of the entire project. It describes the porting in detail, including new implementations, modifications, workarounds done to achieve the goals.

Chapter 4 provides some results of the implementation, like timing performance of applications running on the ported operating system.

Chapter 5 consists of the conclusion for the entire project work, along with the main contributions towards the project. It also explains how this project lays the foundation for future work. Approaches to goal(s) not achieved are presented with the hope to provide a direction for future research.

Background

In the previous chapter, an overview of the project, along with the topics relevant to its context were discussed. This chapter discusses the concepts that are needed to be known in order to proceed with the implementation of the project. The discussion will now proceed from an introductory style to one which contains details of the topics with a higher relevance to this project.

The most important points to be analyzed while porting an operating system to a new processor is whether the processor can support it, and whether the toolchain is mature enough. Hence, we proceed with a discussion about the platform, which includes the compiler, the linker and the processor. Then, we move on to discussing the processor architecture details relevant for this project. Since porting an operating system involves modification of the source code, it is highly desirable to explore open source operating systems for the port. Linux is an open source operating system with rich documentation and online support available. As a result, the structure and organization of the Linux kernel will also be discussed in this chapter. Related work will be discussed after that. This chapter then concludes with a summary of the discussed topics to reinforce relevant concepts needed to understand the implementation presented in Chapter 3.

#### 2.1 The $\rho$ -VEX toolchain

The  $\rho$ -VEX comes with an Open64-based compiler and a GNU binutils port which comprises of the GNU Assembler and Linker modified for the  $\rho$ -VEX. This Open64-based compiler and binutils port together form part of the toolchain for the  $\rho$ -VEX<sup>1</sup>.

Open64 is an open source and GCC compatible C/C++/Fortran compiler, suitable mainly for 32-bit architectures. A compiler, based on the Open64 compiler, was developed for the Lx architecture, which was designed by HP and STMicroelectronics<sup>[25]</sup>. Lx makes use of a scalable issue width VLIW technology and is introduced in [26]. The st200 family of processors is based on this Lx architecture. The  $\rho$ -VEX compiler's front end gcc compatible, while its backend is modified to be compatible with the instruction set of the  $\rho$ -VEX processor. In common terminology, this is a port from an Open64-based compiler meant for Lx to one meant for the  $\rho$ -VEX. It is to be noted here that the compiler (and the binutils, which will be discussed shortly) for the  $\rho$ -VEX, themselves can run on x86 machines. Therefore, a cross-compilation environment can be set up on the host machine which runs Linux.

The binutils port for the  $\rho$ -VEX is the GNU binutils open source project with the target modified for the  $\rho$ -VEX. It consists of the following tools:

<sup>&</sup>lt;sup>1</sup>Actually, the  $\rho$ -VEX toolchain currently also includes a debugger (gdb modified for the  $\rho$ -VEX).

- 1. The  $\rho$ -VEX assembler (rvex-elf32-as)

- 2. The  $\rho$ -VEX linker (rvex-elf32-ld)

- 3. Elf manipulation tools like rvex-elf32-objcopy, to copy the contents of one object file to another, and rvex-elf32-objdump to display internal information of  $\rho$ -VEX specific object files

- 4. Library manipulation tools like rvex-elf32-ar and rvex-elf32-ranlib

- 5. The GNU debugger modified for the  $\rho$ -VEX (rvex-elf32-gdb)

Out of the above, only the assembler and linker will be discussed as they are visible to the programmer in the sense they are explicitly referred to in the Makefiles of the Linux kernel. The rvex-objdump is also useful while analyzing object files for the  $\rho$ -VEX as they provide valuable information as to what part of the code goes in which section (or segment) of the memory. The  $\rho$ -VEX toolchain must be capable of generating Linux kernel images as outputs (will be discussed later). But as a background study, it is very difficult to determine whether the kernel compilation will be successful using the toolchain without any modifications. Even though the compiler is Open64-based, and Open64 itself is gcc compatible and the Linux kernel also uses extensions specific to the GCC<sup>[23]</sup>, compilation and linking incompatibilities can be expected. Therefore, the tool chain was initially tested by compiling some very basic C programs (like a "Hello World" printing application) for the  $\rho$ -VEX, and then running them on simrvex, while verifying the output (of simrvex as well as the application) observed on the terminal. The errors that were expected to be encountered while compiling the entire kernel were deemed to be resolved during the implementation stage.

#### 2.2 The $\rho$ -VEX processor

The  $\rho$ -VEX adopts a 32-bit big endian architecture. It currently exists as a flexible microarchitecture<sup>[23]</sup>. It has FPGA<sup>2</sup> and ASIC<sup>3</sup> implementations, and also has *sim-rvex* as its architectural simulator. [25] provides detailed information about the  $\rho$ -VEX processor, such as registers, instruction set architecture (ISA), debugging, etc. The characteristics of the  $\rho$ -VEX that prove to be advantageous have been discussed in Chapter 1. Here, the intention is to discuss the architectural details of the  $\rho$ -VEX, which would be helpful to understand the implementation presented in Chapter 3.

As we can recall, the  $\rho$ -VEX is a dynamically reconfigurable VLIW processor. In VLIW processors, a single instruction can actually contain multiple instructions, or rather, operations. Only independent operations are allowed to lie inside a VLIW instruction. The operations are called *syllables*, and the instructions are called *bundles*, and further discussion adheres to this terminology. In the VEX architecture, upon which the  $\rho$ -VEX is based, the boundaries between bundles are specified by means of a so-called *stop bit*<sup>[25]</sup>. Therefore, the placement of this stop bit decides the size (in terms of number

<sup>&</sup>lt;sup>2</sup>ML605 and VC707 FPGA development boards<sup>[8]</sup>

<sup>&</sup>lt;sup>3</sup>Application Specific Integrated Circuit

of syllables) of the next issued bundle. If stop bits are not enabled, and if the number of syllables in a bundle comes out to be less than the configured bundle size, the compiler should place NOP (no operation) instructions to align the bundle boundary with the configuration. A configuration capable of executing n syllables per cycle is referred to as an n-way or an n-issue configuration. So, basically, reconfiguration here refers to changing such a configuration of the processor, and the reconfiguration specific to the  $\rho$ -VEX is discussed next.

#### 2.2.1 Reconfiguration in the $\rho$ -VEX

In the  $\rho$ -VEX, the distribution of the *pipelanes* between different programs running in parallel is altered during reconfiguration. Pipelanes are basically groups of computational resources which execute a syllable, and their total number is fixed<sup>[25]</sup>. They are, however, not entirely reconfigurable, in the sense, there exist groups of inseparable pipelanes, which are called *lane groups*. The pipelanes in such lane groups have to remain activated together.

To be able to run multiple programs in parallel, the  $\rho$ -VEX processor supports multiple  $contexts^4$ . As of now, the  $\rho$ -VEX supports 4 contexts (Context 0 to Context 3). Contexts are independent units with each having its own complete state, which consists of the program counter (PC), register files and other control registers. Contexts can run instructions independently are therefore very much like cores in a multicore processor, and [25] states that they can be considered as *virtual cores*. The terms *cores*, *contexts* and *virtual cores* will be used interchangeably henceforth.

Reconfiguration here involves changing the "connections" between the lane groups and the contexts. As per the current state of the  $\rho$ -VEX, the maximum number of execution pipelanes supported is 8 and the minimum number of pipelanes a lane group can consist of is two. The number of pipelanes a core is connected to is called its issue width, and such a number has to be a power of two. Therefore, some of the possible configurations of the  $\rho$ -VEX processor are: 1x8-issue, 2x4-issue, 4x2-issue, 1x4-issue and 2x2-issue. These configurations assume all contexts being activated. In fact, contexts can be deactivated by assigning no lane groups to them. Further configurations can then easily be identified. Such selective deactivation of the contexts is important for reducing power consumption, and also, the deactivated contexts can hold some extra states of the programs under execution on the active contexts, thereby enabling faster context switching. Figure 2.1 helps visualize some of the configurations of the  $\rho$ -VEX processor. As can be seen from this figure, a core of any issue width can get a cache block of appropriate size. This happens because the instruction and data cache blocks in the  $\rho$ -VEX can work together as well as independently. Also, no cache flushes are required during core reconfigurations.

As also discussed in Chapter 1, configurations with many small cores are suited for applications which exhibit a high TLP, while those with a few large cores are suited for applications with a high ILP. The word "suited", here, refers to better performance and more efficient resource utilization. The  $\rho$ -VEX processor can therefore adapt itself to a wide variety of applications.

<sup>&</sup>lt;sup>4</sup>Actually, hardware contexts

Figure 2.1: Some configurations of the  $\rho$ -VEX processor<sup>[1]</sup>

#### 2.2.2 Configuration word encoding

In order to enable certain configuration in the  $\rho$ -VEX core, an encoding needs to be written to one of its context control registers. This encoding, referred to as configuration word, should follow certain rules to result in a valid  $\rho$ -VEX configuration. The configuration word consists of 32 bits, with each nibble concerning with the context a particular lane group is mapped to. For each such nibble, the most significant bit decides whether the lane group is enabled or disabled, with the value '1' standing for disabled. However, the values 9 to F for a single nibble are reserved for future use, therefore, the value a nibble can take lies within the range 0 to 8. This leaves the last three bits of a nibble to represent the context the corresponding lane group is connected to. However, as the  $\rho$ -VEX currently supports only upto 4 contexts, the 3 least significant bits of the nibble can represent values from 0 to 3. If the nibble has a value of 8, the lane group is effectively disabled. Therefore, configuration encoding like 0x7000 is an invalid configuration. Moreover, there are some other special rules governing configuration encoding. These are listed below.

• A context can only be mapped to contiguous lane groups, and the number of such

lanes groups has to be a power of two. For example, 0x0103 is invalid, but 0x0013 is valid.

• The configuration word is of length 32 bits, which means 8 nibbles, therefore, in theory, 8 lane groups can be mapped to contexts. However, as of now, testing has been performed only for design-time configurations of upto 4 lane groups [25]. The nibbles representing non-existent lane groups should be 0. For example, for a configuration of the  $\rho$ -VEX to support 4 lane groups, 0x88888800 is invalid, whereas, the configuration 0x00008800 is valid.

Based on these rules, the configuration of the  $\rho$ -VEX can be identified via the configuration word encoding. For example, an encoding 0x8800 represents a 1x4-issue configuration, 0x0 represents a 1x8-issue configuration, and so on. Figure 2.2 helps visualize a 1x4-issue and 2x2-issue configuration of the  $\rho$ -VEX, with context 3 being deactivated. The corresponding encoding would be 0x2100. It should be noted here that a context can be deactivated by not assigning any lane group to it, and a lane group itself can be deactivated by writing an '8' to the corresponding nibble in the configuration word encoding.

Figure 2.2: A 1x4-issue and 2x2-issue configuration of the  $\rho$ -VEX processor<sup>[2]</sup>

#### 2.2.3 Requesting a reconfiguration to the $\rho$ -VEX processor

There are three ways to request a reconfiguration to the  $\rho$ -VEX processor<sup>[25]</sup>.

- Writing the configuration word to the context control register, CR\_CRR, via a program running on a context.

- Writing the configuration word to the global context control register, CR\_BCRR, via the debug bus by a program running outside the  $\rho$ -VEX core.

- Writing the configuration word to the wake-up configuration register, CR\_WCFG, and setting the appropriate flag in the sleep and wake-up control register, CR\_SAWC. These registers only exist on context 0. When an interrupt is pending on context 0 while it is not already active, reconfiguration as per the encoding occurs, provided there is no other reconfiguration request present. After the reconfiguration, the flag which was set in the CR\_SAWC is cleared, and the old configuration word in CR\_WCFG is restored. This mechanism is called reconfiguration using the sleep and wake-up system.

A new configuration commit process consumes execution cycles of the order of tens of cycles, depending upon how many cycles the reconfiguration controller hardware consumes to halt concerned contexts. A reconfiguration request may be rejected if the encoding does not follow the rules stated in Section 2.2.2, or when another such request from another core or the bus occurs simultaneously, and the arbitration is lost.

#### 2.2.4 The $\rho$ -VEX Instruction Set Architecture

The instruction set architecture of the  $\rho$ -VEX is based on the VEX architecture, which is introduced in [18]. As the  $\rho$ -VEX user manual ([25]) explains the ISA in sufficient detail, the discussion here is kept limited and only as required to understand a few parts of the implementation presented in Chapter 3.

#### Assembly syntax

The following piece of assembly code has been taken directly from [25] for illustration purposes.

```

start:

c0 stw 0x10[$r0.1] = $r0.53

c0 add $r0.3 = $r0.0, -32

c0 and $b0.2 = $r0.0, $r0.10

c0 call $10.0 = interrupt

;;

```

The first line represents a label. Labels always end in a colon. Any non-empty line which is not a label, and does not begin with a semi-colon is a syllable. The 'c0' at the beginning of each syllable represents the cluster the syllable belongs to. The  $\rho$ -VEX does not support clusters, hence specifying the cluster is optional, and if specified, it

is always cluster 0. 'Stw', 'add', etc. are opcodes. The parameter list, which can be seen following the opcodes in each line has an '=' sign. The '=' sign separates the destination on the left from the source (which provides the operands) on the right. The string immediately after the '\$' sign represents the register. The 'r', 'b', 'l', etc., stand for general-purpose, branch and link registers respectively. The types of registers in  $\rho$ -VEX will be discussed shortly. The '0' in '0.xx' specifies cluster 0, while the number following the decimal point represents the register number. There are restrictions on the usage of these numbers, heavily depending on the availability of registers. More on this can be found in [25]. The load and store instructions require a memory reference as one of their operands. A memory reference is represented in the form: literal[\$r0.index], which means, at runtime, the index is added to the value in the r0.index to generate the required address. Finally, the ';;' marks the end of a bundle. The above piece of code, therefore, is actually one complete bundle.

#### Registers

The  $\rho$ -VEX currently uses 5 types of registers, as described below.

#### 1. General-purpose registers

There are 64 32-bit general-purpose registers in the  $\rho$ -VEX core, numbered from 0 to 63. These are intended for arithmetic. Register 0 always reads a 0 when read by the processor. It is, however, also writable. Register 1 is intended to be used as a stack pointer.

#### 2. Branch registers

The  $\rho$ -VEX core contains 8 1-bit branch registers. They are labeled from 0 to 7 and are used for branch conditions, select instructions, divisions, and additions of values wider than 32 bits.

#### 3. Link registers

The  $\rho$ -VEX core contains 1 32-bit link register (l0.0), which is used to store the return address during a function call or a jump. It can also be used as the destination address for an unconditional indirect jump or call, in cases where the branch offset field is too small or when the jump target is determined at runtime.

#### 4. Global and context control registers

The global control registers contain information about the processor state which is not specific to any context. The context control registers contain status information which are specific to a context. The processor can access these register files through memory operations only. A program can only read from a global register file and can only access its own hardware context control registers.

#### 2.2.5 The concept of generic binary

A VLIW processor depends on compiler intelligence to figure out the maximum number of syllables per bundle. Also, there is a one-to-one mapping between a pipelane and a syllable in each bundle in the binary resulting after compilation for the  $\rho$ -VEX<sup>[23]</sup>. The  $\rho$ -VEX, being a VLIW processor with dynamic issue width, would then require programs to be (re-)compiled each time its configuration changes, and somehow reload the (re-)compiled programs. This would spoil the whole purpose of introducing the  $\rho$ -VEX, and the latter is actually infeasible as restoring the context of an evicted binary into the new one, compiled for a different issue width, is next to impossible.

To overcome these difficulties, the concept of generic binaries was introduced in [27]. Generic binaries are compiled for the largest possible bundle size. Also, they can be executed by  $\rho$ -VEX configurations of any issue width. For example, for a binary compiled for 8-issue configuration of the  $\rho$ -VEX, the eight syllables in a bundle can (theoretically) be run in parallel by an 8-issue core, and sequentially by a 2- and a 4-issue core in 4 and 2 steps respectively. There are, however, disadvantages to this approach, for example, the restriction that the branch instruction is placed as the last syllable in a bundle, and performance hampering [23]. But the reconfiguration flexibility gained outweighs the disadvantages by a huge margin.

#### 2.2.6 Trap handler in the $\rho$ -VEX

There are many situations in which a processor needs to pause its execution to handle another event. The nature of such an event can vary from an external interrupt to a situation which the processor cannot handle, like encountering an instruction which it cannot execute. Such events are known as traps in the  $\rho$ -VEX terminology. The ability of a processor to handle such exceptions plays an important role in deciding the capability of running an operating system. While there are various other aspects of the  $\rho$ -VEX processor architecture to be described, the trap handler is one of the most important features, hence, it is chosen to be presented in details. For other details of the  $\rho$ -VEX architecture, [25] can be referred.

We split the study here between sources of traps and the way traps are handled. The sources of traps can be categorized into the following six types<sup>[25]</sup>:

#### • Interrupts

When interrupts are enabled, and an interrupt occurs, a TRAP\_EXT\_INTERRUPT trap is generated. This trap causes the control to jump to the trap or panic handler, which has code to handle the event, like in an interrupt service routine.

#### • Faults

A fault occurs when an instruction cannot be executed for some reason. It usually leads to halting the execution altogether, except in case of a page fault.

#### • Context switch request

In order to help represent a change of a software context, two registers, CR\_RSC

(Requested software context) and CR\_CSC (Changed software context) are provided. These do not exist on context 0 and are hardwired to their equivalents on context 0.

The encoding for these registers depends on the user, provided the end result is that the memory location of the software context becomes known. When the values in these registers do not match and the context switching system is enabled by setting the C flag in CR\_CCR (the main context control register), the TRAP\_SOFT\_CTXT\_SWITCH trap is generated. After handling the context change, the trap handler routine should update CR\_CSC with the value in CR\_RSC.

#### • Debug traps

These are generated when a hardware or a software breakpoint is reached. Depending on the contents of the Debug control register, the debug traps are handled in different manners.

#### • The TRAP instruction

This instruction is used to explicitly generate a trap from a program. This is useful when a new functionality is to be implemented with the help of the trap handling mechanism.

#### • The STOP instruction

This instruction is used to halt the execution of the core altogether. On encountering this instruction, the A TRAP\_STOP trap is generated while the next execution is executing.

Usually when a trap occurs, the control jumps to the *trap handler*. A trap handler is a subroutine which contains code to handle the situation. The trap handler subroutine always ends with either a RFI (return from interrupt) or a STOP instruction. The address of the trap handler is to be stored in the CR\_TH control register by the initialization code. In most of the cases of a trap occurrence, the software is responsible for storing the state of the processor's registers. After the trap is handled, it is expected that the processor state is restored by the software and the execution is resumed from the instruction before which the trap occurred.

The  $\rho$ -VEX processor identifies a trap with the help of contents of the trap cause (CR\_TC) and trap argument (CR\_TA) control registers. The trap cause register stores an 8-bit encoding for the trap cause and the trap argument register stores a 32-bit value depending on the cause of the trap. For a complete list of encodings for the different trap causes, [25] can be referred.

Another feature worth considering here is the panic handler. A major difference between the panic handler and the trap handler is that for the former it is not expected to return to the program. In case of a trap, the control can also jump to the panic handler. The ready for trap (R) flag in the CR\_CCR register decides whether the control will jump to the trap handler or the panic handler. If the flag is set, the control jumps to the trap handler. Two such handlers are necessary to avoid loss of context for the first trap if two consecutive traps occur. The normal way of working is that the  $\rho$ -VEX clears the R flag in the CR\_CCR register upon entering the trap handler, so that the next trap is handled by the panic handler.

## 2.3 Simrvex: The architectural simulator for the $\rho$ -VEX

An architectural simulator is a software that models the behaviour of a computer such that its performance and output for a given input can be predicted<sup>[28]</sup>. Architectural simulators can be classified into different types depending on the following contexts<sup>[28]</sup>:

#### • Scope

Simulators can be microarchitectural or full system simulators (emulators). A microarchitectural simulator simulates the processor only, while a full system simulator includes I/O devices, memory, drivers, etc. into its scope apart from the processor. Full system simulators can run software meant for the real system as it is.

Microarchitectural simulators can in turn be classified into instruction set simulators and cycle accurate simulators. Instruction set simulators can simulate the behaviour of a real processor by reading instructions like the real processor and representing the registers via internal variables. Cycle accurate simulators, as the name suggests, simulate the design and behaviour of a processor at the microarchitectural level in a cycle accurate manner. The drawback is that these simulators are slow. However, they are useful for prototyping a new architecture and accurately predicting timing performance.

#### • Detail

Under this context, simulators can be classified into functional and timing simulators. These focus on simulating as accurately as possible the functionality and timing behaviour of a processor respectively.

#### • Nature of input

Simulators here can be classified into trace-driven and execution-driven simulators. Trace-driven simulators run a predetermined set of instructions with known inputs (like in a script), whereas execution-driven simulators allow for dynamic changes in instructions, depending on the nature of input.

Simrvex falls under the category of cycle accurate simulators. It was developed at TU Delft and is a heavily modified version of the architectural simulator for the st200 family of processors, with all dynamic capabilities, control registers and other characteristics implemented as per the  $\rho$ -VEX concept. It is written in C, and can run on x86 machines after being compiled using gcc. As mentioned before, the st200 family of processors is based on the Lx architecture, which is a 32-bit architecture and uses a scalable issue width VLIW technology. The architecture of st200 is therefore very much similar to the  $\rho$ -VEX architecture.

Simrvex has an MMU integrated and this component is very much similar to the one used in the st200 simulator. To be specific, in simrvex the TLB (Translation Lookaside Buffer) carries out the memory translation and protection, the way an MMU does. An operating system with memory management support is what this project intends to port, hence a study of the TLB is necessary before proceeding with the implementation. This study is presented next. Only the TLB will be discussed in the context of simrvex,

as its other characteristics are similar to the  $\rho$ -VEX processor, and have already been discussed.

#### 2.3.1 TLB in simrvex

The TLB in simrvex allows for experimenting with porting operating systems with memory management support. A TLB is like a cache for the system memory, in the sense, it stores the recent translations of virtual memory to physical memory [29]. Most systems with virtual memory support resort to paging. Usually, the mapping between the (virtual) pages and page frames, which are the corresponding physical memory units, is done by a physical structure called page table. The more the number of accesses to the page table, the lower is the performance. This is where TLB comes into picture. It is a small hardware unit usually incorporated into the (hardware) MMU[3]. A TLB consists of a small number of entries, each containing some information about a page, and most importantly, its corresponding page frame. In most cases, the program generates the virtual address while referencing a piece of memory. This address goes to the MMU for decoding, instead of directly being sent on the memory bus, the MMU first checks whether the address is available in the TLB. If yes, and if the access is valid, the TLB returns the page frame. If not, the MMU finds the page frame from the page table and places it in the TLB after evicting another entry, following certain algorithm.

It is extremely important to note here that the discussion in the paragraph about explains TLB management in hardware by the MMU, but simrvex uses a software-managed approach. It leaves the task of adding TLB entries to the operating system. Also, in case of a TLB miss, a fault is generated (page fault) to notify the operating system, which takes the necessary page frame replacement action and then re-executes the instruction which led to the fault. When the TLB is software-managed the MMU becomes much simpler, which is why the entire memory translation and protection related operations can be carried out by the t1b unit itself, in simrvex. Therefore, while referring to MMU in simrvex, we are actually referring to the t1b unit. For TLBs with sizes greater than or equal to 64 entries, the performance of a software-based TLB management approach becomes acceptable [3]. Besides, various strategies have been researched which help improve the efficiency of the software-based TLB management approaches. It is also to be noted here that in the context of simrvex, since it is a piece of software itself, a hardware component concerning the  $\rho$ -VEX is actually a piece of (C) code which emulates the hardware.

Simrvex follows the TLB implementation very much in line with the one in the st200 simulator. Therefore, the specifics related to the simrvex TLB presented are referred from the st200 instruction set architecture manual<sup>[30]</sup> and by observing the simrvex code. Simrvex uses a small instruction TLB (ITLB), a small data TLB (DTLB) and a larger unified TLB (UTLB). The ITLB performs instruction address translations, while the DTLB performs address translation for data. Both of these act as caches for the UTLB. Changes in the UTLB are not reflected in the ITLB or DTLB, however, this is untrue for the other way round. The DTLB, ITLB and TLB control registers have to arbitrate for access to the UTLB, with the priorities of accesses being in the order: TLB control registers, DTLB and then ITLB. The TLB for simrvex currently has the

following configuration, with each 'entry' being 128 bits wide.

TLB component | Number of entrices

| TLB component | Number of entries |

|---------------|-------------------|

| ITLB          | 4                 |

| DTLB          | 8                 |

| UTLB          | 64                |

Table 2.1: TLB configuration for simrvex

As the  $\rho$ -VEX has a 32-bit architecture, the virtual address space becomes  $2^{32} = 4$ Gbyte. The TLB in simrvex performs mapping between virtual and physical addresses with the help of pages of size 8KB. The TLB operation can be controlled by means of certain control registers. These control registers are not explicitly given any memory in the  $\rho$ -VEX architecture, but were accommodated (not under this project) in the unused memory space in simrvex to support the TLB. We discuss next these control registers and register flags which govern the operation of the TLB.

#### • The CCR\_TLB\_ENABLE flag

This bit, on position 10 of the main context control register (CR\_CCR), decides whether the TLB unit will be enabled or disabled. If this bit is 0 or disabled, the virtual addresses are treated as physical addresses.

## $\bullet$ The TLB\_ENTRYx registers

Here, 'x' can be 0, 1, 2 or 3. These 4 registers together can map all the 128 bits of a TLB entry.

#### • The TLB\_INDEX register

This register is, like all other registers, 32 bits wide. Only the 8 least significant bits [7:0] are used. These bits represent the entry out of the 64 UTLB entries mapped to the TLB\_ENTRYx registers.

#### • The TLB\_REPLACE register