# Circumventing Secure JTAG

# A detailed plan of attack

M.L.J. van Beusekom

# Circumventing Secure JTAG

A detailed plan of attack

by

M.L.J. van Beusekom

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Tuesday June 13, 2019 at 9:00 AM.

Student number: 4029127

Project duration: April 14, 2018 – January 15, 2019

Thesis committee: Prof. dr. ir. S. . Hamdioui, TU Delft, supervisor

M. Taouil, TU Delft S. Picek, TU Delft C. Klaver, NFI

This thesis is confidential and cannot be made public until November 13, 2021.

An electronic version of this thesis is available at http://repository.tudelft.nl/.

## **Abstract**

Forensic science is the cornerstone of the modern justice system, as it allows us to analyze evidence in order to discover the truth behind a crime scene. As mobile phones became more important to our daily lives they've taken up a bigger part in forensic research as well. These devices contain digital traces telling us the story of our lives. Digital forensic research traditionally focused on recovering data, in particular data from broken or undocumented systems. While security was not the primary concern of most manufacturers, this has changed in recent times. Cryptography has become a major roadblock in forensic science, which has shifted the focus from recovery towards exploitation.

Traditionally Digital forensic research focused on physical acquisition. While often tools supported logical extraction, this would leave many deleted traces inside of the memory chip intact. Instead methods such as Flasher tools, JTAG-based acquisition, In-System Programming and Chip-off were often used to make images of the physical contents of the memory chip. This would then be analyzed by data-analysts in order to extract evidence from the images. On many modern devices cryptography has ensured that these methods are no longer effective. Software exploitation techniques such as DirtyCow have proven to become much more important in digital forensic science, but more methods should be developed. JTAG is of particular interest in this regard. It is a testing system that was previously left unsecured and providing attackers with an easy way in. More recently manufacturers have started using novel ways of protecting JTAG from malicious use, but very little research exists testing these new security measures. This is a recipe for vulnerabilities.

This thesis focuses on attacking Secure JTAG; Samsung's authentication module for ARM CoreSight. Several potential attacks have been highlighted that are potentially applicable to Secure JTAG. A novel model has been developed that allows an attacker to evaluate the complexity of their attacks. While models such as CVSS and DREAD exist, these focus on threat analysis rather than offensive research. Using this model two attacks were chosen: One focusing on reversing the internal JTAG boundary scan chains and the other attempting to force authentication through fault injection.

In order to reverse the JTAG boundary scan chains a new set of tools had to be developed. Existing tools were often incapable of communicating with the internal scan chains or did not provide enough freedom to enable research. After their development these new tools were able to confirm that the internal scan chains were secured. The internal boundary scan chains will not be a viable attack vector until the authentication mechanism is circumvented.

The second attack focused on a potential fault injection vulnerability in the Secure JTAG authentication scheme. Because Secure JTAG is a purely hardware component it provided a unique challenge. Where normally firmware is analyzed to prove the existence of a vulnerability, Secure JTAG has no such firmware available. This makes discerning between failure because the device is not vulnerable and failure because of chance nearly impossible. To increase confidence in the attack and decrease attack space this project focused on Electromagnetic Side-channel Analysis. By locating the signals produced by Secure JTAG authentication it is possible to greatly reduce the attack space, thereby increasing confidence in the attack. In the end correlating signals were located near the high-power processor of the chip, albeit not the hashing engine itself. This lowered the attack space enough for an eventual fault injection attack.

# **Preface**

This thesis marks the end of the 12 year long adventure that was my formal education. It has been a long road with many an obstacle, but not one i've ever regretted taking.

I'd like to thank everyone involved in this project. First, of course, my supervisors for the opportunity to work on this subject. This is apparently an uncommon thing to say, but i have legitimately loved writing this thesis. I also would like to thank them for their significant support, without which this thesis would no doubt have taken significantly longer to produce.

Secondly i'd like to thank everyone at NFI for their hospitality. For sharing their enthusiasm for their work with me, and teaching me all exciting techniques in the field. Thanks to you, nothing about this thesis felt like work and every day was exciting.

Lastly of course, i want to thank my family and friends for supporting me throughout my entire study. Without you i would not have gotten where i am today.

It's an odd feeling to end my study after so long. But luckily there's many more exciting ventures ahead!

M.L.J. van Beusekom Delft, June 2019

# Contents

| 1 |       |                                        | 1      |

|---|-------|----------------------------------------|--------|

|   |       | Motivation                             | 1<br>2 |

|   | 1.2   | State of the Art                       | 2      |

|   | 1.3   | Contributions                          | 4      |

|   | 1.4   | Organization                           | 4      |

| 2 | Hard  | ware Attacks                           | 7      |

|   |       |                                        | 7      |

|   |       |                                        | 8      |

|   | 2     | 2.2.1 Chip-off                         | 8      |

|   | 2     | 2.2.2 In-System Programming            | 9      |

|   | 2     | 2.2.3 JTAG                             | 9      |

|   | 2     | 2.2.4 Side-channel Analysis            | 9      |

|   | 2.3 A | Attacks on Functionality               | 9      |

|   | 2     | 2.3.1 Microprobing                     |        |

|   | 2     | 2.3.2 Fault Injection                  |        |

|   | _     | 2.3.3 FIB Modifications                |        |

|   | 2.4 A | Attacks on IP                          |        |

|   |       | 2.4.1 Backside Imaging                 |        |

|   |       | 2.4.2 Reverse Engineering              |        |

|   |       | 2.4.3 Laser scanning                   |        |

|   | 2.5 I | Discussion                             | 1      |

| 3 |       | view of Hardware Testing mechanisms 13 |        |

|   |       | Boundary Scan Standards                |        |

|   |       | 3.1.1 IEEE 1149.1 - JTAG               |        |

|   |       | 3.1.2 IEEE 1500 - SECT                 |        |

|   |       | 3.1.3 IEEE 1687 - IJTAG                |        |

|   |       | Securing JTAG                          |        |

|   |       | Access Control                         |        |

|   |       | 3.3.1 Disabling JTAG                   |        |

|   |       | 3.3.2 Simple Lock & Key                |        |

|   |       | 3.3.3 Challenge-Response Protocol      |        |

|   |       | Masking                                |        |

|   |       | Detection of Malicious Use             |        |

|   |       | 3.5.1 Sequence filter                  |        |

|   |       | 3.5.2 Statistical Analysis             |        |

|   |       | Comparison                             |        |

| 4 | Sams  | ung Secure JTAG 23                     | 3      |

| 7 |       | Concept of Work                        | _      |

|   |       | Debug system: CoreSight                |        |

|   |       | 1.2.1 Overview                         |        |

|   |       | 1.2.2 Security                         |        |

|   |       | 1.2.3 Debug Access Port                |        |

|   |       | 1.2.4 JTAG-DP                          |        |

|   |       | 12.5 ITAG-AP                           |        |

viii Contents

|     | 4.3 Samsung Secure JTAG Implementation                         |        |

|-----|----------------------------------------------------------------|--------|

|     | 4.3.1 Overview                                                 |        |

|     | 4.3.2 SJTAG-SHA2                                               |        |

|     | 4.3.3 SJTAG-PCK                                                |        |

|     | 4.3.4 Access Controller                                        |        |

|     | 4.3.5 JTAG Detector                                            |        |

|     | 4.4 In Practice                                                |        |

| 5   | Attacks on Secure JTAG                                         | 39     |

|     | 5.1 Potential Attacks on Samsung Secure JTAG                   |        |

|     | 5.1.1 Attacks on Data                                          |        |

|     | 5.1.2 Attacks on Functionality                                 |        |

|     | 5.1.3 Attacks on IP                                            |        |

|     | 5.1.4 Discussion                                               |        |

|     | 5.2 Cost Evaluation of the attacks                             |        |

|     | 5.2.2 Attack Evaluation                                        |        |

|     | 5.3 BSC Reversing Attack                                       |        |

|     | 5.4 EM Fault Injection Attack                                  |        |

|     | 5.4.1 Potential Fault Injection Vulnerabilities in Secure JTAG |        |

|     | 5.4.2 Fault injection on Secure JTAG                           |        |

|     | 5.4.3 Side-channel analysis to locate Secure JTAG              |        |

| 6   | Validation and Result Analysis                                 | 53     |

| U   | 6.1 Platform                                                   |        |

|     | 6.1.1 Samsung Galaxy S6 (SM-G920F)                             |        |

|     | 6.1.2 Development Platform: Howchip HC7420-UFSeMM              |        |

|     | 6.1.3 CoreSight Management Script                              |        |

|     | 6.2 BSC Reversing Attack                                       |        |

|     | 6.2.1 Determining the Length of the Instruction Register       | <br>57 |

|     | 6.2.2 Validating TDO output data                               |        |

|     | 6.2.3 Discussion and Evaluation                                |        |

|     | 6.3 EM Fault Injection Attack                                  |        |

|     | 6.3.1 Triggering on Secure JTAG authentication                 |        |

|     | 6.3.2 Locating Secure JTAG                                     |        |

|     | 6.3.3 Discussion and Evaluation                                | <br>67 |

| 7   | Conclusion                                                     | 69     |

|     | 7.1 Summary                                                    |        |

|     | 7.2 Future Work                                                | <br>69 |

| Α   | Attack Evaluation Tables                                       | 71     |

| Ril | liography                                                      | 77     |

| ווע | μοβιαριίλ                                                      | , ,    |

# **Abbreviations**

ADI Arm Debug Interface. 59

ADIv5 Arm Debug Interface Version 5. 4, 25, 50

AHB Advanced High-performance Bus. 26, 40

ALU Arithmetic Logic Unit. 62, 65, 67

AP Access Port. 25-27

APB Advanced Peripheral Bus. 24, 26

AXI Advanced eXtensible Interface. 26, 40

BSC Boundary Scan Chain. 4, 5, 13–15, 17, 20, 22–24, 26, 28, 39, 40, 48–50, 53, 56–58, 69

**DAP** Debug Access Port. 23, 25–28, 38, 50, 51, 54

**DP** Debug Port. 25, 26

DR Data Register. 49, 50

EM Electro Magnetic. 8-11, 39, 51, 52, 54, 58, 60-62, 67, 70

EPROM Erasable Programmable Read-Only Memory. 10

FIB Focused Ion Beam. 11, 40, 41, 49, 69, 70

FMP Flash Memory Protector. 38

IC Integrated Circuit. 2, 4, 7–11, 15, 42, 54

IP Intellectual Property. 7, 39, 40, 69

IR Instruction Register. 56-58

ISP In-System Programming. 3, 8, 9

JTAG-AP JTAG Access Port. 28, 29

LIVA Laser Induced Voltage Alteration. 11, 69

**OBIC** Optical Beam Induced Current. 11

PLL Phase-Locked Loop. 10

SECT Standard for Embedded Core Test. 15

SJTAG Secure JTAG. 1, 4, 5, 7, 16, 17, 19, 20, 22, 23, 25, 26, 33–40, 50–54, 59–62, 64–67, 69, 70, 78, 79

**SoC** System on Chip. 3, 7–10, 15, 23, 40, 50, 52–56, 59, 61

SSS Security SubSystem. 26, 28, 38, 39, 56

TAP Test Access Port. 13, 14

# Introduction

This chapter introduces the topic of this thesis, it's importance, context, related work and contributions. Section 1.1 presents the motivation and describes the forensic context of the thesis. Section 1.2 discusses historical techniques used in Digital Forensics and presents state of the art attacks on JTAG security mechanisms. Section 1.3 Describes the main contributions of this thesis. Lastly, 1.4 lists the organization of this thesis.

#### 1.1. Motivation

Forensic science is a cornerstone of the modern justice system, as it allows us to analyze evidence in order to discover the truth behind a crime scene. As mobile phones became more important to our everyday lives they've taken up a bigger part in forensic research as well. These devices contain digital traces of our daily activities such as messaging and location history.

Digital forensic research has largely focused on recovering data, in particular recovery from broken or undocumented systems. While security was not generally the primary concern of most manufacturers, this has changed in recent times. Scandals such as the Snowden revelations [54] have underlined the importance of digital privacy for many. Manufacturers have answered this call, which has resulted in solutions such as the standard application of cryptography [21]. Cryptography has become a major roadblock to digital forensics, and has shifted the focus from recovery to exploitation.

There are three main attack vectors in order to defeat device encryption: Attacking the implementation of the cryptography, attacking the secret key of the cryptography or obtaining the key through alternative means. These vectors often have to be combined in order to stage a successful attack.

Cryptography is a difficult field and small mistakes can greatly reduce the computational complexity. By reducing the computational complexity, attacks that once took decades may be reduced to days or hours [30].

Attacking the secret key is similar in nature. While fully random keys are highly entropic and difficult to guess, human-friendly passwords are considerably simpler [13].

A lot of systems, including Android [47], combine the user key with a strong high-entropy key in order to strengthen the encryption against these kinds of attacks. This highly entropic key, commonly referred to as the hardware key, is typically stored in a secure area of the device. Obtaining the hardware key greatly simplifies cryptographic attacks by solving part of the encryption key.

There are numerous attack vectors to exploit a system. Historically, the testing mechanism known as JTAG was one such vector. JTAG is intended to be used during manufacturing in order to verify the correctness of circuits so as to minimize the shipping of defective units. Testing mechanisms like JTAG require full access to the system in order to completely test it. Full unrestricted access leads to obvious security problems [45]. Yet this mechanism was often left open after manufacturing. This enabled attackers to misuse JTAG in order to take complete control of the system. As a result, most JTAG ports are now disabled in an effort to increase device security.

Permanently disabling JTAG has a number of downsides for manufacturers, as this hinders repair and fault analysis. As such a lot of research has gone into developing novel methods to control access to the JTAG testing mechanism while remaining convenient for manufacturers to use. However, comparatively little public research exists which tests the security of these methods. This is a recipe for vulnerabilities and makes JTAG an interesting attack vector. This thesis focuses on attacking Secure JTAG (SJTAG) in order to resurrect

2 1. Introduction

JTAG as an attack vector on modern devices. Re-enabling JTAG would result in the return of a powerful tool in the forensic toolkit.

#### 1.1.1. The Forensic Process

Originating from a need for data recovery, digital forensics has become fundamental to criminal investigations. Virtually all electronic devices, such as personal computers and cellphones, contain a treasure trove of information [37]. Smartphones in particular document a person's entire life. Creating methods to extract information such as incriminating photographs or messages is of great benefit to law enforcement.

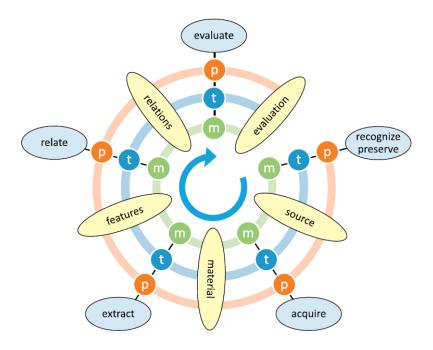

Forensic science resolves around the use of scientifically derived and proven methods throughout the following stages [6]:

- 1. **Recognition** and **Preservation** of *sources*, such as data carriers, so that potentially relevant traces may not be lost.

- 2. **Acquisition** of the raw *material* from the source, so that they may be analyzed. These include, for instance, a disk image of a hard drive.

- 3. Extraction of features from the raw material, e.g., photos and emails from a disk image.

- 4. **Relate** of the raw traces by correlating it to the known features of the relevant case. For instance, creating a graph of bitcoin transactions makes it possible to spot possible *relations* between suspects.

- 5. **Evaluation** of the results of the previous steps. Not all results are necessarily relevant to the case, and those that do should be probabilistically tested against several hypotheses.

Each of these stages has their own set of methods, tools and procedures. This is referred to as forensic knowledge, and is used to transition from each stage in the forensic process to the next. Methods comprise the knowledge and expertise required to transition from one stage and onto the next. These are based on scientific research, experiments and reverse engineering. Tools are intended to automate methods in order to make them applicable for case work. While this can include dedicated hardware and scripts for full automation, simpler tools such as a manual or a checklist also fall into this category. Lastly, procedures define how methods and tools are employed during investigations. These are typically standardized in official guidelines or ISO standards such as ISO 177025 [15].

Figure 1.1 shows forensic knowledge used to progress through each stage of the forensic process. By consistently applying and documenting all steps it's possible to maintain a chain of evidence. The ability to verify each step for correctness is critical for traces to maintain their evidentiary weight. If any part of the chain of evidence is breached, it cannot be ensured that evidence has not been tampered with thus making it inadmissible. Using forensically sound methodology as outlined above will keep evidence verifiable and admissible in court.

#### 1.2. State of the Art

Historically, forensic research on mobile devices focused purely on data recovery. Early tools mainly relied on logical extraction, leaving many deleted traces inside of the memory chip untouched [10]. This section starts by discussing traditional methods of forensic data recovery and then discusses modern pitfalls and shortcomings.

#### • Flasher Tools

Flashing used to be the easiest way to perform data extraction. Flasher tools can be connected to a device interface such as the USB port in order to extract all data. Ordinarily these are used by manufacturers or service centers in order to perform maintenance on their devices, but some are created by hacking groups in order to change the functionality of the device [10].

#### • ITAG

JTAG is a testing mechanism for Integrated Circuits (IC), which allows manufacturers to control the values of a chip's external pins. This way interconnections can be tested quickly and through a simple interface. For an attacker this level of control can be used to gain complete control of a chip and its surroundings. Flash memory chips are not typically JTAG enabled, instead they are usually connected

1.2. State of the Art

Figure 1.1: A circular graph of the forensic process [6]

to a JTAG enabled processor. An attacker can abuse the testing mechanism to gain access to the flash chip through control of the processor's external pins. JTAG itself is discussed thoroughly in Chapter 3. On modern devices the JTAG port is typically disabled, which is discussed in Chapter 4.

#### • In-System Programming

The components of a device are typically assembled and then soldered onto the motherboard. Soldering is not done by hand but rather through the use of reflow stations. These reflow stations heat the entire board which causes the solder paste to flow and subsequently attach the components to the board. Data stored on flash memory chips cannot withstand the high temperatures involved during the reflow process. To ensure correctness any data is typically written to the flash memory after manufacturing of the board. A common method is In-System Programming (ISP). This method uses test points on the PCB that allow the manufacturer to connect to the flash memory. If left enabled an attacker can search for and subsequently connect to these points in order to gain direct access to the chip. Parasitic connections to System on Chip (SoC)-memory bus can also be used for ISP based reading of memory.

#### • Chip-off

The most direct way to dump a memory chip is to physically remove it from the PCB so that it may be read using external tools. While conceptually simple, care needs to be taken not to damage either the memory chip, pcb or the data in the process [10].

On many modern devices, but smartphones in particular, using the methods above to obtain a dump of the flash memory is no longer enough. Android for instance supports full-disk encryption since version 5.0, which is enabled by default on devices that ship with Android 6.0 [21]. As such, digital forensic research has shifted more into the realm of software and hardware exploitation in order to circumvent this new layer of security. Privilege escalation attacks [18] such as DirtyCow [50] are potentially very useful tools in the digital forensic space.

Research on security of the debug system has been one-sided, focusing primarily on novel ways to secure JTAG while retaining its functionality. These have been further described in Chapter 3. Until recently, little research has been done to verify the security of these mechanisms.

Outsourcing testing to third parties is a growing trend among fabrication facilities. With this outsourcing comes the risk of IP piracy and reverse engineering. To counter this it is becoming more common to employ

4 1. Introduction

obfuscated test chains. These allow third party labs to verify correctness of the circuit without the ability to meaningfully control JTAG. In 2019 [1] proposed a novel method to counteract scan chain obfuscation by translating it into a satisfiability (SAT) problem. SAT problems are NP-complete problems for which reasonably efficient solvers exist. This allows the encryption key to be derived, thus breaking the obfuscation.

Also in 2019, [41] demonstrated the power of the ARM debug system as an attack vector on unsecured systems. The NAILGUN attack allows an attacker to run arbitrary code and obtain secured information through unsecured debug systems, effectively circumventing the protection supplied by ARM TrustZone.

#### 1.3. Contributions

The primary objective of this thesis is the circumvention of the security provided by Secure JTAG (SJTAG). Thorough analysis has been performed on various hardware attacks. Several security measures for JTAG Boundary Scan Chain (BSC) have also been analyzed including Samsung's implementation. This resulted in various tools and methods that can be used to attack SJTAG.

The main contributions of this thesis are:

#### • A classification of hardware attacks in the digital forensic attack space.

Attacks have been classified on their intended targets. Specifying whether an attack focuses on data, functionality or intellectual property results in a good overview of the digital forensic toolset for the hardware space.

#### · A classification of security measures for JTAG

JTAG security has been classified into the three major classes based on their overarching method. Each method is complemented by a discussion of a particular implementation.

#### · A new attacker focused model to judge attack complexity.

Most vulnerability models are intended for defense rather than offense. While they are excellent in evaluating a need to react, it is not suitable to choose an optimal attack vector. The model outlined in this thesis uses the existing CVSS v3 model [22] as a basis for an attacker oriented version. Usage and accuracy is demonstrated by evaluating potential SJTAG attacks with it.

#### • A framework to enable easier attacks and standardization over the debug system.

The CoreSight Management script was created in order to address shortcomings in existing tooling. Primarily it provides a powerful scripting engine and a library focused on the target device. Most importantly, it implements JTAG-AP which enables research of the JTAG BSC on Arm Debug Interface Version 5 (ADIv5) supported systems.

#### • Confirmation that the internal JTAG BSC is secured on the target device.

No security measures were described for the internal JTAG BSC. By converting existing BSC attack methodology to be applicable to the JTAG-AP interface and the creation of the appropriate tools, this thesis showed that the internal BSC is secured.

#### • A novel method to prepare the target device for fault injection.

Preparing a modern Integrated Circuit (IC) for fault injection and side-channel analysis is a challenging task. This thesis provides several methods to prepare advanced targets for these kinds of attacks.

#### • The successful application of side-channel analysis to determine key factors for fault injection.

The device under test is a complete black box, which complicates fault injection. In particular, it makes differentiating whether failure is because the device is secure or because of poor luck impossible. With side-channel analysis it was possible to determine the approximate location and timing of a fault, which greatly helps the confidence in an attack.

#### 1.4. Organization

This thesis is divided into 7 chapters. The first three chapters aim to provide the appropriate background and context for an attack on Secure JTAG (SJTAG). The fourth chapter discusses the target, SJTAG, and relevant components of the device under test. The fifth chapter evaluates several potential attacks and describes the

1.4. Organization 5

testing methodology. Chapter 6 implements the testing methodology and discusses the results. The last chapter concludes this thesis.

In detail, the remaining chapters contain the following:

#### Chapter 2: Hardware Attacks

- A classification of hardware attacks

- Mapping of existing attacks in the digital forensic space onto the classification

- Discussion of each attack to provide context for attacks.

#### Chapter 3: Overview of Hardware Testing Mechanisms

- Discussion of important boundary scan standards such as JTAG

- A classification of JTAG security measures.

- Explanation of several JTAG security measures and their mapping onto the classification

#### Chapter 4: Samsung Secure JTAG

- A detailed description of the CoreSight debug system

- Thorough explanation and discussion of SJTAG and it's components.

- Several attack vectors that are currently blocked by SJTAG.

#### Chapter 5: Attacks on Secure JTAG

- A discussion of attacks that are applicable on SJTAG

- Specification of a novel model to grade the complexity of attack vectors.

- Application and evaluation of the model on the proposed attacks.

- Attack methodology for BSC reversing attacks.

- Attack methodology for fault injection on SJTAG

- Methodology to decrease the attack space through side-channel analysis.

#### Chapter 6: Validation and Result Analysis

- A description of the attack platforms.

- Implementation and execution of the Boundary Scan Chain (BSC) reversal attack.

- A description of the trigger setup, a crucial component for side-channel analysis and fault injection.

- An overview of the various testing methodologies used to obtain results.

- Discussion and evaluation of the test methodologies

#### Chapter 7: Conclusion

- Provides a summary of the entire thesis

- Discusses future work

2

## Hardware Attacks

Hardware, as opposed to software, is uniquely vulnerable to attacks on their physical properties. Even if the logic is sound the security of a chip can often still be broken through external manipulation. For instance, the CPU can deny access to the NAND flash memory, but it won't stop a determined attacker from physically removing and reading the memory externally. This chapter covers a variety of hardware-based attacks that may prove useful in circumventing Secure JTAG (SJTAG)'s security. Section 2.1 presents a classification of hardware attacks. Sections 5.1.1, 5.1.2 and 2.4 focuses on attacks that can be performed in the field. These are grouped by attacks on data, functionality and intellectual properties, respectively. Section 5.1.4 provides a brief discussion on hardware attacks in general.

#### 2.1. Classification of Hardware Attacks

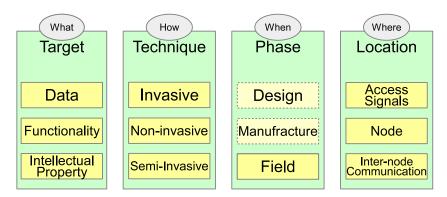

Hardware encompasses an vast amount of objects, from the smallest transistors to the largest space stations. It follows then that attacks on hardware can be performed in a myriad of ways. The attack space remains vast even when limiting attacks to System on Chips (SoC). In order to properly discuss and understand attacks in the hardware space it is necessary to classify attacks further. A useful starting point is asking four simple questions:

#### • What is being attacked?

The first question refers to the **target** of the attack. This classification observes 3 types of targets to be attacked: Intellectual Property (IP), data and functionality. Attacks may focus on the IP of an Integrated Circuit (IC) to learn more about its design. This may be used to reproduce it for financial gain. Other attacks may focus on data inside of the IC such as cryptographic keys. Attacks on the functionality of the IC focus on modifying behavior such as bypassing a password check.

#### • How is it being attacked?

This question refers to the type of **technique** used in the attack. These can be classified as invasive, non-invasive and semi-invasive [56]. Invasive attacks require the packaging of the IC to be opened so that the silicon die can be attacked directly, while non-invasive attacks do not require the packaging of the system to be removed. Semi-invasive attacks do remove the packaging but do not tamper with the silicon die otherwise.

#### • When is it being attacked?

An IC or device goes through multiple **phases** throughout its lifetime. First they are designed by the manufacturer in order to meet user demands. Next, they are manufactured at a factory according to specifications. Finally, the completed product is delivered to the end-users in the field.

Each of these phases provide an attacker with various capabilities. During the design phase, for instance, an attacker could modify the design to include a hardware trojan [7]. During the manufacturing phase certain components or secrets may be stolen to facilitate cloning and reproduction of the device [23]. Devices are typically easiest to acquire in the field, but as a result many of the attacks that are feasible during design or manufacturing phases are no longer viable. However, the lack of manufacturer

8 2. Hardware Attacks

oversight does provide an attacker with a certain degree of freedom. While the design and manufacturing processes can be tightly controlled, it is not feasible to have this level of control when the devices are in the hands of end-users.

#### Where is it being attacked?

A device consists of several components which allows attacks to be performed on several **locations**. Generally these can be classified in 3 types: Access signals, Nodes, and Inter-Node communication.

Access signals refers to the intended interfaces for the end-user, such as an USB connection. These attacks typically exploit intended operations in unintended ways. JTAG based attacks described in Section 2.2.3 are an example of this.

Nodes refers to the various components of a device, such as the SoC, memory and the internal dies. Electro Magnetic (EM) fault Injection as described in Section 2.3.2 is an example of a node-based attack.

Lastly, inter-node communication consists of the communication lines between the various nodes. For instance, the connections between the SoC and the flash memory chip. These may be used in attacks such as In-System Programming (ISP) described in Section 2.2.2.

Within the field of cyber security it's often good to study who the attacker is and why an attack is taking place. These questions focus on threat analysis rather than offensive security research. As such these questions are considered to be out of the scope of this Thesis. This classification has been summarized into Figure 2.1.

The remainder of this chapter discusses various attacks that are possible in the hardware space. Given the forensic context of this Thesis only attacks that can be executed in the field are also considered to be out of scope. The attacks will be classified by target in order to present a digital forensic tool-set rather than a full overview of hardware attacks.

Figure 2.1: Classification of attacks in the hardware space

#### 2.2. Attacks on Data

Attacks on data focus on retrieving secrets from inside of the Integrated Circuit (IC) or modifying data in order to alter functionality. It could be argued that attacks on data that alter functionality should be classified as an attack on functionality. However, as the IC is still functioning as designed these attacks are treated as a side-effect of data manipulation.

#### 2.2.1. Chip-off

Chip-off attacks are conceptually very simple. Systems often require some kind of non-volatile memory chip in order to store persistent data. A chip-off attack removes this chip and accesses it through external means [9]. In practice there are a lot of variables to consider such as the protocol used in the chip, its connections or its physical properties. For example, a chip may not retain its data at the temperatures required to desolder it. While the manufacturing process of modern systems has made it more difficult to perform chip-off attacks, the primary obstacle is the application of cryptography. Encrypted data cannot be interpreted or modified in a meaningful way without breaking the cryptography.

#### 2.2.2. In-System Programming

During manufacturing of the IC flash chips will be put into a reflow oven in order to solder the components onto the PCB. Data consistency cannot be guaranteed when exposed to the conditions of the reflow process, so any programming must be done after assembly. In-System Programming (ISP) is a method used by manufacturers to provide connection points to be able to program and test flash memory. From an attacker's context these same points can be used to read and modify the flash memory. The effects of this attack are similar to chip-off attacks, but have the advantage that the chip does not need to be removed.

#### 2.2.3. JTAG

Testing whether all components are assembled onto the board correctly is crucial for the manufacturer in order to minimize defective units shipped. It is generally cheaper to intercept defective units during production, compared to the costs of shipping and replacing a defective item. Testing efficiently can increase profits and customer satisfaction [5].

In order to be able to detect faults many ICs are designed for testing and include specialized testing hardware. The most popular hardware testing standard is JTAG, which is discussed in more detail in Chapter 3. In order to properly test the ICs the testing hardware needs to have full access and control over the chip. An attacker can exploit the testing hardware to gain full control and thus extract or modify any data contained within the IC [8].

In the past access to the testing hardware used to be completely open, which made the testing hardware an excellent point of attack. These days manufacturers have caught on to these attacks and have started securing the testing hardware. As such it is generally no longer a viable attack vector. The security measures are further discussed in 3.

It should also be noted that JTAG can also be used to attack functionality. In forensic context it is commonly used as a data extraction tool, which is why it has been categorized as an attack on data.

#### 2.2.4. Side-channel Analysis

When an IC performs an operation it will usually generate some side-effect. Analyzing these side-effects and using them to learn more about the operation is the essence of side-channel analysis.

The simplest form of side-channel attacks are one dimensional and only measure time. These are also referred to as timing attacks. Timing attacks hinge on the concept that one branch of a program does not have the same execution time as another branch. For instance, an incorrect character during a password check may terminate execution immediately. Conversely, a correct character would progress further into the operation, thus resulting in a different execution time. This information can be used to distinguish correct characters in a password, thus greatly reducing time-complexity when brute-forcing. A more powerful application of this attack would be to derive the private key of an ECC cryptosystem [11]. To prevent these kinds of attacks the designer needs to take care to make processing time of all branches indistinguishable.

Similar analysis can be done by measuring power consumption over time, thus making the attack two-dimensional. These are referred to as power analysis attacks. A device's power consumption is dependent on the number of state changes of its transistors [56]. By analyzing the power spikes it becomes possible to distinguish persistent values used in computations such as the carry bit during shift operations. There have been various attacks on cryptosystems using both Simple Power-Analysis (SPA) [44] and Differential Power Analysis (DPA) [28]. In SPA the power consumption is directly interpreted by an attacker, while in DPA statistical analysis is used to detect small differences in power consumption.

A third side channel attack is through electromagnetic analysis. Electronic devices such as microchips leak Electro Magnetic (EM) radiation[19]. Like with power analysis, the amount of radiation changes when a CMOS gate changes states. By positioning an antenna over the IC it's possible to analyze the changes in radiation. This is especially interesting for System on Chips (SoC) as the location of the antenna is correlated to the components located inside of the SoC. Take note that this adds a spatial dimension, making it a three-dimensional side-channel attack.

#### 2.3. Attacks on Functionality

These types of attacks focus on temporarily altering the behavior of the Integrated Circuit (IC) through external means. As noted in Section 5.1.1 it is possible to alter the behavior of the device by altering the data. However, as this is still correct behavior of the IC these attacks fall outside of the realm of attacks on functionality. Instead, attacks on functionality focus on generating incorrect behavior of the IC in order to reach a

10 2. Hardware Attacks

desired outcome. For instance, forcing a password check to report an incorrect result may lead an attacker to be authenticated using an invalid password. Incorrect behavior may lead to access or modification of data. This is considered to be a side-effect of attacks on functionality and is not classified as attacks on data.

#### 2.3.1. Microprobing

Microprobing used to be an incredibly important attack [56]. It an attack on the intercommunication of the die. To gain access to these signals the die has to be exposed by decapsulating the IC. By also removing the passivation layer the internal connection lines become accessible. Using a microscope and small probing needles it's possible to connect to these lines. This allows an attacker to either eavesdrop on the chip or to inject signals. Due to the increased complexity and reduced size of modern ICs these attacks are becoming extremely hard.

#### 2.3.2. Fault Injection

ICs are designed to operate within given specifications such as a certain voltage level or clock rate. Correct operation cannot be guaranteed when operating an IC outside of its specification. This is the essence of all fault injection attacks [56]. By briefly running the system outside of the specifications it is possible to generate an error in a way beneficial to an attacker. Password checks, for instance, could be skipped over completely.

There are several methods of fault injection, each with their own properties. These are discussed in the rest of this section

#### 2.3.2.1. UV Attacks

UV attacks is one of the older variants of fault injection and a bit different to the other fault injection attacks covered in this chapter. It is an attack specific to Erasable Programmable Read-Only Memory (EPROM) chips. EPROM chips are erased when exposed to UV light after which they can be reprogrammed. Rewritable EPROM chips have a small window in the IC for this purpose. This window can be used to expose the memory to UV light. Some manufacturers use EPROM as one time programmable memory by removing the window. An attacker can expose the die once more through decapsulation, allowing it to be erased with UV light once more [56]. By exposing only part of the die to UV light it is even possible to target specific bits for erasure. This can for instance be used to remove important security bits without erasing critical data.

#### 2.3.2.2. Clock Glitching

A processor is designed to run at a given clock speed so that it can be ensured operations are completed before the next clock tick. By briefly raising the clock speed past its specification it is possible to introduce errors during execution. This happens, because an instruction has not yet been loaded into the cache from memory in time for processing. There exist many more potential failures, but these failures can often be modeled as skipped instructions. These attacks are referred to as glitching attacks [56]. Modern System on Chips (SoC) are typically no longer vulnerable to clock glitching due to the application of Phase-Locked Loops (PLL). PLLs are designed to absorb jitter in order to produce a stable frequency. This causes them to absorb a glitch which makes clock glitching ineffective.

#### 2.3.2.3. Voltage glitching

Voltage glitching [56] is very similar to clock glitching. An IC is designed to operate within a certain voltage range. When briefly underpowering an IC it can, for instance, no longer be guaranteed that every CMOS gate transistions states correctly. This causes errors that can generally be modeled to skipped instructions. Alternatively, by supplying too much power to the IC it is possible to create floating signals which can similarly lead to errors. Caution needs to be taken when supplying too much voltage, as it is easy to cause permanent damage.

#### 2.3.2.4. Electro Magnetic Fault Injection

Strong Electro Magnetic (EM) fields are known to affect operation of electronic circuits. By using a coil to apply a high energy EM pulse it is possible to generate a fault on a specific location in the IC [16]. Similar to other techniques employed this causes transistors to enter an unintended state, thus leading to skipped instructions. EM fault attacks are interesting because they can be applied directly to a critical area of an IC or SoC without opening the chip. This makes it a more targeted attack than Clock and Voltage glitching.

2.4. Attacks on IP

#### 2.3.2.5. Optical Fault injection.

Optical fault injection is similar to EM fault injection. Silicon is sensitive to light and transistors will start conducting when exposed to a powerful light source [57]. By decapsulating the IC it is possible to fire a laser onto the die. This makes an attack considerably more accurate than EM fault injection. It is even possible to flip specific values of a register using these techniques [56]. However, this accuracy is also to its detriment. Modern ICs are very dense, which makes finding the appropriate attack position considerably harder than when using EM attacks.

#### 2.3.3. FIB Modifications

Connecting to the internal connection lines is harder as the fabrication technology gets smaller, and will need more sophisticated tools. A Focused Ion Beam (FIB) workstation is one of the best tools for technologies smaller than  $0.5~\mu m$  [56]. Similar to an electron microscope, it uses accelerated gallium ions to create an image at a resolution of as low as 2.5~nm. However, unlike an electron microscope a FIB can be used to add and remove chip material. This allows an attacker to modify a chip's behavior by modifying the circuit. For instance, a line dedicated to monitoring security could be connected to either the ground or the supply line, thus forcing it into a specific state.

#### 2.4. Attacks on IP

Attacks on intellectual properties are normally executed in order to make a profit. For instance by learning about the design of an Integrated Circuit (IC) it's possible to replicate it and sell it. Another example is faking the design of a cheap product to look like its expensive counterpart. These attacks on IP do not typically apply to a forensic context, but some methods can be used in order to learn more about the target. This section focuses on detailing some of the methods that can be used in a forensic context in order to enable further attacks.

#### 2.4.1. Backside Imaging

Visual observation is a good first step to gain understanding an understanding of the IC. By putting a silicon die under the microscope it used to be possible to see the structures and gain some understanding on the chip. However, as the technology gets smaller and denser, visual inspection becomes more difficult. This is in part because the features are smaller, but mostly because of multiple metal layers blocking the view. An approach is to use infrared light and a sensitive camera to observe the chip from the backside. However, modern chips use highly doped silicon, which is less transparent to sensitive light so a stronger light source needs to be used.

#### 2.4.2. Reverse Engineering

Reverse engineering is useful but a difficult method for understanding the chip. In order to reverse engineer a chip all layers of the die are removed and photographed. This allows a knowledgeable attacker to document the entire internal structure of the chip.[56] After all transistors and interconnections are documented a knowledgeable attacker may be able to understand the structures. Depending on the device, operation does not just depend on the internal structure but also on program code. In these cases the program code needs to be extracted and analyzed as well.

#### 2.4.3. Laser scanning

Optical Beam Induced Current (OBIC) and Laser Induced Voltage Alteration (LIVA) are the two major laser scanning techniques. LIVA is used on a powered system in order to find the currently active areas. It works by monitoring the voltage changes of the power supply while a laser is scanned across the IC surface[56]. OBIC scans are supplied to an unpowered chip with its power supply pin connected to a current amplifier. A power current is generated when a laser is scanned across the surface of the IC. This current can be used to detect high-doped areas in the IC.

#### 2.5. Discussion

A lot of the described attacks are no longer as effective as they initially were. Some, like JTAG attacks, are the result of deliberate countermeasures by manufacturers. Others, like backside imaging, are a result of the increased complexity of Integrated Circuits (IC).

12 2. Hardware Attacks

JTAG attacks are an interesting case because manufacturers do not typically want to remove their own JTAG access. Restoring access to JTAG would once again grant access to one of the stronger attacks on data.

# Overview of Hardware Testing mechanisms

Testing is a crucial part of manufacturing, and special testing mechanisms such as JTAG Boundary Scan Chain (BSC) have been developed to aid in this endeavor. This chapter discusses an overview of BSC standards and their security. However, providing high-privilege level access to the hardware also opens up a very powerful attack vector for malicious entities. As such, various mechanisms have been developed in order to keep BSC testing mechanisms secure while maintaining the advantages. Section 3.1.1 discusses the JTAG BSC standard and several extensions. Section 3.2 provides a novel classification of various ways to secure JTAG. Sections 3.3, 3.4 and 3.5 discusses the classifications and provides examples for each. Finally, 3.6 discusses the various security solutions in general.

#### 3.1. Boundary Scan Standards

#### 3.1.1. IEEE 1149.1 - JTAG

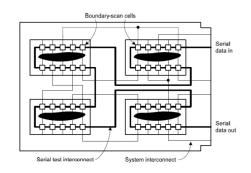

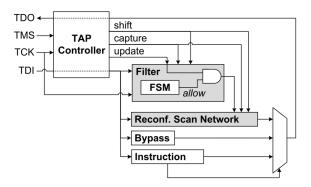

Testing circuit boards has become more difficult over time. As the number of components on a circuit board increased, so too has the number of pins that would be needed to access and test these components. Miniaturization has further compounded this problem as pins became harder or even impossible to reach with external tools. In response to this, the IEEE 1149.1 Standard [2] was developed by JTAG Technologies. It specifies a Boundary Scan Chain (BSC) implementation more commonly referred to as JTAG. It allows access to the pins of all JTAG compliant devices on the PCB through a serial connection, thus greatly improving testability. A basic layout is provided in figure 3.1.

The JTAG standard consists of three important components:

- The BSC register cells

- The Test Access Port (TAP)

- The TAP controller

The BSC register cells are placed on the pins of a compliant component. They consist of two flip-flops and the logic to support their operation. One provides the ability to capture and control the values of the pin, while the other is used to buffer control values before applying them on the pin [2].

The specification for the Test Access Port (TAP), provides four additional pins that are used for the control of the BSC

Figure 3.1: Example layout of a BSC equipped system [2].

mechanism. It requires four pins to be included into the design: one for the clock (TCK), another to enable various test modes (TMS), and two for in- and output of boundary cell data (TDI and TDO, respectively). These four lines can be daisy chained along various JTAG compatible components in order to provide full access to the system without requiring additional TAPs [2]. TMS, TDI and TDO are all serial connections that are sampled on the rising edge of TCK. The TAP controller controls JTAG's internal logic such as the instruction registers and associated circuitry.

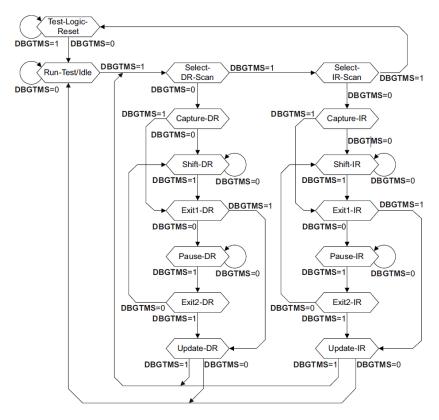

Figure 3.2: The JTAG State Machine [31]

#### 3.1.1.1. The JTAG State Machine

The TAP controller implements the state machine shown in Figure 3.2 in order to control the BSC. The TAP controller state is controlled by the serial data on Test Mode Select. It has sixteen states, eight for the data registers and eight for the instruction register with similar functionality. The most important states are:

- Capture-DR: loads the input cells on the data registers as specified by the currently loaded instruction.

- Capture-IR: loads a fixed pattern into the instruction shift-register that causes the controller to exit it's current state.

- Shift-DR/Shift-IR: Allows to shift data from TDI onto the data register / input register and out into TDO.

- Pause: Pause a shifting operation

- Update: makes the currently shifted in value the live value.

- Test-Logic-Reset: resets JTAG and sets IDCODE as the default instruction

All other states are temporary states that exist only to assist with transitions.

#### 3.1.1.2. Standard JTAG Instructions

Instructions can be shifted into the instruction register for more specific behavior. The standard specifies a number of required and several optional instructions. For this project, the most useful standardized instructions are:

- IDCODE: Sets the data register to access the IDCODE register, which can be used to identify components on the BSC

- BYPASS: Allows to temporarily disable the BSC registers of this component to speed up testing.

- SAMPLE: Allows to take a snapshot of normal operation of the component to be taken and examined.

- PRELOAD: Allows data to me shifted into the BSC register while the component is still in normal operation mode.

- EXTEST: Captures the current pin state and drives the value loaded in the BSC register onto the pins.

- INTEST (optional): Captures the pin state of the internal logic, and drives the values loaded into the BSC register onto the inner chip logic.

Additional Non-standard instructions, such as authentication registers, may be defined by the manufacturer and will need to be investigated separately.

#### 3.1.2. IEEE 1500 - SECT

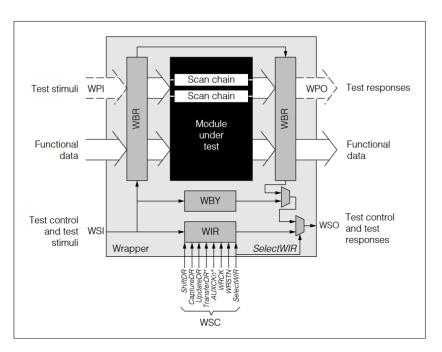

Figure 3.3: Architectural overview of the IEEE 1500 Sect wrapper. [36]

In order to increase functionality and performance the previously relatively simple Integrated Circuits (IC) have evolved into complete packages called a System on Chip (SoC). SoCs include numerous components and modules previously covered by several ICs, many not originally developed by the manufracturer. JTAG test chains need to be calculated for each chip's specific design, which becomes exceedingly complex with the highly modular design of SoCs. As such, treating the entire SoC as one entity is not ideal.

The IEEE 1500 Standard for Embedded Core Test (SECT)[36] is an extension of the original IEEE 1149.1 JTAG standard. It aims to expand the JTAG standard with plug-and-play interoperability, thus allowing for component manufacturers to design and exchange tests for the components in the SoCs. It achieves this by implementing wrapper around components of the soc, shown in Figure 3.3, and a formalized language: Core Test Language (CTL) [58]. CTL is used to formalize tests for components and is what allows tests to be shared. The wrapper interprets CTL and executes the intended test. When used together each component has it's own isolated scan chain with it's own associated tests. This allows component tests to be shared and reused over different SoC designs. The wrapper is otherwise conceptually similar to JTAG and further discussion is out of the scope of this thesis.

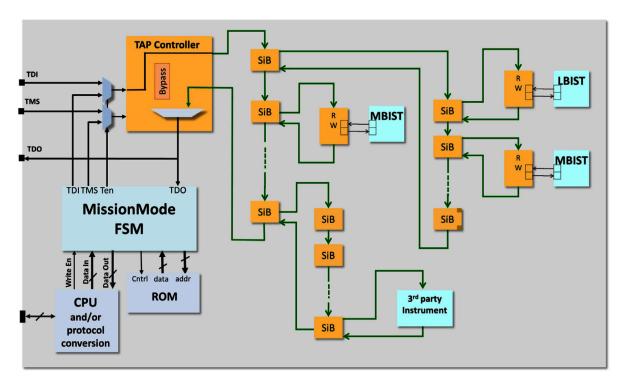

#### 3.1.3. IEEE 1687 - IJTAG

Figure 3.4: An example Layout for an IJTAG enabled system [38].

IJTAG, or instrument JTAG, is an important extension of the IEEE 1149.1 JTAG standard. It aims to extend JTAG with standards to manage configuration, operation and collection of data from embedded circuitry [26].

One problem with the JTAG standard surfaces when a JTAG compatible circuit contains tens or hundreds of components. These cases can result in extremely long scan paths with long test times as a result. Individual components can be bypassed in order to reduce the length. However, bypassing the various components requires a lot of instructions which is also considered to be inefficient.

IJTAG resolves this with the introduction of Segment-Insertion Bits (SIB) that allow the scan chain to be of variable length. These are single bit registers that, when closed, allow a shortcut on the segment of the scan chain. Thus potentially bypassing an entire network of instruments. The SIB can also be used in combination with a multiplexer, in which case it can be used to choose between alternative scan paths. These are referred to as Scanmux Control Bits (SCB).

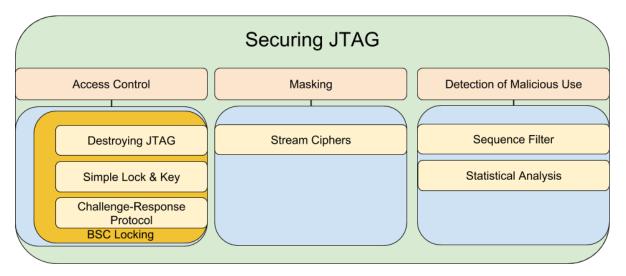

#### 3.2. Securing JTAG

One major problem in investigating secured variants of JTAG is the lack of standardization. As such, implementations may vary significantly between manufacturers. In order to aid in the conceptual understanding of Secure JTAG (SJTAG), figure 3.5 classifies a number of security measures for JTAG that can be found in the public domain. Examples will be discussed more thoroughly in chapter 3.2 and compared in chapter 3.6.

3.3. Access Control

Figure 3.5: Classifications of security measures for JTAG.

There are three major schools of thought within JTAG security. The most important one of which is access control. These systems focus on denying access to the TAP controller, usually until the correct authorization can be determined. Masking is a method of protection where obfuscation of the data streams is central. While they do not block access to the TAP controller, they typically use encryption to make communication impossible. Detection of malicious usage is the class with the most recent advancements. Systems within these classes typically provide free access and rely on monitoring to detect a possible attacker in order to generate a response. They will often be used in combination with the other two classes

The Exynos 7420's implementation of SJTAG is equipped with a form of challenge-response authentication. These protocols are similar in concept but can still differ significantly in implementation, as such three sub-classifications for it have also been provided.

This remainder of this chapter discusses specific implementations of the classes mentioned in chapter 3.2. While there exist some variants of these implementations, on the conceptual level they are too similar to make a meaningful distinction for the scope of this paper.

#### 3.3. Access Control

Access control mechanisms focus on restricting access to the JTAG Boundary Scan Chain (BSC) by (temporarily) disabling it. There exist various public implementations of this, and this section aims to provide an overview of various methods to implement access control on JTAG.

#### 3.3.1. Disabling JTAG

The simplest and the most effective solution of securing JTAG is destroying the JTAG port. This can be done in many ways, ranging from physical destruction of the connections to burning a security fuse. While very secure, this also makes JTAG unavailable for fault analysis by the manufracturer [14]. Additionally, depending on the method used, it may be possible for an attacker to repair JTAG access. Securing JTAG without permanently disabling access is typically preferred on most chips because of these reasons.

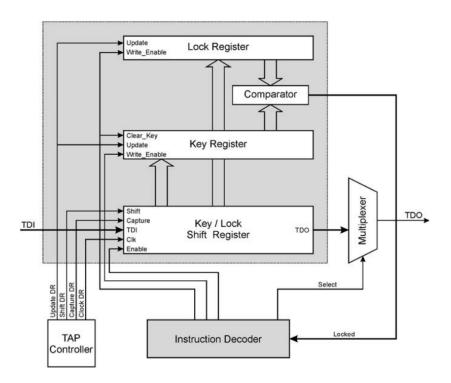

#### 3.3.2. Simple Lock & Key

Figure 3.6: Structure of the locking mechanism [42].

The second class of security is a simple locking mechanism. This particular variant introduces three additional registers: the Lock register, the Key register and the Lock/Key register. Locking is done by shifting the LOCK instruction into the instruction register. This allows the user to shift in the key and enter it into the Lock register using Update DR. Unlocking is done in a similar fashion with the Key register and the UNLOCK instruction. All instructions, except UNLOCK, are mapped to the harmless BYPASS instruction while the chip is in a locked state [42]. Other implementations exist and may improve on security by, for instance, using a hash and a hashing engine to avoid storing the key in the system directly.

#### 3.3.3. Challenge-Response Protocol

Challenge-response authentication is a commonly used form of authentication that relies on public key cryptography. According to the protocol the verifier generates a random secret, and the prover uses this secret to prove he has knowledge of the access key. Commonly, this is done using public key cryptography where the prover can encrypt the secret using his private key. The verifier can then decrypt the data with the public key to recover the random secret to confirm the identity. There are some variants to this protocol within the JTAG ecosystem, including the one found on the Exynos 7420 [35]. As such, the public variants are discussed in the remainder of this section.

#### 3.3.3.1. Challenge-response with SHA-256

The implementation discussed in [14] uses a SHA-256 hashing algorithm to provide the necessary authentication to JTAG [14]. It aims to provide a basic protection scheme that doesn't block access entirely, but is more secure than a simple password.

The implementation requires a secret key to be stored on the chip as well as a good random number generator and a SHA-256 hashing engine. In order to verify authentication, the device generates a random number and communicates it to the user. The user appends their secret key and hashes both with SHA-256. When this hash is communicated back to the device, it can generate it's own version of the hash using the stored secret key and random number to match it against the user's. If the hashes are equal, access is granted.

3.3. Access Control

#### 3.3.3.2. Challenge-response with PKC

Protected JTAG [12] is an implementation of the Challenge-Response authentication with public key cryptography. It's designed to only restrict the more sensitive internal processor functions, not the standard circuitry debugging ones.

Protected JTAG introduces three protection levels and four access modes, labeled PL0 through PL2 and AM0 through AM3 respectively. The protection levels define the security of the device, while the access mode is a configurable attribute that defines a default protection level with the ability to lower it. [12]. The protection levels can be summarized as:

- PL0 is the fully protected level and limits user access to external functions such as interconnections and the built in self test.

- PL1 extends the functionality found in PL0 by allowing access to registers, CPU and programmable flash memory.

- PL2 is the lowest level of protection, providing full access and is identical to JTAG.

And the access modes can be described as:

- AM3 is a non-protected access mode, which can be utilized during development to gain full unrestricted access. As such, the default protection mode is PL2.

- AM2, low protection mode, can be used during development once the devide's secure features have been tested and verified, and can be locked off. While the default access level is PL1, AM2 includes a feature to temporarily allow an authorized user to lower the protection level to PL2.

- AM1 is the high protection mode, and is typically used when a device is delivered to the customer. With

the default level of protection set to PL0, it protects the device from being attacked through the JTAG

port. Still, as JTAG is sometimes instrumental in recovering data, the protection level can be lowered to

either PL1 or PL0 by an authorized user.

- AM0 is the maximum protection mode. The default protection mode is PL0 with no ability to downgrade it. It's intended for very sensitive devices that contain data that's not meant to be accessed by anyone.

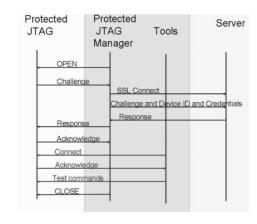

Because Protected JTAG is implemented on an embedded device, it has limited database functionality. As such, authorization is handled through a trusted authorization server. In order to ensure authorization is done securely, a challenge-response based identification algorithm is used. The Protected JTAG module is outfitted with the ability to create challenges and verify responses to enable it. The authentication protocol is based on elliptic curve encryption, where the device holds the public key and the remote server holds the private key.

The authorization sequence, as displayed in figure 3.7, works as follows: First, the device generates a challenge that includes the requested access level and a random component, and signs it with the public key. This challenge, along with the device ID and the user's credentials, can then be communicated to the authorization server. Using the credentials, the server can then verify if the user's authoriza-

Figure 3.7: The authorization sequence found in Protected JTAG [12].

tion matches the requested access. The device ID is used to find the correct private key, and the server generates an appropriate response with it. Once communicated to the Protected JTAG module, it can verify the response's authenticity using it's public key and grant the requested access.

#### 3.3.3.3. Challenge-response with a certificate authority

Secure JTAG Implementation using Schnorr [17] is a Challenge-Response implementation that, unlike the name implies, is unrelated to Samsung's implementation of Secure JTAG (SJTAG). Previous approaches suppose a one-way authentication, where either the server or the circuit is considered trusted. This solution is suitable in cases where neither the circuit or server is trusted.

This solution presents another use of public key cryptography: Using Schnorr protocol it is possible to ensure that both the circuit and server can be trusted. In the Schnorr protocol, the prover (such as the user) has a signed certificate containing his public key. This certificate has been signed with the authentication server's private key. The validator (the circuit) can then validate a user's identity using the authentication server's private key, and extract the prover's public key. The validator then signs his own public key using the prover's, and communicates it to the prover. This securely exchanges public keys, which can then be used for safe communication.

#### 3.3.4. Boundary Scan Cell Locking

Figure 3.8: Overall architecture of BSC locking [46].

Figure 3.9: The access monitor of BSC locking [46].

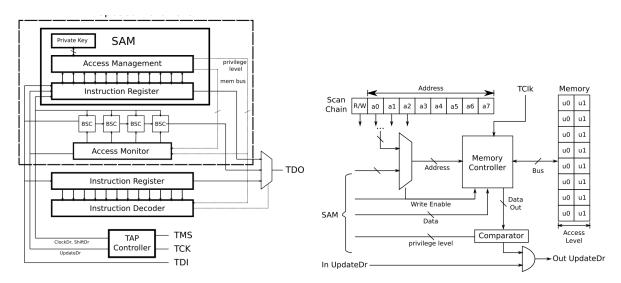

Multi-level Secure JTAG is an extension of previous authentication systems but primarily based on Protected JTAG, described in section 3.3.3.2. While the aforementioned have detailed protocols for authentication, but do not control user access afterwards. They also generalize the permission scheme introduced by Protected JTAG by allowing the designer to set any amount of permission levels. A user can only execute functions that have an access level equal or lower than their permission level.

Multi-level SJTAG introduces a Secure Authentication Module and an Access Monitor. The Secure Authentication Module is designed to work with any challenge-response protocol, and works similarly as Protected JTAG's. After authentication, the Secure Authentication MODULE will pass the privilege level to the Access Monitors, and acts as their control interface.

The Access Monitor is the primary extension, and monitors the BSC cells. Specifically, it monitors the connection between the flip-flop used for Shift-dr and the flip-flop used for Update. This allows it to determine if an update to that cell is allowed, and to subsequently allow or deny it.

#### 3.4. Masking

This security class focuses on masking the data streams sent through JTAG rather than controlling access. If implemented correctly this makes it impossible to control JTAG with any accuracy and impossible to interpret the output in any meaningful way.

Stream Ciphers are the only good way to implement masking on native JTAG. However, there are two variants that are conceptually in line with this class, but are unfit for inclusion:

- The first of these variants is obfuscating of the Boundary Scan Chain (BSC), where, for instance, the length of the scan chain is variable from device to device. This makes reversing the scan chain harder, but not significantly so. As such, this is not a proper security measure and has not been included in the classification.

- The second of these variants exists only when JTAG is used as the physical layer for a packet-based protocol. When using packets it's possible to use different cryptographic mechanisms such as RSA.

Conceptually this is similar to Stream ciphers, but no longer applied to the JTAG protocol. If the encryption is applied to a custom protocol it's security for that given protocol, and as such has not been included in the classification.

#### **Stream Ciphers**

Figure 3.10: Stream cipher architecture [29].

A Stream cipher is a type of encryption where data is encrypted per bit. As JTAG is a bit-level protocol the sensible encryption is a bit-level encryption. Stream ciphers are employed in two places: Firstly, in order to maximize the data protection TDO is XOR'ed with the output of the cipher key stream [29]. Encrypting the output only protects the system data against reading, not control. A second, different, cipher is added on TDI pin in order to decode an encrypted input stream. This requires a user to encrypt the input Stream, thus securing against control of the system.

#### 3.5. Detection of Malicious Use

Rather than trying to control who uses the JTAG interface, this class focuses on identifying malicious use.

#### 3.5.1. Sequence filter

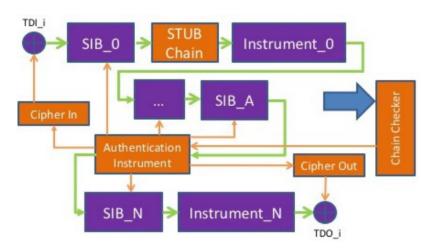

Figure 3.11: Structure of the sequence filter [4].

This method to secure JTAG is based on IJTAG's ability to reconfigure the scan network. The core concept behind this setup is to restrict access to protected SIBs so that sections containing sensitive components cannot be accessed through the TAP. This is achieved by using a sequence filter in the TAP controller [4]. The filter monitors shifted-in data and will block the update if the sequence would affect SIBs that would grant access to protected parts of the scan chain.

#### 3.5.2. Statistical Analysis

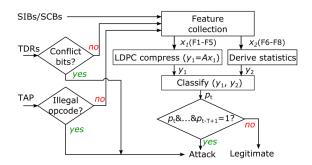

Figure 3.12: Flow Diagram of the detection of an attack in IJTAG [48].

Statistical analysis is a state of the art method to protect JTAG. It makes use of machine learning in order to detect attacks [48] [49]. It's based around the idea that illegitimate users will behave differently to legitimate users as they don't know what JTAG functions are implemented or how they should be operated. It employs an on-chip neural network classifier in order to recognize illegitimate access. For instance, an attacker may not know the appropriate length of the DR register and may attempt to shift an incorrect amount of times in order to determine the length. Another classifier that can be used are common transitions, as an attacker would be trying to discover and learn about them, rather than using them in the expected fashion. If enough consecutive predictions indicate an attacker, an alarm is raised and the attacker is locked out. The overall flow of a detection is shown in figure 3.12. While this has been proven to be an effective strategy for JTAG, with a 99.2% detection rate [49], this approach is ineffective in IJTAG. This is primarily because, due to it's hierarchical nature, many more combinations of operations are possible [48]. This results in a highly dimensional feature set which is challenging to store on a chip. While high dimensional, the feature set also very sparse; This makes it possible to use a low-density parity-check (LDPC) matrix to compress the dataset.

#### 3.6. Comparison

Almost all solutions focus on restricting access to the TAP controller, rather than the scan chain. As all communication is done through the TAP controller this is a logical solution, but it does provide a single point of failure. This includes the stream cipher, as the data is unencrypted as it passes through the scan chain. These single point of failures might make it viable to circumvent the authentication mechanisms instead of attacking the authentication protocols directly. The major exception is Multi-level Secure JTAG (SJTAG) as it attempts to lock down the Boundary Scan Chain (BSC) cells rather than access to the scan chain.

Another common theme in the public key encryption is the use of Elliptic Curve Cryptography(ECC) rather than RSA. The reason for this is mainly economical: The implementation for ECC is much smaller on the chip than RSA is [17]. This makes it cheaper to fabricate, significantly so if a company produces thousands of chips. Despite being cheaper to implement, the security offered by ECC is similar to RSA.

Detection mechanisms, while effective, assume attackers are unfamiliar with the chip's architecture. With enough documentation or resources, it may still be possible for an attacker to pose as a legitimate user.

4

# Samsung Secure JTAG

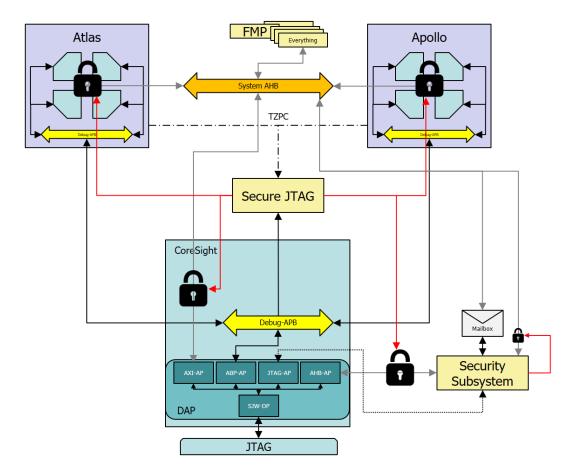

Chapter 3 discussed various methods in order secure JTAG Boundary Scan Chain (BSC). This chapter focuses on Samsung's implementation: Secure JTAG (SJTAG). A brief conceptual overview of SJTAG is provided in Section 4.1. To aid in the understanding of SJTAG and related attacks, Section 4.2 discusses the CoreSight debug system. SJTAG itself is detailed in Section 4.3.2. Lastly, Section 4.4 provides a brief explanation of a number of potential attack vectors if SJTAG were to be disabled.

#### 4.1. Concept of Work

Section 2.2.3 discussed the power of JTAG as an attack vector. As JTAG is an important testing standard, several methods were discussed in Chapter 3 that attempt to secure it. Secure JTAG (SJTAG) [35] is Samsung's method to secure the debug system. While the name implies that it is a secure form of JTAG, it is not applied to the JTAG standard. Instead SJTAG is a module intended to extend the ARM CoreSight debug system with an access control mechanism. SJTAG is implemented in Samsung Exynos System on Chips (SoC), which are commonly found on various Samsung devices such as smartphones. The debug system and it's security is further described in Section 4.2, while SJTAG is detailed in Section 4.3

#### 4.2. Debug system: CoreSight

This section discusses the debug system found in ARMv7 and ARMv8 architectures and it's important components. Sections 4.3.1 and 4.2.2 provide an overview of the debug system and it's security measures. Section 4.2.3 covers the Debug Access Port (DAP) which is an important component in accessing the debug system. JTAG-DP and JTAG-AP are critical components of the DAP, and are discussed separately in Sections 4.2.4 and 4.2.5.

#### **4.2.1. Overview**

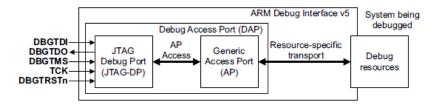

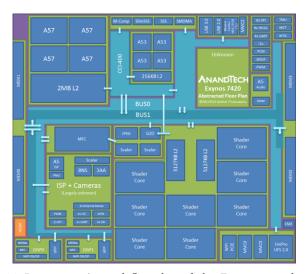

Figure 4.1: Simplified drawing of debug system

All ARMv7 and ARMv8 architectures contain an on-chip debug and trace architecture referred to as CoreSight. It replaces JTAG Boundary Scan Chain (BSC) where possible. Additionaly, the debug system provides support for JTAG BSC, which is used for components that do not support CoreSight. CoreSight-enabled devices have a separate debug bus called the Debug Advanced Peripheral Bus (APB) and all supported components have debug related registers memory mapped on it. This includes for instance registers governing breakpoints and trace information. The debug registers of the CPUs are grouped as follows:

- **DBG**: Debug, providing various debug info and controls.

- CTI: Cross Trigger Interface provides control mechanisms for simultaneous communication to multiple cores.

- PMU: Performance Monitoring Unit reports information about the core such as cache misses.

- ETM: Embedded Trace Macrocell is used in generation of execution traces for debugging purposes.

Further details can be found in Chapter H of the respective architecture's manuals [32] [34] and the CoreSight documentation [33] in general.

#### **4.2.2. Security**

As debug mechanisms have been proven to be a huge security concern, the ARMv7 and ARMv8 architectures specify up to four external security signals. These are:

• DBGEN: DeBuG ENable; enables invasive debug.

- **SPIDEN**: Secure Privileged Invasive Debug ENable; enables debug while the relevant processor core is in a secure state.

- NIDEN: Non-Invasive Debug ENable; enables trace functionality.

- **SPNIDEN**: Secure Privileged Non-Invasive Debug ENable; enables tracing while the relevant processor core is in a secure state.

Enabling these signals significantly impacts the device's security, as they govern, for instance, the ability to halt the CPU and step through instructions. Research has shown that the debug capabilities can be used by an attacker for a privilege escalation attack [41]. Notable about the attack described is that it can be executed purely from software, using CoreSights On-System Debugging features. The security signals are controlled by an external authentication mechanism. This mechanism is vendor specific and not specified by the ARM standard. Samsung's implementation as used on the Exynos 7420 is called Secure JTAG (SJTAG) and is discussed in Section 4.3.

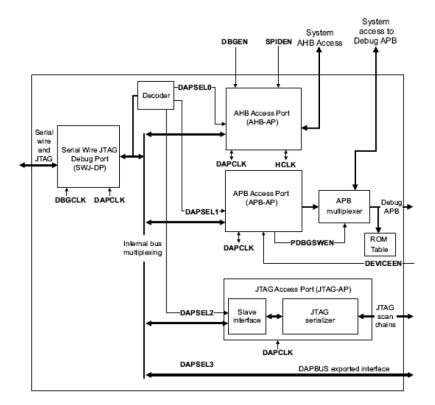

# 4.2.3. Debug Access Port

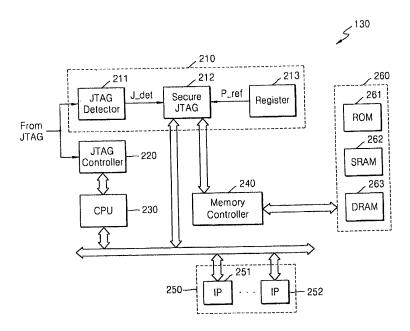

Figure 4.2: The Debug Access Port[35]

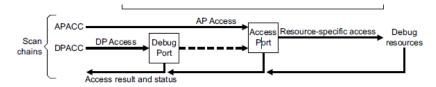

The DAP is the debug component in charge of external communication into the debug system. It is an implementation of the Arm Debug Interface Version 5 (ADIv5)[35]. As can be seen in Figure 4.2 the DAP comprises of two Debug Ports (DP), three Access Ports, a decoder and the DAPBUS. The decoder is used to select which AP is used, and the DAPBUS exposes the debug system to the CPU for on-system debugging.

#### 4.2.3.1. Debug Ports

The DPs are divided into three classes, only two of which are actual DPs:

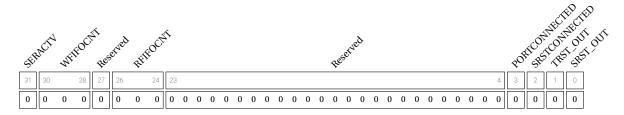

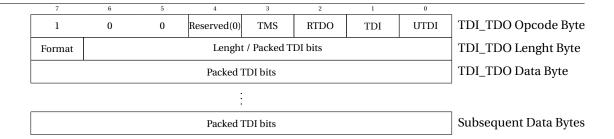

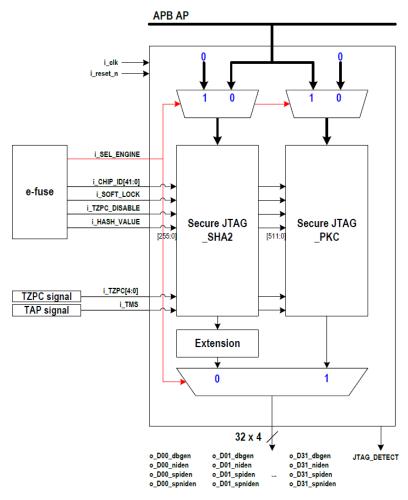

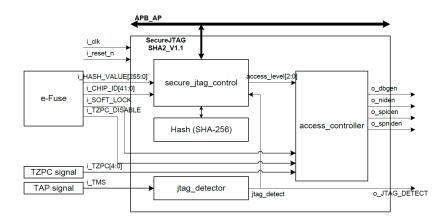

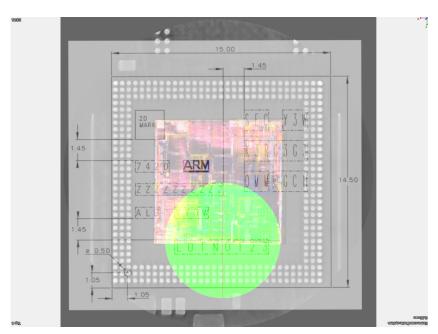

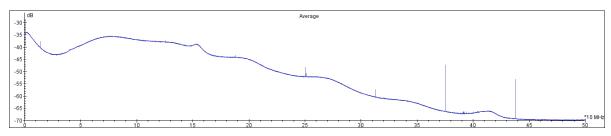

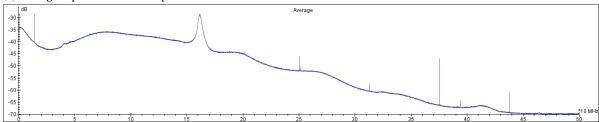

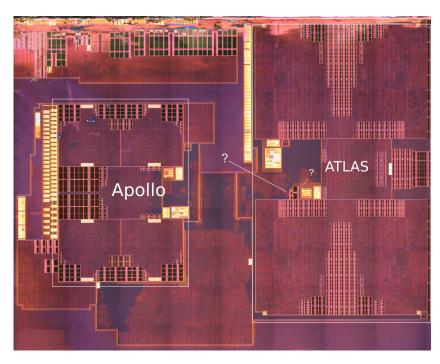

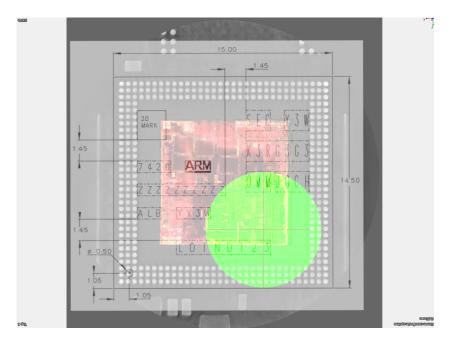

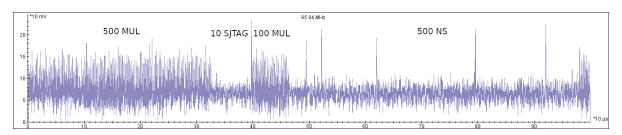

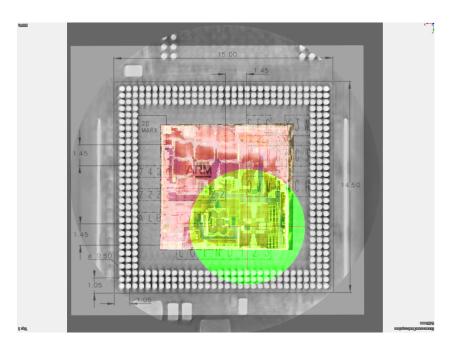

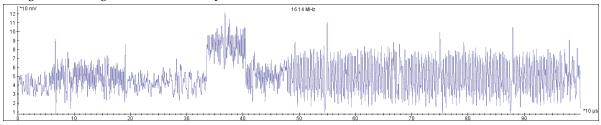

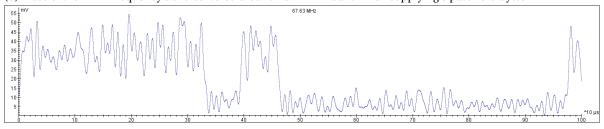

#### • ITAG-DP: