## M.Sc. Thesis

## Design and Implementation of Real-Time High-Definition Stereo Matching SoC on FPGA

Lu Zhang B.Sc.

#### Abstract

Stereo matching has been widely used in many fields, such as view-point interpolation, feature detection system and free-view TV. However, the long processing time of stereo matching algorithms has been the major bottleneck that limits their real-time applications. During the past decades, many implementation platforms and corresponding algorithm adaptations are proposed to solve the processing time problem. Although notable real-time performances have been achieved, these works rarely satisfy both real-time processing and high stereo matching quality requirements.

In this thesis, we propose an improved stereo matching algorithm suitable for hardware implementation based on the VariableCross and the MiniCensus algorithm. Furthermore, we provide parallel computing hardware design and implementation of the proposed algorithm. The developed stereo matching hardware modules are instantiated in an SoC environment and implemented on a single EP3SL150 FPGA chip. The experimental results suggest that our work has achieved high speed real-time processing with programmable video resolutions, while preserving high stereo matching accuracy. The online benchmarks also prove that this work delivers leading matching accuracy among declared real-time implementations, with only 8.2% averaged benchmark error rate. We have also achieved 60 frames per second for  $1024 \times 768$  high-definition stereo matching, which is the fastest high-definition stereo matching to the best of our knowledge.

## Design and Implementation of Real-Time High-Definition Stereo Matching SoC on FPGA

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

EMBEDDED SYSTEMS

by

Lu Zhang B.Sc. born in Shandong, China

This work was performed in:

Computer Engineering Group Department of Microelectronics & Computer Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

## **Delft University of Technology**

Copyright © 2010 Computer Engineering Group All rights reserved.

# Delft University of Technology Department of Microelectronics & Computer Engineering

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled "Design and Implementation of Real-Time High-Definition Stereo Matching SoC on FPGA" by Lu Zhang B.Sc. in partial fulfillment of the requirements for the degree of Master of Science.

| Dated: 2010-September-03 |                         |

|--------------------------|-------------------------|

| Chairman:                | Prof.dr.ir. Koen Bertel |

| Advisors:                | Dr.ir. Gauthier Lafrui  |

|                          | Dr.ir. Georgi Kuzmanov  |

| Committee Members:       | Dr.ir. Rene van Leuker  |

|                          |                         |

## Abstract

Stereo matching has been widely used in many fields, such as viewpoint interpolation, feature detection system and free-view TV. However, the long processing time of stereo matching algorithms has been the major bottleneck that limits their real-time applications. During the past decades, many implementation platforms and corresponding algorithm adaptations are proposed to solve the processing time problem. Although notable real-time performances have been achieved, these works rarely satisfy both real-time processing and high stereo matching quality requirements.

In this thesis, we propose an improved stereo matching algorithm suitable for hardware implementation based on the VariableCross and the MiniCensus algorithm. Furthermore, we provide parallel computing hardware design and implementation of the proposed algorithm. The developed stereo matching hardware modules are instantiated in an SoC environment and implemented on a single EP3SL150 FPGA chip. The experimental results suggest that our work has achieved high speed real-time processing with programmable video resolutions, while preserving high stereo matching accuracy. The online benchmarks also prove that this work delivers leading matching accuracy among declared real-time implementations, with only 8.2% averaged benchmark error rate. We have also achieved 60 frames per second for  $1024 \times 768$  high-definition stereo matching, which is the fastest high-definition stereo matching to the best of our knowledge.

## Acknowledgments

This thesis work has been performed at IMEC (Leuven, Belgium) with support from the Computer Engineering group of TU Delft (Delft, the Netherlands). I want to take this opportunity to thank everyone who has helped me during this thesis work period.

First I would like to thank Dr. Gauthier Lafruit, Prof. Diederik Verkest and Prof. Kees Goossens for their agreement to offer me the opportunity to do my master's thesis project at IMEC. Their rich experience and scientific insights have also put the whole research and development in the correct direction - dedicated hardware implementation of high performance stereo matching.

During the thesis work period, I thank Ke Zhang for his ingeniously developed VariableCross stereo matching algorithm and guiding me into the stereo vision world. Ke also inspires me a lot during the hardware architecture and computing flow design. I thank Bart Vanhoof for his advices of selecting and using the suitable FPGA and development tools. Bart also contributes a lot to the camera interface and image rectification implementations on FPGA. I thank Luc Rynders for his collaboration on viewpoint interpolation analysis and corresponding software developments. I would like to thank Prof. Georgi Kuzmanov for his invaluable suggestions for improvements and all the hours he put in proofreading my thesis. Along the way Qiong Yang and Bart Masschelein also spent time on teaching me background knowledge and proposing insightful advices. I also would thank Gauthier Lafruit, Francesco Pessolano and Johan De Geyter for their excellent management.

Special thanks give to Prof. Tian Sheuan Chang and Gauthier Lafruit. Without their support and contributions this thesis work cannot make our desired achievements. Prof. Chang has proposed the Mini-Census transform, which is applied in our implementation to improve the robustness of stereo matching and reduce the memory consumption. I am also grateful to have his inspiration and encouragement. Gauthier's enthusiasm and ambition is the propulsion of the whole research and development. I owe cordial appreciation for his constant guidance, trust and support.

The recent two years' study and research in Delft and Leuven has been a wonderful experience. TU Delft and IMEC give me the opportunity to interact with outstanding and talented people from all over the world. I want to express my gratefulness to all my friends for their love, support and sharing all the happy time with me in the two fantastic European towns. I also deeply thank my family for their remote and emotional support and encouraging.

Finally I thank all my thesis defense committee members including Prof. Koen Bertels, Prof. Georgi Kuzmanov, Dr. Gauthier Lafruit and Prof. Rene van Leuken.

Lu Zhang B.Sc. Delft, The Netherlands 2010-September-03

## Contents

| A            | Abstract |          |                                                                 |     |

|--------------|----------|----------|-----------------------------------------------------------------|-----|

| $\mathbf{A}$ | ckno     | wledgn   | nents                                                           | vii |

| 1            | Intr     | oducti   | ion                                                             | 1   |

|              | 1.1      | Motiva   | ation                                                           | 1   |

|              | 1.2      | Proble   | em Definition                                                   | 3   |

|              | 1.3      | Solution | ons and Contributions                                           | 4   |

|              | 1.4      | Overv    | iew of Chapters                                                 | 5   |

| 2            | Bac      | kgrour   | nd and Related Work                                             | 7   |

|              | 2.1      | Epipo    | lar Geometry and Image Rectification                            | 7   |

|              | 2.2      | Stereo   | Matching Computation Flow                                       | 8   |

|              |          | 2.2.1    | Matching Cost Computation                                       | 8   |

|              |          | 2.2.2    | Area-Based Matching Cost Aggregation                            | 9   |

|              |          | 2.2.3    | Disparity Estimation                                            | 12  |

|              |          | 2.2.4    | Disparity Refinement                                            | 12  |

|              | 2.3      | Relate   | ed Work                                                         | 13  |

|              | 2.4      | Design   | n Considerations and Targets                                    | 14  |

| 3            | Ste      | reo Ma   | atching Algorithm: Software-Hardware Co-Design                  | 17  |

|              | 3.1      | Overv    | iew of the Stereo Matching Pipeline                             | 17  |

|              | 3.2      | Design   | n of the Pre-Processor Pipeline                                 | 21  |

|              |          | 3.2.1    | Median Filter                                                   | 21  |

|              |          | 3.2.2    | Census Transform and Adaptive Support Region Construction $\ .$ | 24  |

|              |          | 3.2.3    | Output Logic                                                    | 28  |

|              | 3.3      | Design   | n of the Stereo-Matcher Pipeline                                | 29  |

|              |          | 3.3.1    | Raw Cost Scatter and Correlation Region Builder                 | 31  |

|              |          | 3.3.2    | Parallelized Cost Aggregations                                  | 32  |

|              |          | 3.3.3    | Winner-Takes-All and L-R Disparity Maps                         | 37  |

|              |          | 3.3.4    | Output Logic                                                    | 39  |

|              | 3.4      | Design   | n of the Post-Processor Pipeline                                | 41  |

|   |                   | 3.4.1                                                                      | L-R Consistency Check                      | 41                                      |

|---|-------------------|----------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------|

|   |                   | 3.4.2                                                                      | Disparity Voting                           | 42                                      |

|   |                   | 3.4.3                                                                      | Median Filter and Output                   | 46                                      |

| 4 | Ste               | reo Ma                                                                     | atching SoC Implementations on FPGA        | 47                                      |

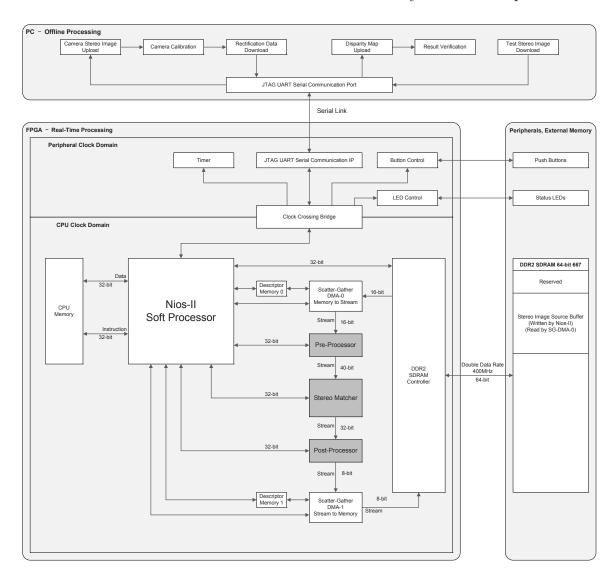

|   | 4.1               | Overv                                                                      | iew of the Proposed System                 | 48                                      |

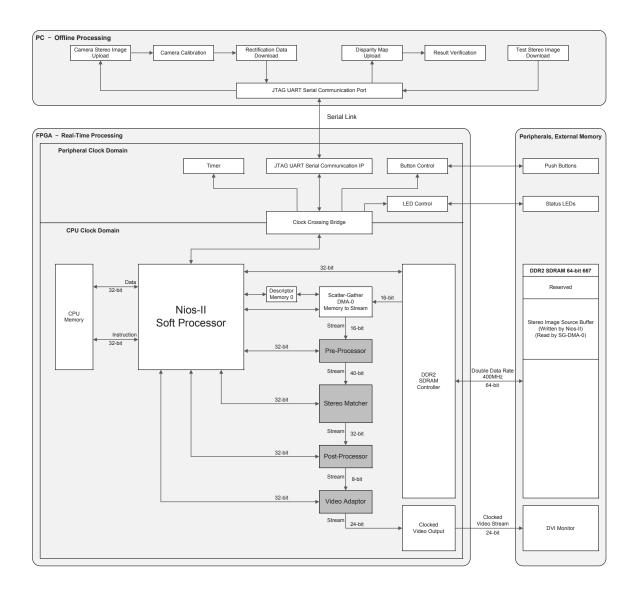

|   |                   | 4.1.1                                                                      | The PC Tasks                               | 49                                      |

|   |                   | 4.1.2                                                                      | The FPGA Tasks                             | 49                                      |

|   | 4.2               | Introd                                                                     | luction to the SoC Hardware                | 50                                      |

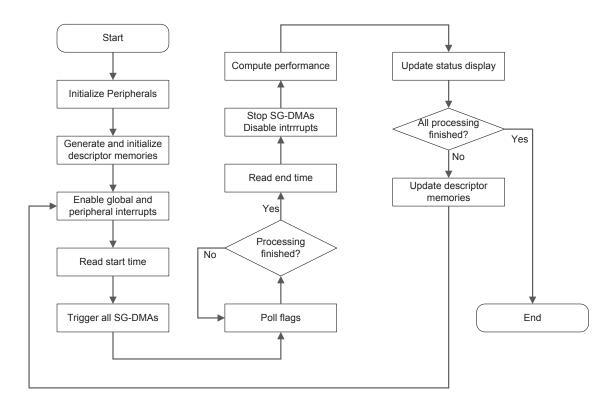

|   | 4.3               | Introd                                                                     | luction to the SoC Software                | 51                                      |

|   | 4.4               | System                                                                     | n on a Chip Interconnections               | 53                                      |

|   |                   | 4.4.1                                                                      | Avalon Memory Mapped Interconnect          | 53                                      |

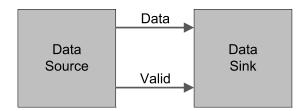

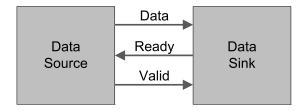

|   |                   | 4.4.2                                                                      | Avalon Streaming Interconnect              | 54                                      |

|   | 4.5               | Storag                                                                     | ge System                                  | 54                                      |

|   | 4.6               | Bandy                                                                      | width Utilization Estimations              | 56                                      |

| 5 | Des               | ign Ev                                                                     | valuation and Experimental Results         | 59                                      |

|   | 5.1               | Evalua                                                                     | ation of the Proposed Algorithm            | 59                                      |

|   | 5.2               |                                                                            |                                            |                                         |

|   |                   | Evalua                                                                     | ation of the FPGA Implementation           | 63                                      |

|   |                   | Evalua 5.2.1                                                               | ation of the FPGA Implementation           | 63<br>63                                |

|   |                   |                                                                            | -                                          |                                         |

|   | 5.3               | 5.2.1<br>5.2.2                                                             | Introduction to the FPGA Hardware Resource | 63                                      |

|   | 5.3               | 5.2.1<br>5.2.2                                                             | Introduction to the FPGA Hardware Resource | 63<br>65                                |

|   | 5.3               | 5.2.1<br>5.2.2<br>Evalua                                                   | Introduction to the FPGA Hardware Resource | 63<br>65<br>67                          |

|   | 5.3               | 5.2.1<br>5.2.2<br>Evalua<br>5.3.1<br>5.3.2                                 | Introduction to the FPGA Hardware Resource | 63<br>65<br>67                          |

| 6 | 5.4               | 5.2.1<br>5.2.2<br>Evalua<br>5.3.1<br>5.3.2<br>Comp                         | Introduction to the FPGA Hardware Resource | 63<br>65<br>67<br>67<br>68              |

| 6 | 5.4               | 5.2.1<br>5.2.2<br>Evalua<br>5.3.1<br>5.3.2<br>Comp                         | Introduction to the FPGA Hardware Resource | 63<br>65<br>67<br>67<br>68<br>70        |

| 6 | 5.4<br>Cor        | 5.2.1<br>5.2.2<br>Evalua<br>5.3.1<br>5.3.2<br>Comp                         | Introduction to the FPGA Hardware Resource | 63<br>65<br>67<br>67<br>68<br>70        |

| 6 | 5.4<br>Cor<br>6.1 | 5.2.1<br>5.2.2<br>Evalua<br>5.3.1<br>5.3.2<br>Comp<br>nclusio<br>Conclusio | Introduction to the FPGA Hardware Resource | 63<br>65<br>67<br>68<br>70<br><b>73</b> |

## List of Figures

| 1.1  | A disparity map example                                          | 1  |

|------|------------------------------------------------------------------|----|

| 1.2  | The eye gazing angle problem                                     | 2  |

| 1.3  | The Eye Contact Silhouette system                                | 2  |

| 1.4  | IMEC proposed eye gazing solution                                | 3  |

| 1.5  | Proposed view interpolation setup with FPGA                      | 5  |

| 2.1  | Correspondences and the half occlusion problem                   | 8  |

| 2.2  | Rectified images and epipolar lines                              | 8  |

| 2.3  | Basic pixel-to-pixel matching method                             | 9  |

| 2.4  | Cost aggregation over a fixed window                             | 10 |

| 2.5  | Cost aggregation over an shaped window                           | 11 |

| 2.6  | Stereo matching pseudo code                                      | 12 |

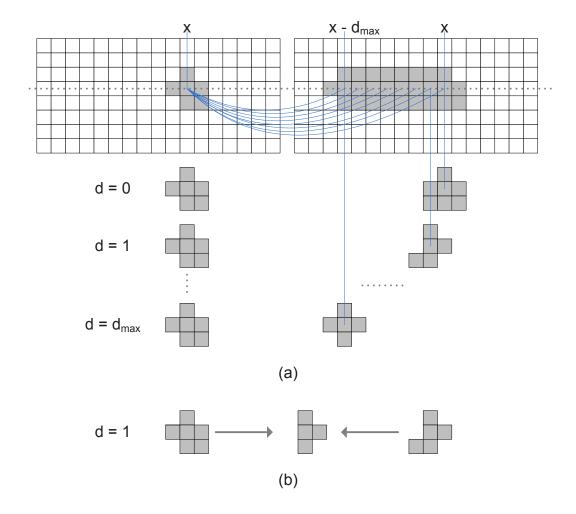

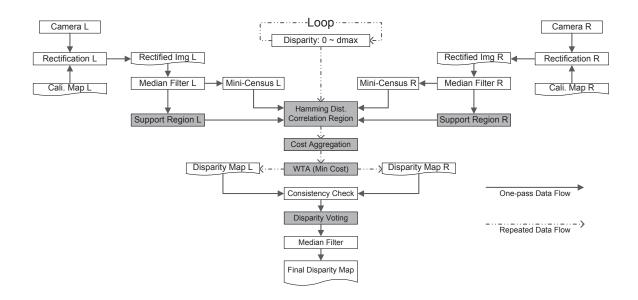

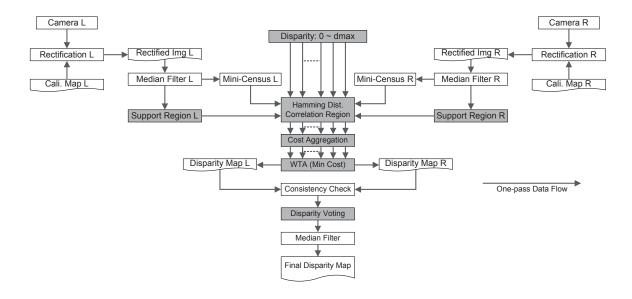

| 3.1  | Sequential stereo matching processing flow                       | 18 |

| 3.2  | Parallelized stereo matching processing flow                     | 18 |

| 3.3  | Stereo matching pipeline and functions                           | 19 |

| 3.4  | Pre-Processor internal processing pipeline                       | 21 |

| 3.5  | Median filter                                                    | 22 |

| 3.6  | Median filter data stream                                        | 22 |

| 3.7  | Line buffers and registers in a median filter                    | 23 |

| 3.8  | Slide window for a median filter                                 | 24 |

| 3.9  | Median filter sorting array                                      | 24 |

| 3.10 | Mini-Census transform                                            | 25 |

| 3.11 | Local adaptive cross and support regions on an image             | 26 |

| 3.12 | Adaptive support region representation                           | 26 |

| 3.13 | Census transform and adaptive support region construction window | 28 |

| 3.14 | Stereo-Matcher processor internal processing pipeline            | 29 |

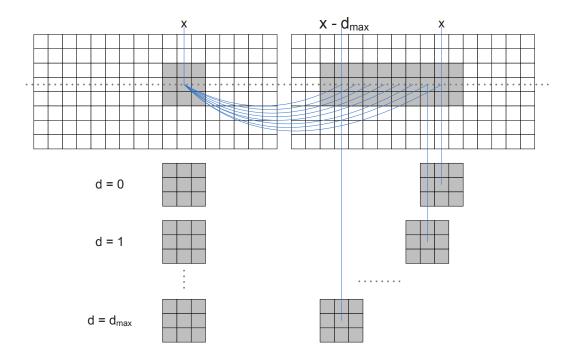

| 3.15 | 1-dimensional local search area                                  | 30 |

| 3.16 | Scattering raw matching costs using shift register arrays        | 31 |

| 3.17 | Two orthogonal 1D aggregations                                   | 32 |

| 3.18 | Integral costs and horizontal cost aggregation                   | 33 |

| 3 19 | Horizontal cost aggregation logic                                | 34 |

| 3.20 | Aggregation data reuse in vertical aggregation                  | 35 |

|------|-----------------------------------------------------------------|----|

| 3.21 | Vertical cost aggregation without data reuse                    | 36 |

| 3.22 | Vertical cost aggregation with data reuse                       | 36 |

| 3.23 | Pipelined data flow                                             | 37 |

| 3.24 | Winner-Takes-All select tree                                    | 37 |

| 3.25 | Compute the disparity map of the right image                    | 38 |

| 3.26 | Lineup buffers and read patterns                                | 39 |

| 3.27 | L-R disparity maps generated by the Stereo-Matcher              | 40 |

| 3.28 | Post-Processor internal processing pipeline                     | 41 |

| 3.29 | Synchronized L-R disparity data word                            | 42 |

| 3.30 | L-R consistency check logic                                     | 42 |

| 3.31 | Left disparity map after consistency check                      | 43 |

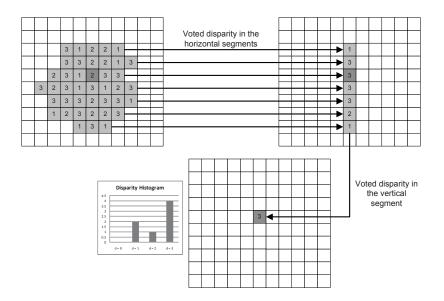

| 3.32 | Disparity histogram and voted disparity                         | 43 |

| 3.33 | $2\times 1D$ orthogonal voting method                           | 44 |

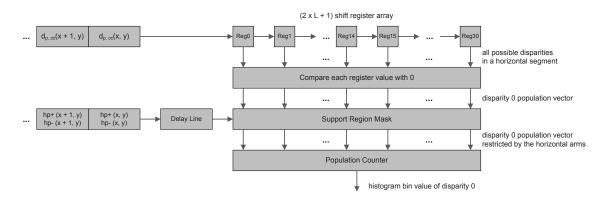

| 3.34 | Horizontal voting unit for disparity 0                          | 44 |

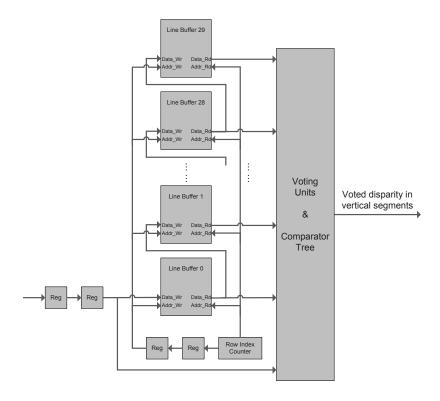

| 3.35 | Vertical voting logic and line buffers                          | 45 |

| 3.36 | Voted disparity maps                                            | 46 |

| 3.37 | Final disparity map                                             | 46 |

| 4.1  | Proposed SoC with both source and result frame buffer           | 47 |

| 4.2  | Proposed SoC with source frame buffer and display               | 48 |

| 4.3  | Flow chart of the main loop tasks                               | 52 |

| 4.4  | The minimum Avalon-ST interconnect                              | 54 |

| 4.5  | Avalon-ST interconnect in our system                            | 54 |

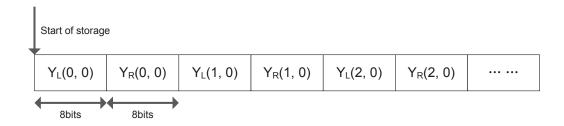

| 4.6  | Packed stereo frame data storage                                | 55 |

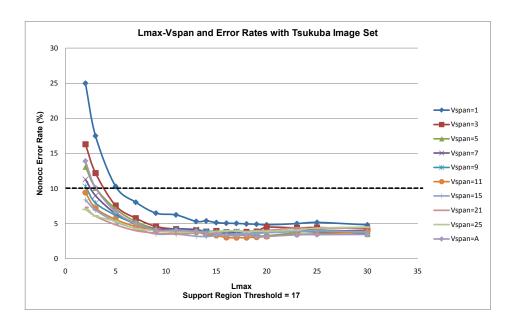

| 5.1  | Lmax-Vspan and error rates with Tsukuba image set               | 60 |

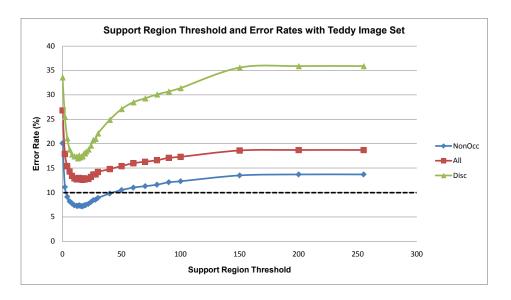

| 5.2  | Lmax-Vspan and error rates with Teddy image set                 | 60 |

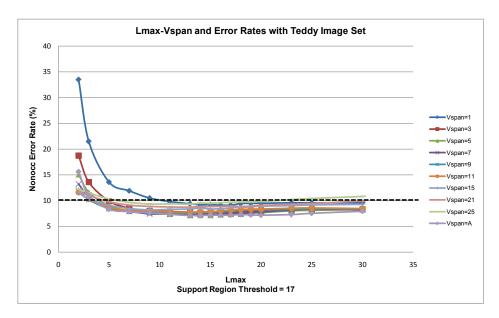

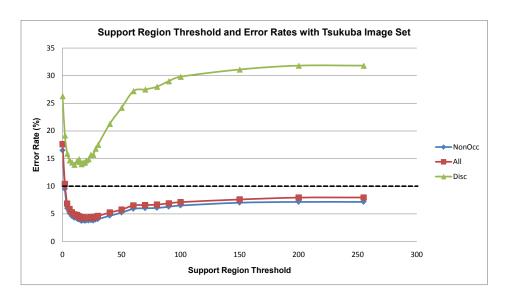

| 5.3  | Support region threshold and error rates with Tsukuba image set | 61 |

| 5.4  | Support region threshold and error rates with Teddy image set   | 61 |

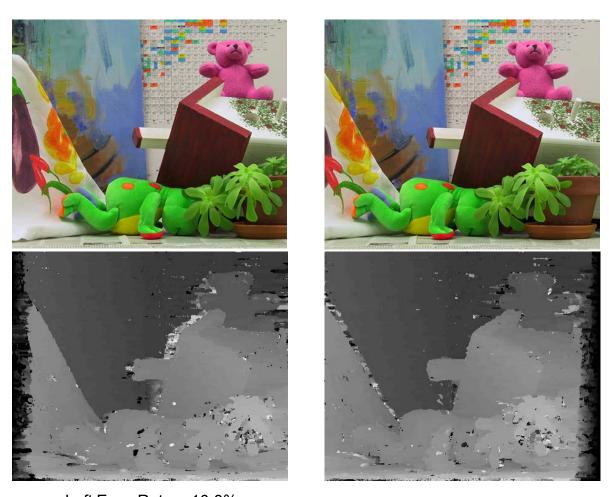

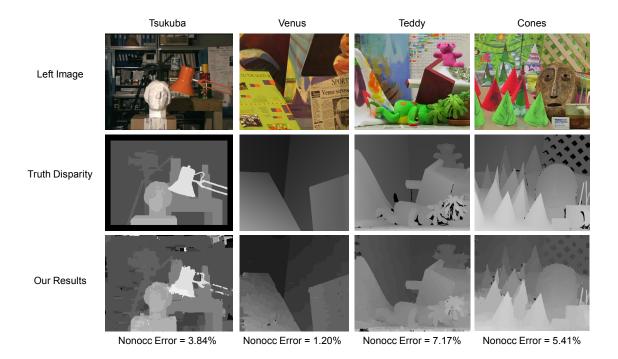

| 5.5  | Truth disparity maps and our results                            | 62 |

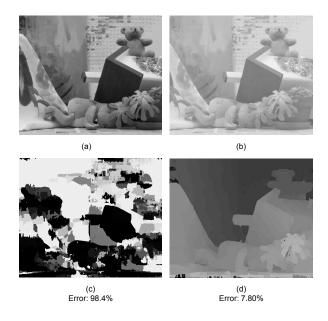

| 5.6  | Luminance biased images and the resulted disparity maps         | 62 |

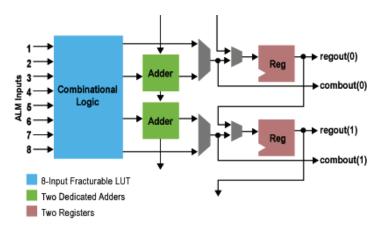

| 5.7  | High-level block diagram of Stratix-III ALM                     | 63 |

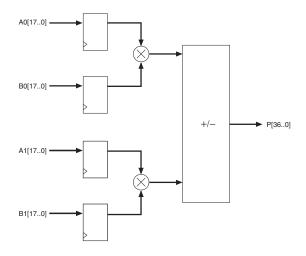

| 5.8  | Basic Two-Multiplier Adder DSP unit                             | 64 |

## List of Tables

| 2.1  | Matching cost computations and aggregations                     | 11 |

|------|-----------------------------------------------------------------|----|

| 5.1  | EP3SL150 on-chip memory features                                | 64 |

| 5.2  | EP3SL150 DSP block configurations                               | 65 |

| 5.3  | EP3SL150 hardware resource summary                              | 65 |

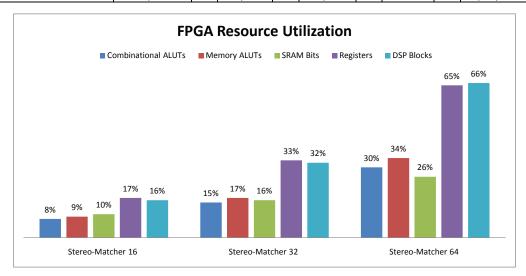

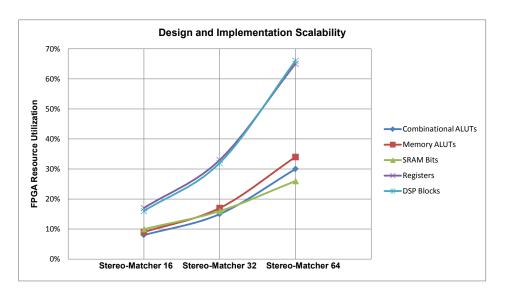

| 5.4  | EP3SL150 hardware resource utilization summary                  | 66 |

| 5.5  | Design and implementation scalability                           | 67 |

| 5.6  | Stereo matching pipeline latency summary                        | 67 |

| 5.7  | Stereo matching processing speed summary                        | 68 |

| 5.8  | Theoretical frame rates (FPS) with different pixel clocks       | 68 |

| 5.9  | FPGA frame rates (FPS) with SoC1 and 100MHz Clock $\dots \dots$ | 69 |

| 5.10 | FPGA frame rates (FPS) with SoC2 and standard pixel clocks      | 69 |

| 5.11 | Stereo matching algorithm error rate benchmark                  | 70 |

| 5.12 | Stereo matching algorithm frame rates                           | 71 |

Introduction

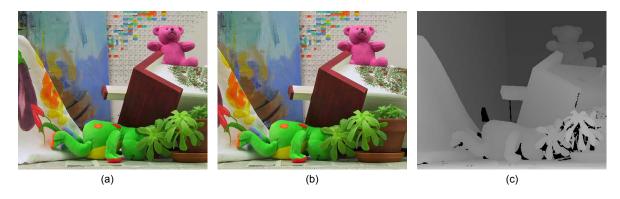

Stereo matching has been, and continues to be one of the most active research topics in computer vision. The task of stereo matching algorithm is to analyze the images taken from a stereo camera pair, and to estimate the displacement of corresponding points existing in both images in order to extract depth information (inversely proportional to the pixel displacement) of objects in the scene. The displacement is measured in number of pixels and also called *Disparity*; disparity values normally lie within a certain range, the *Disparity Range*, and disparities of all the image pixels form the disparity map, which is the output of a stereo matching processing. An example with the *Teddy* benchmark image set is shown in Figure 1.1. In the figure the disparities are visualized as grayscale intensities, and the brighter the grayscale, the closer (to the stereo cameras) the object. Therefore the disparity map encodes the depth information

Figure 1.1: A disparity map example

(a): Image taken by the left camera. (b): Image taken by the right camera. (c): The ground truth disparity map associated with the left image.

of each pixel, and once we infer the depth information by means of stereo matching, we are able to obtain the 3D information and reconstruct the 3D scene using triangulation. Since stereo matching provides depth information, it has great potential uses in 3D reconstruction, stereoscopic TV, navigation systems, virtual reality and so on.

### 1.1 Motivation

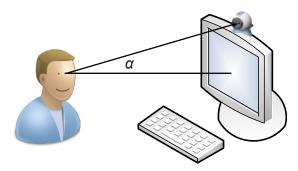

The motivation of this thesis research and design work is to facilitate eye-gazing video conferencing with the support of high quality and real-time stereo matching. As many of the audience may have experienced, a common desktop video communication through

Skype and a webcam often lacks natural eye contact. The reason is obvious: providing natural eye contact requires the communication participants looking directly into the camera, but unfortunately, traditional video conferencing devices with a camera positioned above the screen (as shown in Figure 1.2) fail to satisfy this requirement. The angular displacement (noted as  $\alpha$  in Figure 1.2) between the single camera and

Figure 1.2: The eye gazing angle problem

monitor center causes one participant cannot look at the camera simultaneously while looking at the remote participant shown on the display. The lack of natural eye contact leads to awkward and uncomfortable feelings, and sometimes causes distrust between meeting participants. There are several approaches to correct the eye gazing problem, one remarkable one is the *Eye Contact Silhouette* system provided by Digital Video Enterprises (DVE). As shown in Figure 1.3, the camera is physically positioned behind

Figure 1.3: The Eye Contact Silhouette system

the display, which means that when the local participants look at the display showing remote participants, they are also looking directly into the camera and providing true eye contact (with zero gazing angle) to the far end sites. However, this arrangement is bulky and expensive, and more importantly it does not fit well to our commodity computer peripherals. A more elegant solution is to provide a computer-synthesized video which looks as if it were captured from a camera directly behind the monitor screen.

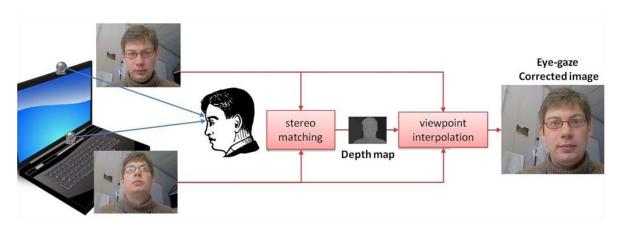

Our proposed solution is shown in Figure 1.4. It requires two cameras positioned on the top and bottom (or left and right) of the display, which provide the computer with stereo vision. The depth information in the computer's vision (meeting participants)

Figure 1.4: IMEC proposed eye gazing solution

is therefore obtained by means of stereo matching, and the in-between view from the virtually centered camera position is provided by a view interpolation algorithm. In this thesis we consider the two cameras are horizontally aligned, i.e., left and right. When the cameras are vertically aligned, they can also be considered as left and right with image rotation processing.

The full proposed eye-gazing video pipeline contains image acquisition, camera calibration, image rectification, stereo matching, view interpolation and video display. This thesis work focuses on the stereo matching part, which introduces the major processing bottleneck as discussed in the following section.

### 1.2 Problem Definition

In the processing pipeline, stereo matching is normally the most time consuming part. Due to high computational complexity, solutions that obtain satisfactory synthesizing quality under the constraint of real-time execution are quite rare, e.g. a recent three-camera viewpoint interpolation prototype system [32] proposed by Sharp Corporation only reaches a couple of frames per second for low-resolution images. In order to provide real-time and high-quality interpolation results, the stereo matching bottleneck must be solved first, especially for high frame rate and high definition (e.g. 50 frames per second with  $1024 \times 768$  video size) applications such as business eye-gazing video conference systems.

Recent stereo matching design and implementations utilize various processing platforms such as high-performance multi-core CPU, GPU, DSP, FPGA and ASIC. Meanwhile, many stereo matching algorithms and adaptations are also proposed for efficient implementations on these platforms. Nevertheless, these work rarely satisfies both real-time and high matching accuracy requirements. For example, a recent implementation on a

GeForce8800 GTX GPU proposed by Zhang et al. [50] preserves high matching quality with an averaged benchmark error rate 7.65%, but only reaches 12 frames per second with  $450 \times 375$  image resolution. In contrast, the FPGA implementation proposed by Jin et al. [23] achieves 230 frames per second stereo matching with VGA ( $640 \times 480$ ) resolution, but the matching accuracy degrades a lot with averaged benchmark error rate 17.24%.

Furthermore, frames to match in stereo matching come from two different cameras and hence might exhibit very different luminance or radiometric variations, incurring a severe matching cost bias to which some stereo matching cost functions are very sensitive. Some of the recently proposed algorithms are not robust in this condition.

### 1.3 Solutions and Contributions

To satisfy both real-time and high-accuracy stereo matching requirements, especially for high-definition view interpolation applications, we propose a hardware friendly high-accuracy stereo matching algorithm and a dedicated hardware implementation approach. The prototyping and evaluation design are implemented on a single EP3SL150 FPGA, and the implemented algorithm is based on *Adaptive Cross-Based Local Stereo Matching (VariableCross)* proposed by Zhang et al. [49] with our hardware friendly adaptations. Compared with the other two kinds of implementations (on CPU and GeForce8800 GTX GPU) of the same algorithm, this design has achieved significant speedup regarding processing time (speedup factor ranges from 41 to 162 compared with the CPU implementation), while preserving high matching accuracy.

Our main achievements are twofold: on one side, we improved the state-of-the-art VariableCross [49] algorithm regarding its accuracy and robustness; on the other side, we provided a high-performance and high-quality hardware design of the proposed algorithm. Summarized contributions of this thesis work are listed below:

We proposed an improved algorithm that:

- Preserves high matching accuracy with 8.2% averaged benchmark error rate.

- Maintains robust to radiometric distortions and bias differences introduced by stereo cameras. The robustness is obtained with the support of *Mini-Census Transform* proposed by Chang et al. [4].

We implemented the algorithm in hardware that:

- Achieves real-time stereo matching with various and run-time programmable resolutions e.g.,  $450 \times 375$  @ 193FPS,  $640 \times 480$  @ 105FPS and  $1024 \times 768$  @ 60FPS, independent on the disparity range.

- Proposes fully pipelined and scalable hardware structure. The hardware scales with the maximum disparity range under consideration, and the scalability offers hardware resource savings with small disparity range applications. On the FPGA

EP3SL150 we have evaluated implementations with maximum disparity range of 16, 32 and 64.

- Implements industry standard on-chip interconnections (Avalon System Interconnect Fabric). This enables our design to work properly with other Avalon-compatible processing modules, for example the Altera's Video and Image Processing (VIP) Suite.

- Provides fully functional SoC reference design with run-time configurable parameters and disparity map visualizations on a standard DVI monitor.

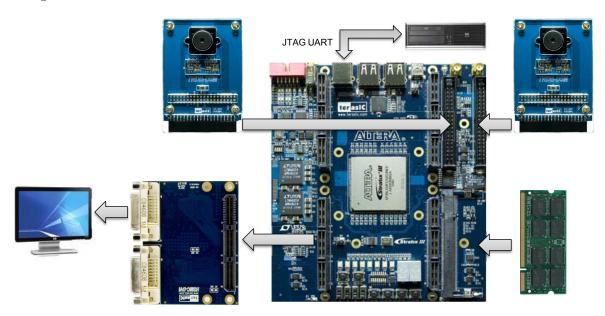

The whole design is implemented on the DE3 evaluation board, which contains the EP3SL150 FPGA and rich peripherals e.g., DDR2 SDRAM, USB and camera interfaces. A DVI extension board is also employed for the disparity map display. To verify the hardware implementation on FPGA, the stereo matching hardware processing starts with rectified stereo images from an external frame buffer (DDR2 SDRAM) and finally output disparity maps to a result frame buffer. The disparity maps are uploaded to a PC for verification and benchmarking. To visualize disparity maps, the result frame buffer is removed and the disparity maps are output to a monitor. To enable follow-up work and view interpolation prototyping, the complete setup is also proposed, as shown in Figure 1.5.

Figure 1.5: Proposed view interpolation setup with FPGA

## 1.4 Overview of Chapters

The content of the thesis text is organized as follows: Chapter 2 introduces the background knowledge of stereo matching computing flow, related work and our design

considerations. In Chapter 3, we present the proposed stereo matching algorithm and corresponding hardware module design in a top-down approach. Chapter 4 provides two reference SoC designs with the stereo matching modules on our selected FPGA and corresponding hardware/software tasks. In chapter 4, we also estimate the external memory storage and bandwidth utilizations. Chapter 5 evaluates the whole design and implementation according to our design considerations, and provides comparison to related work. Finally, Chapter 6 summarizes the thesis and suggests valuable optimization techniques and interesting application developments as future work based on our stereo matching results.

Background and Related Work

In the past two decades, various stereo matching algorithms have been proposed and they were summarized and evaluated by Scharstein and Szeliski [35]. In this notable work, these proposed stereo matching algorithms are categorized into two major types: local area based methods and global optimization based methods. In local methods, the disparity evaluation at a given pixel is based on similarity measurement performed in a finite window. The similarity metric is defined by a *Matching Cost* and all costs in the local window are often aggregated to provide a more reliable and robust result. On the other hand, global methods define global cost functions and solve an optimization problem. Global algorithms typically do not perform an aggregation step, but rather seek a disparity assignment that minimizes a global cost function.

In this thesis we are particularly interested in local stereo matching methods, which generally have low computation complexity and less storage requirement; and therefore they are suitable for real-time and embedded implementations. In Section 2.1 we introduce the image rectification required by efficient local stereo matching; In Section 2.2 fundamental basis of the stereo matching computation flow and our chosen algorithm are discussed. We present our design considerations and corresponding algorithm adaptations in Section 2.4 and conclude this chapter with related work and comparisons.

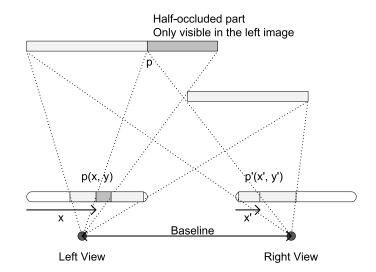

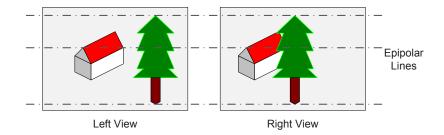

## 2.1 Epipolar Geometry and Image Rectification

For a given pixel in the left image, the stereo matching algorithm is to seek the corresponding one in the right image, for example in Figure 2.1 the object point p appears in both left and right views as pixel p(x,y) and p'(x',y'), respectively. The two pixels are defined as a correspondence pair, and the displacement of their locations in the stereo view is the disparity; in this case the disparity is equal to (x-x'). In Figure 2.1, the distance between the stereo cameras' focal axis is defined as the Baseline. To enable efficient stereo matching, it is necessary that the two input images are Rectified, fulfilling Epipolar Geometry. In epipolar geometry each pixel in the left image finds its correspondence in the right image (if exists) on a specific line, called the *Epipolar Line*. If the two images are rectified, the epipolar lines coincide with the image rows and run parallel to the baseline; so that the correspondence search only needs to be performed along a 1-dimension scanline. The concept is shown in Figure 2.2. Image rectification according to epipolar geometry is an important processing step before the stereo matching algorithm, enabling less complex implementation of the correspondence searching. Detailed rectification algorithm and implementations are not further discussed in this thesis, and we therefore assume in the sequel input stereo images are rectified.

Figure 2.1: Correspondences and the half occlusion problem

Figure 2.2: Rectified images and epipolar lines

## 2.2 Stereo Matching Computation Flow

In general, stereo matching algorithms perform the following steps:

- 1. Matching cost computation.

- 2. Cost (support) aggregation.

- 3. Disparity computation / optimization

- 4. Disparity refinement.

The four steps are introduced in the following subsections. In local algorithms, emphasis is on the matching cost computation and cost aggregation steps.

### 2.2.1 Matching Cost Computation

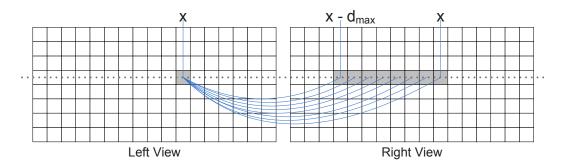

Thanks to image rectification, searching for correspondences is reduced to 1-dimensional. In addition, the disparity values lie within a certain disparity range;

so the basic matching method is performed pixel-to-pixel in a horizontal line segment, as shown in Figure 2.3. In this example the disparity range is  $[0 \dots d_{max}]$ , and  $d_{max} = 7$  in this figure. The disparity range is determined by the distance between the scene

Figure 2.3: Basic pixel-to-pixel matching method

objects and the camera baseline, and the length of the baseline itself. To determine the matched correspondences in a stereo pair, the matching costs are defined to evaluate the probability of a correct match; the smaller the costs, the higher the probability. For pixel-to-pixel matching, the matching cost is commonly defined as *Absolute Difference*, Squared Difference, Hamming Distance etc., on both gray and color images. The Equation 2.1 defines the matching cost measured by absolute intensity difference; where  $I(\cdot)$  returns the grayscale intensity of a pixel in the left image and  $I'(\cdot)$  returns the intensity of a right image pixel. The two pixels under consideration are related by a disparity hypothesis d.

$$Cost(x, y, d) = |I(x, y) - I'(x - d, y)|$$

(2.1)

In this simple case, the correspondence is determined by the minimum cost value, and the associated d is the disparity of the pixel p(x, y) in the left image.

Hamming distance cost is normally computed based on transformed images. The transform is a pre-processing (often a filter) step before the matching cost computation. In our implementation we adopted the *Mini-Census Transform* proposed by Chang et al.[4]. Details of this transform algorithm are introduced in Chapter 3.

To avoid ambiguity, in the following context we refer the matching cost between two single pixels as the *Raw Matching Cost*. Raw matching costs in a restricted area are often aggregated to improve the matching accuracy.

#### 2.2.2 Area-Based Matching Cost Aggregation

Typically, to increase the reliability of cost evaluation and the robustness to image noise, local stereo matching methods choose to aggregate (accumulate) raw matching costs over a *Support Region*. The most basic support region is a square window, as shown in Figure 2.4. In this example, a fixed  $3 \times 3$  support region is built for a given pixel in the left image and all raw costs in this region are aggregated. The same computation applies to each pixel in the disparity range in the right image.

Figure 2.4: Cost aggregation over a fixed window

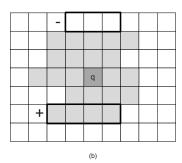

The well known challenge for area-base local stereo matching is that a local support region should be large enough to contain sufficient intensity variation for reliable matching, while it should be small enough to avoid disparity discontinuity inside the region. Therefore state-of-the-art stereo matching algorithms often shape the support window in order to include only pixels with the same (unknown) disparity. Veksler [42] found a useful range of window sizes and shapes while evaluating the aggregated cost. Zhang et al. [49] adaptively shaped a support window with variable crosses in order to bound the pixels near arbitrarily shaped disparity discontinuities. Yoon and Kweon [48] also assigned a support weight to the pixel in a support window based on color similarity and geometric proximity. The Figure 2.5 illustrates a simple shaped support region example. The support regions are built around the anchor pixel in the left image, and the pixels in the disparity range in the right image. Normally for evaluating each hypothetical pair, only the overlapped area of the two support windows is considered to take both images into account.

Some local stereo matching algorithms simply sum up all the raw matching costs in a support region, for example the Sum of Absolute Differences (SAD), Sum of Squared Differences (SSD) and Sum of Hamming Distances. These algorithms are clearly broken down into step 1 and 2 as mentioned above. On the other hand, some of the algorithms merge step 1 and 2 and define a new matching cost based on the support region, such as Normalized Cross-Correlation (NCC). The Table 2.1 summarizes involved computations for these commonly used matching cost aggregation. In the table, the  $\sum_{x,y}(\cdot)$  denotes aggregation over the (overlapped) support region;  $I(\cdot)$  returns the intensity of a pixel and  $BitVec(\cdot)$  gives the bit vector associated with a pixel after

Figure 2.5: Cost aggregation over an shaped window (a): Shaped window for pixels in the left and right image. (b): Overlapped area of the windows associated with a hypothetical pair.

| Matching Cost                | Computations                                                                                 |

|------------------------------|----------------------------------------------------------------------------------------------|

| Sum of Absolute Differences  | $\sum_{x,y}  I(x,y) - I'(x-d,y) $                                                            |

| Sum of Squared Differences   | $\sum_{x,y} (1(x,y) - 1'(x - d,y))^2$                                                        |

| Sum of Hamming Distances     | $\sum\nolimits_{x,y} Hamming(BitVec(x,y),BitVec'(x-d,y))$                                    |

| Normalized Cross-Correlation | $\frac{\sum_{x,y} (I(x,y) \cdot I'(x-d,y))}{\sqrt{\sum_{x,y} (I(x,y)^2 \cdot I'(x-d,y)^2)}}$ |

Table 2.1: Matching cost computations and aggregations

a certain transform, e.g. Census. More extensive discussions and evaluations about state-of-the-art matching cost computations/aggregations are found in [19].

### 2.2.3 Disparity Estimation

Disparity estimation is to choose at each pixel in the left image the disparity d associated with the minimum cost value. Generally, this involves a local "Winner-Takes-All" (WTA) optimization at each anchor pixel p(x,y) in the left image and the pixels in the disparity range in the right image. Therefore the basic concept of stereo matching is explained by the pseudo code listed in Figure 2.6. Though straightforward, the

```

FOR (y IN 0 TO ImageHeight - 1)

FOR (x IN 0 TO ImageWidth - 1)

FOR (d IN 0 TO d<sub>max</sub>)

IF (Cost(x, y, d) < MinCost(x, y, d))

MinCost(x, y, d) = Cost(x, y, d)

d<sub>p</sub>(x, y) = d

END IF

END FOR

END FOR

```

Figure 2.6: Stereo matching pseudo code

embedded computing loops cause the major bottleneck for real-time implementations, and one of the contributions of this thesis work is to solve this problem with parallel and pipelined computing.

A limitation of this disparity estimation is that uniqueness of matches is only guaranteed for one image (the left image), while pixels in the right image might get matched to multiple points. To compensate for this problem, a similar matching process is also performed based on the right image, and the disparity map of the right image is also generated. The uniqueness and consistency tests are performed in the disparity refinement step, combining both disparity maps.

### 2.2.4 Disparity Refinement

The correspondence may not exits for each pixel in one image due to *Half-Occlusion*, as shown in Figure 2.1. *Consistency Check* (comparing left-to-right and right-to-left disparity maps) is often employed to detect occluded areas and perform uniqueness tests, and detected mismatches can be fixed by surface fitting or by distributing neighboring valid disparity estimates [35].

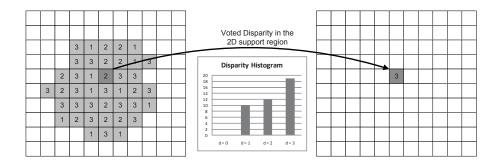

If disparity results pass consistency check, some additional techniques are used to further the disparity reliability and accuracy, for example *Sub-Pixel Estimations* [37] or local high-confidence *Disparity Voting* [28] in a support region. After this step, a final median filter is also helpful for removing speckle noises and smoothing the disparity map.

Disparity refinement normally contributes considerable improvements to the WTAestimated disparity map, so in our final implementation we applied consistency check, local disparity voting and median filtering.

## 2.3 Related Work

To enable efficient stereo matching computation, especially for real-time applications, various approaches have been developed during the past two decades. In recent years, notable achievements have been made in either matching accuracy and processing speed. We categorize them according to the implementation platforms.

General purpose CPUs are often used as the first algorithm prototyping platform, and many efficient aggregation methods are proposed to accelerate the CPU processing. Tombari et al. [39] proposed an efficient segmentation-based cost aggregation strategy, which achieves a frame rate of 5 FPS for  $384 \times 288$  images with 16 disparity range on an Intel Core Duo clocked at 2.14 GHz. But it drops to only 1.67 FPS with 450 × 375 images and 60 disparity range. Later, Salmen et al. [34] optimized a dynamic programming algorithm on a 1.8 GHz PC platform and achieved a frame rate of 5 fps for  $384 \times 288$  and 16 disparity range stereo matching. Kosov et al. [26] combined a multi-level adaptive technique with a multi-grid approach that allows the variational method to reach 3.5 FPS with  $450 \times 375$  images and 60 disparity range. Zhang et al. [49] proposed the VariableCross algorithm and orthogonal integral image technique to accelerate the aggregation over irregularly shaped regions. This work achieves 7.14 FPS with  $384 \times 288$  and 16 disparity range, but only 1.21 FPS with  $450 \times 375$  and 60 disparity range. Though real-time performances are generally poor, CPU implementations often achieve very good accuracy with less than 10% averaged error rates. Error rates of the above mentioned four implementations are 8.24\%, 8.83\%, 9.05\% and 7.60%, respectively.

With GPU implementation, a global optimizing real-time algorithm was developed by Yang et al. [46] on a GeForce 7900 GTX GPU. The authors used hierarchical belief propagation and reached 16 FPS for  $320 \times 240$  images with 16 disparities. This work presented high matching accuracy with 7.69% averaged error rate, but clearly its frame rates and image resolution are limited. Another GPU implementation was introduced by Wang et al. [43]. It is based on an adaptive aggregation method and dynamic programming and reaches a frame rate of 43 FPS for  $320 \times 240$  images and 16 disparity levels on an ATI Radeon XL1800 graphics card. Compared with the work by Yang et al. [46], it achieves higher frame rates, but its accuracy degrades to 9.82%. Later, the authors of VariableCross algorithm [49] also implemented the same algorithm on GeForce GTX 8800 [50], which achieves 100.9 FPS with  $384 \times 288$ images and 16 disparity range. However, the frame rate drops to 12 FPS with 450  $\times$ 375 resolution and 64 disparities. Most recently, Humenberger et al. [20] optimizes the Census Transform on GeForce GTX 280 GPU, and reaches 105.4 FPS with 450  $\times$ 375 resolution and 60 disparity range. This work also maintains high accuracy with averaged error rate of 9.05%. Although notable performances have been achieved with GPU implementations, GPUs are not efficient in power and memory consumption and hence not suitable for highly integrated embedded systems. Furthermore, these works rarely report the performances with high-definition stereo matching.

Chang et al. [3] investigated the performance of using DSP as the implementation platform. In this work, the authors proposed a  $4\times5$  jigsaw matching template and the dual-block parallel processing technique to enhance the stereo matching performance on a VLIW DSP. The DSP implementation achieved 50 FPS with disparity range of 16 for  $384\times288$  stereo matching. Nevertheless, its accuracy degrades a lot, with above 20% averaged error rate and its frame rate drops to 9.1 with  $450\times375$  images and 60 disparity range.

Implementations with CPUs, GPUs and DSPs are all software based approaches. The major problem with software is that the computing logic and data paths are fixed and not configurable. As a result, they are not optimized for available algorithms. Furthermore, their performances also require very high device clock frequency and memory bandwidth. To overcome the software limit, recent works also investigated the performance of dedicated hardware design. Chang et al. [4] proposed a high performance stereo matching algorithm with Mini-Census and Adaptive Support Weight (MCADSW) and also provided its corresponding real-time VLSI architecture. The design is implemented with UMC 90nm ASIC, and reaches 42 FPS with  $352 \times 288$  images and 64 disparity range. It also preserves high matching accuracy (unknown average) with benchmark image sets. Jin et al. [23] proposed a fully pipelined hardware design using Census Transform and Sum of Hamming Distances. This work has achieved 230 FPS with  $640 \times 480$  resolution and 64 disparities. However, its averaged error rate is 17.24%. Though the two hardware implementations achieve remarkable performance, the image resolutions are limited by the on-chip memories, due to relatively high storage requirements or less efficient hardware design. In Chapter 5, we provide a comparison between our implementation and all of the above mentioned references.

## 2.4 Design Considerations and Targets

In order to enable real-time processing speed while preserving high stereo matching accuracy, we considered the following aspects to choose an algorithm and make adaptations for our implementation.

### 1. Matching accuracy

Our target implementation should achieve less than 10% averaged error rate.

#### 2. Robustness

Frames to match in stereo matching come from two different cameras and hence might exhibit very different luminance or radiometric variations, incurring a severe matching cost bias to which some stereo matching cost functions are very sensitive. Our implementation should also be robust, i.e., none or slight matching accuracy variation in this situation.

### 3. Real-time Implementations

Our design targets for at least 50 frames per second with programmable resolutions, and high-definition stereo matching is desired.

#### 4. Implementation Complexity

Our design should avoid complex computations such as divisions and square root calculations.

#### 5. Implementation Scalability

The proposed hardware structure should scale well with the maximum allowed resolution and disparity range. Our desired target is HDTV resolution.

Compared with software approaches, the major benefit of using FPGA or ASIC is the great flexibility in logic and data path design, which offers extreme parallelism in data flow and pipelined processing. Therefore they enable highly efficient and optimized designs and implementations. Based on the related work and our investigation, we believe customized hardware design is the most suitable approach for our proposed algorithm. Since FPGAs provide great resources for parallel computing and fast prototyping, we choose FPGA to implement our algorithm. To achieve a fast prototyping and enable future developments, we select Terasic DE3 development board as the development platform. The board contains Altera EP3SL150 FPGA and rich peripherals like JTAG UART port, DDR2-SDRAM, camera interfaces and DVI extension card and so on.

## Stereo Matching Algorithm: Software-Hardware Co-Design

In this chapter, we introduce the proposed stereo matching algorithm which is modified from Adaptive Cross-Based Local Stereo Matching proposed by Zhang et al. [49]. We modify this algorithm in order to make it more robust and more hardware friendly. Key to the best processing throughput is to fully pipeline all processing steps, i.e. with source image pixels come progressively in scanline order, a new income pixel gets its disparity at the end of the pipeline after a certain pipeline latency, and valid disparities also come successively in scanline order, synchronized with the input pixel rate. To enable fully pipelined implementation, parallelization is also important to provide all required data at the entrance of a pipelined processing module.

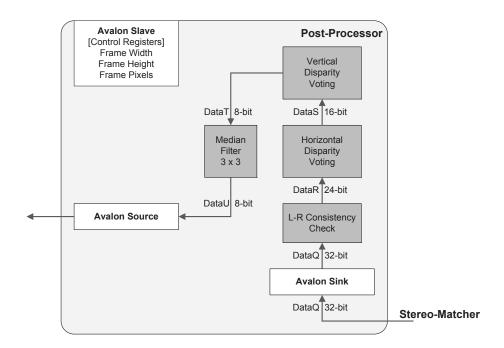

Our proposed algorithm and corresponding hardware pipeline design are introduced together in a top-down approach. Section 3.1 discusses the overview of the whole stereo matching processing and proposed data-level parallelism. The full pipeline is divided into three major processing blocks, i.e., pre-processing, stereo matching and post-processing. In hardware their functions are performed by corresponding Pre-Processor, Stereo-Matcher and Post-Processor, which are introduced in three subsections of this chapter.

## 3.1 Overview of the Stereo Matching Pipeline

Overview of the stereo matching processing flow is presented in Figure 3.1, corresponding to the aforementioned pseudo algorithm code (see Figure 2.6). Clearly the embedded computing loops cause the major problem for efficient implementations. If design follows this diagram, e.g., using state machines, raw stereo image data has to be read repeatedly into the processing module, which not only prolongs processing time but also exhausts external memory bandwidth.

According to our research, the disparity evaluation loop can be unrolled and all following processing modules are also parallelized accordingly. The parallelized data flow is illustrated in Figure 3.2. In the parallelized computing, matching costs with different hypothetical disparities are computed and aggregated mutually independently. As shown in the figure, multiple concurrent computing paths are employed to enable the parallelization. In principle any number of parallel paths are supported by the algorithm, but in practice this number is usually limited by the available hardware resources.

Our proposed hardware design follows the parallelized data flow, with pipelined processing at each algorithmic module. Although the cameras and image rectifications are shown in the figure, they are not implemented with this thesis work. The purpose

Figure 3.1: Sequential stereo matching processing flow Modified functions by this thesis work are shaded

Figure 3.2: Parallelized stereo matching processing flow Modified functions by this thesis work are shaded

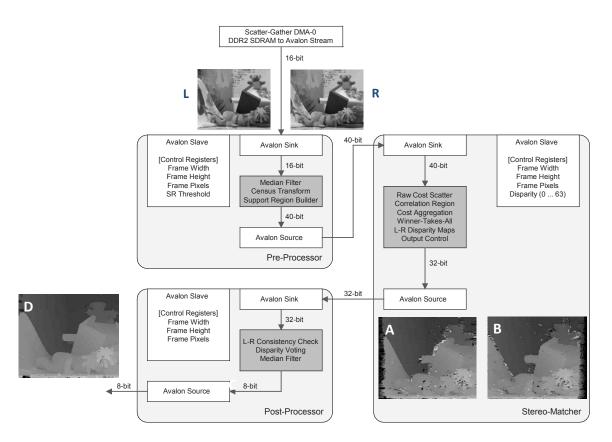

of their presence is to show that the left and right images are processed independently before the actual stereo matching starts; and their pixel coordinates must be synchronized to ensure a valid stereo matching processing. Processing modules shown in Figure 3.2 are categorized into three higher level modules, i.e., the Pre-Processor, Stereo-Matcher and Post-Processor. Their functions and inputs/outputs are shown in Figure 3.3. DMAs and Avalon interfaces are implemented for SoC integrations, which

Figure 3.3: Stereo matching pipeline and functions

will be introduced in Chapter 4. The hardware pipeline processing sequence is explained below.

- 1. The DMA transfers a pair of stereo frames to the Pre-Processor, with only luminance intensities. Synchronized luminance pixels from the left and right image are packed into one 16-bit data word.

- 2. The Pre-Processor performs median filter, census transform and support region construction on left and right frame independently and sends its transformed images to the Stereo-Matcher.

- 3. The Stereo-Matcher first computes the raw matching cost and overlapped support region at each pixel according to different hypothesis disparities. Then all the costs in an overlapped support region are aggregated; costs with different hypothesis disparities are processed independently in parallel.

- 4. Aggregated costs of all disparity hypothesis are presented to the WTA module by the cost aggregation module, and the best disparity is selected by a tree-based minimum value searching structure.

- 5. In the Stereo-Matcher, two disparity maps are generated for the left and right image respectively, denoted as image A and B in Figure 3.3.

6. The Post-Processor receives two disparity maps and support region data from the Stereo-Matcher, performs L-R consistency check, local disparity voting and median filter to detect occluded regions and improve the disparity map quality. The Post-Processor outputs the final disparity maps.

Each processor also contains several control registers for run-time parameter configuration, these parameters include image resolution, disparity range and some threshold values. In the following sections, we present the proposed algorithm functions together with the corresponding hardware design. We also provide the latency calculations based on 100MHz operation clock with the selected EP3SL150 FPGA. If some functions become critical paths with another device technology, it is required to implement more pipeline stages.

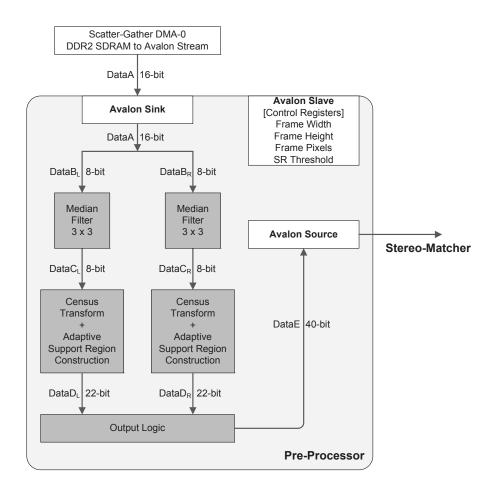

## 3.2 Design of the Pre-Processor Pipeline

Figure 3.4: Pre-Processor internal processing pipeline

The internal processing pipeline of Pre-Processor is shown in Figure 3.4. Each data word in the pipeline is comprised of several fields. Since most processing modules require data from left and right video frames simultaneously for parallel computing, the corresponding data word also contains both. In the Pre-Processor, left and right frames are processed independently, and corresponding data words are marked with 'L' or 'R' subscripts.

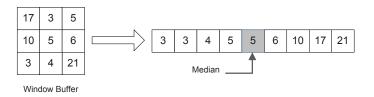

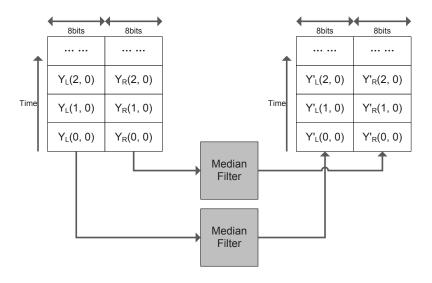

#### 3.2.1 Median Filter

We have applied a  $3 \times 3$  median filter to each raw frame pixel to remove impulsive noises. The function of a median filter is shown in Figure 3.5. Input (DataA) to the median filter module is a systolic stream carrying a combined data word with both left and right luminance pixels in progressive scanline order (see Figure 3.6). Computations on the left and right frames (DataB) are performed independently in

Figure 3.5: Median filter

parallel, and the output from the median filter module is the filtered data stream (DataC), in synchronization with the input pixel rate.

Figure 3.6: Median filter data stream

To get the median value from a  $3 \times 3$  array, we first prepare all the 9 pixels in a window buffer and afterwards they are captured simultaneously by a follow-up sorting module, which delivers the median value in a few pipeline cycles. The pixel buffer window slides over the whole frame and provides a new  $3 \times 3$  pixel array in every valid pipeline cycle, therefore after the initial latency for preparing the first window content and sorting the 9 values, we get continuous filtered pixels synchronized with the input pixel rate.

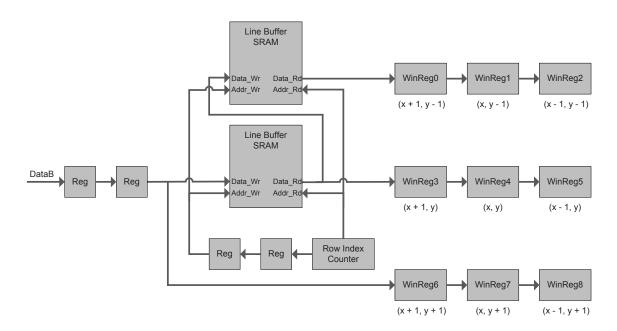

Because the pixel stream comes in scanline order, and a  $3 \times 3$  filter window is required for each pixel, 2 horizontal lines and 3 shift register arrays of length 3 are used to form a valid filter window. The structure and interconnections of line buffers and shift registers are illustrated in Figure 3.7. In the implementation, each line buffer stores one scanline of 8-bit luminance pixels, and each WinReg contains one 8-bit luminance pixel. The  $Row\ Index\ Counter\ cyclically\ counts\ from\ 0\ to\ (frame\ width - 1)\ and\ provides\ read/write\ addresses\ for\ the\ line\ buffer\ memory\ blocks.$  Because the line buffer\ memory has a 2-cycle read latency, its write address and write data are also delayed by 2 cycles to match the processing sequence. This module prepares all the required pixels for computing the median for the center pixel p(x,y), buffered in WinReg4.

Figure 3.7: Line buffers and registers in a median filter

The depth of a line buffer is determined by the maximum allowed frame width. A 1024  $\times$  8 SRAM block supports any frame width no larger than 1024. For an input pixel p(x,y) from DataB stream, it has to wait for

$$2 (read \ latency) + frame \ width + 2 (WinReg3 \ and \ WinReg4)$$

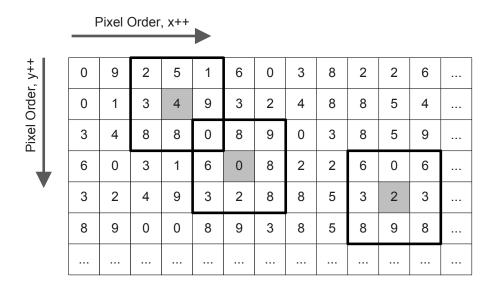

cycles to arrive in WinReg4. As pixels come in continuously, the 3  $\times$  3 pixel window also slides over the whole frame in scanline order (see Figure 3.8; the four boundary pixel rows/columns are not filtered, by-passing the sorting module) and provides all neighboring pixels of each center pixel simultaneously for the following sorting module.

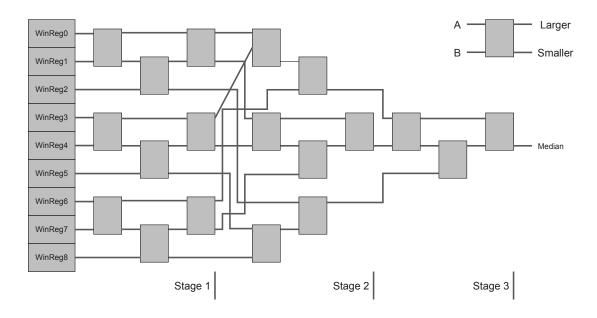

The 9 luminance values in a filter window are captured by a sorting module to get the median of them. We have adopted the median sorting structure proposed by Vega-Rodrguez et al. [41] and implemented suitable pipeline stages. The implemented median sorting module is shown in Figure 3.9. Each basic building block in this systolic array is a combination of a comparator and two multiplexers, which performs a basic sorting function on two unsigned values. The full array is divided in 3 pipeline stages so the desired median is available after 3 valid pipeline cycles.

Median filtering is performed on the left and right frames independently in parallel, and the output streams of this module are filtered stereo frames (DataC in Figure 3.4). The pipeline latency of the median filter module is given by Equation 3.1.

$$Latency_{mf} = frame \ width + C_{mf} \tag{3.1}$$

In the equation  $C_{mf}$  is a small constant value depending on the above mentioned read latency, shift register cycles and actual implemented pipeline stages. Quantitative reports of the latencies are presented in Chapter 5.

Figure 3.8: Slide window for a median filter

Figure 3.9: Median filter sorting array

#### 3.2.2 Census Transform and Adaptive Support Region Construction

#### 3.2.2.1 Census Transform

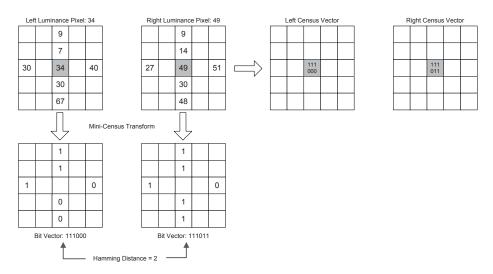

Census transform is a process extracting relative information for the center pixel from its neighbors, and its output is a bit vector encoding the relative information. Census transform has a few variants depending on different patterns of selected neighbor pixels; the one we have adopted is the *Mini-Census* algorithm proposed by Chang et al. [4],

and the transform is illustrated in Figure 3.10.

Figure 3.10: Mini-Census transform

In the transform, each square in the census window represents a (median filtered) 8-bit luminance pixel, but only the pixel locations marked with values are considered for the two example center pixels. If the luminance of a neighbor pixel under consideration is larger than that of the center pixel, the corresponding bit is set to '0', otherwise '1'. All of the comparison results form a 6-bit vector as the output of a mini-census transform. In the later *Raw Cost Scatter* module, the cost function is to compute the hamming distance between two hypothesis pixel's mini-census vectors.

Using census transform and hamming distance as cost function has been proved to be very robust to radiometric distortions [19], and much more hardware-friendly than other methods e.g., Rank filter and Normalized cross-correlation (NCC). Another important advantage of census transform is that it saves two valuable bits by converting an 8-bit luminance pixel to a 6-bit census vector. In SAD based cost computation, the maximum raw cost of two pixels is 255 (8-bit storage), while in hamming distance calculations the maximum raw cost is only 6 (3-bit storage). If also consider the cost aggregation over a support region, the mini-census transform significantly reduces the memory requirements.

#### 3.2.2.2 Adaptive Support Region Construction

Aggregating matching cost in an adaptive support region is the key idea of the Variable-Cross algorithm. The approach of adaptive support region construction is to decide an upright cross for each pixel  $p(x_p, y_p)$  in the input frame. As shown in Figure 3.11, this pixel-wise adaptive cross consists of two orthogonal line segments, intersecting at the anchor pixel p. The cross of each pixel is defined by a quadruple  $\{h_p^-, h_p^+, v_p^-, v_p^+\}$  that denotes the left, right, up, and bottom arm length, respectively (see Figure 3.12). Since the cross-based support region is a general concept, there are a variety of approaches to

Figure 3.11: Local adaptive cross and support regions on an image

(a) A pixel-wise adaptive cross defines a local support skeleton for the anchor pixel, e.g., p. (b) A shape adaptive full support region U(p) is dynamically constructed for the pixel p, integrating multiple horizontal line segments H(q) of neighboring crosses. (c) Sample shape adaptive local support regions, approximating local image structures appropriately.

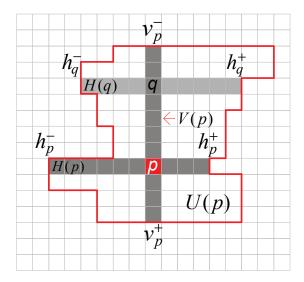

Figure 3.12: Adaptive support region representation

It shows the configuration of a local upright cross  $H(p) \cup V(p)$  for the anchor pixel p, and the constructed full support region U(p). Pixel q is on the vertical segment V(p).

decide the four adaptive arm lengths. Here we implement an efficient approach based on luminance similarity: for each anchor pixel  $p(x_p, y_p)$  in the frame, luminance difference evaluations are performed in the four directions on its consecutive neighboring pixels in order to find out the largest span  $r^*$  in each direction. The computation of  $r^*$  is formulated in Equation 3.2.

$$r^* = \max_{r \in [1,L]} \left( r \prod_{i \in [1,r]} \delta(p, p_i) \right)$$

(3.2)

In the equation  $p_i = (x_p - i, y_p)$  and L is a preset maximum allowed directional arm length;  $\delta(p_1, p_2)$  is an indicator function evaluating the luminance difference between

the pixel  $p_1$  and  $p_2$  based on a given threshold value  $\tau$ .

$$\delta(p_1, p_2) = \begin{cases} 1, & |Y(p_1) - Y(p_2)| \le \tau \\ 0, & \text{otherwise} \end{cases}$$

(3.3)

The value of  $\tau$  is a run-time configurable parameter that controls the confidence level of luminance similarity. It is set empirically by the end user according to different applications. Its effect on the benchmark images are discussed in Chapter 5.

Based on the four arms  $\{h_p^-, h_p^+, v_p^-, v_p^+\}$ , the adaptive cross of pixel p are given by Equation 3.4.

$$\begin{cases}

H(p) = \{(x,y)|x \in [x_p - h_p^-, x_p + h_p^+], y = y_p\} \\

V(p) = \{(x,y)|x = x_p, y \in [y_p - v_p^-, y_p + v_p^+]

\end{cases}$$

(3.4)

The shape adaptive full support region U(p) of each frame pixel is therefore built by integrating all the horizontal segments H(p) of the pixels residing on the vertical segment V(p).

The output of the support region construction module is a data word containing the four arm lengths  $\{h_p^-, h_p^+, v_p^-, v_p^+\}$ , which are used in the Cost Aggregation and Disparity Voting modules.

#### 3.2.2.3 Combined Hardware Processing

Because both of the mini-census transform and the adaptive support region construction are window-based processing, and they all operate on the same data stream (filtered stereo frames), they are designed to share the same line and window buffers. The left and right frames are again processed independently in parallel.

In order to compute all the four arm lengths simultaneously,  $2 \times L_{max}$  lines of the filtered frame are stored in line buffers and a shift register matrix of  $(2 \cdot L_{max} + 1) \times (2 \cdot L_{max} + 1)$  is used for providing all the neighboring pixels for the centered anchor pixel. The configurations and interconnections of line buffer memory blocks are similar with these in the median filter module (see Figure 3.7), with different number of blocks. One important hardware parameter in this module is the maximum allowed arm length  $L_{max}$ , which is set to 15 in our implementation. Its effect on the matching accuracy is duscussed in Chapter 5. To make clear illustrations in Figure 3.13  $L_{max}$  is set to 7.

In Figure 3.13, the centered pixel's mini-census transform and support region are ready to be computed. Computing the census transform is straightforward: the luminance values of shaded pixels are compared with the center pixel's luminance concurrently and the census vector is obtained by packing the result bits in a certain order. The four arm lengths in the center pixel's adaptive cross are also computed in parallel; take the  $h_p^+$  for example, first all 7 pixels in the anchor pixel's right direction are evaluated concurrently and the corresponding  $\delta(p, p_i)$  values are obtained. Then the packed  $\delta(p, p_i)$  values are sent to a priority encoder that performs the function of Equation 3.2.

Because the input data stream to this module carries consecutive video frames, pixels in this window are possibly not form the same frame. To solve the problem, pixel row

Figure 3.13: Census transform and adaptive support region construction window

and column counters are also implemented in this module. The outlier pixels in this window are masked before computing the census vector and support regions.

The pipeline latency of the census transform and adaptive support region construction module is given by Equation 3.5.

$$Latency_{ctsr} = 15 \times frame \ width + C_{ctsr}$$

(3.5)

#### 3.2.3 Output Logic

The output logic packs all the data words produced by the Pre-Processor and prepare additional data fields required by the following Stereo-Matcher processor. Content of the 40-bit output data word is listed below, from most significant bit to least. A data field followed by 'L' indicates a value from the left frame, and 'R' indicates a value from the right frame, with the same pixel coordinates.

- 4-bit all '0'

- 6-bit mini-census vector L

- $\bullet$  8-bit horizontal arms  $(h_p^- \text{ and } h_p^+)$  L

- 6-bit mini-census vector R

- 8-bit horizontal arms  $(h_{p'}^- \text{ and } h_{p'}^+) R$

- 8-bit vertical support region segment  $(v_p^- \text{ and } v_p^+)$  L

Because we set the maximum allowed arm length to 15, a 4-bit word is sufficient to represent any value in the quadruple  $\{h_p^-, h_p^+, v_p^-, v_p^+\}$ . The 4-bit all '0' bits are simple used to pad the data word width to a multiple of 8, as required by the Avalon bus.

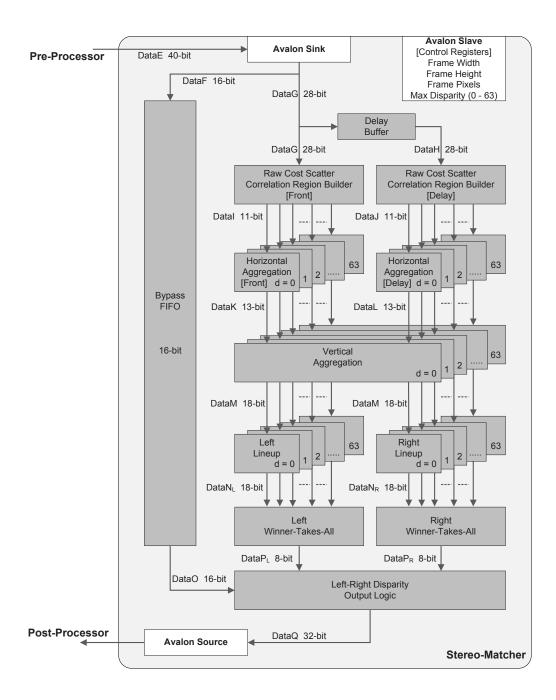

## 3.3 Design of the Stereo-Matcher Pipeline

Figure 3.14: Stereo-Matcher processor internal processing pipeline

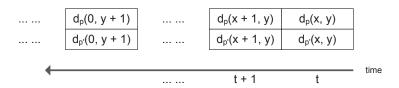

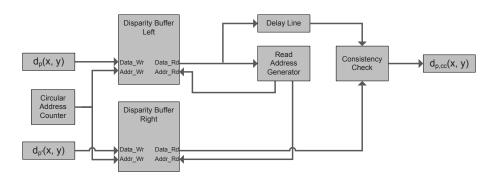

Overview of the internal processing pipeline of the Stereo-Matcher processor is shown in Figure 3.14. The Stereo-Matcher processor operates on the data stream coming from Pre-Processor (DataE). The data from the Pre-Processor is always associated with a new stereo frame pair and passes through each pipeline stage in the Stereo-Matcher. Once the final results (L-R disparity maps) are available, the Stereo-Matcher sends

them to the Post-Processor. In the figure, before the vertical aggregation step there are two major data paths, denoted by *Front* and *Delay* respectively. They work for the data reuse technique implemented in the vertical aggregation. After the vertical aggregation step, there are still two major data paths, but now they are associated with the left and right disparity map respectively.

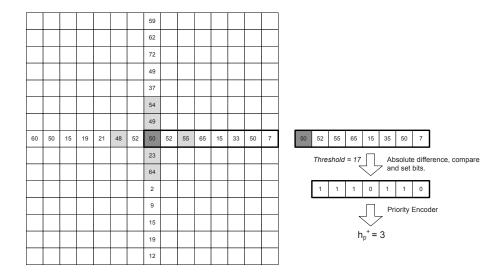

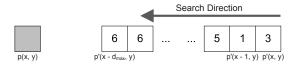

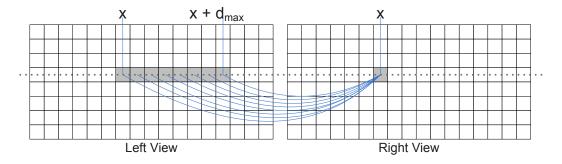

As a local stereo matching algorithm, the key emphasis of its processing is to find out the best correspondence for a pixel p(x, y) in the left frame, from a local area in the right frame. Because the stereo frames are already rectified, this local area shrinks to a 1-dimensional segment of pixels located on the same scanline (see Figure 3.15). Given

Figure 3.15: 1-dimensional local search area

The number at each pixel location indicates the raw matching cost

a pair of hypothetical correspondences, i.e., p(x, y) in the left frame and p'(x', y') in the right frame, we define the following variables before inferring the best correspondence. Here the coordinates of p and p' are correlated with a hypothetical disparity d ranging from 0 to  $d_{max}$  (the maximum disparity under consideration), i.e., x' = x - d and y' = y.

- Raw Matching Cost: the Hamming distance between their Mini-Census vectors i.e.,  $HammingDist(cv_p(x,y), cv_{p'}(x',y'))$

- Correlation Region: the overlapped area of the two pixels' support regions

- Aggregated Matching Cost: the accumulated raw matching costs in their correlation region i.e., AggCost(x, y, d)

- Aggregated Pixel Count: the total number of pixels in their correlation region i.e., PixCount(x, y, d)

- Averaged Matching Cost: the aggregated cost divided by the aggregated pixel count in their correlation region i.e.,

$$AvgCost(x, y, d) = \frac{AggCost(x, y, d)}{PixCount(x, y, d)}$$

(3.6)

Therefore the best correspondence is defined by the hypothetical pair that gives the minimum averaged matching cost. The hypothetical disparity d that leads to the minimum averaged cost is recorded as the result disparity  $d_p(x, y)$  for pixel p(x, y). All the computed disparities form the disparity map for the left frame.

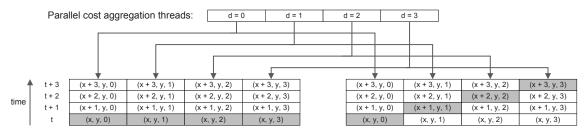

For a given pixel p(x, y) in the left frame, cost aggregations in correlation regions with different hypothetical disparities are independent on each other; so it is possible to compute them all in parallel, and all the aggregated costs and pixel counts are available

simultaneously as the output of all parallel computing threads. Therefore the minimum averaged cost is picked out using the *Winner-Takes-All* method. To make this parallel computing successful, two key problems have to be solved:

- 1. Raw matching costs are provided for all computing threads simultaneously.

- 2. All computing threads are fully pipelined to match the input pixel data rate.

Solutions to the two problems are explained in Section 3.3.1 and Section 3.3.2 respectively. The Stereo-Matcher processor provides disparity maps for both left and right stereo frames, which are sent to the Post-Processor for *L-R Consistency Check* that detects mismatched correspondences caused by occlusion. The modules for generating both disparity maps are introduced in Section 3.3.3. We also present a method with aggregation data reuse technique in Section 3.3.2, which significantly reduces the required line buffer memories.

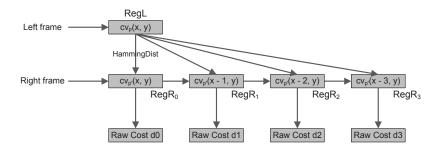

#### 3.3.1 Raw Cost Scatter and Correlation Region Builder

The task of this module is to provide raw matching costs for all hypothetical disparities simultaneously. Input data stream to this module carries the census vectors  $cv_p(x, y)$  and  $cv_{p'}(x', y')$  for pixel p(x, y) in the left frame and pixel p'(x', y') in the right frame, respectively. Because the x' coordinate of pixel p' ranges from x to  $x - d_{max}$  for all hypothetical disparities, an array of shift registers are used to buffer the full disparity range for pixel p. Assuming  $d_{max} = 3$ , as shown in Figure 3.16, in a certain pipeline

Figure 3.16: Scattering raw matching costs using shift register arrays

cycle t, the census vector  $cv_p(x,y)$  arrives in the RegL while in the same cycle the census vector  $cv_{p'}(x,y)$  also arrives in  $RegR_0$ ; meanwhile all the census vectors stored in the RegR array shift to the right for one position. Therefore the desired Hamming distances  $HammingDist(cv_p(x,y),cv_{p'}(x-d,y))$ , with d ranging from 0 to 3, are available simultaneously by comparing all registers' content in RegR array with the content in RegL.

Similarly, the horizontal arms  $(h_p^-, h_p^+, h_{p'}^-, h_{p'}^+)$  for both p and p' are buffered using the same technique. Since the correlation support region is defined as the overlapped area

of two pixel's support regions, the horizontal arms in each correlation support region  $(h_{pc}^-, h_{pc}^+)$  are obtained by selecting the shorter arm.

$$h_{pc}^{-} = \begin{cases} h_{p}^{-}, & h_{p}^{-} \leq h_{p'}^{-} \\ h_{p'}^{-}, & \text{otherwise} \end{cases} h_{pc}^{+} = \begin{cases} h_{p}^{+}, & h_{p}^{+} \leq h_{p'}^{+} \\ h_{p'}^{+}, & \text{otherwise} \end{cases}$$

As a result, this module provides 4 parallel streams of data, carrying the raw matching costs and horizontal arms in scanline order for 4 hypothetical disparities. The 4 streams are scattered into 4 parallel data paths, which lead to the follow-up cost aggregation modules. In the next cost aggregation step we use fixed vertical arms for correlation region, i.e.,  $v_{pc}^- = v_{pc}^+$ . The adaptive vertical arms  $v_p^-$  and  $v_p^+$  are used in the later disparity voting step; they are put in the FIFO to bypass the cost aggregation modules.

The latency of this module is a small constant, depending on the implemented pipeline stages.

$$Latency_{rcs} = C_{rcs} (3.7)$$

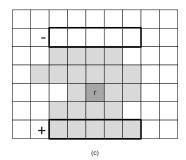

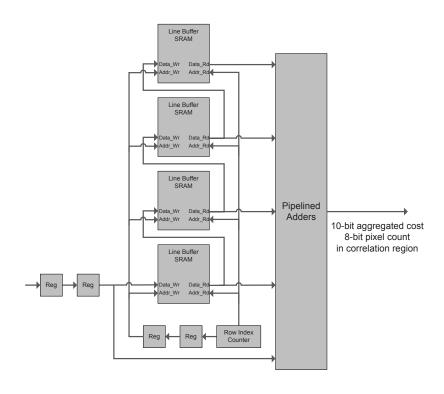

#### 3.3.2 Parallelized Cost Aggregations

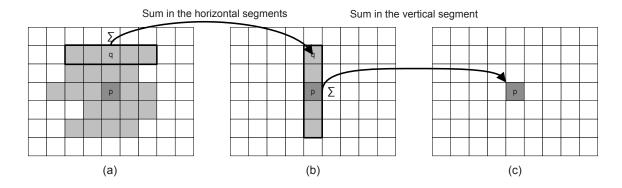

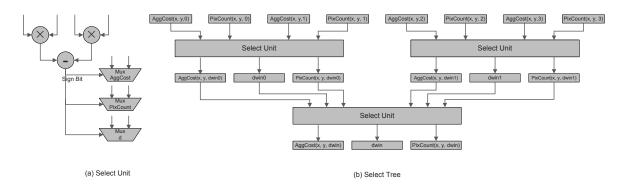

After the raw cost scatter module, cost aggregations are able to be performed on all raw cost streams in parallel, and mutually independently by  $(d_{max} + 1)$  parallel computing threads. For each thread, aggregating all the raw costs in a correlation region is achievable through the line buffer plus register matrix configuration used in the Pre-Processor. But the arbitrarily shaped 2D support region makes this solution not hardware friendly. We solve this problem by decomposing the 2D aggregation into two orthogonal 1D aggregations, i.e., a horizontal step followed by a vertical one (see Figure 3.17).

Figure 3.17: Two orthogonal 1D aggregations

Figure 3.17 (a) shows the correlation region of pixel p (shaded region), and q indicates a pixel lying in the vertical segment of p. First we aggregate all the raw costs in the horizontal segment of pixel q. As pixel q slides along the vertical segment of pixel p, we obtain the aggregated cost in the horizontal segment of each q. Next we aggregate all the horizontally aggregated costs along the vertical segment of pixel p, as shown in

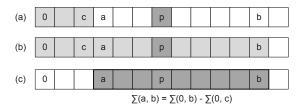

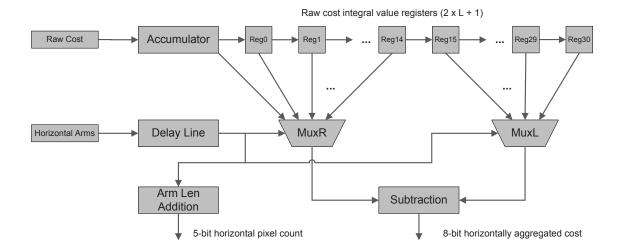

Figure 3.17 (b - c). The aggregated cost by this two orthogonal 1D process is exactly identical with the aggregation result in the 2D region, and meanwhile this technique also simplifies the hardware implementation.