# A Toolchain for Streaming Dataflow Accelerator Designs for Big Data Analytics

Defining an IR for Composable Typed Streaming Dataflow Designs

M. A. Reukers

# A Toolchain for Streaming Dataflow Accelerator Designs for Big Data Analytics

Defining an IR for Composable Typed Streaming Dataflow Designs

by

M. A. Reukers

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Friday July 8, 2022 at 10:00 AM.

Student number: 4227220

Project duration: November 25, 2021 – July 8, 2022

Thesis committee: Prof. dr. H. P. Hofstee, TU Delft, supervisor

Dr. ir. T. G. R. M. van Leuken, TU Delft Dr. ir. Z. Al-Ars, TU Delft Voltron Data

An electronic version of this thesis is available at http://repository.tudelft.nl/.

## **Abstract**

Tydi is an open specification for streaming dataflow designs in digital circuits, allowing designers to express how composite and variable-length data structures are transferred over streams using clear, data-centric types. This provides a higher-level method for defining interfaces between components as opposed to existing bit- and byte-based interface specifications.

In this thesis, an open-source intermediate representation (IR) is introduced which allows for the declaration of Tydi's types. The IR enables creating and connecting components with Tydi Streams as interfaces, called Streamlets. It also lets backends for synthesis and simulation retain high-level information, such as documentation. Types and Streamlets can be easily reused between multiple projects, and Tydi's streams and type hierarchy can be used to define interface contracts, which aid collaboration when designing a larger system.

The IR codifies the rules and properties established in the Tydi specification and serves to complement computation-oriented hardware design tools with a data-centric view on interfaces. To support different backends and targets, the IR is focused on expressing interfaces, and complements behavior described by hardware description languages and other IRs. Additionally, a testing syntax for the verification of inputs and outputs against abstract streams of data, and for substituting interdependent components, is presented which allows for the specification of behavior.

To demonstrate this IR, a grammar, parser, and query system have been created, and paired with a backend targeting VHDL.

### **Preface**

This thesis proved to be considerably challenging, and an excellent learning experience. It was very interesting to explore various technologies around hardware accelerator design, compilation, and language parsing, and learn some of the specifics of VHDL syntax while implementing the backend.

I would like to thank Prof. dr. Peter Hofstee for his continued support during my work on the thesis, and for pushing me to constantly evaluate the novelty and direction of my work. Likewise, I would like to thank Dr. Zaid Al-Ars, Yongding Tian and the entire ABS Group for the interesting meetings and support over this time. Finally, I would like to thank Johan, Matthijs Brobbel and Joost, for their ideas and the extensive discussions, for answering my questions around the Tydi specification, and for so thoroughly reviewing my paper before I submitted it to ICCAD.

Some of the contents of this thesis also appear in "An Intermediate Representation for Composable Typed Streaming Dataflow Designs", a paper which I submitted to ICCAD 2022. [35]

M. A. Reukers Delft, July 2022

# Contents

| 1 | Intro | oduction                                                | 1 |

|---|-------|---------------------------------------------------------|---|

|   | 1.1   | Problem Statement                                       | 1 |

|   | 1.2   | Methodology                                             |   |

|   | 1.3   | Contributions                                           | 3 |

| 2 | Bac   | kground                                                 | 5 |

| _ |       | Stream Processing                                       |   |

|   |       | 2.1.1 Data Streams                                      |   |

|   |       | 2.1.2 Interface Specifications                          |   |

|   | 2.2   | Tydi                                                    |   |

|   |       | 2.2.1 Element-manipulating Types                        |   |

|   |       | 2.2.2 Streams                                           |   |

|   |       | 2.2.3 Physical Streams                                  |   |

|   | 2.3   | Alternatives                                            |   |

|   | 2.0   | 2.3.1 Hardware Description Languages                    |   |

|   |       | 2.3.2 Design Tools and High-Level Synthesis             |   |

|   |       | 2.3.3 Frameworks and Embedded Domain-Specific Languages |   |

|   |       | , , ,                                                   | , |

| 3 | Inte  | rmediate Representation: Composition                    | _ |

|   | 3.1   | Type Declarations and Interface Design                  |   |

|   |       | 3.1.1 Type Declarations                                 |   |

|   |       | 3.1.2 Interfaces as Contracts                           |   |

|   |       | 3.1.3 Compatibility                                     |   |

|   | 3.2   | Component Composition and Implementation                | ) |

|   |       | 3.2.1 Structural Composition                            | ) |

|   |       | 3.2.2 Linked Implementations                            |   |

|   | 3.3   | Recommendations for Language and Compiler Features      |   |

|   |       | 3.3.1 Type Parameters                                   | 2 |

|   |       | 3.3.2 Generation                                        | 3 |

|   |       | 3.3.3 Intrinsics                                        | 1 |

|   |       | 3.3.4 Annotations                                       | 3 |

|   | 3.4   | Project Structure and Reusability                       | 7 |

|   |       | 3.4.1 Project Properties                                | 3 |

|   |       | 3.4.2 Import Behavior                                   | 3 |

|   |       | 3.4.3 Notes on Reusability                              | 9 |

| 1 | Into  | rmediate Representation: Specification 3 <sup>r</sup>   | 1 |

| • |       | High-level Assertions                                   | • |

|   | 7.1   | 4.1.1 Parallel by Default                               |   |

|   |       | 4.1.2 Sequences                                         |   |

|   |       | 4.1.3 Descriptive Errors                                |   |

|   |       |                                                         |   |

|   |       | 4.1.4 Asserting Equality                                |   |

|   | 4.0   | 4.1.5 Issues with Explicit Assignment and Comparison    |   |

|   | 4.2   | Proof of Concept                                        |   |

|   |       | 4.2.1 Physical Transfers                                |   |

|   |       | 4.2.2 Demonstration                                     |   |

|   |       | 4.2.3 Results and Future Work 38                        | ۲ |

viii Contents

|   | 4.3       | Complex Test Cases                                            |

|---|-----------|---------------------------------------------------------------|

|   |           | .3.1 Limitations of High-Level Assertions                     |

|   |           | .3.2 Using Test Streamlets for Verification                   |

|   |           | .3.3 Substitution                                             |

|   | 4.4       | etting up Subjects                                            |

| _ | luan un l | mentation 43                                                  |

| 5 |           |                                                               |

|   | 5.1       | Query System                                                  |

|   | 5.2       | Grammar and Parser                                            |

|   |           | .2.1 Parsers                                                  |

|   |           | .2.2 Grammar                                                  |

|   |           | .2.3 Parser Implementation                                    |

|   | 5.3       | (HDL Backend                                                  |

|   |           | .3.1 Components and Organization                              |

|   |           | .3.2 Linked Implementations                                   |

|   |           | .3.3 Structural Implementations                               |

|   |           | .3.4 Additional and Future Functionality                      |

|   | 5.4       | xample                                                        |

|   | 5.5       | artial Implementations                                        |

| 6 | Eval      | ation 55                                                      |

| • | 6.1       | ydi Specification                                             |

|   | 0         | .1.1 Directly nested Streams which must both be retained      |

|   |           | .1.2 Significance of Strobe and Index Signals                 |

|   |           | .1.3 Transferring Empty Outer Sequences at Lower Complexities |

|   |           | .1.4 Indicating Inactive Lanes at Lower Complexities          |

|   |           | .1.5 Minor Inconsistencies                                    |

|   | 6.2       | Readability                                                   |

|   | 0.2       | .2.1 Readable Output                                          |

|   |           |                                                               |

|   | 6.0       | .2.2 Type Identifiers                                         |

|   | 6.3       | ·                                                             |

|   | 6.4       | darser                                                        |

|   |           | .4.1 Merits of Chumsky                                        |

|   |           | .4.2 Issues Using Chumsky                                     |

|   |           | .4.3 Recommendations for TIL Parser                           |

| 7 | Con       | usion 63                                                      |

|   | 7.1       | Conclusions and Summary                                       |

|   | 7.2       | ecommendations for Future Work                                |

| Α | Con       | lete TIL Example 65                                           |

|   |           | Backend Example 69                                            |

|   |           | ·                                                             |

|   |           | Specification 71                                              |

| D | AXI4      | IL Definition and VHDL Output 73                              |

1

## Introduction

In order to transfer streaming data between components within digital circuits, designers have a choice to either design their own interfaces, or use general interface specifications such as Intel's Avalon-ST [21] or Arm's AXI4-Stream [7]. By using an interface specification, it is easier for other designers to connect components, as the signals and how they relate to data transfers are standardized. This can promote reuse, and is used by hardware design tools to provide IP (Intellectual Property) libraries and automate integration [9, 24].

The aforementioned specifications do not specify how data structures are represented, however, and as a result designers must still design, document and share these representations. Additionally, the IP integration tools are proprietary, reducing the simplicity of integrating such IPs outside of these specific tools. Addressing the first issue, Peltenburg et al. proposed Tydi (Typed dataflow interface) [32], an open specification which allows designers to explicitly define the data which is being transferred by providing a type system for composite and variable-length data structures, in addition to defining how data elements are organized in transfers and the requirements on transfers. This thesis aims to address the second issue, by utilizing the Tydi specification as part of an IR (intermediate representation) for defining interfaces and connecting components.

The goal of the IR is not to serve as a complete hardware description language, but to provide a simple and robust way to declare Tydi's types, define interfaces and connect components which adhere to the Tydi specification, serving as part of a toolchain in order to integrate and reuse components within and across projects. To this end, the IR is not capable of directly implementing behavior, but should instead be combined with transaction-level verification to *specify* intended behavior.

To demonstrate the potential of such an IR, and to explore potential approaches towards implementing a toolchain built around it, a prototype toolchain has been conceived and implemented. This consists of a query system, which tracks and computes information defined through the IR, a grammar called TIL (Tydi Intermediate Language) and parser, as a more portable, text-based way of representing designs in the IR, and finally a VHDL backend to emit designs defined in the IR.

#### 1.1. Problem Statement

While much research is focused on developing and accelerating algorithms for streaming data in both hardware [31, 34] and software [22], many designs for low-level hardware still have to transfer streams over interfaces which are either custom or based on generic, bit- and/or byte-oriented specifications such as AXI4-Stream [7] and Avalon-ST [21]. As a result, higher-level information about data structures and how streams of data are organized over transfers must be devised and implemented by designers, and are not reflected by the declaration of the interface in a traditional HDL.

Some of this design effort can be alleviated through the use of high-level synthesis: tools such as Vivado HLS can be employed to leverage C, C++ or SystemC combined with IP-blocks using *ap\_fifo* or AXI4-Stream to handle data streams [4], while synthesizing compilers such as Optimus [17] have been developed in the past to leverage StreamIt [42], a language specifically for streaming applications. At the same time, many researchers are working on improved hardware description languages and IRs, such as Chisel [11], FIRRTL [23] and LLHD [40].

2 1. Introduction

These are not suitable replacements for a higher-level interface specification, however: HLS tools either obfuscate the interfaces between low-level hardware and/or use proprietary IRs and tools to connect components, making reuse more difficult. While the HDLs and IRs mentioned are aimed at more general hardware designs, so still require custom interfaces for streaming data transfers.

As such, the aim of this thesis is to develop a free, open-source IR for defining high-level streaming dataflow interfaces mapped onto hardware and for connecting these interfaces. This would complement existing HDLs and IRs which describe behavior, and enable components designed in higher-level front-end languages for HLS to propagate more type information to the resulting interfaces.

Long-term, the Accelerated Big Data Systems group aims to develop a toolchain for streaming dataflow accelerator designs for big data analytics. The work done for this thesis is part of such a toolchain, providing a grammar and parser, query system for the IR, and a compiler to VHDL. At the same time, Yongding Tian has been working on a front-end language for his thesis and as another component of this toolchain, enabling designers to express behavior as well.

#### 1.2. Methodology

As the aim of this thesis is not only to define an intermediate representation, but contribute to a toolchain, there was an increased focus on *implementing* such tools. Essentially, by creating and iterating on a "vertical slice" of a partial toolchain, it is possible to evaluate the effectiveness of the IR and the feasibility of the proposed toolchain overall.

An ideal vertical slice would have the following properties and components:

- 1. A (partial) specification for the intermediate representation; i.e., what (additional) concepts should it be able to express.

- 2. A means to integrate a compiler, using one or both of:

- (a) A grammar and a parser, taking a text-based representation and allowing a subsequent backend to interpret the results.

- (b) A query system not unlike the one employed by the Rust compiler [37], which would allow a backend to perform queries to retrieve and/or compute information from a definition in the IR, reducing the need for separate optimizing passes. (As such, the information stored in the system does not necessarily need to be the result of a (single) parser, but can be input programmatically.)

- 3. A backend for emitting designs defined in the IR as a conventional hardware description language suitable for simulation and synthesis. Due to familiarity and broad support, this language will be VHDL(-93). The backend should be capable of as many of the following as possible:

- (a) Emit Streamlets with structural implementations; i.e., Streamlets which contain and connect other Streamlets.

- (b) Link behavioral implementations.

- (c) Emit a testbench based on high-level assertions defined in the IR.

Based on interim progress towards these features and results of finished (prototype) implementations, the next step would be to:

- Continue working on and/or expanding specific features. (The initial implementation is successful and/or promising, or the feature requires further evaluation.)

- Revise goals and/or the IR specification. (The feature is not feasible, or an alternative appears more effective.)

- Omit them and instead recommend their implementation as future work. (The feature is feasible and promising, but cannot be implemented satisfactorily within the time frame of this thesis.)

As an example, if a concept expressed in the IR is impossible or very difficult to express in VHDL (or any target HDL), the solution would be to either revise the IR to include more information (i.e., the concept is possible to express, but requires more/different input), or to summarize these findings in this thesis and remove it or recommend it as future work.

The results of this methodology are described in Chapter 6.

1.3. Contributions 3

#### 1.3. Contributions

The contributions of this thesis can be summarized as follows, with references to the relating chapters and sections:

- An intermediate representation for composition and linking behavior This thesis proposes an intermediate representation for composing streaming dataflow designs, using the Tydi specification. It features means to define Streams and the data they carry, to create interfaces with clock and reset domains tied to specific ports, create components (Streamlets) and connect them, and link to implementations of behavior. Sections 3.1 and 3.2

- Recommendations for further improvements to the intermediate representation After evaluation of the intermediate representation, it was determined certain language and compiler-oriented features would improve the intermediate representation's ability to describe designs and aid backends in emitting them to a target language. Specifically, the addition of type parameters (3.3.1), the inclusion of code generation constructs (3.3.2), the addition of limited, behavioral intrinsic functions (3.3.3), the inclusion of annotations for backends (3.3.4) and changes to the existing representation to improve the readability of the output (6.2). This thesis also discusses potential difficulties when implementing them, as features need to translate well to many potential target languages.

- Proposals for (and partial, preliminary implementation of) a high-level testing framework

— As the intermediate representation primarily exposes typed interfaces, tests can be performed

as high-level assertions against transfers of typed data (Sections 4.1 and 4.2), while the inclusion

of substitutions helps when testing more complex or incomplete dependencies (4.3). This thesis

also discusses the potential problems (and some solutions) when setting up (resetting) subject

components in Section 4.4.

- A complete toolchain as proof of concept, from intermediate representation to target language As part of the work on this thesis, a query system for the intermediate representation (5.1), a VHDL backend (5.3), and a text-based grammar (Tydi Intermediate Language, TIL) and parser (5.2) were implemented. These are provided in a free, open-source repository along with a simple example application which allows a user to compile a TIL file to VHDL, described in Section 5.4.

- Validating the Tydi interface specification By implementing the Tydi interface specification programmatically, a number of unaddressed and contradictory situations were brought to light, for which the specification should be amended. Section 6.1

- Evaluation of the intermediate representation's ability to describe interfaces and connections The intermediate representation was evaluated for its ability to produce human-readable and traceable output in Section 6.2. The evaluation of its effectiveness in representing streaming interfaces and connections between them is described in Section 6.3, using the existing AXI4 and AXI4-Stream standards as a reference point.

$\sum$

# Background

#### 2.1. Stream Processing

#### 2.1.1. Data Streams

Stream processing refers to means of processing data which is produced or consumed incrementally, rather than a set of data which is known and stored ahead of time on the system. The order of the data and rate at which it arrives cannot necessarily be controlled, and the number of elements is potentially unbounded, requiring the system to process elements as they arrive and before the next element does.

Examples of practically unbounded data streams would be analyzing real-time weather events or human behavior, but even limited sets of data can be treated as streams when timing is critical to performance, such as when encrypting and decrypting data to and from a storage medium. As a result, stream processing has been actively researched for over 20 years, with software paradigms and hardware acceleration being worked on in parallel in attempts to improve performance and establish effective data and execution models [15, 22].

**Software models** In software, stream processing has been approached in many different ways to various ends. More recent examples of stream processing include Kafka Streams, which is a stream processing library of Apache Kafka [39], and Spark Streaming [49, 5] (now Structured Streaming [6]). Both aim to provide a useful subset of high-level functions for processing data streams, mapped onto their existing domains. There are also more wholesale approaches, such as StreamIt [42], which is a language specifically designed for streaming applications.

**Hardware Acceleration** In hardware acceleration, the constraints of stream processing are less uncommon; hardware designs are already heavily constrained by timing, and do not necessarily have a notion of state. More specifically addressing recent needs of stream processing, there are a number of frameworks such as Fleet [43] and S2FA (Spark-to-FPGA-Accelerator) [48] which use FPGAs to accelerate streaming operations which conventional processors may struggle with.

#### 2.1.2. Interface Specifications

When designing digital circuits for stream processing hardware accelerators, internal communication will likewise take the form of unbounded streams of messages between sources and sinks. There exists a number of interface specifications to ensure these streams of data are correctly transferred and represented: For example, ARM devised the AXI4-Stream protocol [7], and Intel defines the Avalon-ST interface specification [21].

Both protocols are able to optionally organize sequences of data into packets over transfers; AXI4-Stream uses the *last* signal to indicate that a transfer is the last in a sequence making up a packet, while Avalon-ST uses the *startofpacket* and *endofpacket* signals to do the same. Likewise, both interface specifications incorporate means to indicate whether data is being transferred from a source (using a *valid* signal) and can be transferred to a sink (using a *ready* signal), and allows for valid transfers to be indicated as entirely or partially empty. These properties ensure that sequences of data can be transferred over time and without needing to account for the rate at which individual elements arrive, nor for the total size of a sequence.

6 2. Background

Additionally, by using a standard and well-defined interface, designers can not only ensure that transfers are consistent within a project, but can share components between different projects and even across organizations. For example, this is employed by AMD/Xilinx [3] and Intel [20] to establish libraries of IP cores for designs implemented on their respective FPGAs. Finally, when representing streams of data in high-level synthesis, such standards ensure data can be consumed from or produced for such IP cores; e.g., Vivado HLS uses AXI4-Stream and *ap\_fifo* for this purpose [4].

#### 2.2. **Tydi**

The Tydi specification and type system was introduced by Peltenburg et al. [32] and defines an abstract way to describe data structures transferred over hardware streams. Tydi promises to reduce the design effort of creating hardware for streaming dataflow computing, by providing clear and intuitive ways to map composite, variable-length data structures onto a hardware streaming protocol. An open-source repository and documentation [44] expanding on the specification and providing example code for mapping Tydi's streams onto VHDL component ports is now available.

The specification defines five *logical types*: the stream-manipulating Stream type, and the element-manipulating Null, Bits, Group and Union types.

#### 2.2.1. Element-manipulating Types

Element-manipulating types are how Tydi represents kinds of data; that is to say, these types represent arbitrary data as well as specific data structures.

- The *Null* type is for transfers of one-valued data, its only valid value is null. This can be used to indicate (part of) a transfer being valid and active, but no data being transferred.

- The Bits(N) type represents a data signal of N bits. It is used to transfer arbitrary data.

- The *Group* type contains named *fields*, which are themselves any logical type. Groups are compositions, and represent all fields being active simultaneously.

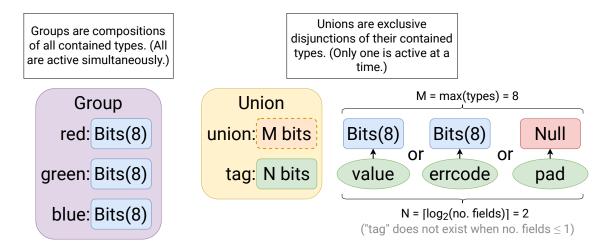

- The *Union* type is comparable to the Group type, in that it contains named *fields* of logical types. Unlike Groups, Unions are exclusive disjunctions; only one field may be active at a time. Figure 2.1 further illustrates the difference.

Field *Names* of Groups and Unions consist of (ASCII) letters, digits and/or underscores [45], and may not contain two or more consecutive underscores. Names within a Group or Union must be unique, cannot start or end with an underscore, and cannot start with a digit. The latter constraints ensure broad compatibility with potential target HDLs, while consecutive underscores are reserved for use in *Path Names*, discussed in Section 2.2.3.

Figure 2.1: An illustration of the difference between Group and Union types.

The element-manipulating types alone can represent many data structures, for example:

2.2. Tydi 7

• Bits(N) can be used to transfer primitive data types such as numbers, booleans and characters.

- A Union of Null and another type can indicate optional data.

- Groups can be used to directly represent records of data.

However, as Streams are also logical types, Groups, Unions and Streams themselves can carry further nested logical Streams, each with their own data and properties.

#### 2.2.2. Streams

The Stream type adds a further layer of flexibility to these element-manipulating types. It does not only represent the physical stream and signals carrying the element-manipulating types, but also features properties for further describing data structures. Notably, Streams have a *dimensionality* property, which indicates whether the data being transferred is part of a sequence. In hardware, this is translated to a "last" signal; when this signal is driven high, it indicates that the data being transferred is the last element in a sequence, and a Stream with a higher dimensionality will have multiple last bits, to indicate nested sequences.

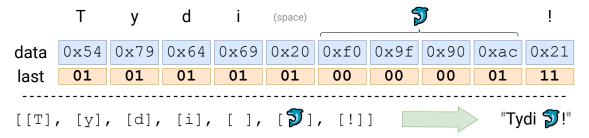

A *last* signal is typically used to reflect sequences or other kinds of variable-length data. Both AXI4-Stream and Avalon-ST lack Tydi's ability to assign multiple *last* bits to a transfer or element, however. This gives Tydi interfaces more flexibility in naturally reflecting different data types, or combining multiple variable-length data structures. Figure 2.2 illustrates how this can be used to better reflect a UTF-8 encoded string transferred as bytes; the inner dimension is used to represent UTF-8 characters, which can be between 1 and 4 bytes long, and the outer dimension is used to represent the string as a whole. Of course, UTF-8 itself already encodes whether a byte is part of a group making up a character, but this simplifies processing downstream, and alleviates the need for similar encoding on other data types. For instance, when representing a video with an arbitrary resolution, three dimensions can be used to indicate the end of a row, the end of a frame, and the end of the video overall respectively.

Figure 2.2: Using multiple last bits to transfer a UTF-8 encoded string as bytes, where the inner dimension is used to easily distinguish groups of bytes making up single characters.

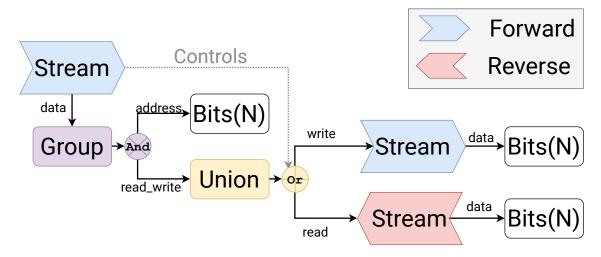

Another noteworthy property is *direction*, which indicates whether a Stream flows in the same direction as its parent, or in reverse. This allows designers to express that certain Streams have a relation: As an example, a Group can have both a "Forward" and "Reverse" Stream to indicate that interdependent data is transferred between the sink and source, such as a memory address and the data retrieved from that address. Giving a parent and child Stream different directions can also be used to indicate that one Stream (direction) directly controls another; expanding on the previous example, consider a Stream which can be used to read and write to memory, but which prevents reading and writing simultaneously. One way to implement this is as follows: The parent Stream carries a Group with the fields "address" and "read\_write", "address" is simply a Bits(N) type, but "read\_write" is a Union carrying both a Forward "write" and Reverse "read" field. As illustrated by figure 2.3, this allows the parent Stream to control whether read or write is active by setting the Union's *tag*.

In addition to dimensionality and direction, Streams have properties for describing how transfers should be organized in space and time, the specifics of their implementation will be described in the next section:

Throughput is a positive, rational number indicating how many elements are expected to be transferred per individual handshake, or relative to its parent Stream. The number of element lanes is a Stream's throughput multiplied by that of all parent Streams, rounded up to a natural number.

8 2. Background

Figure 2.3: A Union of Streams with opposite directions allows a parent Stream to control whether data should be read or written.

- Synchronicity refers to how strong the relation between a child Stream and its parents are with

regards to dimensional information. "Sync" indicates that for each element transferred on the parent, the child has a matching transfer, while "Desync" indicates that the child may have transfers

of arbitrary size. Both options also have a "Flat" variant, which results in redundant last signals

on the child being omitted.

- Complexity is a number which encodes guarantees on how elements of a sequence are transferred. In brief, lower complexities place more constraints on source streams, such as by requiring that transfers of sequences occur over consecutive cycles.

- A *keep* property can be used to ensure a *logical* Stream is synthesized into physical signals, as nested Streams may otherwise be combined into a single physical stream.

Finally, in the event these properties are insufficient for a use-case, Streams can also have a *user* signal carrying an element-manipulating type. This user signal can be used to provide additional information independent from transfers or clock cycles.

#### 2.2.3. Physical Streams

Many of the properties described in the previous section have no impact on the kinds of data being transferred, but instead affect *how* it will be transferred. These changes are reflected in the *physical streams* [46] resulting from a logical Stream definition. A physical stream "canonically" consists of some variation on the following signals:

- ready: 1 bit, when driven high, this indicates that the sink device is prepared to accept transfers.

- valid: 1 bit, when driven high, this indicates that the source device is transferring valid data.

- data:  $E \times N$  bits, carries an element-manipulating logical type (of size  $0 \le E < \infty$  bits), and may be composed of one or more data lanes  $(1 \le N < \infty)$ .

- *last*:  $D \lor D \times N$  bits, indicates whether a particular transfer, or element, represents the end of one or more sequences. If complexity  $C \ge 8$ , there is a last signal/slice per element lane, otherwise, this signal refers to the entire transfer. Its size is equal to dimensionality D.

- endi:  $0 \vee \lceil log_2(N) \rceil$  bits, the "end index": Only exists when the number of element lanes N > 1, and complexity  $C \geq 5$  or dimensionality  $D \geq 1$ . Indicates the end of all active element lanes in a valid transfer.

- $stai: 0 \lor \lceil log_2(N) \rceil$  bits, the "start index": Only exists when the number of element lanes N > 1, and complexity  $C \ge 6$ . Indicates the start of all *active* element lanes in a valid transfer. Can be combined with *endi* to form a range of active elements, but cannot be used to mark an entire transfer as inactive. (The value of stai must be smaller than or equal to that of endi.)

2.2. Tydi 9

•  $strb: 0 \lor 1 \lor N$  bits, the "strobe" signal: When dimensionality  $D \ge 1$ , can be used to mark all of a transfer's elements inactive, as a single bit. When complexity  $C \ge 7$ , all element lanes N have an individual strb bit, allowing for individual element lanes to be marked inactive, rather than the ranges supported by the start- and end indices.

• *user*: *U* bits, this signal carries the element-manipulating type defined in the Stream's *user* property, its properties are entirely user-defined.

Any signals sized 0 are omitted entirely, and Tydi allows for the *ready* and *valid* signals to be omitted when the physical stream is always ready or always valid, respectively. Physical streams are not necessarily directly equivalent to logical Streams; this is a result of Tydi making Streams themselves logical types, allowing for nested Streams in a Stream's data property. As the *data* signal itself cannot represent a Stream, such logical Streams will be split into multiple physical streams.

The exact procedures for converting logical types into physical streams are defined in the Tydi specification as the *split*, *fields* and *synthesis* functions. In brief:

- Logical Streams are split into a list of named physical streams. Names of physical streams are

based on potential field Names of Groups and Unions, which are concatenated hierarchically as

Path Names; Path Names are emitted as Names joined by two underscores. As a root Stream or

directly nested Stream is not part of a field, split Stream names may be empty. When two Streams

are directly nested, they may be flattened, combining their properties into a single Stream (by for

example multiplying their throughputs and determining an absolute direction).

- Non-Stream logical types are converted into *fields*, which are lists of named bitfields, based on their size. These fields eventually make up the *data* signal. As before, Names of Group and Union fields are used to determine these names, and are concatenated into Path Names. Likewise, a field name may be empty if it is directly part of a Stream's data or user property.

- The *synthesis* function converts all *split* Streams into a list of named *PhysicalStream(E,N,D,C,U)* definitions:

- E is the element content, derived from the fields function on a split Stream's data property.

- N is the number of element lanes, which is equal to the split Stream's throughput [t].

- D is the physical stream's dimensionality, equal to that of the split Stream.

- − C is the physical stream's complexity, equal to that of the split Stream.

- *U* is the *user content*, derived from the *fields* function on a split Stream's *user* property.

The *synthesis* function also accounts for defining separate, user-defined signals which flow in parallel to a physical stream (in addition to the *user* signal), but this is not currently relevant to the use-case of specifically generating Tydi-compliant interfaces. It is also worth noting that the output of the *split* function is not discarded after *synthesis*: The *direction* property is not part of physical streams, so must be retrieved from their respective Stream definition.

The Tydi specification also permits alternative representations of physical streams, bundling element types into aggregate/record types in the target language. For example, in VHDL, rather than simply using a bit vector to represent a Group's data over multiple lanes, it is possible to instead use a record type with field names corresponding to those of the Group's, and then using an array of this record type to represent the data signal overall. However, it recommends that any "outer" interfaces still use the "canonical" representation described at the start of this section, to ensure interoperability between potential IP blocks.

The *number of element lanes N* applies to the data signal, multiplying the total bit width defined by *element content E*. It does not apply to the *user* signal.

The *complexity*  $\mathcal{C}$  affects how elements and sequences are organized over element lanes and consecutive lanes. Overall, a lower complexity imposes more restrictions on a source, in the inverse, this results in a higher complexity making it more difficult to implement a sink. As an example, a complexity of  $\leq 2$  requires that elements of an inner sequence are transferred over consecutive cycles by a source, while higher complexities allow it to stall independently from the sink. The specification currently defines 8 levels of complexity [46]. Table 2.1 illustrates the cumulative changes between complexity levels.

10 2. Background

| Complexity | Dimension<br>Information        | Sequence Transfer Requirements                                                                                                                          | Notes                                                                                                                                                                                      |

|------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | Per transfer,<br>on active data | Entire sequence must be transferred in consecutive lanes, with all possible lanes active, aligned to lane 0, over consecutive cycles.                   | Uses endi (end index) to pad the end of a sequence when using multiple element lanes. (E.g., when fitting a sequence of 2 elements in 3 element lanes.)                                    |

| 2          | Per transfer,<br>on active data | Innermost sequences (dimension 0) must be transferred in consecutive lanes, with all possible lanes active, aligned to lane 0, over consecutive cycles. | May set valid = '0' after an innermost sequence.                                                                                                                                           |

| 3          | Per transfer,<br>on active data | Innermost sequences (dimension 0) must be transferred in consecutive lanes, with all possible lanes active, aligned to lane 0.                          | May set valid = '0' after any transfer.                                                                                                                                                    |

| 4          | Per transfer                    | Innermost sequences (dimension 0) must be transferred in consecutive lanes, with all possible lanes active, aligned to lane 0.                          | May use strb = '0' with valid = '1' to transfer dimension information after a transfer with active data.                                                                                   |

| 5          | Per transfer                    | Innermost sequences (dimension 0) must be transferred in consecutive lanes, <i>aligned to lane 0</i> .                                                  | Does not need to fill all element lanes until done transferring an innermost sequence. (May split an innermost sequence of 2 elements over 2 transfers, even when 2+ lanes are available.) |

| 6          | Per transfer                    | Innermost sequences (dimension 0) must be transferred in consecutive lanes.                                                                             | Can use stai (start index) to set the starting lane.                                                                                                                                       |

| 7          | Per transfer                    | None                                                                                                                                                    | Can use strb (strobe) to set individual lanes inactive.                                                                                                                                    |

| 8          | Per <u>element</u>              | None                                                                                                                                                    | Has a last signal per element lane.                                                                                                                                                        |

Table 2.1: The changes between Tydi's *complexity* levels. For clarity, constraints which will be omitted next complexity level are *italicized* and marked red, and any potential replacement constraint or property is underlined.

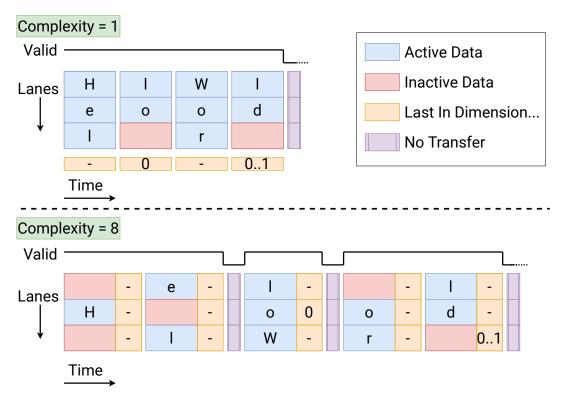

Figure 2.4 illustrates how a higher *complexity* allows for transfers to be organized differently. When transferring [[H, e, 1, 1, o], [W, o, r, 1, d]], at *complexity* = 1 all elements must be aligned to the first lane, *last* data is asserted per transfer, and all data must be transferred over consecutive cycles and lanes. At *complexity* = 8, there are no requirements for how elements are aligned, transfers may be postponed (asserting *valid* low), and *last* data is asserted per lane, and may be postponed (using an inactive lane to assert *last* for a previous lane or transfer).

The *synchronicity* and *keep* properties of the original logical Stream type are not directly reflected by the physical stream, but do affect how they are synthesized and how transfers are expected to behave. As mentioned in the previous section, *synchronicity* s indicates whether the transfers of a child Stream are constrained by its parent Stream, and only applies if the child Stream's *dimensionality* d > 0.

• If s=Sync, for each element in the parent Stream, one sequence must be transferred on the child Stream. E.g., both the parent and child Stream have *dimensionality* d=1, and the parent Stream features a Group(a: Bits(1), b: Stream(data: Bits(1), ...), where b is this child Stream. To transfer the sequence [ (a: 1, b: [1, 0, 1]), (a: 0, b: [0, 0]) ], the parent Stream will use its data signal to transfer the value of a, while the child Stream will transfer the sequence on b independently, but before the next transfer on the parent Stream. The

2.2. Tydi 11

Figure 2.4: Streams determine which signals are used and valid to organize elements in transfers, and how transfers are organized over time

child physical stream will have d=2, and duplicate the *last* information of the parent transfer. (Resulting in a transfer [ (a: 1), (a: 0) ] on the parent, and [ [1, 0, 1], [0, 0] ] on the child.)

- If s = Flatten, the child Stream will behave as Sync, but the child physical stream will not duplicate the (redundant) *last* information of the parent physical stream. (Hence, the previous examples transfer would become [1, 0, 1], [0, 0] for the child.)

- If s = Desync, the child Stream will still inherit the parent's dimensionality (i.e., if the parent and child have d = 1, the resulting child physical stream will still have D = 2), but its transfers will not be constrained by those on its parent Stream. I.e., its transfers will still be shaped as  $[\ ]$ ,  $[\ ]$ , but they will have no (apparent) relation to the parent Stream's transfers. This does not preclude designers from using the *user* signal to provide context, instead.

- s = FlatDesync is the equivalent of *Flatten* for *Desync*, in that it does not duplicate the parent Stream's dimensionality for the child Stream. In effect, the child Stream now has no apparent relation to the parent Stream.

In the event two Streams are directly nested, they are *flattened* by default in the *split* function: Rather than a parent Stream with no *data* signal, whose only purpose is to transfer the outer *last* bits, the function will instead produce a single Stream combining the dimensionalities of parent and child. This process will only occur when both the *data* and *user* signals of the parent would otherwise be empty. The *keep* property mentions before prevents a Stream from being *flattened* regardless of its data and user signals being empty. This partly avoids issues with the parent and child Stream not having unique names (which would otherwise be derived from the Group or Union field name for the child Stream), requiring one replace the other, though the use of the *keep* and *user* properties can nonetheless introduce this issue, as discussed later in Section 6.1.1.

12 2. Background

#### 2.3. Alternatives

This thesis aims to simplify development of streaming dataflow accelerator designs for big data analytics by improving reusability and making it easier to connect different components through the use of the Tydi specification. Outside of the application of Tydi, however, these are existing problems for which solutions are already being developed, and which can ostensibly be further adapted to suit more specific needs. This section lists alternative solutions which have been considered, and how they align with the goals of the IR and toolchain.

#### 2.3.1. Hardware Description Languages

Strictly speaking, it would be possible to implement hardware accelerators with Tydi interfaces in existing hardware description languages manually, rather than building a toolchain to emit them. It would also be possible to limit the scope of the toolchain, by directly compiling from a more abstract front-end language to an existing HDL, or by providing a standard library of components, or by generating templates in a target HDL. In particular, there are a number of languages which promote reuse and/or are suited to expressing streaming data processing efficiently.

Lime [10], StreamIt [42] and HPVM [25] are able to express streaming data processing, with StreamIt in particular being designed for this purpose alone. StreamIt and HPVM are not explicitly designed as hardware description languages, but nontheless map very well to hardware (using a suitable synthesizing compiler in StreamIt's case [17]).

Chisel [11], FIRRTL [23] and LLHD [40] are more general HDLs which aim to simplify expression of hardware and hardware interfaces, and promote reuse. All have since been incorporated into the CIRCT (Circuit IR Compilers and Tools) project [27] as different parts of an overall toolchain.

The IR is, first and foremost, an extension of the existing Tydi interface specification. In that it codifies the rules for designing and connecting interfaces, how to define data types, and how to transfer data. As such, the goal is not to outright replace any of the aforementioned languages, but serve a complementary role by expressing Tydi streams and Streamlets as efficiently as possible. It also aims to propagate high-level information down to the languages a backend might emit, including documentation. By intentionally limiting the IR's scope compared to conventional HDLs, it should also serve as an intermediary for very different kinds of front-ends. For instance, its focus on composable interfaces can also be applied to more visually-oriented design tools, such as Vivado's "block design" view discussed in the next section.

#### 2.3.2. Design Tools and High-Level Synthesis

At the same time, there are multiple ongoing efforts to improve the tools used for designing such hardware accelerators, in the form of new hardware description languages [11, 23], intermediate representations [40] and compilers [27], high-level synthesis based on software programming languages [30], and more general program representations for heterogeneous systems [34, 25].

**High-level synthesis** can help programmers who are unfamiliar with HDLs and hardware design in general to more quickly implement their ideas. This is especially relevant when the goal is to use a hardware accelerator to speed up an algorithm which was previously implemented in software, as it allows for these ideas to be translated more easily. However, the ideas expressed in HLS rarely propagate very far to the resulting hardware descriptions and simulations, making it more difficult to perform verification and analyze issues and targets for optimization from the same perspective. Some of this can be addressed by also building simulators for the high-level language, and introducing additional directives and macros to better match hardware, as in SystemC [2].

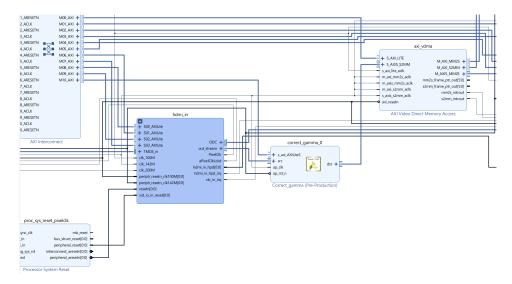

Comprehensive **design tools** may also incorporate ways to encourage and improve avenues for reuse. For instance, Vivado includes a "block design" view which allows for individual components (IP blocks) to be connected using standard AXI4(-Lite/-Stream) or *ap\_fifo* interfaces, as shown in Figure 2.5. This is combined with Xilinx's existing HLS tools and IP block library [3] to allow for integrating these components as well, such as through pragmas (directives) indicating particular parameters or variables in a high-level language should correspond to a given interface type [4].

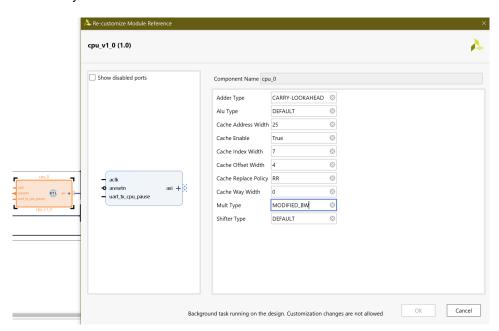

Such tools are undoubtedly easy to use, especially when IP blocks surface configuration items to allow them to be modified from the same visual block design interface, as in Figure 2.6. The reusability enabled by such tools is less clear, however; they are proprietary, and any components designed for them must adhere to the constraints set by Vivado to enable the most desirable features, such as easily

2.3. Alternatives

Figure 2.5: Using Vivado's "block design" interface to connect individual IP blocks using, among others, AXI4-Lite interfaces.

connected interfaces and exposed configuration properties. It can very much promote reuse, but only within a closed ecosystem.

Figure 2.6: Using Vivado's "block design" interface to configure properties of certain IP blocks.

#### 2.3.3. Frameworks and Embedded Domain-Specific Languages

One approach to building hardware accelerators for a specific domain is to instead surface hardware-oriented language and/or methods within an existing language. For instance, Fleet [43], S2FA [48] and Melia [47] all promise to easily integrate FPGA accelerators into existing software data processing environments. These improve ease-of-use by bringing the accelerator designs closer to their intended targets, and enable reuse of accelerator "kernels" throughout a project or over different projects. This approach can be quite effective, but is too specific to benefit hardware accelerator design reuse across different domains and potential processing frameworks.

# Intermediate Representation: Composition

The primary purpose of the intermediate representation is to define Tydi Streams and Interfaces, and use these to compose Streamlets. This chapter describes the ways this functionality is implemented, its use-cases, and the considerations which have gone into the IR's design overall.

To illustrate the various IR concepts described in this chapter, there are listings in TIL (Tydi Intermediate Language) a grammar for the IR which was designed (and can be parsed) as part of the overall prototype toolchain. For more details on TIL and its implementation, see Section 5.2.

#### 3.1. Type Declarations and Interface Design

#### 3.1.1. Type Declarations

As described in Section 2.2, Tydi features 5 "logical types", with Groups, Unions and Streams themselves having fields or properties containing these logical types. The IR must be able to represent definitions of all types, account for being able to nest types, and enable comparison between types to ensure compatibility between interfaces. Listing 3.1 demonstrates expressions for the four "element-manipulating" types.

```

Null

Bits(7)

Group (

field_name1: Bits(2),

field_name2: Bits(7),

)

Union (

field_name1: Bits(7),

field_name2: Group (

field_name1: Bits(2),

field_name2: Bits(3),

),

field_name3: Null,

)

```

Listing 3.1: Expressions for element-manipulating logical types in TIL

The "stream-manipulating" logical type, *Stream*, is defined in a similar way. As it is the only type with explicit properties, however, it also features a number of *default* values for some of these properties when they are omitted, as explained in the comments in Listing 3.2. Note that Streams can be used in the exact same way as any other logical type, in that it can be used as a Group or Union's field,

or another Stream's *data* property; the only exception is the Stream's *user* property, which may only contain element-manipulating types.

Listing 3.2: Expression the stream-manipulating logical type in TIL

As tracking deeply nested types can become convoluted for a compiler emitting to the IR, and make the output hard to read, the IR also features the ability to declare types within a *namespace* and give them a unique identifier to track them by. Listing 3.3 showcases how these identifiers can be used; identifiers serve as an alternative to explicit type definition expressions.

```

namespace namespace name {

type bits type name = Bits(7);

type group type name = Group (

field name1: Bits(2),

field name2: bits type name,

type union type name = Union (

field name1: bits type name,

field name2: group type name,

field name3: Null,

type stream type name = Stream (

data: union type name,

dimensionality: 0,

synchronicity: Sync,

complexity: 4,

type parent stream type name = Stream (

data: stream type name,

dimensionality: 1,

synchronicity: Sync,

complexity: 4,

);

```

Listing 3.3: Statements declaring logical types in TIL

So as not to diverge from the Tydi specification, which does not feature identifiers as a property of logical types, these identifiers only exist as a property of the namespace, and should not affect the output of a compiler for the IR. That is to say, a *Bits(8)* is always the same as any other *Bits(8)*, regardless of the identifier it was given, and whether it was given an identifier at all. The merits and demerits of this approach are elaborated on in Sections 3.1.3 and 6.2.

In order to represent each type definition in the query system, each type definition is *interned*: Each distinct type is stored as an immutable entry in memory and tracked using a unique identifier. This has a number of advantages:

• It reduces the amount of data stored by the query system. (No need for multiple entries in memory for identical type definitions.)

- Types which contain nested types as fields or properties only need to contain the identifier, instead of a copy of the definition or a direct reference to memory.

- Comparison between types is trivial, as it is only necessary to compare intern identifiers: If types are different, their identifiers will be different, as well.

- The query system will not have to track different kinds of type expressions: Whether they are namespace identifiers or direct definitions, each type ultimately becomes an intern identifier.

#### 3.1.2. Interfaces as Contracts

As Section 2.2 would suggest, Tydi's types can convey a significant amount of information; not just what data is transferred, but also how it is transferred, and how sequences of elements relate to one another. In effect, a sufficiently detailed Stream definition can be treated as a *contract* between components (and in a sense, designers) on how a stream of data will be implemented.

The intermediate representation builds on this when declaring *Interfaces*. In its simplest form, an Interface represents a collection of ports on a component (Streamlet), each of which carries a logical Stream either into or out of the component. Any streamlet must have an interface; as a result, all streamlet definitions can be subsetted into interfaces, as shown in Listing 3.4. By default, backends are not expected to emit interface declarations which are not part of streamlet definitions, and the names of interface declarations should not have any effect on the resulting output. It is however allowed to define a streamlet without any implementation, consisting only of an interface - defining an interface without any ports is also allowed.

```

interface my_interface = (a: in stream, b: out stream);

streamlet my_streamlet = my_interface;

streamlet my_impl_streamlet = (

a: in other_stream,

b: out stream

) {

impl: ...

};

streamlet subsetted_streamlet = my_streamlet {

impl: ...

};

```

Listing 3.4: Statements declaring interfaces and streamlets in TIL

However, each Interface and its ports may also feature *documentation*. Distinct from comments on a grammar, documentation is an actual property of a port or interface, and is expected to be implemented by a backend, typically by generating matching comments on the related output. Documentation being propagated from higher-level descriptions to the actual computation-oriented design tools that the IR complements is primarily useful when either implementing a component based on an interface template, or when trying to identify how physical signals relate to their abstract definition.

While Tydi's Streams assume a single clock and reset signal, which together make up their clock and reset domain, regardless of how many physical streams they are composed of, the ports of an Interface do not need to rely on the same clock and reset signals. Instead, an Interface may have one or more uniquely named *domains* which represent a clock and reset signal, each of which is associated with one or more of the Interface's ports.

Subsequently, while the intermediate representation does not feature the ability to define a specific clock or how a reset signal should be handled, designers can use these domains to ensure multiple clock and reset signals are available on a component, and that ports which belong to different domains are not directly connected. In the event no domain is specified on the Interface, a default domain is instead created and assigned to all ports, as Tydi currently only defines Streams in the context of a clock.

It is worth noting, as a recommendation for future work, that the use of ready-valid signals *should* make it possible to represent fully asynchronous (clock-less) micropipelines [41] using Tydi. Even if the specification currently assumes the existence of a clock, many of the timing constraints enforced

through it can be replaced by the ready and valid signals serving as events for forward and reverse propagation.

#### 3.1.3. Compatibility

The ports of Interfaces are compatible with one another when they have the same logical type, appropriate directions (for each physical stream, there is a source and matching sink), and the same (clock) domain

A domain in Tydi and the IR consists of a clock and reset signal; while the reset signal does not have any specific constraints to the clock signal, the reset behavior, requiring the *valid* and *ready* signals to be driven low during a reset, is constrained by it. The Tydi specification generally assumes a single clock and reset signal, but this only applies in the context of a Stream and its compatibility with other Streams. Therefor, it is possible to surmise that a (clock) domain and a Stream are intrinsically linked; the compatibility of two interfaces using Tydi Streams is contingent on them being part of the same clock domain.

To reflect these properties, the IR assumes a single "default" domain, but allows for the definition of additional/alternative domains and for linking them to specific interface Streams; the actual clock speed is irrelevant to compatibility, only whether a designer indicates something is a different domain.

```

// As no domain has been defined, the "default" is assigned

(a: in stream, b: out stream) {

impl: {

// Sharing one domain, these are compatible

a -- b;

}

// Declaring new domains removes the default domain, and

// requires that they are assigned to individual ports.

<'a domain, 'b domain>(

a: in stream 'a domain,

b: out stream 'b domain,

) {

impl: {

// As these now have different domains, these are incompatible

a -- b;

}

}

```

Note that while types in the IR may be defined with identifiers, these identifiers are not a property of the logical type in question, and only exist within the namespace. This choice was made to restrict the IR to properties defined in the Tydi specification.

As a result, types with different names but otherwise identical properties are fully compatible; on an abstract level, this can be interpreted as a kind of implicit casting between types. Although when evaluating this with respect to readability of backend output, discussed in Section 6.2, and in light of the potential added value of a stricter type system, this approach may need to be reconsidered in the future. An alternative approach might make identifiers an intrinsic property of types, and separately support type aliases for functionality similar to the current behavior - depending on the language being targeted, such aliases could even be propagated to the backend.

However, while type identifiers are not currently relevant to compatibility, *field* identifiers are an actual property of the Group and Union types. Hence, a Group (a: Null) is not compatible with a Group (b: Null), regardless of whether they are physically identical.

```

type bits8 = Bits(8);

type byte = Bits(8);

// bits8 and byte are compatible

type a_group = Group(a: bits8);

type b group = Group(b: bits8);

```

```

type group_a = Group(a: byte);

// a group and group a are compatible, but neither are compatible with b group

```

Finally, while *complexity* is a property of the Stream type, the Tydi specification does conditionally allow Streams with different complexities but otherwise identical properties to be connected. Specifically, a physical *source* stream may be connected to a *sink* if its complexity is equal to or lower than that of the sink. Note however that this applies to physical streams: logical Streams do not have a notion of sinks and sources, and may contain child Streams which flow in reverse directions, resulting in them containing both sink and source physical streams.

As such, the IR considers the Streams of ports incompatible when their complexity is not identical. While the process of connecting compatible physical streams can be optimistically automated to improve reuse, as discussed later in Section 3.3.3, designers should generally strive for a shared, normalized complexity between Streams.

#### 3.2. Component Composition and Implementation

In addition to Interfaces, the IR introduces the ability to declare components, referred to as *Streamlets*. These Streamlets consist of an Interface and optionally an Implementation. In effect, there are two different kinds of Implementation for a Streamlet: a *structural* implementation, which can be used to combine instances of streamlets into a larger design, and a *link* to an implementation of behavior in the target language or format.

Streamlets are the intended output of a project; Types, Interfaces and Implementations are not expected to be included in a backend's emissions unless they are part of a Streamlet, but can be shared between IR projects.

As Streamlets always have an Interface, they can be *subsetted* to Interfaces, which can be used to express alternate implementations of the same component, e.g. when versioning a component or when substituting one for the purposes of testing as described in Section 4.3.

#### 3.2.1. Structural Composition

As the goal of both Tydi and the IR is to improve compatibility and reuse of primitive components, the IR features the ability to connect Streamlets to one another. The IR refers to this as a *Structural* implementation.

Structural implementations can contain *instances* of Streamlets and connections between ports of Streamlets. Instances consist of a local name and a reference to a Streamlet declaration, the ports of their interfaces are assigned separately through connections. If the parent interface has named domains, these must also be assigned to the Streamlet instance.

```

// Creating an instance with a default domain

instance_name = streamlet_name;

// Creating an instance and assigning domains

instance_name = streamlet_name<'parent_domain_name>;

// Or:

instance_name = streamlet_name<'streamlet_domain_name = 'parent_domain_name>;

```

Listing 3.5: Statements for instantiating instances of Streamlets in TIL.

Connections can be created between the ports of both Streamlet instances and the containing Streamlet which is being implemented, and require both ports to have identical types and clock domains (for the reasons described in Section 3.1.3). Connections are explicitly not "assignments", as the direction of a port is already known, and there is not necessarily one overall direction for a Stream type due to the possibility to define Streams which are *Reversed* (such as when representing request and response streams). Hence, the *source* and *sink* between two ports of a connection is determined during lowering for each resulting Physical Stream.

```

instance_name.instance_port1 -- instance_name.instance_port2;

instance_name.instance_port -- parent_port;

```

```

parent_port1 -- parent_port2;

```

Listing 3.6: Statements for connecting ports in TIL.

By default, the IR requires that each port of each Streamlet is connected to exactly one other port. Leaving ports unconnected is against the Tydi specification, which requires that a default signal is driven for omitted signals [46]. While HDLs such as VHDL and Verilog support one-to-many and many-to-one connections at a signal-level, these are not allowed by the IR due to the fact that ports represent Streams with handshake signals, which would need to be combined.

```

streamlet example_streamlet = <</pre>

parent domain1.

'parent_domain2,

parent_port1: in stream 'parent_domain1,

parent port2: out stream 'parent domain1,

impl: {

parent port1 -- parent port2;

// dom_example has two domains, one for ports a and d, and one for port b and c

different_domains = dom_example<'parent_domain1, 'parent_domain2>;

different_domains.a -- different_domains.d;

different_domains.b -- different_domains.c;

// By assigning them the same domain, a and b and c and d can nonetheless be connected

same domains = dom example<'parent domain1, 'parent domain1>;

same_domains.a -- same_domains.b;

same_domains.c -- same_domains.d;

// For clarity, when assigning domains it's also possible to specify

// which domain of the instance is being assigned to, rather than using their order.

explicit_doms = blank_doms<'c = 'parent_domain1, 'a = 'parent_domain2, 'b = 'parent_domain2>;

// It's also possible to mix named assignments with ordered assignments,

// provided the named assignments succeed all ordered assignments.

mixed_assignments = blank_doms/parent_domain2, 'c = 'parent_domain1, 'b = 'parent_domain2>;

```

Listing 3.7: A full Structural implementation in TIL.

While combining the *ready* signals of multiple sinks could be achieved with simple logical *and* expressions for a one-to-many connection, combining multiple transfers in a many-to-one connection has no clear, universally applicable, solution. Even the aforementioned one-to-many implementation is not universal, as some designs may call for only one of the many to alternately accept transfers. Finally, as a connection does not necessarily have a single direction, a one-to-many connection between ports may well contain physical many-to-one transfers.

Instead, the solution to unconnected and one-to-many ports would be to explicitly define their behavior. In the current implementation, that means designing specific Streamlets for this purpose; but as there is a common subset of expected behavior (drive default, sink and ignore input, transmit transfers to all in a one-to-many source-to-sink configuration, etc.), the ultimate goal would be to provide intrinsics which automatically implement this behavior, as described in Section 3.3.3.

#### 3.2.2. Linked Implementations

The intermediate representation intentionally omits expressions for implementing or simulating arbitrary behavior of components. Designing a language or set of expressions for functional hardware design and simulation is a difficult problem which is already being addressed by many researchers and organizations, as explained in Sections 2.1 and 2.3.1. Instead, "behavioral implementations" in the IR exist only as *links* to directories, which contain the relevant code in languages more suited for expressing behavior.

How these links are used is left up to the backend, though a simple use-case would be to create or copy a file in the target output language based on the Streamlet's name. As these are directories, multiple such files can exist side-by-side for different targets, and implementations do not need to be constrained to a single file; a linked directory could even be used to refer to a project or library consisting of multiple files, provided this exposes the Interface of the Streamlet being implemented.

It is worth noting that linked implementations are not to be treated like *imports*: A linked implementation is still fundamentally part of the IR project, and should be included with its sources/output. A link

should not refer to a common library directory, and linked implementations should use relative paths (relative to the project root), rather than absolute paths. Provided front-end languages use these same constraints, this has the added benefit of ensuring projects can be easily shared between developers and tracked in version control systems.

In TIL's grammar, links are simply written as path strings enclosed in double quotes. Whether a path uses valid formatting and characters is determined by the query system, though the query system will not verify whether the directory actually exists; it is up to the connected backend (and its potential configuration) to decide whether to treat a non-existent directory as a failure condition, or to instead create the directory if it does not exist.

```

streamlet example_streamlet = <

'parent_domain1,

'parent_domain2,

> (

parent_port1: in stream 'parent_domain1,

parent_port2: out stream 'parent_domain1,

) {

impl: "./path/to/a/directory"

};

```

Listing 3.8: A linked implementation in TIL.

Note that, as shown in Listing 3.8, linked implementations still require a complete Streamlet definition, consisting of a name and an interface in addition to its implementation. As mentioned before, the Streamlet name is used to let the backend determine which file or set of files to use from a directory. It also ensures that its interface definition can be included in the target language's project structure, and instances can be created inside structural implementations. E.g., when emitting to VHDL, the interface definition and name are used to create a component definition in the emitted project's *package* file(s), and these components are used inside the emitted architectures of structural implementations. The interface definition and name can also be used to automatically generate a correctly named and structured *template* in the linked directory, if the target does not already exist.

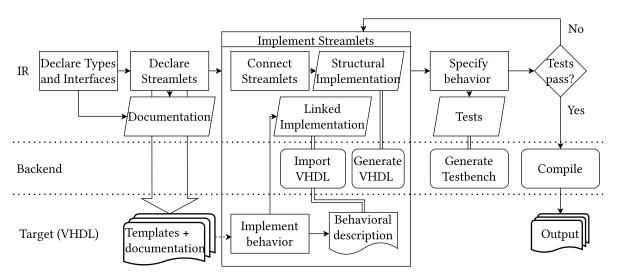

Figure 3.1 illustrates how linked implementations fit within a partial toolchain and workflow, consisting of Streamlets, structural implementations and tests defined in the IR, combined with behavior defined in a target language (VHDL, in this example) by a suitable backend. Not pictured are tools for simulating the testbenches produced by the backend, further passes on the output, nor any potential frontend language.

Figure 3.1: An example workflow, demonstrating how Streamlets are implemented using the IR, a suitable backend, and behavior defined in the target language.

#### 3.3. Recommendations for Language and Compiler Features

While the previous sections cover the primary functionality of the IR, which is to describe types, interfaces, Streamlets, and implementations of Streamlets, there are still a number of language features

which can improve or simplify the IR's ability to describe designs overall. To preface these language features, however, it is important to note that these are not (solely) intended to make the IR easier to write or read by humans; as this is an IR, it will primarily be emitted as output of a more ergonomic, front-end language and read by a compiler via the query system. As such, language features in the IR should not be "syntactic sugar", which is ultimately different styles of expression for existing language constructs. New features should meaningfully translate to something a compiler can directly implement, and should not expand to existing IR constructs (except potentially as a fallback). By extension, these features should be possible to implement in common HDLs.

#### 3.3.1. Type Parameters

Type parameters allow for the creation of variable types (also known as *generic types*), by parameterizing specific properties and allowing variations upon the type to be instantiated as needed. Listing 3.9 shows what such type parameters might look like in TIL. Such type parameters can be useful in simplifying and organizing the expression of related interfaces which share many properties, for example, if a certain (collection of) Streams represents a memory interface, its bus width can be parameterized.

```

type generic stream<

a: bitcount,

b: type,

c: complexity,

d: throughput,

e: keep,

f: direction,

> = Stream(

data: Group(a: Bits(a), a2: Bits(a), b: b),

complexity: c,

throughput: d,

keep: e,

synchronicity: Sync,

dimensionality: 0,

direction: f,

);

type concrete stream = generic stream<6, Bits(5), 4, 3.14, false, Forward>;

Listing 3.9: Theoretical grammar for generic types in TIL.

```

The omission of type parameters was not purely due to implementation time constraints, but due to the properties of such parameters being subject to debate, relating to the quality described in the preface: Language features should be possible to translate by a backend to their target language. There are two distinct ways to implement generic types in the IR:

- 1. Generic types are evaluated before compilation, either by the parser or by the query system before a compiler requests a definition. Only concrete types exist in the resulting output.

- 2. Type parameters are stored as properties on the IR, and can be used during compilation to translate to equivalent language features.

The first option is easiest to implement; as suggested, evaluating generic types to concrete types does not even need to be a feature of the IR itself, but can be handled by the parser for TIL. This makes them similar to identifiers on the namespace: A feature for tracking and reusing types, rather than something to be propagated to a compiler's output. For instance, one could save time on implementing multiple Streams with the same complexity, synchronicity and dimensionality by making the relevant properties type parameters.