EE-BS-2008-01

# **BSc THESIS**

# Interconnect estimation from C-code

Michel Vos (1267825), Rick van Akkeren (1157493) and Silvian Bensdorp

#### Abstract

FPGAs are easy and cheap to produce, a world of new possibilities is opened. One of those is in the area of reconfigurable computing. It is possible to extend normal CPUs with FPGAs for specific tasks, especially for those tasks which requires a lot of computational power. The Delft WorkBench is such a project. In this project, C-code is directly rewritten into a new piece of software and a set of hardware descriptions, suitable to program on a FPGA. In the rewritten part of the software, the computational parts are replaced by simple instructions to control the FPGA. The FPGA will run in parallel with the software and in this way, software can work up to 100 times faster. This thesis focus on the estimation of the required area of interconnect on a FPGA, depending on a given set of software metrics. These metrics are found by a special compiler, based on ELSA, and are specific for each part of C-code. With this estimation, it is possible to say, in an early stage of the whole process, if a certain part of software will fit on the FPGA. The developed model is based on a dataset from 127 kernels and is suitable for the Virtex2 and the Virtex4 platforms.

Faculty of Electrical Engineering, Mathematics and Computer Science

$\mathbf{2008}$

### THESIS

# submitted in partial fulfillment of the requirements for the degree of

### BACHELOR OF SCIENCE

in

# ELECTRICAL ENGINEERING

$\mathbf{b}\mathbf{y}$

Michel Vos (1267825), Rick van Akkeren (1157493) and Silvian Bensdorp

Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

by Michel Vos (1267825), Rick van Akkeren (1157493) and Silvian Bensdorp

#### Abstract

Since FPGAs are easy and cheap to produce, a world of new possibilities is opened. One of those is in the area of reconfigurable computing. It is possible to extend normal CPUs with FPGAs for specific tasks, especially for those tasks which requires a lot of computational power. The Delft WorkBench is such a project. In this project, C-code is directly rewritten into a new piece of software and a set of hardware descriptions, suitable to program on a FPGA. In the rewritten part of the software, the computational parts are replaced by simple instructions to control the FPGA. The FPGA will run in parallel with the software and in this way, software can work up to 100 times faster. This thesis focus on the estimation of the required area of interconnect on a FPGA, depending on a given set of software metrics. These metrics are found by a special compiler, based on ELSA, and are specific for each part of C-code. With this estimation, it is possible to say, in an early stage of the whole process, if a certain part of software will fit on the FPGA. The developed model is based on a dataset from 127 kernels and is suitable for the Virtex2 and the Virtex4 platforms.

| Bachelor in<br>Codenumber | : | Electrical Engineering<br>EE-BS-2008-01 |

|---------------------------|---|-----------------------------------------|

| Committee Members         | : |                                         |

| Advisor:                  |   | R.J. Meeuws M.Sc., CE, TU Delft         |

| Chairperson:              |   | Dr. K.L.M. Bertels, CE, TU Delft        |

| Member:                   |   | Dr. ir. A.J. van Genderen, CE, TU Delft |

| Member:                   |   | L. Mhamdi, CE, TU Delft                 |

# Contents

| List of Figures  | v   |

|------------------|-----|

| List of Tables   | vii |

| List of Listings | ix  |

| Acknowledgements | xi  |

| Intr | roduction                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1  | Problem description                                                                                                                                                     | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.2  | Structure                                                                                                                                                               | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Bac  | ekgrounds                                                                                                                                                               | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.1  | Reconfigurable computing                                                                                                                                                | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 2.1.1 Principles                                                                                                                                                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 2.1.2 Advantages                                                                                                                                                        | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 2.1.3 Disadvantages                                                                                                                                                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.2  | Examples of RC systems                                                                                                                                                  | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 2.2.1 Field Programmable Gate Arrays                                                                                                                                    | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 2.2.2 PipeRench                                                                                                                                                         | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.3  | FPGAs                                                                                                                                                                   | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 2.3.1 Interconnect on a FPGA                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 2.3.2 Xilinx: Profile and design flow 1                                                                                                                                 | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.4  | MOLEN: A reconfigurable computing system                                                                                                                                | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 2.4.1 Overview                                                                                                                                                          | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 2.4.2 Components                                                                                                                                                        | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 2.4.3 Programming paradigm                                                                                                                                              | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.5  | The Delft WorkBench toolchain                                                                                                                                           | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 2.5.1 Overview                                                                                                                                                          | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 2.5.2 Design flow                                                                                                                                                       | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Inte | erconnect estimation from C-code 2                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.1  | Operational requirements                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 3.1.1 Operational requirements for the prediction model                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 3.1.2 Operational requirements for the accompanying tool                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.2  | Related research                                                                                                                                                        | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.3  | Quipu                                                                                                                                                                   | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.4  | Related theory                                                                                                                                                          | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 3.4.1 Statistical Modeling 2                                                                                                                                            | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 3.4.2 Linear regression $\ldots \ldots 2$                                                  | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | <ol> <li>1.1</li> <li>1.2</li> <li>Bao</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>Into</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> </ol> | 1.1       Problem description       12         Structure       12         Structure       12         Backgrounds       12         2.1       Reconfigurable computing       12         2.1.1       Principles       12         2.1.2       Advantages       12         2.1.3       Disadvantages       12         2.1.3       Disadvantages       12         2.2       Examples of RC systems       12         2.2.1       Field Programmable Gate Arrays       12         2.2.2       PipeRench       12         2.3       FPGAs       12         2.3.1       Interconnect on a FPGA       12         2.3.2       Xilinx: Profile and design flow       12         2.4       MOLEN: A reconfigurable computing system       14         2.4.1       Overview       14         2.4.2       Components       14         2.4.3       Programming paradigm       14         2.5.1       Overview       14         2.5.2       Design flow       14         2.5.2       Design flow       14         2.5.2       Design flow       15         1       Operational r |

|              | 3.<br>3.                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                        | $   \ldots \ldots \ldots \ldots \ldots \ldots \ldots 25   \ldots \ldots \ldots \ldots 26 $ |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|

| 4            | Method         4.1       G         4.2       Sy         4.3       E:         4.4       B:         4.5       A:         4.5       A:         4.6       M         Expert | blogy<br>erating VHDL code from the kernels<br>hesizing & Implementing the VHDL<br>acting necessary data from the log f<br>ling up the statistical estimation mo<br>Transformations on the data<br>yzing the model<br>Elimination of data outliers<br>fing predictions using the prediction<br>ental setup and results | 27         s                                                                               |  |

|              | 5.<br>5.                                                                                                                                                               | Used hardware                                                                                                                                                                                                                                                                                                          | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                       |  |

| 6            | 6.1 C                                                                                                                                                                  | ons and recommendations<br>clusions                                                                                                                                                                                                                                                                                    |                                                                                            |  |

| Bi           | bliogra                                                                                                                                                                | У                                                                                                                                                                                                                                                                                                                      | 49                                                                                         |  |

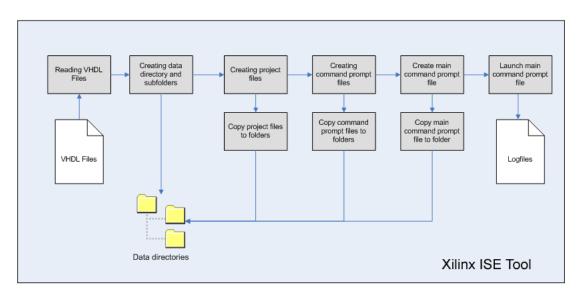

| A            | Xilinx<br>A.1 W                                                                                                                                                        | <b>E Tool</b><br>(flow                                                                                                                                                                                                                                                                                                 | <b>51</b><br>                                                                              |  |

| в            | <b>Logfile</b><br>B.1 W                                                                                                                                                | <b>Fool</b><br>( flow                                                                                                                                                                                                                                                                                                  | <b>55</b><br>                                                                              |  |

| С            |                                                                                                                                                                        | on Tool<br>c flow                                                                                                                                                                                                                                                                                                      |                                                                                            |  |

| D            | D.1 V                                                                                                                                                                  | d data from log files<br>ex2P                                                                                                                                                                                                                                                                                          |                                                                                            |  |

| $\mathbf{E}$ | Softwa                                                                                                                                                                 | Complexity Metrics                                                                                                                                                                                                                                                                                                     | 73                                                                                         |  |

| F            | F.1 cc<br>F.2 so                                                                                                                                                       | <b>of CD-ROM</b><br>biled tools/                                                                                                                                                                                                                                                                                       |                                                                                            |  |

# List of Figures

| 2.1        | The design space between flexibility and performance                                               | 6               |

|------------|----------------------------------------------------------------------------------------------------|-----------------|

| 2.2        | FPGA internal structure based on the Xilinx architecture style                                     | 10              |

| 2.3        | Internal structure of a CLB                                                                        | 10              |

| 2.4        | Wire segments in an interconnect structure                                                         | 11              |

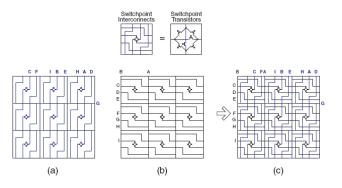

| 2.5        | A typical interconnect structure with wires and switch points                                      | 12              |

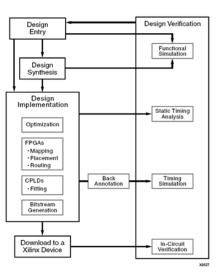

| 2.6        | Xilinx design flow                                                                                 | 13              |

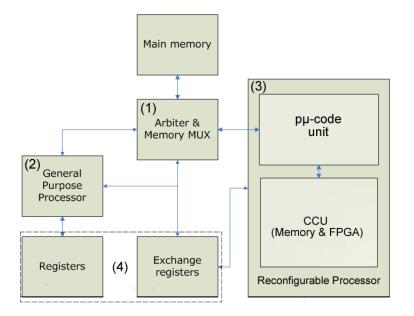

| 2.7        | Overview of the MOLEN platform                                                                     | 14              |

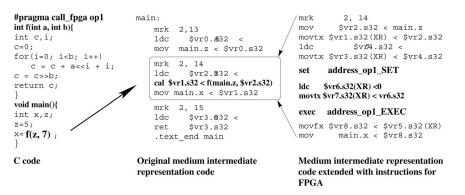

| 2.8        | Medium intermediate representation code                                                            | 16              |

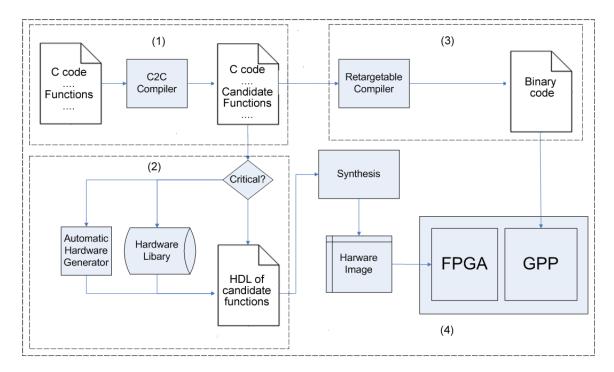

| 2.9        | Overview of the Delft WorkBench tool chain                                                         | 17              |

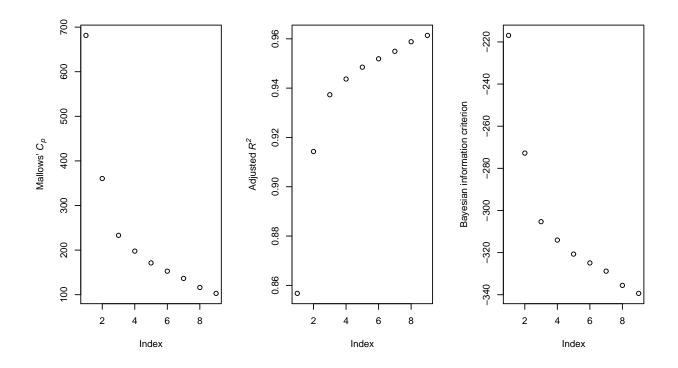

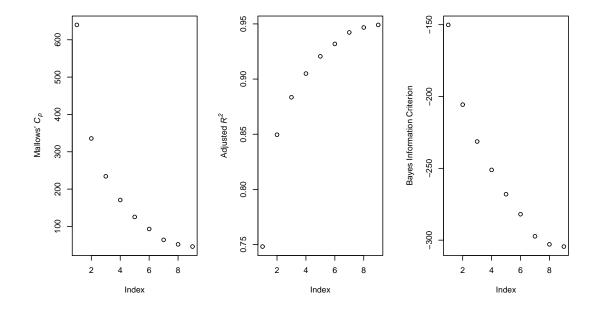

| 5.1        | Three criterion statistics for the number of predictors to include in the OLSD we del Winter ILDue | 32              |

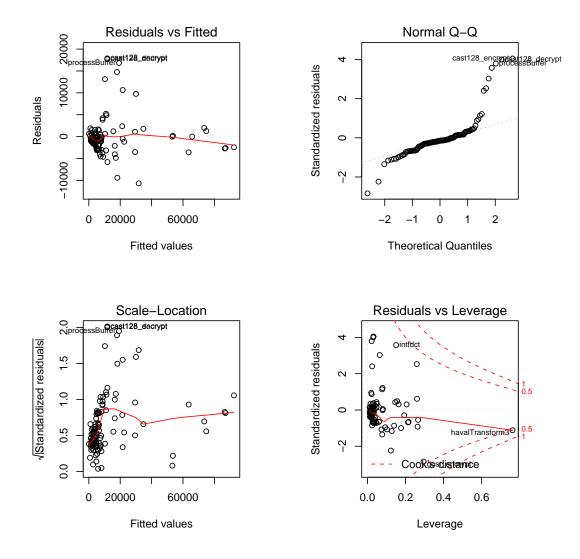

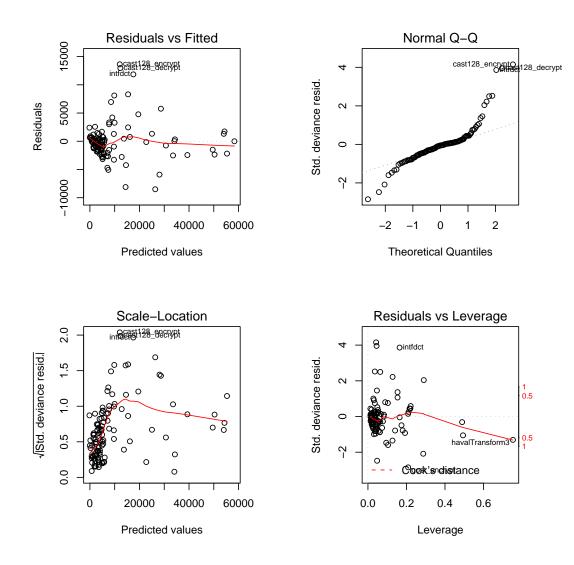

| 5.2        | OLSR model, Virtex-II Pro                                                                          | $\frac{32}{34}$ |

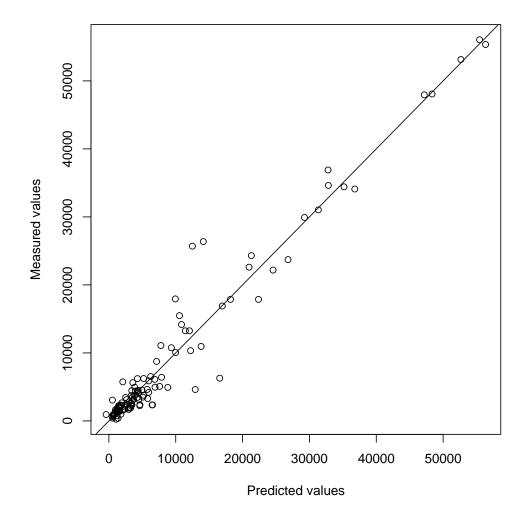

| 5.2<br>5.3 | Measured values plotted against the predicted values of the OLSR model,                            | 34              |

| 0.0        | Virtex-II Pro                                                                                      | 35              |

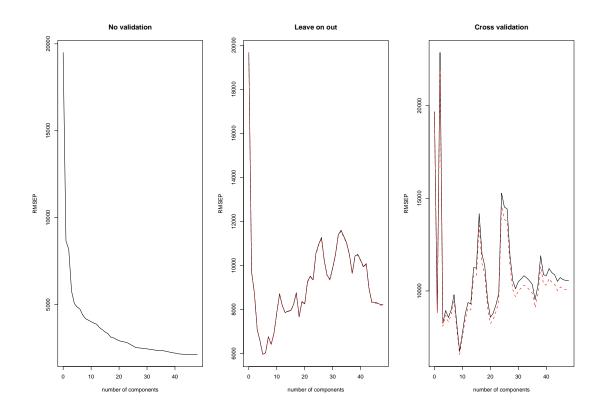

| 5.4        | RSMD for number of components in model for different validation meth-                              | 55              |

| 0.4        | ods, Virtex-II Pro                                                                                 | 37              |

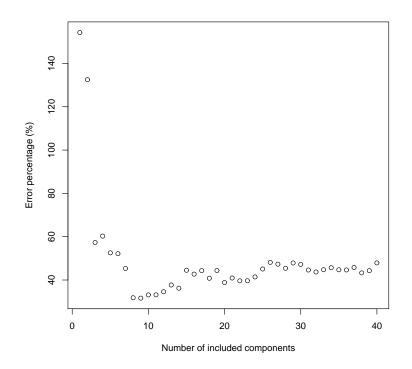

| 5.5        | Relative error of the PLSR model for different number of prediction pa-                            | 01              |

| 0.0        | rameters, Virtex-II Pro                                                                            | 38              |

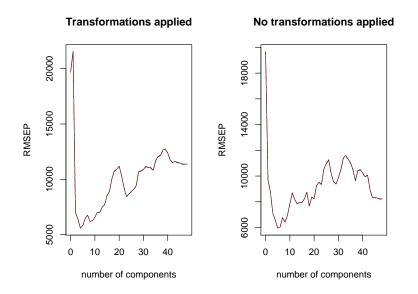

| 5.6        | RMSD for transformed and non-transformed predictors, Virtex-II Pro                                 | 38              |

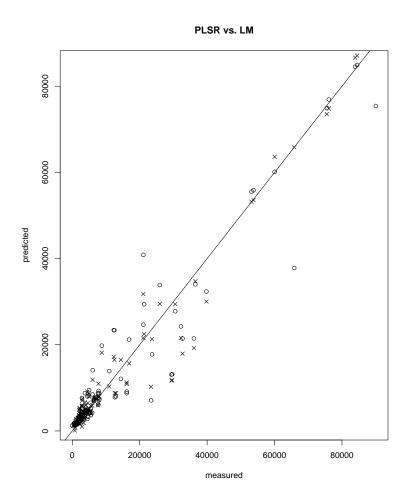

| 5.7        | The OLSR model vs. the PLSR model when fitted, Virtex-II Pro                                       | 39              |

| 5.8        | Three criterion statistics for the number of predictors to include in the                          | 00              |

| 0.0        | OLSR model,Virtex-4                                                                                | 40              |

| 5.9        | Some standard R test statistics for the linear model, Virtex-4                                     | 41              |

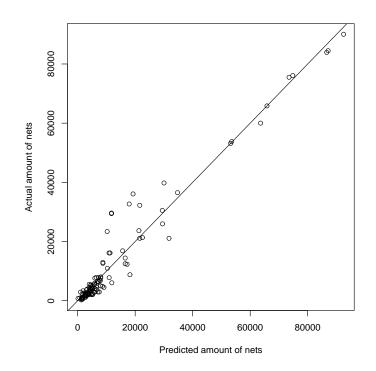

| 5.10       | Fitted values vs. the measured values of the OLSR model, Virtex-4                                  | 43              |

| A.1        | Global overview of the Xilinx ISE Tool                                                             | 51              |

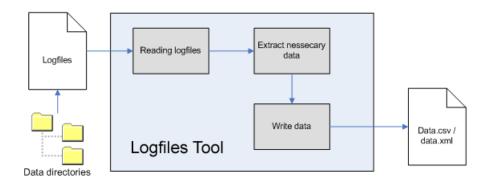

| B.1        | Global overview of the Logfiles Tool                                                               | 55              |

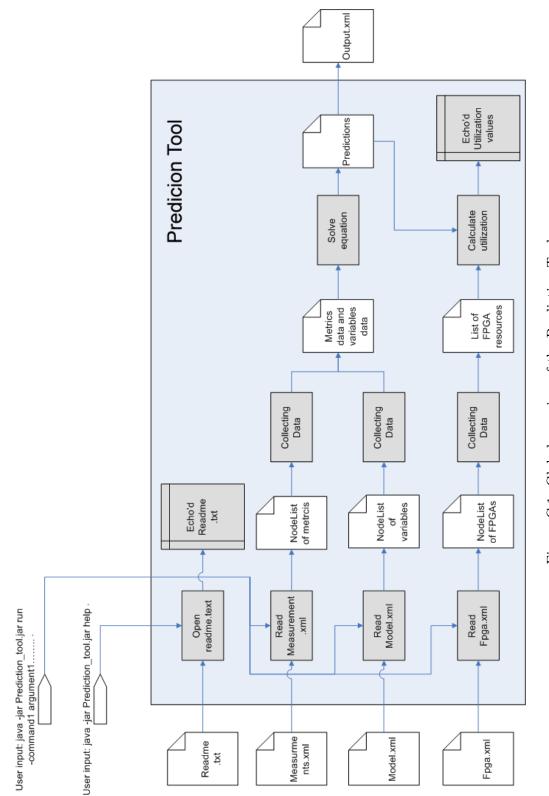

| C.1        | Global overview of the Prediction Tool                                                             | 58              |

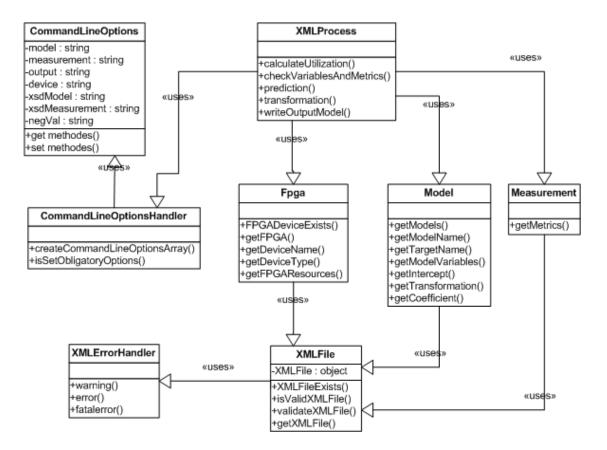

| C.2        | Class diagram of the Prediction Tool                                                               | 61              |

# List of Tables

| 5.1 | R results for the linear fit of the OLSR model, Virtex-II Pro           | 33 |

|-----|-------------------------------------------------------------------------|----|

| 5.2 | Statistics of the OLSR model, Virtex-II Pro                             | 33 |

| 5.3 | Best predictor set for Virtex-II Pro OLS given the number of parameters | 36 |

| 5.4 | Statistics of the PLSR model, Virtex-II Pro                             | 36 |

| 5.5 | R results for the linear fit of the OLSR model, Virtex-4                | 40 |

| 5.6 | Statistics of the transformed OLSR model, Virtex-4                      | 42 |

| 5.7 | Best predictor set for OLSR given the number of parameters, Virtex-4 $$ | 42 |

| C.1 | Overview of the command and arguments options                           | 57 |

# Listings

| A.1 | projectfile.prj     | 52 |

|-----|---------------------|----|

| A.2 | projectfilework.prj | 52 |

| A.3 | synthesize.cmd      | 52 |

| A.4 | ngdbuild.cmd        | 52 |

| A.5 | map.cmd             | 52 |

| A.6 | par.cmd             | 52 |

| A.7 | trce.cmd            | 53 |

|     | xdl.cmd             |    |

| C.1 | model.xml           | 59 |

| C.2 | measurements.xml    | 59 |

# Acknowledgements

This report is written as part of the course 'Bachelor afstudeerproject', ET3905. With this report we hope to fulfill part of our obligations in attaining the degree of Bachelor of Science in Electrical Engineering. After this we hope to proceed with the Master phase.

Readers who are interested or not familiar with the background of this project are referred to Chapter 2 of this report. The readers who are already familiar with the background and are interested in more specific information on the project can go directly to Chapter 3 and 4. Results can be found in Chapter 5 and conclusions and recommendations are given in Chapter 6.

We would like to thank the following people: Koen Bertels (CE, TU Delft), for guiding us in the beginning of the project, Yi Lu (CE, TU Delft), for helping us with the Xilinx ISE, Yana Yankova (CE, TU Delft), for providing us with the VHDL code of the software kernels and all the other people who did something for us, but kept unnoticed

Our special thanks goes out to Roel Meeuws (CE, TU Delft) for supervising us during the whole project. He gave us great support and advice. Also he read the concept versions of our report, providing us with useful comments on how to improve certain things.

Michel Vos (1267825), Rick van Akkeren (1157493) and Silvian Bensdorp Delft, The Netherlands July 3, 2008

# Introduction

1

Since the beginning of the computer era many different types of computer systems have been developed. Early computer systems were based on the fixed program architecture. These systems could only do simple mathematics, but not such things like word processing or running video games. To change a program the whole architecture had to be re-wired, re-structured or even completely redesigned, often a laborious task.

The idea of a stored program architecture, also called the Von-Neumann architecture [1],[2], changed that. This architecture was divided into several units. A processing unit, a combined data and program memory, and data and control elements between the processing unit and the memory. By creating an instruction set for the processing unit it could fetch data from the memory, making a calculation and storing it back into the memory. Executing instructions sequentially allows a next instruction to use the result of a previous instruction in its calculation. This made the implementation of algorithms much simpler and therefore the variety of programs for this architecture much larger.

However this idea also showed a bottleneck, known as the Von-Neumann bottleneck[2]. Division between the processing unit and the memory, caused that instructions and data continually had to be moved between them, also called the throughput. Because the processing unit could work at a much faster speed than the rate of throughput, the processing unit had to wait continuously for data to be fetched from memory, what lead to longer execution times. Every increase in the amount of data transferred would increase the execution time. To reduce this performance problem, caches were placed between the CPU and the main memory. Despite this bottleneck this architecture is still the dominating architecture in conventional computing, because it offers a lot of flexibility.

Although the computer systems based on the Von-Neumann architecture are dominating conventional computing, other systems are used in specific areas. Application Specific Integrated Circuits (ASICs) for example. ASICs are designed to execute specific applications in hard-wired technology. Though this is a very fast technology for executing applications, it has the same lack of flexibility as the fixed program architecture.

In recent years the amount of data processed in computer systems has increased rapidly. For computer machines based on the Von-Neumann architecture this is becoming a problem. The earlier mentioned bottleneck causes these machines to be insufficient due the increasing execution time by large amounts of data. Therefore, designers increasingly use ASICs to execute applications with large amount of data. Though this is a good solution for speeding up the execution time, the lack of flexibility still remains.

To solve this problem researchers came up with a technology called reconfigurable computing (RC). It combines the flexibility of the Von-Neumann architecture with the speed of ASICs. RC systems consist of software programmable processing units and programmable hardware components, like a Field Programmable Gate Arrays (FPGAs). These systems provide new possibilities to speed up compute-intensive calculations multiple times. However, the design and applications for RC systems demand a new approach for hardware and software design. This new approach requires knowledge of hardware and software. Current application designers for conventional computing do not have this knowledge. To prevent application designers from ignoring this new technology, because it does not integrate with their systems, a comprehensive high-level development platform is required. This platform should give the application designer an easy way to implement their applications on a reconfigurable computing system.

The DelftWorkBench (DWB) tool chain, in development at the Delft University [3], is such a software design platform. It provides the application designer with an easy way to implement their application. Going through several phases in the tool chain the application will be implemented on the reconfigurable platform. These phases are: Code profiling and cost modeling, code transformations and optimizations, retargetable compiler, retargetable processor and (exchange) registers; all of which are further discussed in section 2.5.

### 1.1 Problem description

This report will focus on the first phase of the DWB: *Code profiling and cost modeling*. As part of the Hardware/Software Partitioning process this phase is an important step in the development of reconfigurable systems. Hardware/Software Partitioning is nothing more then identifying those parts of an application that should be executed in hardware and those parts that should be executed in software. The goal of Hardware/Software Partitioning is to divide an application (the hardware part and the software part) in such a way that it can offer the optimal performance when implemented on a reconfigurable system. To achieve this goal, parts of the application have to be analyzed and profiled on certain aspects, like area metrics and time delay. To get the best results it is important to know in an early stage some of these aspects, so the process of partitioning becomes easier and better. Therefore one possibility would be to build up a statistical estimation model, that can predict these aspects in an early stage. In addition to this statistical estimation model, a tool should be written that is able to make predictions with the prediction model and earlier determined Software Complexity Metrics (SCMs), see [4] for more details on SCMs.

The original idea of this project was to build up a statistical estimation model to estimate the area used by the inter-modular interconnect between two or more kernels on an FPGA, based on the size of the kernels, the amount of data exchanged between kernels and the amount of kernels on a chip. Unfortunately, the Xilinx ISE [5] was not capable to place multiple kernels on a FPGA in an easy and useful way. Besides that, the necessity of this model was also questionable. At this moment, it is still not possible to use the Delft WorkBench to place multiple kernels on the FPGA. Therefore, such a statistical estimation model of the interconnect is not applicable in the current situation.

Therefore, the assignment was revised. Still, a statistical estimation model for interconnects was required, but now focusing on the intra-modular interconnect of a kernel. Using a special C-compiler<sup>1</sup>, based on ELSA [6], some SCMs become available. These SCMs are used as input for the prediction model. As output will be the probable amount of interconnect needed by the specific piece of C-code. Using this model is important to predict if a kernel will fit on a FPGA and so whether the Hardware/Software Partitioning is successful or not.

To achieve this, many different software kernels written in C-code will be compiled to VHSIC Hardware Description Language (VHDL) using DWARV [7]. Mapping the VHDL from each software kernel onto the FPGA will provide data about the interconnect resources. This data, combined with the SCMs will form the basis for the model.

### 1.2 Structure

This report consists of six chapters. The next chapter provides information about the background of this project. Detailed are reconfigurable computing, MOLEN: A reconfigurable computing system [8], [9], [10], [11] and the Delft WorkBench tool chain. Subsequently, chapter 3 translates the problem into a set of operational requirements and discusses some related research and related theory. Chapter 4 describes the methodology of the project and shows the experimental setup. In chapter 5 the experimental results are provided. Finally, conclusions and further recommendations are given in chapter 6. In addition, the tools developed during this project are discussed in the appendices.

$<sup>^{1}</sup>$ C is a general-purpose, block structured, procedural, imperative computer programming language. Although C was designed as a system implementation language, it is also widely used for applications.

In the previous chapter conventional computing was described and what kind of problem is occurring at the moment. We briefly mentioned reconfigurable computing as a solution to this problem. Also the Delft WorkBench was mentioned, which is a comprehensive high-level development platform for reconfigurable computing. In this chapter more information is given on the background studies of this project. In section 2.1 we discuss about reconfigurable computing in more detail. Section 2.3 provides some information about FPGAs, used in reconfigurable computing systems. Subsequently, section 2.4 introduces and explains MOLEN, a reconfigurable computing system. Finally, in section 2.5 the Delft WorkBench is discussed in more detail.

# 2.1 Reconfigurable computing

Reconfigurable computing (RC) has become an important subject in research. This is due to the fact that it allows executing computationally intense parts of an application in hardware to increase the performance significantly compared to software execution while the flexibility of a software solution still remains [12].

Before the rise of RC there were two main approaches in conventional computing. The first approach was to use hard-wired technology such as Application Specific Integration Circuits (ASICs). This approach has the advantage that it is much faster than software implementation, but the disadvantage is its lack of flexibility. Every time an application changes the ASIC should be redesigned and re fabricated, which is an intensive and expensive task.

The second approach was to use a software programmable processing unit such as an Intel processor. This is already a far more flexible solution than using hard-wired technology. An application written in a high-level programming language, for example C, is compiled to lower-level instructions and executed by the processor. Now if the application changes, only part of the application code has to be rewritten and recompiled. However, the disadvantage of this approach is that it is limited by the capabilities of the processor and by the sequential execution of instructions, leading back to the Von-Neumann bottleneck. This causes poor performance when applications become more computationally intensive.

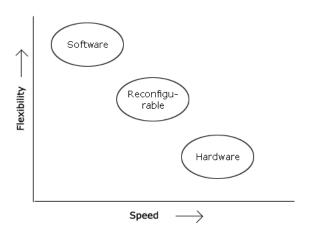

RC combines aspects of both of these approaches and it aims to fill the gap between software and hardware[12], depicted in Figure 2.1. It has some of the speed of hardware and some of the flexibility of software.

Figure 2.1: The design space between flexibility and performance. Reconfigurable filling the gap between software and hardware

#### 2.1.1 Principles

The basic idea of reconfigurable computing is to combine a General Purpose Processor (GPP) with reconfigurable hardware [13]. An application normally executed on a processor should then be divided into compute-intensive parts and less compute-intensive parts. Executing the compute-intensive parts on the reconfigurable hardware and the other parts on the GPP, should provide significantly better performance.

The early RC systems consisted of two important main components. A GPP and a reconfigurable hardware component, for example a FPGA. These kinds of systems could implement specific functionality on FPGAs rather than on the GPP. The GPP in such a system no longer provided the major computational power, instead the FPGA took over this task. Because the major computations were now done in hardware on the FPGA, it could provide a significantly better performance. These early systems are known as static RC systems [13]. They carry the name static, because only one configuration was loaded onto the FPGA and could not be changed during run-time.

Today, most of the RC systems are run-time RC systems [13]. They have the possibility to reconfigure the FPGA during run-time. Therefore these systems consists of three important main components, the GPP, the reconfigurable part and the Arbiter.

The GPP is a normal processor also used in conventional computing. It executes those parts of the application that are less compute-intensive.

The second component is the reconfigurable part, also called the *reconfigurable unit* (RU). This component actually consists of two subcomponents. The FPGA and the *reconfigurable processor* (RP). The logic of the compute-intensive parts of the application are mapped onto the FPGA, while the task of the RP is to control the logic that is mapped onto the FPGA. Therefore, the RP is extended with an additional instruction set. This instruction set has instructions to set and execute the logic mapped on the FPGA. In section 2.4.3 such an instruction set, used for the MOLEN platform, will be further discussed.

The third component is the so called *arbiter*. The task of the arbiter is to decide, during run-time, whether the application code should be executed by the GPP or by the RU. The arbiter recognizes these additional instructions in the application code and then decides whether it should be executed by the RU or by the GPP. How these additional instructions appear in the application code will be further discussed in section 2.5 on the Delft WorkBench tool chain.

#### 2.1.2 Advantages

RC offers several advantages above conventional computing methods. Combining the speed of hardware execution and the flexibility of software execution the following advantages can be identified.

• Flexibility

Because the FPGA can be reconfigured many times, different configurations can be loaded. Therefore making it unnecessary to change the physical hardware every time an application is updated. This saves a lot of time in redesigning and refabricating of hardware.

• Cost efficiency

Using only one FPGA which can be reconfigured with different configurations, saves a lot of money on purchasing multiple FPGAs for each different configuration.

• Speed

Due to the fact that the computationally intense parts of an application can be done in hardware, rather than on a GPP, the execution time of an application reduces significantly. Due to the reduced execution time the amount of computing power over time increases.

• Power efficiency

Having less execution time for an application, reducing the time the RC system is consuming power. This is making these systems more power efficient.

#### 2.1.3 Disadvantages

Though RC offers several advantages above conventional computing methods, there are also several disadvantages to be mentioned.

• Application design

As mentioned earlier in the introduction, designing an application for RC systems requires a different approach than designing an application for the current conventional computing technology. In such an approach, hardware and software knowledge are required. Because of this, there is a risk that current application designers will ignore reconfigurable technology. In order to prevent this from happening, a comprehensive high-level development platform should be developed. This platform should provide an easy way for the application designer to implement their application. The Delft WorkBench is such a platform and will be further discussed in section 2.5. • Speed

Although executing an application on a RC system is faster than executing it only on a GPP, the use of ASICs still remains the fastest solution for executing an application in hardware.

• Reconfiguration delay

By requiring multiple reconfigurations to complete a computation, the time it takes to reconfigure the FPGA becomes a significant concern. The systems should be idle during this reconfiguration time, wasting a lot of processing cycles that otherwise could be used for useful work.

# 2.2 Examples of RC systems

RC systems come in various shapes and sizes. These systems can be classified by four distinctive properties: reconfigurability, granularity, coupling and reconfiguration time. More information about these properties can be found in [14]. In this section we will only focus on three of them. Below are some examples of RC systems given.

### 2.2.1 Field Programmable Gate Arrays

FPGAs are reconfigurable Very Large Scale Integration<sup>1</sup> (VLSI) components that allow for the implementation of arbitrary sequential and combinatorial circuits which are described in a hardware description language. Therefore, they can be seen as a reconfigurable computing system. The simplest form of an FPGA consists of an array of Configurable Logic Blocks (CLBs), a set of input and output blocks (IOBs) and a programmable interconnect architecture, see also section 2.3.

• *Reconfigurability*

FPGAs are widely used as an alternative for ASICs, because they are reprogrammable. Therefore, allowing to implement different applications just by reprogramming the FPGA. Examples of applications that can be implemented on an FPGA are real-time digital signal processing and data encryption.

• Granularity

FPGAs can be considered as fine-grained computing systems. The CLBs on a FPGA are fine-grained components. They can be used as a replacement for two to six simple logic gates or a single flip flop in a gate level circuit design. Most of the commercially available FPGAs also contain larger, coarse-grained blocks, such as ALUs, which provide commonly used functionality.

• Reconfiguration time

The reconfiguration time of an FPGA is specific to each FPGA series. FPGAs require a complete reset before a new application can be programmed. The reset is done by an external bit stream, which can take several seconds to perform. This

$<sup>^{1}\</sup>mathrm{VLSI}$  is the process of creating integrated circuits by combining thousands of transistor-based circuits into a single chip

makes them statically reconfigurable only, because a delay of several seconds is too long for reconfiguring it during run time. At present, some FPGA series support limited runtime reconfiguration, for example the Xilinx Virtex4 series.

• Coupling

Because an FPGA is a single VLSI component, it cannot be used as a generic computing platform. In order to make it suitable as a generic computing platform, it should be mounted on a printed circuit board that provides I/O facilities. An FPGA mounted on such a board is an example of a fully reconfigurable architecture.

#### 2.2.2 PipeRench

PipeRench is Carnegie Mellon University's answer to the reconfigurable computing challenge. The system, which is particularly suitable for stream based media processing applications, was designed with the benefit of hindsight on FPGA based reconfigurable computing systems. The PipeRench fabrics aims to beat FPGA based computing machines on five points, as described in [14].

• Reconfigurability

The PipeRench design consists of pure reconfigurable fabrics and thus in itself is a fully reprogrammable system. However, unlike FPGAs, the PipeRench is not suitable for complete System-on-Chip (SoC) implementations. The designers of the system envisioned PipeRench as a co processor. It requires an additional computing system in order to be used as a full computing platform.

• Granularity

The configurable logic units in PipeRench are designed for computation purposes. The PipeRench chip consists of so called stripes which represent pipeline stages in a computation. A stripe contains a number of configurable processing elements such as ALUs. Therefore, PipeRench can be seen as a coarse-grained fabric.

• *Reconfiguration time*

A powerful feature of the PipeRench is its extremely short configuration time. Its short reconfiguration time enables the PipeRench architecture to simulate long virtual pipelines on hardware with minimal overhead.

• Coupling

PipeRench was designed to function as an attached co processor in a general purpose computing system. The co processor is intended to be used as a loosely coupled system, which processes longer instruction sequences with relative autonomy.

## 2.3 FPGAs

There are several manufacturers that produce FPGAs based on static memory (SRAM). A couple of these are Xilinx [15], Altera [16] and Atmel [17]. Each of these manufacturers have their own architectural implementation, but the basics are the same. This report

will refer to the architectural implementation of Xilinx, because the Xilinx ISE, discussed in Section 2.2.3, is used to synthesize the software kernels.

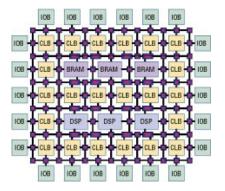

The basics of an FPGA architecture are depicted in Figure 2.2 [18].

Figure 2.2: FPGA internal structure based on the Xilinx architecture style.

A FPGA is a semiconductor device consisting of configurable logic blocks (CLBs), interconnects, and input/output blocks (IOBs) that allow implementing complex digital circuits. On the outside of the FPGA the IOBs form a ring for connection I/O pins that are situated on the exterior of the FPGA. Inside this ring lies a rectangular array of logic blocks. A typical FPGA logic block consists of a four-input lookup table (LUT) and a flip-flop. Modern FPGA devices also include higher-level functionality such as Digital Signal Processing (DSP), high-speed IOBs, embedded memories (BRAM) and embedded processors. The programmable interconnect wires are required to connect CLBs to other CLBs and CLBs to IOBs.

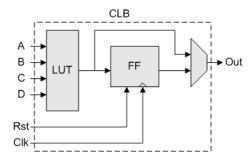

A slice (Xilinx terminology) contains a small set of building blocks (LUTs, flip-flops and control elements). This is the basic unit area when determining the FPGA-based design size. CLBs consists of several number of slices. Modern FPGAs consists of tens of thousands of CLBs and a large programmable interconnection network. In Figure 2.3 a CLB is depicted.

Figure 2.3: Internal structure of a CLB.

Unlike ASICs which perform only one specific function, FPGAs can be reprogrammed many times to perform a different function. For programming the FPGA, code written in a Hardware Description Language (HDL) is used, for example VHDL.

Since their introduction in 1985, FPGAs [19] have been used in various systems implementing a broad range of applications. In most of these systems, they are used to implement certain logic, providing high-level integrated circuits without the expenses and risks that are involved with using ASICs.

Where the performance of FPGAs increased rapidly, their use in RC systems payed considerable attention [19]. With the inheritance of speed and parallelism from a hard-ware solution, FPGA-based co-processors are used to execute compute-intensive tasks while maintaining the flexibility of a software programmable solution. Due to this fact, the first systems with FPGA-based co-processors that compete with parallel computers and even supercomputers have started to emerge.

#### 2.3.1 Interconnect on a FPGA

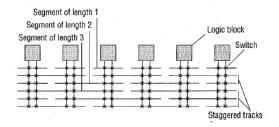

As described above, there is a huge amount of logical blocks on a FPGA. In order to realize a working system, it is necessary to connect those blocks to each other. The whole process of creating and programming this interconnect structure is called routing. This process is very important for the speed of the design, because the wiring is responsible for a big part of the delays on a FPGA. This is due to the capacitors between the wiring and the ground.

On a FPGA, a reprogrammable interconnect system is available to take care of this. About 80% of the FPGA area is reserved for this system [20].