#### Investigation of Pressure Assisted Nanosilver Sintering Process for Application in Power **Electronics**

Zhang, Hao

DOI

10.4233/uuid:49ccc901-a128-424f-9e9d-e2f8c63ad31b

**Publication date**

**Document Version**

Final published version

Citation (APA)

Zhang, H. (2019). Investigation of Pressure Assisted Nanosilver Sintering Process for Application in Power

The Mark Process of Tachas and Peters and Process for Application in Power

The Process of Tachas and Peters Electronics. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:49ccc901-a128-424f-9e9d-e2f8c63ad31b

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy**Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## INVESTIGATION OF PRESSURE ASSISTED NANOSILVER SINTERING PROCESS FOR APPLICATION IN POWER ELECTRONICS

## INVESTIGATION OF PRESSURE ASSISTED NANOSILVER SINTERING PROCESS FOR APPLICATION IN POWER ELECTRONICS

#### **Proefschrift**

ter verkrijging van de graad van doctor

aan de Technische Universiteit Delft,

op gezag van de Rector Magnificus Prof. dr. ir. T.H.J.J. van der Hagen,

voorzitter van het College voor Promoties,

in het openbaar te verdedigen op

dinsdag 25 juni 2019 om 15:00 uur

door

#### Hao ZHANG

Master of Engineering in Materials Processing Engineering Harbin University of Science and Technology, China geboren te Changtu, China Dit proefschrift is goedgekeurd door de:

Promotor: Prof. dr. G.Q. Zhang Promotor: Prof. dr. ir. W.D. van Driel

#### Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Prof. dr. G.Q. Zhang, Technische Universiteit Delft

Prof. dr. ir. W.D. van Driel, Technische Universiteit Delft

Onafhankelijke leden:

Prof. dr. F.L. Sun Harbin University of Science and Technology

Prof. dr. X.J. Fan Lamar University

Prof. dr. H. Fremont University of Bordeaux

Prof. dr. ir. K.M.B. Jansen, Technische Universiteit Delft

Dr. ir. R.H. Poelma Nexperia B.V.

Reserve:

Prof. dr. M. Zeman Technische Universiteit Delft

Keywords: nanosilver sintering, pressure, shear strength, nanoindentation,

stress distribution

Printed by: IPSKAMP Printing

Copyright © 2019 by Hao Zhang

ISBN: 978-94-6366-176-8

An electronic version of this dissertation is available at

http://repository.tudelft.nl/.

### **CONTENTS**

| 1 | Intr | oductio | on                                                         | 1  |

|---|------|---------|------------------------------------------------------------|----|

|   | 1.1  | Backg   | round                                                      | 1  |

|   | 1.2  | Revie   | w of die attach technologies                               | 3  |

|   |      | 1.2.1   | Lead free soldering technology                             | 3  |

|   |      | 1.2.2   | Transient liquid phase bonding                             | 6  |

|   |      | 1.2.3   | Silver sintering technology                                | 8  |

|   |      | 1.2.4   | Comparison of three main die attach technologies           | 12 |

|   | 1.3  | Resea   | rch objectives                                             | 14 |

|   | 1.4  | Thesis  | s outline                                                  | 15 |

|   | Refe | erences |                                                            | 16 |

| 2 | Bon  | ding m  | echanisms analysis of nanosilver sandwich sintered package | 28 |

|   | 2.1  | Introd  | luction                                                    | 29 |

|   | 2.2  | Metho   | odology                                                    | 30 |

|   | 2.3  | Effect  | s of pressure on the mechanical properties                 | 31 |

|   | 2.4  | Effect  | s of temperature on the mechanical properties              | 35 |

|   | 2.5  | Effect  | s of time on the shear mechanical properties               | 37 |

|   | 2.6  | Densi   | fication mechanisms of silver nanoparticles                | 39 |

|   | 2.7  | Sumn    | nary                                                       | 40 |

|   | Refe | erences |                                                            | 41 |

| 3 | Mici | ro mec  | hanical properties of pressure sintered nanosilver joint   | 45 |

|   | 3.1  | Introd  | luction                                                    | 46 |

|   | 3.2  | Metho   | odology                                                    | 47 |

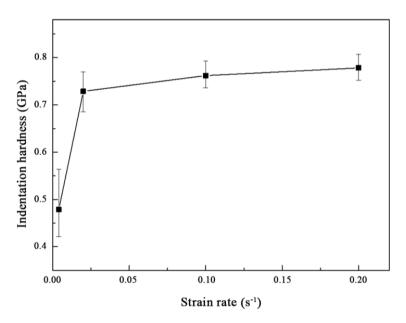

|   | 3.3  | Effect  | s of strain rate on the indentation hardness               | 48 |

|   | 3.4  | Plastic | c stress-strain constitutive model at room temperature     | 49 |

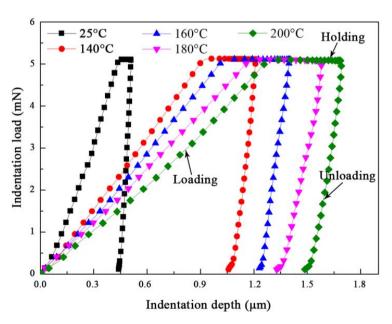

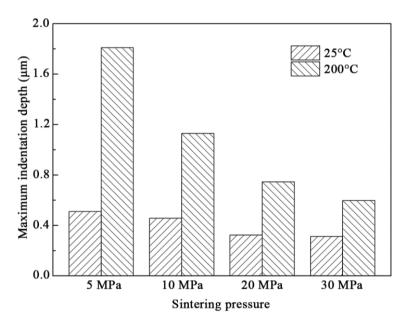

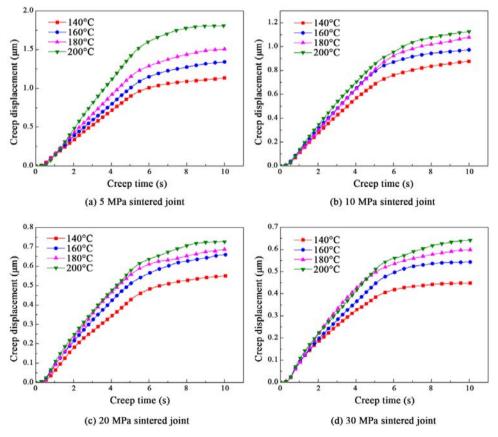

|   | 3.5  | Effect  | s of temperature on the micro mechanical properties        | 50 |

|   |      | 3.5.1   | Evolution of indentation depth                             | 50 |

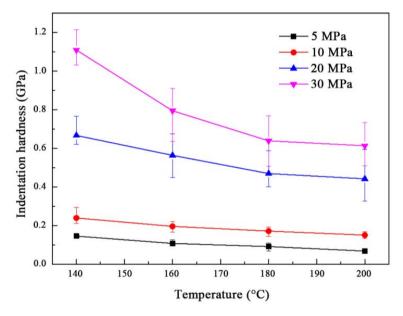

|   |      | 3.5.2   | Temperature dependence of hardness                         | 52 |

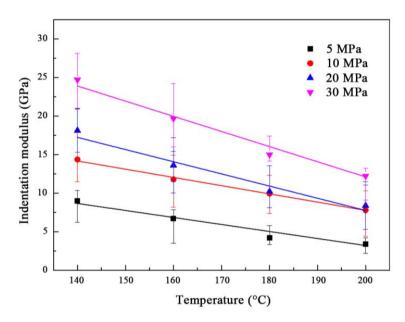

|   |      | 3.5.3   | Temperature dependence of elastic modulus                  | 53 |

|   | 3.6  | Initial | creep behavior of nanosilver sintered joint                | 55 |

|   | 3.7  | Sumn    | nary                                                       | 56 |

|   | Refe | erences |                                                            | 56 |

viii Contents

| 4   | Mec     | chanical properties of nanosilver double side sintered package          | 61    |

|-----|---------|-------------------------------------------------------------------------|-------|

|     | 4.1     | Introduction                                                            | . 62  |

|     | 4.2     | Methodology                                                             | . 64  |

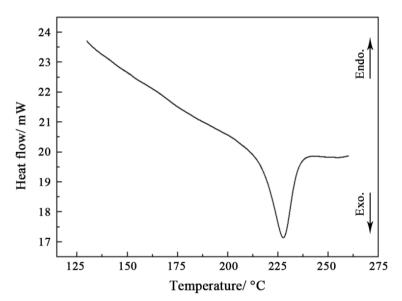

|     | 4.3     | Characterization of sintered nanosilver film                            | . 66  |

|     |         | 4.3.1 Pressure-free sintered nanosilver film                            | . 66  |

|     |         | 4.3.2 Comparison of sintered silver nanoparticles                       | . 68  |

|     | 4.4     | Effects of sintering pressure on the shear strength                     | . 68  |

|     | 4.5     | Effects of sintering pressure on the fracture morphology                | . 70  |

|     | 4.6     | Summary                                                                 | . 73  |

|     | Refe    | erences                                                                 | . 73  |

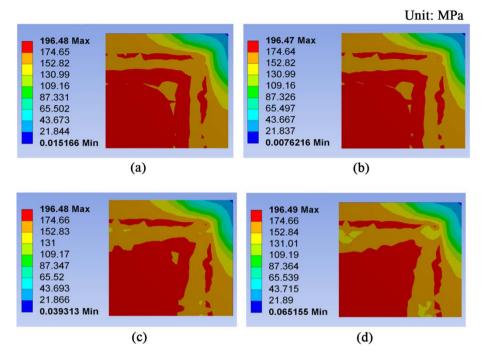

| 5   | Stre    | ss analysis of nanosilver double side sintered package using FEA method | 78    |

|     | 5.1     | Introduction                                                            | . 79  |

|     | 5.2     | Experimental set-up                                                     | . 80  |

|     | 5.3     | Simulation model                                                        | . 82  |

|     | 5.4     | Results experiments                                                     | . 84  |

|     | 5.5     | Results simulations                                                     | . 86  |

|     | 5.6     | Summary                                                                 | . 90  |

|     | Refe    | erences                                                                 | . 90  |

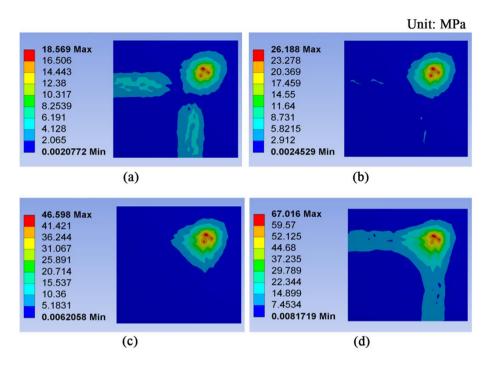

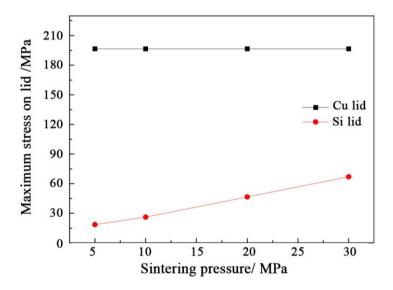

| 6   | App     | lication of nanosilver sintering in ceramic packages                    | 95    |

|     | 6.1     | Introduction                                                            | . 96  |

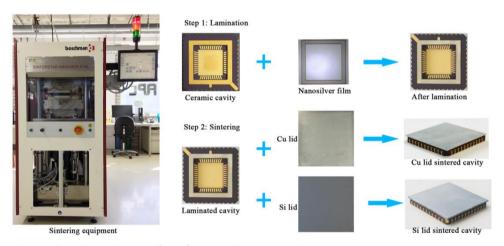

|     | 6.2     | Experimental set-up                                                     | . 97  |

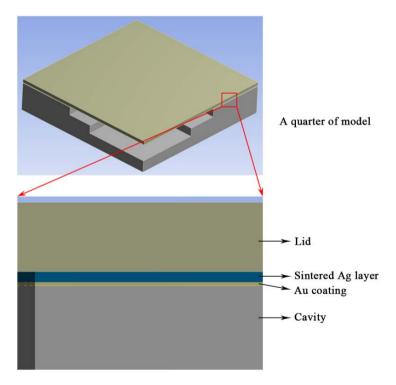

|     | 6.3     | Simulation methodology                                                  | . 98  |

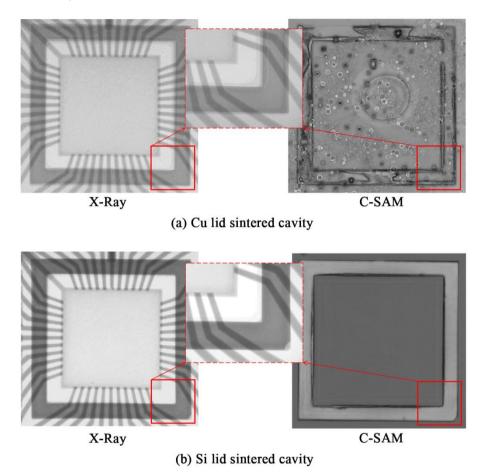

|     | 6.4     | Evaluation of bonding quality                                           | . 100 |

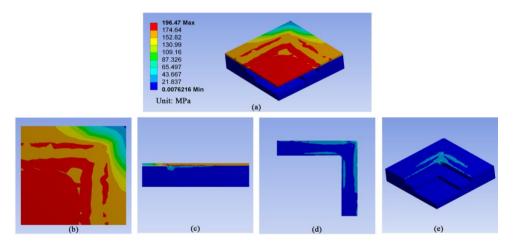

|     | 6.5     | Stress distribution analysis of sintered cavity                         | . 102 |

|     | 6.6     | Summary                                                                 | . 105 |

|     | Refe    | erences                                                                 | . 106 |

| 7   | Con     | clusions and recommendations                                            | 111   |

|     | 7.1     | Conclusions                                                             | . 111 |

|     | 7.2     | Recommendations                                                         | . 113 |

| Su  | mma     | ary                                                                     | 116   |

| Sa  | menv    | vatting                                                                 | 119   |

| Ac  | know    | vledgements                                                             | 123   |

| Lis | st of F | Publications                                                            | 127   |

|     |         |                                                                         |       |

# 1

### INTRODUCTION

#### 1.1. BACKGROUND

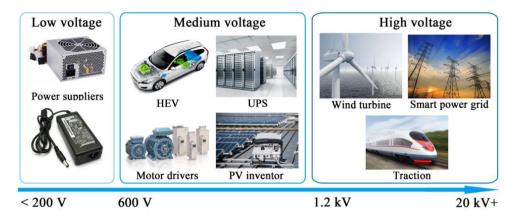

Power electronics are the applications of solid state electrical devices whose primary function is to converse, control and process electric power [1-3]. Until now, the commercially available power electronic devices in the market are mainly silicon (Si) based, which has a limited operation temperature and power density around 175°C and 200 W/cm<sup>2</sup>, respectively [4, 5]. However, wide band gap semiconductors, which are typically represented by silicon carbide (SiC) and gallium nitride (GaN), have been extensively investigated for power electronic packages and modules in the past few years [6, 7]. These semiconductors offer larger band gap, higher break down voltage and operation temperature when compared with Si based semiconductors. The GaN power electronic devices are mainly used for low voltage devices (600 V), due to its growth dependence on Si, SiC, or sapphire substrates [8, 9]. In contrast, the SiC power electronic packages and modules are designed for medium to high voltage (1.2 kV~20 kV) applications, such as bipolar junction transistors (BJTs), metal oxide semiconductor field effect transistor (MOSFETs), diodes, and insulated gate bipolar transistor (IGBT) [9, 10]. The major applications of power electronic packages and modules are shown in Figure 1.1. Along with the development of wide band gap semiconductors, advanced packaging methods and technologies are also needed to meet the new demands resulted from the operation process.

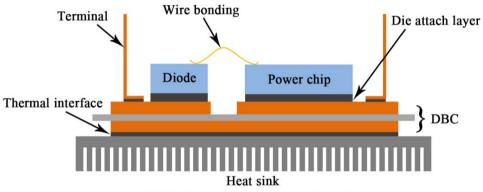

Increasing demands for power electronic packages and modules have been proposed to be higher in efficiency (>200 kHz), higher in voltage (>1.2 kV), and capable of operating at temperatures over 350°C [11, 12]. The interface between the power chip and its application circuit is always given by die attach layer. This layer provides the stable mechanical adhesion, internal stress compensation, heat dissipation, and electrical connection within the package [13]. Therefore, the die attach layer plays an important role to ensure the entire system works consistently. Figure 1.2(a) is the schematic

Figure 1.1: Major applications of power electronic devices

(a) Wire-bonded power electronic package

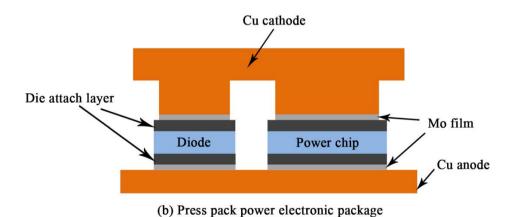

Figure 1.2: Schematic diagrams of wire bonding and press pack package (not drawn to scale)

diagram of mainstream power electronic with wire bonding technology. The power die and DBC (Direct Bond Copper) are bonded by die attach layer, and the main function of die attach layer in this structure is heat dissipation. But the wire-bonded power electronic package has high failure rate resulted from the bondwire and solder layer connections of internal chips [14, 15]. In comparison, the die attach layer in press pack power electronic package is responsible for both thermal and electrical conduction, as seen in Figure 1.2(b). The press pack power module is mainly used for high current density areas because of its higher reliability and better cooling capability when comparing with the wire-bonded package [14].

In the following section, the three main die attach technologies used for power packages, which are i) lead free soldering, ii) transient liquid phase (TLP) bonding and iii) silver sintering, are respectively reviewed in detail. Firstly, the fabrication process of die attach material is introduced. Then the processing technologies are discussed accordingly. Thirdly, the properties of typical materials used for each technology is summarized. Finally, a general comparison of lead free soldering, TLP bonding and silver sintering is given.

#### 1.2. REVIEW OF DIE ATTACH TECHNOLOGIES

#### 1.2.1. LEAD FREE SOLDERING TECHNOLOGY

The high lead (Pb) based solder alloys, with more than 85 wt% (by weight percentage, wt%) of Pb element and melting temperatures around 300°C, have historically been used as die attach materials for power electronic packages and modules [16]. Among which, Pb-5Sn-2.5Ag solder alloy has been used in the industry for decades as a standard die attach material, offering high melting temperature, acceptable thermal conductivity (23 W/(m·K)) and electrical conductivity  $(0.35 \times 10^7/(\Omega \cdot m))$  [4]. However, the toxicity of lead in solder alloys limited their wide application, which resulted in the development of lead free solder alloys.

Lead free solders, typically referring to Sn based solder alloys, have been applied for low power electronic packages and modules. The Sn-Ag-Cu (SAC) lead free solders have been proven to be suitable for Si based low power devices, due to their favorable wettability and mechanical properties [17-19]. However, the operation temperature of SiC based power modules can reach more than 200°C, which indicates that these lead free solders are no longer applicable. Gold (Au) based high temperature lead-free solders with melting temperature above 280°C have been widely used as die attach materials in high power devices. While several disadvantages of Au based solder alloys are known, such as the high cost, coarsening of microstructure, brittle nature of interfacial

intermetallic compounds (IMCs) and void issues, especially for the purpose of attaching large dies [19].

#### FABRICATION OF LEAD FREE SOLDERS

Solder paste is one of the most widely used forms of solder alloys for electronic assembling and it is usually mixed by solder powders and corresponding flux. The gained paste can be printed or dispensed on various substrates, such as DBC (Direct Bond Copper) and AMB (Active Metal Brazing). However, the limitation of stencil thickness, as well as the contamination of flux evaporation, restricts the application of solder paste in some occasions, especially for press pack packages.

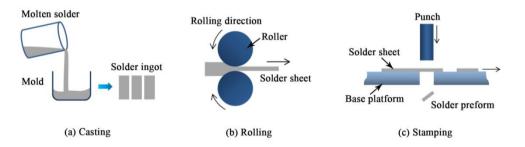

Solder preform is one of the most potential candidates for jointing various dies, substrates and lead frames. The solder preform is usually described as a two-dimensional film or sheet with ultrathin thickness. Solder preforms show many advantages over solder paste, such as high accuracy in thickness distribution after soldering, flux free processing, and repeatable production with complex sizes and shapes [20]. The fabrication process of solder preform is presented in Figure 1.3, which mainly consists of three steps: casting, rolling and stamping [21]. The molten solder is first poured into the mold and the solder ingot is obtained after cooling down to room temperature, as shown in Figure 1.3(a). Then the solder ingot is rolled into thin sheet with various thicknesses via adjusting the distance between two rollers, as indicated in Figure 1.3(b). The solder sheet is furtherly punched into small pieces according to the dimension of solder pad and the schematic diagram is shown in Figure 1.3(c). The complicated shapes of preform can be gained by the designing of mold.

Figure 1.3: Schematic diagrams of solder preform fabrication (not drawn to scale)

#### LEAD FREE SOLDERING PROCESS

Currently, several technologies have been developed for soldering process, such as reflow soldering, ultrasonic soldering, laser soldering, wave soldering, induction soldering [22].

The reflow soldering is regarded as the primary processing method for attaching power dies on substrate. Normally, prior to the reflow soldering, the solder paste / preform is first printed or dispensed / placed on the DBC, and then the die is placed onto the solder paste / preform. The reflow process usually consists of four continuous processes: preheating, soaking, reflow and cooling. Firstly, the assembled die/solder/DBC is quickly heated up from room temperature in the preheating step. During soaking process, the flux inside the paste begins to evaporate and removes the oxidation layer on the surfaces of solders and bonding pads. Then the solder is melting to form a liquid, and wet on bonding pads in the reflow process. Finally, the bonded package will be cooled down to room temperature in the cooling process.

During reflow, chemical reactions occur between the Sn based lead-free solder alloys and coating materials on substrate, such as Cu, Ni, Ag, and Au, and result in the formation of intermetallic compounds (IMCs) at the interface [23, 24]. It is well known that the presence of IMCs between solder alloys and substrate provides a good metallurgical bonding. However, an excessive layer of IMCs at the interface may cause reliability problems due to the brittleness of IMCs and their tendency to form defects [23, 25].

#### HIGH TEMPERATURE LEAD FREE SOLDER ALLOYS

Various lead free solders have been explored for high temperature applications with high thermal conductivity and reliability. The typical high melting temperature solders are represented by Sn-5Sb [26, 27], Au-20Sn [28, 29], Au-12Ge [30, 31], Au-3.2Si [32], Bi-Ag-X [33-35], Al-Zn-Mg [36], Al-Zn-Ge [36, 37] and Al-Zn-Cu [38], details are summarized in Table 1.1. Among which, the Au-20Sn eutectic solder alloy has been extensively applied in power electronic packages modules, due to its advantages of high electrical  $(1.64\times10^7/(\Omega\cdot m)$  [28]) and thermal conductivity (57 W/(m·K) [29, 39]), superior high temperature reliability, and possibility of flux free soldering [40, 41]. According to Au-Sn phase diagram, stable intermetallic compounds (IMCs) including  $Au_5Sn$ , AuSn,  $AuSn_2$ ,  $AuSn_4$  are formed at room temperature [16, 42], and  $Au_5Sn$  and AuSn are the two intermetallic compounds at the eutectic point. However, the high cost and poor resistance to thermomechanical stress also limited the application of Au-20Sn eutectic solder alloy [43].

| Solder<br>(wt%) | Bonding temp. (°C)* | Re-melting<br>temp. (°C)** | Thermal conductivity<br>W/( m·K) | CTE<br>10 <sup>-6</sup> K <sup>-1</sup> | Ref.     |

|-----------------|---------------------|----------------------------|----------------------------------|-----------------------------------------|----------|

| Sn-5Sb          | 245+30              | 245                        | 28                               | 27                                      | [26, 27] |

| Au-20Sn         | 278+30              | 278                        | 57                               | 18                                      | [29, 39] |

| Au-12Ge         | 356+30              | 356                        | 52                               | 12                                      | [30]     |

| Au-3.2Si        | 363+30              | 363                        | 27                               | 12                                      | [32]     |

| BiAgX           | 265+30              | 265                        | -                                | 15.4                                    | [33]     |

| Zn-Al-Mg        | 350+30              | 350                        | 42.94                            | 23.58                                   | [36]     |

| Zn-Al-Ge        | 362+30              | 362                        | 60.46                            | 20.03                                   | [36]     |

| Zn-Al-Cu        | ~380+30             | ~380                       | -                                | -                                       | [38]     |

Table 1.1: Summary of lead free solders used in power electronic packages and modules

#### 1.2.2. Transient Liquid Phase Bonding

Following the traditional soldering technology, transient liquid phase (TLP) bonding or termed as solid–liquid interdiffusion (SLID) bonding has been developed and offers low bonding temperature (around 250°C), flux free joining and high temperature reliability [44, 45]. The TLP bonding technology consists of at least one low and one high melting temperature metal, or a solder alloy with special designed constituent. After TLP bonding process, full IMCs are formed within the whole die attach layer. The formation of IMCs between die and substrate provides a stable bonding when they services at temperatures higher than the processing temperature [46]. However, the TLP bonding is a time-consuming process time due to the required isothermal solidification and sufficient bond homogenization, which usually takes more than 30 min per process [47]. In addition, and the evolution of formed IMCs will cause performance issues in the service process.

#### PREPARATION OF METAL LAYERS

There are three main methods used for fabricating the intermediate layers for TLP bonding. The first one is the solder preform with designed compositions according to the

<sup>\*</sup>Bonding temperature is 30~50°C higher than the liquid temperature

<sup>\*\*</sup>Only slight increase is induced due to the formation of small amount of IMCs in solder bulk

phase diagram. The preform can be prepared by applying the similar method as described in section **1.2.1**. The second method is depositing several single metal layers on the die backside or on the top of substrate or on both two areas. Comparing with physical vapor deposition (PVD) method, the metal layers fabricated by electroplating method are more simple and cost effective, and the gained layer structure is reproducible and uniform [44]. The third method uses the mixed pure metal powders (average diameter of  $5\sim20~\mu m$ ) which consist of a lower melting temperature one and a higher melting temperature one [48, 49]. The powders will be firstly mixed with certain amount of organics to form paste and then it can be printed or dispensed on substrate.

#### TLP BONDING PROCESS

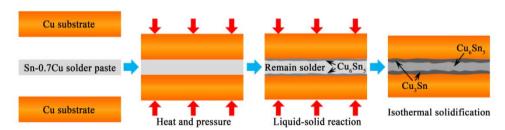

The TLP bonding process (taking Cu-Sn system as an example) can be achieved by several steps [50], as shown in Figure 1.4. Firstly, the Cu substrates and Sn layer are brought into contact, and then certain heat and pressure are applied. Secondly, the bonding process occurs when heating temperature upon the melting temperature of Sn. Once reached, the molten Sn diffuses and reacts with Cu, and results in the formation of IMCs (mainly  $Cu_6Sn_5$ ) at the interface. Vacuum or inert gas may also be needed for promoting the diffusion of Sn. Thirdly, the isothermal solidification process is needed to ensure the complete formation of IMCs within the whole joint. The final joint consists of two main phases:  $Cu_6Sn_5$  and  $Cu_3Sn$ , with melting temperature of 415°C and 676°C, respectively. Therefore, the re-melting temperature of TLP bonded joint is expected to increase from 232°C (Sn) to 415°C ( $Cu_6Sn_5$ ).

Figure 1.4: Schematic diagram of Cu-Sn TLP bonding process

#### MATERIALS FOR TLP BONDING

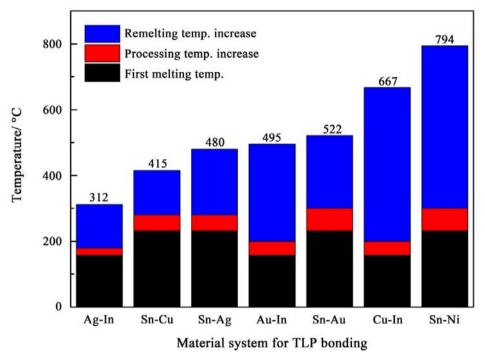

Different TLP bonding systems have been developed for attaching power die, such as Ag-In [51], Sn-Cu [52], Sn-Ag [53], Au-In [54, 55], Sn-Au [56], Cu-In [55] and Sn-Ni [57]. Figure 1.5 summarizes the temperature changes during TLP bonding process. Among the material systems, the Si-Ni system gained the highest re-melting temperature of 794°C

after bonding, which consists of  $Ni_3Sn_4$  and residual Ni. Besides, the Sn-Ni system got the highest increase of melting temperature (re-melting temp. minus first melting temp.). Besides, comparable electrical performances were gained for Sn-Ni TLP bonded IGBTs and commercial soldering ones [57]. The comprehensive comparison of various TLP bonding processes is summarized in Table 1.2.

Figure 1.5: Summary of temperature changes during TLP bonding

#### 1.2.3. SILVER SINTERING TECHNOLOGY

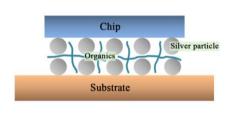

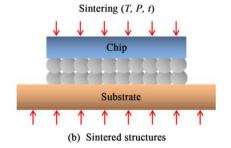

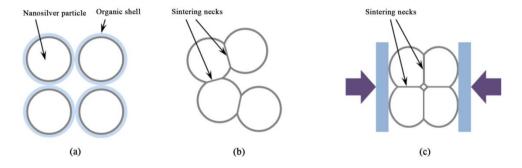

Sintering with metal nanoparticles has attracted increased attention in the die attach process [58-60]. The nanosilver sintering technology has been used as a die attach method in power devices since early 2000s [61]. The nanoparticles can be sintered as a bulk at relative lower temperatures when comparing with the melting point of pure metals. The simplified sintering process is shown in Figure 1.6. Several advantages in nanosilver sintered joints have been proven, such as low processing temperature (around 250°C), high thermal conductivity (240 W/(m·K)) and electrical conductivity (2.6×10<sup>7</sup> /( $\Omega$ ·m)), good thermal stability and favorable bonding strength [30, 62]. This method has been successfully applied in SiC and GaN based transistors and amplifiers with junction temperatures above 200°C [63]. Besides, the nano-copper sintering technology has also been developed for die attach process [64-67]. However, the highly oxidation of Cu nanoparticles during sintering limits the practical application in die attach process [68].

| Material system | Bonding requirements              | Resulted phases                                      | Re-melting<br>temp. (°C) | Ref.     |

|-----------------|-----------------------------------|------------------------------------------------------|--------------------------|----------|

| Ag-In           | 180°C, 3 MPa, 8 min, vacuum       | $Ag_2In$                                             | 312                      | [51]     |

| Sn-Cu           | 280°C, 0.05 MPa, 20 min, nitrogen | Cu <sub>6</sub> Sn <sub>5</sub> & Cu <sub>3</sub> Sn | 415                      | [52]     |

| Sn-Ag           | 280°C, 0.3 MPa, 30 min            | Ag <sub>3</sub> Sn & Ag                              | 480                      | [53]     |

| Au-In           | 200°C, 5 MPa, 10 min, argon       | $AuIn_2 & Au_9In_4$                                  | 495                      | [54, 55] |

| Sn-Au           | 350°C, 2.5 MPa, 30 min, vacuum    | $Au_{0.85}Sn_{0.15}$                                 | 522                      | [56]     |

| Cu-In           | 200°C, 50 MPa, 5 min, air         | $Cu_7In_3$                                           | 667                      | [55]     |

| Sn-Ni           | 300°C, 0.3 MPa, 120 min           | $\mathrm{Ni_{3}Sn_{4}}$                              | 794                      | [57]     |

Table 1.2: Summary of TLP bonding technology

(a) Screen printed silver material

Figure 1.6: Schematic diagram of sintering process, T, P and t represents the temperature, pressure and time, respectively

#### FORMATION OF SILVER PASTE

The Carey Lea's colloidal approach is one of the most commonly used ways to synthesis silver nanoparticles [69]. Generally, the silver nitrate (AgNO<sub>3</sub>) and sodium citrate dihydrate (Na<sub>3</sub>C<sub>6</sub>H<sub>5</sub>O<sub>7</sub>·2H<sub>2</sub>O) are used as ionic precursor and reducing agent, respectively. Firstly, a precursor is gained by dissolving AgNO<sub>3</sub> into deionized water and then the solution is heated to 80°C. Secondly, the reducing agent of Na<sub>3</sub>C<sub>6</sub>H<sub>5</sub>O<sub>7</sub>·2H<sub>2</sub>O is added slowly into the precursor under magnetic stirring, then the solution is heated to 90°C and kept for 1 hour. After this process, the solution is cooled down to room temperature in ambient atmosphere. Thirdly, the solution is concentrated by centrifugation and only water was left on the top. The nanosilver particles are obtained by removing the upper water.

The silver nanoparticles will be further mixed with binders and thinners to form

nanosilver paste. Binders are long chain polymers and mainly used for supporting the nanoparticles and preventing the cracking of sintered paste during heating process. The sintered nanosilver joint with binder system of low burnout temperatures showed a denser microstructure [70]. Thinners are used for controlling the viscosity of silver paste, which will be further used for screen/stencil printing or syringe dispensing.

#### SILVER SINTERING PROCESS

Generally, there are two main methods used for nanosilver sintering: pressureless sintering and pressure assisted sintering. The pressureless sintering of silver paste is usually achieved in a heating plate, furnace or even the reflow oven. The whole heating process mainly consists of three stages, the preheating (initial heating and drying), sintering and cooling stage. Since the silver paste contains certain amount of organics, the preheating process is necessarily needed for the drying of some organics, which will last for around 30 min [71, 72]. The silver paste is usually heated up to 250~300°C during sintering stage and kept for  $5\sim30$  min. The whole sintering process can be finished in air. The most significant advantage of pressureless sintering is the simple operation process. However, obvious disadvantages are also proposed and the first one is the time-consuming process of this technology. Secondly, the incomplete evaporation of organics inside the silver paste will result in the increase of porosity. Meanwhile, the contamination issue of organic burnout is another concern for the reliability of power packages. Thirdly, the pressureless sintered joint usually has a high porosity, which will decrease the thermal and electrical performance of power package. Besides, the pressureless sintering is only suitable for the sintering of chips that is smaller than 3×3 mm<sup>2</sup> [73, 74].

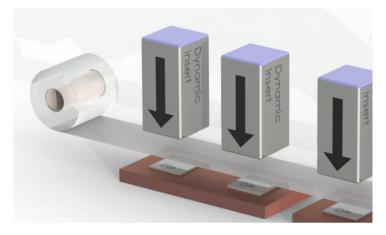

It has been proven that the application of pressure during sintering improved the properties of sintered joints [75, 76]. Firstly, the applied pressure helps to increase the number of interactions between different nanoparticles. Secondly, the pressure acted as a mechanical force to help the evaporation of organic shells except thermal load. It is suggested that the application of 5 MPa pressure during sintering can help the joints to get a high shear strength [77, 78]. Figure 1.7 shows a simplified layout of pressure assisted sintering equipment, which has already been used for many commercial projects.

According to the research conducted by Wang [79], the pressure assisted sintering process is carried out as follows: firstly, the nanosilver film is first transferred to the bonding area of the die. Next, by using a pick-and-place process, the die will be furtherly assembled on DBC substrate which locates at the designed loading plate. After assembling, the loading plate will be moved into the equipment for fast sintering, which

only takes few minutes. During this process, a precisely controlled pressure will be applied on individual die through the patented dynamic insert. It is suggested that the final sintered structure has a uniform microstructure and a typical density more than 85% can be obtained.

Figure 1.7: Layout of pressure assisted sintering (Courtesy of Boschman Technologies)

#### MATERIALS FOR SILVER SINTERING

When the size of metal particle reduces to nanoscale, the driving force for sintering increases due to the high surface curvature of nanoparticle, which will also lead to the decrease of melting temperature [80-82]. These phenomena are expected to enhance the sintering of nanosilver particles. Until now, different types of silver materials have been developed for die attach process, such as silver nanoparticle paste [83, 84], silver micro-particle paste [85], silver oxide micro-particle paste [86, 87], silver flake paste [88], silver nanonord paste [89], and etc. Besides, in order to increase the packing density inside sintered layer, the silver particles with different diameters are usually mixed together. For instance, the typical volumetric ratio of 1:3 is suggested for nano to micron-Ag ratio to get the maximum packing density [90]. According to the test results from Li *et al* [91], the sintered layer, which originally consists of 10 and 50 nm particles, has gained high thermal conductivity (278.5 W/(m·K)) and shear strength (41.8 MPa), as well as excellent resistance to thermal cycling.

In addition, due to the high electrical and thermal conductivity, as well as low cost of copper, the copper particles with an average diameter of 50 nm were added into nanosilver paste [92-94]. The composite paste was then sintered at 380°C without applying pressure. The bonding strength, thermal and electrical conductivity showed a decreasing trend with the increasing percentage of copper particles. The high weight percentage of copper particles resulted in the increase of porosity. The best bonding

properties were found on silver coated substrate. As a result, the composite paste with 20 wt% copper particles showed acceptable sintering properties. Similar results were gained with aluminum refined nanosilver paste [95-98]. In addition, the die attached by silver epoxy and conductive adhesives showed lower thermal conductivities ( $\sim$ 60 W/(m·K) and  $\sim$ 10 W/(m·K), respectively) when compared with sintered nanosilver particles with dimensions of  $10\sim$ 30 nm (200 W/(m·K)) [99-101].

Recently, the nanosilver film, which has a similar composition as the silver paste, has been proven to be one of the most potential die attach materials [102-104]. The nanosilver film sintered layer has a uniform thickness distribution and less organic burnout, which ensures the high bonding quality between the power die and substrate. However, few researches have been done to systematically investigate the sintering properties of this material.

#### 1.2.4. Comparison of three main die attach technologies

The comprehensive comparisons of die attach methods are listed in Table 1.3, and three main differences can be found. Firstly, there is a big difference in the composition of die attach materials. Comparing with the lead free soldering and silver sintering, the materials used in TLP bonding technology consist of at least one or two materials with different melting temperatures.

Secondly, the final compositions vary from each other. The remaining solder alloy and IMCs are the main phases in lead free soldered layer. However, full IMCs are formed in the final die attach layer of TLP bonding. Different from the previous two methods, the nano/micro silver sintered layer only consists of pure silver and small amount of residual organics.

Thirdly, the nano/micro silver sintered die attach layer gained the highest increase of re-melting temperature, which is comparable to the melting temperature of the bulk silver material (961°C). The re-melting temperature of TLP bonded die attach layer is higher than lead free soldered layer due to the formation of IMCs within the whole layer. Although the IMCs formed at the interface of lead free solder and substrate, the re-melting temperature of lead free soldered layer only increases slightly.

Table 1.3: Comprehensive comparison of die attach methods

|                                  | Soldering<br>(Au-20Sn)                                          | TLP bonding<br>(Sn-Cu)                       | Sintering<br>(Nanosilver paste) |

|----------------------------------|-----------------------------------------------------------------|----------------------------------------------|---------------------------------|

| Material compositions            | Solder alloy                                                    | Solder alloy or pure Sn                      | Nanoparticles + organics        |

| Material types                   | Paste, preform                                                  | Paste, thin layer                            | Paste, film                     |

| Substrate/die surface coating    | Ni-Au (both)                                                    | Ni-Au on die                                 | Ag or Au (both)                 |

| Processing method                | Reflow, ultrasonic soldering                                    | Direct heating                               | Sintering                       |

| Processing temp.                 | 310°C                                                           | 230°C                                        | 250°C                           |

| Pressure<br>required             | No                                                              | Yes                                          | Yes/No                          |

| Final compositions               | Solder alloy + IMCs                                             | Full IMCs (Cu <sub>6</sub> Sn <sub>5</sub> ) | Pure Ag + organic<br>residuals  |

| Re-melting<br>temperature        | Slightly higher than solder's melting point                     | Melting point of IMCs                        | Theoretically<br>961°C          |

| Thermal conductivity             | 57 W/(m·K) [42]                                                 | 34.1 W/(m·K) [105]                           | 240 W/(m·K) [106]               |

| Electrical conductivity          | $1.64 \times 10^7 / (\Omega \cdot \text{m}) [41]$               | 0.57×10 <sup>7</sup> /(Ω·m) [105]            | 2.6×10 <sup>7</sup> /(Ω·m) [30] |

| CTE at 25°C                      | 18×10 <sup>-6</sup> /K [107]                                    | 16.3×10 <sup>-6</sup> /K [108]               | 19×10 <sup>-6</sup> /K [106]    |

| Young's<br>modulus               | 70.95 GP, at 25°C [107]                                         | 119 GP, at 25°C [109]                        | 9 GP, at 25°C [106]             |

| Accurate control of final height | Difficult                                                       | Difficult                                    | Can be controlled               |

| Voiding issue                    | Can be optimized                                                | Can be optimized                             | Micro/nano voids                |

| Reliability issues               | Brittle interfacial<br>IMCs, and evolution<br>of microstructure | Evolution of IMCs                            | Evolution of voids              |

#### 1.3. RESEARCH OBJECTIVES

The press pack IGBT module has shown superior performance in high power density applications and is expected to work at temperatures higher than 200°C. Comparing with the high temperature soldering technology and TLP bonding technology, the nanosilver sintering technology has significant advantage in attaching chips in a press pack IGBT module. However, limited researches have reported the application of nanosilver sintering technology in high power press pack modules. Furthermore, most of the literatures are studying the properties of pressureless sintered silver joint, which has exhibited limitations in high power modules due to the degradation of the electrical and thermal performance resulted from its high porosity. In comparison, the pressure assisted sintering technology shows great potentials since the sintering pressure enhances the bonding quality of nanosilver sintered joint. In addition, current research lacks the knowledge of pressure assisted nanosilver sintering process.

According to the problem descriptions above, the objectives of this thesis are:

- (1) The sintering pressure, temperature and time are the three dominating factors in determining the sintering properties of nanosilver particles. The sintering behavior of nanosilver particles at various parameters is one of the main topics that this research is set to explore. The corresponding shear strength and fracture morphology of sintered joint are investigated. The obtained results provide technical guidance to the feasibility of employing pressure assisted nanosilver sintering technology in attaching power chips.

- (2) The nanosilver sintered layer is expected to serve applications with such requirements as high bonding strength while maintaining high temperature stability. Thus, the high temperature nanoindentation is performed in this thesis to obtain the micro mechanical properties of sintered layer. The plastic behavior and creep properties of sintered nanosilver particles are investigated by considering both the temperature effect and pressure effect. The test results provide foundational knowledge for the future pressure assisted sintering of nanosilver particles, which is also one of the most valuable novelties of this research to the whole power electronics field

- (3) The pressure assisted sintering technology is designed for the nanosilver double side sintered press pack power package. Mechanical tests prove the high bonding quality of sintered layer. The designed technology is successfully implemented in the mass production of press pack power package. The finite element analysis is carried out to simulate the effects of sintering sequence on the stress distribution of sintered package. The sintering stress analysis will be intensely addressed in this thesis as it is

1.4. THESIS OUTLINE 15

one of the most challenging parts in the power package fabrication process.

(4) The nanosilver sintering technology is employed in the ceramic package. The sintered area is examined by several methods to ensure the high bonding quality. The finite element analysis method is used to predict the stress distribution of sintered package. Comparisons are given between the two kinds of lids sintered package, including bonding quality, stress distribution and sintering pressure effects.

#### 1.4. THESIS OUTLINE

The rest of this thesis is structured as follows:

Chapter 2 focuses on the effects of sintering parameters on the bonding quality of nanosilver sintered sandwich package. The evolution of shear strength and fracture morphology is respectively investigated at various sintering pressures, temperatures, time. The bonding mechanism of nanosilver particles is discussed based on the results obtained. Based on the analysis in Chapter 2, Chapter 3 focuses on investigating the micro mechanical properties of pressure sintered nanosilver joint at various test temperatures. The nanoindentation test is performed for sintered joint to evaluate the sintering pressure effects on the bonding properties of nanosilver particles. The plastic stress-strain constitutive equations of pressure sintered nanosilver joint at room temperature are demonstrated in Chapter 3. The effects of temperature on the hardness and elastic modulus are analyzed accordingly. Besides, the initial creep properties of pressure sintered nanosilver joint at high temperatures are characterized.

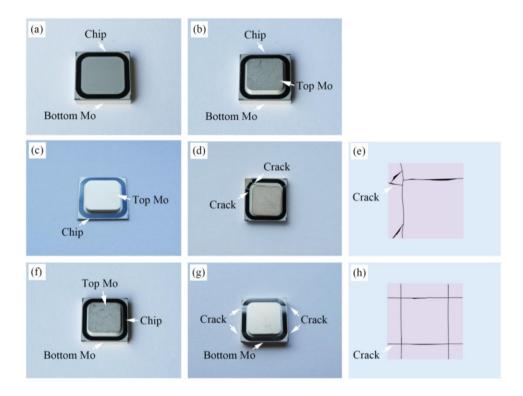

Chapter 4 focuses on employing the nanosilver sintering technology in the double side sintered press pack power module. The morphologies and density of pressure free and pressure assisted sintered nanosiver particles are first compared. Mechanical characterization is conducted and the module shows satisfying performance in terms of shear strength and fracture morphology, proving the presented nanosilver sintering technology as promising approach for attaching chips of high power press pack module application. Chapter 5 focuses on investigating the stress distributions of sintered package in various sintering sequences and sintering pressures since the cracking of die becomes the critical issue in pressure assisted sintering process. One of the research approaches employed in this thesis is the combination of the experimental tests and finite element analysis simulations. Three main sintering sequences are designed to fabricate the double side nanosilver sintered module. The simulation results explained the crack generation and prolongation in chips. The optimal sintering sequence is recommended for the future mass production.

Chosen as another application scenario of nanosilver sintering technology, the

sealing of a hermetic cavity is realized and presented in Chapter 6. The silver coated copper and silicon are selected as lid materials for the hermetic cavity. The bonding properties of sintered layer are characterized by the X-ray and C-SAM. The test results showed that the silicon lid sintered cavity displays good bonding quality. Finite element analysis (FEA) is employed to evaluate the stress distribution on sintered cavity and the obtained results are analyzed and compared with the experimental results. In addition, the effects of sintering pressure on the evolution of maximum stress distribution on both copper lid and silicon lid are explained in detail in this chapter.

In Chapter 7, the main conclusions and recommendations of this thesis are summarized. The achievement of this thesis provides fundamental knowledge for the further development of pressure assisted nanosilver sintering technology. Finally, an outlook for future research and development is presented.

#### REFERENCES

- [1] J.G. Kassakian and T.M. Jahns, *Evolving and emerging applications of power electronics in systems*, IEEE Journal of Emerging and Selected Topics in Power Electronics 1, 47 (2013).

- [2] F. Iacopi, M. Hove, M. Charles, and K. Endo, *Power electronics with wide bandgap materials: Toward greener, more efficient technologies*, MRS Bulletin **40**, 390 (2015).

- [3] B. Ji, X. Song, E. Sciberras, W. Cao, Y. Hu, and V. Pickert, *Multiobjective design optimization of IGBT power modules considering power cycling and thermal cycling*, IEEE Transactions on Power Electronics **30**, 2493 (2015).

- [4] L.A. Navarro, X. Perpiñà, P. Godignon, J. Montserrat, V. Banu, M. Vellvehi, and X. Jordà, *Thermomechanical assessment of die-attach materials for wide bandgap semiconductor devices and harsh environment applications*, IEEE Transactions on Power Electronics **29**, 2261 (2014).

- [5] R. Khazaka, L. Mendizabal, D. Henry, and R. Hanna, *Survey of high-temperature reliability of power electronics packaging components*, IEEE Transactions on Power Electronics **30**, 2456 (2015).

- [6] C. Hang, J. He, Z. Zhang, H. Chen, and M. Li, Low temperature bonding by infiltrating Sn3.5Ag solder into porous Ag sheet for high temperature die attachment in power device packaging, Scientific Reports 8, 17422 (2018).

- [7] J. Broughton, V. Smet, R.R. Tummala, and Y.K. Joshi, Review of thermal packaging

technologies for automotive power electronics for traction purposes, Journal of Electronic Packaging **140**, 040801 (2018).

- [8] J. Millan, P. Godignon, X. Perpina, A. Pérez-Tomás, and J. Rebollo, *A survey of wide bandgap power semiconductor devices*, IEEE Transactions on Power Electronics **29**, 2155 (2014).

- [9] H.A. Mantooth, M.D. Glover, and P. Shepherd, *Wide bandgap technologies and their implications on miniaturizing power electronic systems*, IEEE Journal of Emerging and Selected Topics in Power Electronics **2**, 374 (2014).

- [10] L. Fu, X. Zhang, M. Scott, C. Yao, and J. Wang, *The evaluation and application of wide bandgap power devices*, in *IEEE Conference and Expo Transportation Electrification Asia-Pacific (ITEC Asia-Pacific 2014)*, 2014, pp. 1-5.

- [11] H.A. Mustain, W.D. Brown, and S.S. Ang, *Transient liquid phase die attach for high-temperature silicon carbide power devices*, IEEE Transactions on Components and Packaging Technologies **33**, 563 (2010).

- [12] Y. Nakakohara, H. Otake, T.M. Evans, T. Yoshida, M. Tsuruya, and K. Nakahara, Three-phase LLC series resonant DC/DC converter using SiC MOSFETs to realize high-voltage and high-frequency operation, IEEE Transactions on Industrial Electronics 63, 2103 (2016).

- [13] H.S. Chin, K.Y. Cheong, and A.B. Ismail, *A review on die attach materials for SiC-based high-temperature power devices*, Metallurgical and Materials Transactions B **41**, 824 (2010).

- [14] U.M. Choi, F. Blaabjerg, and K.B. Lee, *Study and handling methods of power IGBT module failures in power electronic converter systems*, IEEE Transactions on Power Electronics **30**, 2517 (2015).

- [15] H. Ye, M. Lin, and C. Basaran, *Failure modes and FEM analysis of power electronic packaging*, Finite Elements in Analysis and Design **38**, 601 (2002).

- [16] G. Zeng, S. McDonald, and K. Nogita, *Development of high-temperature solders:* review, Microelectronics Reliability **52**, 1306 (2012).

- [17] H. Yu and J.K. Kivilahti, *Nucleation kinetics and solidification temperatures of SnAgCu interconnections during reflow process*, IEEE Transactions on Components and Packaging Technologies **29**, 778 (2006).

- [18] M. Drienovsky, L.R. Trnkova, M. Martinkovic, M. Ozvold, I. Cernickova, M. Palcut, and J. Janovec, *Influence of cerium addition on microstructure and properties of*

- Sn-Cu-(Ag) solder alloys, Materials Science and Engineering: A 623, 83 (2015).

- [19] A.A. Bajwa, Y. Qin, R. Reiner, R. Quay, and J. Wilde, *Assembly and packaging technologies for high-temperature and high-power GaN devices*, IEEE Transactions on Components, Packaging and Manufacturing Technology **5**, 1402 (2015).

- [20] P. Godijn, W. Veldhuizen, P. Lusse, M.T. Holtzer, R. Ekeren, and M. Haan, *Solder preforms for use in electronic assembly*, (2009), US Patent 7533793B2.

- [21] N. Hirano, A. Tanahashi, Y. Sakamoto, K. Tsuruta, T. Ishii, and S. Soga, *Solder preform and a process for its manufacture*, (2010), US Patent 7793820B2.

- [22] http://www.welding-consultant.com/SolderingBrazing.

- [23] T. Laurila, V. Vuorinen, and J. Kivilahti, *Interfacial reactions between lead-free solders and common base materials*, Materials Science and Engineering: R: Reports **49**, 1 (2005).

- [24] Y. Liu, F. Sun, L. Luo, C.A. Yuan, and G. Zhang, *Microstructure evolution and shear behavior of the solder joints for flip-chip LED on ENIG substrate*, Journal of Electronic Materials **44**, 2450 (2015).

- [25] O.M. Abdelhadi and L. Ladani, *IMC growth of Sn-3.5Ag/Cu system: combined chemical reaction and diffusion mechanisms*, Journal of Alloys and Compounds **537**, 87 (2012).

- [26] S.W. Chen, P.Y. Chen, and C.H. Wang, Lowering of Sn-Sb alloy melting points caused by substrate dissolution, Journal of Electronic Materials 35, 1982 (2006).

- [27] H. Beyer, V. Sivasubramaniam, M. Bayer, and S. Hartmann, Reliability of lead-free large area solder joints in IGBT modules with respect to passive and active thermal cycling, in 9th International Conference on Integrated Power Electronics Systems (CIPS 2016), 2016, pp. 1-6.

- [28] Z. Tao, T. Bobal, M. Oud, and S.L. Jia, *An introduction to eutectic Au/Sn solder alloy and its preforms in microelectronics/optoelectronic packaging applications*, Electronics & Packaging **8**, 2 (2005).

- [29] J.W. Yoon, H.S. Chun, J.M. Koo, and S.B. Jung, *Au–Sn flip-chip solder bump for microelectronic and optoelectronic applications*, Microsystem Technologies **13**, 1463 (2007).

- [30] V.R. Manikam and K.Y. Cheong, Die attach materials for high temperature

- applications: A review, IEEE Transactions on Components, Packaging and Manufacturing Technology 1, 457 (2011).

- [31] N. Weyrich, S. Jin, L.I. Duarte, and C. Leinenbach, *Joining of Cu, Ni, and Ti using Au-Ge-based high-temperature solder alloys*, Journal of Materials Engineering and Performance **23**, 1585 (2014).

- [32] A. Hartnett and S. Buerki, *Process and reliability advantages of AuSn eutectic die attach*, Proc. 42nd IMAPS 281 (2009).

- [33] Z. Shen, R.W. Johnson, and M.C. Hamilton, *SiC power device die attach for extreme environments*, IEEE Transactions on Electron Devices **62**, 346 (2015).

- [34] H. Zhang and N.C. Lee, *A novel high melting lead-free mixed solder paste system*, in *IEEE 13th Electronics Packaging Technology Conference (EPTC 2011)*, 2011, pp. 567-572.

- [35] Z. Shen, K. Fang, R.W. Johnson, and M.C. Hamilton, *Characterization of Bi–Ag–X solder for high temperature SiC die attach*, IEEE Transactions on Components, Packaging and Manufacturing Technology **4**, 1778 (2014).

- [36] M. Uvarajan, L. Lim, M. Goh, F. Ng, and W. Pan, *Temperature cycling aging studies of Zn-based solders for high-temperature applications*, in *IEEE 17th Electronics Packaging and Technology Conference (EPTC 2015)*, 2015, pp. 1-5.

- [37] A. Haque, Y. Won, A. Haseeb, and H. Masjuki, *Investigations on Zn-Al-Ge alloys as high temperature die attach material*, in *3rd Electronic System-Integration Technology Conference (ESTC 2010)*, 2010, pp. 1-5.

- [38] N. Kang, H.S. Na, S.J. Kim, and C.Y. Kang, *Alloy design of Zn–Al–Cu solder for ultra high temperatures*, Journal of Alloys and Compounds **467**, 246 (2009).

- [39] H. Zhang, J. Fan, J. Zhang, C. Qian, X. Fan, F. Sun, and G. Zhang, *Reliability optimization of gold-tin eutectic die attach layer in HEMT package*, in *13th China International Forum on Solid State Lighting (SSLChina 2016)*, 2016, pp. 52-56.

- [40] C.P. Wang, T.T. Chen, H.K. Fu, T.L. Chang, P.T. Chou, and M.T. Chu, *Analysis of thermal characteristics and mechanism of degradation of flip-chip high power LEDs*, Microelectronics Reliability **52**, 698 (2012).

- [41] Y. Wang, W. Liu, Y. Ma, Y. Huang, Y. Tang, F. Cheng, and Q. Yu, *Indentation size effect* and micromechanics characterization of intermetallic compounds in the Au–Sn system, Materials Science and Engineering: A **610**, 161 (2014).

[42] Y. Tian, W. Zhou, and P. Wu, A density functional investigation of the structural, elastic and thermodynamic properties of the Au–Sn intermetallics, Journal of Electronic Materials 45, 639 (2016).

- [43] M. Hindler, Z. Guo, and A. Mikula, *Lead-free solder alloys: Thermodynamic properties of the (Au+Sb+Sn) and the (Au+Sb) system*, The Journal of Chemical Thermodynamics **55**, 102 (2012).

- [44] A.A. Bajwa and J. Wilde, *Reliability modeling of Sn–Ag transient liquid phase die-bonds for high-power SiC devices*, Microelectronics Reliability **60**, 116 (2016).

- [45] S. Marauska, M. Claus, T. Lisec, and B. Wagner, Low temperature transient liquid phase bonding of Au/Sn and Cu/Sn electroplated material systems for MEMS wafer-level packaging, Microsystem Technologies 19, 1119 (2013).

- [46] V. Vuorinen, A. Rautiainen, and M. Paulasto-Krockel, *Design for reliability of Au-Sn and Cu-Sn based SLID bonds*, in *European Microelectronics Packaging Conference (EMPC 2015)*, 2015, pp. 1-6.

- [47] G.O. Cook and C.D. Sorensen, *Overview of transient liquid phase and partial transient liquid phase bonding*, Journal of Materials Science **46**, 5305 (2011).

- [48] F. Lang, H. Yamaguchi, H. Nakagawa, and H. Sato, *Thermally stable bonding of SiC devices with ceramic substrates: Transient liquid phase sintering using Cu/Sn powders*, Journal of The Electrochemical Society **160**, D315 (2013).

- [49] H. Feng, J. Huang, J. Yang, S. Zhou, R. Zhang, and S. Chen, *A transient liquid phase sintering bonding process using nickel-tin mixed powder for the new generation of high-temperature power devices*, Journal of Electronic Materials **46**, 4152 (2017).

- [50] A. Syed Khaja, C. Kaestle, and J. Franke, *Reliable packaging technologies for power electronics: Diffusion soldering and heavy copper wire bonding,* in *3rd International Electric Drives Production Conference (EDPC 2013)*, 2013, pp. 1-6.

- [51] S.J. Hsu and C.C. Lee, Bonding of SiC chips to copper substrates using Ag-In system, in IEEE 65th Electronic Components and Technology Conference (ECTC 2015), 2015, pp. 1247-1250.

- [52] K. Chu, Y. Sohn, and C. Moon, *A comparative study of Cn/Sn/Cu and Ni/Sn/Ni solder joints for low temperature stable transient liquid phase bonding*, Scripta Materialia **109**, 113 (2015).

- [53] N.S. Nobeen, R. Imade, B.R. Lee, R. Phua, E. Jian, C.C. Wong, C.L. Gan, and Z. Chen, Transient liquid phase (TLP) bonding using Sn/Ag multilayers for high

temperature applications, in *IEEE 15th Electronics Packaging Technology Conference (EPTC 2013)*, 2013, pp. 647-652.

- [54] B.J. Grummel, Z.J. Shen, H.A. Mustain, and A.R. Hefner, *Thermo-mechanical characterization of Au-In transient liquid phase bonding die-attach*, IEEE Transactions on Components, Packaging and Manufacturing Technology **3**, 716 (2013).

- [55] J.B. Lee, H.Y. Hwang, and M.W. Rhee, *Reliability investigation of Cu/In TLP bonding*, Journal of Electronic Materials **44**, 435 (2015).

- [56] T.A. Tollefsen, A. Larsson, O.M. Lovvik, and K.E. Aasmundtveit, *High temperature interconnect and die attach technology: Au–Sn SLID bonding*, IEEE Transactions on Components, Packaging and Manufacturing Technology **3**, 904 (2013).

- [57] S.W. Yoon, M.D. Glover, and K. Shiozaki, *Nickel–tin transient liquid phase bonding toward high-temperature operational power electronics in electrified vehicles*, IEEE Transactions on Power Electronics, **28**, 2448 (2013).

- [58] J. Scola, X. Tassart, C. Vilar, F. Jomard, E. Dumas, Y. Veniaminova, P. Boullay, and S. Gascoin, *Microstructure and electrical resistance evolution during sintering of a Ag nanoparticle paste*, Journal of Physics D: Applied Physics **48**, 145302 (2015).

- [59] T. Yamakawa, T. Takemoto, M. Shimoda, H. Nishikawa, K. Shiokawa, and N. Terada, Influence of joining conditions on bonding strength of joints: efficacy of low-temperature bonding using Cu nanoparticle paste, Journal of Electronic Materials **42**, 1260 (2013).

- [60] C. Buttay, B. Allard, and R. Riva, Silver sintering for power electronics integration, in International Conference on Electronics Packaging and iMAPS All Asia Conference (ICEP-IACC 2015), 2015, pp. 554-558.

- [61] Z. Zhang and G.Q. Lu, *Pressure-assisted low-temperature sintering of silver paste* as an alternative die-attach solution to solder reflow, IEEE Transactions on Electronics Packaging Manufacturing **25**, 279 (2002).

- [62] J. Bai, Z. Zhang, J. Calata, and G. Lu, Characterization of low-temperature sintered nanoscale silver paste for attaching semiconductor devices, in 2005 Conference on High Density Microsystem Design and Packaging and Component Failure Analysis, 2005, pp. 1-5.

- [63] C. Buttay, D. Planson, B. Allard, D. Bergogne, P. Bevilacqua, C. Joubert, M. Lazar, C.Martin, H. Morel, and D. Tournier, State of the art of high temperature power

- electronics, Materials Science and Engineering: B 176, 283 (2011).

- [64] J. Liu, H. Chen, H. Ji, and M. Li, *Highly conductive Cu–Cu joint formation by low-temperature sintering of formic acid-treated Cu nanoparticles*, ACS Applied Materials & Interfaces **8**, 33289 (2016).

- [65] B.H. Lee, M.Z. Ng, A.A. Zinn, and C.L. Gan, Evaluation of copper nanoparticles for low temperature bonded interconnections, in IEEE 22nd International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA 2015), 2015, pp. 102-106.

- [66] T. Ishizaki, A. Kuno, A. Tane, M. Yanase, F. Osawa, T. Satoh, and Y. Yamada, Reliability of Cu nanoparticle joint for high temperature power electronics, Microelectronics Reliability 54, 1867 (2014).

- [67] T. Ishizaki, T. Satoh, A. Kuno, A. Tane, M. Yanase, F. Osawa, and Y. Yamada, *Thermal characterizations of Cu nanoparticle joints for power semiconductor devices*, Microelectronics Reliability **53**, 1543 (2013).

- [68] J. Kähler, N. Heuck, A. Wagner, A. Stranz, E. Peiner, and A. Waag, *Sintering of copper particles for die attach*, IEEE Transactions on Components, Packaging and Manufacturing Technology **2**, 1587 (2012).

- [69] G. Frens and J.T.G. Overbeek, *Carey Lea's colloidal silver*, Kolloid-Zeitschrift und Zeitschrift für Polymere **233**, 922 (1969).

- [70] J.G. Bai, T.G. Lei, J.N. Calata, and G.Q. Lu, *Control of nanosilver sintering attained through organic binder burnout*, Journal of Materials Research **22**, 3494 (2007).

- [71] A.A. Wereszczak, B.R. Chen, and B.A. Oistad, *Reflow-oven-processing of pressureless sintered-silver interconnects*, Journal of Materials Processing Technology **255**, 500 (2018).

- [72] X. Wang, Y. Mei, X. Li, M. Wang, Z. Cui, and G.Q. Lu, *Pressureless sintering of nanosilver paste as die attachment on substrates with ENIG finish for semiconductor applications*, Journal of Alloys and Compounds **777**, 578 (2019).

- [73] K. Qi, X. Chen, and G.Q. Lu, Effect of interconnection area on shear strength of sintered joint with nano-silver paste, Soldering & Surface Mount Technology **20**, 8 (2008).

- [74] W. Guo, Z. Zeng, X. Zhang, P. Peng, and S. Tang, *Low-Temperature sintering bonding using silver nanoparticle paste for electronics packaging*, Journal of Nanomaterials **2015**, 10 (2015).

[75] T.G. Lei, J.N. Calata, G.Q. Lu, X. Chen, and S. Luo, *Low-temperature sintering of nanoscale silver paste for attaching large-area chips*, IEEE Transactions on Components and Packaging Technologies **33**, 98 (2010).

- [76] M. Knoerr and A. Schletz, Power semiconductor joining through sintering of silver nanoparticles: evaluation of influence of parameters time, temperature and pressure on density, strength and reliability, in 6th International Conference on Integrated Power Electronics Systems (CIPS 2010), 2010, pp. 1-6.

- [77] Y. Mei, G. Chen, Y. Cao, X. Li, D. Han, and X. Chen, *Simplification of low-temperature sintering nanosilver for power electronics packaging*, Journal of Electronic Materials **42**, 1209 (2013).

- [78] G. Chen, Y. Cao, Y. Mei, D. Han, G.Q. Lu, and X. Chen, *Pressure-assisted low-temperature sintering of nanosilver paste for 5×5 mm*<sup>2</sup> *chip attachment*, IEEE Transactions on Components, Packaging and Manufacturing Technology **2**, 1759 (2012).

- [79] L. Wang, Low temperature hermertic packaging with Ag sintering process, in 16th International Conference on Electronic Packaging Technology (ICEPT 2015), 2015, pp. 1317-1320.

- [80] H. Alarifi, A. Hu, M. Yavuz, and Y.N. Zhou, Silver nanoparticle paste for low-temperature bonding of copper, Journal of Electronic Materials 40, 1394 (2011).

- [81] H. Alarifi, M. Atis, C. Özdoğan, A. Hu, M. Yavuz, and Y. Zhou, *Molecular dynamics* simulation of sintering and surface premelting of silver nanoparticles, Materials Transactions **54**, 884 (2013).

- [82] P. Peng, A. Hu, A.P. Gerlich, G. Zou, L. Liu, and Y.N. Zhou, *Joining of silver nanomaterials at low temperatures: processes, properties, and applications*, ACS Applied Materials & Interfaces **7**, 12597 (2015).

- [83] S. Park, D. Seo, and J. Lee, *Preparation of Pb-free silver paste containing nanoparticles*, Colloids and Surfaces A: Physicochemical and Engineering Aspects **313**, 197 (2008).

- [84] W.H. Li, P.S. Lin, C.N. Chen, T.Y. Dong, C.H. Tsai, W.T. Kung, J.M. Song, Y.T. Chiu, and P.F. Yang, *Low-temperature Cu-to-Cu bonding using silver nanoparticles stabilised by saturated dodecanoic acid*, Materials Science and Engineering: A **613**, 372 (2014).

[85] J. Jiu, H. Zhang, S. Nagao, T. Sugahara, N. Kagami, and K. Suganuma, *A new micro-silver paste for high power semiconductor devices*, in *China Semiconductor Technology International Conference (CSTIC 2016)*, 2016, pp. 1-3.

- [86] A. Hirose, H. Tatsumi, N. Takeda, Y. Akada, T. Ogura, E. Ide, and T. Morita, *A novel metal-to-metal bonding process through in-situ formation of Ag nanoparticles using Ag<sub>2</sub>O microparticles,* Journal of Physics: Conference Series **165**, 012074 (2009).

- [87] F. Mu, Z. Zhao, G. Zou, H. Bai, A. Wu, L. Liu, D. Zhang, and Y.N Zhou, *Mechanism of low temperature sintering-bonding through in-situ formation of silver nanoparticles using silver oxide microparticles*, Materials Transactions **54**, 872 (2013).

- [88] C.A. Lu, P. Lin, H.C. Lin, and S.F. Wang, Effects of metallo-organic decomposition agents on thermal decomposition and electrical conductivity of low-temperature-curing silver paste, Japanese Journal of Applied Physics 45, 6987 (2006).

- [89] J. Jiu, K. Murai, K. Kim, and K. Suganuma, *Synthesis of silver nanorods and application for die attach material in devices*, Journal of Materials Science: Materials in Electronics **21**, 713 (2010).

- [90] K.S. Siow and Y. Lin, *Identifying the development state of sintered silver (Ag) as a bonding material in the microelectronic packaging via a patent landscape study,* Journal of Electronic Packaging **138**, 020804 (2016).

- [91] M. Li, Y. Xiao, Z. Zhang, and J. Yu, Bimodal sintered silver nanoparticle paste with ultrahigh thermal conductivity and shear strength for high temperature thermal interface material applications, ACS Applied Materials & Interfaces 7, 9157 (2015).

- [92] K.S. Tan and K.Y. Cheong, *Physical and electrical characteristics of silver-copper nanopaste as alternative die-attach*, IEEE Transactions on Components, Packaging and Manufacturing Technology **4**, 8 (2014).

- [93] K.S. Tan and K.Y. Cheong, *Mechanical properties of sintered Ag–Cu die-attach nanopaste for application on SiC device*, Materials & Design **64**, 166 (2014).

- [94] K.S. Tan, Y.H. Wong, and K.Y. Cheong, *Thermal characteristic of sintered Ag–Cu nanopaste for high-temperature die-attach application*, International Journal of Thermal Sciences **87**, 169 (2015).

- [95] V.R. Manikam, K.A. Razak, and K.Y. Cheong, Reliability of sintered Ag80–Al20 die attach nanopaste for high temperature applications on SiC power devices,

- Microelectronics Reliability 53, 473 (2013).

- [96] V.R. Manikam, K.A. Razak, and K.Y. Cheong, *A novel silver–aluminium high-temperature die attach nanopaste system: the effects of organic additives content on post-sintered attributes*, Journal of Materials Science: Materials in Electronics **24**, 2678 (2013).

- [97] V.R. Manikam, K.A. Razak, and K.Y. Cheong, Sintering of silver–aluminum nanopaste with varying aluminum weight percent for use as a high-temperature die-attach material, IEEE Transactions on Components, Packaging and Manufacturing Technology 2, 1940 (2012).

- [98] V.R. Manikam, K.A. Razak, and K.Y. Cheong, *Physical and electrical attributes of sintered Ag80–Al20 high temperature die attach material with different organic additives content*, Journal of Materials Science: Materials in Electronics **24**, 720 (2013).

- [99] P. Panaccione, T. Wang, X. Chen, S. Luo, and G.Q. Lu, *Improved heat dissipation* and optical performance of high-power LED packaging with sintered nanosilver die-attach material, Journal of Microelectronics and Electronic Packaging 7, 164 (2010).

- [100] A.A. Bajwa, E. Moller, and J. Wilde, Die-attachment technologies for high-temperature applications of Si and SiC-based power devices, in IEEE 65th Electronic Components and Technology Conference (ECTC 2015), 2015, pp. 2168-2174.

- [101] G.Q. Lu, J.N. Calata, Z. Zhang, and J.G. Bai, *A lead-free, low-temperature sintering die-attach technique for high-performance and high-temperature packaging,* in Sixth IEEE CPMT Conference on High Density Microsystem Design and Packaging and Component Failure Analysis (HDP'04), 2004, pp. 42-46.

- [102] G. Greca, P. Salerno, J. Durham, F. Henaff, J.C. Harel, J. Hamelink, and W. He, Double side sintered IGBT 650V/200A in a TO-247 package for extreme performance and reliability, in IEEE 18th Electronics Packaging Technology Conference (EPTC 2016), 2016, pp. 589-592.

- [103] R. Khazaka, B. Thollin, L. Mendizabal, D. Henry, and R. Hanna, Characterization of nanosilver dry films for high-temperature applications, IEEE Transactions on Device and Materials Reliability 15, 149 (2015).

- [104] F. Henaff, G. Greca, P. Salerno, O. Mathieu, M. Reger, O. Khaselev, M. Boureghda, J. Durham, A. Lifton, and J. C. Harel, "Reliability of double side silver sintered devices

with various substrate metallization," in *International Exhibition and Conference* for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management (PCIM Europe 2016), 2016, pp. 1027-1034.

- [105] H. Frederikse, R. Fields, and A. Feldman, *Thermal and electrical properties of copper-tin and nickel-tin intermetallics*, Journal of Applied Physics **72**, 2879 (1992).

- [106] Y. Mei, G. Chen, L. Guo-Quan, and X. Chen, Effect of joint sizes of low-temperature sintered nano-silver on thermal residual curvature of sandwiched assembly, International Journal of Adhesion and Adhesives 35, 88 (2012).

- [107] Y. Liu, J. Zhao, C.A. Yuan, G.Q. Zhang, and F. Sun, Chip-on-flexible packaging for high-power flip-chip light-emitting diode by AuSn and SAC soldering, IEEE Transactions on Components, Packaging and Manufacturing Technology 4, 1754 (2014).

- [108] C.C. Lee, P.J. Wang, and J.S. Kim, *Are intermetallics in solder joints really brittle?*, in 57th Electronic Components and Technology Conference (ECTC 2007), 2007, pp. 648-652.

- [109] Y. Zhong, R. An, C. Wang, Z. Zheng, Z. Liu, C. Liu, C. Li, T.K. Kim, and S. Jin, Low temperature sintering  $Cu_6Sn_5$  nanoparticles for superplastic and super-uniform high temperature circuit interconnections, Small 11, 4097 (2015).

2

# BONDING MECHANISMS ANALYSIS OF Nanosilver Sandwich Sintered Package

Though silver (Ag) nanoparticles have significant advantages on the physical and the mechanical properties, it is difficult to achieve the theoretical performances of bulk Ag by solid sintering of Ag nanoparticles. Due to the geometrical effect of the nanoparticles, the particle neck and pores suppress the properties of the sintering layer. An effective way to decrease the porosity in the sintering layer is to add external pressure during the sintering process. Besides, the decreasing porosity also has positive effects on the thermal and electrical performance of the sintering layers. Therefore, pressure assisted Ag sintering has gradually become the developing trend and been used in industry. This chapter focuses on investigating the effects of sintering parameters on the bonding quality of nanosilver sintered package. The effects of sintering pressure, temperature and time on the evolution of the bonding strength and fracture properties of nanosilver sintered sandwich package are presented. Besides, the effects of sintering parameters on the bonding mechanisms of sintered silver nanoparticles are discussed.

#### 2.1. Introduction

The developments of power electronics are moving toward high-power density, high efficiency and low-power loss [2-4]. The main function of power electronics is to control and convert electric power [5, 6]. The fast development of wide band gap semiconductors facilitates the extensive application of power electronics. They have already become the key components in fields of smart grid systems, photovoltaic inverters, uninterrupted power supply, hybrid electric vehicles and high speed tractions [7, 8]. The power electronics are expected to work at temperatures higher than 350°C [9], which propose severe requirements for the corresponding packaging materials.

The power die is normally attached to the substrate through the die attach layer. This layer plays an important role in the power module including mechanical connection, electrical conduction and thermal dissipation. The die attach layer needs to withstand the high current density while maintain high temperature reliability. Among the die attach materials, the nanosilver sintering paste/film has been developed and widely been applied for attaching power dies [1, 10]. The nanosilver sintered layer has the combined advantages of high electrical and thermal conductivity because of the silver. The sintering material is mainly composed of the silver nanoparticles, which possess the low sintering driving force due to their high surface energy [11]. The sintering process is achieved at temperatures around 200 to 300°C with or without the assistance of pressure.

Fu et al found that the pressureless nanosilver sintered IGBT module has a higher reliability than the Sn5Pb92.5Ag2.5 soldered one [12, 13]. Wang et al demonstrated that a shear strength of 25 MPa can be obtained by sintering silver nanoparticles at 200°C for 20 min, but the porosity of sintered layer was as high as 35.7% [14]. Besides, the weak spots were randomly distributed in the pressureless bonded joint after sintering, which resulted in the low bonding strength [15]. In order to bond large area chips (>100mm²) in pressureless sintering process, the ultrasonic vibration was introduced into the bonding process [16]. However, the shear strength only reached 18.9 MPa at the maximum ultrasonic power. Due to the high porosity generated in the sintered Ag layer during pressureless sintering process, the reliability of sintered module is decreased. In addition, the pressureless sintering process also takes a long period (>30 min) to get the enough bonding strength [13, 17]. Therefore, in order to ensure the high reliability of sintered layer and improve the efficiency, the application of pressure is of great importance, especially for die sizes larger than 25 mm<sup>2</sup> [18]. However, limited researches focused on the systematical analysis of the sintering parameters on bonding quality of nanosilver sintered joint.

This chapter investigates the sintering parameters on the bonding quality of

2.2. METHODOLOGY 29

nanosilver sintered joint. The effects of sintering pressure on the shear strength of sintered power package and the corresponding fracture morphologies are first analyzed. Then the effects of sintering temperature and time on the sintering properties are also studied, respectively. Finally, the effects of various sintering parameters on the densification of nanoparticles during sintering process are analyzed from the theoretical point of view.

#### 2.2. METHODOLOGY

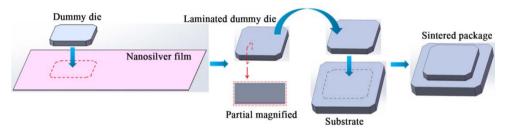

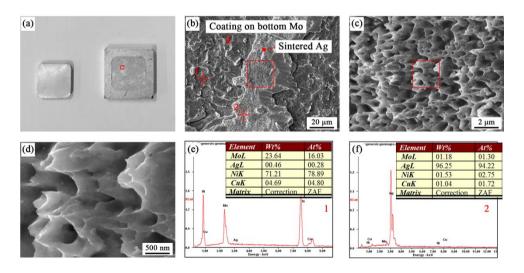

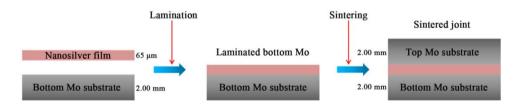

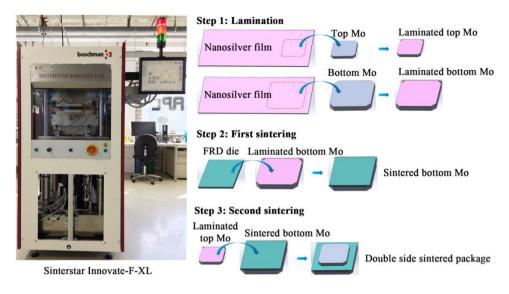

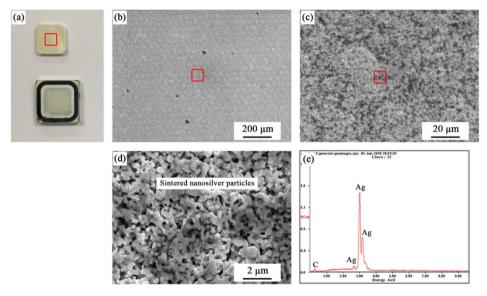

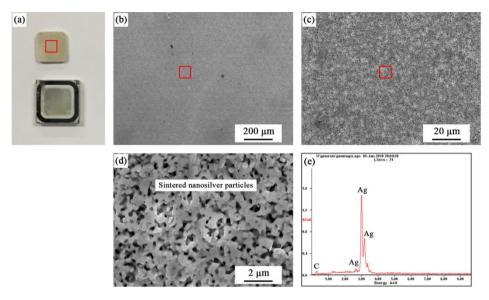

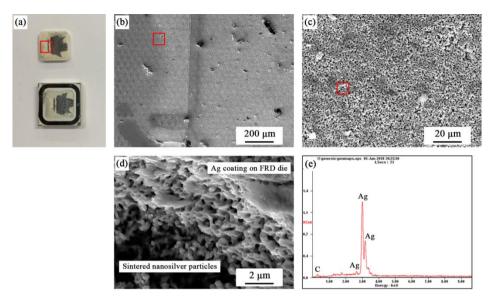

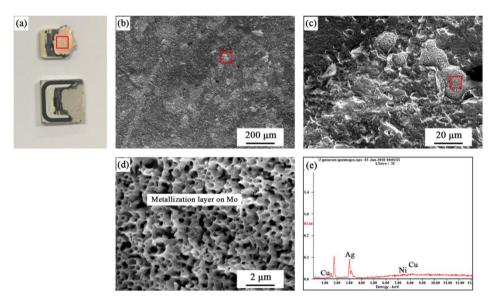

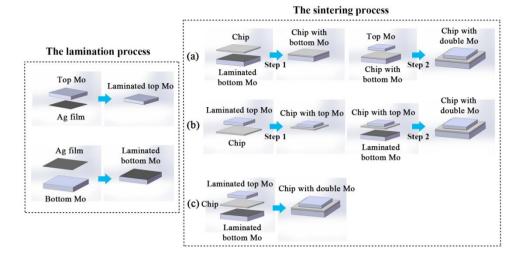

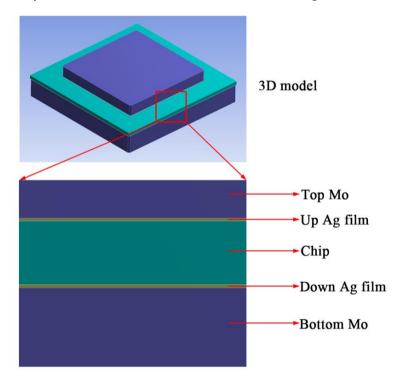

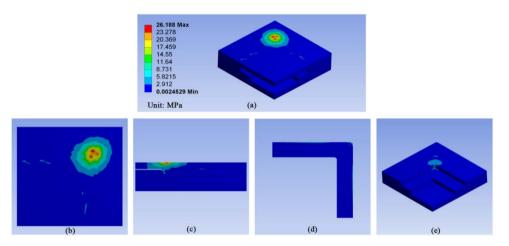

The nanosilver film used in this research has a thickness of 65  $\mu$ m. The power package with a sandwich structure, dummy die/nanosilver sintered layer/substrate, was applied in this research. The small Molybdenum (Mo) and big Mo, coated with (Mo)/Ni/Cu/Ag on the top surface, was used as dummy die and substrate, respectively. The dimension of dummy die and substrate was  $9.4\times9.4\times1.2$  mm³ and  $13.6\times13.6\times2.0$  mm³, respectively. The schematic diagram of sample fabrication process is presented in Figure 2.1.

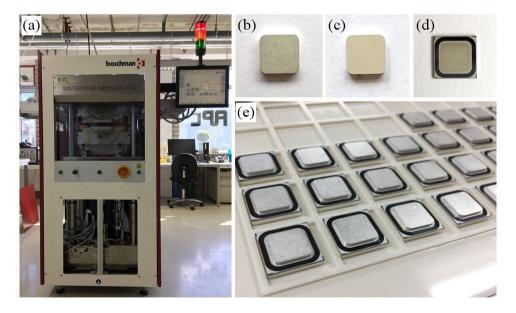

Figure 2.1: Schematic diagram of sample fabrication

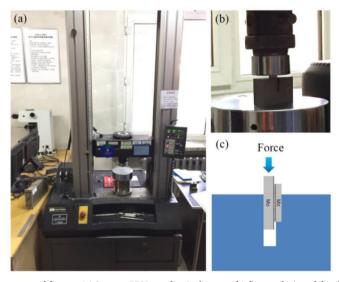

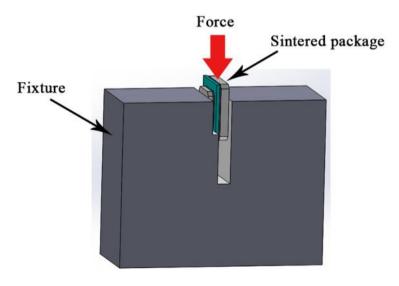

The nanosilver film was first laminated to one side of the dummy die at 130°C for 2 min. The substrate was fixed in a special designed mold and then the laminated dummy die was placed on the central of the substrate. The assembled package was then sintered in the Sinterstar Innovate-F-XL at various parameters in air. The sintering parameters were summarized in Table 2.1. When investigating one parameter, the other two are fixed as a constant. Note that the sample in the line of No. 2 is the common one, which is also applicable for the other two parameters' tests. The sintering pressure was applied on the top of the dummy die and can be precisely controlled at high temperatures through the patented dynamic insert technology. The shear strength of sintered package was examined by Instron 5569 electromechanical test machine with a specially-designed fixture as shown in the Figure 2.2(a) and 2.2(b). The constant shear speed of 0.3 mm/min was used. The schematic diagram of the shear test is presented in Figure 2.2(c). The shear test was based on the standard of MIL-STD-883E, Method 2019.5. The fracture morphology of sheared package was observed by scanning electron microscopy (SEM) and the chemical composition was analyzed by energy dispersive spectrometer (EDS).

| No. | Pressure/ MPa | Temperature/ °C | Time/ min |

|-----|---------------|-----------------|-----------|

| 1   | 5             | 250             | 3         |

| 2   | 10            | 250             | 3         |

| 3   | 20            | 250             | 3         |

| 4   | 30            | 250             | 3         |

| 5   | 10            | 210             | 3         |

| 6   | 10            | 230             | 3         |

| 7   | 10            | 270             | 3         |

| 8   | 10            | 250             | 1         |

| 9   | 10            | 250             | 2         |

| 10  | 10            | 250             | 4         |

Table 2.1: Sintering parameters used in this research

Figure 2.2: Shear tester and fixture: (a) Instron 5569 mechanical tester; (b) fixture designed for the specimens; (c) schematic diagram of the shear test

## **2.3.** EFFECTS OF PRESSURE ON THE MECHANICAL PROPERTIES

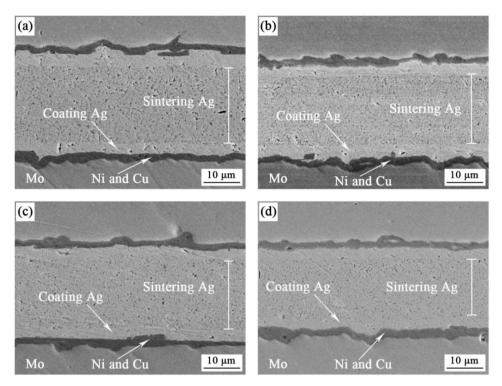

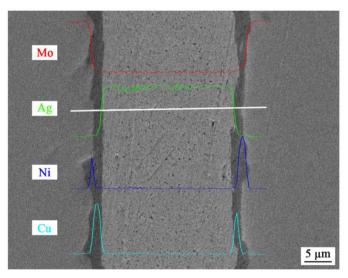

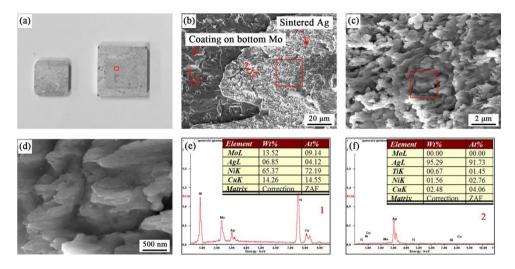

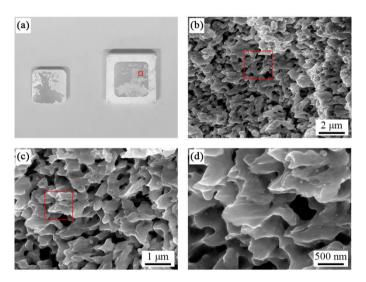

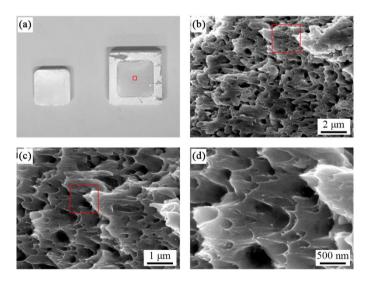

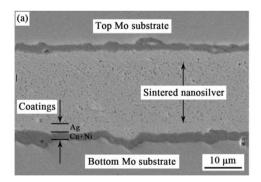

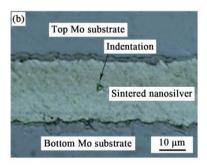

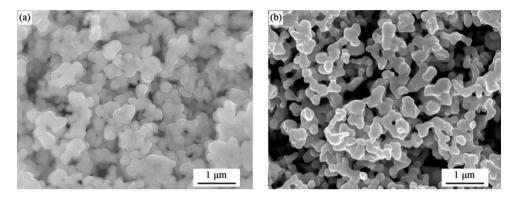

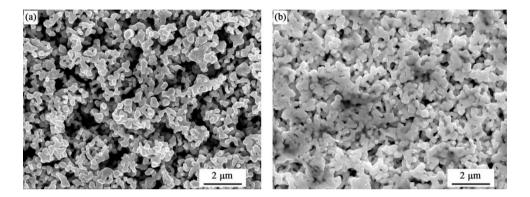

Figure 2.3 shows the cross-sectional SEM morphologies of the sintering interfaces under the sintering pressures of 5, 10, 20, and 30 MPa, respectively. The result of the EDS line scan as shown in Figure 2.4 indicates that the top and the bottom layers are Mo. The dark layer next to the Mo layer, which consists of two elements, Ni and Cu, is formed of Ni-coated layer on the Mo plate and Cu-coated layer on Ni coated layer. Here the total

thickness of the Ni and the Cu layers is about 2  $\mu m$ . The layer next to the Cu layer is the Ag-coated layer exposed to air of the Mo substrate. The thickness of this Ag-coated layer is about 5  $\mu m$ .

Figure 2.3: Cross-sectional SEM micrographs of the sintering interfaces under the sintering pressures of: (a) 5 MPa; (b) 10 MPa; (c) 20 MPa; (d) 30 MPa

Figure 2.4: EDS line scan result of the sintering interface

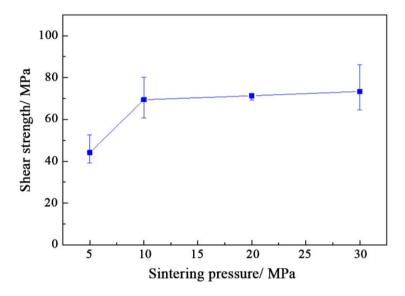

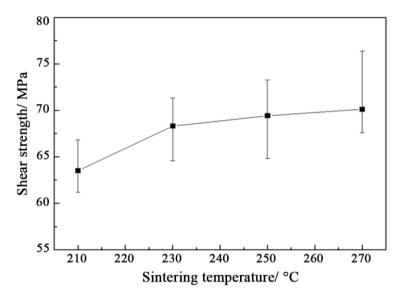

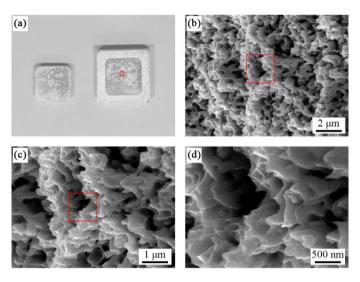

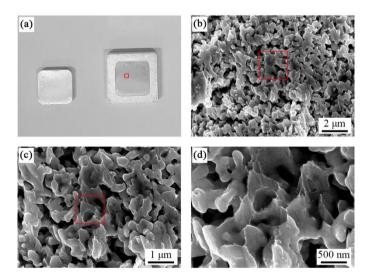

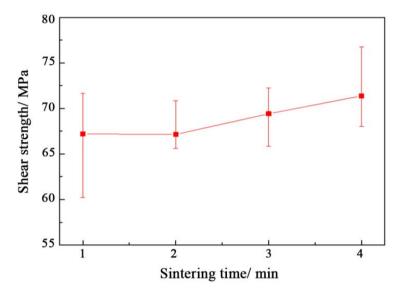

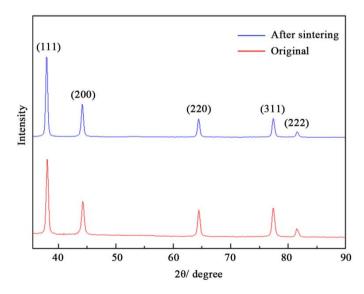

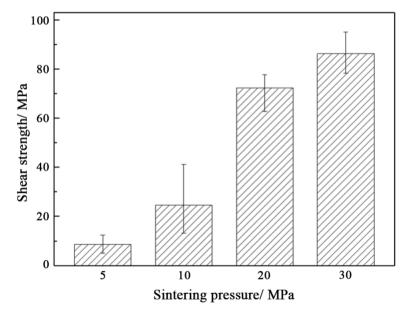

The effect of sintering pressure on the mechanical properties of sintered Ag layer is shown in Figure 2.5. As the sintering pressure increases from 5 MPa to 10 MPa, the average shear strength of sintered Ag layer increases from 44.2 MPa to 69.4 MPa. This gives the maximum increase rate of 36.34%. The shear strength of 30 MPa sintered Ag layer is 73.4 MPa, which only increases slightly when comparing with the 10 MPa sintered one. These results indicate that the sintering pressure of 10 MPa is adequate to ensure the high bonding strength of sintered Ag layer and pressures higher than 10 MPa are not highly recommended.

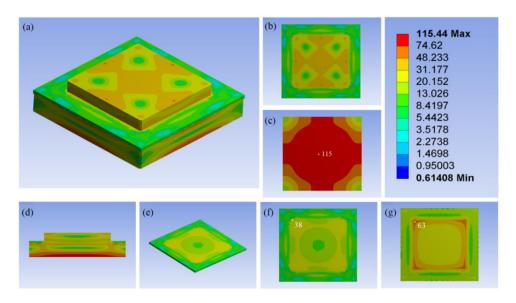

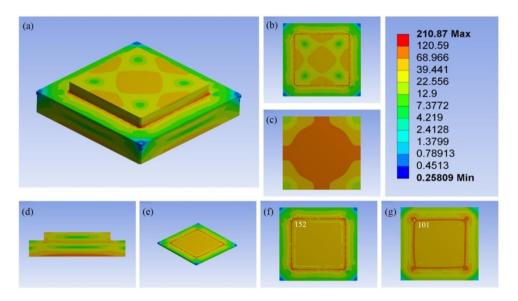

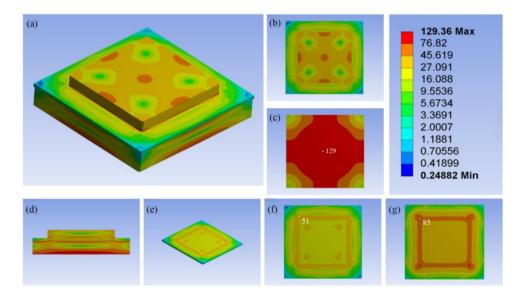

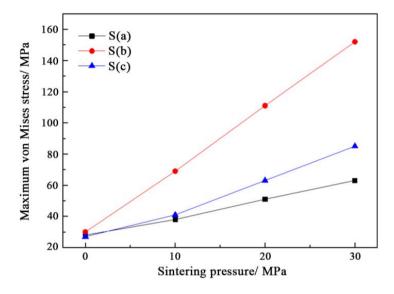

Figure 2.5: Relationship between sintering pressure and shear strength of sintered Ag layer (250°C, 3 min)