# Compiler for Color Center-based Quantum Computers

by

## Matti Dreef

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Tuesday, April 25th, 2023 at 9:30 AM.

Student number: 4456122

Project duration: January, 2022 – April, 2023

Thesis committee: Prof. dr. ir. J.S.S.M. Wong, TU Delft, supervisor

Dr. D. Coronas Elkouss, TU Delft TU Delft TU Delft

This thesis is confidential and cannot be made public until April 30, 2028.

An electronic version of this thesis is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

## **Abstract**

Quantum computing is a promising means of satisfying the ever-increasing need for more and faster computations. While some specific applications can already benefit from quantum computing today, a large-scale general-purpose quantum computer is yet to be developed. Many different technologies are being explored to reach this goal, *color centers in diamond* being a promising candidate. This thesis focuses on a specific kind of color center: the nitrogen-vacancy center (NV center).

Building on top of existing work, a quantum instruction set architecture (QISA) for a quantum computer based on NV centers is designed. A compiler targeting this QISA is designed and implemented using the OpenQL framework. In this process alternative approaches are also explored and contributions useful outside the context of NV centers are made. The final compiler is able to take a quantum circuit operating on logical qubits and transform it into a sequence of QISA instructions operating on physical qubits. This functionality integrates seamlessly with the existing passes in OpenQL, allowing for further extension and the possibility to make use of future developments.

Additional functionality includes optimization, scheduling, and hardware-oriented features such as quantization of operands. Each step is easily configurable using a multitude of scripts and data files, and additional steps can be added in the future if needed.

The functionality of the developed compiler is demonstrated by compiling several circuits, some of which are validated by passing their output through a simulator. The compiler configuration as used in these tests is able to transform logical circuit into simple physical circuits, but the compiler provides all the functionality to use more complicated logical qubits which incorporate quantum error correction.

## **Preface**

After my first thesis topic got stuck in finding what exactly I could contribute, Stephan offered me the possibility of working on a quantum computing project instead. While at the start of this project I had practically no knowledge about quantum computing, it turned out that the part I have been working on fits neatly between quantum algorithms on one side and quantum physics on the other, with basic quantum information theory being enough for me during most of the project. A continuing challenge has been the fact that this thesis focuses mostly on software, while my main interest is in hardware design. Nonetheless I think this project was a great opportunity for a slight sidetrack, and the field of quantum computing in general has definitely sparked my interest.

Completing this thesis would not have been possible without the support of the people around me. I would like to thank Fujitsu Limited and Delft University of Technology for setting up the project this thesis contributes to. I would like to thank Stephan Wong for all the opportunities he has opened up for me and his guidance throughout this project, the group of Sebastian Feld for their help with quantum algorithms and software, and David Elkouss for his advice early on in my thesis that eventually led to the final results. I would also like to thank Folkert de Ronde for his input in many aspects of this project and helping me out with the 'real' quantum physics when needed. My thanks also go out to all the fellow students and employees on the 10th and 11th floor for the fun times outside of studying, from group dinners to just sharing a coffee break.

Finally, I would like to thank my friends and family for their continuous support. Richard, you played a great part in inspiring me to pursue the direction of electrical and computer engineering, and I can always count on you for technical and personal support or just some fun and banter. Thank you for being an amazing friend for all these years. Jori, I've come to realize that by being the younger sibling I always had someone who had to figure out the next step in life before me. Thank you for making all those decisions a little less overwhelming. Mom and dad, your never-ending support and encouragement means the world to me. Thank you.

Matti Dreef Delft, April 2023

## **Notation**

The Glossary lists important terms and their definitions in the scope of this thesis. This is intended both as a reference while reading and to avoid any confusion when certain terms have a different meaning in other fields or inconsistent meaning within the field of quantum computing. When such a term is first introduced it is accompanied by a definition such as the following.

#### **Definition: Example**

Example of a definition. This text is also found in the glossary.

Furthermore, this thesis uses colored text to distinguish cross-references, citations, and URLs. In the electronic version these references can be followed by clicking the text.

## Contents

| Ab  | strac          | et en                                                                                                                                                                                    | i                       |

|-----|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Pre | eface          |                                                                                                                                                                                                                              | ii                      |

| No  | tatio          | n i                                                                                                                                                                                                                          | ii                      |

| 1   | 1.1            | Fujitsu Project                                                                                                                                                                                                              | <b>1</b><br>1<br>1<br>1 |

| 2   |                |                                                                                                                                                                                                                              | 3                       |

|     | 2.1            | 2.1.1 Qubits                                                                                                                                                                                                                 | 3<br>5<br>8<br>9        |

|     | 2.2            |                                                                                                                                                                                                                              | 1                       |

|     |                | 2.2.2 Control       1         2.2.3 Connectivity       1                                                                                                                                                                     | 1<br>2<br>2<br>3        |

|     | 2.3<br>2.4     | Digital control                                                                                                                                                                                                              | ა<br>3<br>4             |

|     |                | 2.4.2 Decomposition       1         2.4.3 Optimization       1         2.4.4 Scheduling       1                                                                                                                              | 4<br>5<br>5             |

|     |                | 2.4.6       Code Generation       1         2.4.7       NV Center-specific Details for Compiler Passes       1         2.4.8       Complete Compiler Toolchains       1                                                      | 5<br>6<br>6<br>7<br>7   |

|     | 2.5            | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                        | 8                       |

| 3   | <b>Des</b> 3.1 | Hardware Architecture                                                                                                                                                                                                        | 9<br>9<br>9             |

|     | 3.2            | NV Mapping Exploration       2         3.2.1 NVP       2         3.2.2 NVD       2         3.2.3 NVC       2                                                                                                                 | 3 5 6                   |

|     | 3.3            | 3.2.4 Comparison       2         3.2.5 Conclusion       2         NVP Mapping Design       2         3.3.1 Topology Transformation       2         3.3.2 Logical P&R       3         3.3.3 Instruction Decomposition       3 | 9992                    |

|     | 3.4            | 3.3.4 Application to NV centers                                                                                                                                                                                              |                         |

Contents

|               |                                                                                                                         |                                                                                                                                                                                                                                                                                                                             | _ | _                                                         |

|---------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------|

| 4             |                                                                                                                         | nplementation                                                                                                                                                                                                                                                                                                               | 3 |                                                           |

|               | 4.1                                                                                                                     |                                                                                                                                                                                                                                                                                                                             |   |                                                           |

|               |                                                                                                                         | 4.1.1 Internal Qubit Organization                                                                                                                                                                                                                                                                                           |   |                                                           |

|               |                                                                                                                         | 4.1.2 Place & Route                                                                                                                                                                                                                                                                                                         |   |                                                           |

|               |                                                                                                                         | 4.1.3 Decomposition                                                                                                                                                                                                                                                                                                         |   |                                                           |

|               | 4.2                                                                                                                     | 2 Common Compiler Passes                                                                                                                                                                                                                                                                                                    |   |                                                           |

|               |                                                                                                                         | 4.2.1 Physical Decomposition                                                                                                                                                                                                                                                                                                |   | 6                                                         |

|               |                                                                                                                         | 4.2.2 Optimization                                                                                                                                                                                                                                                                                                          |   | 7                                                         |

|               |                                                                                                                         | 4.2.3 Scheduling                                                                                                                                                                                                                                                                                                            |   | 7                                                         |

|               | 4.3                                                                                                                     | 3 Classical Backend                                                                                                                                                                                                                                                                                                         |   | 7                                                         |

|               |                                                                                                                         | 4.3.1 Design and Functionality                                                                                                                                                                                                                                                                                              |   | 8                                                         |

|               |                                                                                                                         | 4.3.2 ISA Decomposition                                                                                                                                                                                                                                                                                                     |   |                                                           |

|               |                                                                                                                         | 4.3.3 Operand Evaluation & Quantization                                                                                                                                                                                                                                                                                     |   |                                                           |

|               |                                                                                                                         | 4.3.4 Periodic Instructions                                                                                                                                                                                                                                                                                                 |   | -                                                         |

|               |                                                                                                                         | 4.3.5 Output                                                                                                                                                                                                                                                                                                                |   | -                                                         |

|               |                                                                                                                         | 4.3.6 Future Extensions                                                                                                                                                                                                                                                                                                     |   |                                                           |

|               | 4.4                                                                                                                     |                                                                                                                                                                                                                                                                                                                             |   |                                                           |

|               | 4.4                                                                                                                     | 4 Conclusion                                                                                                                                                                                                                                                                                                                |   | 1                                                         |

| 5             | Res                                                                                                                     | esults                                                                                                                                                                                                                                                                                                                      | 4 | 3                                                         |

|               | 5.1                                                                                                                     | 1 Compilation Results                                                                                                                                                                                                                                                                                                       |   | .3                                                        |

|               |                                                                                                                         | 5.1.1 Single-Qubit Circuit                                                                                                                                                                                                                                                                                                  |   | 3                                                         |

|               |                                                                                                                         | 5.1.2 Two-Qubit Circuit                                                                                                                                                                                                                                                                                                     |   | _                                                         |

|               |                                                                                                                         | 5.1.3 Grover's Algorithm                                                                                                                                                                                                                                                                                                    |   |                                                           |

|               | 5.2                                                                                                                     |                                                                                                                                                                                                                                                                                                                             |   |                                                           |

|               | 5.3                                                                                                                     | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                       |   | .7                                                        |

|               | 0.0                                                                                                                     | 0 001101031011                                                                                                                                                                                                                                                                                                              |   | '                                                         |

|               |                                                                                                                         |                                                                                                                                                                                                                                                                                                                             |   |                                                           |

| 6             | Con                                                                                                                     | onclusion                                                                                                                                                                                                                                                                                                                   | 4 | _                                                         |

| 6             | <b>Con</b> 6.1                                                                                                          |                                                                                                                                                                                                                                                                                                                             |   | _                                                         |

| 6             |                                                                                                                         | 1 Summary                                                                                                                                                                                                                                                                                                                   |   | 8                                                         |

| 6             | 6.1                                                                                                                     | 1 Summary                                                                                                                                                                                                                                                                                                                   |   | 8.8                                                       |

|               | 6.1<br>6.2<br>6.3                                                                                                       | 1 Summary                                                                                                                                                                                                                                                                                                                   |   | .8<br>.8<br>.9                                            |

|               | 6.1<br>6.2<br>6.3                                                                                                       | 1 Summary                                                                                                                                                                                                                                                                                                                   |   | .8<br>.8<br>.9                                            |

| Re            | 6.1<br>6.2<br>6.3                                                                                                       | 1 Summary                                                                                                                                                                                                                                                                                                                   |   | .8<br>.9<br>.9                                            |

| Re            | 6.1<br>6.2<br>6.3<br>efere                                                                                              | 1 Summary                                                                                                                                                                                                                                                                                                                   |   | .8<br>.9<br>.9<br>.5                                      |

| Re            | 6.1<br>6.2<br>6.3<br>ferences                                                                                           | 1 Summary                                                                                                                                                                                                                                                                                                                   |   | 8 8 9 1 5 6 6                                             |

| Re            | 6.1<br>6.2<br>6.3<br>ferences                                                                                           | 1 Summary                                                                                                                                                                                                                                                                                                                   |   | 8 8 9 1 5 6 6                                             |

| Re            | 6.1<br>6.2<br>6.3<br>ferences<br>ossa<br>Figu<br>A.1                                                                    | 1 Summary                                                                                                                                                                                                                                                                                                                   |   | 8 8 9 1 5 6 6 6                                           |

| Re<br>GI<br>A | 6.1<br>6.2<br>6.3<br>ferences<br>ossa<br>Figural A.1<br>A.2                                                             | 1 Summary 2 Contributions 3 Future Work rences sary igures 1 NVx Topology 2 NVx Mapping Example                                                                                                                                                                                                                             |   | .8 .8 .9 .1 .5 .6 .6 .7                                   |

| Re<br>GI<br>A | 6.1<br>6.2<br>6.3<br>ferences<br>ossa<br>Figu<br>A.1<br>A.2                                                             | 1 Summary 2 Contributions 3 Future Work  rences sary igures 1 NVx Topology 2 NVx Mapping Example 6A Reference                                                                                                                                                                                                               |   | 8 8 9 <b>1 5 6</b> 6 7 <b>8</b>                           |

| Re<br>GI<br>A | 6.1<br>6.2<br>6.3<br>ferences<br>ossa<br>Figu<br>A.1<br>A.2<br>ISA<br>B.1                                               | 1 Summary 2 Contributions 3 Future Work  rences sary igures 1 NVx Topology 2 NVx Mapping Example 3 Reference 1 Global Instruction Set                                                                                                                                                                                       |   | 889<br><b>1 5 6 6 7 8 9</b>                               |

| Re<br>GI<br>A | 6.1<br>6.2<br>6.3<br>ferences<br>ossa<br>Figu<br>A.1<br>A.2<br>ISA<br>B.1<br>B.2                                        | 1 Summary                                                                                                                                                                                                                                                                                                                   |   | 889 <b>1 5 6</b> 67 <b>8</b> 93                           |

| Re<br>GI<br>A | 6.1<br>6.2<br>6.3<br>ferei<br>ossa<br>Figu<br>A.1<br>A.2<br>ISA<br>B.1<br>B.2<br>B.3                                    | 1 Summary 2 Contributions 3 Future Work rences sary igures 1 NVx Topology 2 NVx Mapping Example 3 Reference 1 Global Instruction Set 2 Local Microcode 3 Local Microinstruction Set                                                                                                                                         |   | 889 <b>1 5 6</b> 67 <b>8</b> 935                          |

| Re<br>GI<br>A | 6.1<br>6.2<br>6.3<br>ferei<br>ossa<br>Figu<br>A.1<br>A.2<br>ISA<br>B.1<br>B.2<br>B.3                                    | 1 Summary                                                                                                                                                                                                                                                                                                                   |   | 889 <b>1 5 6</b> 67 <b>8</b> 93                           |

| Re<br>GI<br>A | 6.1<br>6.2<br>6.3<br>ferel<br>ossa<br>Figu<br>A.1<br>A.2<br>ISA<br>B.1<br>B.2<br>B.3<br>B.4                             | 1 Summary 2 Contributions 3 Future Work  rences sary igures 1 NVx Topology 2 NVx Mapping Example 3 GReference 1 Global Instruction Set 2 Local Microcode 3 Local Microinstruction Set 4 Local Registers                                                                                                                     |   | 889 <b>1 5 6</b> 67 <b>8</b> 9357                         |

| Re<br>GI<br>A | 6.1<br>6.2<br>6.3<br>ferer<br>ossa<br>Figu<br>A.1<br>A.2<br>ISA<br>B.1<br>B.2<br>B.3<br>B.4                             | 1 Summary 2 Contributions 3 Future Work  rences sary igures 1 NVx Topology 2 NVx Mapping Example 3 A Reference 1 Global Instruction Set 2 Local Microcode 3 Local Microinstruction Set 4 Local Registers ecomposition Reference                                                                                             |   | 889 <b>1 5 6</b> 67 <b>8</b> 9357 <b>0</b>                |

| Re<br>GI<br>A | 6.1<br>6.2<br>6.3<br>ferer<br>ossa<br>Figu<br>A.1<br>A.2<br>ISA<br>B.1<br>B.2<br>B.3<br>B.4<br>Dec<br>C.1               | 1 Summary 2 Contributions 3 Future Work rences sary igures 1 NVx Topology 2 NVx Mapping Example 3 A Reference 1 Global Instruction Set 2 Local Microcode 3 Local Microinstruction Set 4 Local Registers ecomposition Reference 1 NVP1 Decomposition Rules                                                                   |   | 889 <b>1 5 6</b> 67 <b>8</b> 9357 <b>0</b> 0              |

| Re<br>GI<br>A | 6.1<br>6.2<br>6.3<br>ferel<br>ossa<br>Figu<br>A.1<br>A.2<br>ISA<br>B.1<br>B.2<br>B.3<br>B.4<br>Dec<br>C.1<br>C.2        | 1 Summary 2 Contributions 3 Future Work rences sary igures 1 NVx Topology 2 NVx Mapping Example 3 A Reference 1 Global Instruction Set 2 Local Microcode 3 Local Microinstruction Set 4 Local Registers ecomposition Reference 1 NVP1 Decomposition Rules 2 Physical Decomposition Rules                                    |   | 889 <b>1 5 6</b> 67 <b>8</b> 9357 <b>0</b> 04             |

| Re<br>GI<br>A | 6.1<br>6.2<br>6.3<br>ferel<br>ossa<br>Figu<br>A.1<br>A.2<br>ISA<br>B.1<br>B.2<br>B.3<br>B.4<br>Dec<br>C.1<br>C.2        | 1 Summary 2 Contributions 3 Future Work rences sary igures 1 NVx Topology 2 NVx Mapping Example 3 A Reference 1 Global Instruction Set 2 Local Microcode 3 Local Microinstruction Set 4 Local Registers ecomposition Reference 1 NVP1 Decomposition Rules                                                                   |   | 889 <b>1 5 6</b> 67 <b>8</b> 9357 <b>0</b> 04             |

| Re GI A B     | 6.1<br>6.2<br>6.3<br><b>Figu</b><br>A.1<br>A.2<br><b>ISA</b><br>B.1<br>B.2<br>B.3<br>B.4<br><b>Dec</b><br>C.1<br>C.2    | 1 Summary 2 Contributions 3 Future Work rences sary igures 1 NVx Topology 2 NVx Mapping Example 3 A Reference 1 Global Instruction Set 2 Local Microcode 3 Local Microinstruction Set 4 Local Registers ecomposition Reference 1 NVP1 Decomposition Rules 2 Physical Decomposition Rules                                    |   | 889 <b>1 5 6</b> 67 <b>8</b> 9357 <b>0</b> 045            |

| Re GI A B     | 6.1<br>6.2<br>6.3<br>ference ossa<br>Figure A.1<br>A.2<br>ISA<br>B.1<br>B.2<br>B.3<br>B.4<br>Dec<br>C.1<br>C.2<br>C.3   | 1 Summary 2 Contributions 3 Future Work  rences sary igures 1 NVx Topology 2 NVx Mapping Example 3 A Reference 1 Global Instruction Set 2 Local Microcode 3 Local Microinstruction Set 4 Local Registers  ecomposition Reference 1 NVP1 Decomposition Rules 2 Physical Decomposition Rules 3 ISA Decomposition Rules        |   | 889 <b>1 5 6</b> 67 <b>8</b> 9357 <b>0</b> 045 <b>0</b>   |

| Re GI A B     | 6.1<br>6.2<br>6.3<br>ferel<br>ossa<br>Figu<br>A.1<br>A.2<br>ISA<br>B.1<br>B.2<br>B.3<br>B.4<br>Dec<br>C.1<br>C.2<br>C.3 | 1 Summary 2 Contributions 3 Future Work rences sary igures 1 NVx Topology 2 NVx Mapping Example 3 GA Reference 1 Global Instruction Set 2 Local Microcode 3 Local Microinstruction Set 4 Local Registers ecomposition Reference 1 NVP1 Decomposition Rules 2 Physical Decomposition Rules 3 ISA Decomposition Rules ircuits |   | 889 <b>1 5 6</b> 67 <b>8</b> 9357 <b>0</b> 045 <b>0</b> 0 |

Introduction

Quantum computing is a promising means of satisfying the ever-increasing need for more and faster computations. By utilizing superposition and entanglement of quantum mechanical systems, certain computations can be carried out exponentially faster than classical computers.

While some specific applications can already benefit from quantum computing today [1], a large-scale general-purpose quantum computer is yet to be developed. Many different technologies are being explored to reach this goal, *color centers in diamond* being a promising candidate. This thesis focuses on a specific kind of color center: the nitrogen-vacancy center (NV center).

## 1.1. Fujitsu Project

To further explore the possibilities of NV center-based quantum computing, Fujitsu Limited and Delft University of Technology have started a collaboration with the Fujitsu Project. The goal of this project is to develop a scalable quantum computer architecture using color centers. More specifically, the focus at this point in time is on NV centers, while in the future also tin-vacancy centers are to be utilized.

#### 1.2. Problem Statement

As with classical computers, at the lowest level quantum computers work with basic operations that have practical use only when combined into more complex algorithms. Additionally, the qubits a quantum computer operates on are inherently analog. The inevitable noise limits the usability of a single qubit, requiring multiple to be combined for practical quantum algorithms.

This motivates the use of a compiler that can translate a high-level quantum algorithm to the corresponding low-level operations. The goal of this thesis is to design and implement a compiler capable of performing this translation for a quantum computer utilizing NV center qubits. Additionally, this requires defining a quantum instruction set architecture (QISA) serving as an interface between the quantum software and hardware. These requirements are summarized in the main research question of this thesis:

Can we design and implement a functional compiler that targets a quantum instruction set architecture for quantum computers based on NV centers?

## 1.3. Methodology

In order to answer the research question the following subtasks have been identified:

- Identify how NV centers need to be controlled.

This encompasses defining the low-level operations that can be applied directly to NV centers.

- Design and extend a QISA for a quantum computer based on NV centers.

This requires defining high-level instructions that can be implemented using the available low-level operations.

- Design and implement a compiler targeting this QISA.

This consists of identifying NV center-specific features, formulating and designing the required

1.4. Thesis Overview 2

compiler functionality, and implementing it using a new or existing compiler framework.

#### 4. Verify the functionality of the compiler.

This involves comparing the compiler output to the expected output for simple cases, as well as evaluating the scalability of the implementation with more complex situations.

The focus in this thesis is on making the compiler *functional*, and not necessarily directly usable for large-scale applications. The compiler should however be able to adapt and scale to accommodate these applications in the future. A similar approach will be taken for the QISA; it should be designed for the *current* outlook of the quantum hardware while also taking the possibility of future extensions into consideration.

#### 1.4. Thesis Overview

The remainder of this thesis is structured as follows; Chapter 2 introduces the quantum theory and NV center physics relevant to the scope of this thesis, as well as outlining the state-of-the-art on quantum compilers and control systems. In Chapter 3 the design of a new control architecture and compiler is discussed. The implementation of the compiler is described in Chapter 4, after which Chapter 5 shows how the compiler can be used in practice. Finally, Chapter 6 concludes this thesis and suggests potential improvements and future work.

Background

This chapter provides background information and introduces existing work relevant to this thesis. A theoretical background of quantum computing is given in Section 2.1. Section 2.2 introduces NV centers, the qubit technology that is the focus of this thesis. Section 2.3 describes existing work related to the classical digital control system surrounding a quantum computer. A comparison of existing compiler techniques, full compiler toolchains, and how these can be applied to NV centers is given in Section 2.4.

## 2.1. Quantum Computing Theory

The following sections first introduce individual qubits and their mathematical notation, followed by multiple qubits and quantum gates. Subsequently quantum circuits are discussed, and finally how qubits are used in practice with quantum error correction. Focus is given to the aspects relevant to this thesis. Many resources are available for a more complete background of quantum computing, as for example provided by QuTech Academy [2].

#### 2.1.1. Qubits

Where a classical bit can represent either 0 or 1, a quantum bit (qubit) can represent not just these states but also a *superposition* of both. This can be seen as the probabilities that the qubit is in one specific state, such as 30% 0 and 70% 1. The possibility of being in a superposition is one of the key features that gives quantum computing an advantage over classical computing.

The state of a single qubit can be represented by a column vector  $\begin{bmatrix} \alpha & \beta \end{bmatrix}^T$  with  $\alpha$  and  $\beta$  complex numbers. The 'probabilities' of the qubit being in the 0 or 1 state are  $P_0 = ||\alpha||^2$  and  $P_1 = ||\beta||^2$ . These probabilities must add up to 100% which translates to the vector having to be being normalized, i.e., it must have length 1.

#### **Ket Notation & Basis Vectors**

As will become clear later, when multiple qubits are introduced the vector notation becomes unwieldy very quickly. As alternative the *ket* notation is commonly used, which denotes a qubit state as  $|\psi\rangle$  where  $\psi$  is a distinguishing identifier. Kets are actually only half of what is known as bra-ket notation, but only kets are of interest for the purpose of this thesis.

While the ket notation theoretically allows for any description to be used as identifier, a number of standard qubit states known as the basis vectors can be defined which are shown below. Each pair forms an orthogonal basis of the qubit state space. The pairs are each named after a Cartesian axis, the reason for which will become clear in the next section. Note how the identifiers for the basis vectors are based on the value of their second component, while the first component is kept as simple as possible.

Arbitrary qubit states can now be written as linear combinations of these basis vectors, for example the qubit state shown previously can be written as

$$|\psi\rangle = \begin{bmatrix} \alpha \\ \beta \end{bmatrix} = \alpha \begin{bmatrix} 1 \\ 0 \end{bmatrix} + \beta \begin{bmatrix} 0 \\ 1 \end{bmatrix} = \alpha |0\rangle + \beta |1\rangle.$$

It is also possible to use other basis vectors here, or use combinations of arbitrary qubit states. This suggests these other vectors can also be used as 'default' basis. Indeed, the qubit state  $\begin{bmatrix} \alpha & \beta \end{bmatrix}^T$  is only a representation in the Z-basis. The same state can be written as a column vector with coefficients corresponding to the X- or Y-basis as well, although the Z-basis is the most common.

#### The Bloch Sphere

An alternative but very useful representation of a qubit state is the *Bloch vector*. Using the polar form of the complex numbers  $\alpha$  and  $\beta$ , the representation used in the previous section can be written as

$$|\psi\rangle = \alpha |0\rangle + \beta |1\rangle = e^{i\delta_0} r_0 |0\rangle + e^{i\delta_1} r_1 |1\rangle.$$

As mentioned previously the length of the vector must be 1, which is the same as requiring the point  $(r_0,r_1)$  to lie on a unit circle. This constraint means the values of  $r_0$  and  $r_1$  can be represented using a single angle  $\theta$  as  $r_0=\cos(\theta/2)$  and  $r_1=\sin(\theta/2)$ . The reason for dividing  $\theta$  by 2 will become clear later. This gives

$$|\psi\rangle = e^{i\delta_0}\cos(\theta/2)|0\rangle + e^{i\delta_1}\sin(\theta/2)|1\rangle$$

.

Taking out the common factor in the complex angles allows them to be written as

$$e^{i\delta_0} + e^{i\delta_1} = e^{i\delta_0} (1 + e^{i(\delta_1 - \delta_0)}).$$

Applying this to the qubit state with  $\phi = \delta_1 - \delta_0$  gives

$$|\psi\rangle = e^{i\delta} \left(\cos(\theta/2)|0\rangle + e^{i\phi}\sin(\theta/2)|1\rangle\right)$$

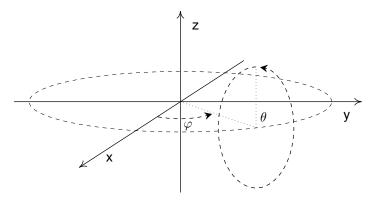

This finally leads to the Bloch vector, which represents a qubit state as a point on the surface of a radius-1 sphere with  $\theta \in [0,\pi]$  the polar angle and  $\phi \in [0,2\pi]$  the azimuthal angle as shown in Figure 2.1. The common factor  $\delta$  known as the *global phase* turns out to have no physical effect, so it is ignored in the Bloch vector representation. The range of  $\theta$  together with the division by 2 limits the sine and cosine argument to a single quadrant; other quadrants are merely sign changes which get absorbed by the exponents.

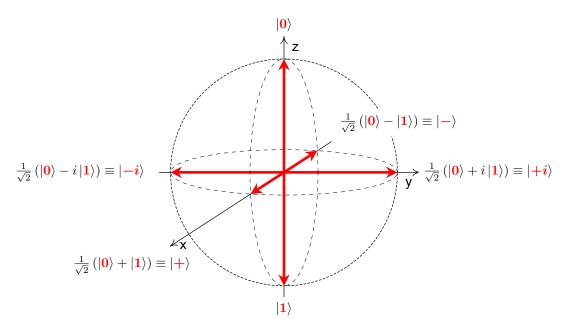

Figure 2.2 shows the basis vectors introduced previously as Bloch vectors. It can be seen that each pair of vectors aligns with an axis which corresponds to their basis. More generally, any two opposing Bloch vectors are orthogonal to each other in Cartesian form, allowing such a pair to be used as orthogonal basis.

Figure 2.1: Angles representing a point on the surface of a sphere.

Figure 2.2: Bloch sphere visualization of a single qubit.

When applying these theoretical concepts to real physical qubits, the frame of reference can be chosen arbitrarily. Since the Z-basis is most often used it is usually chosen as the most convenient physical axis to work with.

#### **Multiple Qubits**

Just by itself, introducing another qubit to a quantum system does not do much. Without any interaction each qubit can still be represented individually using a vector, ket notation, or as Bloch vector. The two qubits can also be represented in a combined state, which can be obtained by taking the *tensor product* of their individual states. This is represented in ket notation as

$$(\alpha_0 |0\rangle + \beta_0 |1\rangle) \otimes (\alpha_1 |0\rangle + \beta_1 |1\rangle) = \alpha_0 \alpha_1 |00\rangle + \alpha_0 \beta_1 |01\rangle + \beta_0 \alpha_1 |10\rangle + \beta_0 \beta_1 |11\rangle$$

and in vector form as

$$\begin{bmatrix} \alpha_0 \\ \beta_0 \end{bmatrix} \otimes \begin{bmatrix} \alpha_1 \\ \beta_1 \end{bmatrix} = \begin{bmatrix} \alpha_0 \alpha_1 \\ \alpha_0 \beta_1 \\ \beta_0 \alpha_1 \\ \beta_0 \beta_1 \end{bmatrix}.$$

The Bloch vector representation can also be extended to multiple qubits but is less useful than in the single qubit case, so it will not be discussed here,

These examples show how adding a qubit to a quantum system multiplies the number of terms required to represent that system by 2. Thus, adding a third qubit results in a total of 8 terms, a fourth in 16 terms, and so on continuing with exponential growth.

So far the combined state of the qubits is nothing more than a very tedious and redundant way of representing the individual qubit states, since they can be separated again back into their original components. This changes however when qubits start to interact with each other.

#### 2.1.2. Quantum Gates

To be able to perform computations using qubits it is necessary to manipulate them somehow using quantum gates.

The term 'gate' suggests a similarity with classical gates such as AND, OR, and NOT, but this is only partially true. First, a quantum gate can not consume or create qubits, and as such the number of outputs must be equal to the number of inputs. Secondly, a quantum gate must be *reversible*, meaning each input produces a unique output such that the input can be reconstructed.

Using the vector notation, quantum gates can be represented by a matrix that is multiplied with the quantum state to produce an output vector. Arbitrary gates can be represented by matrices, but to comply with the reversibility requirement the matrix must be unitary, meaning its conjugate transpose is equal to its inverse. That is, a matrix U is unitary if

$$UU^{\dagger} = UU^{-1} = I.$$

#### **Definition: Gate**

A reversible, unitary operation on any number of qubits. Depending on the context it can also be specifically referred to as a *quantum gate*.

#### **Single-qubit Gates**

Regardless of the physical implementation of a qubit and its control system, any quantum gate on a single qubit effectively 'rotates' the Bloch vector some angle along a specified axis. For this reason single-qubit gates are also called rotations, and in this thesis this term is used specifically for single-qubit gates only.

#### **Definition: Rotation**

A single-qubit gate, for example an 180° X or 90° Y rotation.

Using vector notation, the Pauli matrices  $\sigma_x, \sigma_y, \sigma_z$  represent rotations of 180° along the X, Y, and Z axes, respectively.

$$\sigma_x = \begin{bmatrix} 0 & 1 \\ 1 & 0 \end{bmatrix} \qquad \qquad \sigma_y = \begin{bmatrix} 0 & -i \\ i & 0 \end{bmatrix} \qquad \qquad \sigma_z = \begin{bmatrix} 1 & 0 \\ 0 & -1 \end{bmatrix}$$

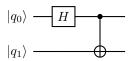

Besides the Pauli matrices a number of other single-qubit rotations are commonplace, a notable example being the *Hadamard* or H-gate. This gate performs a 180° rotation around the axis 45° between the +Z and +X directions. Its matrix representation is

$$\hat{H} = \frac{1}{\sqrt{2}} \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix}.$$

As an example, applying the Hadamard gate to the  $|0\rangle$ -state gives

$$\hat{H}\left|0\right\rangle = \frac{1}{\sqrt{2}} \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix} \begin{bmatrix} 1 \\ 0 \end{bmatrix} = \frac{1}{\sqrt{2}} \begin{bmatrix} 1 \\ 1 \end{bmatrix} = \left|+\right\rangle.$$

Gates can also be applied based on some external condition, performing the gate only if the condition evaluates to true. These are referred to as *conditional gates*.

#### **Definition: Conditional gate**

A gate with classical control, likewise for a conditional rotation.

#### **Multi-qubit Gates**

As with single-qubit gates, multi-qubit gates can be represented by a matrix. The controlled NOT gate (CNOT) for example, is a 2-qubit gate that performs an X-rotation on one qubit based on the state of another with a matrix representation as shown in (2.1). The first qubit is also referred to as the 'target', while the second is the 'source' or 'control' qubit. This makes the CNOT a *controlled* gate, or more specifically a controlled X-gate. Controlled gates should not be confused with a conditional gates; a controlled gate has qubit control, while a conditional gate has classical control.

#### **Definition: Controlled gate**

A gate with qubit control, for example a CNOT.

Using a qubit as control works identical to classical control when the qubit is in the  $|0\rangle$  or  $|1\rangle$  state. When the control qubit is in a superposition however, performing the CNOT gives rise to *entanglement*. To illustrate what happens, we start with two qubits: one as control in the  $|+\rangle$  state and one as target in the  $|0\rangle$  state. Their combined state is

$$\frac{1}{\sqrt{2}} \begin{bmatrix} 1 \\ 1 \end{bmatrix} \otimes \begin{bmatrix} 1 \\ 0 \end{bmatrix} = \frac{1}{\sqrt{2}} \begin{bmatrix} 1 \\ 0 \\ 1 \\ 0 \end{bmatrix}.$$

Multiplying this with the matrix representation of the CNOT gate gives

$$\begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{bmatrix} \frac{1}{\sqrt{2}} \begin{bmatrix} 1 \\ 0 \\ 1 \\ 0 \end{bmatrix} = \frac{1}{\sqrt{2}} \begin{bmatrix} 1 \\ 0 \\ 0 \\ 1 \end{bmatrix}. \tag{2.1}$$

Unlike the initial combined qubit state, this outcome can *not* be written as the product of two separate states anymore. At this point the qubits are said to be entangled. Extending entanglement to even more qubits, the number of terms required to represent the combined state grows exponentially as mentioned in Section 2.1.1. Additionally, a measure of exactly how entangled two qubits are can be defined. This is given by the *concurrence*

$$C(|\psi\rangle) = 2 |\alpha_{00}\alpha_{11} - \alpha_{01}\alpha_{10}|,$$

which is nonzero for entangled states. When C=1 the two qubits are *maximally entangled*, as for example is the case for the result of (2.1).

Where single qubits have the X-, Y-, and Z-basis, there is also a commonly used 2-qubit basis known as the *Bell basis*, the basis vectors of which represent pairs of maximally entangled qubits.

$$\begin{split} |\Phi_{+}\rangle &= \frac{1}{\sqrt{2}}(|00\rangle + |11\rangle) = \frac{1}{\sqrt{2}}\begin{bmatrix} 1 & 0 & 0 & 1 \end{bmatrix}^{T} & |\Psi_{+}\rangle &= \frac{1}{\sqrt{2}}(|01\rangle + |10\rangle) = \frac{1}{\sqrt{2}}\begin{bmatrix} 0 & 1 & 1 & 0 \end{bmatrix}^{T} \\ |\Phi_{-}\rangle &= \frac{1}{\sqrt{2}}(|00\rangle - |11\rangle) = \frac{1}{\sqrt{2}}\begin{bmatrix} 1 & 0 & 0 & -1 \end{bmatrix}^{T} & |\Psi_{-}\rangle &= \frac{1}{\sqrt{2}}(|01\rangle - |10\rangle) = \frac{1}{\sqrt{2}}\begin{bmatrix} 0 & 1 & -1 & 0 \end{bmatrix}^{T} \end{split}$$

Other single-qubit gates also have controlled counterparts, such as the controlled Y- or Z-gates or even controlled arbitrary rotations. Another common 2-qubit gate is the swap gate, which as the name implies simply swaps the states of two qubits.

Going beyond 2 qubits there are only few standard or common gates. A notable example is the 3-qubit *Toffoli* gate, also known as the CCNOT or CCX gate. This is an extension of the 2-qubit CNOT gate with multiple control qubits. Only if both control qubits are in the  $|1\rangle$ -state is the target qubit fully flipped. This can be extended to any number of control qubits.

#### 2.1.3. Quantum Operations

Unitary gates are just one kind of operation that can be performed on qubits. There are also non-unitary operations which by definition are non-reversible and destroy (part of) the existing qubit state. Nevertheless they are vital for useful quantum algorithms.

#### **Definition: Quantum operation**

Any action that can be performed on qubits, including gates, non-unitaries, and platform-specific operations.

#### Initialization

For a quantum circuit to be useful the initial state of the qubits has to be defined. So far any qubits used in examples were already in a given state without further consideration of how they got there. In reality, physical qubits can often be initialized only in a limited number of states. Generally the reference frame is picked such that at least initialization in  $|0\rangle$  can be performed natively. Initialization in other states can then be achieved by rotating the qubits from  $|0\rangle$  into the desired state.

Initialization is not a unitary quantum gate since it forces the qubit into a specific state regardless of the previous state, making the operation irreversible.

#### Measurement

Unfortunately, the complete state of a qubit can not be measured directly. Instead it is only possible to measure a qubit in a chosen basis, and the measurement itself causes the qubit state to *collapse* into one of the basis vectors. The only way to get more information about a qubit state is to repeat the steps that got it there and measuring again, repeating this process until the desired accuracy is achieved.

#### **Platform-specific Operations**

While initialization and measurement are universally present in practical quantum computers, certain qubit technologies or even specific implementations may require their own platform-specific operations.

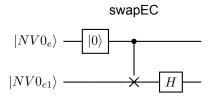

An example of such an operation is entanglement generation when using NV centers. Instead of performing 2-qubit gates to entangle the qubits in 2 different NV centers, a special procedure can generate a Bell-pair directly called an *ebit*.

#### **Definition: Ebit**

A pair of maximally entangled qubits.

Similar to single-qubit initialization, the previous qubit state has no effect on the outcome, making this a non-unitary operation. The ebit generation procedure for NV centers is explained in more detail in Section 2.2.3.

#### 2.1.4. Quantum Circuits

As with classical computing, quantum operations can be performed in sequence to implement a quantum algorithm. This sequence of operations is referred to as a *quantum circuit*.

#### **Definition: Quantum circuit**

A specific type of quantum algorithm that consists of a sequence of quantum operations.

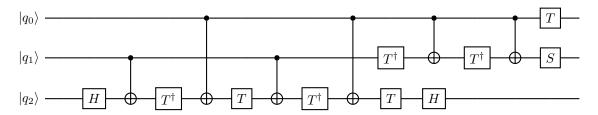

Figure 2.3: Decomposition of the 3-qubit Toffoli gate into rotations and CNOTs.

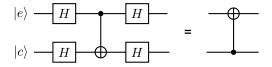

Since individual gates are reversible, a quantum circuit or portion thereof consisting purely of quantum gates is also reversible as a whole. Theoretically, these gate sequences are just a large and complex gate, with a single matrix representing its operation. This concept is the basis of *gate synthesis*, where a complex gate is broken down into (usually) 1- and 2-qubit gates that can be performed in practice.

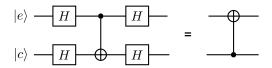

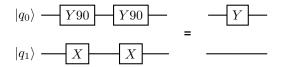

More generally the processes of breaking down complex operations into simpler ones is called *decomposition*. An example of this is shown in Figure 2.3 for the 3-qubit Toffoli gate.

#### 2.1.5. Quantum Error Correction

Real physical qubits are inherently analog. As a result, they suffer from errors caused by noise. This originates from multiple sources such as the control electronics or other qubits.

To counter these errors, quantum error correction (QEC) can be used. Much like classical error correction, QEC allows for detection and correction of errors. By making use of some peculiarities of quantum mechanics, this can even go beyond what is possible with classical analog signals.

#### **Classical Error Correction**

Consider the most basic classical digital error correcting code: the repetition code. A single bit can be encoded by repeating its value over for example 3 bits. This way, if one bit experiences an error, the other 2 can be used to detect and correct this error through a majority vote. Essentially, a single *logical* bit is represented by multiple *physical* bits.

With analog electronics a similar approach can be used, for example by applying the same input to multiple identical circuits and averaging the outputs. However, any common-mode noise will not be filtered out this way. The total error is reduced, but not completely eliminated.

#### **Improved Quantum Error Correction**

At first glance qubits might seem to face the same fate as classical analog electronics, but more pressing is the inherent property of qubits that they can not be copied or cloned [3]. Instead, a close alternative is to perform a controlled NOT gate from the source qubit onto the target qubits that have been initialized in the  $|0\rangle$  state. While this does result in the target qubits being identical for purposes of measurement or as source qubits, it also means the 3 qubits may now be entangled depending on their initial state. As a result, measuring one qubit will not only collapse its own superposition but also (partially) collapse the superposition of the others, making a direct majority vote impossible. However, quantum error correction is still possible by making use of *indirect parity* measurements.

'Indirect' means that the qubits are not measured directly but rather through additional qubits. A distinction can be made between *data* qubits that store a quantum state for longer periods of time, and *auxiliary* qubits that are used for indirect measurements or other short-term procedures. Multiple data and auxiliary qubits then make up a single logical qubit.

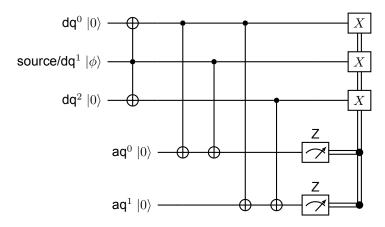

Figure 2.4: Quantum repetition code with 3 data gubits.

#### **Definition: Auxiliary qubit**

A qubit used to perform indirect operations such as measurements, as opposed to a data qubit. Also known as an *ancilla* qubit.

'Parity' means that instead of trying to measure a single qubit, a parity check of two qubits is performed. This process is illustrated in Figure 2.4. After initializing the data qubits, two CNOTs are performed on each of the auxiliary qubits after which they are measured in the Z-basis. Because these measurements only give information on the combined state of two or more qubits rather than of an individual one, the superposition of the data qubits is preserved.

Even without knowledge of the exact states of the data qubits, the parity measurements still provide enough information to detect and correct errors. For classical bits this is illustrated in the following table. Note that only single-bit errors can be correctly detected, since a 2- or 3-qubit error is indistinguishable from a 1-qubit error or no error at all.

| $aq^0$ | $aq^1$ | Single-bit error |

|--------|--------|------------------|

| 0      | 0      | None             |

| 0      | 1      | $dq^2$           |

| 1      | 0      | dq <sup>0</sup>  |

| 1      | 1      | $dq^1$           |

This shows the process with digital values, however superposition of qubits is an analog phenomenon. This is where the peculiarities of quantum mechanics come to help: the auxiliary qubits are still entangled with the data qubits, and measuring them will discretize the error on the data qubits. After applying the conditional gates, this results in the error being fully corrected. It should be noted however that this simple repetition code can only correct unwanted X-rotations.

#### **Better Quantum Error Correction**

To correct *all* possible errors in a logical qubit, more advanced error correction is necessary. An example of such a QEC are the *surface codes* [4], which perform both X and Z-parity measurements on the data qubits as opposed to only X-parity with the repetition code. Additionally, as the name suggest the data and auxiliary qubits are laid out in a 2D plane and interaction edges between qubits do not cross each other. This simplifies the requirements for the physical qubit system.

Different kinds of surface codes exist with different advantages and disadvantages, implementation requirements, and other properties that might make one more suitable for a specific use case. Some examples are color codes [5], holographic codes [6], and lattice surgery [7]–[9]. QEC is an active

field of research with novel ideas, combinations of existing work, and specific implementations being introduced regularly.

### 2.2. NV Center Physics

While many different qubit technologies exist, the current focus of the Fujitsu project and therefore also of this thesis are nitrogen-vacancy center (NV center)s.

A nitrogen-vacancy center is a point defect in diamond, formed by a nitrogen substitution and carbon vacancy next to each other. The negatively charged NV<sup>-</sup> state, which occurs when an additional electron from the environment is captured, is of primary interest for this thesis. The neutrally charged NV<sup>0</sup> state also has its uses [10], but these are limited. A short description of the NV center qubits from a control perspective is provided next. For more details on the underlying physics, the reader is referred to [11]–[15].

#### 2.2.1. Qubits

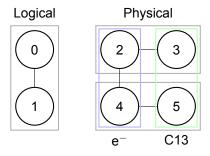

Central to the operation of an NV center-based quantum system is the qubit associated with the electron (e<sup>-</sup>) spin in the NV center. This qubit is highly controllable through radio-frequency electromagnetic fields and photons. However, this comes at the cost of being susceptible to noise.

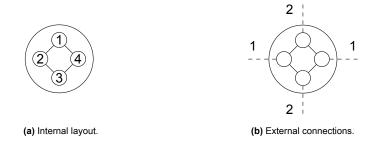

Additionally, nuclear spins from naturally occurring Carbon-13 ( $^{13}$ C) isotopes within the diamond can be used as qubits. These spins cannot be controlled directly, instead they interact with the electron spin and can be controlled indirectly. The carbon spin qubits have the advantage of being less susceptible to noise and decoherence. This motivates their use as data qubits, storing quantum states for longer periods of time while the  $e^-$  qubit performs most operations [15]. Control of a single NV center with up to 8 of these qubits has been demonstrated [16], however an increasing number of carbon spin qubits is only useful up to a point due to increased runtime and decreased control. What amount of qubits is useful in practice remains to be seen.

Finally, the nuclear spin of the nitrogen atom itself can be used as qubit, in a way similar to the <sup>13</sup>C qubits [16], [17]. However, other types of color centers do not necessarily have a usable nuclear spin like nitrogen does, so for the purpose of generality this qubit is not treated as a special case.

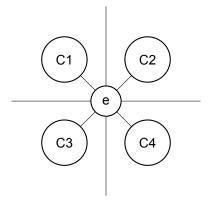

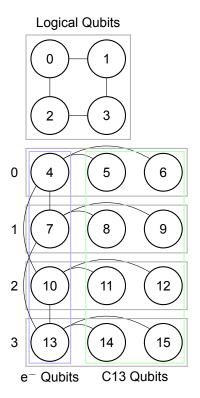

A schematic overview of an NV center with 4 <sup>13</sup>C qubits is shown in Figure 2.5.

**Figure 2.5:** A nitrogen-vacancy center with 4 carbon spin qubits. The lines extending outwards from the electron spin qubit represent connections with other NV centers.

#### 2.2.2. Control

As mentioned, only the electron spin qubit in an NV center can be controlled directly. This can be done using either an AC magnetic field or photons.

The magnetic field can be used to perform gates on a single NV center. Starting from single-qubit rotations on the  $e^-$  qubit, controlled and uncontrolled rotations of the  $^{13}$ C qubit can also be achieved [13]–[15].

Different photon wavelengths can be used for different operations as described below. The NV center can also (re-)emit photons which have to be detected. This requires single-photon detectors, which can be designed using for example superconducting nanowires [18].

Initialization is done with a procedure known as charge pumping, where photons are continuously fired upon the NV center until they are not absorbed anymore, indicating initialization has been achieved. Measurement is done in a similar fashion, where the number of photons absorbed is indicative of the qubit state [11].

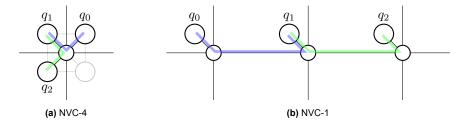

Photons can also be used to entangle the electron spin qubits in two different NV centers. This involves exciting the NV center with a photon, resulting in another photon being emitted. Interfering the photons emitted by two NV centers and measuring the outcome results in the  $e^-$  qubits to be entangled. Since this procedure is not 100% guaranteed to be successful, it can be repeated and combined with single-qubit rotations to improve the entanglement fidelity [13], [19], [20].

#### 2.2.3. Connectivity

A major advantage of the photon-based entanglement described in the previous section is that photons can be easily transported. On a small scale, on-chip wave guides could be used to allow interactions not limited to neighboring NV centers. Ignoring photon losses any arbitrary network would be possible only under the constraints of the waveguides. On a larger scale, fiber optic cable could be used to connect NV centers across longer distances of several meters [21] or even hundreds of meters [22]. This would allow multiple quantum computers to work together using the same or similar entanglement procedures as used internally.

A peculiarity of this photon-based entanglement is that it does not allow one to perform unitary gates between NV centers. Instead, the only operation possible is to initialize the two e<sup>-</sup> qubits in a maximally entangled Bell pair state. This means that if the desired action is to perform a unitary gate, some extra steps are required. However, if maximum entanglement itself is the desired result this can thus be performed as a single operation.

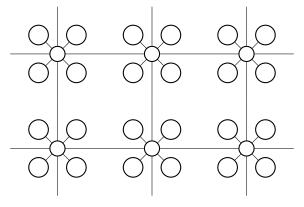

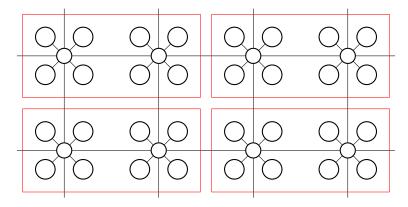

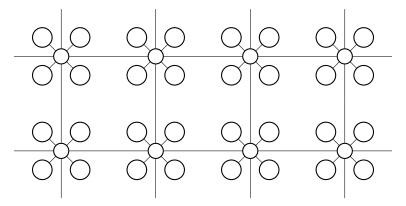

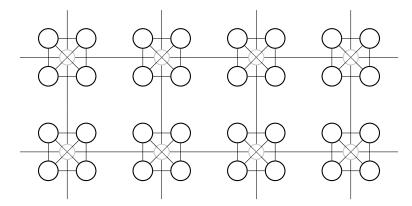

Figure 2.6 shows an example of 6 NV centers connected in a 2D nearest-neighbor grid, illustrating both connectivity within a single NV center and between multiple. A 2D grid is used here just for simplicity, but as mentioned the NV center connections can be arbitrary.

Figure 2.6: Connectivity of multiple NV centers, here shown with 4 <sup>13</sup>C qubits each.

2.3. Digital control

#### 2.2.4. Comparison with Other Technologies

Quantum hardware based on NV centers or other color centers has a number of features that distinguish it from other qubit technologies. This section discusses these differences and their implications on higher-level systems such as the digital control system and compiler.

#### Stability

The stability of NV centers make them useful at temperatures higher than other commonly used qubit technologies. Even at room temperature some features of NV centers are usable. This mainly applies to quantum sensing [23], [24], but also unitary gates and entanglement have been demonstrated at ambient conditions [25], [26].

#### **Hybrid Qubits**

Within a single NV center, the two qubit types have distinctly different properties resulting in a hybrid qubit system. The  $e^-$  qubits are highly controllable but vulnerable to decoherence, while the  $^{13}$ C qubits are stable for relatively long periods of time. This motivates their use as auxiliary and data qubits respectively.

Additionally, the <sup>13</sup>C qubits cannot be controlled or interact with each other directly, only through the e<sup>-</sup> qubit. Figure 2.6 shows an example for six NV centers. This contrasts with for example superconducting and trapped ion technologies where each qubit functions the same, and connectivity is more uniform [27], [28].

#### Connectivity

The possibility of arbitrary connections between NV centers as described in Section 2.2.3 is in stark contrast with for example superconducting qubits, which even in state-of-the-art implementations are limited to nearest-neighbor connectivity [29]. The prevalence of superconducting qubit systems is reflected in the large amount of work being done towards surface codes which are inherently planar. There is an advantage to be gained with higher-connectivity systems however [27], [30], and some possibilities for superconducting systems have already been explored [31], [32].

The native connectivity possibility of NV centers may give them an edge over superconducting qubits. While trapped-ion qubits provide high connectivity as well, the shared control electronics limits the number of simultaneous operations, while NV centerscan also operate individually when required.

## 2.3. Digital control

To execute a quantum program, the analog control hardware described in Section 2.2.2 needs to perform the required operations in the correct order. This can be handled by a digital control system which executes a quantum program as a sequence of instructions, much like a classical computer.

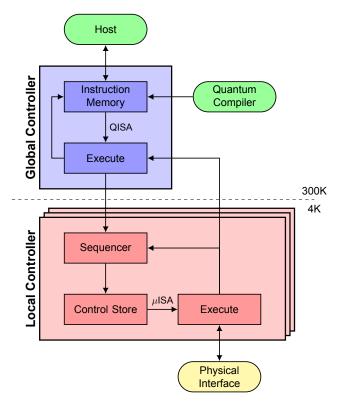

In the context of the Fujitsu project, a layered control architecture is envisioned. The lower layer consists of local controllers responsible for one NV center each, and the upper layer consists of a single global controller which orchestrates the operation of the lower layer. By separating the control architecture in this way, the local controllers can directly manage the analog control electronics of individual NV centers in a highly parallel manner, while these details are kept away from the global controller which can operate on much higher-level instructions.

This contrasts with existing work where a single controller is directly responsible for many physical qubits, as for example shown in [33]. An example of a more separated control architecture is presented in [34], but also here there is a certain degree of global control at the lower layers. A control architecture with 2 fully separated layers is presented in [35], which implements quantum error correction on the lower layer.

Based on the layered concept, in [36] a version of such a QISA has already been designed. However, this QISA does not clearly distinguish between the two levels. Additionally, further developments in other areas of the Fujitsu project have brought new possibilities to light.

### 2.4. Compiler

While the basic instructions described in the previous section provide all necessary control over the quantum hardware, they are very fine-grained. This makes writing a full algorithm in assembly a tedious and error-prone task. For this reason software is typically written in a high-level programming language.

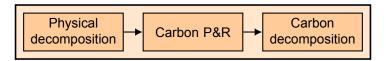

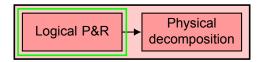

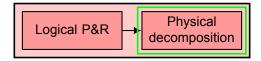

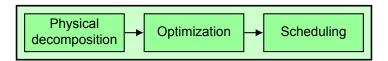

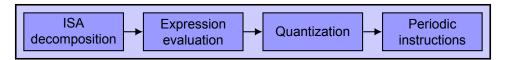

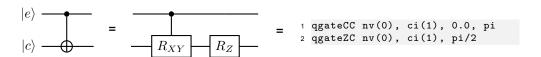

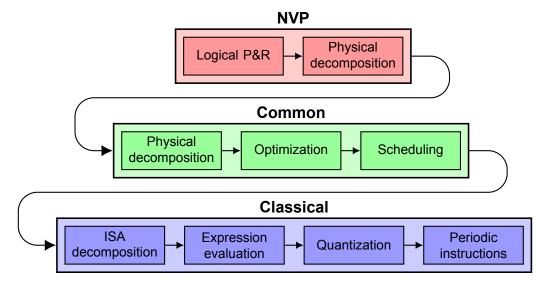

Since the control electronics only understands the lower-level instructions, it is necessary to convert these high-level languages down to assembly language. This is done by a compiler. The process is typically divided into several *passes*, each responsible for a certain kind of transformation. These passes are performed on an intermediate representation (IR) that represents the code in an abstract way suitable for the compiler.

Passes can be categorized into being fully internal or being part of the *frontend* or *backend*. The internal passes are more generic, performing actions on the IR with little to no assumptions about how and where the program was written or what will happen to the output. Passes belonging to the frontend are specific to a certain type of input such as an input programming language. Similarly the backend passes perform actions specific to the target platform.

#### **Definition: Execution platform**

Something which can execute a quantum algorithm, be it a simulator or real quantum computer. In this thesis a platform is assumed to be compatible with quantum circuits.

A classical compiler can include passes such as optimization, analysis, and code generation. A quantum compiler can include passes with similar functionality, but will have some passes specific to quantum computing as well. The following sections describe several passes in detail, how they apply to NV centers, and the resulting compiler requirements.

#### 2.4.1. Frontend

The frontend is how the main user input enters the compiler. This can be in the form of files written in a dedicated programming language such as cQASM [37], but also as a generic programming language extended with a library such as Qiskit[38]. In both cases the frontend converts the user input into an intermediate representation used by the internal compiler passes.

#### 2.4.2. Decomposition

Decomposition is the process of 'taking apart' complex operations. This is needed if not all quantum operations can be applied directly to the hardware. For example, a certain quantum system might have CNOTs as the only 2-qubit gate, requiring other operations involving 2 or more qubits to be decomposed into a sequence of CNOTs and single qubit gates. Since many existing qubit technologies allow for 2-qubit gates at most, decompositions such as these can be generally applicable.

Decompositions can also target a certain technology or even specific implementation. For example, rotations could be limited to some specific axes, requiring rotations in other axes to be decomposed into multiple rotations over valid axes.

#### 2.4.3. Optimization

Optimization is the process of transforming a quantum circuit into a 'better' equivalent, usually optimizing for execution time. This can be done by for example reorganizing and combining gates or removing redundant operations [39]. Similar to decomposition it can be generic or tuned to a specific technology or implementation.

A basic optimization for a quantum compiler is to combine Clifford gates which act on just a single qubit. Sequences of Clifford gates can sometimes be merged into fewer gates, although this does depend on the gates supported by the target platform.

#### 2.4.4. Scheduling

If the output of one operation is used as an input for the next they must be executed sequentially. If there is no such dependency they can be executed in parallel, decreasing execution time. A scheduler pass performs this dependency analysis and schedules instructions accordingly.

Information about how long each instruction takes can help increase the effectiveness of this process. Additionally, there may be other constraints to consider, for example when some control electronics are shared between multiple qubits.

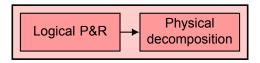

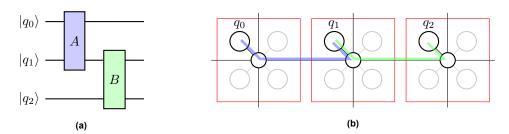

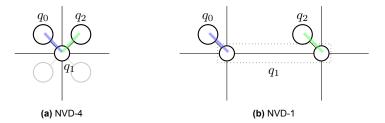

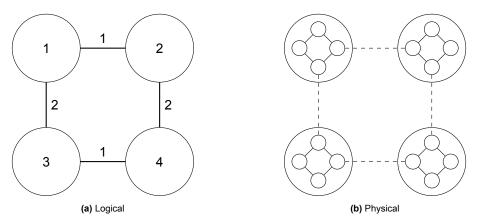

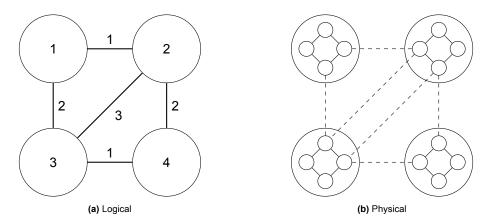

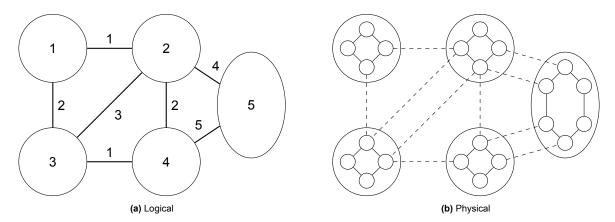

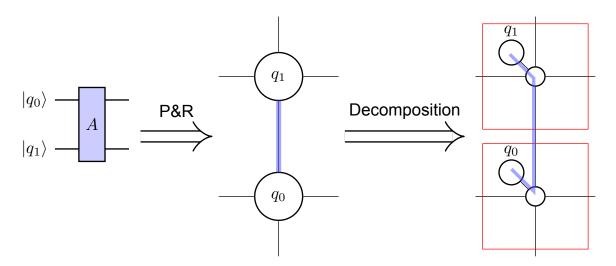

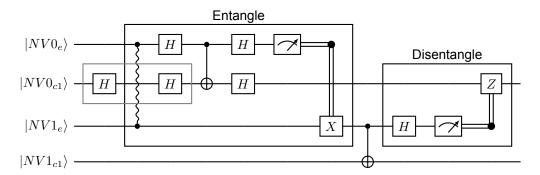

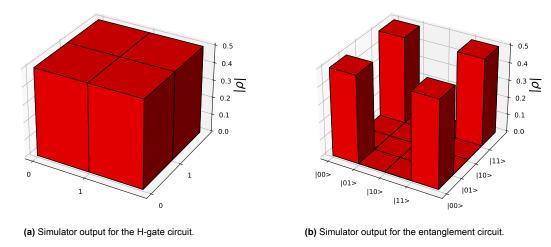

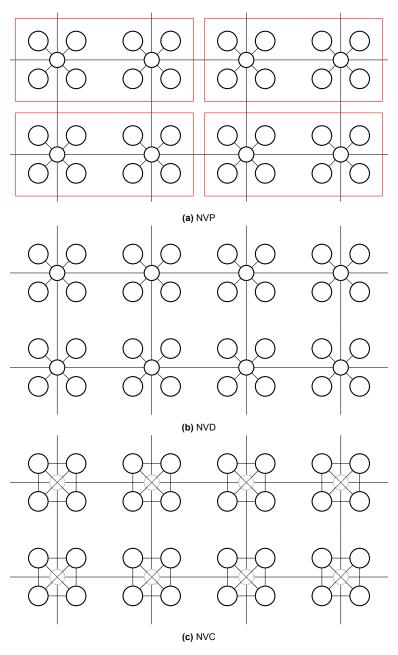

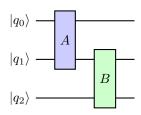

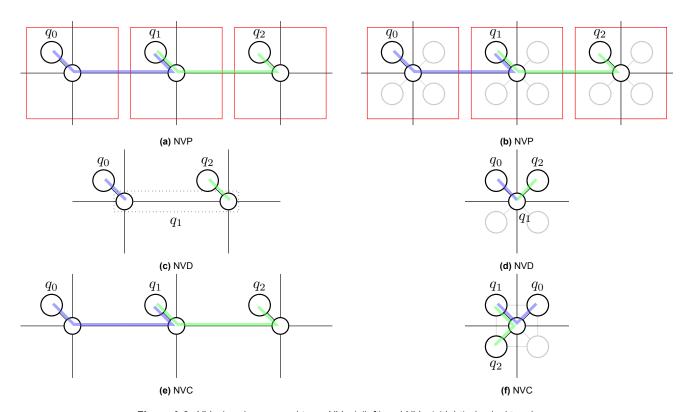

#### 2.4.5. Mapping