# Stellingen TR34393

behorende bij het proefschrift

### Multimedia Hardware Accelerators

Edwin Antonius Hakkennes

Delft, 7 december 1999

- 1. Een overloop van een optelling onthouden of doorgeven, dat is de vraag in dit proefschrift.

- 2. Optellen is eenvoudiger als aftrekken.

- 3. Het aantal reclames voor nieuwe computers houdt gelijke tred met het aantal reclames waarin bedienend personeel wordt geworven.

- 4. Naarmate de tijd voortschrijdt, duurt alles korter.

- 5. Als redundantie en fout-corrigerende eigenschappen net zo makkelijk aan schakelingen toegevoegd kon worden als aan opgeslagen data, zou de opbengst van de verschillende chipfabrieken allang tot 100% zijn gestegen.

- De lage prijs, de goede beschikbaarheid en het gemak van CDrecordables is zeker een factor waardoor Open Source Software in de lift zit.

- Het algemene ontwikkelingsdoel van computer engineering is het maken van snellere computers. Hieruit kan worden afgeleid dat de huidige computers niet snel genoeg zijn.

- 8. De regels van de sociale zekerheid veranderen zodra je ervan afhankelijk wordt.

- 9. De levensduur van straatverlichtingsapparatuur wordt aanmerkelijk verlengd door het gebruik ervan.

- 10. Het woorduitvinden moet aan banden worden gelegd.

- 11. Het openbaar vervoer kan veel goedkoper als we het gratis maken.

12. De betere stellingen worden pas bedacht, als het proefschrift naar de drukker is gebracht.

- 1. To carry or not to carry, that is the question in this thesis.

- 2. Addition is simpler than subtraction.

- 3. The number of commercials for new computers is at equal pace with the number of commercials recruiting people to operate them.

- 4. As time progresses, events last shorter.

- 5. If redundancy and error-correcting properties could be added to circuitry as easy as to stored data, the yield of the chip manufacturing industry would have increased to a 100% a long time ago.

- 6. The low price, the high availability and the ease of use of CD Recordables are reasons for Open Source Software to flourish.

- 7. The general research goal of computer engineering is to provide faster computers. This implies that the speed of today's computers is unsatisfactory.

- 8. Social security's rules change as soon as one becomes dependent on them.

- 9. Lamp-posts live longer by using them.

- 10. Wordinvention should be restrained.

- 11. Public transport could be much cheaper, if it is provided free of charge.

12. The more impressive propositions (theses) spring to mind only at the moment the printer is printing the dissertation.

733231 3439 3044591 TR 3439

## Multimedia Hardware Accelerators

Edwin Hakkennes

### Multimedia Hardware Accelerators

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor

aan de Technische Universiteit Delft,

op gezag van de Rector Magnificus prof.ir. K.F. Wakker,

in het openbaar te verdedigen ten overstaan van een commissie,

door het College voor Promoties aangewezen,

op dinsdag 7 december 1999 te 16.00 uur

door

**Edwin Antonius HAKKENNES**

elektrotechnisch ingenieur geboren te 's Gravenhage Dit proefschrift is goedgekeurd door de promotor:

Prof.dr. S. Vassiliadis

De leden van de promotiecommissie zijn:

Rector Magnificus, voorzitter

Prof.dr. S. Vassiliadis, Technische Universiteit Delft, promotor

Prof.dr. ir. H.J. Sips, Technische Universiteit Delft

Prof.dr. J.-M. Muller, Ecole Normale Supérieure de Lyon

Prof.dr. J.G. Delgado-Frias, State University of New York, Binghampton

Dr.ir. E.F.A Deprettere, Technische Universiteit Delft Dr. H. Corporaal, Technische Universiteit Delft

Dr.ir. P. van der Wolf, Philips Research Laboratories, Eindhoven

#### ISBN 90-9013314-3

Subject headings: computer arithmetic, computer design and engineering, multimedia enhancements, hardware accelerators, multimedia processors, multimedia architecture.

The text of this book was edited using various EMACS versions, running under the Linux operating system on a dual pentium workstation. It is typeset in 11 points Times-Roman by  $\LaTeX$  Times-Roman by  $\LaTeX$  and the bibliography was compiled by BibTeX.

Copyright © 1999 by Edwin Hakkennes E.Hakkennes@ET.TUDelft.nl

All rights reserved. No part of this publication may be reproduced in any form or by any electronic or mechanical means (including photocopying, recording, or information storage and retrieval) without prior written permission of the author. An exception is made for retrieval (but not storing or printing) from the Word Wide Web for personal use only.

This dissertation is dedicated to Lyonne, for her patience and understanding.

### Multimedia Hardware Accelerators

#### **Edwin Hakkennes**

### **Abstract**

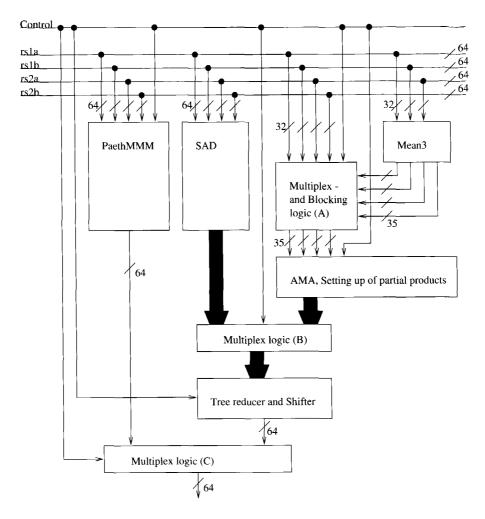

In this dissertation we we investigate the possibility to implement in hardware complex expressions and operations shown to be frequently used in multimedia applications. The first group of expressions we consider can be formulated as a general add-multiply-add operation and thus they can be captured by a single compound instruction family. For this family of operations we show that hardware can be built that requires approximately the same execution pipeline stages as the multiply instruction. This implies that the Add-Multiply-Add family of instructions should require the same execution time as the multiply instruction, significantly speeding up the execution of multimedia applications. Furthermore we show that two operations frequently used in motion estimation, the Sum and the Mean of Absolute Differences, can be implemented in hardware requiring also approximately the same execution time as the multiplication. Our approach can be extended easily to provide the computation of the Sum and Mean of Absolute Differences of a 16x16 pixel block in no more than four machine cycles. Additionally we propose a codec hardwired mechanism for the Paeth predictor used in the Portable Network Graphics Standard (PNG). We show that this execution unit requires at most two general purpose ALU cycles. We extend the Paeth unit to include the median, maximum and minimum operations on three inputs with no additional cycle time and we also extend the Add-Multiply-Add unit to include the mean of three numbers. Finally we propose the designs of two units to accommodate all the proposed instructions. One unit comprises all multiply related operations, the other the ALU related operations. The first one can be viewed as an extension of the multiply execution stage hardware. The other can be viewed as a stand alone, ALU like unit. Both units can be combined to a single execution unit that operates on 32 instructions in total.

# Preface and acknowledgements

The work presented in this dissertation has been carried out at the Computer Architecture and Digital Techniques (CARDIT) Laboratory, Electrical Engineering Department, of the Delft University of Technology. Numerous people have contributed in several ways to the results presented here. I will try to give a chronological list of the people who crossed (or should I say pushed my along) my research path. My work at CARDIT begun in September 1992, when ir. Reinoud Koolhaas hired me to supervise practical courses for both first and third year students. The experience gained from this teaching and the technical discussions regarding digital design with Reinoud, ir. Loek Thijssen and the other practical-supervisors (especially John van Leeuwen, Edwin Santing, Bryan Tjon-Kam, Gideon Zweijtzer and Steven Roos) were very valuable. Later on, I started with my masters project, guided by ir. Louis Muller and Jan Snelders. During this masters period, I gained insight in the problems of pattern recognition as well as design trajectory of a unit containing both custom hardware and software. To all the people who were part of this masters research, bedankt.

Towards the end of my masters project, I found out that I wanted to do more in this field. At this point I came in contact with my advisor, prof. dr. Stamatis Vassiliadis, who offered me a Ph.D. position. I want to thank him for giving me this opportunity and for the guidance and discussions during this research and the preparation of this dissertation. Stamatis,  $\varepsilon v \chi \alpha \rho \iota \sigma \tau \dot{\omega}$ . I also would like to thank dr. ir. Sorin Coţofană, with whom I shared the office for 2 years. Questions are always asked to the person nearest by, and Sorin mostly had an adequate answer. Îţi mulţumesc Sorin. Later, ir. Stephan Wong joined the group, and the scope of the research bended somewhat towards Multimedia. Stephan did a lot of literature research, which I used for both ideas and references. Stephan, henvgàn xìe.

The computer cluster used for the research at CARDIT is a heterogenous cluster of machines, which Bert Meijs administers, part of the time aided by ir. Tobias Nijweide and ir. Rogier Wolff. You provided not only me with an excellent working environment. Also, giving me the opportunity to experiment with some of the more exciting parts of system administration, such as installing Linux on not yet supported architectures and machines, provided me with an excellent distraction and perspective in computer engineering. Bert, Tobias and Rogier, Bedankt!

I want to thank Linus Torvalds, and all people working with him around the world, for creating and freely distributing Linux, which proved both a wonderful working environment and a welcome distraction of my research. Linus, kiitoksia oikein paljon.

I would like to thank my friends and family, for their interest in my work and finally I would like to thank my girlfriend, drs. Lyonne Zonneveld, for her patience, carefull proofreading and love. Lyonne, dank je wel.

# **Contents**

| Ał | Abstract         |                                           |    |  |  |  |  |

|----|------------------|-------------------------------------------|----|--|--|--|--|

| Ac | Acknowledgements |                                           |    |  |  |  |  |

| 1  | Introduction     |                                           |    |  |  |  |  |

|    | 1.1              | Background                                | 2  |  |  |  |  |

|    | 1.2              | Related work and open questions           | 6  |  |  |  |  |

|    | 1.3              | Assumptions                               | 10 |  |  |  |  |

|    | 1.4              | Framework of the dissertation             | 11 |  |  |  |  |

| 2  | Add              | -Multiply-Add                             | 15 |  |  |  |  |

|    | 2.1              | Preliminaries                             | 16 |  |  |  |  |

|    | 2.2              | Two's Complement Multiplication           | 17 |  |  |  |  |

|    | 2.3              | Inversion-selection                       | 21 |  |  |  |  |

|    | 2.4              | Half-adder encoding                       | 30 |  |  |  |  |

|    | 2.5              | Conclusions                               | 36 |  |  |  |  |

| 3  | Sun              | and Mean of Absolute Differences          | 39 |  |  |  |  |

|    | 3.1              | Background                                | 41 |  |  |  |  |

|    | 3.2              | Computing the Sum of Absolute Differences | 47 |  |  |  |  |

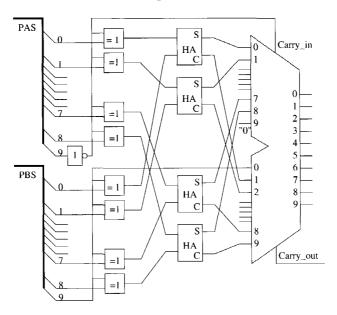

|    | 3.3              | A Sample Hardware Implementation          | 53 |  |  |  |  |

|    | 3.4              | Conclusions                               | 56 |  |  |  |  |

| 4  | Pae              | th Prediction and Coding                  | 59 |  |  |  |  |

|              | 4.1    | Introduction                                | 60  |  |  |  |

|--------------|--------|---------------------------------------------|-----|--|--|--|

|              | 4.2    | Background                                  | 62  |  |  |  |

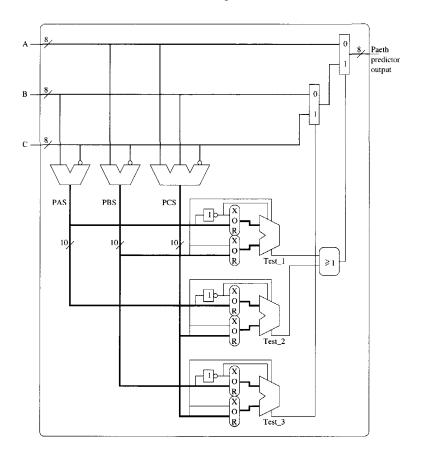

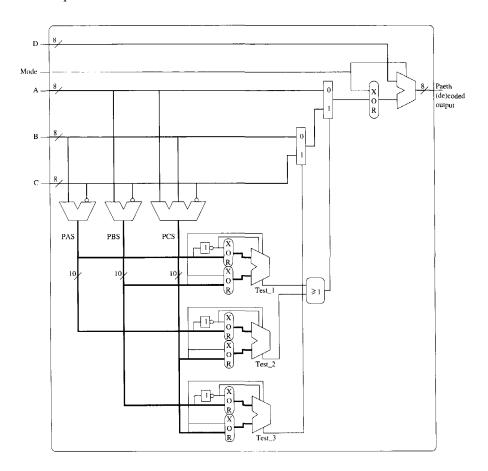

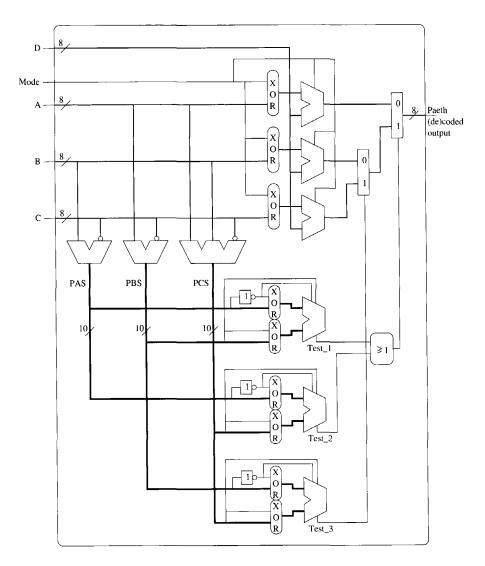

|              | 4.3    | Computing the Paeth predictor               | 66  |  |  |  |

|              | 4.4    | Implementation of a Paeth codec             | 69  |  |  |  |

|              | 4.5    | Hardware and time estimations               | 72  |  |  |  |

|              | 4.6    | Conclusions                                 | 74  |  |  |  |

| 5            | Med    | lian, Max, Min, and Mean                    | 75  |  |  |  |

|              | 5.1    | Background                                  | 76  |  |  |  |

|              | 5.2    | Computing the median: the software solution | 77  |  |  |  |

|              | 5.3    | Efficient computation of the Median         | 79  |  |  |  |

|              | 5.4    | Extending the Median Unit with Min and Max  | 83  |  |  |  |

|              | 5.5    | The mean of three numbers                   | 84  |  |  |  |

|              | 5.6    | Conclusions                                 | 88  |  |  |  |

| 6            | Putt   | ing it all together                         | 91  |  |  |  |

|              | 6.1    | Instruction Set                             | 91  |  |  |  |

|              | 6.2    | Sample implementation                       | 108 |  |  |  |

|              | 6.3    | Conclusions                                 | 114 |  |  |  |

| 7            | Fina   | l Remarks and Conclusions                   | 115 |  |  |  |

|              | 7.1    | Contributions                               | 118 |  |  |  |

|              | 7.2    | Future research directions                  | 119 |  |  |  |

| Bi           | bliogi | raphy                                       | 121 |  |  |  |

| Samenvatting |        |                                             |     |  |  |  |

| Cı           | ırricu | llum Vitae                                  | 133 |  |  |  |

| A            | Mot    | ion Estimation                              | 135 |  |  |  |

|              | A.1    | True Motion Estimation                      | 135 |  |  |  |

|              | A.2    | Block-Based Motion Estimation               | 136 |  |  |  |

## Chapter 1

## Introduction

Multimedia<sup>1</sup> processing is embedded processing especially tuned to efficiently execute multimedia applications. Accelerating multimedia processing is the subject of this dissertation, as it relates to the logic design of multimedia processors. More specifically we investigate the hardware implementation of execution units capable of improving the performance of multimedia processors. We note here that even though we discuss architectural issues, the definition of a complete multimedia architecture is not the primary scope of this dissertation. While we discuss design issues for a number of operations and propose instruction formats, we do not perform performance analysis considering for example frequencies of instructions<sup>3</sup> and cycle count based estimations for an entire application. In essence we do not attempt to legitimize an architectural choice from performance benefit in terms of cycles saved in the entire execution of a program but rather we consider performance improvements due to the realization of a specific function in hardware rather than in software. Furthermore we do not consider issues related to the physical realization of the units we propose. We particularly focus on the execution stage of an instruction and consider a pipelined processor as described in e.g. [2] and [3].

Under the above assumptions we establish instructions that have "small" num-

<sup>&</sup>lt;sup>1</sup>Multimedia is defined as the combination of diverse information including text, graphics, video, and audio. These forms of information comprised in multimedia are also referred to as *multimedia formats*.

<sup>&</sup>lt;sup>2</sup>Architecture here and in the rest of this dissertation denotes the attribute of a system as seen by the programmer, i.e., the conceptual structure and functional behavior of the processor. It is distinct from the organization of the data flow and physical implementation of the processor [1].

<sup>&</sup>lt;sup>3</sup>Instructions are the basic operations performed by a processor.

bers of cycle count requirements. More precisely the following is covered in general:

- consideration of the data flow of a proposed pipelined instruction and the logic design descriptions of the execution pipeline stage,

- estimation of the number of cycles required to perform the execution of the instructions we consider.

- providing estimations of the performance improvements for the proposed units when compared to other existing approaches where the same operations are executed in software.

We note that our work and proposals constitute the first basic steps for the definition of an architecture and that our considerations are necessary to further investigate the inclusion of new instructions to an architecture. Further discussion and substantiations of our choices will be found throughout the presentation of our proposals. Some general preliminary assumptions are discussed in the section 1.3.

The organization of the discussion of this chapter is as follows. First we provide some background information with some discussion on multimedia standards and some terminology definitions. Subsequently we discuss previous art and open questions followed by some general assumptions regarding architecture implementation and technologies. This chapter is concluded with a brief discussion of the organization of this dissertation.

### 1.1 Background

As indicated earlier, multimedia processors are processors especially tuned to perform "well" for multimedia applications. Multimedia is defined as the combination of the following forms of information: text, graphics, video, and audio – referred to as *multimedia formats* in the remainder of this dissertation. Traditionally, multimedia formats were being represented in an analog form, but currently we are observing a migration from the analog to the digital representation. The digital representation of the multimedia formats proved to have certain advantages. Examples of such advantages include easier editability and improved error resilience. While there are several advantages, the digital representation presented the scientific community and the industry with a sizeable

problem, which is the large volume of data to be processed, stored and communicated. The first solution to this problem is to increase the size of storage devices and the bandwidth of transmission lines.

The second solution, which can be combined with the first solution, is to compress the digital information. A substantial amount of research has been performed in this area, resulting in a multitude of compression techniques which are being used in current multimedia standards. These techniques exploit the fact that redundancies exist within the digital information and that these redundancies can be removed from the digital information with the possibility to reconstruct the original digital information using the remaining (compressed) digital information. The compression techniques can be basically divided into two classes, namely lossless compression and lossy compression. In lossless compression, statistics of the digital information are used to reveal redundancies within the digital information. Decompression of lossless compressed data produces an exact identical copy of the original data. This makes lossless compression applicable to all classes of data, regardless of its contents. In lossy compression, other information besides the statistics of the digital information is used to remove redundant information. An example is using the Human Visual System (HVS) model which describes the inner working of the human eye. Using this model, information which cannot be detected by the human eye is removed from the original digital information in order to obtain higher compression ratios than lossless compression. An exact copy of the original digital information cannot be reconstructed if lossy compression is used, hence the term lossy is being used. This property makes lossy compression unusable for certain classes of data, such as text or programs. In general, most multimedia data can be compressed using lossy techniques. A large part of this dissertation focuses on multimedia architectural issues that relate to compression techniques which are used to compress digital pictures and digital video. Each of the compression techniques is highly tuned towards a certain multimedia format which is being used by multimedia applications

Usually, a multimedia standard is general in the sense that multiple multimedia applications can be targeted by the standard. This is achieved by defining the parameters for each targeted application. One important fact to mention is that the encoding process is not specified in many multimedia standards.

<sup>&</sup>lt;sup>4</sup>A multimedia standard is generally defined as the collection of:

<sup>1.</sup> the definition of the structure of the bit-stream,

<sup>2.</sup> the rules on how to decode the bit-stream, and

<sup>3.</sup> a set of parameters which indicate certain constraints on the handled data.

to transfer information. In this sense, the multimedia applications pose the requirements which must be met by the compression techniques. For example, the VideoCD application stores video and audio (with predetermined parameters, like resolution of the frames and sampling frequency) on a compact disc which is being read by a CD-player at the bit-rate of 150 kBytes/s. This fact already determines that certain compression techniques can not be used, because they can not deliver the compression ratio to obtain the desired bit-rate.

Multimedia standards usually target multiple multimedia applications by combining several compression techniques well-suited to meet the requirements posed by the targeted multimedia applications. Using the proposed compression techniques, the original digital information is compressed into a bit-stream which can be stored or transmitted. To obtain a copy of the original digital data, which can be an exact copy of the original or a copy closely resembling the original, the inverse of the compression technique is used. The process of obtaining the compressed bit-stream is called the encoding process and the inverse is called the *decoding* process. Most multimedia standards only define the decoding process and the structure of the bit-stream and leave the encoding process undefined on purpose. Because of this fact, future results of continued research into faster and more efficient algorithms can be used in the encoding process. Additionally, manufacturers are currently enabled to implement their own algorithms to distinguish their products from other manufacturers. However, extreme differences after decoding due to the different encoding algorithms must be avoided. To this end, a rough guideline is given containing several error measures which must not be exceeded.

As stated in the previous paragraph, the encoding process is often not defined in a multimedia standard and only rough guidelines are given how to implement the encoding process. Therefore, different implementations are possible for the encoding process enabling manufacturers to differentiate their own products from other manufacturers. There are basically two approaches in how to implement multimedia standards. One approach is to implement the entire standard in software run on general-purpose processors. Using this approach, the implementation is fast in adapting to changes, but usually the performance is not good enough. The second approach is to implement the multimedia

<sup>&</sup>lt;sup>5</sup>A multimedia application is defined as any digital system which uses one or more multimedia formats to transport information and which performs the associated functions to accomplish this goal. Usually, multimedia standards are used to handle the multimedia formats used by the application.

<sup>&</sup>lt;sup>6</sup>A multimedia implementation is defined as a structure for realization and the realization itself in hardware or software for handling of multimedia formats specified by multimedia standards.

5

standards in hardware using Application Specific Integrated Circuits (ASICs). Using this approach, the highest achievable performance is possible, but usually adaptation to changes requires new designs which is a time-consuming and expensive process. This led to a hybrid solution between the two previous approaches, namely programmable Digital Signal Processors (DSPs) or Application Specific Instruction Set Processors (ASIPs). These processors are programmable as general purpose processors, and also have some specialized hardware execution units which can perform more complex, application-range specific, operations. This thesis studies such specialized execution units which may help to enrich the instruction set architectures of such processors to support multimedia applications. Additional information regarding these issues will be discussed found in the following section.

Before continuing on describing related work and open questions we briefly introduce some terminology that is found in multimedia and used throughout the dissertation. The following are some commonly used terms and standards:

- Pixel or Pel: The smallest element of any system that represents data in the form of 2-D arrays of visual information, e.g. on a video screen.

- **Resolution:** The fineness of the detail represented by any form of media: audio, images or video. In case of image and video, the resolution is defined by the number of pixels per picture.

- Luminance: The intensity, or brightness component, of an electronic image.

- **Chrominance:** The color portion of the information contained in an electronic color image.

- Multimedia Standards: Examples of multimedia standards are: JPEG, MPEG-1, MPEG-2, and H.261. Table 1.1 shows which multimedia applications are targeted by these standards. The JPEG standard is used to compress digital continuous-tone still-pictures using a wide variety of compression techniques while retaining good picture quality. The MPEG-1 and MPEG-2 standards are used to compress video and audio information. These standards provide video quality which is equal to or better than VHS tapes. The H.261 standard is very similar to the two MPEG standards, but targets applications like video-telephony (using regular telephone lines). This requires a very low bit-rate of the compressed bit-stream. Two newer standards are the Portable Network Graphics (PNG) and the Multiple Network Graphics (MNG) stan-

dards. These two provide lossless compression for images respectively sequences of images.

| Multimedia standard | Targeted multimedia application(s)          |  |

|---------------------|---------------------------------------------|--|

| JPEG                | Lossy compression of photographic images    |  |

| MPEG-1              | VideoCD                                     |  |

| MPEG-2              | DVD                                         |  |

|                     | digital broadcast of video                  |  |

|                     | HDTV                                        |  |

| H.261               | Video conferencing                          |  |

|                     | Video telephony                             |  |

| PNG                 | Lossless compression of images and graphics |  |

| MNG                 | Lossless compression of sequences           |  |

|                     | of images or graphics                       |  |

**Table 1.1:** Examples of multimedia applications targeted by different multimedia standards.

In the following sections we discuss the previous art and open questions, and we describe our assumptions that will be observed throughout the study.

#### 1.2 Related work and open questions

In order to improve the processing of multimedia applications, four types of processors have been investigated, namely:

**Specialized multimedia standard processors:** In this class of processors a specific standard such as MPEG-2 is assumed, and for such a standard a processor is designed that uniquely performs this standards requirements. There are several processors available that assume this approach. Examples of such processors are for example MPEG-2 Decoders [4, 5].

Stream based video processors: This class of processors performs various operations on streaming video. These processors are not targeted to a specific standard, but rather to a specific application domain, such as video-recorders and television sets. The programmability of these processors is limited, in that they can only perform a predefined set of operation. Typical operations executed by these processors are image en-

hancement, picture-in-picture and on-screen-display. Examples of these processors can be found in [6, 7, 8, 9, 10, 11, 12, 13, 14] and [15].

Specialized processors for augmented multimedia processing: In this class of processors, programmability is assumed and no restrictions to standards are imposed. That is, the processing follows the usual general purpose paradigm of programmability and the instructions set definition. These C-programmable processors are general purpose processor with extensions that make them particularly suited for media processing. For the Philips Trimedia architecture and processors [16] these are fine-grain extensions to the VLIW processor as well as coarse-grain coprocessors for e.g. VLD decoding. Another example of this class of processors is the Texas Instruments Multimedia Video Processor (MVP) [17].

General purpose processors: The family of general purpose machine is extended with coprocessing capabilities to improve the performance of multimedia applications. This approach follows the traditional extension oriented processing. That is, a general purpose processor architecture is extended with new architectural features in order to improve a certain application domain, which allows the design of coprocessors specialized for the considered application. Examples of such extensions include the floating point and vector extension of general purpose computing. Examples of this type of extensions with respect to multimedia include:

- Intel MMX(Multi Media eXtensions) [18, 19],

- ALPHA MVI (Motion Video Instruction extensions) [20, 21, 22],

- Sun VIS (Visual Instruction Set) [23, 24, 25] and

- MIPS DME (Digital Media Extensions) [26].

All these classes of processors provide improvements in multimedia processing and there is discussion which of the approaches should be followed. In this dissertation we do not discuss nor decide which of these approaches is a better multimedia solution. Rather we propose mechanisms that provide some improvements to all possible types of processors by proposing new execution units.

In order to determine the scope of our discussion we consider some of the open questions left by the previous proposals. Processors specialized for a specific standard assume fixed functions for all processing including the execution

hardware. This approach is rather limited to a single application (imposed by the standard) and it can hardly follow the multimedia requirements in their entirety. For example, an MPEG-2 specialized processor has no capabilities to perform the functions required by other standards or applications. Furthermore, advancement in standards can not be followed, except by redesigning the processor. Consider the following scenario as an example. Assume a specific motion estimator has been designed using the Sum of Absolute Differences operation. Given that the motion estimation algorithm is implemented in hardware, no change can occur even when a new, possibly better, algorithm also containing the sum of absolute differences function is proposed and desirable to implement. The previous discussion leaves open the following question:

• Can frequently used functions be parametrically specified and provided with appropriate interfacing so that standard improvements can be followed with minimal design effort and no redefinition of functions?

The last three classes of multimedia processors partially resolve this open question by providing programmability and new instructions. There are several examples of this approach. For example, the sum of absolute differences discussed previously, has been implemented as the PERR instruction in Alpha MVI [22] and as the newly added PSADBW instruction in Intel MMX [27]. The open question is resolved in part. While an appropriate interfacing is given (all programmable processor instructions have this property) the proposed instructions do not parameterize their implementation resulting in a potential bottleneck for their performance. To further elaborate, consider the sum of absolute differences function. If we assume a word parallel architecture based on 64-bit registers and if we assume a "word" is a byte then at most 8 "words" can be processed by a sum of absolute differences function instruction. While this is an improvement, it is also a bottleneck. It implies a maximum parallelism of 8 while the sum of absolute differences operates on blocks of 16 by 16 pixels. An additional open question imposed by this approach is that to the best of our knowledge, no specific direct implementations are reported that require minimum number of cycles necessary.

<sup>&</sup>lt;sup>7</sup>Recently, a new instruction has been added in the Intel MMX architecture and possibly a new implementation has been reported in the direction we propose [27]. Following the discussion of the microprocessor report [27] we conclude that the described approach is not the best possible. To determine the sum of absolute differences it is stated that their implementation performs the following three micro-operations:

<sup>•</sup> determine for each pair of inputs the difference,

<sup>•</sup> take the absolute value of this difference,

<sup>•</sup> take the sum of these absolute differences.

9

An additional open issue is phrased by the following:

• In determining the instruction set it is of interest to include the highest number of possible functions that are related to each other, so that a unit may be implemented that allows a number of functions to be performed at approximately the same cycle time with the least hardware expense.

In general purpose computing this problem has been addressed extensively (and plus or minus completely resolved). While multimedia instruction sets have added a number of instructions that follow the general purpose paradigm, the issue is far from a final settlement and continues to constitute an interesting open question phrased by the following:

• Which instructions can be added to the instruction set that are implementable with small hardware additions to the existing execution unit or that can be implemented as a new hardware unit capable of performing this new set of instructions?

We resolve in part<sup>9</sup> this open question by proposing:

- new instructions that can be added to existing units, e.g. a multiplier unit, with small additional cost and by proposing

- a separate "ALU like unit" capable of performing specialized multimedia functions, with cycle times comparable to general purpose ALU cycles.

The additions we introduce are meant to be the initiation of new unit design and the proposed research direction is to solidify this multimedia unit(s) by adding instructions in the future with similar hardware requirements.

Before we proceed with the further elaborations of our proposal we need to discuss a number of parameters. We dedicate the next section to the description of our assumptions.

As we have shown in [28] and describe in Chapter 3 of this dissertation, a better approach exists to compute this function.

<sup>&</sup>lt;sup>8</sup>See for example ALU related operations for fixed point units and adder or multiply related operations in floating point instruction sets.

<sup>&</sup>lt;sup>9</sup>In part here means that while we consider a number of multimedia formats we did not perform an exhaustive search. Basically we add-on on an existing art without pretending to examine all possible situations as such an attempt is rather impossible.

### 1.3 Assumptions

In order to determine new architectural features, a number of assumptions has to be put in order. The reason for such assumptions lies mostly in the difficulty to establish "universal" parameters for the evaluation and the acceptance of a proposal. Our assumptions for this dissertation are implied by the computer engineering general paradigm relating to the following factors:

- architecture,

- implementation,

- realization.

As suggested earlier we assume an add-on architectural approach, in that we assume a general purpose scenario rather than an application specific one. This assumption implies that our descriptions will strictly follow processing behavior that is programmable and possibly usable by multiple multimedia application requirements. Our assumptions regarding implementation rely on pipelined, possibly super-scalar machine organizations, which follow general logic design techniques, e.g. boolean logic instead of threshold logic [29]. Furthermore we assume "usual" pipeline structures. That is, we assume fixed point, non memory interfacing instructions, a pipeline structure of fetching, decoding, execute and write cycles. Additional cycles are assumed for load/store instructions<sup>10</sup> and other complex instructions such as multiply and divide.

Cycle related requirements such as critical paths, are imposed by well known algorithms for the design of general purpose units for addition related operations. That is, our cycle time assumptions mostly relate to the implementation of:

- ALU operations incorporating the design of parallel adders. See for example [30, 31, 32, 33, 34, 35, 36, 37, 38, 39, 40] and

- multipliers, dividers and other "multi-operand addition" functions, see for example [39, 40, 41, 42, 43, 44, 45, 46, 47, 48, 49, 50, 51, 52, 53].

We do not consider serial implementations as for example described in [54, 55, 56, 57, 58, 59, 60, 61, 62, 63, 64, 65, 66, 67] as such implementations are not used commonly in general purpose computers.

<sup>&</sup>lt;sup>10</sup>Note that given the fact that we are concerned mostly with the execution unit, very little is discussed about memory interfacing as such interfacing is not part of our concern in this dissertation.

11

Our technological assumptions are dictated by the implementation assumptions and the currently available technologies. In particular we assume that the technology is a gate array type of technology. For such technology we imply the availability of a library with gates called a bookset performing prespecified functions. The technology in which the gates are implemented is assumed to be CMOS. The assumed CMOS gates (bookset) consist of: a two-way XOR and XOR-INVERT; up to a three-way AND, OR, AND-INVERT, and OR-INVERT; and up to  $\pm 3x4$  AO books where + indicates the AND-OR function and - indicates the AND-OR-INVERT function. This is the same bookset assumed in [36] for the design of high speed, non-custom binary adders and it is also the bookset assumed in [68] for the design of high speed complex ALU operations. We further assume that every book in this library constitutes one stage of delay. While these assumptions are restricted to a particular technology, they do not limit the applicability of our discussion since such a bookset is common in currently available technologies and it is extendable to other technologies having similar characteristics or equivalent functional power within their booksets [36].

#### 1.4 Framework of the dissertation

The contributions of this dissertation are discussed in five chapters. More specifically the following is discussed.

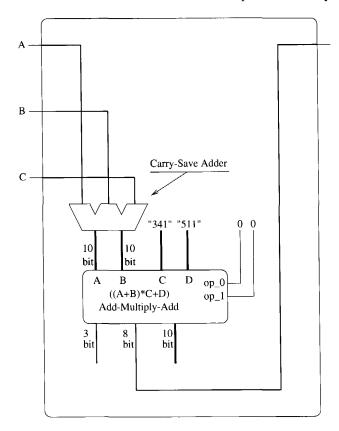

• In Chapter 2, entitled Add Multiply Add, we investigate complex (compound) instructions which could provide performance improvement for embedded systems and multimedia applications if implemented in hardware. In particular we show that a number of arithmetic expressions of certain forms occur frequently in embedded system applications. These arithmetic expressions have certain data-dependencies among the individual (fine grain) operations that constitute the arithmetic expression. A number of these expressions can be captured by an unique expression:  $(A \pm B) * C \pm D$ , or Add-Multiply-Add. Consequently, we propose two schemes for the implementation of such an expression, assuming two's complement number representation. The first scheme, the Inversion Selection technique, is a direct multiplication scheme for array and/or parallel implementations. The second scheme, the Half-Adder technique, performs a modified Booth Encoding and is also suitable for parallel design. The end result of the investigation in this chapter is that the Add-Multiply-Add expression can be computed in two machine

cycles (comparable to the machine cycles of a two cycle multiply), suggesting no more cycle time than the multiply instruction alone. This in turn suggests that the expressions we consider can experience a substantial benefit from the data dependency collapsing unit we propose. More specifically, the expression will require four machine cycles using standard hardware and three machine cycles using multiply-add hardware. This suggests that a speed-up between 1.5 and 2 will be achieved if the Add-Multiply-Add unit we propose is implemented in hardware.

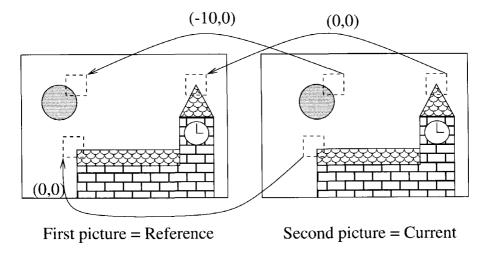

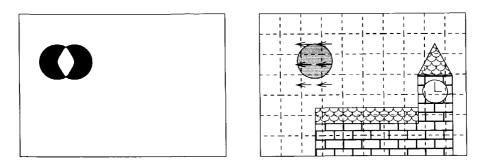

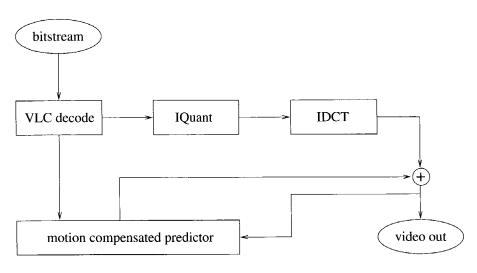

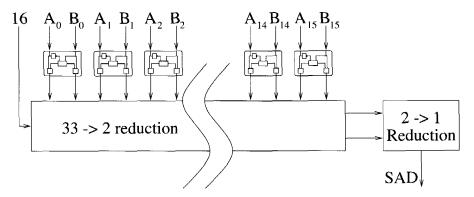

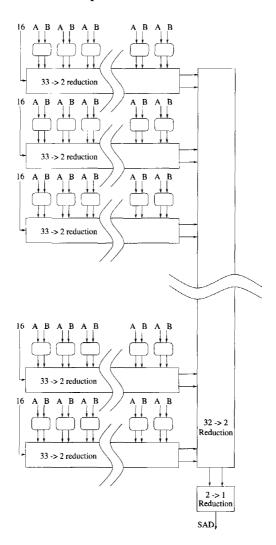

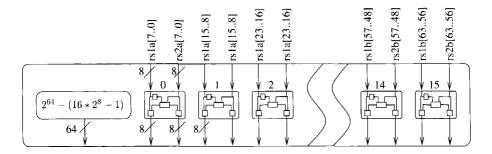

- In Chapter 3, entitled Sum and Mean of Absolute Differences, we investigate the Sum Absolute Difference (SAD) operation, an operation frequently used by a number of algorithms for digital motion estimation. For such an operation, we propose a single vector instruction that can be performed (in hardware) on an entire block of data in parallel. We investigate possible implementations for such an instruction. Assuming a machine cycle that is comparable to the cycle of a two cycle multiply, we show that for a block of 16x1 or 16x16, the SAD operation can be performed in 3 or 4 machine cycles respectively. The proposed implementation operates as follows: first we determine in parallel which of the operands is the smallest in a pair of operands. Second we compute the absolute value of the difference of each pairs by subtracting the smallest value from the largest and finally we compute the accumulation. The operations associated with the second and the third step are performed in parallel resulting in a multiply (accumulate) type of operation. Our approach covers also the Mean Absolute Difference (MAD) operation at the exclusion of a shifting (division) operation.

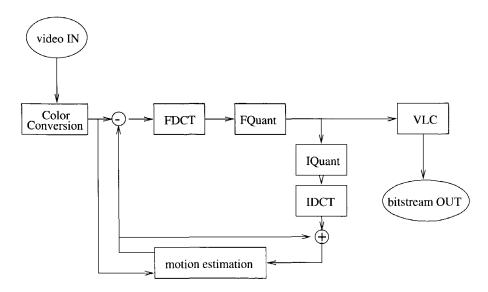

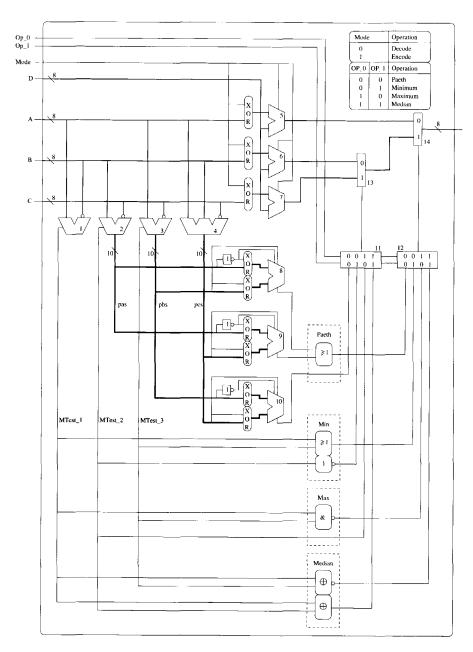

- In Chapter 4, entitled **Paeth Prediction and Coding**, we describe an execution unit capable of computing the Paeth predictor, as used in the Portable Network Graphics (PNG) standard. PNG is a rather new, lossless compression method for real-world pictures. It features five prediction schemes, of which the modified Paeth predictor is the most computational intensive. This chapter focuses on a hardware implementation of the Paeth predictor. We propose a hardware Paeth codec, capable of computing three different quantities:

- the Paeth predictor of three inputs,

- the difference of the current pixel and the Paeth predictor of the other inputs (Coding), and

- the sum of the coded input and the Paeth predictor of the other three inputs (Decoding).

The Paeth unit computes these values within two cycles, where a cycle is comparable to the cycle of a two cycle multiply. Depending on the mode of operation, the proposed mechanism produces the predictor or the (de/en)-coded pixel value.

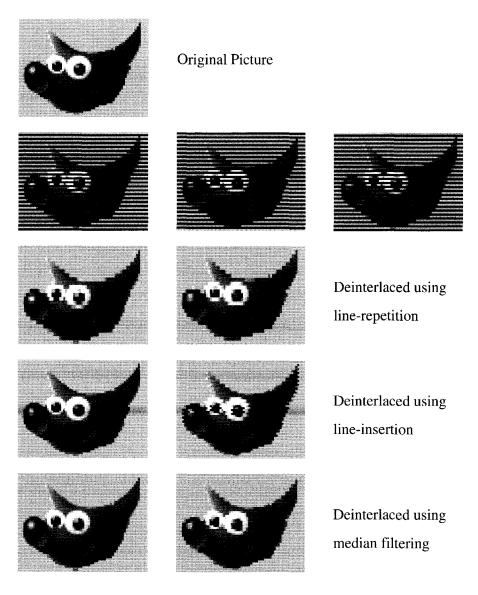

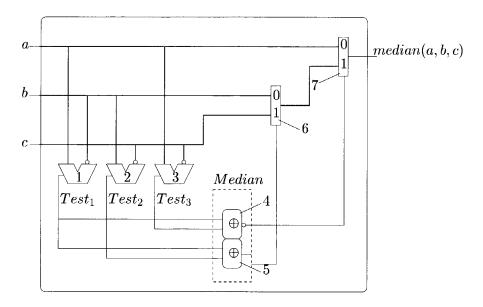

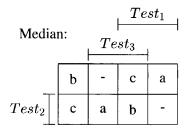

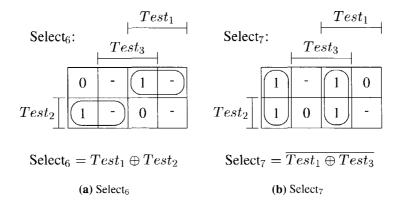

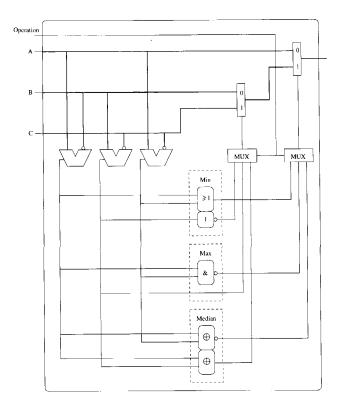

- In Chapter 5, entitled Median, Max, Min and Mean we introduce an extension of the Paeth unit by which it can additionally compute the Median of three inputs. This median is used in video-deinterlacing, which is needed for displaying normal (interlaced) video on a non-interlaced computer screen or a modern, high-end television set. We will further extend the Paeth logic, so that is can also compute the maximum and minimum of the three inputs. Furthermore, we introduce an extension of the Add-Multiply-Add unit, described in Chapter 2 by which the Add-Multiply-Add unit can compute the Mean of three inputs. The overall direction of this chapter is to introduce new instructions and show that they can be of advantage when compared to their software equivalent.

- In Chapter 6, entitled **Putting it all together**, the data-formats of the input and output of our proposed unit design are described. We also describe how the units can be integrated in one single unit implementation. Finally we propose a data-flow capable of performing all 32 instructions.

In the conclusion chapter we briefly discuss our findings and summarize the contributions of our proposals. We conclude the discussion by indicating some possible directions for future research.

## Chapter 2

# Add-Multiply-Add

It is widely accepted that true data dependencies [2] constitute one of the major obstacles for the improvement of speed in the computer based computational paradigm. True data dependencies occur when the execution of an instruction has to wait, because the instruction requires operands that are the result of the execution of a previous instruction. In the recent past it has been shown that some important classes of true data dependencies for the general purpose computational paradigm can be resolved resulting in a substantial gain of performance [69, 70, 71, 72, 73].

A major open question regarding special purpose multimedia computations, and embedded systems in general, is phrased by the following: while special purpose engines execute code that can possibly substantially benefit from the resolution of data dependencies techniques, thus far little has been achieved in such an area for this class of computations. There is evidence suggesting that current research is headed to the direction of investigating such an open question. For example, the application analysis presented by F. Onion et al. [74] for applications such as 2D convolution, filters, FFT, DCT, histogram flattening, edge detection, etc., shows that more elaborate data dependency collapsing hardware is required to resolve most of the true data dependencies.

More in particular the investigation in [74] has revealed that the following expressions (assuming the compiler can expose them) appear frequently in the benchmarks they have considered.

- Add-Add

- Add-Multiply

- Multiply-Add

- Add-Multiply-Add

- Multiply-Add-Add

In this chapter we resolve in part the open question regarding the expressions which Onion et al. [74] have uncovered. We consider fixed point number representations and combine four of the above five exposed expressions in a single instruction, for which we propose a hardware implementation. We do not consider floating point notations which are left as a further research topic.

Our investigation strongly suggests that the add-multiply-add expression we consider, in addition to the covering most of the expressions or operations revealed in [74], can potentially be implemented using a parallel hardware organization and potentially be executed within two machine cycles. The previous conjecture is put in place by showing that the partial product matrix associated with the expression requires no more than n+2 rows, n being the number of bits of the input-values, which will most likely require no more cycle time than a fixed point multiplier in most implementations. We propose two schemes for the computation of the add-multiply-add operation. The first scheme, the Inversion Selection technique, is a direct multiplication scheme for array and/or parallel implementations. The second scheme, the Half-Adder technique, performs a modified Booth Encoding and is also suitable for parallel design.

The organization of this chapter is as follows. In the section to follow we give some background information on the multiplication of two two's complement numbers. In Section 2.3 the first approach will be presented, the Inversion Selection Technique and in section 2.4 the second approach, the Half Adder Encoding is described. Section 2.5 concludes this chapter.

#### 2.1 Preliminaries

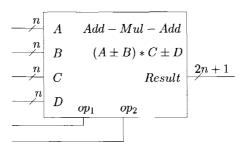

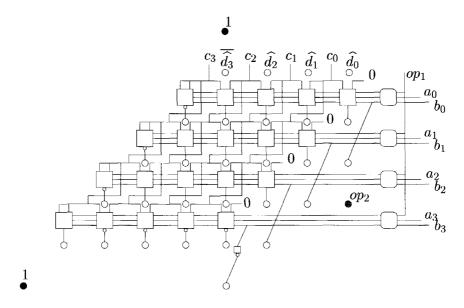

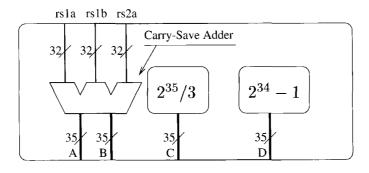

The general form of the expression we investigate in this chapter is  $(A \pm B) * C \pm D$ . The four operands, A, B, C and D are assumed to be n-bit numbers in two's complement notation. The result is a (2n+1)-bit number, also in two's complement notation. Figure 2.1 gives a graphical representation of the unit. Table 2.1 shows that a specific operation is carried out with the setting of the controls denoted as  $op_1$ ,  $op_2$ . Additionally, by proper setting of the operands, a multiplicity of other operations, e.g., multiply, add, add-add can also be computed. In the next two sections we present two implementation schemes for the

expression we consider. In the final section we conclude the presentation with some remarks. We first present the two's complement notation and a modification of the Baugh-Wooley algorithm for multiplying two two's complement numbers.

**Figure 2.1:** The outside view of the Add-Multiply-Add Unit.

| $oper_1$ | $oper_2$ | $(A \ oper_1 \ B) * C \ oper_2 \ D$ | $op_1$ | $op_2$ |

|----------|----------|-------------------------------------|--------|--------|

| +        | +        | (A+B)*C+D                           | 0      | 0      |

| +        | _        | (A+B)*C-D                           | 0      | 1      |

| -        | +        | (A-B)*C+D                           | 1      | 0      |

| -        |          | (A-B)*C-D                           | 1      | 1      |

**Table 2.1:** The operations that can be performed by the Add-Multiply-Add Unit.

#### **Two's Complement Multiplication** 2.2

Let X and Y be two n-bit two's complement numbers, where  $X_0$  is the least significant bit and  $X_{n-1}$  is the most significant bit, then the values of X and Y are defined as:

$$X = -x_{n-1} * 2^{n-1} + \sum_{j=0}^{n-2} x_j * 2^j$$

$$Y = -y_{n-1} * 2^{n-1} + \sum_{i=0}^{n-2} y_i * 2^i$$

(2.1)

$$Y = -y_{n-1} * 2^{n-1} + \sum_{i=0}^{n-2} y_i * 2^i$$

(2.2)

and their product XY is equal to:

$$XY = \left(-x_{n-1} * 2^{n-1} + \sum_{j=0}^{n-2} x_j * 2^j\right) \tag{2.3}$$

\*

$$(-y_{n-1} * 2^{n-1} + \sum_{i=0}^{n-2} y_i * 2^i)$$

(2.4)

This product can be written as a sum of four terms:  $Term_1$ ,  $Term_2$ ,  $Term_3$  and  $Term_4$ , which are defined as follows:

$$Term_{1} = (-x_{n-1} * 2^{n-1}) * (-y_{n-1} * 2^{n-1})$$

$$Term_{2} = (-x_{n-1} * 2^{n-1}) * \left(\sum_{i=0}^{n-2} y_{i} * 2^{i}\right)$$

$$Term_{3} = (-y_{n-1} * 2^{n-1}) * \left(\sum_{j=0}^{n-2} x_{j} * 2^{j}\right)$$

$$Term_{4} = \left(\sum_{j=0}^{n-2} x_{j} * 2^{j}\right) * \left(\sum_{i=0}^{n-2} y_{i} * 2^{i}\right)$$

$$(2.5)$$

The four terms can be rewritten as:

$$Term_{1} = x_{n-1}y_{n-1} * 2^{2n-2}$$

$$Term_{2} = -2^{n-1} * \sum_{i=0}^{n-2} x_{n-1}y_{i} * 2^{i}$$

$$Term_{3} = -2^{n-1} * \sum_{j=0}^{n-2} y_{n-1}x_{j} * 2^{j}$$

$$Term_{4} = \sum_{i=0}^{n-2} \sum_{j=0}^{n-2} x_{j}y_{i} * 2^{j+i}$$

(2.6)

The result of the multiplication of two n-bit two's complement numbers is a 2n-bit two's complement number. It can be observed that  $Term_2$  and  $Term_3$  are negative. This is detrimental to a hardware implementation as it is required to perform element subtractions. While it is possible to be achieved, it requires multiple cell designs [40]. Baugh and Wooley [75] introduced an algorithm which requires no element subtraction. Given that in our investigation we will

also introduce an algorithm that contains no element subtraction we discuss for background purposes a modification of the Baugh-Wooley algorithm in this section.

Baugh and Wooley [75] indicate that instead of subtracting a partial product, the negation of this partial product can be added. The negative partial product rows can be converted to positive elements rows via the addition of  $2^n$  and truncation. As the result of the multiplication is a 2n bit result, the  $2^n$  constant is truncated in the final steps and therefore it doesn't influence the result.

More in particular, the negative elements elimination is achieved as follows. The negative  $Term_2$

$$Term_2 = -2^{n-1} \sum_{i=0}^{n-2} x_{n-1} y_i * 2^i$$

(2.7)

can be rewritten to a positive term by adding  $2^n$ :

$$2^{2n} + Term_{2} = 2^{2n} - 2^{n-1} \sum_{i=0}^{n-2} x_{n-1} y_{i} * 2^{i}$$

$$= 2^{n-1} \left( 2^{n+1} - \sum_{i=0}^{n-2} x_{n-1} y_{i} * 2^{i} \right)$$

$$= 2^{n-1} \left( 2^{n} + 2^{n-1} + 1 + \sum_{i=0}^{n-2} 2^{i} - \sum_{i=0}^{n-2} x_{n-1} y_{i} * 2^{i} \right)$$

$$= 2^{n-1} \left( 2^{n} + 2^{n-1} + 1 + \sum_{i=0}^{n-2} (2^{i} - x_{n-1} y_{i} * 2^{i}) \right)$$

$$= 2^{n-1} \left( 2^{n} + 2^{n-1} + 1 + \sum_{i=0}^{n-2} (1 - x_{n-1} y_{i}) * 2^{i} \right)$$

$$= 2^{n-1} \left( 2^{n} + 2^{n-1} + 1 + \sum_{i=0}^{n-2} \overline{x_{n-1} y_{i}} * 2^{i} \right)$$

$$= 2^{n-1} \left( 2^{n} + 2^{n-1} + 1 + \sum_{i=0}^{n-2} \overline{x_{n-1} y_{i}} * 2^{i} \right)$$

$$= 2^{n-1} \left( 2^{n} + 2^{n-1} + 1 + \sum_{i=0}^{n-2} \overline{x_{n-1} y_{i}} * 2^{i} \right)$$

$$= 2^{n-1} \left( 2^{n} + 2^{n-1} + 1 + \sum_{i=0}^{n-2} \overline{x_{n-1} y_{i}} * 2^{i} \right)$$

$$= 2^{n-1} \left( 2^{n} + 2^{n-1} + 1 + \sum_{i=0}^{n-2} \overline{x_{n-1} y_{i}} * 2^{i} \right)$$

$$= 2^{n-1} \left( 2^{n} + 2^{n-1} + 1 + \sum_{i=0}^{n-2} \overline{x_{n-1} y_{i}} * 2^{i} \right)$$

$$= 2^{n-1} \left( 2^{n} + 2^{n-1} + 1 + \sum_{i=0}^{n-2} \overline{x_{n-1} y_{i}} * 2^{i} \right)$$

$$= 2^{n-1} \left( 2^{n} + 2^{n-1} + 1 + \sum_{i=0}^{n-2} \overline{x_{n-1} y_{i}} * 2^{i} \right)$$

$$= 2^{n-1} \left( 2^{n} + 2^{n-1} + 1 + \sum_{i=0}^{n-2} \overline{x_{n-1} y_{i}} * 2^{i} \right)$$

$$= 2^{n-1} \left( 2^{n} + 2^{n-1} + 1 + \sum_{i=0}^{n-2} \overline{x_{n-1} y_{i}} * 2^{i} \right)$$

This means that the negative  $Term_2$  can be replaced with the following positive equivalent:

$$Term_2 = 2^{n-1} \left( 2^n + 2^{n-1} + 1 + \sum_{i=0}^{n-2} \overline{x_{n-1} y_i} * 2^i \right)$$

(2.9)

$Term_3$  can be treated in the same way:

$$Term_3 = 2^{n-1} \left( 2^n + 2^{n-1} + 1 + \sum_{j=0}^{n-2} \overline{y_{n-1} x_j} * 2^j \right)$$

(2.10)

From this point, our approach differs from Baugh and Wooley's. While their goal was to make a multiplication structure with the highest possible regularity, they had to eliminate the NAND function required for  $Term_2$  and  $Term_3$ . Our goal is to minimize the number of terms to be added together. Therefore, we try to eliminate as much constants as possible by adding them together beforehand.

If we add the constant part of 2.9 and 2.10, we get:

$$Term_2$$

\_Constant =  $2^{n-1} (2^n + 2^{n-1} + 1)$

$Term_3$ \_Constant =  $2^{n-1} (2^n + 2^{n-1} + 1)$  +

$Term_{2,3}$ \_Constant =  $2^{2n} + 2^{2n-1} + 2^n$  (2.11)

where  $2^{2n}$  is the carry-out of the addition, which can be ignored.

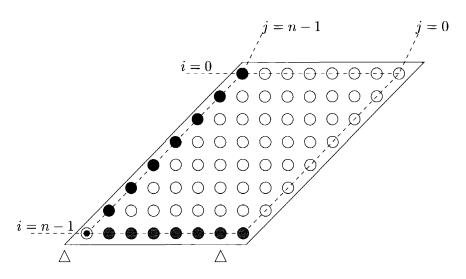

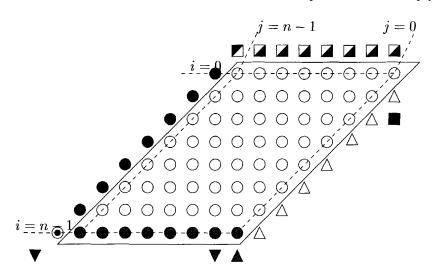

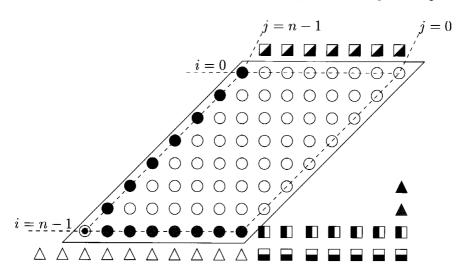

The end effect is that we have to invert two times n-1 bits, and add two single hot ones: on position n and on position 2n-1. Figure 2.2 shows a graphical representation of this multiplication. The white 'dots' and the 'dot' in the lower left corner are the normal multiplication bits,  $x_jy_i$ . The black and gray 'dots' are the inverted partial products,  $\overline{x_jy_i}$  and the two hot-ones are represented as two triangles. As we can see from the figure, the number of rows to be reduced equals n, the number of bits of the input numbers.

In this section we discussed the well known Baugh-Wooley algorithm [75]. This algorithm provides the capability of eliminating negative elements for the multiplication matrix, in order to avoid irregularities from these negative elements in the the partial product reduction hardware. In next section we describe two techniques, called inversion selection and half adder encoding for computing  $(A \pm B) * C \pm D$ . Both of them consist of two steps and use similar derivations of the Baugh-Wooley algorithm discussed previously. In the first step the partial products from  $(A \pm B) * C$  are computed. Those partial products are added together with D to produce  $(A \pm B) * C \pm D$  in the second step. The aim of both schemes is to provide a low-latency, hardwired unit with relatively modest hardware requirements, that computes  $(A \pm B) * C \pm D$  in the same time required by a normal multiply.

21

- $\odot$   $Term_1$ , which is inverted twice

- $\bullet$   $Term_2$ , which is inverted

- Term<sub>3</sub>, which also is inverted

- $\bigcirc$  Term<sub>4</sub>, the normal multiplication bits

- ∧ The combined constants

Figure 2.2: Graphical representation of a normal multiplication.

### 2.3 Inversion-selection

The inversion-selection-technique is based on the fact that in the two's complement notation -X is almost equal to  $\overline{X}$  (to be precise:  $-X = \overline{X} + 1$ ).

We rewrite the  $(A \pm B) * C$  so that we compute it with  $A * C + B * \overline{C}$  (or  $A * C + \overline{B} * \overline{C}$ ), in which the bits of C choose between passing the bits of A or  $B(\overline{B})$ .

As an example, we will compute (A - B) \* C. We can do so by rewriting it to:

$$(A - B) * C = A * C - B * C$$

(2.12)

$$= A * C + B * (-C) \tag{2.13}$$

In this last equation, we use the two's complement rule in that we rewrite -C as  $\overline{C}+1$ . The hot one is not added directly in this case. This makes

$$(A - B) * C = A * C + B * (\overline{C} + 1)$$

(2.14)

$$(A-B) * C = A * C + B * \overline{C} + B$$

$$(2.15)$$

This means that for each bit of C, we have to add either A (if the bit of C is one) or B (if it is zero) to the partial product matrix, in stead of both or neither of them. C is used as a select signal to choose between them.

Normally, if a certain bit of C is one, we would have to feed A and -B to the partial product matrix on that position. If that bit would have been zero, we would have to add nothing. The maximum number of partial product rows would be equal to two times the number of bits of C. In our scheme, each row is always filled with either A or B, and the number of rows equals the number of bits of C and one extra row for B.

We will now rewrite the four instances of  $(A \pm B) * C \pm D$  so that they fit this scheme.

Depending on the operation, there are four instances of the expression  $(A \ oper_1 \ B) * C \ oper_2 \ D$ . These are shown below:

1)

$$oper_1 = +$$

and  $oper_2 = +$   $(op_1 = 0; op_2 = 0)$

$(A+B)*C+D = A*C+B*C+D$

$= A*C+(-B)*(-C)+D$

$= A*C+(\overline{B}+1)*(\overline{C}+1)+D$

$= A*C+\overline{B}*\overline{C}+\overline{B}+\overline{C}+D+1$  (2.16)

2)

$$oper_1 = +$$

and  $oper_2 = (op_1 = 0; op_2 = 1)$

$(A + B) * C - D = A * C + B * C - D$

$= A * C + (-B) * (-C) - D$

$= A * C + (\overline{B} + 1) * (\overline{C} + 1) + (\overline{D} + 1)$

$= A * C + \overline{B} * \overline{C} + \overline{B} + \overline{C} + \overline{D} + 2$  (2.17)

3)

$$oper_1 = -$$

and  $oper_2 = +$   $(op_1 = 1; op_2 = 0)$

$(A - B) * C + D = A * C - B * C + D$

$= A * C + B * (\overline{C} + 1) + D$

$= A * C + B * \overline{C} + B + D$  (2.18)

23

4)

$$oper_1 = -$$

and  $oper_2 = (op_1 = 1; op_2 = 1)$

$(A - B) * C - D = A * C - B * C - D$

$= A * C + B * (\overline{C} + 1) + (\overline{D} + 1)$

$= A * C + B * \overline{C} + B + \overline{D} + 1$  (2.19)

All the instances are summarized in Table 2.2. In the Table  $op_1$  and  $op_2$  (the operations) are the control signals to the hardware to indicate what needs to be computed. Equal to zero implies addition and equal to one implies subtraction.

The four instances can be combined into a single expression as follows:

$$(A \ oper_1 \ B) * C \ oper_2 \ D =$$

$$A * C + \widehat{B} * \overline{C} + \widehat{B} + \widehat{C} + \widehat{D} + \overline{op_1} + op_2$$

(2.20)

in which  $\widehat{B}=B\oplus \overline{op_1}$ ,  $\widehat{C}=\overline{C}\ \&\ \overline{op_1}$  and  $\widehat{D}=D\oplus op_2$ . The computation

| $op_1$ | $op_2$ | expression    | expression used for the                                                                |  |  |

|--------|--------|---------------|----------------------------------------------------------------------------------------|--|--|

|        |        |               | Inversion Selection Technique                                                          |  |  |

| 0      | 0      | (A+B)*C+D     | $A * C + \overline{B} * \overline{C} + \overline{B} + \overline{C} + \overline{D} + 1$ |  |  |

| 0      | 1      | (A+B)*C-D     | $A*C+\overline{B}*\overline{C}+\overline{B}+\overline{C}+\overline{D}+2$               |  |  |

| 1      | 0      | (A-B)*C+D     | $A * C + B * \overline{C} + B + D$                                                     |  |  |

| 1      | 1      | (A-B) * C - D | $A * C + B * \overline{C} + B + \overline{D} + 1$                                      |  |  |

**Table 2.2:** The possible operations used for the Inversion-Selection Technique.

of the expression 2.20 can be split in two parts. The first part is generating the partial products and correction-terms (correction-terms are needed to avoid negative elements). The second part is summing up the partial products and the correction-terms. We first concentrate on producing the partial products.

First we compute  $A*C+\widehat{B}*\overline{C}$ . This is achieved by two multiplications and an addition. It can immediately be noted that if a certain bit in C is 1 then the corresponding bit in  $\overline{C}$  is 0, and vice versa. This implies that in generating the partial products certain eliminations of bits can be carried out. This indicates that a combined matrix can be generated directly and eliminates the hardware requirements for one of the two multiplications and the addition.

The same scheme that is used for the multiplication of X and Y, (formulas 2.5 through 2.11) can be used for computing  $A*C+\widehat{B}*\overline{C}$ . We simply compute both terms of the sum and add them together. The four terms, which were used in Section 2.2 can be computed as follows:

$$Term_{1} = (-c_{n-1} * 2^{n-1}) * (-a_{n-1} * 2^{n-1})$$

$$+ (-\overline{c_{n-1}} * 2^{n-1}) * (-\widehat{b_{n-1}} * 2^{n-1})$$

$$= c_{n-1} * a_{n-1} * 2^{2n-2} + \overline{c_{n-1}} * \widehat{b_{n-1}} * 2^{2n-2}$$

$$= (c_{n-1} * a_{n-1} + \overline{c_{n-1}} * \widehat{b_{n-1}}) * 2^{2n-2}$$

$$= (c_{n-1} \& a_{n-1} | \overline{c_{n-1}} \& \widehat{b_{n-1}}) * 2^{2n-2}$$

$$(2.21)$$

The \* between c and a and between  $\overline{c}$  and  $\widehat{b}$  (bitwise multiplication) is equivalent to the AND (&) operator, and the + (arithmetic addition) is equivalent to the OR (|) operator, because either  $c_{n-1}$  or  $\overline{c_{n-1}}$  is equal to zero.

$$Term_{2} = (-a_{n-1} * 2^{n-1}) * \left( \sum_{i=0}^{n-2} c_{i} * 2^{i} \right) + (-\widehat{b_{n-1}} * 2^{n-1}) * \left( \sum_{i=0}^{n-2} \overline{c_{i}} * 2^{i} \right)$$

$$= -2^{n-1} * \sum_{i=0}^{n-2} a_{n-1} * c_{i} * 2^{i} - 2^{n-1} * \sum_{i=0}^{n-2} \widehat{b_{n-1}} * \overline{c_{i}} * 2^{i}$$

$$= -2^{n-1} * \sum_{i=0}^{n-2} \left( a_{n-1} * c_{i} * 2^{i} + \widehat{b_{n-1}} * \overline{c_{i}} * 2^{i} \right)$$

$$= -2^{n-1} * \sum_{i=0}^{n-2} \left( c_{i} \& a_{n-1} | \overline{c_{i}} \& \widehat{b_{n-1}} \right) * 2^{i}$$

$$(2.22)$$

$$Term_{3} = (-c_{n-1} * 2^{n-1}) * \left( \sum_{j=0}^{n-2} a_{j} * 2^{j} \right) + (-\overline{c_{n-1}} * 2^{n-1}) * \left( \sum_{j=0}^{n-2} \widehat{b_{j}} * 2^{j} \right)$$

$$= -2^{n-1} * \sum_{j=0}^{n-2} c_{n-1} * a_{j} * 2^{j} - 2^{n-1} * \sum_{j=0}^{n-2} \overline{c_{n-1}} * \widehat{b_{j}} * 2^{j}$$

$$= -2^{n-1} * \sum_{j=0}^{n-2} \left( c_{n-1} * a_{j} * 2^{j} + \overline{c_{n-1}} * \widehat{b_{j}} * 2^{j} \right)$$

$$= -2^{n-1} * \sum_{j=0}^{n-2} \left( c_{n-1} \& a_{j} | \overline{c_{n-1}} \& \widehat{b_{j}} \right) * 2^{j}$$

$$(2.23)$$

$$Term_{4} = \left(\sum_{j=0}^{n-2} a_{j} * 2^{j}\right) * \left(\sum_{i=0}^{n-2} c_{i} * 2^{i}\right)$$

$$+ \left(\sum_{j=0}^{n-2} \widehat{b}_{j} * 2^{j}\right) * \left(\sum_{i=0}^{n-2} \overline{c_{i}} * 2^{i}\right)$$

$$= \sum_{j=0}^{n-2} \sum_{i=0}^{n-2} a_{j} * c_{i} * 2^{i+j} + \sum_{j=0}^{n-2} \sum_{i=0}^{n-2} \widehat{b}_{j} * \overline{c_{i}} * 2^{i+j}$$

$$= \sum_{j=0}^{n-2} \sum_{i=0}^{n-2} (a_{j} * c_{i} + \widehat{b}_{j} * \overline{c_{i}}) * 2^{i+j}$$

$$= \sum_{j=0}^{n-2} \sum_{i=0}^{n-2} (c_{i} \& a_{j} | \overline{c_{i}} \& \widehat{b_{j}}) * 2^{i+j}$$

$$(2.24)$$

It should be noted that the terms involved in the computation of  $A*C+\widehat{B}*\overline{C}$  are similar to the terms involved in the computation of X\*Y. The main difference is the use of a 2-input MUX instead of a 2-input AND (using the bit of C to select between A and  $\widehat{B}$ ).

As the addition of negative terms introduces irregularities in the partial product reduction logic, we are are interested in eliminating the negative elements  $(Term_2 \text{ and } Term_3)$ . We modify these terms to positive using the fact that all computations are done in two's complement. Because the result is 2n+1 bits wide,  $N^-=2^{2n+1}-N$ .

$$Term_{2} = 2^{2n+1} - 2^{n-1} * \sum_{i=0}^{n-2} (c_{i} \& a_{n-1} | \overline{c_{i}} \& \widehat{b_{n-1}}) * 2^{i}$$

$$= 2^{n-1} * \left( 2^{n+2} - \sum_{i=0}^{n-2} (c_{i} \& a_{n-1} | \overline{c_{i}} \& \widehat{b_{n-1}}) * 2^{i} \right)$$

$$= 2^{n-1} * \left( \sum_{i=n-1}^{n+1} 2^{i} + \sum_{i=0}^{n-2} 2^{i} + 1 - \sum_{i=0}^{n-2} (c_{i} \& a_{n-1} | \overline{c_{i}} \& \widehat{b_{n-1}}) * 2^{i} \right)$$

$$= 2^{n-1} * \left( \sum_{i=n-1}^{n+1} 2^{i} + 1 + \sum_{i=0}^{n-2} (1 - c_{i} \& a_{n-1} | \overline{c_{i}} \& \widehat{b_{n-1}}) * 2^{i} \right)$$

$$= 2^{n-1} * \left( \sum_{i=n-1}^{n+1} 2^{i} + 1 + \sum_{i=0}^{n-2} (\overline{c_{i}} \& a_{n-1} | \overline{c_{i}} \& \widehat{b_{n-1}}) * 2^{i} \right)$$

$$= 2^{n-1} * \left( \sum_{i=n-1}^{n+1} 2^{i} + 1 + \sum_{i=0}^{n-2} (\overline{c_{i}} \& a_{n-1} | \overline{c_{i}} \& \widehat{b_{n-1}}) * 2^{i} \right)$$

$$= 2^{n-1} * \left( \sum_{i=n-1}^{n+1} 2^{i} + 1 + \sum_{i=0}^{n-2} (\overline{c_{i}} \& a_{n-1} | \overline{c_{i}} \& \widehat{b_{n-1}}) * 2^{i} \right)$$

$$= 2^{n-1} * \left( \sum_{i=n-1}^{n+1} 2^{i} + 1 + \sum_{i=0}^{n-2} (\overline{c_{i}} \& a_{n-1} | \overline{c_{i}} \& \widehat{b_{n-1}}) * 2^{i} \right)$$

$$= 2^{n-1} * \left( \sum_{i=n-1}^{n+1} 2^{i} + 1 + \sum_{i=0}^{n-2} (\overline{c_{i}} \& a_{n-1} | \overline{c_{i}} \& \widehat{b_{n-1}}) * 2^{i} \right)$$

$$= 2^{n-1} * \left( \sum_{i=n-1}^{n+1} 2^{i} + 1 + \sum_{i=0}^{n-2} (\overline{c_{i}} \& a_{n-1} | \overline{c_{i}} \& \widehat{b_{n-1}}) * 2^{i} \right)$$

$$= 2^{n-1} * \left( \sum_{i=n-1}^{n+1} 2^{i} + 1 + \sum_{i=0}^{n-2} (\overline{c_{i}} \& a_{n-1} | \overline{c_{i}} \& \widehat{b_{n-1}}) * 2^{i} \right)$$

$$= 2^{n-1} * \left( \sum_{i=n-1}^{n+1} 2^{i} + 1 + \sum_{i=0}^{n-2} (\overline{c_{i}} \& a_{n-1} | \overline{c_{i}} \& \widehat{b_{n-1}}) * 2^{i} \right)$$

And in the same way:

$$Term_{3} = 2^{2n+1} - 2^{n-1} * \sum_{j=0}^{n-2} (c_{n-1} \& a_{j} | \overline{c_{n-1}} \& \widehat{b_{j}}) * 2^{j}$$

$$= 2^{n-1} * \left( \sum_{j=n-1}^{n+1} 2^{j} + 1 + \sum_{j=0}^{n-2} \overline{(c_{n-1} \& a_{j} | \overline{c_{n-1}} \& \widehat{b_{j}})} * 2^{i} \right)$$

(2.26)

Consequently the total multiplication  $A * C + \widehat{B} * \overline{C}$  can be computed as:

$$A * C + \widehat{B} * \overline{C} = (c_{n-1} \& a_{n-1} | \overline{c_{n-1}} \& \widehat{b_{n-1}}) * 2^{2n-2}$$

$$+ 2^{n-1} * \left( \sum_{i=n-1}^{n+1} 2^{i} + 1 + \sum_{i=0}^{n-2} \overline{(c_{i} \& a_{n-1} | \overline{c_{i}} \& \widehat{b_{n-1}})} * 2^{i} \right)$$

$$+ 2^{n-1} * \left( \sum_{j=n-1}^{n+1} 2^{j} + 1 + \sum_{j=0}^{n-2} \overline{(c_{n-1} \& a_{j} | \overline{c_{n-1}} \& \widehat{b_{j}})} * 2^{i} \right)$$

$$+ \sum_{i=0}^{n-2} \sum_{i=0}^{n-2} (c_{i} \& a_{j} | \overline{c_{i}} \& \widehat{b_{j}}) * 2^{i+j}$$

$$(2.27)$$

If we group all constants from the above equation:

$$A * C + \widehat{B} * \overline{C} = (c_{n-1} \& a_{n-1} | \overline{c_{n-1}} \& \widehat{b_{n-1}}) * 2^{2n-2}$$

$$+ 2^{n-1} * \sum_{i=0}^{n-2} \overline{(c_i \& a_{n-1} | \overline{c_i} \& \widehat{b_{n-1}})} * 2^i$$

$$+ 2^{n-1} * \sum_{j=0}^{n-2} \overline{(c_{n-1} \& a_j | \overline{c_{n-1}} \& \widehat{b_j})} * 2^j$$

$$+ \sum_{j=0}^{n-2} \sum_{i=0}^{n-2} (c_i \& a_j | \overline{c_i} \& \widehat{b_j}) * 2^{i+j}$$

$$+ 2^n * \left(1 + \sum_{i=n-1}^{n+1} 2^i\right)$$

(2.28)

If we rewrite this last term using the fact that all computations are done modulo

$2^{2n+1}$ , we get:

$$2^{n} * \left(1 + \sum_{i=n-1}^{n+1} 2^{i}\right) = 2^{n} + 2^{n} * \sum_{i=n-1}^{n+1} 2^{i}$$

$$= 2^{n} + 2^{2n-1} + 2^{2n} + 2^{2n+1}$$

$$= 2^{n} + 2^{2n-1} + 2^{2n}$$

(2.29)

In order to compute  $(A \pm B) * C \pm D$  we have to add  $\widehat{B}$ ,  $\widehat{C}$ ,  $\widehat{D}$ ,  $\overline{op_1}$  and  $op_2$  to 2.28, as derived in 2.20.

The three constants,  $(2^{2n}, 2^{2n-1} \text{ and } 2^n)$ , and the negative sign bits of  $\widehat{B}$ ,  $\widehat{C}$  and  $\widehat{D}$  (on position  $2^{n-1}$ ) can easily be combined to a single bit-string according to Table 2.3 and 2.4.

| Hot_ones $-\sum (\widehat{b_{n-1}},\widehat{c_{n-1}},\widehat{d_{n-1}})$ | = | result                            |

|--------------------------------------------------------------------------|---|-----------------------------------|

| $2^{2n} + 2^{2n-1} + 2^n - 0 * 2^{n-1}$                                  |   | $2^{2n} + 2^{2n-1} + 2 * 2^{n-1}$ |

| $2^{2n} + 2^{2n-1} + 2^n - 1 * 2^{n-1}$                                  |   | $2^{2n} + 2^{2n-1} + 1 * 2^{n-1}$ |

| $2^{2n} + 2^{2n-1} + 2^n - 2 * 2^{n-1}$                                  |   | $2^{2n} + 2^{2n-1} + 0 * 2^{n-1}$ |

| $2^{2n} + 2^{2n-1} + 2^n - 3 * 2^{n-1}$                                  | = | $2^{2n} + 2^{2n-1} - 1 * 2^{n-1}$ |

**Table 2.3:** Summing up the hot ones

| Result                            | $\overline{Bit_{2n}}$ | $\overline{Bit}_{2n-1}$ | $Bit_{2n-2}$ | $Bit_n$ | $Bit_{n-1}$ |

|-----------------------------------|-----------------------|-------------------------|--------------|---------|-------------|

|                                   |                       |                         | $Bit_{n+1}$  |         |             |

| $2^{2n} + 2^{2n-1} + 2 * 2^{n-1}$ | 1                     | 1                       | 0            | 1       | 0           |

| $2^{2n} + 2^{2n-1} + 1 * 2^{n-1}$ | 1                     | 1                       | 0            | 0       | 1           |

| $2^{2n} + 2^{2n-1} + 0 * 2^{n-1}$ | 1                     | 1                       | 0            | 0       | 0           |

| $2^{2n} + 2^{2n-1} - 1 * 2^{n-1}$ | 1                     | 0                       | 1            | 1       | 1           |

Table 2.4: The bit-string resulting from the hot-ones and the sign-bits.

From Table 2.4 we can derive the formulas for these bits.

$$Bit_{n-1} = \widehat{b_{n-1}} \oplus \widehat{c_{n-1}} \oplus \widehat{d_{n-1}}$$

$$Bit_{n} = \widehat{b_{n-1}} \& \widehat{c_{n-1}} \& \widehat{d_{n-1}} | \widehat{b_{n-1}} \& \widehat{c_{n-1}} \& \widehat{d_{n-1}}$$

$$Bit_{n+1} .. Bit_{2n-2} = \widehat{b_{n-1}} \& \widehat{c_{n-1}} \& \widehat{d_{n-1}}$$

$$Bit_{2n-1} = \widehat{b_{n-1}} \& \widehat{c_{n-1}} \& \widehat{d_{n-1}}$$

$$Bit_{2n} = 1$$

(2.30)

The block realizing these formula's (2.30) is as complex as a full-adder.

#### 2.3.1 Putting the pieces together

The complete formula is as follows:

$$(A \ oper_1 \ B) * C \ oper_2 \ D$$

$$= A * C + \widehat{B} * \overline{C} + \widehat{B} + \widehat{C} + \widehat{D} + \overline{op_1} + op_2$$

$$= (c_{n-1} \& a_{n-1} | \overline{c_{n-1}} \& \widehat{b_{n-1}}) * 2^{2n-2}$$

$$+ 2^{n-1} * \sum_{i=0}^{n-2} \overline{(c_i \& a_{n-1} | \overline{c_i} \& \widehat{b_{n-1}})} * 2^i$$

$$+ 2^{n-1} * \sum_{j=0}^{n-2} \overline{(c_{n-1} \& a_j | \overline{c_{n-1}} \& \widehat{b_j})} * 2^j$$

$$+ \sum_{j=0}^{n-2} \sum_{i=0}^{n-2} (c_i \& a_j | \overline{c_i} \& \widehat{b_j}) * 2^{i+j}$$

$$+ \sum_{i=0}^{n-2} (\widehat{b_i} * 2^i) + \sum_{i=0}^{n-2} (\widehat{c_i} * 2^i) + \sum_{i=0}^{n-2} (\widehat{d_i} * 2^i)$$

$$+ \overline{op_1} + op_2 + \sum_{i=n-1}^{2n} Bit_i * 2^i$$

$$(2.31)$$

Where the term  $\sum Bit_i * 2^i$  is defined in 2.30. If we re-arrange the terms we get:

$$(A \ oper_1 \ B) * C \ oper_2 \ D$$

$$= A * C + \widehat{B} * \overline{C} + \widehat{B} + \widehat{C} + \widehat{D} + \overline{op_1} + op_2$$

$$= \sum_{j=0}^{n-2} \sum_{i=0}^{n-2} (c_i \& a_j | \overline{c_i} \& \widehat{b_j}) * 2^{i+j}$$

$$+2^{2n-2} * (c_{n-1} \& a_{n-1} | \overline{c_{n-1}} \& \widehat{b_{n-1}})$$

$$+2^{n-1} * \sum_{i=0}^{n-2} \overline{(c_i \& a_{n-1} | \overline{c_i} \& \widehat{b_{n-1}})} * 2^i$$

$$+2^{n-1} * \sum_{j=0}^{n-2} \overline{(c_{n-1} \& a_j | \overline{c_{n-1}} \& \widehat{b_j})} * 2^j$$

$$+2^{n-1} * \sum_{i=n-1}^{2n} Bit_i * 2^{i-n+1}$$

$$+\sum_{i=0}^{n-2} (\widehat{b_i} * 2^i) + \sum_{i=0}^{n-2} (\widehat{c_i} * 2^i) + \sum_{i=0}^{n-2} (\widehat{d_i} * 2^i)$$

$$+\overline{op_1} + op_2$$

(2.32)

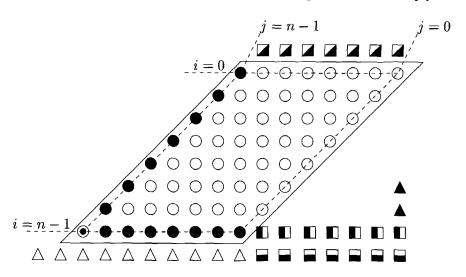

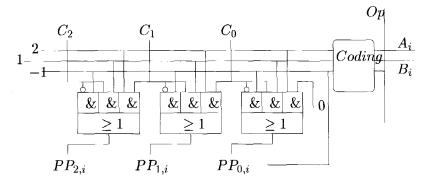

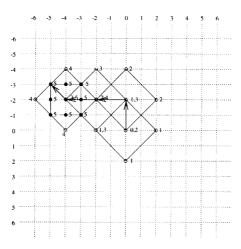

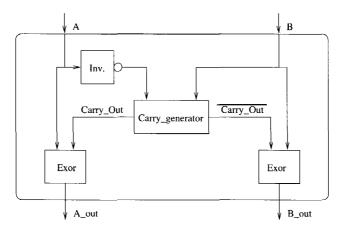

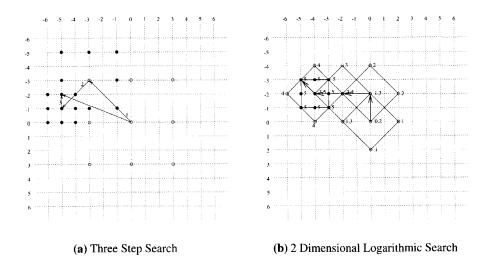

Figure 2.3 shows a graphical representation of the Inversion Selection Technique. The dot in the lower right corner represents the first term in the above Equation (2.31). The second and third term, the inverted partial products, are indicated with black and gray dots, while the white dots represent the fourth term. The white triangles form the correction term  $Bit_x$ . The black and gray triangles are correction terms, resulting from negation of  $B(\overline{op})$  and  $D(op_2)$ . The squares represent the positive elements of  $\widehat{D}$  and the two correction terms  $\widehat{B}$  and  $\widehat{C}$ .

As can be seen in figure 2.3, all the components of the matrix form a compact structure, which can be reduced using counters. See for example [76]. The Figure shows that there are are only two extra rows required for the Add-Multiply-Add when compared to the normal multiply depicted in Figure 2.2. As setting up the partial products is not more complicated than setting up the partial products of a normal multiply, we conclude that this design will require the same execution time as a normal multiply.

Inversion selection technique remarks: In this section, we have introduced the Inversion Selection Technique. Such a technique uses the fact that the partial products generated by  $c_i * A$  and those generated by  $\overline{c_i} * B$  can be added by simply OR-ing them together. This technique results in n+2 partial product lines, that can be summed up in an arbitrary counter structure. In the next section, the Half Adder Encoding Technique will be introduced.

- $\odot$   $Term_1$ , which is inverted twice

- $lacktriangleq Term_2$ , which is inverted

- lacktriangle  $Term_3$ , which also is inverted

- Term<sub>4</sub>, the normal multiplication bits

- $\land$  The correction element  $Bit_{2n}..Bit_{n-1}$

- $\triangle$  The first hot one depending on the operation,  $\overline{op}$

- ▲ The second hot one depending on the operation, op

- $\square$  The term  $\widehat{D} = D \oplus op_2$  (except for the sign-bit)

- $\blacksquare \quad \text{The term } \widehat{B} = B \oplus \overline{op_1} \text{ (except for the sign-bit)}$

**Figure 2.3:** Graphical representation of the Add-Multiply-Add using the Inversion-Selection Technique.

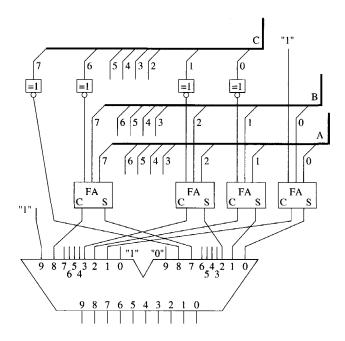

# 2.4 Half-adder encoding

Half-Adder Encoding is derived from Booth-encoding [40]. The main difference is that in the Half-Adder Encoding the "set" of bits which are coded together come from the two operands A and B. This results in n partial products, n being the number of bits of operand A and B, and n hot-ones, resulting from the possible negation of these partial products. For this technique, we add or subtract A and B on a bitwise basis. For this operation, we use a half-

adder, hence the name Half-Adder Encoding. The key-advantage of the use of a half-adder as opposed to a full-adder is the absence of a carry-signal. Earlier we derived four expressions from the add-multiply-add operation, depending on the two controlling inputs  $(op_1 \text{ and } op_2)$  which select the operation. That is the expression:

$$(A \pm B) * C \pm D = (A \ oper_1 \ B) * C \ oper_2 \ D$$

can assume one of the following: (A+B)\*C+D; (A+B)\*C-D; (A-B)\*C+D or (A-B)\*C-D representing one of the choices of  $oper_1$  and  $oper_2$ . We treat the addition/subtraction of D later, for now we only treat the add-multiply part, which has two instances:

$$(A+B)*C$$

$$(A-B)*C$$

From Equation 2.5 through 2.11 we know that the product Z of X and Y, (Z = X \* Y) in two's complement is the sum of four terms. We substitute X by C and Y by  $(A \ oper_1 \ B)$ . This yields:

$$X = C = -c_{n-1} * 2^{n-1} + \sum_{j=0}^{n-2} c_j * 2^j$$

$$Y = (A \ oper_1 \ B) =$$

$$= -(a_{n-1} \ oper_1 \ b_{n-1}) * 2^{n-1} + \sum_{i=0}^{n-2} (a_i \ oper_1 \ b_i) * 2^i \quad (2.34)$$

Since the result of  $(a_i \ oper_1 \ b_i)$  can range from -1 to +2, we have to ensure that multiplying it with C doesn't pose any problems. If C is multiplied by 2, the result will be an (n+1)-bit number. In order to keep all partial products of the same length, C has to be sign-extended by one bit. After this sign-extension, we can safely left-shift it one bit, and ignore the bit that will be shifted out. This yields  $C = -c_{n-1} * 2^n + \sum_{j=0}^{n-1} c_j * 2^j$ .

The four terms for the computation of  $(A oper_1 B) * C$  are: