**T**UDelft

# A High-Speed 40-channel USB 2.0 DAC for Adaptive Optics

by

Y.T.B. Mulder J. Romijn D.S.M. Verhaert

to obtain the degree of Bachelor of Science at the Delft University of Technology, to be defended on Tuesday June 30, 2015 at 1:30 PM.

Y.T.B. Mulder 4232755 J. Romijn 4223802 D.S.M. Verhaert 4234685

Date of submission: June 22, 2015

Project duration: April 20, 2015 – July 3, 2015

Supervisor: Prof.dr. G. Vdovin Director of Flexible Optical B.V.

Thesis committee: Prof.dr. K.L.M. Bertels TU Delft, Jury chairman

Dr.ir. J.A. Martínez Castañeda TU Delft, Jury member

Dr. S. Patlan Senior Researcher at Flexible Optical B.V.

ISBN 978-94-6186-493-2

An electronic version of this thesis is available at http://repository.tudelft.nl/.

# **Preface**

This document is the final product of our Bachelor Graduation Project at the Delft University of Technology in the Netherlands. This project is part of the three yearlong Bachelor Electrical Engineering program and has to be completed to officially receive a Bachelors degree and to be able to carry the name BSc. In this project students will show their academic capability and should be able to design an electronic system in a structured manner. The project officially started on the 20<sup>th</sup> of April and ended on the 3<sup>rd</sup> of July for a total period of 11 weeks.

The commissioner of our Bachelor Graduation Project is Prof. dr. G. Vdovin, full professor at the Delft Center for Systems and Control. He is also director of Flexible Optical B.V., a company specialized in application-oriented development of laser and high resolution imaging adaptive optics, located in Rijswijk, the Netherlands.

The main goal of this thesis is to develop a 'next generation' *digital-to-analog converter* (DAC), which is sold by Flexible Optical B.V. as part of their measurement systems. Two different implementations have been researched by a total of six electrical engineering students. These six students are divided into two groups of three students. The authors of this thesis have researched an implementation using *Universal Serial Bus* (USB) 2.0 in combination with a single 40-channel DAC chip.

The design choices and decisions regarding this implementation are described in this thesis. All subsystems of the final implementation are elaborated and their respective performance and results are shown and discussed.

Y.T.B. Mulder J. Romijn D.S.M. Verhaert Delft, June 2015

#### **Acknowledgements**

We would like to thank the supervisor of our project Prof. dr. G. Vdovin for commissioning the assignment. Next, we would greatly like to thank Dr. Seva Patlan, Senior Researcher at Flexible Optical B.V., for meeting with us on a weekly basis and supplying us with components and knowledge. We would like to thank TransIP for sponsoring and supplying us with a server and we would also like to thank our team members: Laurens van Dam, Sander van Dijk, and Michel van der Kaay. Their positive mindset, discussion skills, and support were very valuable. Lastly, we would like to thank A.C. van Dijk from ADAS Automatisering, dr. ir. A.J. van Genderen, and dr. E.J.H. Mulder for reviewing this thesis and the European Organisation for Astronomical Research in the Southern Hemisphere for supplying us with the wonderful cover photo [1].

# **Abstract**

In this project, a USB DAC was designed. This was done according to a proposal from Flexible Optical B.V. which is located in Rijswijk. This device is used to correct for atmospheric interference in optical measurement systems. The existing DAC is ten years old and needs to be updated to requirements of today. The 'next generation' DAC has been researched in-depth to see if the demanded requirements could be met. The design is divided into four subsystems: USB, controller, DAC, and power regulation and components have been chosen accordingly.

Research showed that it was impossible to achieve the requested refresh rate with USB 2.0. The requirements were therefore altered to accommodate this shortcoming of USB 2.0, since a working prototype was more desirable than a faster product.

The decision was then made to use a combo-unit that handles both the USB and the controller subsystem. For the DAC subsystem a single 40-channel DAC chip with a resolution of 16 bits was chosen. According to the needs of the other subsystems, a power regulation subsystem was designed.

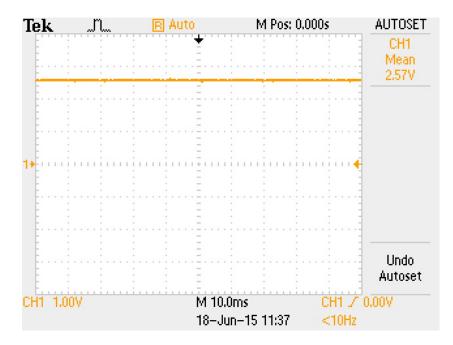

The entire system was first tested on a breadboard. This was used for prototyping and initial measurements. These measurement results did not fully comply with the requirements and adjustments had to be made. With these adjustments eventually all of the requirements have been fulfilled.

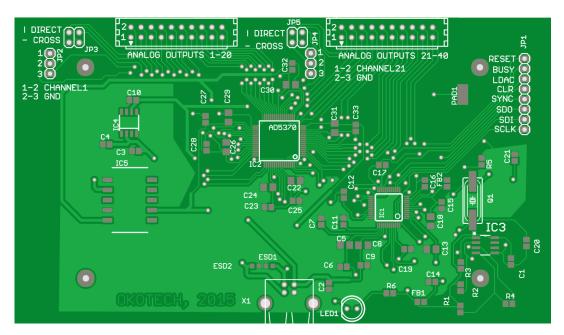

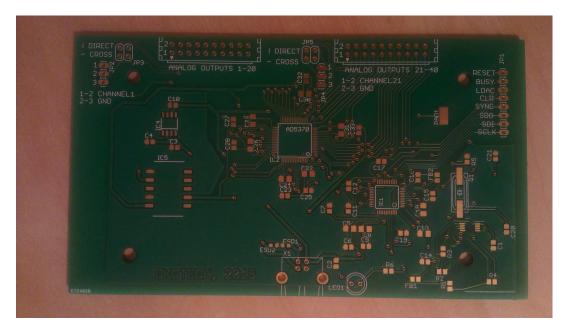

To finalize the design and create a more stable and consistent design, a printed circuit board was designed and manufactured by Eurocircuits. However, it was not manufactured in time, and therefore no results regarding the printed circuit board are presented in this thesis.

There are still some measurements that need to be done to ensure that all requirements are met. The printed circuit board design can still be improved upon to reduce distortion and increase its compactness. Furthermore, pick and place files should be made to make the manufacturing more efficient and other accommodating documents and files should still be finished for a final, market-ready product.

# Contents

| Pr | eface                                                     | €                                                                      |                                                                                                                                                                                                                                                  | iii                                          |

|----|-----------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Αŀ | ostra                                                     | ct                                                                     |                                                                                                                                                                                                                                                  | ٧                                            |

| 1  | Intro                                                     | oductio                                                                | on                                                                                                                                                                                                                                               | 1                                            |

| 2  | 2.1                                                       | Existin<br>Progra<br>2.2.1                                             | efinition  ng Product  am of Requirements  Demanded Specifications  Demanded Documents and Files                                                                                                                                                 | 4<br>4                                       |

| 3  | Res                                                       | earch                                                                  |                                                                                                                                                                                                                                                  | 7                                            |

|    | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul> | Univer 3.2.1 3.2.2 3.2.3 3.2.4 Contro 3.3.1 3.3.2 3.3.3 3.3.4          | m Overview rsal Serial Bus Subsystem Speed Transfer types USB Power Concluding Remarks coller Subsystem Controller Input Protocol Control Signals Concluding Remarks I-to-Analog Converter Subsystem Delta-Sigma DACs Pulse-Width Modulated DACs | 8                                            |

|    | 3.5                                                       | 3.4.3<br>3.4.4<br>Power<br>3.5.1<br>3.5.2<br>3.5.3                     | Resistive DACs . Concluding Remarks . Regulation Subsystem . Power Regulators . Decoupling power signals . Concluding Remarks .                                                                                                                  | 15<br>18<br>18<br>18                         |

| 4  |                                                           | lement                                                                 |                                                                                                                                                                                                                                                  | 21                                           |

|    |                                                           | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Digital<br>4.2.1<br>4.2.2<br>4.2.3 | Choice of Component Architecture Schematic I-to-Analog Converter Subsystem Requirements Choice of Component Architecture                                                                                                                         | 21<br>22<br>22<br>24<br>26<br>26<br>26<br>28 |

|    | 4.3                                                       | 4.3.1<br>4.3.2                                                         | Characteristics                                                                                                                                                                                                                                  | 32<br>33<br>33                               |

viii Contents

|   | 4.4  | 4.3.4 Schematics                      |     |

|---|------|---------------------------------------|-----|

|   | 4.5  | Software                              |     |

|   | 4.0  | 4.5.1 MPSSE                           |     |

|   |      | 4.5.2 Program overview                |     |

|   | 4.6  | Printed Circuit Board                 |     |

|   |      | 4.6.1 Schematic                       |     |

|   |      | 4.6.2 Components                      |     |

|   |      | 4.6.3 Footprints                      |     |

|   |      | 4.6.4 Component packages              |     |

|   |      | 4.6.5 Layout                          | 43  |

|   |      | 4.6.6 Tracing                         | 44  |

|   |      | 4.6.7 Grounding                       | 45  |

|   |      | 4.6.8 Finalizing the PCB              | 45  |

| 5 | Test | Process and Results                   | 47  |

| • | 5.1  | Analog Outputs                        |     |

|   | 0    | 5.1.1 Refresh Rate                    |     |

|   |      | 5.1.2 Resolution                      |     |

|   |      | 5.1.3 Output range                    |     |

|   |      | 5.1.4 Latency                         |     |

|   | 5.2  | Power                                 |     |

|   | 5.3  | Calibration                           |     |

|   | 5.4  | Software                              | 49  |

|   | 5.5  | Printed Circuit Board                 | 50  |

| 6 | Diec | ussion                                | 51  |

| ٠ | 6.1  | USB Controller Subsystem              | -   |

|   | 0    | 6.1.1 Refresh rate                    |     |

|   |      | 6.1.2 Latency                         |     |

|   | 6.2  | Digital-to-Analog Converter Subsystem |     |

|   |      | 6.2.1 Resolution                      |     |

|   |      | 6.2.2 Output Range                    |     |

|   |      | 6.2.3 Load Capacitance                | 52  |

|   | 6.3  | Power Regulation Subsystem            | 52  |

|   |      | 6.3.1 Reference Voltage               |     |

|   |      | 6.3.2 Supply Voltage                  |     |

|   |      | 6.3.3 Current Drawn                   |     |

|   | 6.4  | Software                              |     |

|   | 6.5  | Printed Circuit Board                 | 53  |

| 7 | Ethi | cal Aspects                           | 55  |

|   |      | Applications                          | 55  |

|   |      | Production Circumstances              |     |

|   | 7.3  | Restriction of Hazardous Substances   | 55  |

| 8 | Con  | clusions                              | 57  |

| U |      | Conclusions                           | _   |

|   |      | Future Work.                          |     |

|   |      |                                       |     |

|   |      |                                       | 59  |

| В | Auth | nor per Section                       | 61  |

| С | Figu |                                       | 63  |

|   | C.1  | USB Subsystem                         | 63  |

|   |      | DAC Subsystem                         | 64  |

|   | C.2  | DAC Subsystem                         | · · |

|   | C.3  | PCB                                   | 67  |

| <u> </u> | _   |

|----------|-----|

| Contents | ix  |

| COMENIS  | IX  |

|          | 1/1 |

Bibliography 77

1

# Introduction

This thesis is the result of a project conducted in the field of digital-to-analog converters, commissioned by Flexible Optical B.V. which is located in Rijswijk, the Netherlands [2]. Flexible Optical B.V. is a small company specialized in the field of application-oriented development of laser and high resolution imaging adaptive optics.

A digital-to-analog converter (DAC) is an electronic device which converts a digital signal into an analog signal, for example a current or a voltage. Digital signals can be easily manipulated, stored, and transmitted without degradation whereas analog signals can not and are used to interact with the real world; thus conversion between the two domains is necessary.

Adaptive optics is a technology to correct for optical imperfections in real-time [3]. An everyday example of adaptive optics is a continuous mode auto-focus in a digital camera. More serious applications can be found in the fields of astronomy and biological imaging, where continuous mode correction is applied using a large amount of control signals to correct for complicated aberrations. Aberrations are deviations from the ideal, which lead to reduced power efficiency or reduced resolution of the system.

Lithographic lenses used in adaptive optics provide almost aberration-free imaging and are constructed with immense precise components. However, even though this precision is so high, in the real world optical systems suffer from external parameters which can not be controlled, such as atmospheric turbulence or thermal effects. The aberrations that arise from these external parameters are called static aberrations. Correcting for these aberrations is needed and herefore a smart feedback system is used to correct the lenses. The high-speed 40-channel DAC discussed in this thesis plays a crucial role in this feedback system, since it converts the digital corrections calculated by a computer to analog signals to control the deformable mirrors. Dynamic aberrations also exist, of which defocus is one of the most simple examples. For example, the human eye needs to change focus when the distance to an object is changed. The same holds for optical systems and that is the reason for their adjustable design.

In short, adaptive optics is a rapidly growing branch of applied optics, in which the feedback system plays an ever increasing role in improving the overall performance of the system.

The 'next generation' USB DAC, which will be designed during this project, will have improved specifications over the already existing DAC developed ten years ago by Flexible Optical B.V. The main improvements compared to the existing DAC are an increased refresh rate and a higher resolution, while maintaining the same form factor.

The focus of this thesis is the structural design process and implementation of the 'next generation' DAC, in particular the USB 2.0 implementation in combination with a single 40-channel DAC chip. The problem of this thesis is defined in Chapter 2 and the conducted research is discussed in Chapter 3. The final implementation is discussed in Chapter 4, followed by the achieved results in Chapter 5. These results are discussed in Chapter 6 and Chapter 7 discusses the ethical aspects of the project. Finally, project-wide conclusions are drawn and future work is discussed in Chapter 8.

# **Problem Definition**

This chapter defines the main problem of this bachelor thesis. The existing product manufactured by Flexible Optical B.V. will be discussed, after which the program of requirements for the 'next generation' version will be summarized.

# 2.1. Existing Product

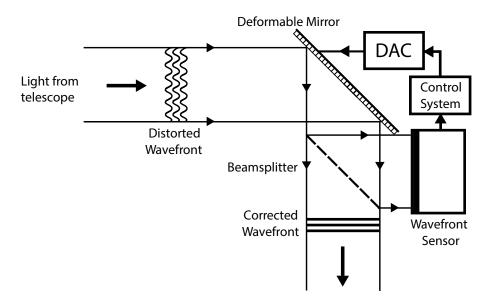

Ten years ago, Flexible Optical B.V. developed a 40-channel USB DAC. The main purpose of this USB DAC is to control deformable mirrors used in adaptive optics. A block diagram of a basic measurement setup is shown in Figure 2.1. The source signal, for example light from a telescope, transmits a signal which is prone to disturbances and results in a distorted wavefront. The wavefront is reflected off and corrected by a wavefront sensor. This correction is applied by using a camera in a negative feedback loop, which detects the wavefront after it has been reflected and sends the data to a control system, which in turn calculates the correction for and adjusts the deformable mirrors.

The deformable mirror is controlled by many analog input signals, which control either actuators or an electromagnetic field to deform the mirror's surface. To transfer the calculated correction from the control system to the mirrors, a DAC is needed and upgrading the existing product is the main goal of this project. The specifications of the existing model are summarized in Table 2.1.

Figure 2.1: Basic adaptive optics measurement setup [4].

4 2. Problem Definition

# 2.2. Program of Requirements

In this section, the various requirements demanded by Flexible Optical B.V. are summarized and elaborated on. The 'next generation' DAC is mainly used in the professional market for adaptive optics measurement setups. The applicable fields of research have grown in the past years and a faster and more precise DAC is demanded. After this project, Flexible Optical B.V. will manufacture and distribute the product.

# 2.2.1. Demanded Specifications

**Parameter Existing DAC** 'Next generation' DAC 40 channels 40 channels Analog outputs Refresh rate 1,000 frames per second 20,000 frames per second Resolution 12 bits per channel 16 bits per channel Output mode Synchronous for all channels Synchronous for all channels 0 V - 5 V with adjustable limits 0V - 5V or -5V - 5V with Output range adjustable limits Power Supplied by USB Supplied by USB > 500 pF> 500 pFLoad capacitance

Table 2.1: Existing and 'next generation' DAC specifications [2].

Flexible Optical B.V. has stated certain technical requirements in their proposal. The existing and 'next generation' specifications can be found in Table 2.1. The biggest shortcoming of the existing DAC is the refresh rate of 1,000 frames per second and the resolution of 12 bits. An increase in refresh rate of the DAC is demanded because it should match the typical frequencies of the disturbances. For example, for atmospheric turbulence the typical frequency is in the range of 100 Hz to 10 kHz [3], depending on the conditions. Introducing a faster DAC device would allow for an expansion of applicability since applications of adaptive optics are nowadays not limited to astronomy, but also used in biological imaging and many other fields of research. Increasing the resolution results in a greater dynamic range and a higher level of precision to control the deformable mirrors.

# **Analog Outputs**

A synchronous output for all 40 channels is necessary since otherwise the mirrors will not properly form. Deformable mirrors manufactured by Flexible Optical B.V. have between 17 and 109 control signals. Most of them have under 40 control signals and these could be controlled with the 'next generation' 40-channel DAC, developed in this project.

#### **Output Range**

Furthermore, the output voltage is requested to be either unipolar, with a range of 0 V to 5 V, or bipolar, with a range of -5 V to 5 V. The user should be able to adjust the outputs if necessary for a particular situation. An analog unipolar output voltage can only have one polarity, whereas an analog bipolar output voltage can have both positive and negative polarity. In the unipolar case, one bit equals

$$\frac{V_{\text{span}}}{2^{\text{bits}}} = \frac{5 \text{ V}}{2^{16}} = 76 \,\mu\text{V}. \tag{2.1}$$

In the bipolar case, one bit equals

$$\frac{V_{span}}{2^{bits}} = \frac{10 \text{ V}}{2^{16}} = 152 \,\mu\text{V}. \tag{2.2}$$

A bipolar output range is more desirable since this increases the voltage of the least significant bit and makes the DAC less prone to errors.

#### **Power**

Supplying the final product with power through the USB connection is purely out of convenience, due to the fact that only one cable is needed to connect the USB DAC to a computer. Also, USB is nowadays present on nearly every computer, which makes it widely employable.

### **Load Capacitance**

The load capacitance parameter specifies the capacitive load to be driven. To guarantee that the voltage amplifier, which amplifies the analog signals from the DAC, can operate correctly, the final product should be able to drive capacitive loads larger than 500 pF.

#### Latency

A parameter that has not been addressed explicitly is the latency of the product. The deformable mirrors will be compensated in real time, since every moment that the mirror is not formed properly, data is wasted. In the ideal case, the latency is zero seconds, but this is of course never possible. There is always a trade-off between data throughput and latency. In this case, the focus lies on minimizing latency and Flexible Optical B.V. mentioned that it should lie in the order of one updated frame. An acceptable latency lies in the range between

$$\frac{1}{\text{Refresh rate}} = \frac{1}{20.000 \,\text{kHz}} = 50 \,\mu\text{s}$$

(2.3)

and

$$\frac{2}{\text{Refresh rate}} = \frac{2}{20.000 \,\text{kHz}} = 100 \,\mu\text{s}.$$

(2.4)

Flexible Optical B.V. requests that all these parameters are updated to standards of today. At the end of the project, a completely functional DAC prototype has to be presented. This prototype has to be conform to the technical specifications mentioned earlier, but also with the existing form factor. In other words, all of the components of the 'next generation' DAC have to fit inside the same box as the existing DAC. The in- and outputs have to be in the same location and the maximum dimensions of the *Printed Circuit Board* (PCB) have to be 77 mm by 135 mm.

#### 2.2.2. Demanded Documents and Files

The following accompanying documents and files should be handed over to Flexible Optical B.V after the project for replication, fabrication and assembly.

- · Schematic of the device.

- · Bill of materials with catalog numbers from a major supplier.

- · Results of computer simulations.

- PCB design in a popular CAD package accompanied by Gerber files.

- · Pick-and-place file for the PCB.

- Any other files necessary for assembly and fabrication.

- · Complete set of software, such as drivers and firmware.

- · Set of example programs for both Linux and Windows.

- · Wrappers for C, LabVIEW, and MATLAB.

# Research

In this chapter, the system as a whole will be split up into various subsystems and each subsystem will be researched and evaluated in their corresponding section. At the end of each subsection, a conclusion will be drawn based on the conducted research in order to choose the best suitable component for the final version of the product.

# 3.1. System Overview

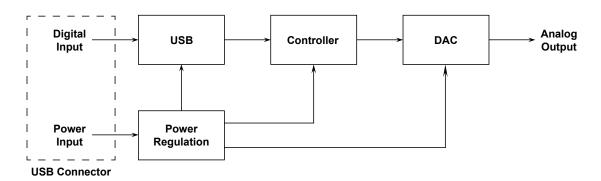

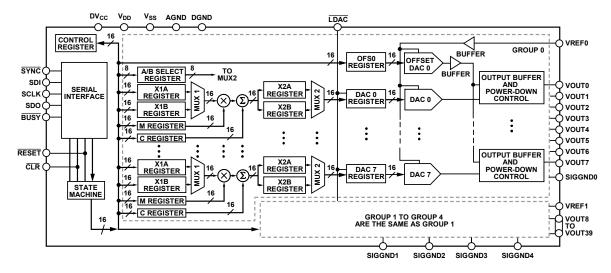

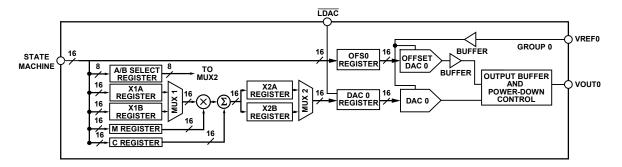

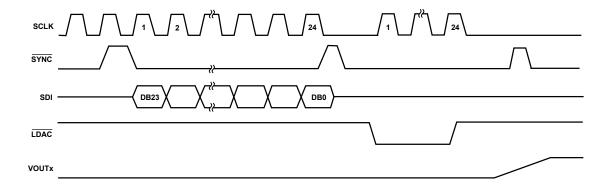

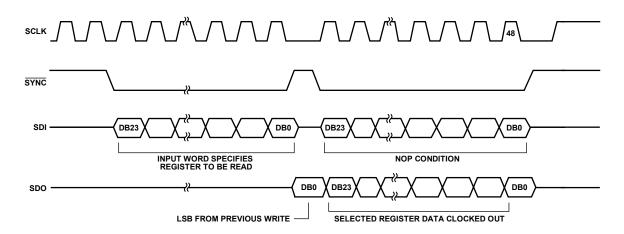

The very first step in structured system design is to divide the system into several subsystems. As specified by Flexible Optical B.V. in the proposal, the input of the system is either USB 2.0 or USB 3.0. The USB subsystem handles both data and power. The data packets received from the computer contain both digital signals and control signals. These digital signals should be converted to analog signals whereas the control signals are used to control the DAC chip. The job of the controller is to distinguish both types of data. It should present the signals for digital-to-analog conversion to the DAC through a protocol which the DAC chip understands and it should use the control data to control the DAC. The DAC chip is the final subsystem in the signal chain. Since all these subsystems require proper power, the last subsystem is the power regulation subsystem which regulates power and ensures that noise is suppressed as much as possible. A block diagram of the complete DAC system can be seen in Figure 3.1. Each subsystem will be researched and evaluated in the following sections.

Figure 3.1: Block diagram of the USB DAC.

# 3.2. Universal Serial Bus Subsystem

Universal Serial Bus (USB) is a protocol designed to standardize the connection of computer peripherals to personal computers, both to communicate and supply electrical power. It is designed and maintained by leading companies in electronics such as Compaq, DEC, IBM, Intel, Microsoft, NEC, and Nortel. USB was mainly designed for its simplicity, especially plug-and-play and compatibility, rather than high performance [5]. Besides computers, USB has become commonplace on other devices too, such as smart-phones and tablets. USB has effectively replaced a variety of earlier interfaces, such as serial and parallel ports, as well as separate power chargers for portable devices [6].

USB has been used and improved a lot since its introduction in 1996, and several versions have been released since. These versions, their release date, and transfer speed can be found in Table 3.1.

| Release name | Release date  | Speed and max. signaling rate                  |

|--------------|---------------|------------------------------------------------|

| USB 1.0      | January 1996  | Low Speed (1.5 Mbit/s), Full Speed (12 Mbit/s) |

| USB 1.1      | August 1998   | Low Speed (1.5 Mbit/s), Full Speed (12 Mbit/s) |

| USB 2.0      | April 2000    | High Speed (480 Mbit/s)                        |

| USB 3.0      | November 2008 | SuperSpeed (5 Gbit/s)                          |

| USB 3.1      | July 2013     | SuperSpeed+ (10 Gbit/s)                        |

Table 3.1: Version history overview of USB with their respective speeds [7] [8].

USB 1.0 is the first official version of USB. It was released with two possible speed modes, low speed (1.5 Mbits/s) and full speed (12 Mbits/s). Two years later USB 1.0 was replaced by USB 1.1. This version fixed issues identified in USB 1.0 and was the first version that was widely adopted.

USB 2.0 was released in April 2000, adding a higher maximum signaling rate of 480 Mbits/s called high speed. This is faster than low speed and full speed, although USB 2.0 is also compatible with these two lower speeds. USB 2.0 is still the most commonly used protocol by far, since it is compatible with practically every device and there is much documentation available.

USB 3.0 and 3.1 are the two newest versions of USB. With these versions new speeds were introduced, namely SuperSpeed (5 Gbit/s) and SuperSpeed+ (10 Gbit/s) for USB 3.0 and USB 3.1 respectively.

Table 3.2: USB 3.0 and 3.1 connector pin-outs [9]. Pins 1 to 4 are referred to as the USB 2.0 pins, while pins 5 to 9 are referred to as the SuperSpeed pins and are exclusive to USB 3.0 and 3.1. The D in D- and D+ stands for Data, where STdA\_SSR and STdA\_SST stand for Standard-A connector for SuperSpeed receiver and transmitter respectively.

| Pin | Signal name | Description                                       |

|-----|-------------|---------------------------------------------------|

| 1   | VBUS        | USB Power                                         |

| 2   | D-          | USB differential pair                             |

| 3   | D+          | OSB dillerential pail                             |

| 4   | GND         | USB Ground                                        |

| 5   | StdA_SSRX-  | LICE 2.0 CuperChand receiver differential pair    |

| 6   | StdA_SSRX+  | USB 3.0 SuperSpeed receiver differential pair     |

| 7   | GND_DRAIN   | USB 3.0 Ground                                    |

| 8   | StdA_SSTX-  | LISP 2.0 SuperSpeed transmitter differential pair |

| 9   | StdA_SSTX+  | USB 3.0 SuperSpeed transmitter differential pair  |

The upgrade from USB 1.1 to USB 2.0 was achieved by using the same amount of pins and optimizing the data throughput through these pins. Therefore all versions up to USB 2.0 consists of four pins, one for power, one for ground, and two for data [9]. USB 3.0 and 3.1 were introduced with five extra pins. One of these pins is ground and the other four pins form two differential pairs and are for SuperSpeed or SuperSpeed+ data transfer. An overview can be found in Table 3.2. Since the older USB connectors only contain four pins, it is impossible to use USB 3.0 or 3.1 at Superspeed or Superspeed+ in older connectors. When USB 3.0 or 3.1 are connected to older connectors, their five new pins will not be

connected and they will only utilise the standard four pins using the old speeds, making them backwards compatible.

The older versions, USB 1.0 and 1.1, are outdated and have very low speeds. USB 3.1 has increased speed and can definitely prove to be advantageous, but is still new and therefore not commonly supported and rarely found on personal computers. There is almost no literature available and it is more expensive. Therefore, realistic options for this project are USB 2.0 using high speed and USB 3.0. Research in these two types has been conducted, with a focus on the refresh rate, transfer types, and power capabilities. The results can be found in this section.

# 3.2.1. Speed

With USB 2.0, the host receives data at a certain frequency which is called the refresh rate. This data needs to be sent with a high signaling rate and a low latency. Commonly, these terms are often confused with each other, especially the refresh rate and the signaling rate. Therefore this subsection will focus on explaining these terms.

- **Signaling rate** is the rate at which the data is transferred from the host to the receiver and is defined as data transfers per second, mostly being in bits or bytes per second.

- **Refresh rate** is the rate the host can communicate with the device and determines the maximum time between data transfers. It is defined in Hertz, which is one cycle per second.

- Latency is the delay between the sent input signal and the corresponding received output signal defined in seconds.

### **Signaling Rate**

The signaling rate does not have a big impact on the DAC, since the data throughput does not have to be that high, but the refresh rate does. Roughly estimated and not taking control or any other signals in consideration, the data throughput equals

$$16 \text{ bits} * 40 \text{ channels} * 20 \text{ kHz} = 12.8 \text{ Mbit/s}.$$

(3.1)

Compared to the earlier mentioned speeds, this is easily achieved with either USB 2.0 high speed of 480 Mbits/s or USB 3.0 SuperSpeed of 5 Gbits/s.

#### Refresh Rate

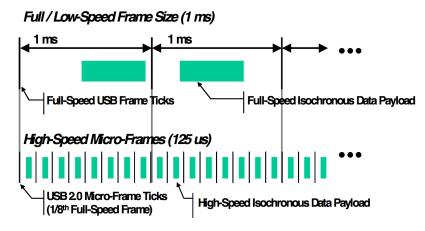

As discussed earlier, USB 2.0 has three modes: low speed, full speed, and high speed. The shortest time for a bus interval of USB 2.0 using low and full speed is defined as 1 ms [9]. This implies that a maximum refresh rate of

$$f = \frac{1}{T} = \frac{1}{1 \text{ ms}} = 1 \text{ kHz}$$

(3.2)

can be achieved, with f the frequency and T the period. This calculation also holds for high speed, of which the shortest time of an interval is 125 µs. This results in a maximum refresh rate of

$$f = \frac{1}{T} = \frac{1}{125 \,\mu s} = 8 \,\text{kHz}.$$

(3.3)

Data will be polled at 1 kHz for low and full speed, and at 8 kHz for high speed.

An overview of how polling works can be found in Figure 3.2. At every polling interval, represented by a black line, the USB protocol will check if a packet is ready to be sent and, if this is the case, it will process the packet. The upper part of the figure shows full/low-speed frame sizes whereas the lower part shows high-speed micro-frame sizes, which are eight times as short. The time that it takes to send the packet differs heavily per transfer, because the USB protocol handles aspects like queuing and errors differently depending on the transfer type used, which in this figure is isochronous. Transfer types will be discussed in Section 3.2.2.

Figure 3.2: Overview of USB 2.0 polling [6].

Where USB 2.0 works with polling, USB 3.0 in SuperSpeed mode works with asynchronous notifications. These asynchronous notifications come from the device and use a point-to-point link between the host and each device to indicate a request to send data to the device. Therefore the polling interval no longer exists. Due to this difference in operation, a much higher refresh rate can be achieved. However this also makes USB 3.0 depend on many other factors like hardware, the cable used, using a laptop in power saver mode and even minor things like moving the mouse while measuring. Therefore, a definite value is hard to determine. A possibility is to test a USB 3.0 transmission with an evaluation board and measure the refresh rate. This is costly, time consuming, and outside of the scope of this project, since a working prototype has to be delivered.

### Latency

The latency of USB 2.0 using high speed and USB 3.0 will now shortly be discussed in light of the just discussed USB polling. In the optimal case, a packet is ready to be sent in an infinitely small time before the bus interval. If the packet gets processed and sent immediately, depending on the package and the timings in the protocol, it is possible that it arrives at the host after only several microseconds and so the latency of this packet will only be this long. Therefore the minimum latency of USB can not be clearly defined since it is dependent on uncontrollable factors.

In the worst case scenario, a packet is ready to be sent in an infinitely small time after the bus interval. As soon as the next bus interval has passed it might take a while to process this package. Furthermore errors can occur which might result in USB resending the package or it never arriving at all depending on the transfer type used. Therefore the maximum latency of USB can also not be defined.

Because of all these factors it is incredibly hard to make an assumption about the latency of USB. For simplicity the average latency of USB 2.0 is in this thesis assumed to be  $125\,\mu s$ , the same length as the bus interval.

## 3.2.2. Transfer types

USB uses four types of transfers [10], each optimized for a different purpose. These transfer types are present since the beginning of USB and therefore are used on every version of USB. They are used to standardize the communication of computer peripherals and must be applicable to a variety of applications. The different types of transfers are the following.

- **Control** transfer is the only bidirectional transfer type. Control packets are typically bursty, random packets, which are initiated by the host and use best effort delivery. This kind of data transfer often occurs for identification and configuration of new devices.

- **Bulk** transfer is optimized for large, bursty data. It is an unidirectional transfer type and mostly used when a high data rate is required. A good example for bulk transfer is a transfer between a computer and a USB stick, or for example a print-job.

- Interrupt transfers are useful when data has to transfer within a specific amount of time, meaning with the shortest amount of latency. It is mostly used for devices which generate the signals themselves and send these to the host, such as keyboards or mice.

- **Isochronous** transfers are streaming, real-time transfers that are useful when data has to arrive at a constant rate. These transfers are optimized for a high refresh rate.

The control transfer type is used for bidirectional transfers and the other three are used to optimize the signaling rate, the latency, and the refresh rate. Characteristics per transmission mode are listed in Table 3.3. In this table the maximum signaling rate of SuperSpeed and SuperSpeed+ are not stated, since these rates are heavily dependent on external factors as stated earlier. Note that the bulk and isochronous transfer types do not support low speed.

Table 3.3: USB maximum signaling rate per transfer type [10]. Assumes transfers use maximum packet size. The signaling rate is in bytes per millisecond. An empty space means that speed is not allowed with the corresponding transfer type.

| Maximum signaling rate | Control | Bulk   | Interrupt | Isochronous |

|------------------------|---------|--------|-----------|-------------|

| Low speed [B/ms]       | 24      | -      | 0.8       | -           |

| Full speed [B/ms]      | 832     | 1,216  | 64        | 1,023       |

| High speed [B/ms]      | 15,872  | 53,248 | 24,576    | 24,576      |

Since the data in this USB DAC has to be transferred as real-time as possible the initial idea was to use isochronous transfer, since this transfer type prioritizes refresh rate over actual reliable data throughput and a high signaling rate. Control was not chosen since this protocol is optimized for bidirectional transfers, mostly being identification and configuration, and not for its signaling rate and refresh rate. Bulk and interrupt were not chosen because their refresh rate was thought not to be able to achieve the maximum refresh rate of USB 2.0, being 8 kHz. However, research led to the following: bulk and interrupt are not optimized for transfer while the bus is busy and in that case these kinds of data may slowly trickle over the bus [11], but in the case of this USB DAC, the bus is exclusively used by one device and so the refresh rate of these modes will not be negatively affected. Therefore the refresh rate of bulk, interrupt, and isochronous are identical and equal to the maximum refresh rate of 8 kHz.

The disadvantage of isochronous mode is that it does not check if data has been received; it is not built in with retry or guarantee of delivery. Because bulk has a guarantee of delivery and interrupt has a next period retry built in, both make sure that the data is present in the next period and both are a solution for this project.

# **3.2.3. USB Power**

The requirements dictate that the power supply should originate from the USB connection. The most interesting parameters are the current and voltage supplied by USB, and their stability.

To be able to work with multiple devices, two hub types are defined in USB, being low power and high power. A hub is a device that expands a single USB port to multiple ports. Low power can draw up to 100 mA and high power can draw up to 500 mA. The voltage properties of both hub types are listed in Table 3.4. It shows that the voltage swing is rather large and will have to be corrected in the implementation.

Table 3.4: Voltage properties of a USB 2.0 connection in non-transient conditions [10].

| Hub type   | Minimum value | Nominal value | Maximum value |

|------------|---------------|---------------|---------------|

| Low Power  | 4.4 V         | 5 V           | 5.25 V        |

| High Power | 4.75 V        | 5 V           | 5.25 V        |

The previous table shows that there is a voltage swing of 0.85 V peak-to-peak in low power and 0.5 V in high power. High power has the lowest voltage swing, this corresponds to a possible deviation of ±5 % from the nominal value. In addition, the voltage can briefly drop to values as low as 4.07 V in transient conditions [10]. These transient conditions only occur for example when the cable is connected or disconnected. The voltage properties of USB 3.0 are the same as for USB 2.0. The current however can be as large as 900 mA and devices can deliver current to the host [9].

The final device will be USB powered and the power specifications for all subsystems need to be determined before the power regulation subsystem can be designed. During the selection of components for the various subsystems, the current and voltage specifications need to be taken into account, since a limited amount of power can be supplied by the USB connection. Also the voltage swing of USB needs to be corrected to guarantee correct operation. Section 3.5 discusses the power regulation subsystem more in-depth.

# 3.2.4. Concluding Remarks

Important parameters of the USB subsystem are the transfer type, power specifications and most importantly the refresh rate. Either bulk or interrupt transfer proves to be the most optimal transfer type since it can achieve the requested maximum refresh rate and has error correction. The power supplied by the USB connection is not stable enough and has to be regulated to guarantee correct operation of all subsystems, but in terms of maximum current, USB 3.0 can supply more than USB 2.0. The estimated refresh rate of USB 2.0 is 8 kHz whereas the refresh rate of USB 3.0 is more promising, but its actual refresh rate is hard to determine. If there was more time available, USB 3.0 could have been researched. However, considering all factors and the scope of this project, the choice has been made by both the students and Flexible Optical B.V. to use USB 2.0: a working product is preferred over a faster product. The requested refresh rate has therefore been modified to the maximum of USB 2.0, which is 8 kHz. This is still eight times higher compared to the existing model. The change of this refresh rate also implies a change in the acceptable latency, and using the same formula as in Chapter 2, it now lies in the range between 125 µs and 250 µs.

# 3.3. Controller Subsystem

In this section, the controller subsystem is discussed, which serves as an intermediary device between the USB controller and the DAC. It needs to read and decode data from the USB subsystem and make sure that the received packets are converted into a protocol that can be used by the DAC. The controller might also need extra pins to control certain functions of the DAC. These three aspects will now be discussed.

## 3.3.1. Controller Input

As discussed in Section 3.2, USB 2.0 will be used for this project and the controller will receive all its input signals from this subsystem. Recall that USB 2.0 has four pins: two are used for power and two for a differential data pair. The data received from the USB connection will be processed by a USB protocol engine and converted to either parallel or serial output signals. In our case, either a parallel or serial protocol has to be found to control and send data to the DAC.

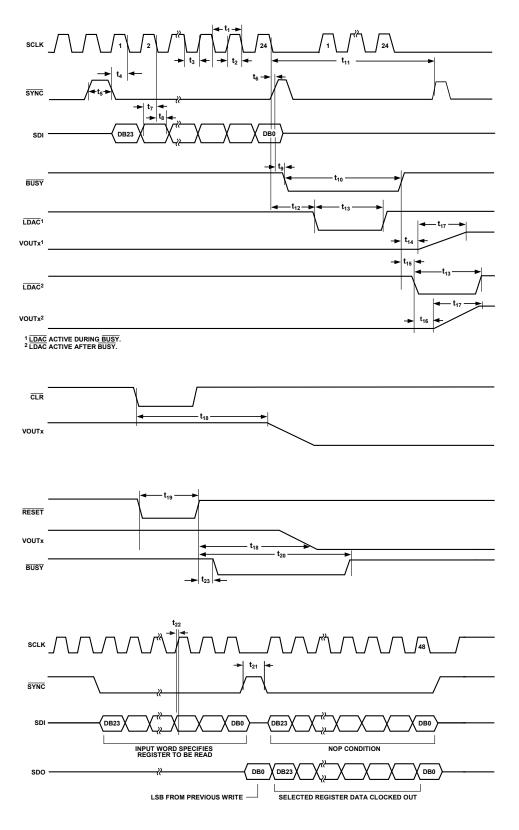

#### 3.3.2. Protocol

The data from the USB connection can be communicated over a channel or bus in two ways, being parallel or serial. In serial communication, one bit of data is sent at a time whereas with parallel communication several bits are sent at the same time [12]. Nowadays, serial communication is mostly used since synchronizing parallel communications gets more difficult as signal frequencies increase: when this happens signal transit time can not be guaranteed to be equal for all data lines. The higher the frequency, the more deviations will impact the signal frequency. The receiver of the data will have to wait untill all data is synchronized, which lowers the refresh rate. Therefore serial communication is a better and easier choice.

Several serial communication protocols exist, each optimized for a certain field. In embedded systems, widely adopted protocols are I<sup>2</sup>C, SPI, and USB [13], where I<sup>2</sup>C and SPI are commonly used between integrated circuits. Since these two protocols and its derivatives are so widely used and many information is available, only these two will be considered and briefly discussed, since the scope of this project does not allow for more exotic solutions.

#### I<sup>2</sup>C Protocol

The *Inter-Integrated Circuit* (I<sup>2</sup>C) protocol is designed for synchronous serial communication between micro-processors and other ICs. It allows multiple 'slaves' to communicate with one or more 'masters' [14] and requires a mere two pins. Therefore I<sup>2</sup>C is incredibly pin efficient compared to other protocols. The *Serial Data* (SDA) line is responsible for all data communications, while the *Serial Clock* (SCL) bus line synchronizes the communications by means of a clock signal.

I<sup>2</sup>C data transfers have five different transfer speeds developed over the years. Bidirectional data transfer speeds of 100 kbit/s, 400 kbit/s, 1 Mbit/s, and 3.4 Mbit/s can be achieved and the so-called Ultra Fast-mode, which is an unidirectional data transfer speed, can achieve up to 5 Mbit/s [15]. An unidirectional transfer is sufficient for communication between the controller and the DAC, but bidirectional transfer would allow read back from the DAC, to for example check certain settings [16].

#### **SPI Protocol**

The second option is the *Serial Peripheral Interface* (SPI), also designed for serial communication between master and slave [17]. Unlike I<sup>2</sup>C, SPI can only support one master, is purely bidirectional, and uses a total of four pins if one slave is used. *Serial Clock* (SCLK) provides the clock rate from master to slave, while the *Master Output Slave Input* (MOSI) and *Master Input Slave Output* (MISO) transfer data between the two. Finally, *Slave Select* (SS) selects the desired slave to transfer data to or from. Every added slave requires a new SS pin, which makes the pin count increase rapidly if many slaves are used. SPI has a relatively high throughput and is quite flexible. A maximum bit rate of 100 Mbits/s can be achieved [18].

Both protocols are summarized in Table 3.5. Most important for this project are the transfer speed, the complexity, and the amount of pins needed. As shown in the table, SPI is faster than  $I^2C$  and the hardware is easier compared to  $I^2C$ , even though  $I^2C$  uses two pins. Due to the modified requirements, USB 2.0 will be used and the rough estimated data throughput, as calculated in Section 3.2.1, has changed to

16 bits \* 40 channels \* 8 kHz =

$$5.12 \text{ Mbit/s}$$

. (3.4)

Even control signals have not yet been taken into account, and  $I^2C$  proves to be inadequate. Thus choosing SPI seems rather obvious, since it has a faster and bidirectional data transfer, which allows read back from the DAC. The extra two pins needed for SPI are a small price to pay compared to these advantages.

Table 3.5: Comparison between I<sup>2</sup>C and SPI. The maximal transfer speed of I<sup>2</sup>C is for the unidirectional case and n is the amount of slaves connected.

| Parameter              | l <sup>2</sup> C | SPI         |

|------------------------|------------------|-------------|

| Maximal Transfer Speed | 5 Mbits/s        | 100 Mbits/s |

| Amount of Connections  | 2                | 3 + n       |

| Multiple Masters       | Yes              | No          |

| Hardware Complexity    | High             | Low         |

# 3.3.3. Control Signals

Control signals are needed to control certain functions of the DAC, or even the entire DAC. Therefore the chosen controller has to have *General-purpose input/output* (GPIO) pins. At the simplest level, a GPIO pin is a switch that can be turned on or off at any time to, for example, reset the DAC at the

beginning of its runtime [19]. When for example two 20-channel DACs are controlled through SPI, five pins are needed for the SPI interface, but also control pins and pins to synchronize both DACs are needed. Multiple DACs result in a more complex control system which needs more pins and since all outputs need to be updated simultaneously, extra pins are needed to synchronize both DACs. A single 40-channel DAC can be controlled through SPI with four pins. The specific amount of GPIO pins needed depends heavily on the chosen DAC and an estimation can not be given without choosing one.

# 3.3.4. Concluding Remarks

The controller is an intermediary between the USB controller and DAC. The data received from the USB connection needs to be converted to a serial protocol, which was chosen to be SPI due to its fast transfer speed and ease of implementation. The controller also needs to have a yet to be determined amount of GPIO pins to control functions of the DAC or DACs, depending on the final implementation. From the point of view of the controller, a single 40-channel DAC would be easier to implement than multiple DACs, since a smaller control system and less pins are needed.

# 3.4. Digital-to-Analog Converter Subsystem

The DAC subsystem converts the digital data signals from the host to an analog signal. This is necessary because the deformable mirrors are controlled using analog signals. The mirrors deform due to electro-magnetic fields, which have to be controlled by analog voltages. The digital signals can easily be manipulated, stored, and transmitted without degradation.

There are several types of DACs available, but since the deformable mirrors are voltage controlled, only the most commonly used DACs with a voltage output are discussed. These are Delta-Sigma DACs, pulse-width modulated DACs, and resistive DACs.

# 3.4.1. Delta-Sigma DACs

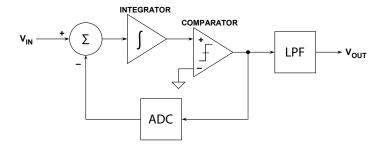

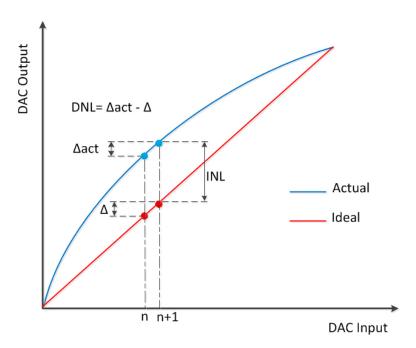

Delta-Sigma DACs are commonly used in integrated circuit solutions. The name Delta-Sigma relates to the core working principles of such a DAC, where Sigma ( $\Sigma$ ) represents the summing over the difference Delta ( $\Delta$ ). Delta-Sigma modulators are available for both analog-to-digital and digital-to-analog conversion. In this section, the heart of a Delta-Sigma DAC is discussed, which is the Delta-Sigma modulator [20].

Figure 3.3 shows a block diagram of a first-order Delta-Sigma modulator on a high level [21] [22]. Many Delta-Sigma DACs have signal shaping sections to guarantee correct operation. However, this signal shaping is outside of the scope of this research and will therefore not be discussed. The main goal of Delta-Sigma modulation is to increase transmission efficiency by only transmitting the change, called delta, of consecutive samples of the input signal, rather than the actual samples [23]. The input signal is fed into a subtractor and the difference is taken between the input and output of the comparator, which is fed through an ADC. When the output of the comparator is 0, the input signal is directly passed to the integrator, which sums the input until it triggers the comparator. At that point, the output changes from 0 to a reference voltage [24]. To smoothen the output of the comparator, a *low-pass filter* (LPF) is used.

Figure 3.3: Block diagram of a Delta-Sigma modulator on a high level [25].

Advantages of a Delta-Sigma DAC are their low cost and high accuracy. Also noise can be filtered away for a large part because of the ability to either increase the clock rate, to oversample the input rate, or to use a higher order Delta-Sigma modulator. Though Delta-Sigma DACs have many advantages which seem very promising, their circuits are of high complexity, mainly higher order modulators. Most chips are tailored towards audio solutions and have a maximum of eight output channels, which is not enough for this project. Multiple chips could be used in parallel, but synchronization algorithms are needed to guarantee correct operation.

#### 3.4.2. Pulse-Width Modulated DACs

Another implementation could be *Pulse-Width Modulation* (PWM), which is a form of signal modulation in which the data is represented as square waves with equal amplitudes but different periods.

When using PWM, the period of a signal is expressed as the ratio of the time of a high signal to the total time of that period, also known as the duty cycle. When the duty cycle is low, it corresponds to a low voltage. The duty cycle is expressed in a percentage, where 100 % means the signal is never low in a period.

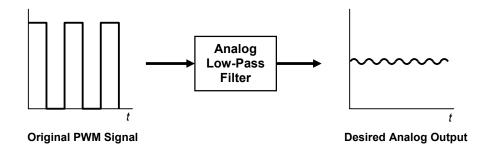

In theory, a PWM DAC transforms the offered digital input signal to a PWM signal, after which it is sent to a low-pass filter which removes high frequency components and ideally leaving only the *Direct Current* (DC) component [26]. This implementation is widely used in low-cost applications [27]. For example, many micro-controllers already have a PWM output. Figure 3.4 shows a PWM DAC, where the input PWM signal enters a low-pass filter, after which only the DC component should be left.

Figure 3.4: Block Diagram of a PWM DAC conversion [28].

Advantages of PWM DACs are their simplicity and low cost of the low-pass filter used. However, since the low-pass filter is a first order filter, the roll off of 20 dB/decade is rather sluggish which in some applications may not be sufficient. Switching signals are filtered by the first order filter, but the resulting signal has a ripple which bottlenecks the achievable resolution of the system. This ripple is clearly visible in Figure 3.4. Higher order or expensive filters could be used, but there is not enough space available. In short, PWM DACs are an easy and cheap way for low resolution DACs, but the required resolution of 16 bits would not be feasible [28].

#### 3.4.3. Resistive DACs

Resistive DACs are a third feasible implementation. These DACs consist of resistor networks which means that they are completely different from the previous two implementations, which both use low-pass filters. The main advantage of resistive DACs is that they can be implemented with uni-polar or bi-polar output ranges by simply applying a negative or positive voltage to the input. In the following section, various kinds of resistive DACs are discussed.

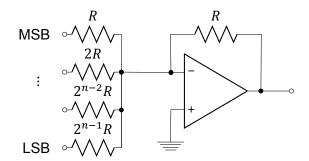

# **Binary Weighted DAC**

A binary weighted DAC uses the ability to add binary weighted currents, which are obtained by applying a voltage over the resistors which each represent a bit. The total current is then converted to an output voltage using an operational amplifier [29]. This type of DAC is one of the fastest implementations available, since the addition is done in the analog domain. The structure of a N-bit binary weighted DAC is shown in Figure 3.5. In this figure, LSB stands for *Least Significant Bit*, which determines whether the number is even or odd. MSB stands for *Most Significant Bit*, which is the bit position in a binary number having the greatest value.

Figure 3.5: Architecture of a N-bit binary weighted DAC.

The binary weighted DAC requires less resistors than the R2R DAC, which will be discussed later, per bit. However the values of these resistors should be doubled per bit used, requiring a large variety of resistor values. Since the default resistor is increased with factors of two, the resulting resistor values can be hard to obtain without combining resistors in series or parallel. Doing this results in a decreased accuracy of the DAC. Also, since these values need to be very precise, these DACs are very expensive and have a limited resolution.

In addition to the already mentioned advantages, correction can be done by either switching a bit high, neutral, or even to a negative value, because a binary weighted DAC is bipolar per bit. Obtaining a bipolar output range is as easy as applying a negative voltage to the resistor bit.

The main disadvantage of the binary weighted DAC is the need for an operational amplifier. The network is then no longer fully static, which increases the settling time, lowering the maximum sample frequency. Another disadvantage is that the non-linearity, gain error, and offset error of the op-amp will disturb the output of the total system. Also high precision resistors are needed which are expensive. A solution is to manufacture precise resistors in integrated circuits, since this is relatively cheap. The problem of this architecture is the need for various resistor values, which again makes manufacturing difficult.

## **R2R DAC**

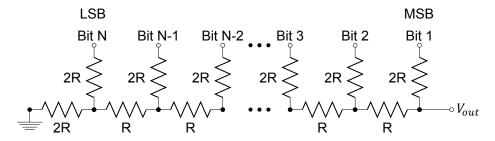

The R2R DAC is the second variant of resistive DACs. It consists of two resistor values throughout the circuit as the name suggests: R and 2R. The absolute value of the resistors do not matter in theory, as long as the resistance is twice as high [30]. Figure 3.6 illustrates an R2R circuit with N input bits. Bit 1 is the MSB, bit N the LSB, and both are driven from logic gates. The bits are switched between 0 V and voltage reference Vref, which represent a digital zero and one respectively. The resistive network causes the bits to be weighted relative to their contribution to the output voltage Vout [31].

A negative voltage output can be achieved by inverting the reference voltage. As stated before, the main problem of resistive DACs is their accuracy at higher bit resolutions. For example, for a 16-bit R2R DAC, the resistors for the MSB should have a maximum error of

$$\frac{\Delta R}{R} < \frac{1}{2^{16 \, bits}} \approx 0.0015 \,\%. \tag{3.5}$$

Therefore, 0.0015 % resistors are required and such accurate resistors are more expensive than conventional resistors. Manufacturing two different resistor values is also more complex than a resistive DAC were only one value is needed. However, R2R DACs have low noise and high accuracy and this architecture can achieve high-voltage outputs [33].

Figure 3.6: Architecture of a R2R DAC with N bits [32].

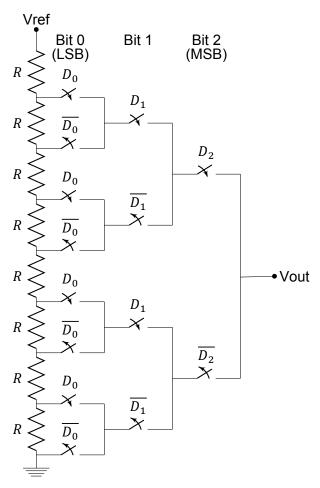

# **Resistive-String DAC**

A third implementation of a resistive DAC is the Resistive-string (R-string) DAC. The R-string DAC requires a large amount of switches compared to the binary weighted DAC and R2R DAC. Figure 3.7 shows the architecture of a 3-bit R-string DAC to get an idea of the size of such an implementation. An N-bit version would theoretically consist of 2N resistors with equal values in series and 2N switches. As shown in the figure, each bit represents one of the vertical arrays of switches, were a switch is connected between each node of the chain between the reference voltage Vref and ground. The output is taken from the appropriate node by closing the correct switches. This type of DAC is therefore generally used in integrated circuits, because integrated circuits can easily contain large amounts of switches and resistors.

Figure 3.7: Architecture of a 3-bit R-string DAC.

One of the advantages of a R-string DAC is that due to the production process, the resistors can be trimmed to obtain near exact values, preventing the use of external accurate and expensive resistors. The low power draw and small die area make small packages possible and monotonicity is guaranteed [33]. However, these circuits are complex and the switches have to be controlled properly, which is prone to errors.

# 3.4.4. Concluding Remarks

This section discussed many implementations of DACs, each with their own advantages and disadvantages. One of the main requirements for the final product is that the components used should be widely available. Even though some of the discussed implementations have many advantages, they may for example not be easily manufactured. Keeping the requirements in mind, the best option is the R-String DAC. Although it has disadvantages such as needing high precision resistors and a complex control system, all resistor values are the same, which prevents the use of external accurate and expensive resistors, and the architecture guarantees monotonicity and allows for a small IC package.

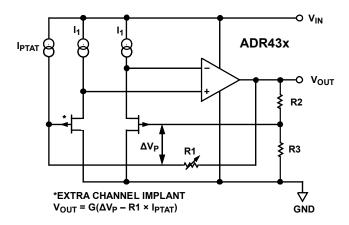

# 3.5. Power Regulation Subsystem

As stated before, the device has to be powered by the USB connection, which specifications were described in Section 3.2.3. The nominal voltage equals 5 V and can have a maximum deviation of  $\pm 5 \%$ . Also, the current that can be drawn depends on the hub type, with a maximum of 500 mA.

Since the power that the USB connection delivers is not stable, a power regulation subsystem is needed. This section elaborates on the research done regarding this power subsystem. Since the components have not yet been chosen in this chapter, the exact requirements of each component are not yet known and therefore this section only discusses general research and pitfalls.

To achieve this power regulation subsystem, there are two approaches. Either design a power regulator system using basic components or use integrated circuits that will do the regulation. Designing a regulator is outside of the scope of this project and therefore readily available solutions will be used. In the following chapter, each subsystem will list the required current and voltage levels for the to-be-designed power regulation subsystem. With those specifications in mind, the final subsystem can be designed.

# 3.5.1. Power Regulators

#### **Linear Converter**

The most basic way to change a voltage is by using a voltage divider, which is nothing more than two resistors in series. The input voltage will divide itself over these two resistors. For example, if the resistors are of equal value, the voltage at the node between the two resistors will be equal to half of the input voltage. The upside of this converter is that the architecture is very simple, since it consists of just two resistors. A downside is that only voltages lower than the supply voltage can be obtained and the voltage stability is not improved with this converter. Additionally, to make an accurate voltage value, accurate resistors are needed, which are expensive.

# **Operational Amplifier**

Another suitable solution for power conversion is an operational amplifier, or op-amp. An op-amp can increase or decrease its input voltage level with a predetermined gain. The upside of an op-amp is that it is a simple implementation and that it can achieve higher voltage levels than its input voltage. However, an op-amp can only increase its input voltage level until it matches its supply voltage level. Since both the input voltage and the supply voltage will be that of the USB connection, only equal or lower output voltage levels can be achieved. Another downside of an op-amp is that it suffers from nonlinearities in its gain. This means that the gain can deviate of what it should be, causing the DC output level to be too high or too low.

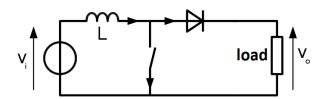

#### Switched-mode Converter

Switched-mode converters can convert voltages or currents to a higher or lower value. Examples of this type of converter are buck, boost, and buck-boost converters. To do the conversion, they use an inductor, a diode and a switch. Each converter has a different configuration using these three components. To perform the required conversion, the switch closes and opens with a specific frequency. This switching causes a ripple on the output. This ripple originates from the fact that energy is stored and released from the inductor and causes an *Alternating Current* (AC) on the DC output. The upside of this type of converter is that it is the only one in this section that is capable to obtain higher voltage levels than its supply voltage. The downside is that it is much more difficult to implement: it requires more components, including a switch. This switch has to be controlled on a certain frequency.

# 3.5.2. Decoupling power signals

The power originates from the USB connection, from which it will be regulated by this subsystem. The proper current and voltage levels will subsequently supply the other subsystems with power. All this transporting of power means that there will be many power lines running through the design.

These power lines can couple to distortion caused by other components, which causes them to have an AC component or ripple on the signal. This ripple will then enter the components through the power lines and can affect their outputs or otherwise harm the IC. Especially the analog outputs are very sensitive to this.

To suppress distortion, decoupling capacitors will be used, which act as a low-pass filter to filter out AC components. They are placed close to the power input of a component. After the filter, the path length should be as short as possible to avoid additional error coupling.

Another reason to use decoupling capacitors is to avoid sudden drops or rises in the supply voltage. When a supplied IC switches some output from high to low or vice versa, the power supply quickly rises or drops. It takes time for the power supply to return to its nominal value. A capacitor stores charge and acts as a small supply source. If the supply voltage drops, the capacitor voltage will drop much slower, because of the capacitor discharging. The same goes for the supply voltage rising, the capacitor voltage will rise slower, because the capacitor is then charging. Both the frequency characteristic and the charging problem need to be taken care of. To do this, each will require its own capacitor. For the charging problem, a large electrolytic capacitor is used because it stores charge very well. However, these electrolytic capacitors have poor characteristics regarding AC filtering. Therefore, a smaller ceramic capacitor is used which has good AC filtering characteristics [34].

# 3.5.3. Concluding Remarks

To supply all subsystems of the final implementation with power, a power regulation subsystem is needed. This power regulation subsystem should deliver different current and voltage levels and increased stability. It will consist of readily available components, because designing a power regulator from the ground up is outside the scope of this project.

Three different kinds of power regulators have been discussed. If the design needs voltage levels that are higher than that of the USB connection, the switch-mode converter would be a good choice. The downsides of this converter are that it is more complex to implement and that its output voltage level is not stable because of a ripple caused by the switching. Therefore in the case of only lower voltage levels, the other two implementations can be more practical, being the linear converter and the operational amplifier. Their implementation is not a real problem, since already available components will be used.

Furthermore, decoupling capacitors will be used to ensure that there is a more stable voltage supply and that AC distortion components are suppressed.

4

# **Implementation**

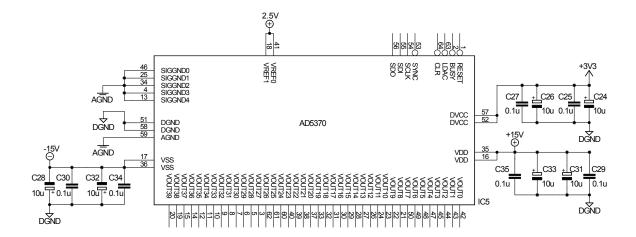

The previous chapter discussed various theoretical implementations and solutions to problems imposed by the requirements. At the end of each subsystem, a small conclusion was presented in which a certain direction or implementation was chosen. These implementations will be extensively elaborated in this chapter with the content narrowed down to this project's final selection of components. The subsystems of this chapter are discussed in the same order as in the previous chapter, except for the USB and the controller sections, which will be combined into one section.

# 4.1. USB Controller Subsystem

In the previous chapter the decision was made to use the USB 2.0 protocol for this project. Therefore it is necessary that the requirements of the final product are compared with the limitations of the USB 2.0 protocol and that this protocol is optimally set for our product. Next a controller has to be chosen which is compatible with these specifications and the type of data sent. For both subsystems, a component has been found which combines these functionalities into one unit, from now on referred to as the USB controller. The working of this USB controller will be explained in detail and finally its schematic will be discussed.

# 4.1.1. Requirements

The requirements as requested by Flexible Optical B.V. can be found in Table 2.1. The challenge in the USB controller lies in transferring the data for 40 channels simultaneously at a high refresh rate and moreover supplying power with a low ripple without degradating any of the other requirements. As discussed in Section 3.2 USB 2.0 will be used but therefore the USB subsystem proves to be a bottleneck for the refresh rate since the maximum refresh rate it can achieve is 8 kHz using high speed. Since the required refresh rate for this project has been modified to match this frequency of 8 kHz achieving this frequency should be possible. The preferred transfer mode was determined to be either bulk or interrupt. Furthermore the USB controller should convert the incoming USB data to the SPI protocol and have GPIO pins to be able to control functions of the DAC or DACs depending on the final implementation, which was concluded in Section 3.3.

# 4.1.2. Choice of Component

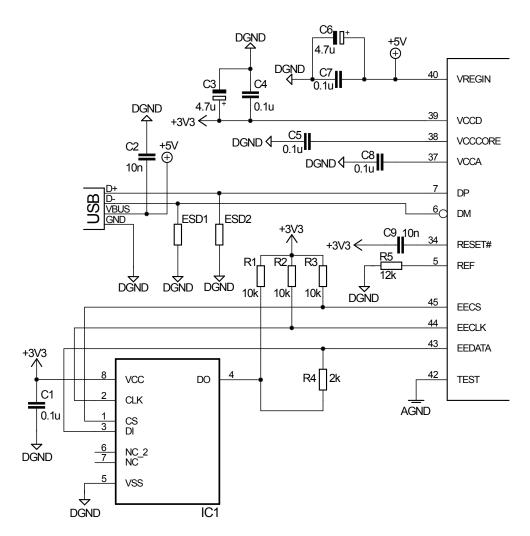

After an extensive search, a suitable USB controller was found: the FT232H [35] from FTDI. This controller complies with the requested demands, since it uses USB 2.0, bulk transfer, supports conversion to the SPI protocol and has GPIO pins. Another advantage of using this USB controller is that an evaluation board including this controller was also available, namely the UM232H [36]. This evaluation board contains the FT232H, the necessary decoupling capacitors, a crystal oscillator and an *Electrically Erasable Programmable Read-Only Memory* EEPROM. This EEPROM is required to facilitate slight adjustments to timings of several USB signals, because these timings are not only dependant

22 4. Implementation

on the USB signal drives, but also by factors such as the PCB layout and external components. An overview of the module is shown in Appendix C.1. On this module, the FT232H is shown along with numerous capacitors and the EEPROM is soldered to the bottom of this module. The chosen EEPROM is the 93LC56B from Microchip [37]. In the following subsection the most important aspects of the USB controller will be discussed.

### 4.1.3. Architecture

### Input power and data

The UM232H has been designed to be compatible with USB. It contains a USB connection to a host system via a mini-B USB connector. Please refer to Section 4.1.4 for a detailed overview of how these pins are connected to the controller.

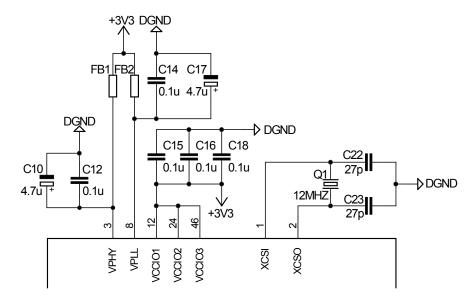

The UM232H has two modes for power: self-powered and bus powered. In self-powered mode the device gets its power from its own supply which is then connected to an external power source, while in bus-powered mode the device gets its power from the USB bus. Since the USB DAC in this thesis needs to be powered by the USB port and does not have access to an external power source, the bus-powered mode is chosen. In this mode the the 5 V is directly connected to the controller. This 5 V however is not stable enough for connection with the core of the controller. Therefore in the controller this rather unstable power supply of USB is corrected for and converted to a 3.3 V and 1.8 V stable voltage by an internal voltage regulator which is suitable for connection with the core of FT232H. See Table 4.1 for all power related signals of the FT232H.

| Component | Parameter         | Input/Output | Nominal voltage |

|-----------|-------------------|--------------|-----------------|

| 93LC56B   | $V_{CC}$          | Input        | 1.8 V to 5.5 V  |

| FT232H    | $V_{CCA}$         | Output       | 1.8 V           |

| FT232H    | $V_{CCD}$         | Output       | 3.3 V           |

| FT232H    | $V_{CCIO}$        | Input        | 3.3 V           |

| FT232H    | V <sub>CORE</sub> | Output       | 1.8 V           |

| FT232H    | $V_{PHY}$         | Input        | 3.3 V           |

| FT232H    | $V_{PLL}$         | Input        | 3.3 V           |

| FT232H    | $V_{REGIN}$       | Input        | 3.6 V to 5.5 V  |

Table 4.1: USB controller power input characteristics.

$V_{CCA}$  and  $V_{CORE}$  are outputs. The 3.3 V inputs can be supplied by  $V_{CCD}$ , the 3.3 V output. Also  $V_{CC}$ , the EEPROM supply voltage, is supplied by this 3.3 V voltage. This leaves only one voltage to be supplied by the power subsystem, which is shown in Table 4.2.

Table 4.2: USB controller power input characteristics.

| Component | Parameter   | Nominal voltage | Deviation | Deliverable Current |

|-----------|-------------|-----------------|-----------|---------------------|

| FT232H    | $V_{REGIN}$ | 3.6 V to 5.5 V  | ±0.25 V   | 54 mA               |

On the evaluation board the data is received by the differential data pair from USB and directly connected to the controller which supports this format. The controller then handles the data and converts it to a protocol corresponding to its configuration mode, which will be discussed now.

#### **Configuration Mode**

The USB controller has two buses: one of eight pins and one of ten pins for a total of 18 pins. These buses are called the ADBUS and the ACBUS respectively. On each bus all pins are configured accordingly to which configuration mode is chosen. Choosing this configuration is important since that determines the operation of the entire controller. There are nine different configuration modes [36]. A configuration mode had to be selected which supports SPI, the chosen serial protocol for the output signals, and which is able to configure GPIO pins.

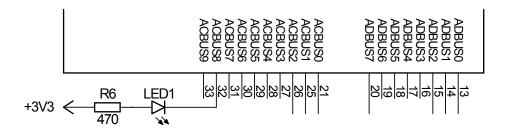

Accordingly the *Multi-Protocol Synchronous Serial Engine* (MPSSE) configuration mode has been chosen. MPSSE is a mode that provides a flexible means of interfacing synchronous serial devices to a USB port, in our case using SPI. Using MPSSE the eighteen output pins of the USB controller will then be configured as follows: four pins for the SPI output, twelve GPIO pins and two other pins. The four SPI pins are configured to be on the channels ADBUS0 to ADBUS3. The twelve GPIO pins on the other hand are configured to be on the channels ADBUS4 to ADBUS 7 and ACBUS0 to ACBUS7. These four SPI and twelve GPIO pins can be easily controlled by software which will be discussed in Section 4.5. The other two pins, being ACBUS8 and ACBUS9, are present and can be connected to LEDs. ACBUS8 will give a high signal when the USB controller is successfully receiving power where ACBUS9 will give a high signal if the controller is sending/receiving data.

#### Latency

The latency of the USB controller can be divided into three parts, being the latency of USB 2.0, the USB controller itself and the speed of a GPIO pin switching. It was estimated in section 3.2 that USB has a latency of 125 µs. The latency of the USB controller can be set to 0 ms and is basically very small compared to the latency of the other parameters [35]. The latency of changing a GPIO signal from low to high is also considered to be very small since the fastest frequency a GPIO can be updated with is 22 MHz [38]. This leads to a GPIO latency of

$$T = \frac{1}{f} = \frac{1}{22 \text{ MHz}} = 45 \text{ ns} \tag{4.1}$$

which can be considered to be zero when compared to the other latency parameters like USB. Herefore the latency of the entire USB controller subsystem can be considered to be equal to the latency of USB 2.0, being  $125 \,\mu s$ .

#### Refresh Rate

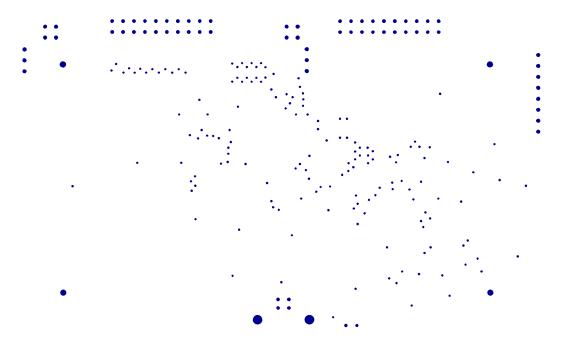

The refresh rate of the USB controller can be measured by capturing the packets which the computer sends to the device. This can be done by using the *Universal Serial Bus Packet capture* (USBPcap) extension in Wireshark [39]. This measurement has been done by sending data continuously to the USB controller for almost a minute and the summary of this is shown in Figure 4.1.

| Traffic •                     | Captured 4  | Displayed 4 | Displayed % ◀ | Marked ◀ | Marked % | 4 |

|-------------------------------|-------------|-------------|---------------|----------|----------|---|

| Packets                       | 395013      | 395013      | 100.000%      | 0        | 0.000%   |   |

| Between first and last packet | 51.041 sec  |             |               |          |          |   |

| Avg. packets/sec              | 7739.079    |             |               |          |          |   |

| Avg. packet size              | 509 bytes   |             |               |          |          |   |

| Bytes                         | 201097709   | 201097709   | 100.000%      | 0        | 0.000%   |   |

| Avg. bytes/sec                | 3939898.082 |             |               |          |          |   |

| Avg. MBit/sec                 | 31.519      |             |               |          |          |   |

|                               |             |             |               |          |          |   |

Figure 4.1: Summary of the measurement of USB packets using USBPcap in Wireshark.

The two most important aspects regarding the refresh rate are the amount of packets and the time between the first and the last packet. These can be used to calculate the time for each packet:

$$\frac{51.041 \text{ s}}{395.013 \text{ Packets}} = 129.21 * 10^{-6} \text{ s} = 129.21 \ \mu\text{s} = 7.739 \text{ kHz} \tag{4.2}$$

24 4. Implementation

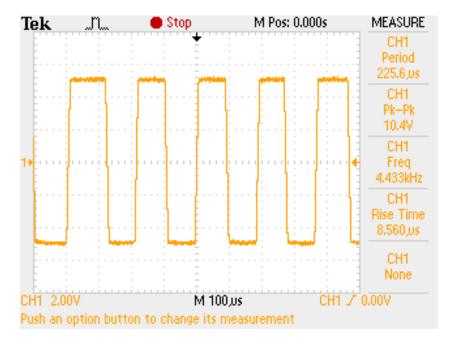

This indicates a that the time between intervals using this USBS controller is  $129.21\,\mu s$ . When inverted this implies a refresh rate of  $7.739\,kHz$ . Compared to the polling interval of  $125\,\mu s$  and the refresh rate of  $8\,kHz$  of USB 2.0 using high speed, it can be concluded that this estimation is correct. This because packets have to be resent when errors occur and so the real estimation takes slightly longer than the optimal situation.

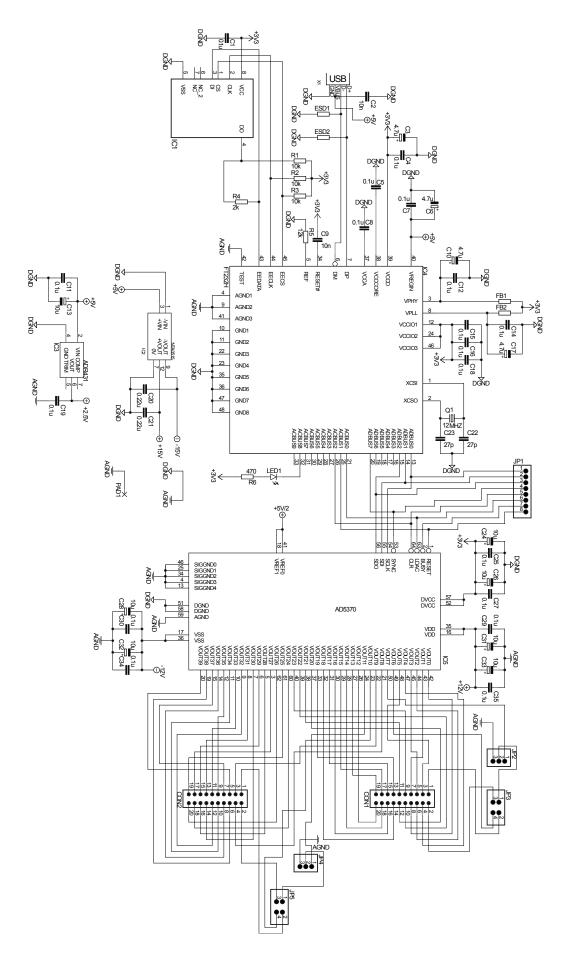

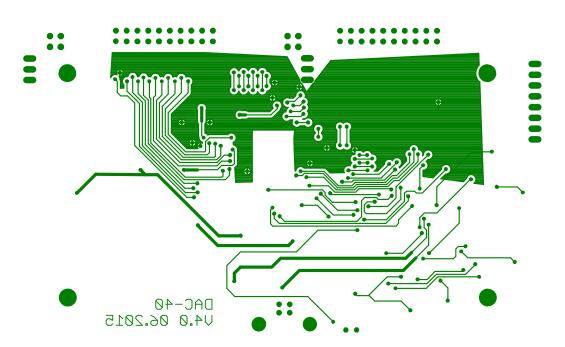

### 4.1.4. Schematic

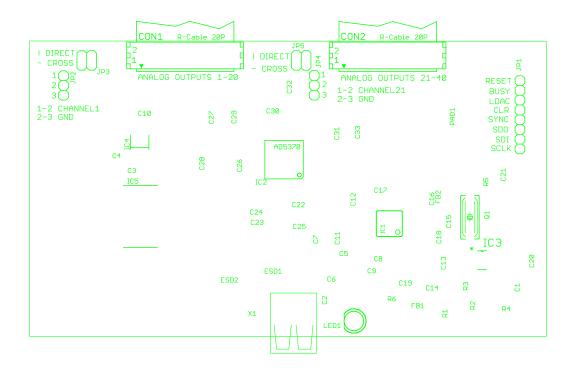

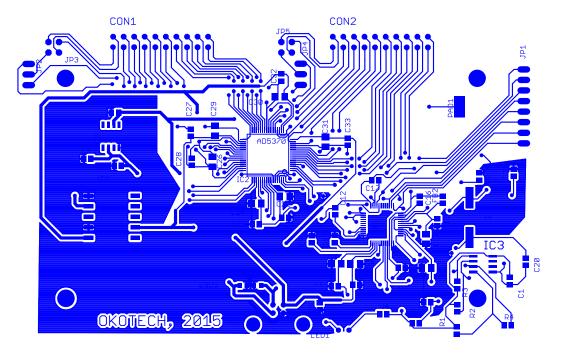

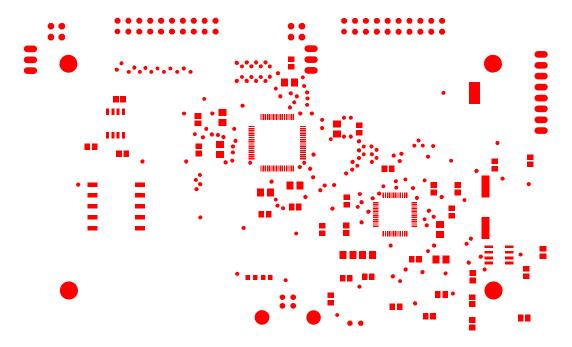

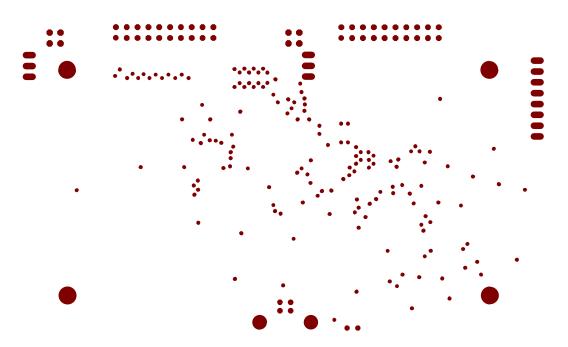

The datasheet of the UM232H [36] shows how to connect the FT232H. This will now be discussed in four parts. The schematic of the entire design is shown in Appendix C.3.

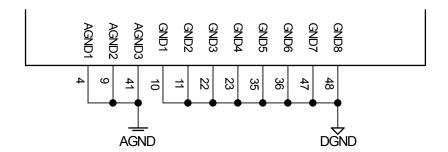

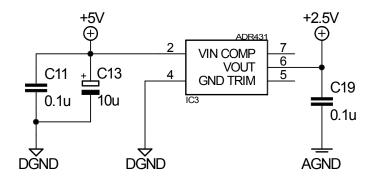

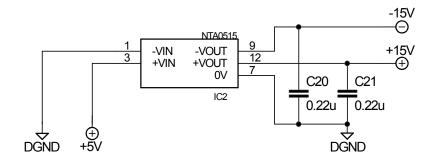

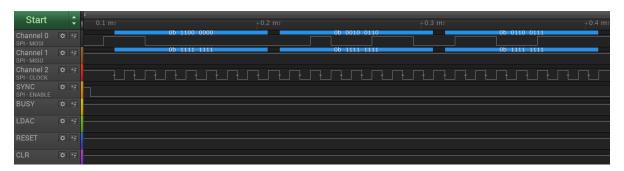

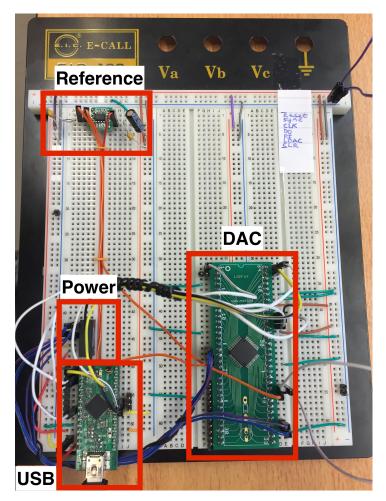

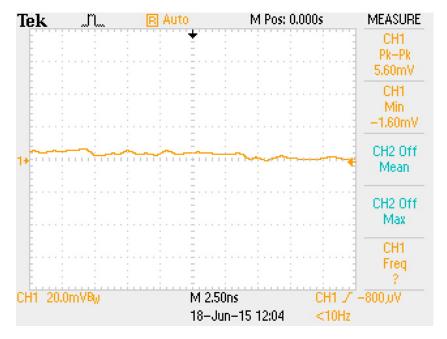

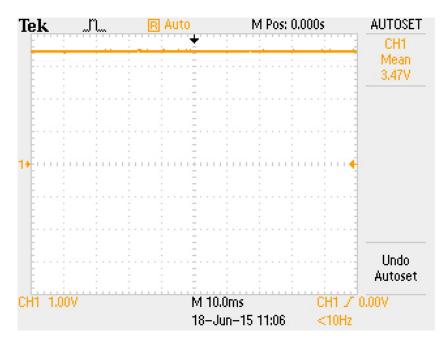

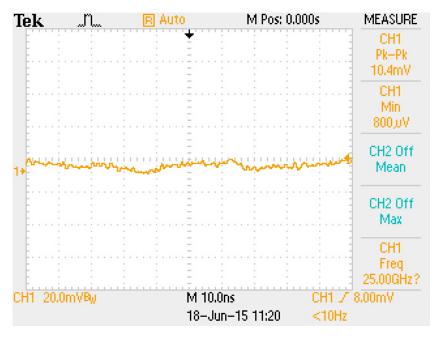

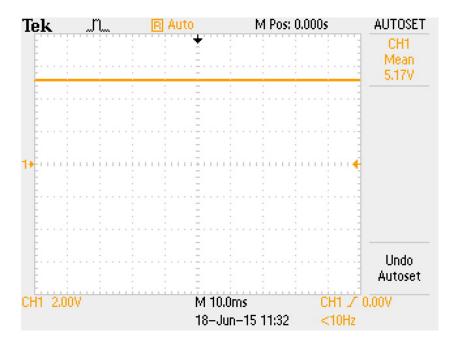

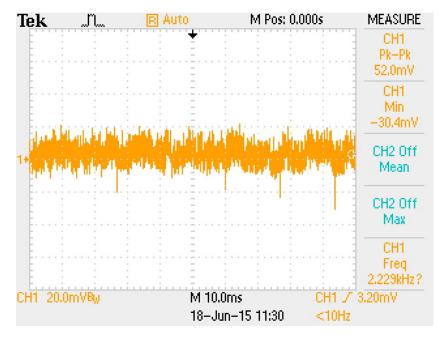

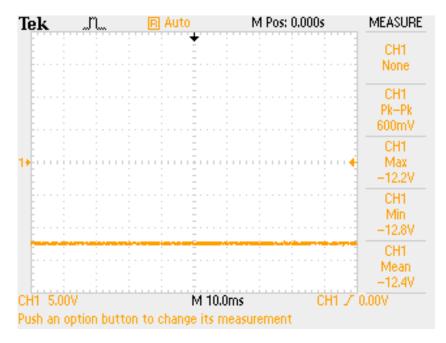

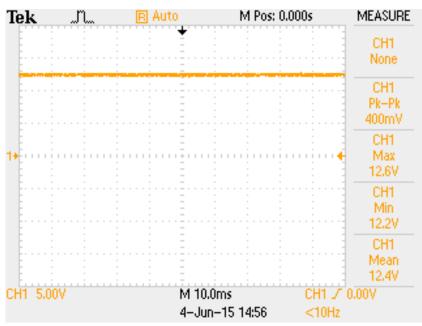

Figure 4.2: First part of the schematic of the FT232H showing the grounding.