# Enhancing Efficiency in Piezoelectric Energy Harvesting

# Collaborative-Flip Synchronized Switch Harvesting on Capacitors Rectifier and Multioutput DC-DC Converters Utilizing Shared Capacitors

Wang, Jing; Yang, Yi; Li, Zhen; Du, Sijun; Yue, Xinling; Liu, Xun; Han, Jun; Zeng, Xiaoyang; Chen, Zhiyuan

10.1109/JSSC.2024.3452113

**Publication date** 2024

**Document Version** Final published version

Published in

IEEE Journal of Solid-State Circuits

Citation (APA)

Wang, J., Yang, Y., Li, Z., Du, S., Yue, X., Liu, X., Han, J., Zeng, X., & Chen, Z. (2024). Enhancing Efficiency in Piezoelectric Energy Harvesting: Collaborative-Flip Synchronized Switch Harvesting on Capacitors Rectifier and Multioutput DC-DC Converters Utilizing Shared Capacitors. *IEEE Journal of Solid-State Circuits*, 60(4), 1474-1485. https://doi.org/10.1109/JSSC.2024.3452113

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# Enhancing Efficiency in Piezoelectric Energy Harvesting: Collaborative-Flip Synchronized Switch Harvesting on Capacitors Rectifier and Multioutput DC–DC Converters Utilizing Shared Capacitors

Jing Wang, Yi Yang, Zhen Li<sup>®</sup>, Sijun Du<sup>®</sup>, Senior Member, IEEE, Xinling Yue<sup>®</sup>, Graduate Student Member, IEEE, Xun Liu<sup>®</sup>, Member, IEEE, Jun Han<sup>®</sup>, Member, IEEE, Xiaoyang Zeng<sup>®</sup>, Senior Member, IEEE, and Zhiyuan Chen<sup>®</sup>, Member, IEEE

Abstract—This article proposes a novel collaborative-flip synchronized switch harvesting on capacitors (CF-SSHCs) rectifier and multioutput synchronous dc-dc converters with shared capacitors. Compared to the traditional SSHC, our CF-SSHC rectifier can increase the number of flipping phases, potentially enhancing the flipping efficiency and output power under specific conditions where  $C_{FLY}$  is close to  $C_P$ . The synchronous dc-dc converters reuse the flying capacitors to achieve a high maximum output power improving rate (MOPIR) over a limited input power range and provide multiple outputs. This work achieves an advanced number of flipping phases in capacitor-based rectifier interface technology and explores multiple-input multiple-output configurations, evaluating the system's performance under periodic and shock conditions for the first time. The system's adaptability to various piezoelectric transducer (PT) array configurations is validated, highlighting its potential for Internet of Things (IoT) networks. The design is fabricated in standard 0.18- $\mu m$  CMOS. Measurement results demonstrate that the voltage flipping efficiency of up to 83% is achieved. Compared with full-bridge rectifier (FBR), the MOPIR can be increased to 5.06 x and 4.78x under off-resonance and on-resonance excitation, respectively. It can also achieve a 2.14x power enhancement under shock excitation. Additionally, when the input power  $P_{\rm IN~FBR}$  is in the range of 1.42-28.4  $\mu$ W, the MOPIR of the proposed system is always greater than 4.

Index Terms—Maximum power point tracking (MPPT), multiinput, multioutput, piezoelectric, piezoelectric energy harvesting

Manuscript received 28 March 2024; revised 8 June 2024 and 12 August 2024; accepted 19 August 2024. Date of publication 23 September 2024; date of current version 28 March 2025. This article was approved by Associate Editor Chulwoo Kim. This work was supported in part by the National Natural Science Foundation of China under Grant 61934002 and in part by the National Key Research and Development Program of China under Grant 2023YFB4403603. (Corresponding author: Zhiyuan Chen.)

Jing Wang, Yi Yang, Zhen Li, Jun Han, Xiaoyang Zeng, and Zhiyuan Chen are with the State-Key Laboratory of ASIC and System, Fudan University, Shanghai 201203, China (e-mail: chen\_zy@fudan.edu.cn).

Sijun Du and Xinling Yue are with the Department of Microelectronics, Delft University of Technology, 2628 CD Delft, The Netherlands.

Xun Liu is with the School of Science and Engineering (SSE), Chinese University of Hong Kong, Shenzhen 518172, China.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2024.3452113.

Digital Object Identifier 10.1109/JSSC.2024.3452113

(PEH), rectifiers, shared capacitors, shock excitation, synchronized switch harvesting on capacitors (SSHCs).

## I. INTRODUCTION

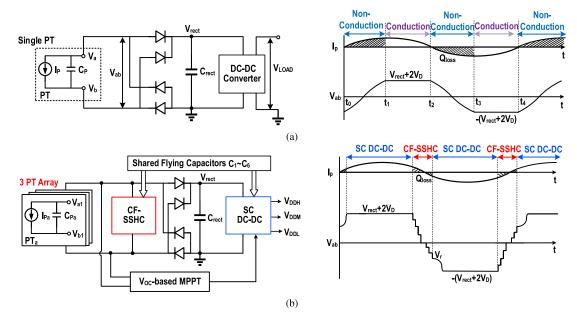

ITH the flourishing development of the Internet of Things (IoT), supplying power to a large number of miniature wireless sensor nodes has become an urgent challenge. Piezoelectric energy harvesting (PEH), which extracts energy from ambient vibration sources, has gained wide attention [1], [2], [3], [4]. Fig. 1(a) illustrates a conventional PEH system based on full bridge rectifier (FBR) [5]. The system is designed for a single piezoelectric transducer (PT). A FBR is used to convert the ac voltage  $V_{ab}$  into the dc voltage  $V_{rect}$ . Subsequently, a dc-dc converter regulates  $V_{\text{rect}}$  based on the input excitation to achieve maximum power point tracking (MPPT). It has advantages such as simplicity, stability, and high integration. However, due to the inherent capacitance  $C_P$ , the system can only harvest output power when  $|V_{ab}| \ge V_{\text{rect}} +$  $2V_D$ . During the remaining time, the diodes are nonconductive. The shaded region in Fig. 1(a) represents the charge wasted in the periodic charging and discharging of  $C_P$ . Consequently, the energy conversion efficiency of the FBR-based PEH system is relatively low. Additionally, single PT has limited energy harvesting capacity, risks single-point failure, and lacks flexibility. In contrast, using multiple PT units enhances energy conversion efficiency and allows for customized layouts to suit specific applications. When multiple elements operate in parallel, the system can maintain energy harvesting through the remaining elements even if some degrade or are damaged, ensuring overall stability and reliability.

In recent years, various flipping techniques based on inductor and switched capacitor have emerged [6], [7], [8], [9], [10], [11], [12], [13], [14], [15], [16]. For the synchronous switch harvesting on the inductor (SSHI), voltage flipping on  $C_P$  is achieved through an LC loop. To achieve higher flipping efficiency, inductors with high Q values are necessary, which

0018-9200 © 2024 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 1. (a) Conventional PEH system based on FBR. (b) Proposed PEH system based on CF-SSHC.

inevitably occupy large volumes. In contrast, the synchronized switch harvesting on capacitors (SSHC) technique relies on charge sharing to flip the charge on  $C_P$ . Multiple-phase and large flipping capacitors are utilized to enhance the output power. Complete PEH systems based on these flipping techniques have been widely implemented [17], [18], [19], [20], [21], [22], [23], [24]. Chen et al. [23] implemented a complete PEH system that includes a split-phase flipping-capacitor rectifier (SPFCR), MPPT, and dc-dc converters. However, this system is designed for a single PT, which not only reduces system reliability but also limits the number of flipping phases. Despite employing the split-phase method, the number of flipping phases is still limited to 21. Du and Seshia [22] presents a split-electrode synchronized switch harvesting on capacitors (SE-SSHCs) rectifier. By splitting the PT electrodes into four regions and temporarily connecting them in series during voltage flipping, the effective intrinsic capacitance of the PT is reduced, thereby significantly increasing the output power. However, due to the series-connecting PT units, this method not only requires high-voltage (HV) CMOS transistors but also results in high switching losses and leakage current, thereby reducing the energy harvesting efficiency. HV transistors also reduce system integration density, increase circuit complexity, and cause greater power consumption.

This article introduces a PEH system based on collaborativeflip synchronized switch harvesting on capacitors (CF-SSHCs) rectifier and multioutput dc-dc converters utilizing shared capacitors, as depicted in Fig. 1(b). By connecting three PT units in parallel, the proposed CF-SSHC rectifier can increase the number of flipping phases, thereby significantly improving the flipping efficiency and output power. For instance, in this article, 37 flipping phases were achieved using three PT units and six flying capacitors, tripling the number of flipping phases compared to traditional SSHC. This represents the highest number of flip phases currently achieved in capacitor-based flipping technologies. Due to the excellent scalability of CF-SSHC technology, this article also analyzes the performance of CF-SSHC with different numbers of stages and PT units. Furthermore, the proposed CF-SSHC utilizes flying capacitors only during brief flipping periods, allocating the remaining time for constructing the multioutput SC dc-dc converters with the flying capacitors, enhancing overall capacitor efficiency and system compactness.

#### II. PROPOSED SYSTEM

# A. Traditional SSHC Interface Circuit

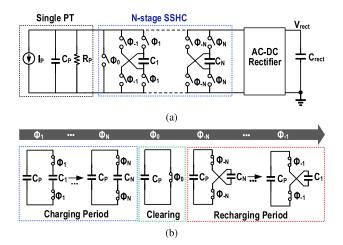

Fig. 2 depicts a traditional N-stage SSHC rectifier circuit and the associated flipping phases [10]. The SSHC interface circuit, consisting of N flying capacitors and 2N + 1 switches, has garnered widespread attention due to its simple structure and scalability. The operational principles of the N-stage SSHC are delineated as follows: At the zero-crossing of  $I_P$ , the initial voltage across  $C_P$  is  $V_{rect}$ . The flipping phases can be classified into three periods: 1) charging period: flying capacitors  $C_1 - C_N$  sequentially share with the charge on  $C_P$ ; 2) clearing period: shorting  $C_P$  to clear residual charge; and 3) recharging period: connecting the flying capacitors  $C_N - C_1$ in reverse polarity to recharge  $C_P$ , thereby establishing the rebuild voltage  $-V_r$ . It effectively reduces the charge wastage caused by the periodic charging and discharging of  $C_P$ . To quantify the enhancement in the performance of different types of synchronous switch harvesting (SSH) interface circuits, we typically employ the flipping efficiency  $\eta$  and its maximum output power improving rate (MOPIR). The expressions for flipping efficiency  $\eta$  and MOPIR are provided by [11]

$$\eta = \frac{V_{\text{rect}} + V_r}{2V_{\text{rect}}} \tag{1}$$

$$\eta = \frac{V_{\text{rect}} + V_r}{2V_{\text{rect}}} \tag{1}$$

$$MOPIR = \frac{P_{\text{rect,SSH,MAX}}}{P_{\text{rect,FBR,MAX}}}. \tag{2}$$

Fig. 2. (a) Traditional N-stage SSHC circuit. (b) Associated flipping phases [10].

For the traditional SSHC interface circuits, the MOPIR is typically determined by the number of stages and the ratio of flying capacitors to an inherent capacitor, denoted as  $C_{\rm FLY}/C_P$  [12]. For instance, in the case of the single-stage SSHC, if the flipping capacitor  $C_{FLY}$  equals  $C_P$ , the MOPIR is 3. However, if  $C_{\text{FLY}} \gg C_P$ , its MOPIR can be elevated to 4. Furthermore, increasing the number of SSHC stages can also enhance the performance of the SSHC interface circuits. If  $C_{FLY}$  equals  $C_P$ , the three-stage SSHC compared to the single-stage SSHC can increase the MOPIR from 3 to 5. If  $C_{\text{FLY}} \gg C_P$ , it can increase the MOPIR from 4 to 8. Therefore, for traditional SSHC interface circuits, to achieve higher output power, one must either increase the number of flipping stages or the capacitance value of the flying capacitors. However, both remedies would increase the overall system volume, deviating from the trend toward miniaturization and integration of PEH. Therefore, we propose a novel CF-SSHC technique to address this challenge.

#### B. Proposed CF-SSHC

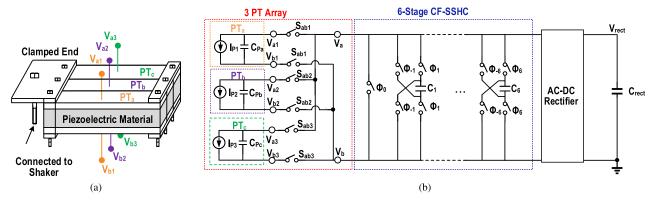

As illustrated in Fig. 3(a), three units are clamped in parallel, ensuring the vibration amplitude and phase between them are consistent. The electrical model of three PT units in parallel can be equivalently represented by a parallel combination of a sinusoidal current source  $I_P$ , inherent capacitor  $C_P$ , and resistance  $R_P$ . For each PT unit, the equivalent current source and capacitance become one-third of their original values, while the open-circuit voltage remains unchanged. It is worth mentioning that the area before and after the PTs are paralleled does not change. Fig. 3(b) depicts the circuit diagram of the proposed six-stage CF-SSHC rectifier. The essential components of the circuit include three PT units and six flying capacitors. We denote the three PT units as PT<sub>a</sub>, PT<sub>b</sub>, and PT<sub>c</sub>. Each PT unit is equipped with individual switches ( $S_{ab1}$ ,  $S_{ab2}$ ,  $S_{ab3}$ ), controlling its connection with the subsequent six flipping capacitors.

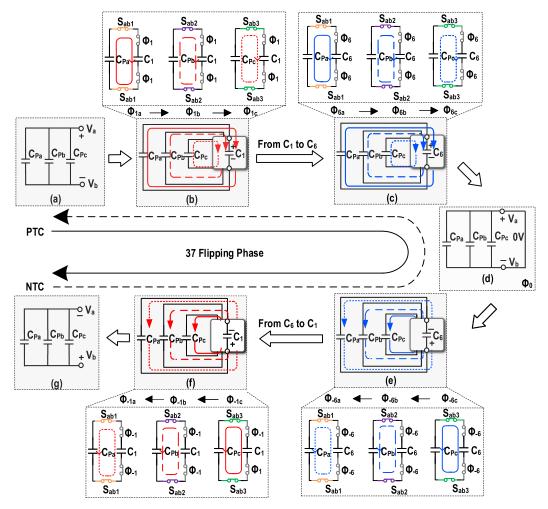

Fig. 4 depicts the operating phase of the proposed 37-phase six-stage CF-SSHC rectifier. Here, we denote the periods where  $I_P$  transitions from positive to negative and from

negative to positive as PTC and NTC, respectively. For clarity, we divide the operating states of the CF-SSHC into (a)–(g).

- Forward Harvesting State: As shown in Fig. 4(a), during the nonflipping moment, the three PT units are connected in parallel and collectively harvest energy from external excitation sources.

- 2) Charging State (18 Phases): As shown in Fig. 4(b) and (c), at the zero crossing of  $I_P$ , the flying capacitor  $C_1$  sequentially flips  $C_{Pa}$ ,  $C_{Pb}$ , and  $C_{Pc}$  of the PT units, gradually increasing the voltage on  $C_1$ . Then,  $C_2$ – $C_6$  are used sequentially to flip  $C_{Pa}$ ,  $C_{Pb}$ , and  $C_{Pc}$ . After 18 flipping phases, the remaining charge on the inherent capacitors of the three PT units gradually decreases.

- 3) *Clearing State:* As shown in Fig. 4(d), the three PT units are directly shorted to clear residual charges.

- 4) Recharging State (18 Phases): Fig. 4(e) and (f) demonstrates the recharging states, which are opposite to the charging state. The flying capacitors  $C_6$  to  $C_1$  are sequentially used in reverse polarity to recharge  $C_{Pc}$ ,  $C_{Pb}$ , and  $C_{Pa}$ , establishing the rebuild voltage.

- 5) Backward Harvesting State: After 37 flipping phases, the voltage across the three PT units changes from positive to negative, and then the three PT units are reconnected in parallel to harvest energy, as illustrated in Fig. 4(g). Symmetrically, the operation phases for NTC and PTC are completely reversed, i.e., from Fig. 4(a)–(g).

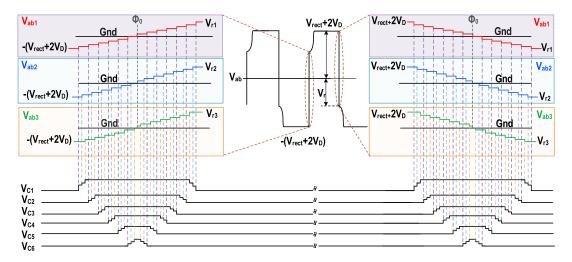

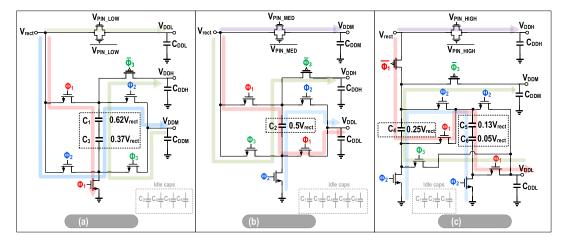

Fig. 5 illustrates the corresponding waveforms of the proposed CF-SSHC. When the circuit is stable, the voltages across the six flying capacitors are  $0.62V_{\text{rect}}$ ,  $0.5V_{\text{rect}}$ ,  $0.37V_{\text{rect}}$ ,  $0.25V_{\text{rect}}$ ,  $0.13V_{\text{rect}}$ , and  $0.05V_{\text{rect}}$ , respectively. It is worth noting that for a specific rectification topology, the ratio between the voltage across the flying capacitor  $(V_{C1} - V_{C6})$ and the rectified voltage  $(V_{rect})$  remains constant, regardless of variations in the input excitation [25]. Due to the very brief duration for which the flying capacitors are used for flipping, we will reuse them to construct the reconfigurable dc-dc converters. Considering the accumulated charge on the flying capacitors at the flipping moments, special attention must be paid when constructing the dc-dc converters to prevent mutual interference between the flipping operation and the dc-dc operation. The detailed structure of dc-dc converters will be presented in Section III.

# C. Performance Analysis of the Proposed CF-SSHC

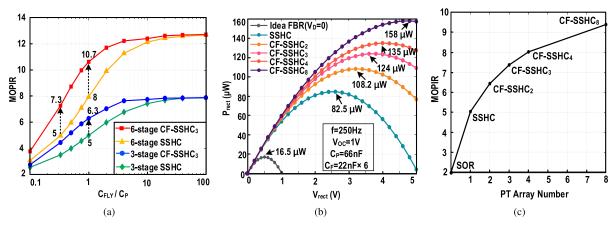

The proposed CF-SSHC has the advantage of scalability, allowing it to be extended to any number of PT units and flying capacitors. We refer to the CF-SSHC with N flying capacitors and M PT units as N-stage CF-SSHC $_M$ . In particular, when M=1, the proposed CF-SSHC is the traditional SSHC. Fig. 6(a) illustrates the relationship between the MOPIR of the proposed CF-SSHC and traditional SSHC with the number of stages and  $C_{\rm FLY}/C_P$ . Under the same number of stages and  $C_{\rm FLY}/C_P$ , the proposed CF-SSHC significantly enhances the MOPIR compared to SSHC. For instance, when  $C_{\rm FLY}/C_P=1/3$ , the proposed six-stage CF-SSHC increases the MOPIR from 5 to 7.3 compared to the traditional six-stage SSHC. Similarly, when  $C_{\rm FLY}/C_P=1$ , the six-stage

Fig. 3. (a) Schematic of three PT units in parallel. (b) Proposed six-stage CF-SSHC interface circuit.

Fig. 4. Operating phase of the proposed 37-phase six-stage CF-SSHC. (a) Forward Harvesting State. (b) Charging current flows from  $C_{pa}$ ,  $C_{pb}$  and  $C_{pc}$  to  $C_1$ . (c) Charging current flows from  $C_{pa}$ ,  $C_{pb}$  and  $C_{pc}$  to  $C_6$ . (d) Clearing State. (e) Recharging current flows from  $C_6$  to  $C_{pa}$ ,  $C_{pb}$  and  $C_{pc}$ . (f) Recharging current flows from  $C_1$  to  $C_{pa}$ ,  $C_{pb}$  and  $C_{pc}$ . (g) Backward Harvesting State.

CF-SSHC boosts the MOPIR from 8 to 10.7. Additionally, we simultaneously compare the three-stage CF-SSHC rectifier with the three-stage SSHC rectifier, further demonstrating the superiority of the proposed CF-SSHC. Only when  $C_{\rm FLY} \gg C_P$ , CF-SSHC and SSHC reach the same maximum MOPIR limit. However, typical PTs have  $C_P$  in the nF range, and achieving this limit requires very large flying capacitors, which does not align with the current trend of miniaturizing PEH systems. Compared to the traditional SSHC interface, the

proposed CF-SSHC interface offers the following advantages: First, the proposed CF-SSHC reduces the inherent capacitance during flipping moments. At flipping moments, as each PT unit sequentially flips the flying capacitors, the inherent capacitance  $C_P$  of each PT unit is only one-third of its original value. This effectively increases the output power and MOPIR. Additionally, while the traditional six-stage SSHC provides 13 flipping phases, the proposed CF-SSHC rectifier can extend the flipping phases to 37, thus improving the flipping efficiency. Compared

Fig. 5. Waveforms of the proposed CF-SSHC.

Fig. 6. (a) Relationship between the MOPIR of the proposed CF-SSHC and traditional SSHC with the number of stages and  $C_{\rm FLY}/C_P$ . (b) Simulation results of  $P_{\rm rect}$  versus  $V_{\rm rect}$  for FBR and the proposed six-stage CF-SSHC with different numbers of PT units. (c) Relationship between the MOPIR with the number of PT units.

to the SE-SSHC proposed in [22], the proposed CF-SSHC connects each PT unit and flipping capacitor in parallel, thereby avoiding high voltage stress and leakage current on the switches.

Fig. 6(b) shows the simulation results of  $P_{\text{rect}}$  versus  $V_{\text{rect}}$ for the FBR, SSHC, and six-stage CF-SSHC under different numbers of PT units. For a fair comparison, although the number of PT units varies, their total capacitance  $C_P$  and open-circuit voltage  $V_{\rm OC}$  remain constant. Simulation results show that as the number of PT units increases, the maximum output power of CF-SSHC also increases. Under the same flying capacitance, the proposed CF-SSHC<sub>3</sub> increases the maximum output power by nearly 50% compared to SSHC. To better illustrate the relationship between the number of PT units and MOPIR in CF-SSHC, we plotted Fig. 6(c) based on Fig. 6(b). It can be seen that although the maximum output power of CF-SSHC increases with the number of PT units, the marginal returns of this increase diminish. Considering the tradeoff between performance and power consumption, the six-stage CF-SSHC with three PT units prototype circuit is implemented in this article.

# III. IMPLEMENTATION

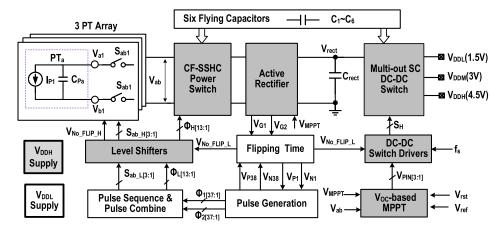

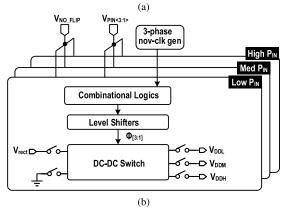

Fig. 7 illustrates the block diagram of the proposed system, which comprises two stages: the first stage is the proposed 37-phase CF-SSHC rectifier, and the second stage consists of reconfigurable multiout SC dc–dc converters. To minimize power consumption, the control circuit operates across both high- and low-voltage domains. Specifically, the pulse generation, pulse sequence, pulse combine modules, and flipping time module are powered by the low-voltage domain  $V_{\rm DDL}$ , while the CF-SSHC power switch, dc–dc switch, lever shifters, MPPT, and active rectifier are powered by the HV domain  $V_{\rm DDH}$ . Next, we will provide a detailed description of the key modules.

### A. Active Rectifier

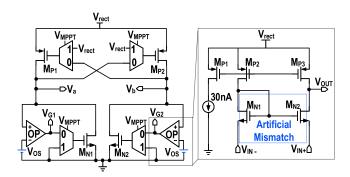

Fig. 8 shows the circuit diagram of the active rectifier. During MPPT, the four multiplexers temporarily disconnect the PT from the active rectifier to perform open-circuit voltage sampling. The active rectifier is composed of two cross-coupled PMOS transistors and two amplifier-based active diodes. The

Fig. 7. Diagram of system block.

Fig. 8. Active rectifier.

falling edges of the amplifier outputs,  $V_{G1}$  and  $V_{G2}$ , indicate the positive and negative zero-crossing of  $I_P$ , respectively. In the ground-input-compatible amplifier, the transistors operate in the subthreshold region. The 30 nA bias current ensures reliable operation under various input conditions [26], [27]. Additionally, we introduce an artificial mismatch by setting the sizes of the input transistors of the operational amplifier to different values, thereby introducing a consistent and predictable positive offset voltage. This improves the accuracy and reliability of the rectifier. Furthermore, this method avoids the complexity associated with implementing a closed-loop control system, thereby simplifying the overall design.

# B. Pulse Generation and Flipping Time Module

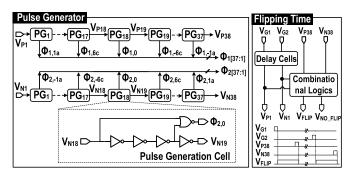

To ensure design margins and prevent phase overlap, the output signals  $V_{G1}$  and  $V_{G2}$  from the active rectifier undergo delay operations in the flipping timing module, resulting in the delayed signals  $V_{P1}$  and  $V_{P2}$ , respectively. Subsequently,  $V_{P1}$  and  $V_{P2}$  are fed into the pulse generation module to produce continuous pulses that drive the power switch array of the proposed CF-SSHC rectifier. Fig. 9 illustrates the pulse generation and flipping time module. The pulse generator cell consists of a chain of inverters, where the delay of this inverter chain determines the pulsewidth. To ensure complete charge sharing and prevent overlap between adjacent pulses, the width-to-length ratio of the transistors in this inverter chain should be set very small, i.e.,  $W \ll L$ .  $V_{P1}$  and  $V_{P2}$

Fig. 9. Pulse generation and flipping time module.

pass through 37 pulse generation cells, generating two sets of continuous pulse signals  $\Phi_{1[37:1]}$  and  $\Phi_{2[37:1]}$ . Additionally, pulse signals  $V_{P38}$  and  $V_{N38}$  represent the timing of the last pulse generation. Together with  $V_{G1}$  and  $V_{G2}$ , they are fed into the flipping time module, where simple combinatorial logic generates the signal  $V_{FLIP}$  representing the flipping time and the signal  $V_{NO}$  FLIP representing the nonflipping time.

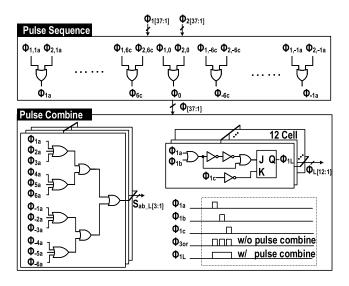

# C. Pulse Sequence and Combine

Fig. 10 shows the diagram of the pulse sequence and pulse combine. Due to the pulse sequence being completely opposite during PTC and NTC, the pulse sequence module needs to merge the head and tail of  $\Phi_{1[37:1]}$  and  $\Phi_{2[37:1]}$  to obtain the signal  $\Phi_{[37:1]}$ . Additionally, considering the reuse of switches in different phases, the pulse combination module will further combine the generated pulse signals. There are mainly two methods for pulse combination. The first method is to directly use three-input OR gates to generate the control signals  $S_{ab1}$ ,  $S_{ab2}$ , and  $S_{ab3}$  for the three PT units. The second method involves combining adjacent groups of three pulse signals (e.g.,  $\Phi_{1a}$ ,  $\Phi_{2a}$ ,  $\Phi_{3a}$ ) to generate the switch control signals for the six flying capacitors, from  $\Phi_1$  to  $\Phi_6$  and  $\Phi_{-1}$  to  $\Phi_{-6}$ . Specifically, we use JK flip-flops to prevent glitches that may arise from directly combining three signals. After passing through the pulse sequence and combine modules, the power switch signals are reduced from 37 bits to 16 bits. To minimize overall power consumption, the pulse generation, sequencing, and combination modules operate in the low-voltage domain.

Fig. 10. Pulse sequence and pulse combine.

However, the power switch arrays must operate in the HV domain, requiring low-power level shifters to convert the pulse signals. Due to the floating voltages at both ends of the power switches, this article employs switches composed of transfer gates with dynamic body bias [11].

#### D. Reconfigurable Multioutput DC-DC Converters

Traditional dc-dc converters typically use a two-phase clock, with the number of flying capacitors limiting the number of conversion ratios. To minimize external capacitance, we will adopt the three-phase clock, effectively utilizing flying capacitors to enhance the compactness of the system [28], [29]. Fig. 11 illustrates the proposed multioutput SC dc–dc converters using the flipping capacitors. Based on the input power, the proposed SC dc-dc converter selects the appropriate structure according to the preset conversion ratios. On one hand, it ensures that the conversion ratios among the three output terminals remain constant, i.e.,  $V_{DDH} = 3V_{DDL}$  and  $V_{\rm DDM} = 2V_{\rm DDL}$ . On the other hand, it directly connects  $V_{\rm rect}$ to one of the three output terminals to achieve MPPT. Based on the residual voltage levels of the flying capacitors after flipping, we connect  $C_1$  and  $C_3$  in series, as well as  $C_5$  and  $C_6$  to construct the SC dc-dc converters. This configuration minimizes the charge redistribution losses in the SC dc-dc converter while not affecting the flipping of the CF-SSHC stage. At low input power, the rectifier voltage  $V_{\text{rect}}$  will be directly connected to the low output voltage  $V_{\rm DDL}$ . In the  $\Phi_1$  period,  $C_1$  and  $C_3$  are connected in series and charged to  $V_{\text{rect}}$ . In the  $\Phi_2$  period,  $C_1$  and  $C_3$  are stacked on the top of  $V_{\text{rect}}$ , pumping  $V_{\text{DDM}}$  to twice  $V_{\text{DDL}}$ . In the  $\Phi_3$  period,  $C_1$  and  $C_3$  are stacked on the top of  $V_{\text{DDM}}$ , pumping  $V_{\text{DDH}}$ voltage to three times that of  $V_{\rm DDL}$ . It is worth noting that the voltage across the series connection of  $C_1$  and  $C_3$  is approximately  $V_{\text{rect}}$ , resulting in near-zero charge redistribution losses. At medium and high input power, the operations are similar to the process described above, and detailed elaborations are omitted here.

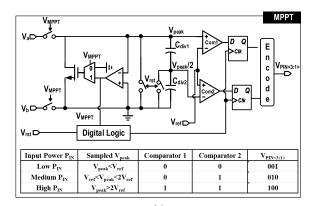

#### E. MPPT and DC-DC Switch Drivers

Fig. 12(a) and (b) illustrates the MPPT module and the dc-dc switch drivers, respectively. The MPPT is based on the fractional open-circuit voltage (FOCV) method [23]. During MPPT,  $V_{\text{MPPT}}$  is high and the PT will disconnect from the CF-SSHC rectifier. The MPPT circuit will sample the peak-peak voltage of the PT, denoted as  $V_{\text{peak}}$ . Subsequently, two identical capacitors divide  $V_{\rm peak}$ . When  $V_{\rm peak}$  and  $1/2V_{\rm peak}$ are compared with  $V_{\text{ref}}$ , there are three possible scenarios. When the input power is low, i.e.,  $V_{\text{peak}} < V_{\text{ref}}$ , both comparators output 0, causing the signal  $V_{PIN<3:1>}$ , which indicates the input power level, to output 001. The operating principle is similar for medium and high input power levels. The reference voltage  $V_{\text{ref}}$  affects the system's assessment of input power levels, thereby influencing the switching points of the subsequent SC dc-dc converters.  $V_{PIN<3:1>}$ , along with  $V_{NO\_FLIP}$  and the three-phase clock signal, are fed into the combinational logic circuit and control the reconfigurable dc-dc switch through the level shifters.

#### IV. MEASUREMENT RESULTS

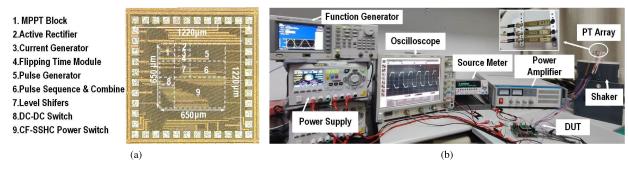

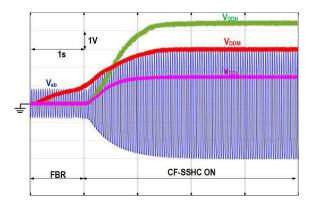

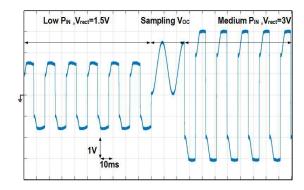

The chip prototype was designed and fabricated using  $0.18~\mu m$  CMOS technology. The microscopic view of the chip is depicted in Fig. 13(a), with an active area of 0.42 mm<sup>2</sup>. By clamping three independent PPA-1021 units together using thick insulating plates, they effectively function as three parallel PT units. When subjected to the same input excitation, their phase and amplitude are identical. Fig. 13(b) illustrates the measurement setup. The functional generator outputs sine wave and pulse wave, which are amplified by the power amplifier and drive the shaker for the periodic sine and shock vibration. Additionally, the oscilloscope monitors the output waveform, and the power supply provides the external reference voltage and the power supply. The intrinsic capacitance  $C_P$  of a single PT is 22 nF, resulting in a total intrinsic capacitance  $C_{P,\text{total}}$  of 66 nF. Each flying capacitor has a capacitance of 22 nF, giving a total of 132 nF for six flying capacitors. The rectifier capacitor  $C_{\text{rect}}$  and the output capacitors  $C_{\rm DDL}$ ,  $C_{\rm DDM}$ ,  $C_{\rm DDH}$  are all 100 nF. Fig. 14 illustrates the start-up of the proposed system. Initially, the system operates in the FBR state. When  $V_{\text{rect}}$  reaches 0.8 V, the CF-SSHC rectifier begins operating, gradually increasing the voltage across the PT to 6 V. This indicates that the proposed CF-SSHC significantly enhances the voltage across the PT, thereby efficiently improving the output power. When the circuit stabilizes, the system provides three output levels, namely  $V_{DDL}(1.5 \text{ V})$ ,  $V_{DDM}(3 \text{ V})$ , and  $V_{DDH}(4.5 \text{ V})$ . Additionally, when the input power changes, each output voltage is set to 1.5, 3, and 4.5 V, respectively, by manually tuning the load current.

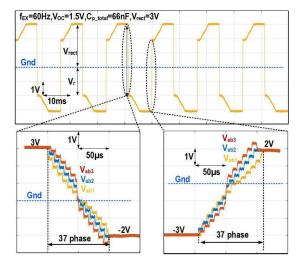

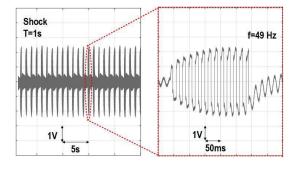

Fig. 15 depicts the measured waveform of the voltage at both ends of the three PT units under the sinusoidal excitation. At the nonflipping moment, the three PTs harvest energy in parallel, so the voltages at both ends of the three PTs are the same. When  $I_P$  crosses zero, the flying capacitors  $C_1$ – $C_6$  successively flip the voltages across the three PTs, for a total of 37 flip phases. The pulsewidth for each phase is

Fig. 11. Proposed multioutput SC dc-dc converters using the flipping capacitors. (a) Low P<sub>IN</sub>. (b) Medium P<sub>IN</sub>. (c) High P<sub>IN</sub>.

Fig. 12. (a) MPPT and (b) dc-dc switch drivers.

approximately 2.7  $\mu$ s, resulting in a total flip time of about 100  $\mu$ s, representing a mere 0.6% of the vibration cycle. According to the flipping sequence, the rebuilt voltages across the three PTs are approximately  $V_{ab3} > V_{ab2} > V_{ab1}$ . The flipping efficiency is about 0.83. Fig. 16 shows the waveforms of PT under the shock excitation. In the case of shock vibration, our excitation source is a square wave with a period of 1 s, and its falling edge is only 10 ns, to simulate the case of gradual disappearance of excitation. Under the shock excitation, it first operated in the CF-SSHC mode, and its conduction time gradually decreased until the minimum open circuit voltage could not maintain the flipping operation.

Fig. 17 illustrates the MPPT process. Initially, due to low external vibration, the reconfigurable dc–dc converter operates in the low  $P_{\rm IN}$  mode, where  $V_{\rm rect}$  is 1.5 V. Then, we increase the input excitation and the system enters the MPPT state. Temporarily disconnecting the PT array from the CF-SSHC rectifier, the peak-to-peak voltage of the PT is sampled, which is approximately 2.5 V, indicating that the open-circuit voltage of the PT is around 1.25 V. The corresponding optimal  $V_{\rm rect}$  is approximately 3 V. Consequently, the dc–dc converter enters the medium  $P_{\rm IN}$  mode, and  $V_{\rm rect}$  is connected to  $V_{\rm DDM}$ , achieving MPPT.

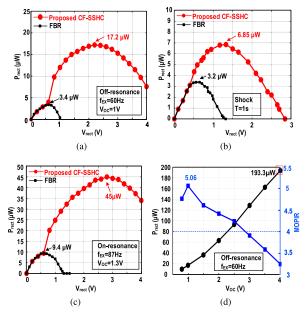

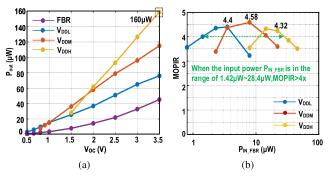

Fig. 18 shows the measured output power of the CF-SSHC rectifier under various excitations. To visually demonstrate the improvements of the proposed CF-SSHC compared to FBR, the corresponding output power of the FBR under the same excitation conditions is also plotted in the figure. Fig. 18(a) presents the output power under the off-resonance frequency of 60 Hz, with  $V_{\rm OC}=1$  V. When  $V_{\rm rect}$  is below 0.8 V, the system operates in the FBR state, resulting in lower output power. The FBR provides 3.4  $\mu$ W at an optimal  $V_{\text{rect}}$  of 0.6 V, which closely matches the theoretical calculation. The proposed CF-SSHC provides 17.2  $\mu$ W at an optimal  $V_{\text{rect}}$ of 2.2 V, representing an improvement of about 5.06 times compared with the FBR. Fig. 18(b) illustrates the output power of the proposed CF-SSHC rectifier as  $V_{\text{rect}}$  varies under shock excitation. The shaker was driven with a shock impulse every 1 s. The PT generated a  $V_{\rm OC}$  of 1.3 V. The on-chip FBR standalone was able to harvest 3.2  $\mu$ W at an optimal  $V_{\text{rect}}$  of 0.6 V. The proposed CF-SSHC interface harvested 6.85  $\mu$ W at an optimal  $V_{\text{rect}}$  of 1.3 V, representing an improvement of about 2.14 times compared with the FBR. Fig. 18(c) shows the harvested power under the mechanical resonance frequency of 87 Hz, with  $V_{\rm OC} = 1.3$  V. The FBR provides 9.4  $\mu \rm W$  at an optimal  $V_{\text{rect}}$  of 0.6 V, which closely matches the theoretical calculation. The proposed CF-SSHC provides 45  $\mu W$  at an optimal  $V_{\text{rect}}$  of 2.8 V, representing an improvement of about 4.78 times compared with the FBR. Fig. 18(d) shows the extracted power for different open-circuit voltages together with MOPIR. It can be seen that as the excitation level increases, the harvested output power also increases. The MOPIR reaches its peak of 5.06 at  $V_{\rm OC} = 1$  V. The MOPIR

Fig. 13. (a) Chip micrograph. (b) Picture of measurement setup.

Fig. 14. Start-up of the proposed CF-SSHC.

Fig. 15. Measured waveforms under the sine excitation.

remains above 4 between an open-circuit voltage range of 0.8–2.8 V, demonstrating the effectiveness of the proposed CF-SSHC. Under higher vibration excitation, the MOPIR of the system slightly decreases due to a significant increase in the power extraction from the FBR and limitations imposed by the process voltage.

Subsequently, the relationship between  $P_{\rm rect}$  and  $V_{\rm rect}$  was measured at various open-circuit voltage ( $V_{\rm OC}$ ) levels. The results demonstrate that the ratio of the maximum power point voltage ( $V_{\rm MPP,CF-SSHC}$ ) to  $V_{\rm OC}$  approximates a constant value, which fluctuates between 2.2 and 2.3. The measured  $P_{\rm OUT}$  versus  $V_{\rm OC}$  under different outputs is depicted in Fig. 19.

Fig. 16. Measured waveforms under the shock excitation.

Fig. 17. Measured waveforms during the MPPT operation.

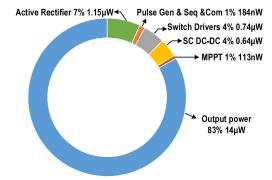

As illustrated in Fig. 19(a), the  $V_{\rm DDL}$  terminal outputs the highest power when  $V_{\rm OC}$  is below 0.9 V. For  $V_{\rm OC}$  values ranging from 0.9 to 1.8 V, the highest output power shifts to the  $V_{\rm DDM}$  terminal. Above 1.8 V, the  $V_{\rm DDH}$  terminal delivers the maximum output power. Therefore, the crossover points of these three output terminals are the points at which the system switches the dc-dc structure. Based on the above test results, we set the reference voltage  $V_{\text{ref}}$  to 1.8 V during our tests. Additionally, the minimum start-up voltage of the proposed system is 0.4 V. The maximum output power of the system reaches 160  $\mu$ W at  $V_{OC} = 3.5$  V. Fig. 19(b) shows the measured relationship between MOPIR versus  $P_{\text{IN FBR}}$  at different output voltages. When the input power  $P_{\rm IN~FBR}$  is in the range of 1.42–28.4  $\mu$ W, the MOPIR of the proposed system is always greater than 4. Fig. 20 provides the measured power breakdown of the proposed system.

Table I shows the comparison of the proposed work with the state of the art. This work demonstrates power enhancement

$\label{eq:TABLE I} \mbox{Performance Comparison With Previous Works}$

|                                        | JSSC'17[10]         | ISSCC'19[23]        | ISSCC'19[22]        | ISSCC'22[24]           | JSSC'23[14]          | This work                                                   |

|----------------------------------------|---------------------|---------------------|---------------------|------------------------|----------------------|-------------------------------------------------------------|

| Technology                             | 0.35 μm             | 0.18 μm             | 0.18 μm HV          | 0.65 μm                | 0.18 μm              | 0.18 μm                                                     |

| Piezoelectric harvester                | MIDE V21BL          | MIDE PPA1021        | Custom MEMS         | N/A                    | Piezo-1803YB         | MIDE PPA1021                                                |

| Inherent capacitor C <sub>P</sub>      | 45 nF               | 22 nF               | 1.94 nF             | N/A                    | 22 nF                | 66 nF                                                       |

| No. of PT                              | 1 PT                | 1 PT                | 4 PT units          | 3 (TEG/PT/PV)          | 1 PT                 | 3 PT units                                                  |

| Energy Extraction Technique            | SSHC                | SPFCR               | SE-SSHC             | MSVR SECE <sup>2</sup> | SSHSC                | CF-SSHC                                                     |

| Excitation type                        | Periodic            | Periodic            | Periodic            | Periodic               | Periodic             | Periodic & shock                                            |

| Operating Freq.                        | 92 Hz               | 200 Hz              | 219 Hz              | N/A                    | 130 Hz               | 49Hz-87Hz                                                   |

| Key Component                          | 8 caps,<br>17 phase | 4 caps,<br>21 phase | 8 caps,<br>17 phase | 1 ind,<br>22μΗ         | 3 caps,<br>8 phase   | 6 caps,<br>37 phase                                         |

| Flipping Capacitors C <sub>total</sub> | 360 nF              | 272 nF              | 4 nF                | N/A                    | 233 μF               | 132 nF                                                      |

| C <sub>total</sub> / C <sub>P</sub>    | 8                   | 12.36               | 2.06                | N/A                    | 10600                | 2                                                           |

| Converter Topology                     | N/A                 | SC DC-DC            | N/A                 | Buck-boost             | N/A                  | SC DC-DC                                                    |

| No. of Outputs                         | 1                   | 1                   | 1                   | 4                      | 1                    | 3 (1.5V/ 3V/ 4.5V)                                          |

| Max Flipping Voltage                   | Below 5V            | Below 6V            | 10.2V               | Below 5V               | Below 5V             | Below 5V                                                    |

| Flipping Efficiency                    | 0.8                 | 0.84                | 0.85                | 0.5                    | 0.78                 | 0.83                                                        |

| MOPIR                                  | 270% - 970%         | 370% - 626%         | 257% - 589%         | 320%                   | 758%                 | 506% (off-resonance)<br>478% (on-resonance)<br>214% (shock) |

| FoM <sup>1</sup>                       | 0.34 - 1.21         | 0.3 - 0.5           | 1.24 - 2.85         | N/A                    | 0.0007               | 1.07 - 2.53                                                 |

| Input power                            | N/A                 | 0.1 μW - 9 μW       | N/A                 | 0.6 μW - 300 μW        | N/A                  | 1.42 μW - 28.4 μW                                           |

| Max Output power                       | 161.8 μW            | 64 μW               | 186 μW              | 1.2 mW                 | 289.5 μW             | 193.3 μW                                                    |

| Chip Size                              | 2.9 mm <sup>2</sup> | 0.2 mm <sup>2</sup> | 5.4 mm <sup>2</sup> | 3.11 mm <sup>2</sup>   | 0.18 mm <sup>2</sup> | 0.42 mm <sup>2</sup>                                        |

|                                        |                     |                     |                     |                        |                      |                                                             |

<sup>&</sup>lt;sup>1</sup> FoM = MOPIR /  $(C_{total}/C_P)$ .

<sup>&</sup>lt;sup>2</sup> [24] is based on SECE, which has different performance metrics from those of SSHI/SSHC interfaces.

Fig. 18. Measured output power of the CF-SSHC rectifier under various excitations. (a)  $P_{\rm rect}$  versus  $V_{\rm rect}$  under off-resonance conditions. (b)  $P_{\rm rect}$  versus  $V_{\rm rect}$  under shock excitation. (c)  $P_{\rm rect}$  versus  $V_{\rm rect}$  under on-resonance conditions. (d)  $P_{\rm rect}$  and MOPIR versus  $V_{\rm OC}$ .

Fig. 19. Measured output power under different outputs. (a)  $P_{\rm OUT}$  versus  $V_{\rm OC}$ . (b) MOPIR versus  $P_{\rm IN\_FBR}$ .

Fig. 20. Power breakdown of the proposed system.

multistage soft-charging (MSC) technique to reduce the normalized capacitance  $(C_{\rm fly}/C_p)$ , achieving a higher FoM. However, our work offers multioutput capability and system

adaptability, validated through comprehensive testing under both periodic and shock conditions.

#### V. CONCLUSION

This article introduces a novel CF-SSHC rectifier and the SC dc–dc converters employing the shared flipping capacitor. The proposed CF-SSHC technology can effectively increase the flipping phase and output power without increasing the flipping capacitance. Its scalability and adaptability to various PT unit configurations make it a promising solution for the evolving needs of IoT networks. By efficiently allocating flying capacitors, it optimizes resource usage and offers a compact design suitable for the multiinput multioutput PEH system.

#### REFERENCES

- F. Dell'Anna et al., "State-of-the-art power management circuits for piezoelectric energy harvesters," *IEEE Circuits Syst. Mag.*, vol. 18, no. 3, pp. 27–48, 3rd Quart., 2018.

- [2] J. Wang, Z. Chen, Z. Li, J. Jiang, J. Liang, and X. Zeng, "Piezoelectric energy harvesters: An overview on design strategies and topologies," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 69, no. 7, pp. 3057–3063, Jul 2022

- [3] G. A. Rincón-Mora and S. Yang, "Tiny piezoelectric harvesters: Principles, constraints, and power conversion," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 63, no. 5, pp. 639–649, May 2016.

- [4] L. He, Y. Han, R. Liu, R. Hu, G. Yu, and G. Cheng, "Design and performance study of a rotating piezoelectric wind energy harvesting device with wind turbine structure," *Energy*, vol. 256, Oct. 2022, Art. no. 124675.

- [5] Y. K. Ramadass and A. P. Chandrakasan, "An efficient piezoelectric energy harvesting interface circuit using a bias-flip rectifier and shared inductor," *IEEE J. Solid-State Circuits*, vol. 45, no. 1, pp. 189–204, Jan. 2010.

- [6] L. Wu, X.-D. Do, S.-G. Lee, and D. S. Ha, "A self-powered and optimal SSHI circuit integrated with an active rectifier for piezoelectric energy harvesting," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 3, pp. 537–549, Mar. 2017.

- [7] S. Du, Y. Jia, C. D. Do, and A. A. Seshia, "An efficient SSHI interface with increased input range for piezoelectric energy harvesting under variable conditions," *IEEE J. Solid-State Circuits*, vol. 51, no. 11, pp. 2729–2742, Nov. 2016.

- [8] Y. Peng et al., "An adiabatic sense and set rectifier for improved maximum-power-point tracking in piezoelectric harvesting with 541% energy extraction gain," in *IEEE Int. Solid-State Circuits Conf. (ISSCC)* Dig. Tech. Papers, Feb. 2019, pp. 422–424.

- [9] A. Quelen, A. Morel, P. Gasnier, R. Grézaud, S. Monfray, and G. Pillonnet, "A 30 nA quiescent 80 nW-to-14 mW power-range shockoptimized SECE-based piezoelectric harvesting interface with 420% harvested-energy improvement," in *IEEE Int. Solid-State Circuits Conf.* (ISSCC) Dig. Tech. Papers, Feb. 2018, pp. 150–152.

- [10] S. Du and A. A. Seshia, "An inductorless bias-flip rectifier for piezoelectric energy harvesting," *IEEE J. Solid-State Circuits*, vol. 52, no. 10, pp. 2746–2757, Oct. 2017.

- [11] Z. Chen, M.-K. Law, P.-I. Mak, W.-H. Ki, and R. P. Martins, "Fully integrated inductor-less flipping-capacitor rectifier for piezoelectric energy harvesting," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3168–3180, Dec. 2017.

- [12] X. Yue and S. Du, "Voltage flip efficiency optimization of SSHC rectifiers for piezoelectric energy harvesting," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2021, pp. 1–5.

- [13] Z. Li et al., "Piezoelectric energy harvesting interface using self-biasflip rectifier and switched-PEH DC-DC for MPPT," *IEEE J. Solid-State Circuits*, vol. 59, no. 7, pp. 2248–2259, Jul. 2024.

- [14] X. Yue and S. Du, "A synchronized switch harvesting rectifier with reusable storage capacitors for piezoelectric energy harvesting," *IEEE J. Solid-State Circuits*, vol. 59, no. 9, pp. 2597–2606, Sep. 2023.

- [15] C. Xie, G. Zhao, Y. Ma, M.-K. Law, and M. Zhang, "Fully integrated frequency-tuning switched-capacitor rectifier for piezoelectric energy harvesting," *IEEE J. Solid-State Circuits*, vol. 58, no. 8, pp. 2337–2348, Aug. 2023.

- [16] P. Angelov and M. Nielsen-Lönn, "A fully integrated multilevel synchronized-switch-harvesting-on-capacitors interface for generic PEHs," *IEEE J. Solid-State Circuits*, vol. 55, no. 8, pp. 2118–2128, Aug. 2020.

- [17] S. Bandyopadhyay and A. P. Chandrakasan, "Platform architecture for solar, thermal, and vibration energy combining with MPPT and single inductor," *IEEE J. Solid-State Circuits*, vol. 47, no. 9, pp. 2199–2215, Sep. 2012.

- [18] S. S. Amin and P. P. Mercier, "MISIMO: A multi-input single-inductor multi-output energy harvester employing event-driven MPPT control to achieve 89% peak efficiency and a 60,000x dynamic range in 28 nm FDSOI," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 144–146.

- [19] P.-H. Chen, H.-C. Cheng, and C.-L. Lo, "A single-inductor triple-source quad-mode energy-harvesting interface with automatic source selection and reversely polarized energy recycling," *IEEE J. Solid-State Circuits*, vol. 54, no. 10, pp. 2671–2679, Oct. 2019.

- [20] G. Chowdary, A. Singh, and S. Chatterjee, "An 18 nA, 87% efficient solar, vibration and RF energy-harvesting power management system with a single shared inductor," *IEEE J. Solid-State Circuits*, vol. 51, no. 10, pp. 2501–2513, Oct. 2016.

- [21] H. Kim, J. Maeng, I. Park, J. Jeon, D. Lim, and C. Kim, "A 90.2% peak efficiency multi-input single-inductor multi-output energy harvesting interface with double-conversion rejection technique and buck-based dual-conversion mode," *IEEE J. Solid-State Circuits*, vol. 56, no. 3, pp. 961–971, Mar. 2021.

- [22] S. Du and A. A. Seshia, "A fully integrated split-electrode synchronized-switch-harvesting-on-capacitors (SE-SSHC) rectifier for piezoelectric energy harvesting with between 358% and 821% power-extraction enhancement," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 152–154.

- [23] Z. Chen, M.-K. Law, P.-I. Mak, X. Zeng, and R. P. Martins, "Piezo-electric energy-harvesting interface using split-phase flipping-capacitor rectifier with capacitor reuse for input power adaptation," *IEEE J. Solid-State Circuits*, vol. 55, no. 8, pp. 2106–2117, Aug. 2020.

- [24] S. Li, X. Liu, and B. H. Calhoun, "A 32 nA fully autonomous multi-input single-inductor multi-output energy-harvesting and power-management platform with 1.2 × 105 dynamic range, integrated MPPT, and multi-modal cold start-up," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, vol. 65, Feb. 2022, pp. 1–3.

- [25] J. Wang, Z. Chen, J. Liang, X. Cheng, J. Han, and X. Zeng, "A cross regulation reduced multi-output and multi-VCR piezoelectric energy harvesting system using shared capacitors," in *Proc. IEEE Int. Symp. Cir*cuits Syst. (ISCAS), May 2022, pp. 2768–2772.

- [26] Y. Sun, N. H. Hieu, C.-J. Jeong, and S.-G. Lee, "An integrated high-performance active rectifier for piezoelectric vibration energy harvesting systems," *IEEE Trans. Power Electron.*, vol. 27, no. 2, pp. 623–627, Feb. 2012.

- [27] X.-D. Do, H.-H. Nguyen, S.-K. Han, D. S. Ha, and S.-G. Lee, "A self-powered high-efficiency rectifier with automatic resetting of transducer capacitance in piezoelectric energy harvesting systems," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 23, no. 3, pp. 444–453, Mar. 2015.

- [28] J. Jiang, W.-H. Ki, and Y. Lu, "Digital 2-/3-phase switched-capacitor converter with ripple reduction and efficiency improvement," *IEEE J. Solid-State Circuits*, vol. 52, no. 7, pp. 1836–1848, Jul. 2017.

- [29] J. Jiang, Y. Lu, C. Huang, W.-H. Ki, and P. K. T. Mok, "A 2-/3-phase fully integrated switched-capacitor DC–DC converter in bulk CMOS for energy-efficient digital circuits with 14% efficiency improvement," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2015, pp. 1–3.

**Jing Wang** received the B.S. degree in microelectronics from Xidian University, Xi'an, China, in 2020. She is currently pursuing the Ph.D. degree with Fudan University, Fudan, China.

Her research interests include ultralow power management systems and piezoelectric energy harvesting systems.

Yi Yang received the B.E. degree in microelectronics from Xidian University, Xi'an, China, in 2020. He is currently pursuing the Ph.D. degree with the School of Microelectronics, Fudan University, Shanghai, China.

His current research interests include power management and energy harvesting.

Zhen Li received the B.S. degree from Anhui University, Hefei, China, in 2016, the M.E. degree from Ningbo University, Ningbo, China, in 2019, and the Ph.D. degree from Fudan University, Shanghai, China, in 2024.

He is currently a Post-Doctoral Researcher at Zhangjiang Laboratory, Shanghai. His research interests encompass piezoelectric energy harvesting systems and power management integrated circuits.

Xun Liu (Member, IEEE) received the B.Eng. degree in electronic and information engineering from Zhejiang University, Hangzhou, China, in 2011, and the Ph.D. degree in electronic and computer engineering from The Hong Kong University of Science and Technology (HKUST), Hong Kong, in 2017.

In 2017, she was a Post-Doctoral Fellow with HKUST and an Engineering Intern with the Department of Power Management IC, Qualcomm Technologies, Inc., San Diego, CA, USA. She was

a Senior Analog Designer with Qualcomm, Santa Clara, CA, USA, from 2018 to 2021. In 2021, she joined Chinese University of Hong Kong (CUHK), Shenzhen, China, as an Assistant Professor. Her research interests include power management integrated circuit (IC) and analog IC design, especially in high-frequency dc-dc converters, hybrid power converters, and power amplifier supply modulator design.

Dr. Liu has been a member of the International Technical Program Committees of the IEEE International Solid-State Circuits Conference (ISSCC) since 2021 and the Eighth International Workshop on Power Supply on Chip (PwrSoC) since 2022. She was a recipient of the President Young Scholar Award from CUHK and the Qualcomm Patent Award in 2020. She was a co-recipient of the ASP-DAC University LSI Design Contest Special Feature Award in 2018. She served as the Session Chair for ISSCC 2022-2024. She also served on the review committee of APCCAS 2022.

Sijun Du (Senior Member, IEEE) received the B.Eng. degree in electrical engineering from Sorbonne University, Paris, France, in 2011, the M.Sc. degree in electrical and electronics engineering from Imperial College, London, U.K., in 2012, and the Ph.D. degree in engineering from the University of Cambridge, Cambridge, U.K., in 2018.

He was with the Laboratory LIP6, Sorbonne University, and then he was a Digital IC Engineer in Shanghai, China, from 2012 to 2014. He was a Post-Doctoral Researcher at Berkeley Wireless

Research Center (BWRC), Department of Electrical Engineering and Computer Sciences (EECS), University of California at Berkeley, Berkeley, CA, USA, from 2018 to 2020. Since 2020, he joined the Department of Microelectronics, Delft University of Technology (TU Delft), Delft, The Netherlands, where he is currently an Assistant Professor. His current research is focused on power management integrated circuit designs.

Jun Han (Member, IEEE) received the B.S. degree from Xidian University, Xi'an, Shanxi, China, in 2000, and the Ph.D. degree in microelectronics from Fudan University, Shanghai, China, in 2006.

He joined Fudan University as an Assistant Professor in July 2006, where he is currently a Full Professor with the State Key Laboratory of Integrated Chips and Systems. His current research interests include domain-specific processors and systems for digital signal processing, machine learning, and human-computer interaction.

Xiaoyang Zeng (Senior Member, IEEE) received the B.S. degree from Xiangtan University, Xiangtan, China, in 1992, and the Ph.D. degree from Changchun Institute of Optics, Fine Mechanics and Physics, Chinese Academy of Sciences, Changchun, China, in 2001.

From 2001 to 2003, he was a Post-Doctoral Researcher at Fudan University, Shanghai, China. Then, he joined the State Key Laboratory of Integrated Chips and Systems, Fudan University, as an Associate Professor, where he is currently a Full

Professor and the Director. His research interests include high-performanceenergy efficient SoC for information security and artificial intelligence applications, and VLSI implementation of digital signal processing and communication systems.

Xinling Yue (Graduate Student Member, IEEE) is currently pursuing the Ph.D. degree in microelectronics with the Electronic Instrumentation Laboratory, Delft University of Technology, Delft, The Netherlands.

She joined the Electronic Instrumentation Laboratory, Delft University of Technology, in December 2020. Her current research interests are energyefficient power management integrated circuits and systems, which include energy harvesting, ac/dc rectifiers, dc/dc converters, and MPPT techniques.

Ms. Yue received the Best Student Paper Award at the 2022 IEEE International Conference on Electronics Circuits and Systems (ICECS), the Student Travel Grant Awards at the 2022 IEEE International Symposium on Circuits and Systems (ISCAS), the 2023 International Solid-State Circuits Conference (ISSCC), and the 2023-2024 Solid-State Circuits Society (SSCS) Predoctoral Achievement Award.

Zhiyuan Chen (Member, IEEE) received the B.Sc., M.Sc., and Ph.D. degrees from the University of Macau (UM), Macau, China, in 2011, 2013, and 2018, respectively.

Since 2018, he has been with the School of Microelectronics, Fudan University, Shanghai, China, as a Post-Doctoral Researcher, where he is currently an Associate Professor. His research interests include ac-dc rectifiers, dc-dc converters, and energy harvesting systems.