# Evaluation of computation-in-memory using traditional (SRAM) and emerging non-volatile devices (memristors)

by

W. Sewnarain

to obtain the degree of Master of Science at the Delft University of Technology.

Student number: 4494245

Supervisor: Prof. Dr. Said Hamdioui

Daily supervisor: Dr. Ing. Anteneh Gebregiorgis

Committee member: Dr. Chang Gao

An electronic version of this thesis is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

# **Abstract**

Modern computer application require large amounts of data processing. Traditional computing models involve constant data transfer between memory and processor. This data transfer is a major contributor to high energy consumption. As these applications scale, the energy demand increases. This poses challenges in terms of sustainability and operational costs. Computation In Memory (CIM) integrates processing within the memory. This reduces the need for data transfer between memory and processor. Potential for drastically lowering energy consumption.

CIM macros are often implemented using modified SRAM cells, though recent literature explores memristor-based CIM designs due to the memristor's low-energy, non-volatile characteristics. How-ever, no comprehensive comparisons between SRAM-based and memristor-based CIM designs exist. While memristor-based designs are hypothesized to be more energy-efficient, this has not yet been proven.

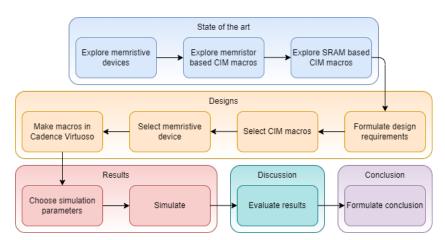

This thesis compares SRAM-based and memristor-based CIM designs to determine which is better suited for CIM applications. This has been achieved by exploring the state of the art of memristive devices, memristor based CIM macros and SRAM based CIM macros. A selection of designs were chosen to compare, including the 1T1R and 8T SRAM design, which are the most popular memristor based and SRAM based CIM designs. The schematics of all the designs were recreated and simulated using as much of the same parameters as possible in all of the designs. A simulation of performing the logic AND and the MAC operation was made. Additionally a layout of the designs was made to extract the area. The designs were compared based on area, energy consumption and delay.

From the results could be concluded that the best device for CIM depends on the application. The memristor design had the smallest area and consumed the least amount of energy for reading, logic and MAC operations. The memristor design also consumed the most amount of energy during writing and the delay for all operations is longer than with the SRAM based designs. If area, energy consumption and delay are equally important for an application, then memristor based CIM would be the better choice only if there are much more logic/read operations than write operations. It could be the better choice for MAC operations if a more energy efficient ADC was used than the one used in this thesis.

# **Contents**

| Al | ostra | ct                                | ii |

|----|-------|-----------------------------------|----|

| 1  | Intro | oduction                          | 1  |

|    | 1.1   | Motivation                        | 3  |

|    | 1.2   | Problem statement                 | 4  |

|    | 1.3   | Thesis contribution               | 4  |

|    | 1.4   | Thesis organization               | 5  |

| 2  | Stat  | te of the art                     | 7  |

|    | 2.1   | Non-volatile devices (memristors) | 7  |

|    | 2.2   | Memristor-based CIM macros        | 10 |

|    | 2.3   | SRAM-based CIM macros             | 12 |

| 3  | Des   | igns                              | 14 |

| -  |       | Design requirements               | 11 |

|    | 3.1   |                                   |    |

|    | 3.2   | Chosen designs                    | 15 |

|    | 3.3   | Chosen memristor technology       | 15 |

|    | 3.4   | SRAM based designs                | 16 |

|    |       | 3.4.1 SRAM macros for logic       | 16 |

|    |       | 3.4.2 SRAM macros for MAC         | 22 |

|    | 3.5   | Memristor based design            | 25 |

|    | 3.6   | Additional components             | 26 |

|    |       | 3.6.1 Input generator             | 26 |

|    |       | 3.6.2 Sense amplifier             |    |

|    |       |                                   |    |

|    |       | 3.6.3 Analog-to-Digital Converter | 27 |

|    | 27    | Lavoute                           | 20 |

iv Contents

| 4   | Res   | ults    |      |      |     |      |      |            |      |     |     |     |     |    |      |      |     |     |     |   |  |  |  |  |  |  |  |  | 33 |

|-----|-------|---------|------|------|-----|------|------|------------|------|-----|-----|-----|-----|----|------|------|-----|-----|-----|---|--|--|--|--|--|--|--|--|----|

|     | 4.1   | Simula  | lati | ion  | se  | tup  |      |            |      |     |     |     |     |    |      |      |     |     |     |   |  |  |  |  |  |  |  |  | 33 |

|     |       | 4.1.1   | F    | ⊃ar  | am  | ete  | rs   |            |      |     |     |     |     |    |      |      |     |     |     |   |  |  |  |  |  |  |  |  | 33 |

|     |       | 4.1.2   | ſ    | Мe   | tho | dol  | ogy  | <i>'</i> . |      |     |     |     |     |    |      |      |     |     |     |   |  |  |  |  |  |  |  |  | 34 |

|     |       | 4.1.3   | (    | Ca   | vea | ts c | of u | sin        | g tl | he  | R   | ed  | Bit | С  | ΝN   | ١.   |     |     |     |   |  |  |  |  |  |  |  |  | 34 |

|     | 4.2   | Schen   | ma   | atic | S.  |      |      |            |      |     |     |     |     |    |      |      |     |     |     |   |  |  |  |  |  |  |  |  | 36 |

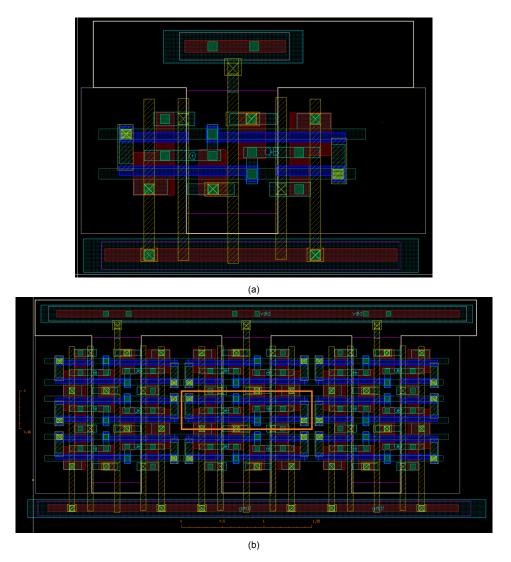

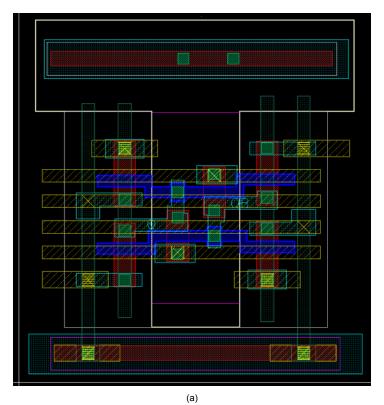

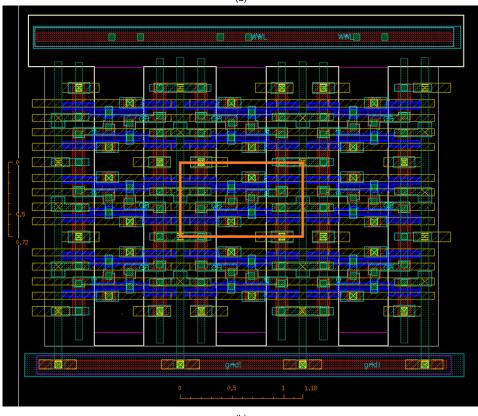

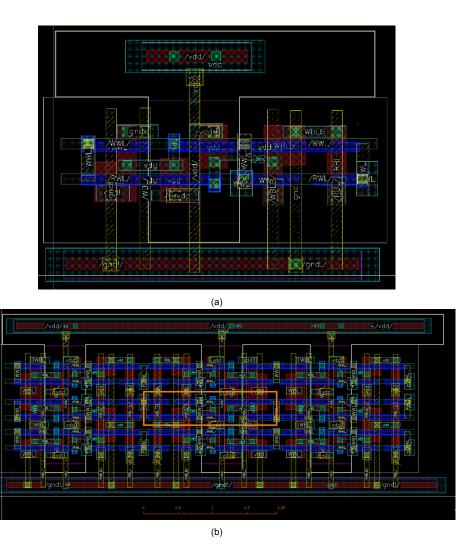

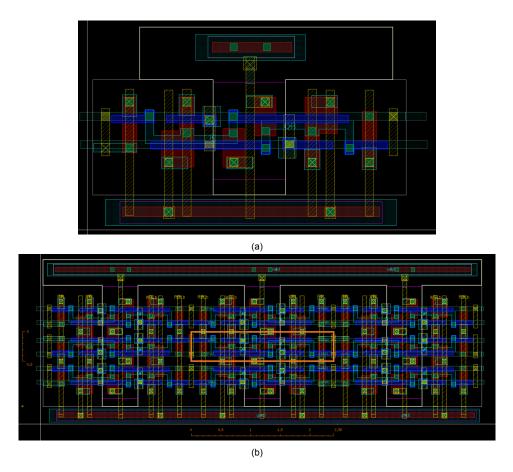

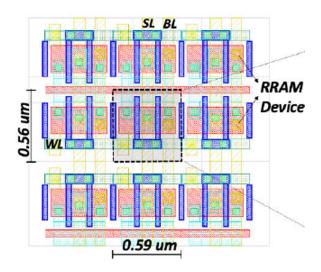

|     | 4.3   | Layou   | uts  |      |     |      |      |            |      |     |     |     |     |    |      |      |     |     |     |   |  |  |  |  |  |  |  |  | 40 |

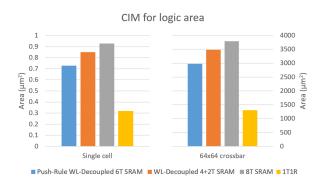

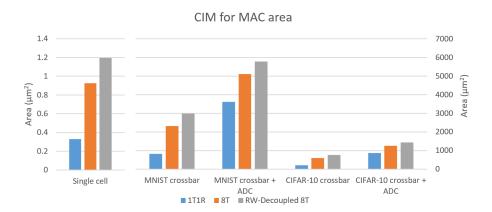

|     | 4.4   | Area.   |      |      |     |      |      |            |      |     |     |     |     |    |      |      |     |     |     |   |  |  |  |  |  |  |  |  | 44 |

|     | 4.5   | Simula  | lati | ion  | res | sult | S.   |            |      |     |     |     |     |    |      |      |     |     |     |   |  |  |  |  |  |  |  |  | 45 |

| 5   | Disc  | ussior  | n    |      |     |      |      |            |      |     |     |     |     |    |      |      |     |     |     |   |  |  |  |  |  |  |  |  | 47 |

| 6   | Con   | clusio  | n    |      |     |      |      |            |      |     |     |     |     |    |      |      |     |     |     |   |  |  |  |  |  |  |  |  | 49 |

| Α   | Com   | npariso | on   | of   | N\  | /Ms  | s in | ı va       | ario | ou  | s v | ΝO  | rk  | S  |      |      |     |     |     |   |  |  |  |  |  |  |  |  | 51 |

| В   | Vario | ous SR  | R.A  | \M   | -ba | sec  | d C  | IM         | ma   | acı | ros | s f | ou  | nd | l ir | ı li | tei | rai | tur | е |  |  |  |  |  |  |  |  | 53 |

| Bil | olioa | raphy   |      |      |     |      |      |            |      |     |     |     |     |    |      |      |     |     |     |   |  |  |  |  |  |  |  |  | 55 |

# Introduction

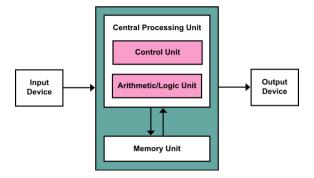

Most modern computers are made using the Von Neumann architecture as shown in Figure 1.1. A computer using this architecture consist of:

- A processing unit. It contains an arithmetic-logic unit (ALU) and registers. The ALU performs the logic operations and the registers contain the data on which the operations need to be performed.

- A control unit. The control unit directs the operation of the processor. It contains an instruction register, which contain the instruction that make up the program, and a program counter.

- **Memory unit**. The memory unit is a separate memory which stores data and instructions (the RAM). When the central processing unit (CPU) needs to perform an operation on data which is not present in the CPU registers (a cache miss), it needs to look for the data in the RAM. The RAM is slower than the CPU cache, but is larger.

There is also external mass storage (HDD or SSD) which is even slower than RAM, but has a higher capacity.

Figure 1.1: Von Neumann Architecture [1].

The Von Neumann architecture is used because of its ability to be easily reprogrammed. Before this architecture was used, computing machines used to be designed for a specific task. It would have a fixed program [2][3].

Since the introduction of the Von Neumann architecture, advancements of computing systems have been made in a couple of ways. The main driver was CMOS scaling [4]. This allowed more transistors to fit on a chip which increases performance, or made more chips to fit on a waver which reduces the

2 1. Introduction

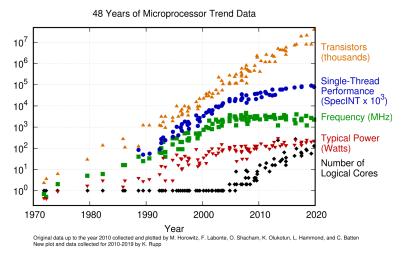

cost of a chip. It also made higher clock speeds possible and lowered power usage by lowering the voltage threshold of the transistors. Since around 2005, performance increase has been realized by increasing the number of logical cores. This in combination with clever techniques like adding multi-threading, branch prediction, out of order execution, etc., has been giving us an exponential increase in computing performance. Unfortunately, this trend is declining as can be seen in Figure 1.2 [5].

Figure 1.2: Microprocessor trend data [6].

The exponential performance increase of processors is declining because we have hit a multiple walls [7].

# CMOS scaling is reaching its limits

When transistors are becoming smaller, they will have a shorter lifetime and higher failure rate [8]. The threshold voltage decreases, which increases the relative sub-threshold leakage [9]. The static leakage could become so large that it might even exceed the dynamic power [10]. CMOS scaling becomes less profitable because of the increased design complexity and test difficulty [11].

# Memory can't keep up with the CPU The memory wall

Data-intensive applications have gained more importance in many domains such as health-care, AI, and economics [11]. In a computer made using the Von Neumann architecture, this means that there will be more frequent data transfer between the CPU and the memory. The processing speed of CPUs has been increasing at a higher rate than the speed of the memory [12]. This increasing gap in speed in combination with the limited memory bandwidth has a huge impact on computation performance. It cost a lot of energy to transfer data between the memory and processor, so frequent data transfer also comes with an increase in energy consumption.

#### We have reached a power limit The power wall

For a while, CPUs were operating at higher frequencies every generation in order to increase the performance. After around 2005, the operating frequency more or less stayed the same which can be seen in Figure 1.2. Increasing the clock speed further would increase the power usage and with that the heat generated by the processor. Due to cooling constraints it would be unfeasible to operate at these higher frequencies [11][12]. The cooling constraints are not the only reason for trying to keep the power usage low. There is an increasing demand for low powered microprocessors for battery powered devices like phones and IoT-devices. There might also be environmental or financial incentive to keep the energy usage of computers low.

# It becomes harder to utilize all logical cores The ILP wall

Processors nowadays consist of multiple logical cores. An easy way to make your code run faster is to make different independent parts of the code run in parallel on different cores. The problem is that we now have so many cores that it becomes difficult to find enough parallelism to make good use of all of the cores [12].

1.1. Motivation 3

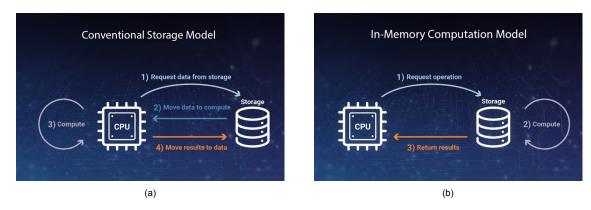

Different computing paradigms and technologies are being explored to try and break the walls that computing systems are facing. One of these paradigms is computation-in-memory (CIM). A computing architecture for in-memory computing can process data in the same location where it is stored. In a computer with a Von Neumann architecture, the CPU would request data from storage. The data will be moved to the CPU. The CPU will perform computations. The results are moved back to the storage. With a CIM architecture, the CPU would request an operation from the storage. The storage will perform the computation and return the results. This is also illustrated in Figure 1.3.

Figure 1.3: (a) Conventional storage model. (b) CIM model [13].

Recent CIM macros proposed in literature perform either logic or MAC operations. A CIM macro for logic can be useful for logic-heavy application like cryptographic security algorithms, edge devices, DNA pattern matching for bio-informatics applications and hamming distance calculation. A CIM macro for MAC can be useful for application with many vector-matrix multiplication operations, like neural networks, signal processing and image compression [14].

A CIM architecture has the potential to help break the memory wall, because if some of the computations can be performed by the memory, then the processor will need to access the memory less often. It could also help to solve the power wall, because transferring data between the memory and processor cost a lot of energy, so when the processor needs to access the memory less often, it will consume less energy. Although a crossbar of cells with a CIM architecture makes it possible to perform many calculations in parallel, the ILP wall refers to the difficulty to parallelize computer programs and CIM doesn't help with that.

# 1.1. Motivation

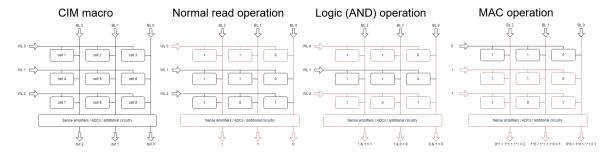

In Figure 1.4 is shown the basics of a CIM macro. A CIM architecture would consist of a crossbar of cells and below each column there would be some additional circuitry that can contain sense amplifiers and ADCs. For reading you would enable just one word-line. For logic operations you would enable two or more word-lines, and for MAC operations you supply a vector of inputs at the world-lines.

Figure 1.4: Basic idea of CIM.

4 1. Introduction

The cells in the crossbar can be modified SRAM cells. It is also being explored to use a new type of non-volatile memory, called memristors. Non-volatile memory is a type of memory that can retain it's data without needing power. It has advantages over SRAM like not needing constant power and being smaller. The disadvantages include being slower than SRAM and having a lower endurance. More about these types of memory can be read in chapter 2.

# 1.2. Problem statement

Unfortunately, there are no comparisons of CIM using SRAM and memristors, so it is not clear which technology would be better suited for CIM. Conducting a meta-analysis by combining data from papers on memristor-based CIM and SRAM-based CIM is difficult. In Table 1.1 is an attempt at comparing different CIM macros. Each paper reports different metrics and different technology nodes, computation operations, voltages, crossbar size, clock frequency, etc. are used.

|                              | 8T SRAM [15] | Push-Rule<br>WL-Dec.<br>6T SRAM [16] | WL-Decoupled<br>4+2T SRAM [17]                 | 8T SRAM<br>CIM With<br>ADC [18] | 6T XNOR<br>SRAM [19] |

|------------------------------|--------------|--------------------------------------|------------------------------------------------|---------------------------------|----------------------|

| Read delay (ps)              | 9.756        |                                      |                                                |                                 |                      |

| Read power (nw)              | 417.4        |                                      |                                                |                                 |                      |

| Read energy                  | 4.069zj      |                                      | 3.96 fJ                                        |                                 |                      |

| Write delay (ps)             | 62.85        |                                      |                                                |                                 |                      |

| Write power (uw)             | 1.579        |                                      |                                                |                                 |                      |

| Write energy (fj)            | 0.09924      |                                      | 4.02                                           |                                 |                      |

| Logic latency                | 1ns          |                                      | 1.3 cycles                                     |                                 |                      |

| Logic energy (fj/bit)        | 21.84        | 0.6                                  | 6.6                                            |                                 |                      |

| Technology node              | 180nm        | 28nm                                 | 55nm DDC                                       | 65nm                            | 28nm                 |

| $V_{DD}$                     |              | 1 V                                  | Read: 0.25 V<br>Write: 0.35 V<br>Logic: 0.35 V | 0.45V / 0.8V                    | 1.0 V                |

| Clock frequency              |              | 787 MHz                              | Read: 4 MHz<br>Write: 2.5 MHz<br>Logic: 15 MHz | 200 MHz                         | 25 MHz               |

| Energy/operation(fJ/Op)      |              |                                      |                                                | 2.04                            | 3.33                 |

| Energy efficiency (TOPS/W)   |              |                                      |                                                | 490-15.8                        |                      |

| Transistors                  | 8T           | 6T                                   | 6T                                             | 8T                              | 6T                   |

| Area/cell (μm <sup>2</sup> ) |              | 0.152                                |                                                | 3.35                            | 0.362                |

| Area/array                   |              |                                      |                                                | $0.055 \ mm^2$                  |                      |

| Array size                   |              | 64x64                                | 128x128                                        | 128x128                         | 256x64               |

| Operations                   | Logic        | Logic                                | Logic                                          | MAC                             | MAC                  |

Table 1.1: Attempt at comparing different CIM macros using data available in literature

A common hypothesis is that memristor-based CIM macros will have higher energy efficiency and occupy a smaller area than SRAM-based CIM macros. However, there is no data proving or disproving this hypothesis. Therefore, it is not possible to make a fair comparison of the two technologies in a CIM macro using the available data in the literature.

# 1.3. Thesis contribution

This thesis seeks to answer the question: Which technology (memristor or SRAM) is better suited for computation-in-memory? This will be accomplished not merely by comparing memristor-based and SRAM-based CIM macros from the literature, but by recreating these designs, simulating them under comparable parameters, and analyzing the simulation results. Through this approach, the following contributions are made:

# Implementation of various SRAM-based CIM designs

Three SRAM-based CIM designs were recreated and tested in this work: Push-Rule WL-Decoupled

6T SRAM, WL-Decoupled 4+2T SRAM, and 8T SRAM. These designs were selected based on their emphasis on logic and MAC (multiply-accumulate) operations, which are central to CIM applications. Schematics from prior works were used as a foundation. Each design was implemented using a consistent set of parameters (e.g., technology node, voltages) to ensure a fair comparison. By simulating these designs under identical conditions, this thesis provides a unified basis for comparison.

#### Implementation of the 1T1R design

The 1T1R design, a popular memristor-based CIM macro, was recreated and analyzed for both logic and MAC operations. This design leverages resistive memory to perform computations in the analog domain, an approach with promising implications for energy efficiency. ReRAM (Resistive Random Access Memory) was chosen as the representative memristor technology due to its scalability and multilevel cell capability. A SPICE model of the ReRAM was used for the recreation of the 1T1R design. While memristor-based designs are hypothesized to excel in energy efficiency and area utilization, empirical comparisons with SRAM-based designs are limited. By implementing a 1T1R design, this research bridges the gap in direct comparisons.

#### Delay, power, and layout-based area estimation

To ensure a comprehensive evaluation, each design was assessed in terms of delay, power consumption, and area efficiency. These metrics are critical in determining the suitability of CIM designs for real-world applications. Each design was implemented in a simulation environment, where logic and MAC computations were tested. Layouts were created to extract accurate area estimations, while simulation tools measured power and delay metrics during operations.

# Quantitative evaluation of SRAM- and memristor-based CIM designs

The core contribution of this thesis lies in the quantitative comparison of SRAM-based and memristor-based CIM designs. This evaluation identifies trade-offs and application-specific advantages of each technology. The results from the individual analyses were combined into a detailed comparison, focusing on area, energy consumption, and delay. An application-specific use case (neural networks) was considered in the analysis. Insights from this work can inform design choices in emerging applications, such as AI accelerators and IoT devices, where energy efficiency and area constraints are critical.

# 1.4. Thesis organization

chapter 2 presents the state-of-the-art analysis. The first part of this chapter discusses various memristor technologies, their working principles, and their respective advantages and disadvantages. The second part explores different types of memristor-based CIM macros. Finally, the third part examines the various SRAM-based CIM macros. chapter 3 details the designs selected for recreation and comparison, their working principles, and the recreation process. The chapter begins by presenting the design requirements used for selecting the designs. Next, the chosen designs are introduced, followed by an explanation of how each design functions and the methods used for their recreation. The chapter concludes with an overview of additional components used in the designs, explaining their functionality and the process of creating them. In chapter 4, the results are presented. The chapter begins with an overview of the simulation setup, followed by the presentation of the layouts. Finally, the performance and energy consumption results are discussed. Following the results, the discussion and conclusion are presented in chapter 5 and chapter 6 respectively. The thesis concludes with the appendix and bibliography. The approach of answering the question 'Which technology (memristor or SRAM) is better suited for computation-in-memory?', is illustrated in Figure 1.5. Each color represents one of the chapters in this thesis.

6 1. Introduction

Figure 1.5: Approach to answer the question: 'Which technology (memristor or SRAM) is better suited for computation-in-memory?'

# State of the art

The first part of this chapter discusses various memristor technologies, their working principles, and their respective advantages and disadvantages. The second part explores different types of memristor-based CIM macros. Finally, the third part examines the various SRAM-based CIM macros.

# 2.1. Non-volatile devices (memristors)

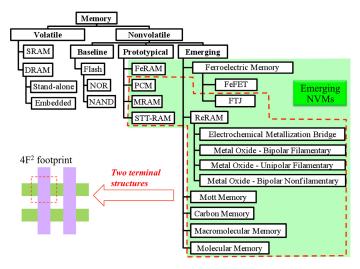

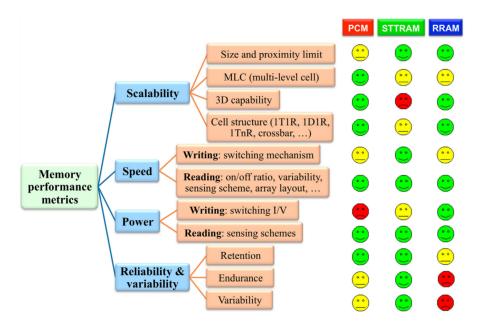

Figure 2.1 shows the memory taxonomy from the 2015 International Technology Roadmap for Semi-conductors (ITRS) Emerging Research Devices (ERD) chapter [20]. Some of the "prototypical" NVM's can also be considered "emerging" [21] so they will be considered as potential candidates for the CIM design as well. All of these devices are based on different technologies, which results in each of them having different benefits and drawbacks.

Figure 2.1: Memory taxonomy from the 2015 ITRS Emerging Research Devices (ERD) chapter [20].

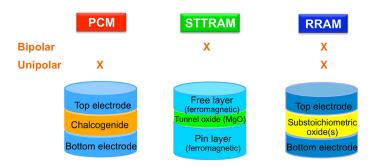

Nine of these emerging NVM technologies were evaluated in a workshop organized by ERD in 2014. PCM, STTRAM and RRAM (also referred to as ReRAM) came out to have the most promising performance. FeFET and FTJ was considered the top choice that needs more resources to explore its potential [21].

8 2. State of the art

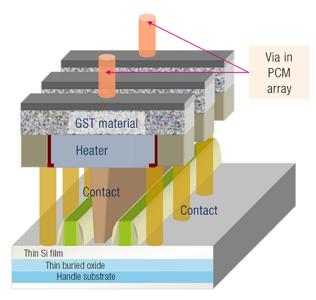

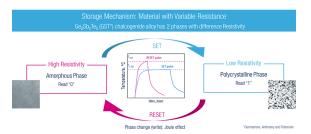

#### Phase Change Memory (PCM)

Figure 2.2 shows the cross section of a PCM bitcell. The GST (Ge-Sb-Te) material is a chalcogenide alloy. Crystallisation occurs in this material when a voltage pulse with low amplitude is applied [22]. This is induced because of joule heating. The crystal structure is broken down (amorphization) when a voltage pulse with high amplitude is applied. In the crystalline phase, the device has a low resistance because of a large concentration of carriers. In the amorphous phase, there is a high resistance because of Fermi level pinning at the mid gap. This process can be seen in Figure 2.3. The time it takes to transition from the amorphous phase to the crystalline phase, called the set process, determines the speed of the PCM [23]. The temperature required to to do the reverse, called the reset process, is the power-limiting step.

Figure 2.2: Cross section of a PCM bitcell [24].

Figure 2.3: Phase change process of PCM [24].

Besides low and high resistance states, it is also possible to to get into intermediate states [11]. This would allow multi-level cell operation. Another advantage of PCMs is that the manufacturing technology is quite mature and is compatible with CMOS. The endurance of PCMs is more than  $10^9$  [25] [26]. This represents the number of switching cycles before the device becomes unreliable. PCMs show desirable scaling behaviors [21]. Citing from [21], the scaling behaviors are: e.g., phase transition at highly scaled dimension (several nm in thin-film thickness or nano-particle diameter), higher crystallization temperature (i.e., longer retention) at smaller dimension, decreasing thermal conductivity (i.e., higher power efficiency) with thinner films, linear dependence of threshold voltage on device size, improved endurance at smaller dimension, etc.

A downside of PCM is the slow programming/switching speed [11][21]. This is due to the slow crystalline process. There is also a resistance drift in the amorphous state that has to be compensated for at circuit level, which further decreases the switching speed.

The performance of PCM devices depends on the phase change materials that are used. They affect the speed and power usage of the device. Doping the GST material might also improve the speed,

endurance and data retention at higher temperatures of the device [27]. Scaling also has a (positive) impact on performance as mentioned before.

# Spin-Transfer Torque RAM (STTRAM)

The structure of a STTRAM can be seen in Figure 2.4. The STTRAM consists of of two ferromagnetic layers and a tunnel layer, that together forms a a magnetic tunnel junction (MTJ) [11]. The *pinned layer* has a fixed magnetization and the magnetization of the free layer can change directions. The two ferromagnetic layers have either magnetization in the same direction (parallel) or in or in opposite directions. Electrons can easily pass through the stack when both layers have parallel magnetization. Therefore the device is in a low resistance state. There is a low probability that electrons pass through the stack when the layers have an anti-parallel magnetization. This is the high resistance state. The magnetization can be controlled by letting a spin-polarized current flow through the magnetic multilayer [28]. This is called the spin-transfer torque (STT) effect.

Figure 2.4: Structure and operation polarity of PCM, STTRAM, and RRAM [21].

STTRAM has the fastest switching speed and best reliability (cycle endurance) among all NVMs [21]. Unfortunately it also has a lot of drawbacks in its current state. It has low energy efficiency, the ferromagnetic materials are not easy to handle and it is challenging to make it compatible with CMOS [11]. It has a small on/off ratio, needs well designed reading schemes and has an increased MTJ variability when scaled [21].

The performance of STTRAM devices is strongly influenced by the manufacturing process. Substrate smoothness, etching damage, encapsulation and materials used for the layers all have a big impact on the performance of the device [21].

#### **Resistive RAM (RRAM)**

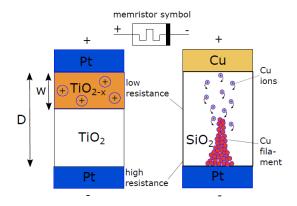

There are three categories of RRAM [29]. You have electrochemical memory (ECM), valence change memory (VCM) and thermochemical memory (TCM). All of them have different mechanisms to generate their resistances. TCMs and ECMs use redoxation and oxidation to build up and break down a structure called filamentary. There are less free electrons when the filamentary is build, so the resistance of the device rises. TCMs are unipolar, which means that polarity doesn't matter when switching states. ECMs are bipolar. Voltage and reversed voltage signals are used to build up and dissolve the metallic filament using redox reactions. VCMs are also bipolar. With them, not only a filament, but also a complete metallic layer is built up and dissolved by the exchange of ions.

Advantages of RRAM are that they offer good scalability [11]. VCM cell sizes can be made in the nanometer range. There is a large difference between the high and low resistance states. This means that simpler CMOS circuits are required to evaluate the resistance. RRAM has fast switching, which is in the nanoseconds range. It also has good compatibility with CMOS manufacturing processes.

RRAM usually has trade-offs between speed-retention, power-speed, endurance-retention, etc [21]. The biggest challenges RRAM has are reliability, variability and failure mechanisms. The resistance and switching voltage varies in each cell and even in each cycle. This is because the location, dimension and composition of the filaments vary in a random manner[30].

RRAM can be made using using different materials for the electrodes and for the resistance changing

10 2. State of the art

Figure 2.5: ECM (left) and VCM (right) RRAMs [29].

layer. Numerous metal oxides and non-oxide have been used to make RRAM (like  $NiO_x$ ,  $HfO_x$ ,  $TiO_x$ , silicon, sulfides, chalcogenides). More recent devices have been made using multi oxide stacks or oxide compositions.

# 2.2. Memristor-based CIM macros

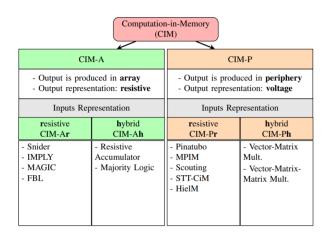

Memristor-based CIM macros can be classified based on input and output data representation [31]. The output of the CIM kernel can be produced in the peripheral circuit in the form of a voltage. Alternatively, the output can be produced in the memory array. When the output is produced in the array, it will be in the form of a resistance in a memristor. The architectures are classified as CIM-P (CIM-Peripheral) and CIM-A (CIM-Array) designs respectively. The location of the input data divides these classes into two sub-classes. CIM designs that require all operands to be in the array, are classified as CIM-Ar and CIM-Pr ('r' for resistive). CIM architectures that only require part of the operands to be in the array are called CIM-Ah and CIM-Ph ('h' for hybrid). The other part of the operands are received via the memory ports as a voltage. An overview of this classification and some popular designs in each class can be seen in Figure 2.6.

Figure 2.6: Classification of memristor-based CIM design styles [31].

Common advantages of CIM-A architectures are that you have maximum parallelism, since the execution in independent of sense amplifiers. You can also have cascading operations without having to feed intermediate results back to the array. The disadvantages are that execution requires the memristive devices to change states. This is a big downside since the endurance of memristive devices is not many cycles. High voltages need to be applied to the memory array during execution, which results in high power consumption and the need of large drivers.

Advantages of CIM-P designs are that they do not change the states of the memristive devices during execution, so computation does not affect the endurance of the device. Low voltages are required to be applied to the array, since the states don't have to change during execution. Because of this, it will have low power consumption and doesn't need large drives. CIP-P designs don't modify the conventional structure of a memory array as much as CIM-A designs, because they focus on modifying the peripheral circuit to realize the operations. CIM-P designs depend on sense amplifiers. A disadvantage because of this is that the level of parallelism depend on the amount of sense amplifiers that is used. A sense amplifier in every column will result in maximum parallelism, but this will also increase the area. Cascading operations is not possible in CIM-Pr architectures since the output is produced as a voltage.

CIM-A architectures change the state of the memristive devices during each computation and memristive devices don't have a high endurance. This makes CIM-A architectures not suitable for any applications using the current state of memristive devices. An example of a CIM-Pr and CIM-Ph architecture is given in the following two paragraphs.

#### Scouting Logic (CIM-Pr design example)

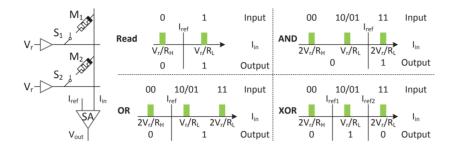

Scouting logic [32] will be used as an example of an CIM-Pr design. Scouting logic is similar to Pinatubo [33], MPIM [34], STT-CiM [35] and Hielm [36] [31]. With scouting logic, you are able to perform the logic functions OR, AND and XOR. The concept can be seen in Figure 2.7.  $M_1$  and  $M_2$  are the two memristors that have the operands stored in their resistive state. The reference current  $I_{ref}$  determines which logical operation is performed. To perform the OR operation, you need to set  $I_{ref}$  between  $2V_r/R_H$  and  $V_r/R_L$ . This works because  $I_{in}$  will be equal or larger than  $V_r/R_L$  if either  $M_1$  or  $M_2$  are in a low resistance state (logical '1'). If one of the memristors is in a high resistance state, then  $I_{in} = V_r/R_L + V_r/R_H$ , which is still equal to approximately  $V_r/R_L$  since  $R_L << R_H$ . For the AND operation you need to set  $I_{ref}$  between  $V_r/R_L$  and  $2V_r/R_L$ . You need both reference currents for the XOR operation. To read the value of a memristor, you need to only enable  $V_r$  on that line.

Figure 2.7: Scouting logic [31].

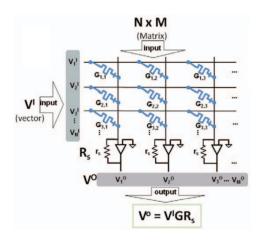

# **Vector-Matrix Multiplication (CIM-Ph design)**

For the CIM-Ph design example we use the design described in [37]. This design is similar to others like [38], [39] and [40]. In Figure 2.8 can be seen how vector  $V=[v_1^I,v_2^I,...,v_N^I]$  is multiplied with matrix  $G=[g_{ij}]$ . The data of matrix G is stored in the resistive value of the memristors. Vector V is provided via the wordlines. The input voltages produce currents with the memristors. These currents represent the multiplication. The input  $v_1^I$  multiplied with the matrix element  $G_{1,1}$  generates the current  $I=\frac{v_1^I}{G_{1,1}}$ . If  $G_{1,1}$  is in the low resistance mode, which represents a '1', then the current is high (if the input was also a '1'). The currents resulting from all the multiplications on the same bitline are added together. Using the reference resistor  $R_S$ , this current produces the output  $v_1^O$ . The output then needs to be converted back to a digital value using an ADC. The input voltages and matrix resistances also don't necessarily have to be binary values.

12 2. State of the art

Figure 2.8: Vector-Matrix multiplication [37].

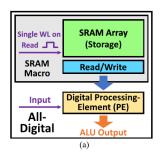

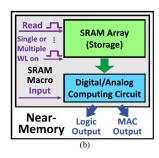

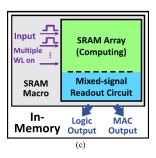

# 2.3. SRAM-based CIM macros

CIM can also be implemented using traditional SRAM. The main advantages of SRAM-CIM are that they have faster switching times and much larger endurance. Just like with memristor-based CIM designs, most recent papers on SRAM-CIM focus on designs which can be used to perform logic or multiplication-accumulation (MAC) operations [14]. SRAM-CIM designs are made by modifying the standard 6T SRAM cells or by adding transistors.

Figure 2.9: Three conceptual approaches to computing: (a) conventional digital computing, (b) near-memory-array computing (NMAC), and (c) in-memory-array computing (IMAC) [14].

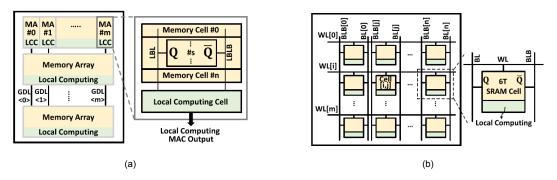

Many schemes for SRAM-based CIM have been proposed in literature. They could be categorized based on where in the memory the computation happens. They could be categorized as as near-memory-array computing (NMAC) or in-memory-array computing (IMAC), see Figure 2.9. In an NMAC scheme, the memory cells and array have the same structure as traditional memory. The computation happens in a circuit block close to the memory-array. With IMAC computation happens in the array. IMAC schemes can be further categorized as in-array local computing (IA-LC), in-cell local computing (IC-LC) and non-local computing, see Figure 2.10. With IA-LC multiple SRAM cells share a set of local computing cells. With IC-LC, each cell has computing circuits embedded in them. With non-local computing, traditional SRAM cells and/or the periphery is modified and the computation is made in the array [14].

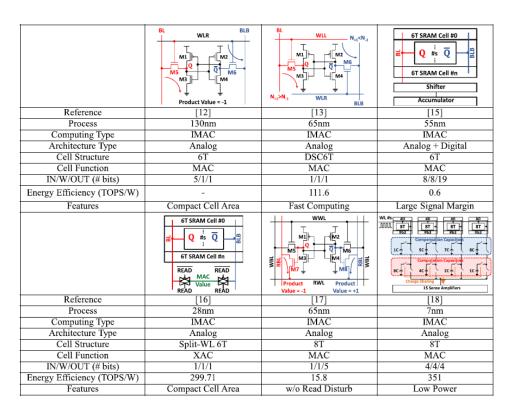

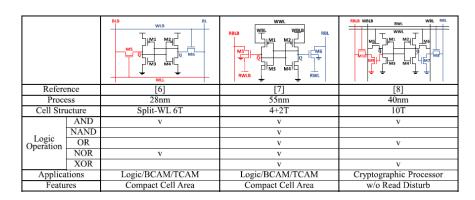

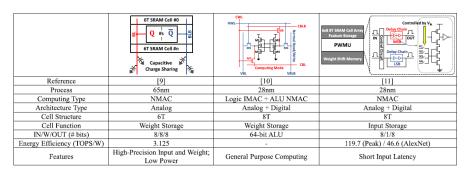

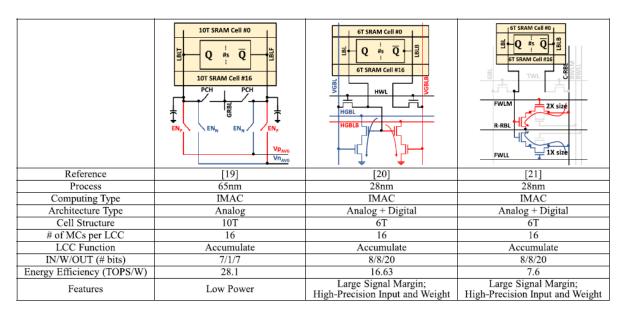

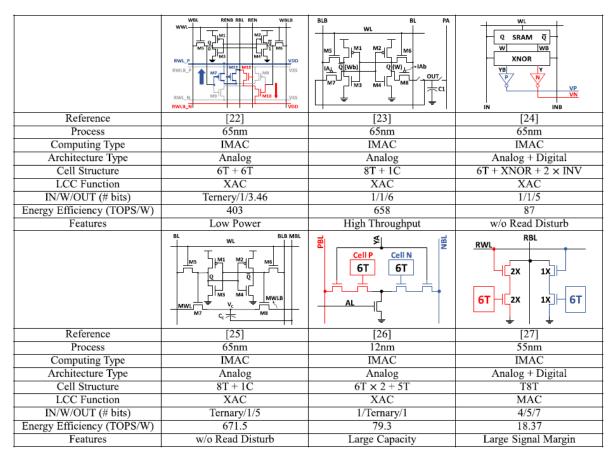

A selection of different SRAM-based CIM macros can be seen in Figure 2.11. Each design has their advantages and disadvantages. A design can focus on different features. They include: high cell density, low read disturb, high precision, low power, short latency, fast computing, large signal margin, high throughput, etc. More examples of SRAM-based CIM macros can be seen in Appendix B. A brief explanation on how each of the designs from these figures work and what their advantages and disadvantages are, can be read in [14].

Figure 2.10: a) In-array local-computing scheme (IA-LC): One local computing cell (LCC) is shared by multiple (n) SRAM cells. b) In-cell local-computing (IC-LC) scheme: Local computing circuits are embedded in each SRAM cell.[14]

Figure 2.11: Comparison table of non local computing (IMAC) CIM schemes [14].

# **Designs**

This chapter outlines the selected designs for recreation and comparison, detailing their working principles and the recreation process. It begins by presenting the design requirements that guided the selection process. The chosen designs are then introduced, followed by an explanation of their functionality. Additional components used in the designs are described next, with an emphasis on their roles and the methods employed in creating them. The chapter concludes with a discussion of the layout design process.

# 3.1. Design requirements

In order to compare the CIM macros, they should be able to perform the same operations. Since most CIM macros are made to perform either logic or MAC operations, it should be a requirement that the chosen designs support either logic or MAC operations. For both technologies (SRAM and memristor), there should be at least one macro for logic and one macro for CIM. Additionally, the designs for logic should have at least one logic operation in common.

In order to get a fair comparison, silicon-verified designs should be used.

To be able to accurately recreate the macros, there should be circuit level info available.

Memristors are being used for CIM with the purpose of giving us higher energy efficiency and smaller area compared to SRAM-based CIM. Most SRAM-based CIM designs already aim to have high energy efficiency and small area, but there are still some that focus more on things like fast computing or low read disturb [14]. In order to see if SRAM-based CIM can outperform memristor-based CIM based on energy consumption and area, it should be a requirement to choose SRAM-based CIM designs that focus on having low energy consumption and small area.

In summary, the designs requirements are:

- Must support either logic or MAC operations.

- Logic designs must have at least one logic operation in common.

- · Should be silicon-verified.

- The design should have circuit level info for verification.

- Should be made for low energy consumption and small area.

3.2. Chosen designs

CIM designs can operate in either the digital or analog domain. However, the majority of memristorbased CIM designs found in literature function in the analog domain. Therefore, this thesis focuses exclusively on analog-based designs.

# 3.2. Chosen designs

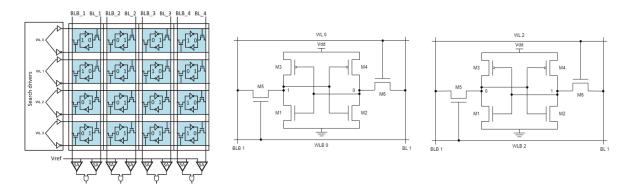

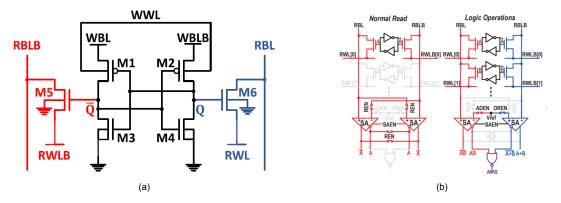

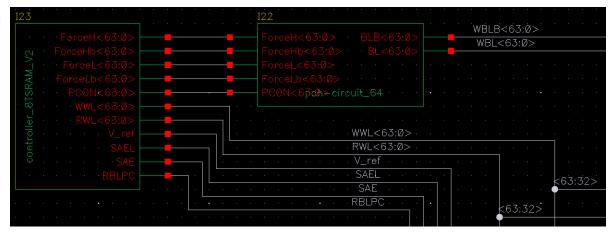

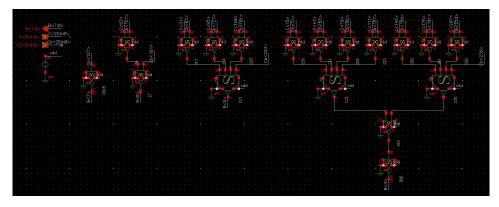

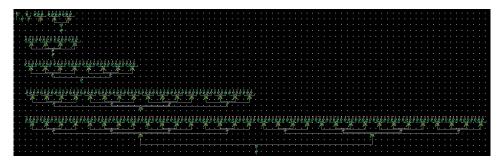

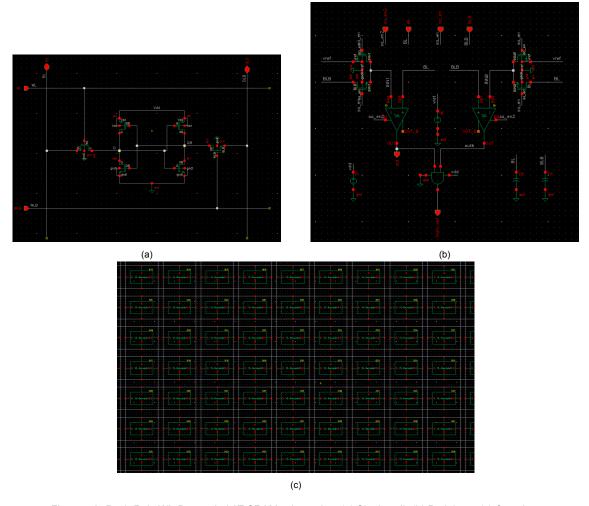

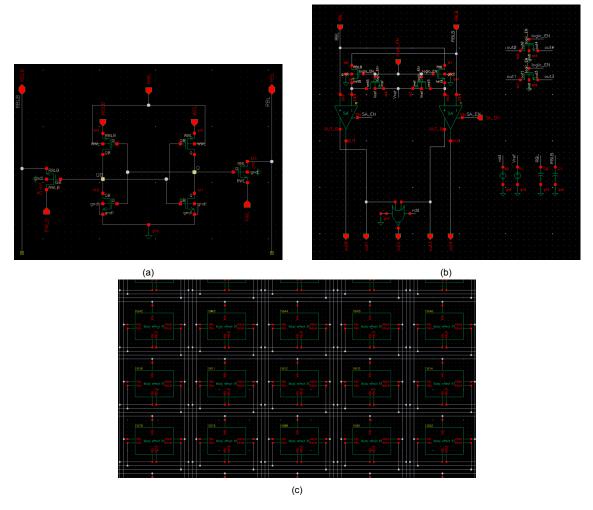

Based on the design requirements, the following designs were chosen: Push-Rule WL-Decoupled 6T SRAM by Jeloka et al. [16], WL-Decoupled 4+2T SRAM by Dong et al.[17], 8T SRAM by A. K. Rajput and M. Pattanaik [15], RW-Decoupled 8T SRAM by Yu et al.[18], and 1T1R by Yu et al. [41]. An overview of the chosen designs can be seen in Figure 3.1. A larger version of the designs schematics is shown further down in this chapter.

| Name                               | Design schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Paper                                                                                                                                                                                                                                                               | Operations     |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Push-Rule WL-<br>Decoupled 6T SRAM |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | S. Jeloka, N. B. Akesh, D. Sylvester and D. Blaauw, "A 28 nm Configurable Memory (TCAM/BCAM/SRAM) Using Push-Rule 6T Bit Cell Enabling Logic-in-Memory," in IEEE Journal of Solid- State Circuits, vol. 51, no. 4, pp. 1009-1021, April                             | AND, NOR       |

| WL-Decoupled 4+2T<br>SRAM          | RBLB WEB RBL RBL RBL RBL RBL RWL BWL BWL BWL BWL BWL BWL BWL BWL BWL B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Q. Dong et al., "A 4 + 2T SRAM for Searching and In-<br>Memory Computing With 0.3-V VDDmin," in IEEE<br>Journal of Solid-State Circuits, vol. 53, no. 4, pp.<br>1006-1015, April 2018                                                                               | AND, OR, XOR   |

| 8T SRAM                            | FWL 1  FWL 1  FWL 2  FWL 2  FWL 2  FWL 2  FWL 2  FWL 2  FWL 3  FW | A. K. Rajput and M. Pattanaik, "Implementation of Boolean and Arithmetic Functions with 8T SRAM Cell for In-Memory Computation," 2020 International Conference for Emerging Technology (INCET), Belgaum, India, 2020, pp. 1-5                                       | NAND, NOR, MAC |

| RW-Decoupled 8T<br>SRAM            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C. Yu, T. Yoo, T. TH. Kim, K. C. Tshun Chuan and<br>B. Kim, "A 16K Current-Based 8T SRAM Compute-In-<br>Memory Macro with Decoupled Read/Write and 1-5bit<br>Column ADC," 2020 IEEE Custom Integrated Circuits<br>Conference (CICC), Boston, MA, USA, 2020, pp. 1-4 | MAC            |

| 1T1R                               | button bu | J. Yu, H. A. D. Nguyen, L. Xie, M. Taouil and S. Hamdioui, "Memristive devices for computation-in-memory," 2018 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 2018, pp. 1646-1651                                           | AND, OR, MAC   |

Figure 3.1: Overview of the chosen designs.

Three SRAM designs for logic were chosen. All three are able to perform the AND operation. The 8T SRAM design is made to perform the NAND operation, but you can take the inverted output of the sense amplifier to get the AND operation. Two designs for MAC have been chosen. One of them is also the 8T SRAM, since it can do both logic and MAC operations. The only difference between the 8T design for logic and the 8T design for MAC is that the logic design has a sense amplifier (SA) in the periphery and the MAC design has an analog to digital converter (ADC). One design has been chosen for the memristor-based CIM. The 1T1R macro is able to perform both logic and MAC operations, just like the 8T SRAM design.

# 3.3. Chosen memristor technology

In chapter 2 was introduced which memristor technologies there are. PCM, STTRAM and RRAM turned out to be the most popular of them. In order to find out which of them would be best suited for CIM, a comparison was made using data from different papers. In Appendix A you will find figures and tables from different papers that were used to make this comparison. In Table 3.1 you will find a summary of the findings. SRAM is also included in this table to show

Each of these devices have their advantages and disadvantages and there is not one that is best at

|                 | SRAM    | Resistive switching | Phase change | Spintronics |

|-----------------|---------|---------------------|--------------|-------------|

| MLC             | No      | Yes                 | Yes          | No          |

| 3D integration  | Good    | Good                | Good         | Limited     |

| Read time (ns)  | Fast    | Fast                | Fast         | Fast        |

| Write time (ns) | Fastest | Medium              | Slow         | Fast        |

| Write power     | Low     | Low                 | High         | Medium      |

| Write energy    | Lowest  | Low                 | High         | Low         |

| Variability     | Low     | High                | Medium       | Low         |

| Endurance       | Best    | Bad                 | Medium       | Good        |

Table 3.1: Characteristics of various memristor technologies and SRAM.

everything. For CIM however, it would be good to have a device that can do MLC, which you can not do with spintronics. PCM has high write power and energy, which would be even more disadvantageous in the large crossbars used for CIM. ReRAM seems to be the best choice for CIM based on this table. Especially when you consider that you can increase the write power to decrease the write time and variability.

# 3.4. SRAM based designs

This chapter is split into two parts. The first part discusses the three SRAM based designs that are made to perform logic operation. The second part will be about the two designs made for MAC operations.

# 3.4.1. SRAM macros for logic

In this section, Push-Rule WL-Decoupled 6T SRAM by Jeloka et al. [16], WL-Decoupled 4+2T SRAM by Dong et al.[17] and 8T SRAM by A. K. Rajput and M. Pattanaik [15] are discussed. Their working principles, together with an example are discussed.

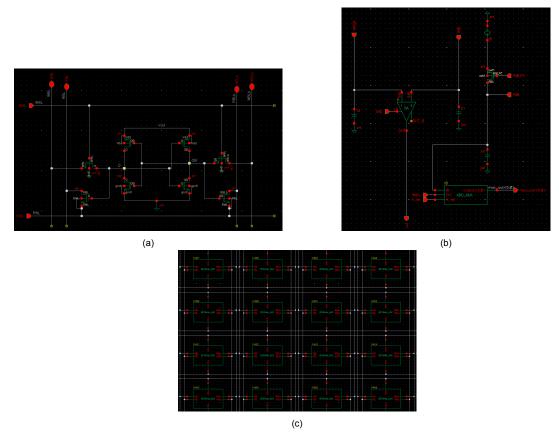

# Push-Rule WL-Decoupled 6T SRAM

#### Working principle

In [16], Jeloka et al. used an existing split-wordline 6T SRAM cell structure [42] to implement logic operations and CAM operations. A CAM operation is where you give some data as in input and retrieve at which address it is stored. The logic AND and NOR operation can be performed using the same design. For our purpose, only the logic operations will be used.

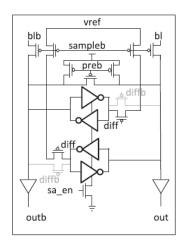

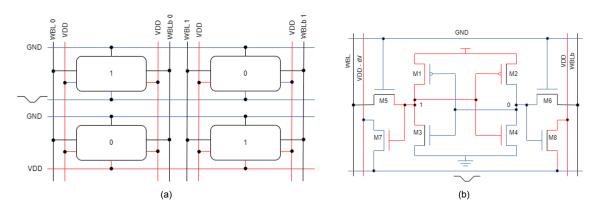

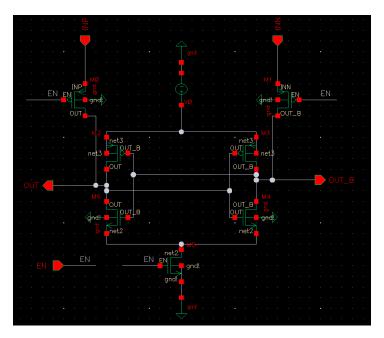

The SRAM cell structure can be seen in Figure 3.3a. In this SRAM cell, the pass gates are decoupled and they are connected to two separate wordlines, the WL and WLB. The sense amplifier is a reconfigurable SA, see Figure 3.2. In logic mode, it will look like Figure 3.3b. The bitline (BL) and bitline bar (BLB) are connected to the positive terminal of of a sense amplifier. The negative terminal is connected to a reference voltage. The output of these sense amplifiers are the input of an AND port. The output of the AND port is the output of the operation. In normal read mode, one of the sense amplifiers has the BL at its positive terminal and the BLB at its negative terminal. The output of the SA is the output of the read operation.

Normal read and write operations are performed in the same way as with traditional 6T SRAM. The WL and WLB have the same input and together act like a single WL. When performing the logic operation, multiple WLs or WLBs are enabled depending on which logic operation is performed and which cells are part of the computation.

The advantages of this design are the small area overhead compared to traditional 6T SRAM cells and the ability to perform CAM operations in addition to logic operations. A disadvantage of this design

Figure 3.2: Push-Rule WL-Decoupled 6T SRAM reconfigurable sense amplifier.

Figure 3.3: (a) Cell structure of Push-Rule WL-Decoupled 6T SRAM (b) AND operation between rows 1 and 3. Rows 2 and 4 are disabled for this operation.[16]

however is that in implementing logic operations, the issue of read disturbance must be considered when computing with many cells on the same bitline.

# Example

Reading and writing is done in the same way as with traditional SRAM. WL and WLB have the same input and together act as a single wordline. An example of performing the AND operation will be given in this section.

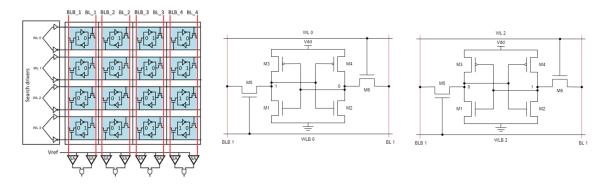

On the left in Figure 3.4 you can see the initial state of the crossbar. Wordlines 0 until 3 store the values "0110", "0101", "1110" and "1110" respectively. On the right side of this image you can see the cells connected to bitline 1 and to wordlines 0 and 2.

The first step of performing the AND operation is charging the bitlines.

Then you enable the wordlines on which you want to perform the operation. In this example wordlines 0 and 2 are enabled. The wordlines that are not used, are masked. Masking a wordline means that both the WL and WLB are not enabled.

What will happen now is that there is a path from bitline 1 to the ground of the cell connected to wordline 0. There is also a path from bitline 1 to the Vdd of the cell connected to wordline 2. The pull down transistors are stronger than the pull up transistors. This causes the pre charged bitline 1 to discharge.

Figure 3.4: Push-Rule WL-Decoupled 6T SRAM logic operation example. Step 0: Initial state.

Figure 3.5: Push-Rule WL-Decoupled 6T SRAM logic operation example. Step 1: Pre-charge bitlines.

The voltage on the bitline falls below the reference voltage of the sense amplifier. The output of the SA connected to the BL becomes 0, so the output of the AND operation becomes 0. If the cell connected to WL 2 also stored a 0, then there would be two paths to ground and the output would be the same. If WL 0 stored a 1 instead of a 0, then there would not be a path to ground and the BL would stay charged. The BLB would also stay charged, because WLB was not enabled. This will cause the output of the AND gate to be a 1.

# WL-Decoupled 4+2T SRAM

#### Working principle

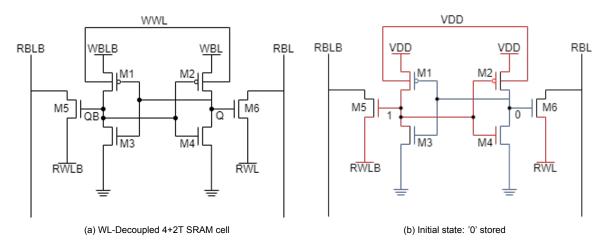

Dong et al.[17] proposed a modified SRAM cell that can perform write operations using only four transistors, see Figure 3.7. This is done by using deeply depleted channel technology (DDC). Transistors with a deeply depleted channel have strong body effect. The body effect in transistors is refers to the change in the threshold voltage when there is a voltage difference between the source and the body of the transistor. The strong body effect of DDC allows this scheme to use the N-well of PMOS M1 and M2 as write wordlines (WWL). Two more transistors (M5 and M6) make it possible to perform the read operation and to perform CAM and logic operations. Figure 3.8 shows the voltages that need to be applied at the different terminals to perform each operation.

The periphery of the WL-Decoupled 4+2T SRAM macro can be seen in Figure 3.7b. During a read/logic operation RBL gets discharged if the cell stores a '1' and RBLB gets discharged if a cell stored '0'. Just like with the Push-Rule WL-Decoupled 6T SRAM design, a reconfigurable SA is used. The design is a little bit different though. In read mode, the two sense amplifiers have the same inputs and consequently the same output. The inverted output of the sense amplifier will be the result of the read operation. In logic mode, one of the sense amplifiers has RBL at its positive input and a reference voltage at its negative input. The other SA has the same reference voltage at the positive input and has RBLB at the negative input. The outputs of the periphery in logic mode can be the results of either the AND, or

Figure 3.6: Push-Rule WL-Decoupled 6T SRAM logic operation example. Step 2: Enable wordlines.

Figure 3.7: (a) WL-Decoupled 4+2T SRAM cell (b) WL-Decoupled 4+2T SRAM read and logic operations[17].

OR operation. The outputs can also be the results of the NAND, AND, XOR, NOR and OR operation, see Figure 3.7b. Which of these two will be the output, depends if you pre-charge RBL, RBLB or both, see Figure 3.8. An example of the write and read/logic operation is given in the next section. This will make the working principle clearer.

|                   |       | WWL                       | WBL                        | WBLB | RWL/ML         | RWLB/MLB       | RBL/SL                        | RBL/SLB                       |

|-------------------|-------|---------------------------|----------------------------|------|----------------|----------------|-------------------------------|-------------------------------|

| Memory            | WRITE | GND(Sel.)<br>VDDH(Unsel.) | GND(Write0)<br>VDD(Write1) |      |                | VDD            | Floating                      | Floating                      |

| Operations        | READ  | VDD*                      | VDD                        | VDD  | GND            | GND            | Precharge(VDD)                | Precharge(VDD)                |

|                   | HOLD  | VDD*                      | VDD                        | VDD  | VDD            | VDD            | Floating                      | Floating                      |

| CAM<br>Operations |       | VDD*                      | VDD                        | VDD  | Precharge(VDD) | Precharge(VDD) | VDD(Search 0)<br>GND(Search1) | GND(Search 0)<br>VDD(Search1) |

| Leade             | AND   | VDD*                      | VDD                        | VDD  | GND            | VDD            | Precharge(VDD)                | Floating                      |

| Logic Operations  | OR    | VDD*                      | VDD                        | VDD  | VDD            | GND            | Floating                      | Precharge(VDD)                |

| Ороганоло         | XOR   | VDD*                      | VDD                        | VDD  | GND            | GND            | Precharge(VDD)                | Precharge(VDD)                |

\*Can also be kept at VDDH.

Figure 3.8: 4+2T SRAM operation table [17].

An advantage of this design is the small area overhead compared to a lot of CIM designs like the 8T SRAM. According to [17], it reduces area overhead by 15% compared to conventional 8T SRAM cells. A disadvantage is that since the WWL is connected to the N-well of transistors M1 and M2, the cells are susceptible to half-select disturbance and data flipping. Applying VDDH to unselect the cells during writing is supposed to alleviate the half-select disturbances.

#### **Example**

This example consists of two parts. In the first part, an example is given of writing to the cell. In the second part, an example is given of performing the read and the logic operation.

Write example

Figure 3.9: WL-Decoupled 4+2T SRAM write operation example.

Figure 3.10: WL-Decoupled 4+2T SRAM write operation example.

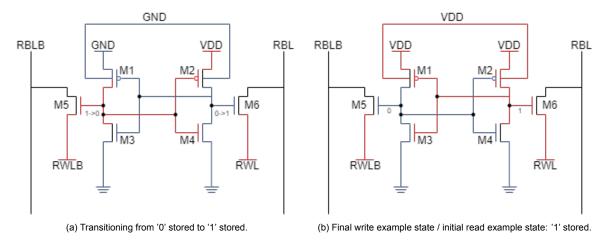

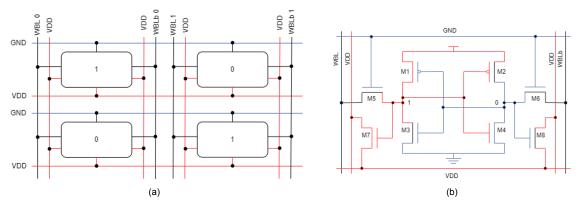

In this example will be shown how you can write a '1' to the cell when a '0' is stored initially. In Figure 3.9a, the WL-Decoupled 4+2T SRAM cell can be seen. When writing to the cell, you only use the transistors M1 to M4. Transistors M5, M6, RBL and RBLB are not used for writing. The initial state of the cell can be seen in Figure 3.9b. This corresponds to the HOLD operation shown in Figure 3.8, which simply means that the cell holds it's stored data and nothing happens. In the figures of this example, red wires mean that there is a high voltage on the wire and blue wires mean that there is a low voltage on there. Black wires mean that it is floating. The cell stores a '0' because the 'Q' wire is blue.

The first step in writing a '1' to the cell is connecting the WWL and the WBLB to ground and connecting the WBL to VDD. The WWL of other rows in the crossbar is set to VHHD, which is a higher voltage than VDD. All other wires do not change. This can also be seen in Figure 3.8 and Figure 3.10a. When WWL is set low, the selected PMOS device becomes much stronger due to its forward body bias. This will short the WBL/WBLB with Q/QB, thus writing into the cell. The WWL in other rows is set to VDDH, which weakens their PMOS devices, preventing anything from being written in the cells. In Figure 3.10 is illustrated what happens during the transition from a '0' stored in the cell to a '1' stored in the cell. The end state when a '1' is stored in the cell is also shown in that figure.

# Read/logic example

For the read example, we look at a cell in which a '1' is stored, see Figure 3.10b. The cell starts in the HOLD state. The reconfigurable SA in the periphery is set in read mode. Both sense amplifiers have RBL at their positive input and RBLB at their negative input. First the RBL and RBLB are pre-charged (Figure 3.11a). Then RWL and RWLB are set to ground (Figure 3.11b). The cell stores a '1', so transistor M6 is enabled. Because of this, there is a path from RBL to ground and RBL is discharged. Once the

Figure 3.11: WL-Decoupled 4+2T SRAM read operation example.

SA is enabled, the output of the sense amplifiers will be '0'. The inverted output of the sense amplifiers present the result of the read operation. The next paragraph will give an example of performing the logic AND operation.

During a logic operation, the reconfigurable sense amplifier is in the logic mode, as described earlier and as shown in Figure 3.7b. Like with the read operation, the cells start in the HOLD state. For the AND operation, RBL needs to be pre-charged. Lastly RWL is connected to ground. The logic operation is performed between two cells in the same column, which means that RWL of both rows need to be connected to ground. If one of the cells stores a '1', then RBL is discharged. If both cells store a '1', then RBL is discharged, but faster. When only one of the cells contain a '1', RBL will be discharged, but it will not have discharged below the reference voltage before the SA is enabled. If both cells store a '0', then RBL will not be discharged and it will also remain above the reference voltage when the SA is enabled. In both cases the output of the SA, which represents the NAND operation, will be '1'. The inverted output of the SA, which represents the AND operation will be '0'. If both cells contain a '1', then RBL will be discharged fast enough that it is below the reference voltage by the time that the SA gets enabled. This will cause the output of the SA to be '0'.

# **8T SRAM**

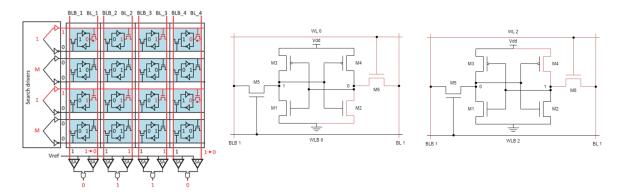

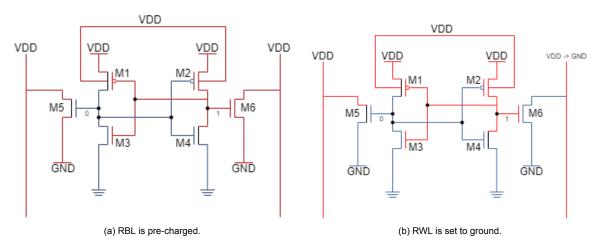

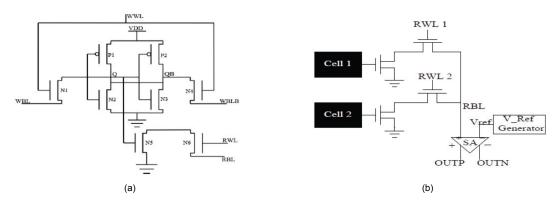

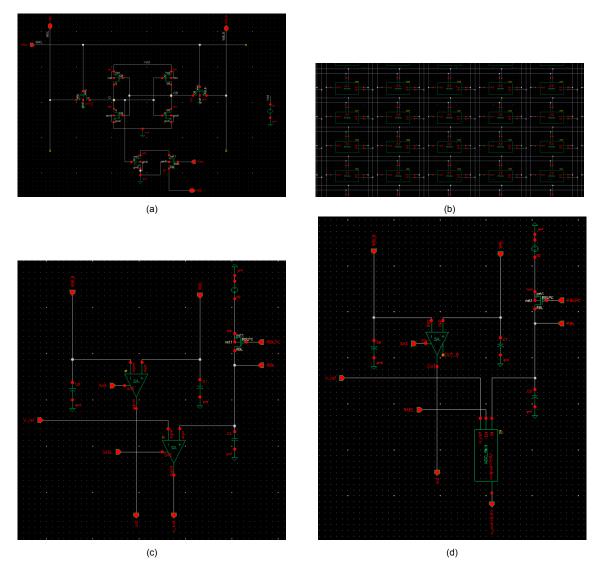

#### Working principle

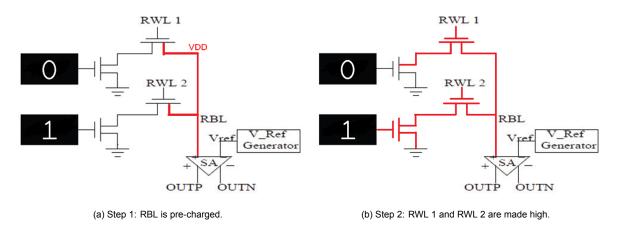

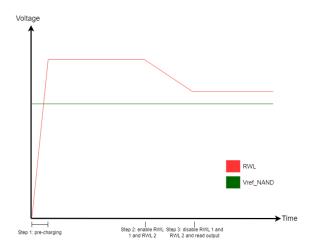

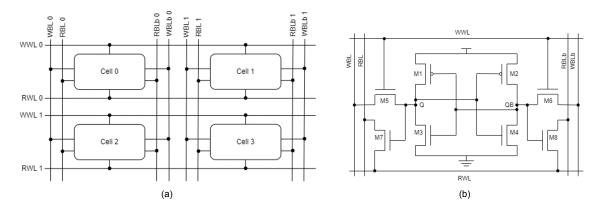

In [15], A. K. Rajput and M. Pattanaik present an 8T SRAM cell design that can be used to perform logic operations. The design is made by adding two additional transistors to the standard 6T SRAM cell, see Figure 3.12a. Logic operations NAND and NOR can be performed in a similar way as with Scouting Logic, which was described in chapter 2. The circuitry that makes it possible for the 6T SRAM part of this design to perform logic operations, can be seen in Figure 3.12b. Cell 1 and cell 2 are normal 6T SRAM cells. RWL 1 or RWL 2 (or both) will be high if you want to use cell 1 or cell 2 for the logic operation. RBL is initially pre charged. If a RWL is high and the corresponding cell stores a '1', then there will be a path from the RBL to ground and the RBL will be discharged. If multiple cells store a '1' and their corresponding RWLs are high, then there will be multiple paths to ground. RBL will then be discharged faster. The reference voltage for the sense amplifier is chosen based on which operation you want to perform.

The advantage of this design is that is has a high read noise margin and energy efficiency according to [15]. A disadvantage is that you require a Vref generator and two sense amplifiers.

#### Example

Reading and writing is performed in the same way as you would read/write to traditional 6T SRAM. In this example will be shown how to perform the NAND operation. Figure 3.12b will be used to illustrate how this operation is performed. In this example, cell 1 will store a '0' and cell 2 will store a '1'.

Figure 3.12: (a) The schematic of 8T SRAM Cell. (b) The circuit schematic for logic operations with 8T SRAM Cell. [15]

Figure 3.13: 8T SRAM NAND operation example.

The first step is to pre-charge the RBL (Figure 3.13a). The second step is to make RWL 1 and RWL 2 high (Figure 3.13b). The transistors connected to RWL 2 and cell 2, are enabled since cell 2 contains a 1 and RWL is high. Because of this, there is a path from RBL to ground and RBL is discharged. The final step is to make RWL 1 and RWL 2 low and to enable the SA. In Figure 3.14 can be seen what the voltage of RBL is, and what Vref for the NAND operation is during the three steps. This is just an illustration of how the voltage of RBL would change during a logic operation. It is not the result of a simulation or a test on silicon. When RWL 1 and RWL 2 were made high, RBL started discharging. At the time of step 3, RBL has been discharged a little bit, but not enough to be below the reference voltage. The resulting output of the sense amplifier will be '1', which is the correct result for the NAND operation.

If both cells stored a '0', then RWL would not discharge and the SA output would still be '1'. If both cells stored a '1', then RBL would discharge faster and it would be below the reference voltage by the time of step 3. This will result in the SA output to be '0'. When you want to perform the OR operation, you set a higher Vref voltage. The voltage is chosen in a way that, at the time of step 3, RBL is higher than Vref if both cells contained a '0'. If one or both cells contain a '1', then RBL has been discharged to below Vref at the time of step 3.

# 3.4.2. SRAM macros for MAC

In this section, 8T SRAM by A. K. Rajput and M. Pattanaik [15] and RW-Decoupled 8T SRAM by Yu et al.[18] are discussed.

Figure 3.14: 8T SRAM RWL and Vref voltage during logic operation.

# 8T SRAM

# Working principle

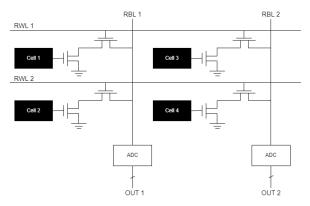

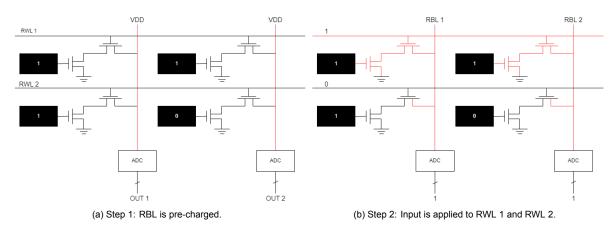

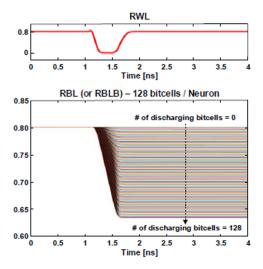

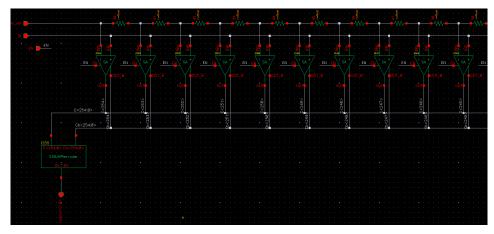

The design of the 8T SRAM macro for MAC operations is almost exactly the same as for logic operations. The circuit is the same with only one exception. The sense amplifier used for logic operations is replaced with an analog to digital converter (ADC). The MAC operation is performed in the same way as the logic operations in the 8T SRAM for logic. The difference is in the way that the RWLs are made high. With the 8T SRAM for logic, you select two rows on which you want to perform the logic operation and make their RWLs high. With the 8T SRAM for MAC, the RWLs are made high based on the input. When you want to multiply the data of a cell in a row with '1', you make the RWL high. When you want to multiply with '0', you make the RWL low. RBL gets discharged faster depending on how many cells containing a '1' are multiplied with an input of '1' in the same column. The ADC converts the amount that the RBL is discharged into a digital output. With a crossbar like Figure 3.15, you can perform the computation shown in Equation 3.1. With the 8T SRAM for logic, there were 3 different voltages that RBL could be by the time that the SA is enabled. With the 8T SRAM for MAC with n cells in a column, there are n+1 possible valtages that RBL can be at, at the time that the ADC is enabled. These voltages are ideally evenly spaced apart. A simulation of the different RBL voltages for a column of 128 cells, can be seen in Figure 3.18. Although this figure is from the paper of the RW-Decoupled 8T SRAM, you would ideally get the same output for all of the CIM MAC macros that are discussed in this thesis.

Figure 3.15: 8T SRAM for MAC 2x2 crossbar.

Figure 3.16: 8T SRAM MAC operation example.

# **Example**

In this example, the calculation in Equation 3.2 will be performed in the crossbar shown in Figure 3.15.

$$\begin{bmatrix} 1 & 1 \\ 1 & 0 \end{bmatrix} \cdot \begin{bmatrix} 1 \\ 0 \end{bmatrix} = \begin{bmatrix} 1 \\ 1 \end{bmatrix} \tag{3.2}$$

The first step is to pre-charge the bitlines (Figure 3.16a). Then the input is applied to the RWLs, which is '1' for RWL 1 and '0' for RWL 2 (Figure 3.16b). The last step is to enable the ADC. The output of the ADC will be the output of the operation.

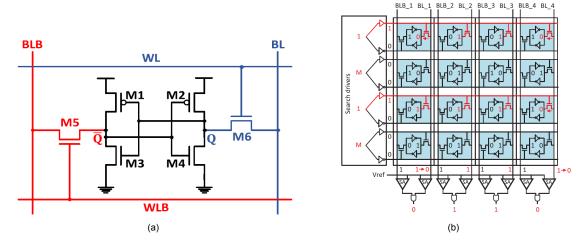

#### **RW-Decoupled 8T SRAM**

# Working principle

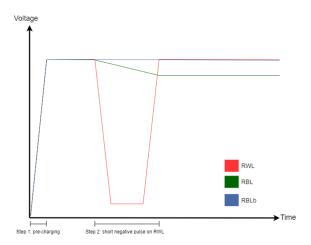

A CIM design by Yu et al.[18] can be seen in Figure 3.17a. Each bitcell has a weight of -1 or +1 stored. A high voltage at Q in the bitcell means that it has a weight of -1 and a low voltage at Q means a weight of +1. A binary 0 can be assigned to the input (RWL) by applying a high voltage. A 1 can be assigned by applying a short negative pulse as seen in Figure 3.18. Multiple of these bitcells can be vertically stacked to make a column-based neuron, see Figure 3.17b. The RBL and RBLb are pre charged to 0.8V. RBL is discharged a little bit when a negative weight is multiplied with a 1 at the input. The same happens at RBLb when a positive weight is multiplied with a 1 at the input. How much RBL and RBLb discharge depend on how many  $1 \cdot 1$  or  $1 \cdot -1$  operations are performed in the same column, see Figure 3.18. The voltage difference between RBL and RBLb represent the accumulated value of the multiplications and can be converted in a digital value using a ADC.

An advantage of this design is that the read and write disturb issue that CIM designs often have, is eliminated by adding the two extra transistors to a 6T SRAM cell. A disadvantage of this design, which is shared with all the CIM designs for MAC, is that an ADCs are needed in each column. An ADC is very large compared to cells and they consume a lot of energy. An ADC could be shared with multiple columns using a MUX. Then the results of each column then need to be calculated one at the time. This is a tradeoff between area and latency that can be made. Another tradeoff that could be made is lowering the resolution of the ADC, which will result in a smaller ADC that consumes less energy, at the cost of the accuracy of the MAC result.

#### Example

Reading and writing to the RW-Decoupled 8T SRAM is done in the same way as with a traditional 6T SRAM cell. In this example, we will look at how a MAC operation is performed. For this example, the 2x2 crossbar shown in Figure 3.19a is used. We will focus on what happens in cell 0, which is shown on the right side in the example images. Cell 0 stores a '1', the input on RWL 0 will be '1' and the input on RWL 1 will be '0'.

Figure 3.17: (a) RW-Decoupled 8T SRAM basic operating principle. (b) Current accumulation in a column-based neuron[18].

The first step is to apply VDD to RWL and to pre-charge RBL and RBLb (Figure 3.20). Next, a short negative voltage pulse is applied on RWL (Figure 3.21). Cell 0 contains a '1'. Because of this, transistor M7 is enabled and shorts RBL with RWL. The negative voltage pulse applied to RWL 0 causes RBL 0 to be discharged by  $\delta V$ . A graph of the voltages of RWL 0, RBL 0 and RBLb 0 over time, can be seen in Figure 3.22. The final step is to enable the ADCs, whose output will be the output of the computation.

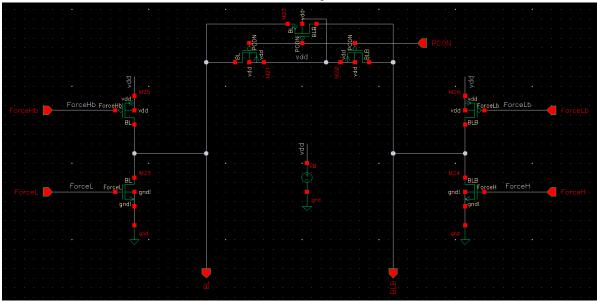

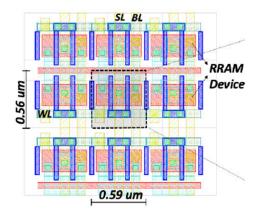

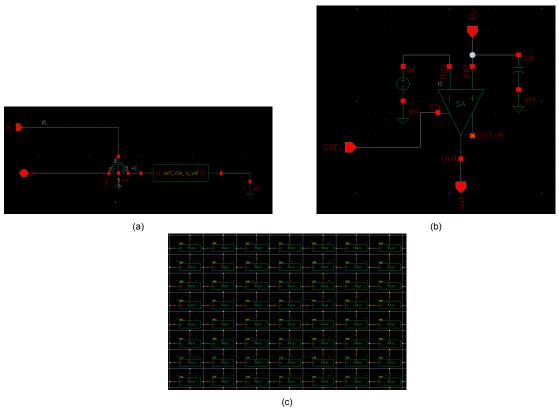

# 3.5. Memristor based design

The most popular CIM-P RRAM designs are based on a one-transistor-one-resistor (1T1R) design. This type of design has received a lot of attention because it provides a reduction of the sneak current problem happening in array applications [43]. Novel applications, such as neuromorphic calculation and in-memory-computing (IMC) architecture, have also been implemented on the 1T1R array structure in the recent decade [44], [45], [46], [47].

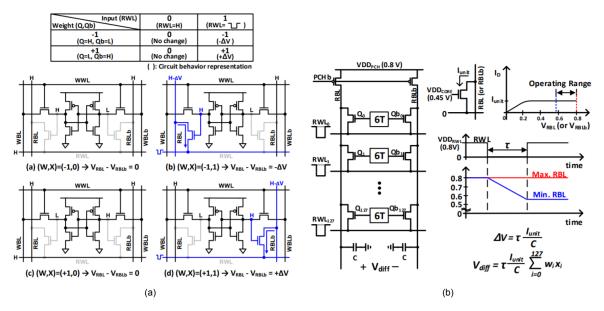

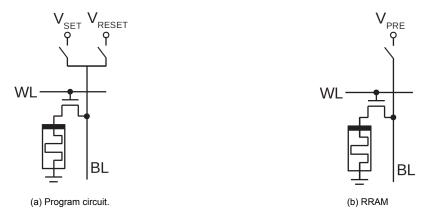

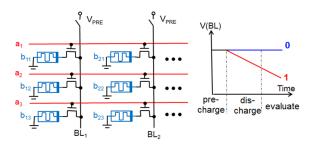

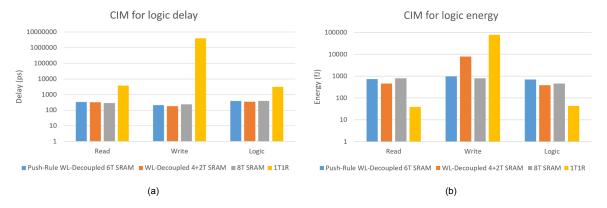

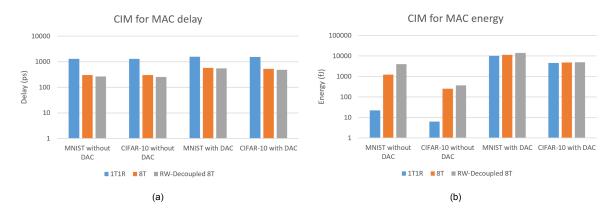

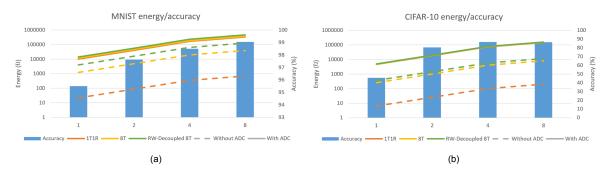

#### Working principle