# A Reduced-Area Low-Power Low-Voltage Single-Ended Differential Pair

J. Mulder, M. van de Gevel, and A. H. M. van Roermund

Abstract— In analog very large scale integratin (VLSI), a high computational density is important. Area savings can be obtained by operating the MOS transistor in the triode region, thus exploiting its symmetrical nature. Applying this theory to a single-ended differential pair results in an area reduction of up to a factor 1.5, which can be significant, e.g., for neural networks, where the basic cells are repeated many times on a single chip. The proposed circuit also has advantages with respect to low-power and low-voltage operation.

Index Terms—Analog VLSI, CMOS analog integrated circuits, neural network hardware.

# I. INTRODUCTION

HIGH computational density is of primary importance in analog neural networks and analog very large scale integratin (VLSI) systems in general [1]. The area required for the implementation of a certain function can often be reduced by exploiting the full functional capacity offered by the MOS transistor. One possibility is to use the body terminal as a second gate [2]–[4]. Another possibility is to use the drain terminal, by operating the MOS transistor in the triode region, instead of in the saturation region [5]–[7].

In this paper, the triode region option is applied to the differential pair. A novel differential pair is proposed which might be interesting, especially for analog neural network applications, where the differential pair is used very often in neurons and synapses, for amplification, to implement the sigmoid function and to facilitate multiplication, e.g., [8]–[10]. Because neurons and especially synapses are repeated many times on a single VLSI neural network chip, area savings in these basic cells becomes significant.

In Section II of this paper, the triode region and the saturation region of the MOS transistor are compared with respect to functionality and a functional relation between the two regions is derived. This theory is applied to the differential pair, in Section III, resulting in the design of a reducedarea low-power low-voltage single-ended differential pair. Measurements in both the weak and strong inversion region are described in Section IV, which verify the operation of the circuit.

# II. MOS TRANSISTOR IN THE TRIODE REGION

A striking characteristic of the MOS transistor is its symmetry with respect to source and drain. This symmetry is apparent from the equation for the drain current  $I_{DS}$  in the triode region. The drain current can be written as the difference of a forward

Manuscript received April 24, 1996; revised July 30, 1996.

The authors are with the Electronics Research Laboratory, Delft University of Technology, 2628 CD, Delft, The Netherlands.

Publisher Item Identifier S 0018-9200(97)01121-9.

current  $I_F$ , which is a function of the source voltage  $V_S$ , and a reverse current  $I_R$ , which is a function of the drain voltage  $V_D$ . In the weak inversion triode region, with the substrate connected to ground, the drain current is given by [11]–[13]

$$I_{DS} = \frac{W}{L} I_o \exp\left(\frac{V_G}{nV_T}\right) \left[\exp\left(\frac{-V_S}{V_T}\right) - \exp\left(\frac{-V_D}{V_T}\right)\right]$$

$$= I_F - I_R \tag{1}$$

where W and L are the width and length of the transistor,  $I_o$  is the zero-bias current, n is the subthreshold slope factor,  $V_T$  is the thermal voltage kT/q and  $V_G$ ,  $V_D$ , and  $V_S$  are the gate, drain, and source voltage, respectively, referenced to the substrate.

In the strong inversion triode region, the MOS transistor shows the same symmetry with respect to its source and drain. The drain current in the strong inversion triode region is given by [12], [13]

$$I_{DS} = \frac{W}{L} \frac{\beta}{2} \left[ (V_G - V_S - V_{th})^2 - (V_G - V_D - V_{th})^2 \right]$$

=  $I_F - I_R$  (2)

where  $\beta$  is the transconductance factor and  $V_{th}$  is the threshold voltage.

Further, (1) and (2) are very similar to the equations for the drain current in the saturation region. The reverse current  $I_R$  tends to zero when  $V_D \gg V_T$  or  $V_D > V_G - V_{th}$ , in the weak and strong inversion regions, respectively.

In the weak inversion saturation region, the drain current is described by [11]–[13]

$$I_{DS} = \frac{W}{L} I_o \exp\left(\frac{V_G}{nV_T}\right) \exp\left(\frac{-V_S}{V_T}\right)$$

$$= I_F. \tag{3}$$

And in the strong inversion saturation region,  $I_{DS}$  is given by

$$I_{DS} = \frac{W}{L} \frac{\beta}{2} (V_G - V_S - V_{th})^2$$

$$= I_F.$$

(4)

Note that (3) and (4) are in fact *simplified* versions of (1) and (2). As a consequence, the functional capacity of an MOS transistor operating in the triode region is higher than the functional capacity of an MOS transistor operating in the saturation region, where the drain terminal has lost control over the drain current.

More specifically: One transistor operating in the triode region is equivalent to two fictitious transistors operating in the saturation region. The drain current of one fictitious transistor is  $I_F$  and the drain current of the other fictitious transistor is  $I_R$ .

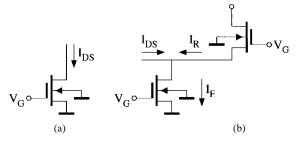

Fig. 1. Equivalence of: (a) one transistor operating in the triode region and (b) two transistors operating in the saturation region.

Fig. 2. (a) Conventional and (b) novel single-ended differential pair.

Since the difference of the fictitious drain currents  $I_F$  and  $I_R$  has to equal the actual drain current  $I_{DS}$ , see (1) and (2), it follows from Kirchhoff's Current Law that the drain of one fictitious transistor is connected to the source of the other fictitious transistor. This is illustrated in Fig. 1.

Further, both fictitious transistors have the same gate and substrate potential, and the same aspect ratio W/L, which follows directly from (1)–(4).

# III. CIRCUIT DESCRIPTION

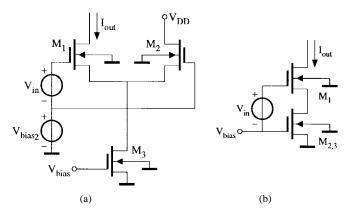

A differential pair is biased by a tail current source. In practice, this source is often implemented by a single transistor, which is biased at a certain gate voltage, in most cases the input voltage of a simple current mirror. A single-ended differential pair is shown in Fig. 2(a), where all MOS transistors operate in the saturation region.

The equivalence derived in the preceding section can be exploited to simplify this differential pair. Since the two transistors  $M_2$  and  $M_3$ , which operate in the saturation region, are biased at a dc gate voltage, and the source of  $M_2$  is connected to the drain of  $M_3$ , they can be combined into one MOS transistor operating in the triode region. The novel single-ended differential pair thus obtained is shown in Fig. 2(b). The circuit has a single-ended input and output, but in many situations this limitation poses no problem.

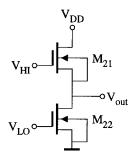

The proposed circuit looks very similar to a differential voltage amplifier published by Johnson in [14], shown in Fig. 3, and therefore, it might be interesting to highlight the differences between these circuits.

First, the body terminal of  $M_{21}$ , shown in Fig. 3, is connected to its source. The body terminals of all transistors

Fig. 3. Differential voltage amplifier [14].

shown in Fig. 2 are connected to ground. The equivalence relation between  $M_2$  and  $M_3$  in Fig. 2(a) and  $M_{2,3}$  in Fig. 2(b) is only valid if  $M_2$  and  $M_3$  have the same body potential, as explained in the previous section.

Second, both transistors  $M_{21}$  and  $M_{22}$ , shown in Fig. 3, operate in the (strong inversion) *saturation* region. Transistor  $M_{2,3}$ , shown in Fig. 2(b) operates in the *triode* region.

As a result of the above two differences, the proposed circuit has a completely different transfer function than Johnson's circuit. The circuit shown in Fig. 3 acts as a differential voltage amplifier with unity gain. The output  $voltage\ V_{\rm out}$  equals the difference of the two input voltages  $V_{\rm HI}$  and  $V_{\rm LO}$ . The output signal of the proposed differential pair is a current. The transfer function describing the relation between the input voltage  $V_{\rm in}$  and the output current  $I_{\rm out}$  is exactly equal to the transfer function of the conventional differential pair. Only for very large values of  $V_{\rm in}$ , when the differential pair is used beyond its usual range of operation, do the circuits become identical, except for the body terminal connection of  $M_{21}$ .

An expression for the output current  $I_{\rm out}$  of the proposed differential pair can be found by applying (1)–(4) to the differential pair shown in Fig. 2(b). Applying (1) and (3), valid in the weak inversion region, to  $M_{2,3}$  and  $M_1$ , respectively, yields

$$I_{\text{out}} = \frac{W}{L} I_o \exp\left(\frac{V_{\text{bias}}}{nV_T}\right) \left[1 - \exp\left(\frac{-V_{S1}}{V_T}\right)\right]$$

(5)

$$I_{\text{out}} = \frac{W}{L} I_o \exp\left(\frac{V_{\text{bias}} + V_{in}}{nV_T}\right) \exp\left(\frac{-V_{S1}}{V_T}\right)$$

(6)

where  $V_{S1}$  is the source voltage of  $M_1$ .

Since  $V_{\rm bias}$  is assumed to be the input voltage of a current mirror, we can find an expression for  $V_{\rm bias}$  in terms of the input current  $I_{\rm bias}$  of this current mirror, using (3)

$$V_{\text{bias}} = nV_T \ln \left(\frac{L}{W} \frac{I_{\text{bias}}}{I_o}\right).$$

(7)

We can use this equation to eliminate  $V_{\rm bias}$  from (5) and (6). Further, a closed expression for  $I_{\rm out}$  can be obtained by elimination of  $V_{S1}$  from (5) and (6). This yields

$$I_{\text{out}} = \frac{1}{2} I_{\text{bias}} \left[ 1 + \tanh\left(\frac{V_{in}}{2nV_T}\right) \right].$$

(8)

This equation is exactly equal to the equation describing the conventional differential pair shown in Fig. 2(a). Since the large-signal transfer function is identical, the small-signal transconductance gain of the proposed differential pair will also be equal to the gain of the conventional differential pair.

In strong inversion, two equations for  $I_{\rm out}$  are found by applying (2) and (4) to  $M_{2,3}$  and  $M_1$ , respectively

$$I_{\text{out}} = \frac{W}{L} \frac{\beta}{2} \left[ (V_{\text{bias}} - V_{th})^2 - (V_{\text{bias}} - V_{S1} - V_{th})^2 \right]$$

(9)

$$I_{\text{out}} = \frac{W}{L} \frac{\beta}{2} \left( V_{\text{bias}} + V_{\text{in}} - V_{S1} - V_{th} \right)^2.$$

(10)

From these expressions,  $V_{\rm bias}$  can again be eliminated, if we assume  $V_{\rm bias}$  to be the input voltage of a current mirror, given by

$$V_{\text{bias}} = \sqrt{\frac{L}{W}} \frac{2}{\beta} I_{\text{bias}} + V_{th}. \tag{11}$$

Next, a closed expression for  $I_{\rm out}$  is found by eliminating  $V_{S1}$  from (9) and (10)

$$I_{\text{out}} = \frac{I_{\text{bias}}}{2} - \frac{W}{L} \frac{\beta}{2} V_{\text{in}} \sqrt{\frac{L}{\beta W} I_{\text{bias}} - \left(\frac{V_{\text{in}}}{2}\right)^2}.$$

(12)

This equation is exactly equivalent to the transfer function of the conventional differential pair in strong inversion.

For analog VLSI applications, the most important advantage of the proposed circuit is a reduction of the required chip area. Instead of two transistors  $M_2$  and  $M_3$ , with equal aspect ratio, only one transistor  $M_{2,\,3}$  is necessary. If  $M_1,\,M_2$ , and  $M_3$  have equal dimensions, the required area is reduced by a factor of about 1.5.

The proposed differential pair also has advantages with respect to low-voltage and low-power operation. First, no voltage has to be wasted on keeping  $M_3$  in the saturation region. In weak inversion, about 100 mV for both the input and the output voltage range is gained, which is significant, e.g., for single-battery operation where the supply voltage can be as low as 1 V [15].

Second, the total current consumption is equal to the output current and not to the tail current, which comes down to a factor of one half at the bias point; see (8) and (9).

#### IV. MEASUREMENT RESULTS

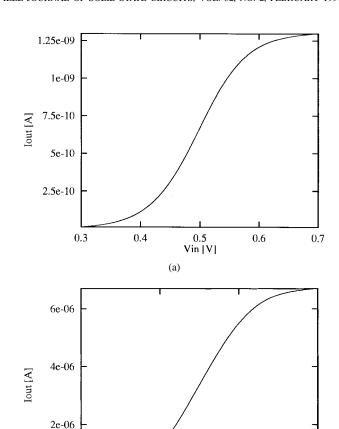

Measurements were performed, using a transistor array, to verify the principle described above. Transistors from a standard 2.5- $\mu$ m process were used. The typical values of the most important parameters are  $V_{th}=0.75~\rm V$ ,  $\beta=48~\mu A/\rm V^2$ , and the K-factor, modeling the body-effect, is  $0.28\sqrt{\rm V}$ . The dimensions of the transistors used are  $W=108~\mu \rm m$  and  $L=7~\mu \rm m$ .

Measurements were performed both for operation in the weak and in the strong inversion region, by biasing the circuit at  $V_{\rm bias} = 0.5$  and 0.9 V, respectively. The results are shown in Fig. 4. Both figures clearly show the well-known input-output characteristic of the differential pair in weak and in strong inversion.

Fig. 4. Measured output current: (a) weak and (b) strong inversion.

0.8

1

12

0.6

# V. CONCLUSIONS

(b)

Vin [V]

By exploiting the relation between the operation of an MOS transistor in the saturation and in the triode region, a higher functional density can be obtained. This was demonstrated for the single-ended differential pair, where the required area is reduced by a factor of up to 1.5, which can be significant in analog VLSI applications, e.g., in neural networks, where the differential pair is often used in neurons and synapses, which are repeated many times on a chip. Other advantages of the proposed differential pair are low-power and low-voltage operation.

## REFERENCES

- [1] A. H. Kramer, "Array-based analog computation: Principles, advantages and limitations," in *Proc. MicroNeuro*, 1996, pp. 68–79.

- [2] M. H. Cohen and A. G. Andreou, "Current-mode subthreshold MOS implementation of the Herault–Jutten autoadaptive network," *IEEE J. Solid-State Circuits*, vol. 27, no. 5, pp. 714–727, May 1992.

- [3] M. v. d. Gevel and J. C. Kuenen, "\(\sqrt{x}\) circuit based on a novel, back-gate-using multiplier," Elec. Lett., vol. 30, no. 3, pp. 183–184, Mar. 1994.

- [4] J. Mulder, A. C. van der Woerd, W. A. Serdijn, and A. H. M. van Roermund, "Application of the back gate in MOS weak inversion translinear circuits," *IEEE Trans. Circuits Syst.—I*, vol. 42, pp. 958–962, Nov. 1995.

- [5] K. Bult and G. J. G. M. Geelen, "An inherently linear and compact MOST-only current division technique," *IEEE J. Solid-State Circuits*, vol. 27, pp. 1730–1735, Dec. 1992.

- [6] E. A. Vittoz and X. Arreguit, "Linear networks based on transistors," Elec. Lett., vol. 29, no. 3, pp. 297-299, Feb. 1993.

- [7] M. H. Cohen and A. G. Andreou, "MOS circuit for nonlinear Hebbian learning," Elec. Lett.,, vol. 28, no. 9, pp. 809-810, Apr. 1992.

- [8] A. J. Annema, "Analysis, modeling and implementation of analog integrated neural networks," Ph.D. dissertation, Twente University, Enschede, Netherlands, 1994.

- [9] L. Merlat and N. Silvestre, "A Hindmarsh and Rose-based electronic burster," in *Proc. MicroNeuro*, 1996, pp. 39–44. [10] D. J. Mayes, A. F. Murray, and H. M. Reekie, "Pulsed VLSI for RBF

- neural networks," in Proc. MicroNeuro, 1996, pp. 177-184

- [11] E. Vittoz and J. Fellrath, "CMOS analog integrated circuits based on weak inversion operation," IEEE J. Solid-State Circuits, vol. SC-12, pp. 224-231, Mar. 1977.

- [12] Y. P. Tsividis, Operation and Modeling of the MOS Transistor. New York: McGraw-Hill, 1987.

- [13] C. C. Enz, F. Krummenacher, and E. A. Vittoz, "An analytical MOS transistor model valid in all regions of operation and dedicated to lowvoltage and low-current applications," Analog IC Sig. Proc., vol. 8, no. 1, pp. 83-114, July 1995.

- [14] M. G. Johnson, "An input-free  $V_T$  extractor circuit using a two-transistor differential amplifier," IEEE J. Solid-State Circuits, vol. 28, pp. 704–705, June 1993.

- W. A. Serdijn, A. C. v. d. Woerd, A. H. M. v. Roermund, and J. Davidse, "Design principles for low-voltage low-power analog integrated circuits," Analog Int. Circuits Sig. Proc., vol. 8, pp. 115-120,