## Non-Binary Spin Wave Based Circuit Design

Mahmoud, Abdulqader Nael; Vanderveken, Frederic; Ciubotaru, Florin; Adelmann, Christoph; Hamdioui, Said: Cotofana, Sorin

10.1109/TCSI.2022.3187654

**Publication date** 2022

**Document Version** Final published version

Published in

IEEE Transactions on Circuits and Systems I: Regular Papers

Citation (APA)

Mahmoud, A. N., Vanderveken, F., Ciubotaru, F., Adelmann, C., Hamdioui, S., & Cotofana, S. (2022). Non-Binary Spin Wave Based Circuit Design. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 69(10), 3888-3900. https://doi.org/10.1109/TCSI.2022.3187654

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# Non-Binary Spin Wave Based Circuit Design

Abdulqader Nael Mahmoud<sup>®</sup>, *Graduate Student Member, IEEE*, Frederic Vanderveken<sup>®</sup>, Florin Ciubotaru<sup>®</sup>, *Member, IEEE*, Christoph Adelmann<sup>®</sup>, Said Hamdioui<sup>®</sup>, *Senior Member, IEEE*, and Sorin Cotofana<sup>®</sup>

Abstract-By their very nature, Spin Waves (SWs) excited at the same frequency but different amplitudes, propagate through waveguides and interfere with each other at the expense of ultra-low energy consumption. In addition, all (part) of the SW energy can be moved from one waveguide to another by means of coupling effects. In this paper we make use of these SW features and introduce a novel non Boolean algebra based paradigm, which enables domain conversion free ultra-low energy consumption SW based computing. Subsequently, we leverage this computing paradigm by designing a non-binary spin wave adder, which we validate by means of micro-magnetic simulation. To get more inside on the proposed adder potential we assume a 2-bit adder implementation as discussion vehicle, evaluate its area, delay, and energy consumption, and compare it with conventional SW and 7 nm CMOS counterparts. The results indicate that our proposal diminishes the energy consumption by a factor of 3.14x and 6x, when compared with the conventional SW and 7 nm CMOS functionally equivalent designs, respectively. Furthermore, the proposed non-binary adder implementation requires the least number of devices, which indicates its potential for small chip real-estate realizations.

*Index Terms*—Spin-waves, spin-wave computing, non-binary computing, non-binary to binary converter, spin wave non-binary adder, energy.

#### I. INTRODUCTION

URING the past decades, the human society experienced an information technology revolution that resulted in a huge raw data increase, which processing requires efficient computing platforms ranging from high-performance clusters to simple Internet of Things (IoT) nodes [1], [2]. Thus far, CMOS downscaling is providing the means to meet the energy and performance requirements [3], however, this becomes more and more difficult due to var-

Manuscript received 1 March 2022; revised 23 May 2022; accepted 20 June 2022. Date of publication 6 July 2022; date of current version 29 September 2022. This work was supported in part by the European Union's Horizon 2020 Research and Innovation Program within the FET-OPEN Project CHIRON under Grant 801055 and in part by IMEC's Industrial Affiliate Program on Beyond-CMOS Logic. The work of Frederic Vanderveken was supported by the Research Foundation—Flanders (FWO) under Grant 1S05719N. This article was recommended by Associate Editor Y. Zhang. (Corresponding author: Abdulqader Nael Mahmoud.)

Abdulqader Nael Mahmoud is with the Computer Engineering Laboratory, Delft University of Technology, 2628 CD Delft, The Netherlands, and also with NXP Semiconductor, 6534 AE Nijmegen, The Netherlands (e-mail: a.n.n.mahmoud@tudelft.nl).

Frederic Vanderveken, Florin Ciubotaru, and Christoph Adelmann are with IMEC, 3001 Leuven, Belgium (e-mail: frederic.vanderveken@imec.be; florin.ciubotaru@imec.be; christoph.adelmann@imec.be).

Said Hamdioui and Sorin Cotofana are with the Computer Engineering Laboratory, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: s.hamdioui@tudelft.nl; s.d.cotofana@tudelft.nl).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TCSI.2022.3187654.

Digital Object Identifier 10.1109/TCSI.2022.3187654

ious technological hurdles predicting that Moore's Law will soon come to the end because of [4]: (i) Leakage wall [5], [6], (ii) Reliability wall [4], and (iii) Cost wall [4], [5]. Therefore, to keep the pace with the exploding market needs, novel alternative technologies are under investigation, e.g., graphene [7]-[10], memristors [11]-[15], and spintronics [16]-[20]. Different spintronics technologies have been developed based on, e.g., magnetization switching [21], Skyrmions generation [22], [23], rectified tunnel magnetoresistance [24], anomalous Hall effect, and negative differential resistance magnetic tunnel junctions [25]. However they exhibit relatively high energy consumption as they operate at very high current densities (of  $10^{11}$  to  $10^{12}$  A/m<sup>2</sup>). On the other hand, Spin Wave (SW) stands apart as one of the most promising spintronic avenue because [3], [26]–[30] it provides: (i) ultra-low energy consumption (relies on SW interference and not on charge movement), (ii) acceptable delay, and (iii) high scalability (SW wavelengths can reach down to nanometer range). Therefore, new ultra-low power circuit designs based on spin-wave are of great interest.

In view of the above, different SW logic gates and circuits were presented [28]-[56]. Single-output logic gates including (N)AND, (N)OR, and X(N)OR were reported in [31]-[33], whereas multi-output SW logic gates were suggested in [28], [29]. Moreover, multi-frequency spin wave logic gates were explained and utilized to enable parallelism in the SW domain [30], [34], [35]. In addition,  $\mu$ m range [45] and mm range prototypes were demonstrated [37]-[40], [57]. Worth mentioning is the mm range prototyping of Magnonic Helographic Memory (MHM) [37], [39] and its potential utilization for parallel data processing [46]–[48], [58]. Reversible SW based logic gates were also proposed [57] and the concept was used to build an AND gate and comparator. Furthermore, different circuits have been also reported without simulation or experimental results [41], [42], [44], [49], [59]. Moreover, a multi-value magnon adder for the implementation of all magnonic neurons was illustrated in [51]. However it operates in the presence of large external fields, which makes the design not scalable and energy hungry. In addition, a SW wavepipelining concept was validated by instantiating 4 cascaded Majority gates by means of micromagnetic simulation [50]. Furthermore, a SW based full adder was suggested and validated by micromagnetic simulation [52], whereas a SW 2-bit input multiplier that makes use of directional couplers for SW amplitude normalization and gate cascading was explained and validated by means of micromagnetic simulation in [53], while a spin wave based approximate 4: 2 compressor was introduced and validated by means of [56].

1549-8328 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

We note that most of the proposed designs make use of majority gates to develop Boolean algebra based SW circuits, which construction requires gate fan-out and cascading capabilities, numerous electric to SW domain conversion, and large external magnetic fields [27], [53]. As such the SW based computation potential is not fully utilized and the ultra-low energy consumption promise is partially lost. In this paper, we go beyond Boolean algebra and propose a non-binary SW computing paradigm that enables full SW circuit construction without requiring gate fanout and cascading, domain conversions, and large external fields. The main contributions of this work can be summarized as follows:

- Proposing a novel non-binary SW computing paradigm: Information is encoded in SW amplitude, computing is performed by means of different amplitude SWs interference, and the output result is detected via a non-binary to binary conversion.

- Developing a SW amplitude converter: multiple directional couplers are utilized to convert a SW amplitude value into its binary representation.

- Designing SW non-binary adder by relying on the proposed computing paradigm and SW amplitude value converter.

- Validating the functionality and demonstrating the superiority: We validate the proposed structure by means of MuMax3 simulations. Also, we evaluate and compare a SW non-binary 2-bit adder with Boolean algebra based SW and 7 nm CMOS designs. The results indicate that our approach diminishes the energy consumption by 3.14× and 6× when compared with the conventional SW and 7 nm CMOS counterparts, respectively. Furthermore, the proposed non-binary adder implementation requires the least number of devices, which indicates its potential for small chip real-estate realizations.

The paper consists of five main sections. Section II explains the fundamentals of SW based computing and provides inside on directional couplers functionality and design. Section III introduces the non Boolean based SW computing paradigm and the SW amplitude converter, and illustrates their utilization for the design of a 2-bit non-binary adder. Section IV describes the simulation platform and presents simulation results. Section V compares the energy, delay, and estimated area of the proposed adder with SW and 7 nm CMOS counterparts, and discusses thermal and variability effects and SW technology challenges. Section VI concludes the paper.

#### II. SW BASED COMPUTING BACKGROUND

In equilibrium, the magnetization of a ferromagnetic material aligns with the effective magnetic field [27] and a small misalignment of the magnetization away from this magnetic field can be seen as an excitation or perturbation of the magnetization. The dynamics of this out-of-equilibrium magnetization is described by the Landau-Lifshitz-Gilbert (LLG)

Fig. 1. One dimensional schematic representation of a spin wave with i)  $\Phi=0$  and k=1, ii)  $\Phi=\pi$  and k=1, and iii)  $\Phi=\pi$  and k=3.

equation [60], [61]:

$$\frac{d\vec{m}}{dt} = -\|\gamma\| \mu_0 \left(\vec{m} \times \vec{H}_{eff}\right) + \alpha \left(\vec{m} \times \frac{d\vec{m}}{dt}\right), \quad (1)$$

where  $\gamma$  is the gyromagnetic ratio,  $\mu_0$  the vacuum permeability, m the magnetization,  $\alpha$  the damping factor, and  $H_{eff}$  the effective field expressed as:

$$H_{eff} = H_{ext} + H_{ex} + H_{demag} + H_{ani}, \tag{2}$$

where  $H_{ext}$  is the external field,  $H_{ex}$  the exchange field,  $H_{demag}$  the demagnetizing field, and  $H_{ani}$  the magnetocrystalline anisotropy field.

When the equilibrium perturbation is weak, the LLG equation has stable wave-like solutions, called Spin Waves (SWs). Such a SW is characterized by its wavelength  $\lambda$ , which is the shortest distance between two electrons that exhibit the same spinning behaviour, wavenumber k ( $k = \frac{2\pi}{\lambda}$ ), phase  $\phi$ , amplitude A, and frequency f, which is the time taken by the electron to complete a full precession, as graphically depicted in Figure 1.

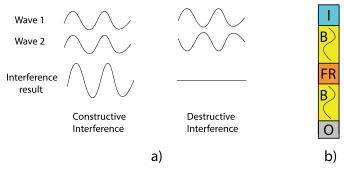

Generally speaking, SWs can carry information encoded into their amplitude and/or phase at different frequencies [27] and three encoding schemes are mainly utilized: binary amplitude, binary phase, and non-binary [27]. In the first case binary amplitude level or binary amplitude threshold encoding can be utilized. For binary amplitude level logic 0 is represented by a 0 amplitude SW (no spin wave) and logic 1 by a SW with amplitude A, whereas binary amplitude threshold encoding relies of the definition of a certain amplitude threshold value T such that a SW represents a logic 1 if its amplitude is larger than (or equal to) T and logic 0, otherwise [27]. In contrast, for phase encoding SWs are excited with a fixed amplitude and either 0 or  $\pi$  phase, corresponding to logic 0 and 1, respectively [27]. Finally, non-binary encoding covers other cases when information is encoded in multiple amplitudes and/or phases at similar/different frequencies [27]. If multiple waves coexist in the same waveguide, they interact with each other based on the wave interference principles. For example, if phase encoding is at hand, SWs interfere constructively if

Fig. 2. a) Wave interference when two spin waves meet in the waveguide. b) Conventional SW device with excitation region I, Waveguide B, Functional region FR, and detection region O.

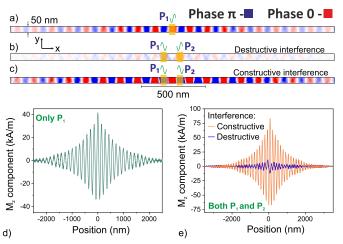

Fig. 3. Micromagnetic simulation results for a) a SW excited with phase of 0 in the inline waveguide, b) Two SWs excited in the inline waveguide, a SW with phase of 0 and a SW with phase of  $\pi$  resulting in a destructive interference between the two SWs, c) Two SWs excited in the inline waveguide with phase of  $\pi$  resulting in a constructive interference between the Two SWs, d) Spin wave magnetization in the waveguide for SW excited with phase of 0, e) Spin wave magnetization in the waveguide for SW constructive and destructive Interferences [27].

they have the same phase  $\Delta \phi = 0$ , and destructively if they are out of phase  $\Delta \phi = \pi$  as depicted in Figure 2a). In addition, we performed micromagnetic simulation to validate the theoretical concept; the simulations were performed for a 50 nm wide and 5 nm thick CoFeB waveguide, 0.004 damping, 1.3 MA/m magnetic saturation, and 18.5 pJ/m exchange stiffness [27]. The micromagnetic simulation results are presented in Figure 3. Figure 3 a) depicts the SW propagation through the waveguide, Figure 3b) presents the destructive interference of two SWs, one excited with 0 phase and the other excited with  $\pi$ , and Figure 3c) presents the constructive interference of two SWs excited with  $\pi$  phase. In a more general case, the interference of SWs with different amplitude, wavelength, frequency, and phase results in complex patterns, which can potentially open the road towards novel future SW computing paradigms [27]. However, in this paper, we concentrate on the interference of SWs with different amplitudes but same frequency, wavelength, and phase.

Generally speaking, a SW device consists of four regions as depicted in Figure 2b): Excitation Stage I, Waveguide B, Functional Region FR, and Detection Stage O [27].

SWs are excited by voltage/current driven transducers, e.g., microstrip antennas [27], magnetoelectric cells [27], Spin Orbit Torque [27], at I. Subsequently, SWs propagate through B that is made of magnetic material, e.g., Permalloy Py, Yttrium Iron Garnet YIG, CoFeB [27], which determines the SW properties. Typically, spin waves can propagate through waveguides over distances in  $\mu$ m to mm range, depending on the waveguide material properties [27]. For example, if the waveguide is made of YIG, which has a damping factor of 0.00005, a SW can propagate over at most 25 mm and has a lifetime of 0.6  $\mu$ m. If the SW circuit is larger than 25 mm or the SW must survive beyond 0.6  $\mu$ m extra circuit elements, e.g., amplifiers, repeaters, converters, must be utilized to restore the SW strength and enable longer propagation and life time [27]. FR is the place where SWs can be manipulated, i.e., amplified, interfere with each other or normalized [27]. Finally, at O the SW output is detected and converted into the electrical domain by means of voltage/current driven transducers that can be similar or different than the one utilized in the excitation stage [27]. We note that amplitude normalization is required in order to produce the correct output and enable gate cascading and can be done by means of a directional coupler as described in the next subsection.

#### A. Directional Couplers

Two waveguides placed in close proximity constitute a dipolar coupler as dipolar fields extend outside the waveguides, and thus magnetically couple them. This coupling induces energy transfer from one waveguide to the other depending on several parameter values, as further discussed in the sequel. A schematic picture of such a dipolar coupler is presented in Figure 4a), where a SW is induced in the top waveguide and, due to coupling, part of its energy reaches *O*1 while the rest is routed to *O*2.

Equations (3) - (14) describe the dispersion relations and energy transfer within the directional coupler [62]–[65]. When the two waveguides are placed close enough to each other, the dipolar coupling splits the SW dispersion relation into a symmetric (has a symmetric profile over both waveguides) and an anti-symmetric (has an asymmetric profile over both waveguides) mode. The SW dispersion relation for the isolated top waveguide (without coupling), in addition to the symmetric and asymmetric modes can be calculated by using Equations (3) and (4), and they are graphically presented in Figure 4b) [64]–[66].

$$f_o(k_x) = \frac{1}{2\pi} \sqrt{\Omega^{yy} \Omega^{zz}},$$

$$f_{s,as}(k_x) = \frac{1}{2\pi} \sqrt{(\Omega^{yy} \pm \omega_M F_{kx}^{yy}(d))(\Omega^{zz} \pm \omega_M F_{kx}^{yy}(d))},$$

(4)

where  $f_o(k_x)$  is the isolated spin wave waveguide dispersion relation,  $f_{s,as}(k_x)$  the symmetric and asymmetric dispersion relations for spin waves in coupled waveguides,  $\Omega^{ii} = \omega_H + \omega_M(\lambda_{ex}^2 k_x^2 + F_{kx}^{ii}(0))$ ,  $i = y, z, \omega_H = \gamma B_{ext}$ ,  $\omega_M = \gamma \mu_o M_s$ ,  $M_s$  the magnetic saturation,  $\lambda_{ex} = 2A_{ex}/\mu_o M_s^2$ ,  $A_{ex}$  the exchange constant,  $d = w + \delta$  the distance between the

Fig. 4. a) Directional coupler with coupling length  $L_c$  and length of the coupled waveguide  $L_w$  where  $L_c$  value depends on different parameters value depends on, e.g., wavelength, applied magnetic field, distance between waveguides, waveguides sizes, SW amplitude, and can be calculated as in equation (7). b) Dispersion relation (DR) of Isolated (I), Symmetric (S), and asymmetric (As) SW waveguide (WG) Modes in the linear region. c) Power transmission ratio between coupled waveguides with  $L_w = 3 \mu m$  representing energy split according to equation (8). d) Dispersion relation of isolated, symmetric, and asymmetric SW WG modes in the non-linear region (with frequency shift effect).

two waveguides centers, w the waveguides width, and  $\delta$  the gap between the two waveguides, and  $\hat{F}_{kx}$  is the tensor that describes the dynamical magneto-dipolar interaction calculated according to Equations (5) and (6) [62]-[65].

$$F_{kx}^{yy}(d) = \frac{1}{2\pi} \int \left( \frac{\|\sigma\|^2 k_y^2}{\tilde{w}k^2} (1 - \frac{1 - e^{-kh}}{kh}) \right) e^{ik_y d} dky, \quad (5)$$

$$F_{kx}^{zz}(d) = \frac{1}{2\pi} \int \frac{\|\sigma\|^2}{\tilde{v}_0} \frac{1 - e^{-kh}}{kh} e^{ik_y d} dk_y, \tag{6}$$

where  $\sigma$  is the Fourier transform of the spin wave profile across the waveguide width,  $\tilde{w}$  the normalized mode profile constant,  $k = \sqrt{k_x^2 + k_y^2}$ , and h the waveguide thickness. Note that  $\tilde{w}$  equals w and  $\sigma = w sinc(k_y w/2)$ , if the electron spins are fully unpinned at the waveguide edges.

Two spin wave modes, i.e., symmetric with wavenumber  $k_s$ and antisymmetric with wavenumber  $k_{as}$ , are simultaneously excited only if the excited spin wave frequency is higher than the asymmetric spin wave minimum frequency. Thus, the overall spin wave energy resonantly transfers from one waveguide to the other after the spin wave propagation along the coupling length  $L_c$  as presented in Figure 4a) [64]–[68]. The  $L_c$  value depends on different parameters such as wavelength, applied magnetic field, space between waveguides, waveguides sizes, spin wave amplitude in addition to its magnetization, and can be calculated as in Equation (7) [64], [65].

$$L_c = \frac{\pi}{\|k_s - k_{as}\|},\tag{7}$$

The amount of energy transferred between the waveguides can be tuned by means of the coupling length  $L_c$  and the length of the coupled waveguide  $L_w$ , which jointly determine the strength of the coupling effect between the two waveguides. Equation (8) presents the relation between these two parameters and the energy transfer ratio [64]

$$\frac{O_1}{O_1 + O_2} = \cos^2\left(\frac{\pi L_w}{2L_c}\right),\tag{8}$$

where  $O_1$  is the output energy of the first waveguide,  $O_2$  the output energy of the second waveguide,  $L_w$  the length of the coupled waveguides and  $L_c$  the coupling length [64]. Figure 4c) presents the energy split according to Equation (8) for the particular case of  $L_w = 3 \mu m$  and one can observe in the Figure that the  $L_c$  value modulates the energy transfer between the two waveguides.

The above equations hold true, if the spin wave amplitude value is low. However, non-linearity effects start increasing as the amplitude increases, which causes non-linear frequency shifts of the spin wave symmetric and asymmetric dispersion relations as expressed in Equation (9).

$$f_{s,as}^{(nl)} = f_{s,as}^{(0)}(k_x) + T_{kx} \|a_{kx}\|^2$$

(9)

where  $a_{kx}$  is the spin wave amplitude,  $T_{kx}$  the spin wave nonlinear frequency shift, which can be calculated using Equation (10) [64], [65], [69], [70].

$$T_{kx} = \frac{w_H - A_{kx} + \frac{B_{kx}^2}{2\omega_o^2} (\omega_M (4\lambda^2 k_x^2 + F_{2kx}^{xx}(0)) + 3\omega_H)}{2\pi}, \quad (10)$$

where

$$A_{kx} = \omega_H + \frac{\omega_H}{2} (2\lambda_{ex}^2 k_x^2 + F_{kx}^{yy}(0) + F_{kx}^{zz}(0)), \quad (11)$$

$$B_{kx} = \frac{\omega_M}{2} (F_{kx}^{yy}(0) - F_{kx}^{zz}(0)), \quad (12)$$

$$B_{kx} = \frac{\omega_M}{2} (F_{kx}^{yy}(0) - F_{kx}^{zz}(0)), \qquad (12)$$

$$F_{2kx}^{xx}(d) = \frac{1}{2\pi} \int \frac{\|\sigma\|^2 4k_x^2}{\tilde{w}k^2} (1 - \frac{1 - e^{-kh}}{kh}) e^{ik_y d} dk_y, \quad (13)$$

(6) where

$$k = \sqrt{4k_x^2 + k_y^2}$$

.

Figure 4d) captures this effect for two different spin wave amplitudes [62], [64]. As depicted in the Figure, when the spin wave amplitude increases from 0.080 to 0.160, the dispersion relation shifts downward. Additionally, the energy splitting ratio is affected by the non-linear frequency shift as indicated by Equation (14) [65].

$$\frac{O_1}{O_1 + O_2} = \cos^2\left(\frac{\pi L_w}{2L_c} - \frac{\pi L_w}{2L_c^2} \frac{\partial L_c}{\partial f} T_{kx} \|a_{kx}\|^2\right)$$

(14)

Equation (14) demonstrates that as the ratio between  $L_c$  and  $L_w$  increases, the non-linearity effect increases, which makes the directional coupler very sensitive to SW amplitude variations.

In the proposed non-binary to binary converter introduced in Section III, two types of directional coupler are required: one working in linear regime such that the energy transfer is not affected by the SW amplitude level, and one working in non-linear regime such that the energy transfer is affected by the SW amplitude level. Therefore, for the first type, the ratio between  $L_c$  and  $L_w$  must be small and the distance between the coupled waveguides must be large to decrease the coupling effect. In contrast, the ratio between  $L_c$  and  $L_w$ , must be large and the distance between the coupled waveguide must be small to increase the coupling effect for the second type.

For example, if the coupler is designed with  $L_c = 370$  nm, 50 nm distance between waveguides (DW), Yttrium Iron Garnet (YIG) waveguide thickness of 30 nm and width of 100 nm, and 340 nm SW wavelength and 2.282 GHz frequency, the spin wave energy equally splits between the waveguides regardless of its amplitude [65]. Whereas, if the coupled waveguide length is  $3 \mu m$ , distance between the waveguides 10 nm, while maintaining the same values for the other parameters, the SW energy splits differently between the waveguides depending on the input spin wave amplitude, i.e., if the SW amplitude is 2A, 3A, and 4A, nothing, 50 %, and 100 % of its amplitude moves to the second waveguide, respectively [65]. Note that these split ratios change as the parameters change, and that the mentioned parameter values were utilized to calculate the dispersion relations in Figure 4.

#### B. Spin Wave Computing

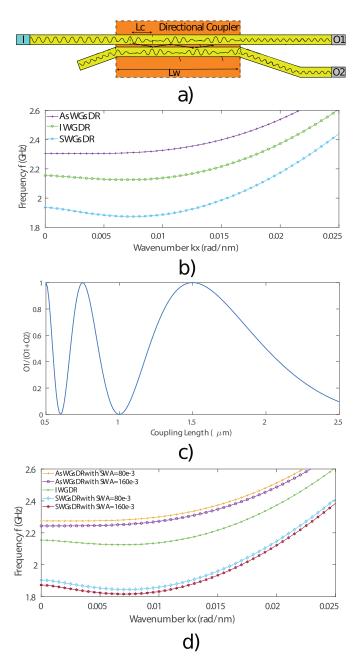

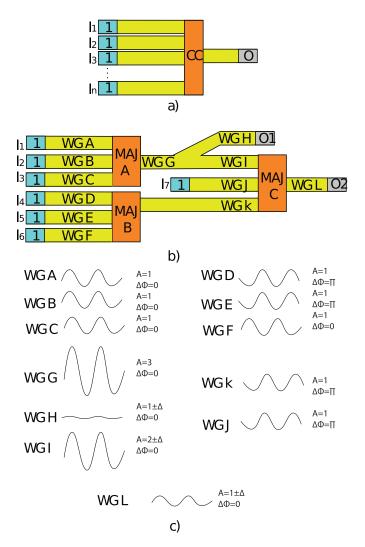

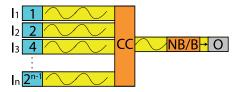

Figure 5a) presents the generic circuit structure for SW phase based information encoding, which consists of three main parts. First, the binary inputs  $I_1, I_2, \ldots, I_n$  are utilized to excite SWs with the same amplitude but different phases reflecting their values. Subsequently, these spin waves propagate through the waveguides, and within the intersection region CC interfere constructively or destructively depending on their phases in order to emulate the functionality of the targeted combinational circuit, e.g., multiplexer, decoder, adder, multiplier. Finally, the interference result is captured at the output O.

To get more inside on the way such a circuit operates let us assume the circuit in Figure 5b), which consists of three 3-input Majority gates (MAJ3) computing  $O_1 = MAJ(I_1, I_2, I_3)$  and  $O_2 = MAJ(MAJ(I_1, I_2, I_3), I_7, MAJ$

Fig. 5. a) SW circuit design conventional structure. b) Cascaded MAJ3 gates. c) SW waveform analysis at  $\{I_1I_2I_3I_4I_5I_6I_7\} = \{0001101\}$ .

$(I_4, I_5, I_6)$ ). Figure 5c) presents, as an example, the interference results for the input pattern  $\{I_1I_2I_3I_4I_5I_6I_7\}$  = {0001101}. Note that we make use of binary amplitude information encoding, thus logic 0/1 are represented with a spin wave with amplitude A and  $0/\pi$  phase. As it can be observed from Figure 5c),  $I_1I_2I_3$  interfere constructively in MAJ A, resulting in a 3A amplitude and 0 phase spin wave, which further travels towards  $O_1$  and MAJ C. However, the majority of its energy flows through WG I because this is a straight waveguide connected to WG G whereas the connection to WG H is bent. On the other hand,  $I_4I_5I_6$  interfere constructively and destructively in MAJ B resulting in an A amplitude and  $\pi$  phase spin wave. Thus, MAJ C operates on the WG I SW (amplitude 3A minus a small portion that went to WG H and phase of 0), WG J SW (with amplitude A and phase of  $\pi$ ), and WG K SW (amplitude A and phase of  $\pi$ ). While the expected MAJ C output in this case is logic 1 (two phase  $\pi$  SWs and one phase 0 SW) Figure 5c) indicates that the WG L SW has a phase of 0, which is wrong. This miscalculation is induced by the fact that MAJ C input SWs have different amplitudes and as such the  $\approx 3A$  amplitude phase 0 SW illegitimacy wins the voting process over the two amplitude A phase  $\pi$  SWs. The correction of this problem requires WG G SW amplitude normalization, i.e., reduction from 3A to A, and SW energy loss prevention in situations like the one at VG G. These can be achieved by means of, e.g., domain conversion, directional coupling [53], and fanout achievement [28], [29], [71], [72], which induces significant area, delay, and energy consumption overheads. Given that the realization of practically relevant non-toy SW circuits requires fanout and gate cascading capabilities, with their associated overheads, the investigation of computation paradigms that make better use of the SW technology is of great interest, and, in this line of reasoning we introduce in the next Section a novel beyond Boolean algebra SW computation paradigm.

#### III. NON-BINARY SPIN WAVE COMPUTING

The traditional combinational circuit implementation starts with the truth table of an *n*-input Boolean function  $f(I_1, I_2, \ldots, I_n)$ , derives the expression of f as sum of products (product of sums), and processes it to make the best use of the available universal set of Boolean gates, e.g., NAND, NOR, while minimizing the implementation cost and delay. The same approach is utilized for SW circuits but in this case the universal gate set comprises Majority gates and inverters. While this is an attractive approach that benefits of the rather mature CMOS circuit design framework, it limits the utilization of SW potential as discussed in Section II. In this section we propose a way to break the Boolean algebra wall by implementing f not based on its  $2^n$  entry true table but on an n-entry one that expresses f as a function of  $\sum_{i=1}^{n} I_{i}$ . Such a description exist for a large class of practically relevant functions called (generalized) symmetric functions, which includes, e.g., AND, OR, Parity, addition, multiplication [73], [74]. Following this paradigm in the SW domain requires two computation steps: (1) the calculation of  $S = \sum_{i=1}^{n} I_j$ , and (2) the assignation of f as function of S. (1) is straightforward if information encoding is done in SW amplitude (logic 0 no SW, logic 1 SW with unit amplitude A) as in this case the input SWs always interfere constructively resulting in a SW with  $S = A \sum_{j=1}^{n} I_j$  amplitude. (2) is more intricate as it requires a SW amplitude conversion process. For example if f is the n-input parity function  $S \in [0, nA]$  and f should be logic 1 if S is odd and logic 0, otherwise, which is what (2) should perform.

To get more inside into stage (1) let us assume the structure in Figure 6, with an n-bit binary number  $(I_1, I_2, \ldots, I_n)$  as input. Each Boolean input  $I_j$ , j=1,n induces a SW with amplitude  $AI_j2^j$ , which results in the formation of a SW with amplitude  $\sum_{j=1}^n AI_j2^j$ , i.e., proportional with the decimal value of the input vector, at the output of the CC block. If we extend the structure to two n-bit inputs X and Y, the output SW amplitude is equal with  $\sum_{j=1}^n A(X_j2^j + Y_j2^j)$ , i.e, the result of the X+Y binary addition. Thus in this way we completed the addition without relying an any Boolean gate as the output SW caries the addition result. What still remains to be done is to obtain the binary representation of X+Y on x+1 bits via a process of non-binary to digital conversion

Fig. 6. Generic non-binary SW circuit structure.

within stage (2). We note that the direct summation can also be applied to binary signed digit representations [75] if SW phase is also considered in the encoding, i.e, 0 corresponds to no SW and 1/-1 to unit amplitude SW with phase 0/1, respectively, but this is out of the scope of this paper.

In contrast to the binary spin wave computing, and by non-binary approach very operation principle, the non-binary approach does not require any SW amplitude normalization, it takes its power form operating on SWs with different amplitudes. As mentioned previously, there are 2 stages only; in the first one SWs with different amplitudes interfere resulting in a SW which amplitude carries the output result, whereas in the second stage a number of properly designed directional couplers are utilized to produce the binary representation of the result.

#### A. SW Non-Binary to Binary Converter

The non-binary to binary converter, i.e., the NB/B in Figure 6, can be implemented by means of multiple waveguides closely spaced to each other. Given the Directional Coupler (DC) ability to route SW energy between its component waveguides we make use of a number of specially tailored DCs to design the Non-Binary to Binary (NB/B) converter. Recall that DCs working in linear regime split the input SW into half between the waveguides regardless of its amplitude and DC working in non-linear regime that can be designed using Equations (3) - (14) split the SW between waveguides with an input SW amplitude dependent ratio.

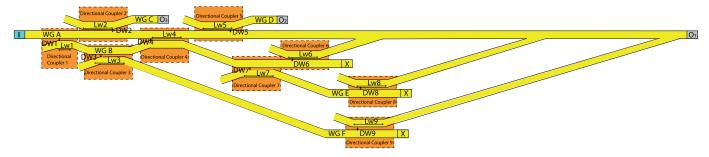

To clarify the NB/B converter concept, we instantiate the 3-bit converter presented in Figure 7. In the Figure, I is the SW input with amplitude from 0A to 7A,  $O_1$ ,  $O_2$ , and  $O_3$  are the outputs, and 9 directional couplers are needed to perform the correct NB to B conversion. In order to properly design the directional couplers one needs to know when each output is 1 and 0, which is presented in Table I for the 3-bit converter in Figure 7:  $O_3 = 1$  if SW input amplitude is larger than 3A, and 0, otherwise,  $O_2 = 1$  if SW input amplitude is 2A, 3A, 6A, and 7A, and 0, otherwise, and  $O_1 = 1$  if SW input amplitude is 1A, 3A, 5A, and 7A, and 0, otherwise. Capturing  $O_3$  seems straightforward as its value obeys one condition only, thus DC2 can be designed such that if SW amplitude is larger than 3A, it moves to  $O_3$ , and nothing moves, otherwise. However, by doing so  $O_1$  and  $O_2$  cannot be captured correctly when they are 1 if the SW amplitude is larger than 3A as the SW energy moves completely to  $O_3$ . Therefore, the input spin wave signal should be divided into two equal parts which means that DC1 should work in the linear regime. After this split  $O_3 = 1$  if SW amplitude is larger than 1.5A. Therefore, the second directional coupler must be

Fig. 7. 3-bit SW NB/B converter.

$\label{eq:table_interpolation} \mbox{TABLE I} \\ \mbox{3-Bit SW NB/B Converter Truth Table}$

| I  | $O_1$ | $O_2$ | $O_3$ |

|----|-------|-------|-------|

| 0  | 0     | 0     | 0     |

| 1A | 1     | 0     | 0     |

| 2A | 0     | 1     | 0     |

| 3A | 1     | 1     | 0     |

| 4A | 0     | 0     | 1     |

| 5A | 1     | 0     | 1     |

| 6A | 0     | 1     | 1     |

| 7A | 1     | 1     | 1     |

designed with a threshold of 1.75A, which is the average of the cases 1.5A and 2A. If the spin wave amplitude is larger than 1.75A the spin wave moves completely to the upper part (WG C) to be captured at  $O_3$ , and nothing moves to WG C, otherwise.

$O_2$  value is determined by two conditions,  $O_2 = 1$  if the spin wave amplitude is larger than 1A and less than 4A, and larger than 5A as indicated in Table I. In order to obtain its proper value DC4 and DC5 need to be designed such that DC5 moves the SW energy in WGA completely to  $O_2$  if SW amplitude is larger than 1A as the SW energy is 0 if SW amplitude is larger than 3A, and DC4 moves the SW energy in WG B completely to  $O_2$  if SW amplitude is larger than 5Ato meet the second condition. However, by doing so  $O_1$  cannot be correctly computed as no SW will be captured at  $O_1$  when the SW amplitude equals to 7A. Therefore, the non-binary spin wave signal in WG B should be divided into two equal parts to correctly detect  $O_1$ , thus DC3 should work in linear regime as a second splitter. Thus, in order to obtain  $O_2 = 1$  if the spin wave amplitude is larger than 0.5A and less than 2Aafter the first splitter, DC 5 must be designed with a threshold value of 0.75A, which is the average of 0.5A and 1A. Hence, the spin wave moves completely to WG D if the spin wave amplitude is larger than 0.75A, and nothing moves to WG D, otherwise. To obtain  $O_2 = 1$  if spin wave amplitude is larger than 1.25A after the splitters, DC4 must be designed with a threshold value of 1.375A, which is the average of the cases 1.25A and 1.5A. By doing this, a WG A spin wave with amplitude less than 1.375A is not affected and no energy is transferred to WG D, and when the amplitude is larger than 1.375A, the spin wave is transferred to WG D.

Finally,  $O_1 = 1$  if the spin wave amplitude is 1A, 3A, 5A, and 7A as presented in Table I. From the above, a spin wave exists in WG A and reaches  $O_1$  when the spin wave amplitude

is less than 0.75A (after the splitters) which meets the first condition:  $O_1 = 1$  when SW amplitude is 1A. Also, the spin wave available in WG B reaches DC6 when it amplitude is less than 1.375A. Therefore, to meet the second condition:  $O_1 = 1$  when SW amplitude is 3A, DC6 must be designed with a threshold value of 0.625A, which is the average of the cases 0.5A and 0.75A such that if spin wave amplitude is larger than 0.625A, the spin wave moves completely to WG A, and nothing moves to WG A, otherwise. In addition, DC7 must be designed with a threshold value of 0.875A, which is the average of the cases 0.5A and 0.75A such that if spin wave amplitude is larger than 0.875A, the spin wave moves completely to WG E and nothing moves to WG E, otherwise. This is done to prevent the existence of a spin wave in WG A when SW amplitude equals to 2A and 4A as  $O_1$  must be 0 at these cases. Moreover, DC8 must be designed with a threshold value of 1.125A, which is the average of the cases 1A and 1.25A such that if spin wave amplitude is larger than 1.125A is moves completely to WG A, and nothing moves to WG A, otherwise. Finally, DC9 must be designed with a threshold value of 1.625A, which is the average of the cases 1.5A and 1.75A such that if spin wave amplitude is larger than 1.625A it moves completely to WG A, and nothing moves to WG A, otherwise. Thus, by designing the directional couplers with the aforementioned thresholds, the three outputs are correctly captured.

Note that the aforementioned explanation is for the ideal case without taking into consideration the damping or the exact energy that remains or moves to the other waveguide(s) from the directional couplers, but the operation principle remains the same. Additionally, the outputs are captured based on the thresholding condition such that if the received spin wave amplitude is larger than a predefined threshold, it corresponds to logic 1, and it is logic 0, otherwise. The outputs should be placed as near as possible after the last directional coupler to minimize spin wave amplitude decay effects. This concept can be extended to *n*-bit NB/B converter, case in which it requires N+1 directional couplers where N is the number of 0 to 1 changes in the conversion table. The same way of thinking can be followed to determine the DCs' thresholds and Equations (3) - (14) to correctly design the directional couplers.

#### B. SW Non-Binary Adder

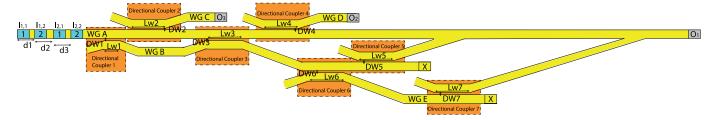

To better explain and illustrate our approach we apply it for the design a 2-bit adder as depicted in Figure 8.

Fig. 8. Proposed SW non-binary adder.

TABLE II

NON-BINARY SW ADDER OUTPUTS

| $I_{12}$ | $I_{11}$ | $I_{22}$ | $I_{21}$ | A1   | A2    | $O_1$ | $O_2$ | $O_3$ |

|----------|----------|----------|----------|------|-------|-------|-------|-------|

| 0        | 0        | 0        | 0        | 0    | 0     | 0     | 0     | 0     |

| 0        | 0        | 0        | 1        | 1A   | 0.5A  | 1     | 0     | 0     |

| 0        | 1        | 0        | 0        | 171  | 0.071 | 1     |       |       |

| 0        | 1        | 0        | 1        |      |       |       |       |       |

| 0        | 0        | 1        | 0        | 2A   | 1A    | 0     | 1     | 0     |

| 1        | 0        | 0        | 0        |      |       |       |       |       |

| 0        | 0        | 1        | 1        |      |       |       |       |       |

| 0        | 1        | 1        | 0        | 3A   | 1.5A  | 1     | 1     |       |

| 1        | 0        | 0        | 1        | 3.71 | 1.071 | 1     | 1     | "     |

| 1        | 1        | 0        | 0        |      |       |       |       |       |

| 0        | 1        | 1        | 1        |      |       |       |       |       |

| 1        | 0        | 1        | 0        | 4A   | 2A    | 0     | 0     | 1     |

| 1        | 1        | 0        | 1        |      |       |       |       |       |

| 1        | 0        | 1        | 1        | 5A   | 2.5A  | 1     | 0     | 1     |

| 1        | 1        | 1        | 0        | JA.  | 2.0A  | 1     |       | 1     |

| 1        | 1        | 1        | 1        | 6A   | 3A    | 0     | 1     | 1     |

The 2-bit binary inputs are transformed into SWs by means of the excitation cells  $I_{11}$ ,  $I_{12}$ ,  $I_{21}$ , and  $I_{22}$ , which take into account the position weights, i.e.,  $I_{11}$  and  $I_{21}$  are excited with an amplitude of 1A, whereas  $I_{12}$  and  $I_{22}$  with 2A. After spin wave excitation, the spin waves propagate through the waveguide and interfere constructively. The resultant SW from interference is converted to binary by the proposed NB/B converter and is captured at the outputs as presented in Figure 8.

The circuit dimensions such as the distances between the excitation cells and directional couplers dimensions must be carefully chosen as described in [53] to ensure correct functionality. For instance, if the required result is to interfere constructively if they have the same phases, then the distances between the excitation cells must be  $n \times \lambda$ , i.e,  $d_1 = d_2 = d_3 = n\lambda$  (where n = 1, 2, 3...).

Since the maximum output of the 2-bit adder is 110 as can be observed in Table II, we simplified the 3-bit NB/B converter in Figure 7 to minimaze delay and save area to the structure presented in Figure 8. Seven different directional couplers are used to convert the non-binary result of the adder to binary outputs. The first directional coupler is designed based on the maximum amount of the outputs that can be logic 1 simultaneously. In this case, as can be seen from Table II, maximum two of the three outputs can be logic 1. Therefore, the non-binary spin wave signal should be divided into two equal parts to allow simultaneously spin wave propagation to two outputs. Hence, the first directional coupler works in the linear regime and splits the energy of the spin wave into two equal parts

independent on the spin wave amplitude. Note that if the implementation of a more complex adder is targeted for which n outputs could simultaneously assume logic 1, the input spin wave energy has to be divided into n equal parts.

The other six directional couplers work in the non-linear regime such that there is an amplitude threshold for the energy transfer from one waveguide to another. The amplitude threshold is different for every coupler and can be determined by considering the amplitudes after the splitter indicated in Table II columns A1 and A2 by following the line of thinking explained in the previous subsection. The same operation principle and design steps are followed but some thresholds are different as one splitter is used here and 6 directional couplers with the following thresholds: 1.75A for DC2, 0.75A for DC3, 2.75A for DC4, 1.25A for DC5, 1.75A for DC6, and 2.25A for DC7. Additionally, the output values are captured by means of thresholding as previously explained.

#### IV. SIMULATION SETUP AND RESULTS

To validate our proposal we make use of the GPU-accelerated micromagnetic software MuMax3 which can solve the LLG equation. MuMax3 simulations require the specification of suitable parameters to describe the simulated structure and reflect the environment. We used a  $Fe_{60}Co_{20}B_{20}$  waveguide with width of 30 nm and thickness of 1 nm to test the proposed structure, in addition to the following parameters: magnetic saturation  $M_s = 1.1 \text{ MA/m}$ , perpendicular anisotropy constant  $k_{ani} = 8.3 \text{ MJ/m}^3$ , exchange stiffness  $A_{ex} = 18.5 \text{ pJ/m}$ , and damping constant  $\alpha = 2 \times 10^{-4}$  [77]. We determined the spin wave dispersion relation for these parameters, and for a wavelength of  $\lambda = 200$ nm, the spin wave frequency is determined to be f = 14.03 GHz. Hence, the distances between excitation cells  $d_1$ ,  $d_2$ , and  $d_3$  has to be 200 nm. Additionally, we used Equations (3) - (14) in order to determine the directional couplers dimensions. Based on the above parameters and equations we obtained the following dimensions:  $L_{w1}$  = 370  $\mu$ m,  $L_{w2} = L_{w3} = L_{w4} = L_{w5} = L_{w6} = L_{w7} =$  $2.55 \mu \text{m}$ ,  $DW_1 = 50 \text{ nm}$ ,  $DW_2 = 15 \text{ nm}$ ,  $DW_3 = 30 \text{nm}$ ,  $DW_4 = 10 \text{ nm}, DW_5 = 11 \text{ nm}, DW_6 = 13 \text{ nm}, \text{ and}$  $DW_7 = 17 \text{ nm}.$

Table III presents the normalized spin wave magnetization at the adder outputs  $O_1$ ,  $O_2$ , and  $O_3$  reported by MuMax3 for different input patterns. By inspecting the Table, one can observe that by defining an appropriate threshold for the three outputs, the correct values can be obtained.

TABLE III

NORMALIZED NON-BINARY ADDER OUTPUTS

| Cases     |           |           | $O_1$     | $O_2$ | $O_3$  |       |

|-----------|-----------|-----------|-----------|-------|--------|-------|

| $I_{1,1}$ | $I_{1,2}$ | $I_{2,1}$ | $I_{2,2}$ |       |        |       |

| 0         | 0         | 0         | 0         | 0     | 0      | 0     |

| 0         | 0         | 0         | 1         | 0.69  | 0.1    | 0.002 |

| 0         | 0         | 1         | 0         | 0.027 | 0.77   | 0.16  |

| 0         | 0         | 1         | 1         | 1     | 0.39   | 0.37  |

| 0         | 1         | 0         | 0         | 0.99  | 0.24   | 0.01  |

| 0         | 1         | 0         | 1         | 0.043 | 0.65   | 0.1   |

| 0         | 1         | 1         | 0         | 0.66  | 0.58   | 0.32  |

| 0         | 1         | 1         | 1         | 0.42  | 0.001  | 0.56  |

| 1         | 0         | 0         | 0         | 0.22  | 0.68   | 0.08  |

| 1         | 0         | 0         | 1         | 0.98  | 0.3    | 0.4   |

| 1         | 0         | 1         | 0         | 0.16  | 0.078  | 0.75  |

| 1         | 0         | 1         | 1         | 0.91  | 0.094  | 0.88  |

| 1         | 1         | 0         | 0         | 0.91  | 1      | 0.27  |

| 1         | 1         | 0         | 1         | 0.008 | 0.0006 | 0.79  |

| 1         | 1         | 1         | 0         | 0.84  | 0.03   | 0.8   |

| 1         | 1         | 1         | 1         | 0.045 | 0.56   | 1     |

For  $O_1$ , the normalized threshold can be found by averaging the normalized output of the two cases  $I_{12}I_{11}I_{21}I_{22} = 0111$ , and  $I_{12}I_{11}I_{21}I_{22} = 1000$ , which equals to 0.32. The normalized threshold for  $O_2$  can be set to 0.27 by averaging the numbers in Table III for the cases  $I_{12}I_{11}I_{21}I_{22} = 0100$ , and  $I_{12}I_{11}I_{21}I_{22} = 1001$ . The normalized threshold for  $O_3$  is equal to 0.48 by averaging the normalized magnetization for  $I_{11}I_{12}I_{21}I_{22} = 1001$  and  $I_{12}I_{11}I_{21}I_{22} = 0111$ .

As it can be observed from the Table, the 3-bit sum value is correctly computed: if  $O_3$ ,  $O_2$ , and  $O_1$  normalized magnetization is larger than 0.48, 0.27, and 0.32 its value is 1 and 0 otherwise, respectively, as it should.

### V. PERFORMANCE EVALUATION AND DISCUSSION

To get some inside on the practical implications of our proposal, we evaluate the energy, delay, and area of the proposed 2-bit adder and compare them with the ones of conventional SW and 7 nm CMOS counterparts. We assume that excitation and detection transducers are magnetoelectric (ME) cells operating at  $V_{ME} = 119$  mV with a capacitance  $C_{ME} =$ 1 fF, and a 0.42 ns switching delay [78]. Note that a damping constant of 0.0002 was utilized for the micromagnetic simulations and with the state-of-the-art comparison. Furthermore, we assumed that the spin waves consume negligible energy in the waveguide and directional couplers when compared to the energy consumed by the excitation and detection cells [53], which implies that the adder energy consumption is  $I \times C_{ME} \times V_{ME}^2$ , where I is the number of excitation and detection cells. MuMax3 simulations results suggest that the spin wave propagation through the waveguide delay is 22 ns. Furthermore, we assume that pulse signals are utilized for SW excitation, which indicates that the energy consumption calculation only depends on the 0.42 ns applied pulse length and it is independent of the overall adder delay. Note that due to the SW technology infancy and foreseeable developments, these assumptions might need be revisited in the near future.

To compare with the conventional spin wave counterpart, we estimate the energy, delay, and number of devices of a SW Majority gate based 2-bit adder implementation. We assume

TABLE IV

PERFORMANCE COMPARISON

|                      | CMOS [79]      | SW [78]                 | SW                              |

|----------------------|----------------|-------------------------|---------------------------------|

| Technology           | 7 nm CMOS      | SW                      | SW                              |

| Implemented function | 2-bit adder    | Standard<br>2-bit adder | Proposed<br>non-binary<br>adder |

| Energy (aJ)          | 600.8          | 317                     | 101                             |

| Delay (ns)           | 0.081          | 23                      | 23                              |

| Utilized Device No.  | 48 Transistors | 22 ME<br>cells          | 7 ME cells                      |

that fanout and gate cascading solutions in [28], [53] are at hand and that fanout is achieved without any delay overhead and gate cascading induces a 22 ns delay overhead [28], [53].

To compare with a 7 nm CMOS 2-bit, which can be built with 3 AND gates, 1 OR gate, and 3 XOR gates we make use of the energy, delay, and area estimates in [79].

Table IV presents the evaluation results, which indicate that while being  $284\times$  slower than the CMOS counterpart, the proposed SW non-binary adder provides a  $6\times$  energy consumption reduction. In addition, the Table suggests that the conventional approach to implement a 2-bit adder in the spin wave domain consumes  $3.14\times$  more energy than the proposed non-binary adder for the same delay. Furthermore, the proposed adder implementation requires the least number of devices.

In addition, the proposed non-binary adder requires a real estate of  $18~\mu\text{m}^2$ , while the standard 2-bit adder requires a real estate of  $36~\mu\text{m}^2$ , indicating a 50% area reduction. Moreover, a 7 nm CMOS 2-bit adder requires a real estate of  $3.584~\mu\text{m}^2$ , which was estimated from the numbers provided in [65]. This indicates that  $5\times$  larger area is needed to implement the proposed 2-bit SW adder in comparison with the 7 nm CMOS 2-bit adder.

#### A. Variability and Thermal Noise

In this paper, our main target is to introduce a novel SW computing paradigm and validate it as a proof of concept while disregarding variability and thermal noise effects. However, SW majority gate functionality was evaluated under the presence of waveguide edge roughness and trapezoidal cross section and it was demonstrated that both of them have limited effects, and that SW gates functions correctly under their presence [64], [80]. In addition, the thermal noise effect was also evaluated in [64] and demonstrated that it has limited effect on gate proper operation at different temperatures. Therefore, we do not expect that variability and thermal noise will have a noticeable effect on the proposed circuit. However, deeper investigations of such phenomena are part of planned future work.

#### B. Challenges Ahead and Future Directions

The SW community's theoretical and practical contributions clearly demonstrate the SW computing paradigm potential to provide support for energy effective computation platforms able to outperform traditional Boolean algebra CMOS based

counterparts. However, a number of road blockers need to be properly removed in order to transform this potentiality into actual reality [27].

- 1) Interconnect: To fulfil SW promise into reality and build magnonic circuits, effective solutions for normalizers, fanout, splitters, amplifiers, enabling waveguide cross and multi-layer designs are required. Although SW amplitude normalization has been dealt with by means of directional couplers [53], this approach adds large delay and area overheads. Thus, more efficient directional couplers or other solutions would be beneficial. In addition, while fanout of 4 Majority gates and programmable logic gates were proposed [28], [29], [71], which is sufficient for many circuits, larger fanout capability can further diminish the need for circuit replications. Although fanout was enabled at the gate level, which benefits the SW circuits, fanout capability at the circuit level is still needed. This could potentially be achieved by adding an amplifier able to multiply the SW amplitude by a factor of n and a splitter. However, efficient experimental splitters and amplifiers are still to be developed. Although a Directional Coupler (DC) can split the SW amplitude by a factor 2, it adds large delay and area, and it has limited capabilities. In some cases, we need to diminish the SW amplitude by a factor 3, 4, 5, and 6, which is more difficult to realise with a DC. In addition, enabling waveguide cross is of great interest for building SW circuits without conversion or replication. Furthermore, enabling multi-layer technology helps optimizing the SW circuit design in terms of area and delay. Therefore, new innovative solutions for SW normalization, fan-out attainment, splitters, amplifiers, enabling line crossing and multi-layer are essential to properly take advantage of the SW computation potential [81].

- 2) Immature Technology: SW excitation and detection can be performed using different techniques including antennas and ME cells [27]. ME cells seem to be the right option to excite and detect SWs as they are potentially highly energy efficient and scalable. However, ME cells are not experimentally realized yet and whether or not 31 nW power consumption ME cells can be practically realized is still an open question.

- 3) Scalability: SW devices are highly scalable because SW wavelength can reach down to the *nm* range which is, conceptually speaking, the only limitation for the SW devices scalability. SW circuits area evaluations have been reported, e.g., the hybrid SW-CMOS 32-bit divider area [78] which is 3.5× smaller than the one of the 10 nm CMOS counterpart. However, we note that SWs cannot be currently distinguished from noise level in deca-*nm* range SW circuits, which must be sorted out before it become a road blocker for further SW circuit design developments.

- 4) Clocking: The necessary evil without which the large majority of computation platforms cannot properly function, is also an important contributor to the overall SW circuit complexity and performance. If information is transferred back and forth between the SW and electric domains at each and every circuit gate output, a complex clocking system is required to control the gate output sampling process. However, if SW amplitude normalizers are available domain conversion is only

- required at gate island level in a similar way pipeline stage outputs are sampled in a pipelined processor structure. Such an island will include a number (determined among others by the utilized ferromagnetic material properties) of SW gates, which substantially diminishes the clock distribution network complexity and allows for lower clock frequency utilization, which can significantly reduce the energy consumption.

- 5) CMOS Circuitry: In S3 domain, domain conversion from SW to charge domain and vice versa is required in order to provide larger than 4 fanout, which has been assumed to be done straight forward without CMOS circuits. This, however, is not accurate because the SW-CMOS or SW-another technology circuit design is limited due to the unavailability of sufficient equivalent circuit models for spin-wave devices and transducers. Calibrated compact models [82] must be established to progress the development of S3 implementation and of any hybrid SW-CMOS or SW-another technology circuit

- 6) Design Cost and Complexity: When talking about design cost one could consider the overall cost of the circuit design trajectory but also the actual cost of the circuit in terms of chip real estate. In principle, Spin Wave (SW) circuits can be developed by making use of the well-established CMOS design framework tailored for SW technology specifics. The main steps requiring changes are: (i) logic synthesis, (ii) circuit simulation, and (iii) physical design. (i) relates to the fact that SW technology provides natural support for Majority instead of standard Boolean gate implementations. Thus, logic synthesis needs to be changed accordingly, and such approaches have been reported in [83]-[85]. Alternatively, standard logic synthesis tools can be utilized as a 3-input Majority gate and can evaluate 2-input AND or OR by hardwiring one of the inputs to logic 0 or 1, respectively. However, such an approach may result in suboptimal circuit complexity. (ii) requires the development of appropriate SW gate SPICE simulation models as current SW circuit simulations are done by means of micromagnetic simulations. These simulations are quite accurate but impractical for large circuit designs. (iii) is required due to the very nature of the SW interference paradigm, which has different requirements on, e.g., circuit geometry and timing closure.

- 7) Fabrication Cost: We believe that SW circuits fabrication cost will be comparable or even smaller than the one of CMOS circuits because: (i) magnetic materials are already integrated in memory technology MRAM already in production, (ii) there are no special requirements nor more processing steps, and (iii) chip area savings are expected for the same functionality. However, as this is an in the making technology no cost related data are currently available. Thus, assuming that the previously mentioned design framework changes are in place, the SW circuit design cost should be comparable to the CMOS design cost. Moreover, it might be smaller given that for the same functionality SW based implementation might be less complex than the CMOS counterpart.

#### VI. CONCLUSION

In this paper we introduced a novel non Boolean algebra based computation paradigm, which enables domain conversion free ultra-low energy consumption SW based computing. Subsequently, we leveraged this computing paradigm by designing a non-binary spin wave adder, which we validated by means of micro-magnetic simulations. To get more inside on the proposed adder potential we assumed a 2-bit adder implementation as discussion vehicle, evaluated its area, delay, and energy consumption, and compared it with conventional SW and 7 nm CMOS counterparts. The results indicated that our proposal diminishes the energy consumption by a factor of 3.14× and 37×, when compared with the conventional SW and 7 nm CMOS functionally equivalent designs, respectively. Furthermore, the proposed non-binary adder implementation requires the least number of devices, which indicates SW potential for the realization of small chip real-estate beyond state-of-the-art circuits and computation platforms.

#### REFERENCES

- N. D. Shah, E. W. Steyerberg, and D. M. Kent, "Big data and predictive analytics: Recalibrating expectations," *JAMA*, vol. 320, no. 1, p. 27, Jul. 2018.

- [2] R. L. Villars, C. W. Olofson, and M. Eastwood, "Big data: What it is and why you should care," in *Proc. IDC*, 2011, pp. 1–14.

- [3] S. Agarwal et al., "International roadmap of devices and systems 2017 edition: Beyond CMOS chapter," Sandia National Lab., Albuquerque, NM, USA, Tech. Rep., 2018. [Online]. Available: https://irds.ieee.org/images/files/pdf/2017/2017IRDS\_BC.pdf

- [4] N. Z. Haron and S. Hamdioui, "Why is CMOS scaling coming to an END?" in *Proc. 3rd Int. Design Test Workshop*, Dec. 2008, pp. 98–103.

- [5] D. Mamaluy and X. Gao, "The fundamental downscaling limit of field effect transistors," *Appl. Phys. Lett.*, vol. 106, no. 19, May 2015, Art. no. 193503.

- [6] B. Hoefflinger, Chips 2020: A Guide to the Future of Nanoelectronics. Cham, Switzerland: Springer, 2012.

- [7] Y. Jiang, N. C. Laurenciu, H. Wang, and S. D. Cotofana, "Graphene nanoribbon based complementary logic gates and circuits," *IEEE Trans. Nanotechnol.*, vol. 18, pp. 287–298, 2019.

- [8] Y. Jiang, N. C. Laurenciu, and S. D. Cotofana, "On basic Boolean function graphene nanoribbon conductance mapping," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 5, pp. 1948–1959, May 2019.

- [9] J. Liu, Y. Yin, L. Yu, Y. Shi, D. Liang, and D. Dai, "Silicon-graphene conductive photodetector with ultra-high responsivity," *Sci. Rep.*, vol. 7, no. 1, pp. 1–7, Mar. 2017.

- [10] L. Huang et al., "Graphene/Si CMOS hybrid Hall integrated circuits," Sci. Rep., vol. 4, no. 1, pp. 1–6, May 2015.

- [11] F. Corinto and M. Forti, "Memristor circuits: Flux—Charge analysis method," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 63, no. 11, pp. 1997–2009, Nov. 2016.

- [12] F. Corinto, A. Ascoli, and M. Gilli, "Nonlinear dynamics of memristor oscillators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 6, pp. 1323–1336, Jun. 2011.

- [13] D. Yu, H. H.-C. Iu, Y. Liang, T. Fernando, and L. O. Chua, "Dynamic behavior of coupled memristor circuits," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 6, pp. 1607–1616, Jun. 2015.

- [14] A. Ascoli, S. Slesazeck, H. Mähne, R. Tetzlaff, and T. Mikolajick, "Non-linear dynamics of a locally-active memristor," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 4, pp. 1165–1174, Apr. 2015.

- [15] M. A. Lebdeh, H. Abunahla, B. Mohammad, and M. Al-Qutayri, "An efficient heterogeneous memristive XNOR for in-memory computing," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 9, pp. 2427–2437, Sep. 2017.

- [16] V. Calayir, D. E. Nikonov, S. Manipatruni, and I. A. Young, "Static and clocked spintronic circuit design and simulation with performance analysis relative to CMOS," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 61, no. 2, pp. 393–406, Feb. 2014.

- [17] H. Farkhani, I. L. Prejbeanu, and F. Moradi, "LAS-NCS: A laser-assisted spintronic neuromorphic computing system," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 66, no. 5, pp. 838–842, May 2019.

- [18] X. Jia, J. Yang, P. Dai, R. Liu, Y. Chen, and W. Zhao, "SPINBIS: Spintronics-based Bayesian inference system with stochastic computing," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 39, no. 4, pp. 789–802, Apr. 2020.

- [19] R. Rajaei and A. Amirany, "Nonvolatile low-cost approximate spintronic full adders for computing in memory architectures," *IEEE Trans. Magn.*, vol. 56, no. 4, pp. 1–8, Apr. 2020.

- [20] Y. Halawani, B. Mohammad, D. Homouz, M. Al-Qutayri, and H. Saleh, "Modeling and optimization of memristor and STT-RAM-based memory for low-power applications," *IEEE Trans. Very Large Scale Integr. (VLSI)* Syst., vol. 24, no. 3, pp. 1003–1014, Mar. 2016.

- [21] A. Lyle, J. Harms, S. Patil, X. Yao, D. J. Lilja, and J.-P. Wang, "Direct communication between magnetic tunnel junctions for nonvolatile logic fan-out architecture," *Appl. Phys. Lett.*, vol. 97, no. 15, Oct. 2010, Art. no. 152504, doi: 10.1063/1.3499427.

- [22] S. Luo et al., "Reconfigurable skyrmion logic gates," Nano Lett., vol. 18, no. 2, pp. 1180–1184, Feb. 2018.

- [23] Z. Z. Zhang et al., "Skyrmion-based ultra-low power electric-field-controlled reconfigurable (SUPER) logic gate," IEEE Electron Device Lett., vol. 40, no. 12, pp. 1984–1987, Dec. 2019, doi: 10.1109/LED.2019.2946863.

- [24] K. Zhang et al., "Rectified tunnel magnetoresistance device with high on/off ratio for in-memory computing," *IEEE Electron Device Lett.*, vol. 41, no. 6, pp. 928–931, Jun. 2020.

- [25] Z. Luo et al., "Reconfigurable magnetic logic combined with non-volatile memory writing," Adv. Mater., vol. 29, no. 4, Jan. 2017, Art. no. 1605027.

- [26] K. Bernstein, R. K. Cavin, III, W. Porod, A. Seabaugh, and J. Welser, "Device and architecture outlook for beyond CMOS switches," *Proc. IEEE*, vol. 98, no. 12, pp. 2169–2184, Dec. 2010.

- [27] A. Mahmoud *et al.*, "Introduction to spin wave computing," *J. Appl. Phys.*, vol. 128, no. 16, Oct. 2020, Art. no. 161101, doi: 10.1063/5.0019328.

- [28] A. Mahmoud, F. Vanderveken, C. Adelmann, F. Ciubotaru, S. Hamdioui, and S. Cotofana, "Fan-out enabled spin wave majority gate," AIP Adv., vol. 10, no. 3, Mar. 2020, Art. no. 035119, doi: 10.1063/1.5134690.

- [29] A. Mahmoud, F. Vanderveken, C. Adelmann, F. Ciubotaru, S. Cotofana, and S. Hamdioui, "2-output spin wave programmable logic gate," in *Proc. IEEE Comput. Soc. Annu. Symp. VLSI (ISVLSI)*, Jul. 2020, pp. 60–65.

- [30] A. Mahmoud, F. Vanderveken, F. Ciubotaru, C. Adelmann, S. Coto-fana, and S. Hamdioui, "N-bit data parallel spin wave logic gate," in *Proc. Design, Autom. Test Eur. Conf. Exhib. (DATE)*, Mar. 2020, pp. 642–645.

- [31] M. P. Kostylev, A. A. Serga, T. Schneider, B. Leven, and B. Hillebrands, "Spin-wave logical gates," *Appl. Phys. Lett.*, vol. 87, no. 15, Oct. 2005, Art. no. 153501, doi: 10.1063/1.2089147.

- [32] K.-S. Lee and S.-K. Kim, "Conceptual design of spin wave logic gates based on a Mach–Zehnder-type spin wave interferometer for universal logic functions," *J. Appl. Phys.*, vol. 104, no. 5, Sep. 2008, Art. no. 053909, doi: 10.1063/1.2975235.

- [33] T. Schneider, A. A. Serga, B. Leven, B. Hillebrands, R. L. Stamps, and M. P. Kostylev, "Realization of spin-wave logic gates," *Appl. Phys. Lett.*, vol. 92, no. 2, Jan. 2008, Art. no. 022505, doi: 10.1063/1.2834714.

- [34] A. N. Mahmoud, F. Vanderveken, C. Adelmann, F. Ciubotaru, S. Hamdioui, and S. Cotofana, "Multifrequency data parallel spin wave logic gates," *IEEE Trans. Magn.*, vol. 57, no. 5, pp. 1–12, May 2021.

- [35] A. Khitun, "Multi-frequency magnonic logic circuits for parallel data processing," J. Appl. Phys., vol. 111, no. 5, Mar. 2012, Art. no. 054307, doi: 10.1063/1.3689011.

- [36] A. Khitun, "Magnonic holographic devices for special type data processing," *J. Appl. Phys.*, vol. 113, no. 16, Apr. 2013, Art. no. 164503, doi: 10.1063/1.4802656.

- [37] F. Gertz, A. Kozhevnikov, Y. Filimonov, and A. Khitun, "Magnonic holographic memory," *IEEE Trans. Magn.*, vol. 51, no. 4, pp. 1–5, Apr. 2015.

- [38] A. Kozhevnikov, F. Gertz, G. Dudko, Y. Filimonov, and A. Khitun, "Pattern recognition with magnonic holographic memory device," *Appl. Phys. Lett.*, vol. 106, no. 14, Apr. 2015, Art. no. 142409, doi: 10.1063/1.4917507.

- [39] F. Gertz, A. V. Kozhevnikov, Y. A. Filimonov, D. E. Nikonov, and A. Khitun, "Magnonic holographic memory: From proposal to device," *IEEE J. Explor. Solid-State Comput. Devices Circuits*, vol. 1, pp. 67–75, 2015.

- [40] F. Gertz, A. Kozhevnikov, Y. Filimonov, and A. Khitun, "Magnonic holographic read-only memory," *IEEE Magn. Lett.*, vol. 7, pp. 1–4, 2016.

- [41] A. Khitun and K. L. Wang, "Non-volatile magnonic logic circuits engineering," *J. Appl. Phys.*, vol. 110, no. 3, Aug. 2011, Art. no. 034306, doi: 10.1063/1.3609062.

- [42] S. Khasanvis, M. Rahman, S. N. Rajapandian, and C. A. Moritz, "Wave-based multi-valued computation framework," in *Proc. IEEE/ACM Int. Symp. Nanosc. Architectures (NANOARCH)*, Jul. 2014, pp. 171–176.

- [43] G. Csaba, A. Papp, and W. Porod, "Spin-wave based realization of optical computing primitives," J. Appl. Phys., vol. 115, no. 17, 2014, Art. no. 17C741, doi: 10.1063/1.4868921.

- [44] P. Shabadi, S. N. Rajapandian, S. Khasanvis, and C. A. Moritz, "Design of spin wave functions-based logic circuits," SPIN, vol. 2, no. 3, Sep. 2012, Art. no. 1240006, doi: 10.1142/S2010324712400061.

- [45] K. Vogt et al., "Realization of a spin-wave multiplexer," Nature Commun., vol. 5, p. 3727, Jan. 2014.

- [46] M. Balynsky et al., "Parallel data processing with magnonic holographic co-processor," in Proc. IEEE Int. Conf. Rebooting Comput. (ICRC), Oct. 2016, pp. 1–4.

- [47] A. Khitun, "Magnonic holographic co-processor: An approach to energy-efficient complementary logic circuitry," in *Proc. 4th Berkeley Symp. Energy Efficient Electron. Syst.* (E S), Oct. 2015, pp. 1–3.

- [48] F. Gertz et al., "Parallel read-out and database search with magnonic holographic memory," *IEEE Trans. Magn.*, vol. 52, no. 7, pp. 1–4, Jul. 2016.

- [49] O. Zografos et al., "Wave pipelining for majority-based beyond-CMOS technologies," in Proc. Design, Autom. Test Eur. Conf. Exhib. (DATE), Mar. 2017, pp. 1306–1311.

- [50] A. Mahmoud, F. Vanderveken, C. Adelmann, F. Ciubotaru, S. Hamdioui, and S. Cotofana, "Achieving wave pipelining in spin wave technology," in *Proc. 22nd Int. Symp. Qual. Electron. Design (ISQED)*, 2021, pp. 54–59.

- [51] T. Brächer and P. Pirro, "An analog magnon adder for all-magnonic neurons," J. Appl. Phys., vol. 124, no. 15, Oct. 2018, Art. no. 152119, doi: 10.1063/1.5042417.

- [52] A. Mahmoud, F. Vanderveken, F. Ciubotaru, C. Adelmann, S. Cotofana, and S. Hamdioui, "Spin wave based full adder," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2021, pp. 1–5.

- [53] A. N. Mahmoud, F. Vanderveken, C. Adelmann, F. Ciubotaru, S. Cotofana, and S. Hamdioui, "Spin wave normalization toward all magnonic circuits," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 68, no. 1, pp. 536–549, Jan. 2020.

- [54] A. Mahmoud, F. Vanderveken, F. Ciubotaru, C. Adelmann, S. Ham-dioui, and S. Cotofana, "Spin wave based approximate computing," *IEEE Trans. Emerg. Topics Comput.*, early access, Dec. 4, 2021, doi: 10.1109/TETC.2021.3136299.

- [55] A. Mahmoud, F. Vanderveken, F. Ciubotaru, C. Adelmann, S. Cotofana, and S. Hamdioui, "Spin wave based 4–2 compressor," in Proc. 28th IEEE Int. Conf. Electron., Circuits, Syst. (ICECS), Nov. 2021, pp. 1–4.

- [56] A. N. Mahmoud, F. Vanderveken, F. Ciubotaru, C. Adelmann, S. Hamdioui, and S. Cotofana, "A spin wave-based approximate 4:2 compressor: Seeking the most energy-efficient digital computing paradigm," *IEEE Nanotechnol. Mag.*, vol. 16, no. 1, pp. 47–56, Feb. 2021.

- [57] M. Balynskiy, H. Chiang, D. Gutierrez, A. Kozhevnikov, Y. Filimonov, and A. Khitun, "Reversible magnetic logic gates based on spin wave interference," *J. Appl. Phys.*, vol. 123, no. 14, Apr. 2018, Art. no. 144501, doi: 10.1063/1.5011772.

- [58] A. Khitun, "Parallel database search and prime factorization with magnonic holographic memory devices," *J. Appl. Phys.*, vol. 118, no. 24, Dec. 2015, Art. no. 243905, doi: 10.1063/1.4938739.

- [59] M. Rahman, S. Khasanvis, J. Shi, and C. A. Moritz, "Wave interference functions for neuromorphic computing," *IEEE Trans. Nanotechnol.*, vol. 14, no. 4, pp. 742–750, Jul. 2015.

- [60] L. Landau and E. Lifshitz, "On the theory of the dispersion of magnetic permeability in ferromagnetic bodies," *Phys. Z. Sowjetunion*, vol. 8, pp. 101–114, Jan. 1935.

- [61] T. L. Gilbert, "A phenomenological theory of damping in ferromagnetic materials," *IEEE Trans. Magn.*, vol. 40, no. 6, pp. 3443–3449, Nov. 2004.

- [62] R. Verba, G. Melkov, V. Tiberkevich, and A. Slavin, "Collective spin-wave excitations in a two-dimensional array of coupled magnetic nanodots," *Phys. Rev. B, Condens. Matter*, vol. 85, no. 1, Jan. 2012, doi: 10.1103/PhysRevB.85.014427.

- [63] M. Beleggia, S. Tandon, Y. Zhu, and M. De Graef, "On the magnetostatic interactions between nanoparticles of arbitrary shape," *J. Magn. Magn. Mater.*, vol. 278, nos. 1–2, pp. 270–284, 2004. [Online]. Available: http://www.sciencedirect.com/science/article/pii/S0304885304000186

- [64] Q. Wang, P. Pirro, R. Verba, A. Slavin, B. Hillebrands, and A. V. Chumak, "Reconfigurable nanoscale spin-wave directional coupler," *Sci. Adv.*, vol. 4, no. 1, p. 1701517, Jan. 2018. [Online]. Available: https://advances.sciencemag.org/content/4/1/e1701517

- [65] Q. Wang et al., "A magnonic directional coupler for integrated magnonic half-adders," Nature Electron., vol. 3, no. 12, pp. 765–774, Dec. 2020.

- [66] A. V. Sadovnikov, E. N. Beginin, S. E. Sheshukova, D. V. Romanenko, Y. P. Sharaevskii, and S. A. Nikitov, "Directional multimode coupler for planar magnonics: Side-coupled magnetic stripes," *Appl. Phys. Lett.*, vol. 107, no. 20, Nov. 2015, Art. no. 202405, doi: 10.1063/1.4936207.

- [67] H. G. Bauer, P. Majchrak, T. Kachel, C. H. Back, and G. Woltersdorf, "Nonlinear spin-wave excitations at low magnetic bias fields," *Nature Commun.*, vol. 6, no. 1, pp. 1–7, Nov. 2015.

- [68] A. V. Sadovnikov, S. A. Odintsov, E. N. Beginin, S. E. Sheshukova, Y. P. Sharaevskii, and S. A. Nikitov, "Toward nonlinear magnonics: Intensity-dependent spin-wave switching in insulating side-coupled magnetic stripes," *Phys. Rev. B, Condens. Matter*, vol. 96, no. 14, Oct. 2017, Art. no. 144428, doi: 10.1103/PhysRevB.96.144428.

- [69] R. Verba, M. Carpentieri, G. Finocchio, V. Tiberkevich, and A. Slavin, "Excitation of propagating spin waves in ferromagnetic nanowires by microwave voltage-controlled magnetic anisotropy," *Sci. Rep.*, vol. 6, no. 1, pp. 1–9, Jul. 2016.

- [70] P. Krivosik and C. E. Patton, "Hamiltonian formulation of nonlinear spin-wave dynamics: Theory and applications," *Phys. Rev. B, Condens. Matter*, vol. 82, no. 18, Nov. 2010, Art. no. 184428, doi: 10.1103/PhysRevB.82.184428.

- [71] A. Mahmoud, F. Vanderveken, C. Adelmann, F. Ciubotaru, S. Hamdioui, and S. Cotofana, "4-Output programmable spin wave logic gate," in *Proc. IEEE 38th Int. Conf. Comput. Design (ICCD)*, Oct. 2020, pp. 332–335.

- [72] A. Mahmoud, C. Adelmann, F. Vanderveken, S. Cotofana, F. Ciubotaru, and S. Hamdioui, "Fan-out of 2 triangle shape spin wave logic gates," in *Proc. Design, Autom. Test Eur. Conf. Exhib. (DATE)*, Feb. 2021, pp. 948–953.

- [73] S. Cotofana and S. Vassiliadis, "Signed digit addition and related operations with threshold logic," *IEEE Trans. Comput.*, vol. 49, no. 3, pp. 193–207, Mar. 2000.

- [74] S. Cotofana and S. Vassiliadis, "Periodic symmetric functions, serial addition, and multiplication with neural networks," *IEEE Trans. Neural Netw.*, vol. 9, no. 6, pp. 1118–1128, Nov. 1998.

- [75] N. Ebeid and M. A. Hasan, "On binary signed digit representations of integers," *Des.*, *Codes Cryptogr.*, vol. 42, no. 1, pp. 43–65, Jan. 2007.

- [76] A. Vansteenkiste, J. Leliaert, M. Dvornik, M. Helsen, F. Garcia-Sanchez, and B. Van Waeyenberge, "The design and verification of MuMax3," AIP Adv., vol. 4, no. 10, Oct. 2014, Art. no. 107133, doi: 10.1063/1.4899186.

- [77] T. Devolder et al., "Time-resolved spin-torque switching in MgO-based perpendicularly magnetized tunnel junctions," Phys. Rev. B, Condens. Matter, vol. 93, no. 2, Jan. 2016, Art. no. 024420, doi: 10.1103/ PhysRevB.93.024420.

- [78] O. Zografos et al., "Design and benchmarking of hybrid CMOS-spin wave device circuits compared to 10 nm CMOS," in Proc. IEEE 15th Int. Conf. Nanotechnol. (IEEE-NANO), Jul. 2015, pp. 686–689.

- [79] O. Abdelkader et al., "Technology scaling roadmap for FinFET-based FPGA clusters under process variations," J. Circuits, Syst. Comput., vol. 27, no. 4, Apr. 2018, Art. no. 1850056.

- [80] Q. Wang et al., "Spin pinning and spin-wave dispersion in nanoscopic ferromagnetic waveguides," Phys. Rev. Lett., vol. 122, no. 24, Jun. 2019, Art. no. 247202, doi: 10.1103/PhysRevLett.122.247202.

- [81] A. Mahmoud et al., "Would magnonic circuits outperform CMOS counterparts?" in Proc. Great Lakes Symp. VLSI, Jun. 2022, pp. 1–5, doi: 10.1145/3526241.3530368.

- [82] S. Dutta, D. E. Nikonov, S. Manipatruni, I. A. Young, and A. Naeemi, "SPICE circuit modeling of PMA spin wave bus excited using magnetoelectric effect," *IEEE Trans. Magn.*, vol. 50, no. 9, pp. 1–11, Sep. 2014

- [83] L. Amarú, P.-E. Gaillardon, and G. De Micheli, "BDS-MAJ: A BDD-based logic synthesis tool exploiting majority logic decomposition," in Proc. 50th Annu. Design Autom. Conf. (DAC), 2013, pp. 1–6.

- [84] L. Amaru, P. E. Gaillardon, and G. D. Micheli, "Majority-inverter graph: A new paradigm for logic optimization," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 35, no. 5, pp. 806–819, May 2016.

- [85] O. Zografos, L. Amaru, P. Gaillardon, P. Raghavan, and G. D. Micheli, "Majority logic synthesis for spin wave technology," in *Proc. 17th Euromicro Conf. Digit. Syst. Design*, Aug. 2014, pp. 691–694.

Abdulqader Nael Mahmoud (Graduate Student Member, IEEE) received the Bachelor of Science degree in electrical and electronics engineering and the M.S. degree in electrical and computer engineering from Khalifa University, Abu Dhabi, United Arab Emirates, in 2015 and 2017, respectively, and the Ph.D. degree in computer engineering from the Delft University of Technology, Delft, The Netherlands, in 2022, where he focused on the spin wave-based circuit design. His M.Sc. research focused on low-power mixed signal integrated circuit

design including DC–DC power converters targeting high-power efficiency. He is currently working as a Mixed Signal Design Engineer with the Research and Development Department, NXP Semiconductor Company, Nijmegen, The Netherlands, where he is designing mixed signal circuits for automotive vehicles.

Frederic Vanderveken received the B.S. degree in electrical engineering and the M.S. degree in nanotechnology, nanoscience, and nano-engineering from KU Leuven University, Belgium, in 2016 and 2018, respectively. He joined IMEC as a Ph.D. Researcher to expand the knowledge of magnetoelastic coupling for high-frequency applications. His current research interests include modeling of magnetoelastic coupling, simulations of spintronic devices, optimizations of magnetoelectric transducers, and spin logic applications.

Florin Ciubotaru (Member, IEEE) received the B.Sc. and M.Sc. degrees in physics from Alexandru Ioan Cuza University, Iaşi, Romania, in 2003 and 2005, respectively, and the Ph.D. degree in physics from Technische Universität Kaiserslautern, Germany, in 2012. He was the beneficiary of an EU Marie Curie Fellowship. In 2014, he joined KU Leuven; and IMEC, Belgium, as a Post-Doctoral Research Fellow. In 2016, he started as Senior Scientist at IMEC and became a Principal Member of Technical Staff in 2019. He currently works on the

development of logic, radio-frequency, and sensor devices based on magnetic spin-related phenomena. He is the coauthor of 26 papers, two granted patents, and two patent applications.