# An Adaptive 2-Mode Bias-Flip Rectifier with Lowered Cold-Startup Voltage Requirement for Multiple Piezoelectric Energy Harvesting

Yue, Xinling; Du, Sijun

DOI

10.1109/TPEL.2025.3532856

**Publication date**

**Document Version** Final published version

Published in

**IEEE Transactions on Power Electronics**

Citation (APA)

Yue, X., & Du, S. (2025). An Adaptive 2-Mode Bias-Flip Rectifier with Lowered Cold-Startup Voltage Requirement for Multiple Piezoelectric Energy Harvesting. *IEEE Transactions on Power Electronics*, 40(6), 8283 - 8291. https://doi.org/10.1109/TPEL.2025.3532856

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# An Adaptive Two-Mode Bias-Flip Rectifier With Lowered Cold-Startup Voltage Requirement for Multiple Piezoelectric Energy Harvesting

Xinling Yue, Graduate Student Member, IEEE, and Sijun Du, Senior Member, IEEE

Abstract—Various bias-flip rectifiers were proposed to improve the energy extraction performance for piezoelectric energy harvesting (PEH), which requires a power supply. However, no stable power supply is available when the system starts from a cold state. Typically, during the cold state, the system operates as a passive full bridge rectifier (FBR) to build up a stable power supply by charging a capacitor and then switching to the active rectifier after the cold state. Unfortunately, the system cannot start up if the open circuit voltage from a piezoelectric transducer (PT) is lower than the required supply voltage level. As a result, the system would end up with cold startup failure. This article proposes a two-mode bias-flip rectifier, which addresses the startup issue by lowering the required input open circuit voltage from the PT. The proposed design was fabricated in a 180-nm BCD process. Measurement results show that the necessary open-circuit voltage from the PT is lowered by 73% to achieve a successful cold startup, and the proposed system achieves 1182% energy extraction enhancement compared to a passive FBR.

Index Terms—Bias-flip rectifier, cold-startup, open circuit voltage, piezoelectric energy harvesting (PEH), synchronized switch harvesting on inductor (SSHI) rectifier.

#### I. INTRODUCTION

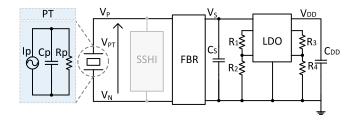

NERGY harvesting (EH) has become a promising solution to replace traditional batteries, often bulky and costly for maintenance in Internet-of-Things applications. The EH can scavenge energy from many external sources, e.g., solar, thermal, RF, and kinetic, etc., to power low-energy electronics [1], [2], [3], [4], [5], [6]. Among these energy sources, kinetic energy has the benefits of low cost, low operating frequency, and high power density, which is around  $10-500 \ \mu \text{W}cm^{-2}$ . The kinetic energy is converted to electrical energy through a piezoelectric transducer (PT). A weakly coupled PT vibrating at its resonance frequency can be modeled as an ac current source,  $I_P$ , in parallel with an intrinsic capacitor,  $C_P$ , and a resistor,  $R_P$ , as shown in the left of Fig. 1. Since the output of the PT is ac energy, a rectifier is required to convert the ac into dc energy to power loads [7], [8], [9], [10], [11], [12].

Received 21 June 2024; revised 16 October 2024 and 13 December 2024; accepted 20 January 2025. Date of publication 24 January 2025; date of current version 20 March 2025. Recommended for publication by Associate Editor Michael A. E. A.E. Andersen. (Corresponding author: Sijun Du.)

The authors are with the Department of Microelectronics, Delft University of Technology, 2628CD Delft, The Netherlands (e-mail: sijun.du@tudelft.nl).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TPEL.2025.3532856.

Digital Object Identifier 10.1109/TPEL.2025.3532856

Fig. 1. Conventional cold-startup circuit working as an FBR.

The most straightforward and typical ac–dc rectifier is a full bridge rectifier (FBR) [13]. It employs four passive diodes and does not require any active components while sacrificing the power extraction efficiency. The poor performance of an FBR is caused by the PT voltage flipping moment from positive to negative, or vice versa, at the zero-crossing moment of  $I_P$ . And in this process, the FBR has to flip the PT voltage slowly with the charge harvested by the PT itself. The passive diodes' high voltage thresholds also dissipate extra energy. To improve the output power efficiency, some active bias-flip rectifiers were proposed in recent years [13], [14], [15], [16], [17]. An efficient bias-flip rectifier, named synchronized switch harvesting on inductor (SSHI) rectifier, has been verified that it can enhance the output power efficiency largely with the help of using an inductor to flip the PT voltage [18], [19], [20], [21], [22].

An SSHI rectifier requires a stable voltage supply  $(V_{DD})$  to operate and control the active switches. However, there is no available dc voltage supply when the system starts from a cold state, resulting in the system having to operate as a passive FBR to build up a stable dc supply. After the cold state, when the voltage supply is ready, the active rectifier will work normally. However, the input open circuit voltage amplitude  $(V_{OC})$  from the PT can be very low, e.g., 0.5 V, in many applications when the PT is implemented in a low-excitation environment. In this case, the system would never build up a stable voltage supply from the low  $V_{OC}$ , and the system cannot start up normally. As a result, the active rectifier will not be engaged. Most prior research works do not give much detail about achieving cold-startup in low  $V_{OC}$ , and they employ precharged capacitors to avoid startup issues [23], [24], [25]. Du et al. [26] divides the PT into two regions and utilizes a specific region to effectively increase the  $V_{OC}$  by sacrificing some generated power. The authors in [27] proposed a reconfigurable SSHI rectifier with

0885-8993 © 2025 IEEE. All rights reserved, including rights for text and data mining, and training of artificial intelligence and similar technologies. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

only one PT, involving four diodes and four capacitors. There are also two modes: 1) mode I and 2) mode II. In mode I, the system works as a voltage multiplier, while in mode II, it works as a typical SSHI with two load capacitors connected in series, reducing the effective output capacitance. The authors in [28] proposed a self-configurable rectifier for an extended operating range of piezoelectric energy harvesting (PEH). However, it only configures an FBR and a voltage doubler, resulting in a limited extension.

Recently multiple PTs energy harvesting techniques have drawn much attention due to their high power density [29], [30], [31]. However, they are not focusing on cold-startup circuit in low excitation. This article investigates an SSHI rectifier with low input open circuit voltage for multiple-PT energy harvesting. The input  $V_{OC}$  is 0.5 V and desired power supply is 1.8 V. The system cannot start up normally for a typical FBR circuit with such a low  $V_{OC}$ . The proposed bias-flip rectifier has two configurable modes, and 4 PTs are employed as the energy sources. The 4 PTs are configured in series connection, namely, mode I, to address the cold-startup issue for low  $V_{OC}$  and build up a high power supply. At the end of mode I, a 1.8-V voltage supply becomes available, ending the cold state. Consequently, the configuration changes to parallel, namely mode II, to achieve higher power tracking and output power efficiency. Compared with other rectifiers [1], [2], [3], the proposed rectifier in our work does not increase the overall cost, as it utilizes the same inductor shared among the input piezoelectric transducers (PTs).

The rest of this article is organized as follows. Section II analyzes the cold startup in traditional and proposed rectifiers. Section III shows the proposed system and circuit implementations, respectively. The measurement results are presented in Section IV. Finally, Section V concludes this article.

#### II. PROPOSED COLD-STARTUP THEORETICAL ANALYSIS

#### A. Cold-Startup in Conventional Circuit

In a cold state, there is no available power supply. The active rectifier would operate as an FBR instead until the power supply,  $V_{DD}$ , is available. Fig. 1 shows the conventional cold-startup circuit. The PT consists of an ac current source,  $I_P$ , in parallel with a capacitor,  $C_P$ , and a large resistor,  $R_P$ . The  $V_{PT}$  is the voltage across PT. In the cold state, the SSHI rectifier is disabled, and only an FBR combined with a low dropout (LDO) regulator can work. The  $C_S$  is the storage capacitor, and  $V_S$  is the output voltage. The LDO is used to build up a  $V_{DD}$  charged by  $C_{DD}$  whose energy is derived from the storage capacitor,  $C_S$ . In traditional FBR circuits, the maximum  $V_{DD}$  can be expressed by

$$V_{DD} = V_{S(MAX)} = V_{OC} - 2V_D \tag{1}$$

where  $V_D$  is the voltage drop of the diode. According to (1), the  $V_{DD}$  is lower than the open circuit voltage  $V_{OC}$ . If  $V_{OC}$  is too low to build up a required  $V_{DD}$ , the circuit would not start up normally, and the system would end up with startup failure.

The output power of an FBR can be written as [32]

$$P_{FBR} = 4C_P V_S f_P (V_{OC} - V_S - 2V_D).$$

(2)

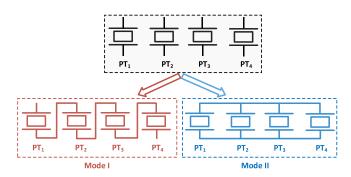

Fig. 2. Multiple energy source inputs of the proposed system for eased cold startup.

When the 4 PTs are connected in parallel as the input, the effective  $C_P$  is increased by  $4\times$  while the open circuit voltage remains unchanged. Therefore, the output power of a conventional FBR with 4 PTs connected in parallel is expressed by

$$P_{FBRP} = 4 \times 4 \times C_P V_S f_P (V_{OC} - V_S - 2V_D)$$

= 16 \times C\_P V\_S f\_P (V\_{OC} - V\_S - 2V\_D). (3)

#### B. Cold-Startup in Proposed Circuit

In the proposed SSHI rectifier, there are four identical PTs employed as the input energy sources [33]. The PTs have the same intrinsic capacitance and resonant frequency. They are implemented on the same vibrating substrate. On the other hand, the four cantilevers are tip-clipped together to avoid off-phase vibration. The proposed 4 PT models,  $PT_1$ ,  $PT_2$ ,  $PT_3$ ,  $PT_4$ , are expressed in Fig. 2, each of them representing a typical PT as shown on the left of Fig. 1. During the cold state, the 4 PTs are connected in Mode I, where PTs are connected in series to generate a summed-up input open circuit voltage amplitude,  $V_{OCE}$ . The  $V_{OCE}$  can be expressed as follows:

$$V_{OCE} = 4 \times V_{OC} \tag{4}$$

where the  $V_{OC}$  is the open circuit voltage generated by one PT. Equation (4) shows that the effective open circuit voltage  $V_{OCE}$  is theoretically increased by  $4\times$ . Considering (1), the required power supply  $V_{DD}$  obtained from the new system can be written

$$V_{DD} = 4 \times V_{OC} - 2 \times V_D. \tag{5}$$

If the desired power supply for the system is 1.8 V, the minimum  $V_{OC}$  of each single PT can be lowered to around 0.5 V ( $V_{OC} = (1.8 + 2 \times 0.1)/4$ V), assuming that the voltage drop,  $V_D$  of the diode is roughly 0.1 V. In a conventional circuit,  $V_{OC} = 0.5$  V is too low to start up. While in the proposed circuit, the system can build up a 1.8V- $V_{DD}$ , and the active rectifier would normally work after the cold state.

When the 4 PTs are connected in series, the  $C_P$  becomes  $4 \times$  smaller while the  $V_{OC}$  increases  $4 \times$ . According to (2), the output power of an FBR with 4 PTs connected in series is expressed by

$$P_{FBRS} = C_P V_S f_P (4V_{OC} - V_S - 2V_D). \tag{6}$$

# C. Better Output Power Tracking Consideration After Cold-Startup

For a typical SSHI rectifier, the output power,  $P_{SSHI}$  can be expressed as

$$P_{SSHI} = 2f_P C_P V_S (2V_{OC} - (V_S + 2V_D)(1 - \eta_F))$$

(7)

where  $f_P$  is the PT vibration frequency and  $\eta_F$  is the flipping efficiency of the SSHI rectifier.

When there are 4 PTs connected in series, the power expression  $P_{SSHIS}$  is written by

$$P_{SSHIS} = 4f_P C_P V_S V_{OC} - \frac{1}{2} f_P C_P V_S (V_S + 2V_D) (1 - \eta_F).$$

(8)

When there are 4 PTs connected in parallel, the power expression  $P_{SSHIP}$  is written by

$$P_{SSHIP} = 16 f_P C_P V_S V_{OC} - 8 f_P C_P V_S (V_S + 2V_D) (1 - \eta_F).$$

(9)

From (7), it can be found that the maximum power can be achieved by making  $V_S = \frac{V_{OC}}{1-\eta_F} - V_D$ . The maximum power can be expressed by

$$P_{SSHI(MAX)} = 2C_P f_P \left(\frac{V_{OC}}{1 - \eta_F} - V_D\right)^2 (1 - \eta_F).$$

(10)

Equation (10) shows that the maximum power is highly dependent on  $V_{OC}$  and flipping efficiency  $\eta_F$ . In the proposed circuit, the system is operated with the initial conditions:  $V_{OC}$ =0.5 V,  $\eta_F$  around 80%. When the active SSHI rectifier works normally, the output voltage  $V_S$  goes higher, resulting in a lower voltage drop,  $V_D$ . As  $V_D$  is very small, the maximum power is dominated by  $V_{OC}$  and  $\eta_F$ . For the SSHI rectifier with four series connected PTs, by making the optimal voltage  $V_{S1} = \frac{4V_{OC}}{1-\eta_F} - V_D$ , the maximum output power,  $P_{SSHI(MAXS)}$ , can be expressed as

$$P_{SSHI(MAXS)} = \frac{1}{2} f_P C_P \left( \frac{4V_{OC}}{1 - \eta_F} - V_D \right)^2 (1 - \eta_F). \tag{11}$$

Assuming  $V_D = 0$  when active diodes are employed in the rectifier, (11) can be written as

$$P_{SSHI(MAXS)} \approx 8 f_P C_P \left(\frac{V_{OC}}{1 - \eta_F}\right)^2 (1 - \eta_F).$$

(12)

When the SSHI rectifier is connected with four parallel-connected PTs, by making the optimal output voltage  $V_{S2} = \frac{V_{OC}}{1-\eta_F} - V_D$ , the maximum output power,  $P_{SSHI(MAXP)}$  is written as

$$P_{SSHI(MAXP)} = 8f_P C_P \left(\frac{V_{OC}}{1 - \eta_F} - V_D\right)^2 (1 - \eta_F).$$

(13)

Similarly, (13) can be written as

$$P_{SSHI(MAXP)} \approx 8 f_P C_P \left(\frac{V_{OC}}{1 - \eta_F}\right)^2 (1 - \eta_F).$$

(14)

Considering (12) and (14), they have the same expression, meaning that the connection configuration does not change the

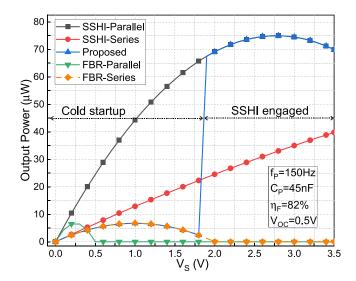

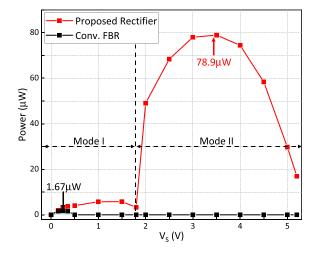

Fig. 3. Simulated output power of the rectifier with series and parallels PTs connection

peak rectified output power. However, the maximum values are achieved at different output voltage levels, with  $V_{S1}=\frac{4V_{OC}}{1-\eta_F}-V_D$  and  $V_{S2}=\frac{V_{OC}}{1-\eta_F}-V_D$  for series and parallel connections, respectively. Assuming that the  $V_{OC}=0.5\,\mathrm{V}$  and  $\eta_F=82\%$ , the optimal output voltages for the maximum power in series and parallel connections are  $V_{S1}=11.1\,\mathrm{V}$  and  $V_{S2}=2.78\,\mathrm{V}$ , respectively. Considering the device breakdown voltage of onchip CMOS switches is 5 V, the low  $V_{S2}$  in parallel connection is better for higher output power if the system has been started.

Fig. 3 shows the output power for different PT connections: parallel-FBR in (3), series-FBR in (6), series-SSHI in (8), and parallel-SSHI in (9). The figure illustrates that the parallel-connected PT FBR has a smaller output power and cannot establish a stable power supply. While the PT is in an FBR connection, it can build up an up to 2 V voltage. When a 1.8 V voltage is ready, the SSHI rectifier will work. Fig. 3 shows that the PT parallel-connected SSHI rectifier has a higher output than the series-connected SSHI rectifier. Therefore, during the cold state, the PTs are connected in series to build a stable high  $V_{DD}$ , namely, mode I. Once the  $V_{DD}$  is ready, the PTs are switched to a parallel connection to extract more power, defined as mode II.

#### III. SYSTEM ARCHITECTURE AND CIRCUIT IMPLEMENTATION

#### A. System Architecture

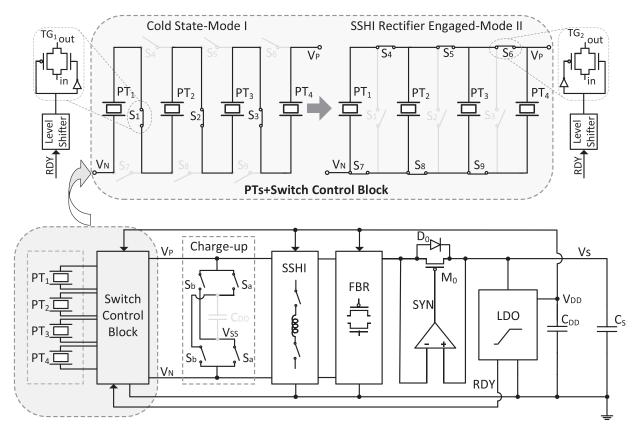

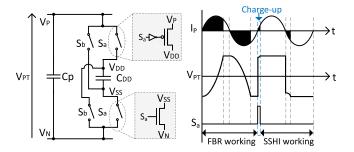

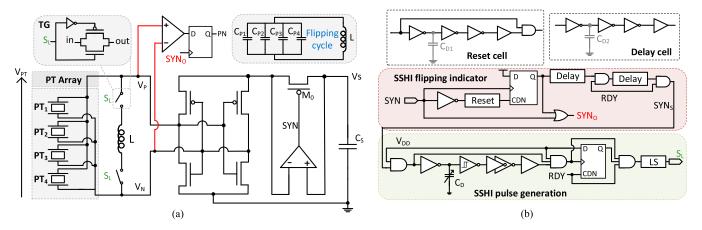

The system architecture is presented in Fig. 4. There are mainly five blocks: A switch control block, a charge-up block, an SSHI rectifier, an FBR and an active diode, an LDO with a load capacitor,  $C_{DD}$ , to provide a stable power supply in the cold-state. There are 4 identical PTs,  $PT_1$ ,  $PT_2$ ,  $PT_3$ , and  $PT_4$  as the inputs. When the system starts from the cold-state with a low input open circuit voltage, these 4 PTs are working in mode I, where the PTs are all connected in series by turning ON  $S_1$  to  $S_3$  and turning OFF  $S_4$  to  $S_9$ . This method allows the effectual output open circuit voltage up to  $4\times$  higher than a single PT. The  $S_1$  to  $S_3$  are the same as  $TG_1$  as shown on the left of Fig. 4,

Fig. 4. System architecture of the two-mode switching bias-flip rectifier.

which is turned ON by low input. Meanwhile, the  $S_4$  to  $S_9$  are the same as  $TG_2$ , as shown on the right, which is turned ON by high input. When the system starts to harvest energy, a RDY signal is generated from the LDO and used to generate a  $SYN_C$  signal to control the switch control block. It follows the output voltage at first and turns to low when the power supply  $V_{DD}$  is ready, indicating that the cold state is finished.

When the cold-state is finished, as mentioned in Section II-C, the connection will be switched from series (mode I) to parallels (mode II) to extract higher power. However, when the connection changes from series from parallels, the voltage,  $V_{PT}$ , will drop naturally by  $4\times$  instantly. Since the single open circuit voltage is only around 0.5 V, it is impossible to charge the dropped  $V_{PT}$  to the threshold voltage  $V_S + 2V_D$  (around 1.8 V). Thus, a charge-up block is required to help  $C_P$  to overcome the threshold voltage after the PTs connection is changed. The charge-up block is implemented by two switches,  $S_a$  and  $S_b$ , and the load capacitor,  $C_{DD}$ , of the LDO as shown in Fig. 4. After the charge-up finishes, the system will operate as an active SSHI rectifier with four paralleled PTs. The circuit implementation details of the system are shown in the following contents.

The FBR includes four cross-connected MOSFETs. The active diode,  $M_0$ , is connected to the output storage capacitor,  $C_S$ , and can prevent the reverse current out of  $C_S$ . The left FBR consists of 4 cross-connected MOSFETs. When the rectified voltage reaches the threshold voltage, the  $M_0$  is ON. Otherwise, it is OFF. The ON-OFF state of the  $M_0$  is controlled by a synchronized signal, SYN, generated from the active diode's comparator.

Fig. 5. Key signals during the transition moment of the two modes.

When the system starts from the cold state, the SYN is not high enough to open  $M_0$  since the threshold voltage of  $M_0$  is around 800 mV. In this case, the body diode  $D_0$  is the main door for the current to flow into  $C_S$ .

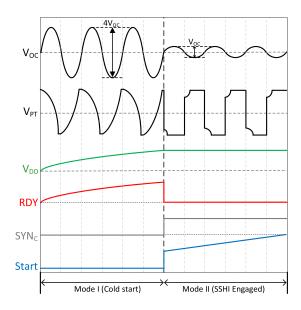

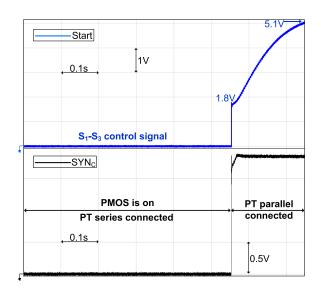

The system signals of  $V_{OC}$ ,  $V_{PT}$ ,  $V_{DD}$ , RDY,  $SYN_C$ , and Start are shown in Fig. 5. In mode I, the four input PTs are connected in series, resulting in  $4 \times V_{OC}$ , where  $V_{OC}$  is the

Fig. 6. RDY signal generation from the LDO.

open circuit voltage of one PT. The  $V_{PT}$  waveform shows no PT voltage flipping during this period since the circuit operates as an FBR. The power supply  $V_{DD}$  is building up, and RDY follows  $V_{DD}$  during this period. When the  $V_{DD}$  is ready, the RDY turns to low, resulting in a rising edge signal for  $SYN_C$  to control the PT switching block. After the level shifters, the  $SYN_C$  is levelly shifted to a high level, namely Start, to drive the switches directly. The Start signal is kept low during the cold state and changes to the highest voltage to fully turn ON the seriesconnected PT switches. Then, it turns OFF the parallel-connected PT switches. So, the PT connection changes from mode I to mode II. Then, input effective  $V_{OC}$  becomes  $1\times$ . Afterward, the charge-up block and SSHI rectifier will start working.

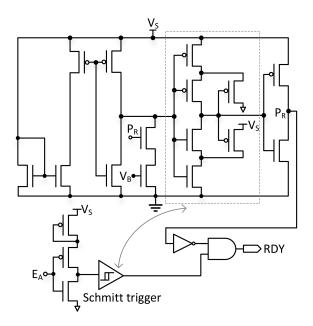

#### B. RDY Signal Generation From LDO

The RDY is used to switch the supply of the bandgap inside the LDO to achieve stable operation and low power for the LDO. Meanwhile, this design also considers it the cold-state indicator. The RDY generation is presented in Fig. 6. The  $E_A$  is generated by comparing the output voltage with a reference voltage as introduced in [34]. It has a high voltage equal to  $V_S - V_{GS}$ , and  $P_R$  is low during the cold-state. Therefore, RDY equals  $V_{DD}$  during the unconscious state. When the output voltage  $V_S$  reaches the required power supply voltage  $V_{DD}$ , the  $E_A$  changes from high to low, and  $P_R$  varies from low to high. Therefore, RDY changes to low, indicating that the cold state has been finished. The Schmitt trigger is used to avoid ringing response during the transition, as shown in Fig. 6.

# C. Charge-Up Block

When the connection of the PTs is changed from series to parallels after the cold state, the  $V_{PT}$  will drop by  $4\times$ . Therefore, the charge-up block is used to charge the dropped  $V_{PT}$  close to

Fig. 7. Charge-up block and associated signals.

Fig. 8. Switch control signal generation for the charge-up block.

the threshold voltage to start the SSHI rectifier normally. The charge-up block is shown in Fig. 7. Considering two flipping directions, there are two group switches,  $S_a$  and  $S_b$ . When the connection changes, for the first flipping cycle, if  $V_{PT}$  needs to flip from negative to positive,  $V_P$  will be connected to  $V_{DD}$ while  $V_N$  will be connected to the ground  $V_{SS}$ . Therefore,  $S_a$ is turned ON and vice versa. The upper switch comprises an inverter and a PMOS, while the lower switch is a NMOS. On the right, the corresponding waveform of  $I_P$ ,  $V_{PT}$ , and  $S_a$  are presented. Before the cold-state is ended, the system operates as an FBR and a lot of energy is wasted during  $V_{PT}$  flipping, as shown in the right black blocks. When the cold-state is ended, the flipping starts at the zero-crossing moment of  $I_P$ , and the charge-up block works in the first flipping cycle. It helps  $V_{PT}$ charge to the threshold voltage by connecting to  $V_{DD}$ . Then, the system would operate as an SSHI rectifier, and the wasted energy is reduced thanks to the inductor for PT voltage flipping.

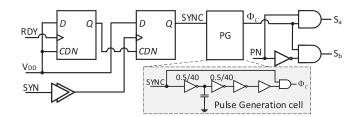

The control signals generation of the charge-up block is shown in Fig. 8. It includes some digital logic gates and a pulse generation block. Because the charge time is only several tens  $\mu$ s. When the  $V_{DD}$  is built up to a preset voltage, the RDY from the LDO will generate a falling edge, which indicates that the cold state is ended. However, the PT connection would not change instantly. When the first PT flipping comes after the cold state ends, the PT connection will change from series to parallels. At the flipping moment, the SYN signal from the comparator of the active diode will generate a rising edge to start the charge-up block. Then, through the pulse generation block in Fig. 8, either  $S_a$  or  $S_b$  is created for the switching control in Fig. 7. The PN is used to indicate the flipping direction. When the  $V_{PT}$  flips from negative to positive, the PN is high, and  $S_a$  is created and vice versa. The details of PN generation are given in the following subsection.

Fig. 9. Implementations of the SSHI rectifier (a) and the corresponding control signals for the switches in the SSHI rectifier (b).

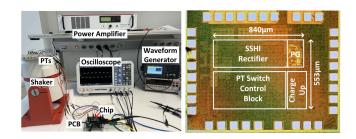

Fig. 10. Measurement setup and chip micrograph.

#### D. Synchronized Switch Harvesting on Inductor Rectifier

After the charge-up, the  $V_{PT}$  can build up to the threshold voltage, and the system starts to harvest the energy. The system would operate as an SSHI rectifier. Therefore, for the second flipping time, the PT voltage will be flipped by the SSHI rectifier. The proposed SSHI rectifier is shown in Fig. 9(a). There are four paralleled PTs as the input with the same intrinsic capacitor,  $C_P$ , and resonant frequency,  $f_P$ . Since the 4 PTs are clipped on the same substrate, they have the same vibrating frequency. Therefore, they will share one standard SSHI rectifier at the same time. When it is time to flip the PT voltage, the switch controlled by  $S_L$  will be turned ON. The PN, indicating the flipping direction of PT voltage, is obtained by comparing the voltage of  $V_P$  and  $V_N$  and triggered by the rising edge of  $SYN_O$ . The  $SYN_O$  is the effective synchronized signal from SYN, as shown on the right. It is generated after the charge-up block is ended. The switch control of  $S_L$  is also presented on the right where  $C_D$ ,  $C_{D1}$ , and  $C_{D2}$  are the adjustable capacitor which can be tuned according to the required period in each cell.

#### IV. MEASUREMENT RESULTS

#### A. Measurement Setup and Die Micrograph

The experimental setup is shown in Fig. 10. The inputs are four commercial PTs (S234-H5FR-1803XB) with resonant frequency 150 Hz and intrinsic capacitance 45 nF. The chip was fabricated in a 180-nm BCD process, and the die micrograph is shown on the right of Fig. 10 with an active area of  $0.47 \, \mathrm{mm}^2$ .

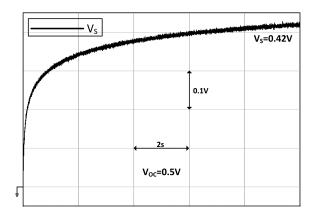

Fig. 11. Rectified output voltage of a conventional startup circuit.

The active area is dominated by four main blocks: An SSHI rectifier, a pulse generation block, a PT switch control block, and a charge-up block.

# B. Cold-Startup Verification

Fig. 11 shows the rectified output voltage of a typical cold-start circuit working as an FBR. The input open circuit voltage is around 0.5 V. The result shows that the maximum output voltage  $V_S$  of typical design is charged to 0.42 V, which is slightly lower than the open circuit voltage 0.5 V due to voltage drop across the diodes. Therefore, the maximum voltage supply generated from the typical cold-start circuit can only go to 0.42 V, which is too low to start the whole system.

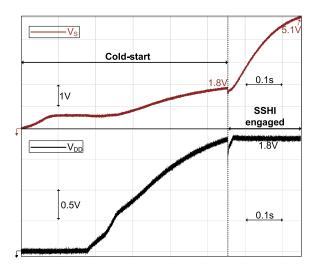

# C. Power Supply Building up and Charge-Up Moment

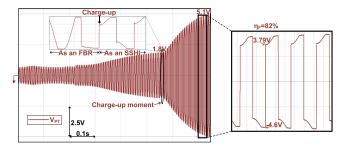

Fig. 12 shows the proposed bias-flip rectifier's output voltage and built-up power supply voltage. The input open circuit voltage amplitude is around  $V_{OC}=0.5\mathrm{V}$ . The top figure shows that the  $V_S$  can be built up from 0 to 1.8 V during the cold-start period. Correspondingly, the power supply  $V_{DD}$  is also built up from 0 to 1.8 V. When the  $V_{DD}$  attains 1.8 V, this indicates that the cold state (mode I) has been finished. Then the system changes to the SSHI-engaged phase (mode II), the  $V_{DD}$  keeps in 1.8 V while

Fig. 12. Measured rectified output power and built-up power supply of proposed bias-flip rectifier.

Fig. 13. Series connected control signal and  $SYN_C$  signal.

the  $V_S$  goes up to 5.1 V. When the system switches from mode I to mode II, the  $V_{DD}$  slightly drops because the charge-up block is engaged. A small amount of energy in the  $C_{DD}$  is used to charge the  $C_P$  since the effective output voltage amplitude from the 4 PTs decreases significantly due to the parallel connection, which is insufficient to sustain the SSHI operation after the SSHI rectification is engaged.

Fig. 13 top shows the switching control signal of the Start signal. It is the gate-driving signal of the PT switches. During the cold state, the Start signal is kept low so that the switches of  $S_1$ – $S_3$  are turned ON to connect the PTs in series. As a result, the effective open-circuit voltage  $V_{OC}$  can be roughly  $4\times$  higher than the open-circuit voltage of a single PT. After the cold-state, the  $V_{DD}$  keeps at around 1.8 V. Then, the Start signal starts to follow the output voltage level to fully turn OFF the switches,  $S_1$ – $S_3$ , so the PT connection is changed into a parallel connection. The bottom of Fig. 13 shows the  $SYN_C$  signal, which is used to generate the top Start signal as indicated in Fig. 4.

Fig. 14. Measured PT voltage of the proposed rectifier.

Fig. 15. Measured output power versus the output voltage of the proposed rectifier.

## D. Performance Analysis of the Proposed Design

Fig. 14 shows the waveform of PT voltage,  $V_{PT}$ . The zoomedin phase is shown on the top when the system changes from an FBR to an SSHI rectifier. After the cold state, the first bias-flip operation is triggered by the charge-up block; then, the SSHI rectifier performs the rest of the bias-flips autonomously. The PT voltage can be up to 5.1 V finally, which corresponds to the maximum rectified voltage in Fig. 12. The right zoomed-in figure shows the maximum flipping efficiency of the proposed circuit. The voltage is flipped from -4.6 to 3.79 V, indicating an 82% flipping efficiency.

Fig. 15 shows the output power of the proposed two-mode bias-flip rectifier and the conventional FBR versus the output voltage  $V_S$ . The conventional FBR rectifier has only 1.67  $\mu$ W with only one PT. In contrast, the proposed bias-flip rectifier can output 78.9  $\mu$ W in mode II, indicating an up to 1180% power enhancement.

Table I shows the comparison table between the proposed work and the prior art. This design was fabricated in a 180-nm BCD process rather than discrete components verification. The input open circuit voltage  $(V_{OC})$  is low to 0.5 V. Thanks to the proposed two-mode bias-flip rectifier, the active method can overcome the cold state, and the ratio of  $V_{OC}/V_{DD}$  can be lowered to 0.27. Among these works, the proposed two-mode rectifier has the highest flipping efficiency (82%) and power enhancement (1180%).

|                              | TPE'19 [26] | TPE'21 [35] | TPE'21 [19] | TIE'22 [22] | TPE'22 [36] | TPE'22 [37] | This work |

|------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-----------|

| Technology (nm)              | 180         | N/R         | N/R         | N/R         | N/R         | N/R         | 180       |

| Technique                    | SSHI        | SSDCI       | SSHI        | SSHI        | FBR/VD      | SSHI        | SSHI      |

| PT Number                    | 1           | 1           | 2           | 3           | 1           | 4           | 4         |

| $C_P$ (nF)                   | 4.5         | 100         | 41          | 100         | N/R         | 170*        | 45        |

| Frequency (Hz)               | 219         | 22          | 19          | 30*         | 153         | 77.5        | 150       |

| Inductor                     | Yes         | Yes         | Yes         | Yes         | No          | Yes         | Yes       |

| $V_{OC}$ (V)                 | 2/4.2       | N/R         | 5.8/5.2     | 5.8         | 0.4-15      | 3.9-5.8     | 0.5       |

| Chip Area (mm <sup>2</sup> ) | 0.2         | Discrete    | Discrete    | Discrete    | Discrete    | Discrete    | 0.47      |

| Flipping Efficiency          | 30%*        | No          | 50%*        | 52.8%       | No          | 66%*        | 82%(Max)  |

| Cold Startup?                | Yes         | Yes         | N/R         | Yes         | Yes         | N/R         | Yes       |

| Startup Technique            | Passive     | Passive     | Passive     | Passive     | Passive     | N/R         | Active    |

| System Mode                  | 2           | 2           | 1           | 1           | 2           | 1           | 2         |

| $V_{OC}/V_{DD}$              | 2.8         | N/R         | N/R         | N/R         | N/R         | N/R         | 0.27      |

| $P_{IC}/P_{FBR}$             | N/R         | 300%        | 370%        | 485%        | 100%        | 322%        | 1180%     |

TABLE I

PERFORMANCE COMPARISON WITH PREVIOUS WORK

#### V. CONCLUSION

This article proposes a two-mode bias-flip rectifier utilizing multiple PTs as inputs to address the cold startup issue caused by low input open circuit voltage. When the system starts from a cold state, the 4 PTs are connected in series to generate a fourfold increase in effective open circuit voltage, referred to as Mode I. During this mode, a  $1.8~{\rm V}~V_{DD}$  is established with the aid of the series-connected PTs. Once the cold state concludes, the circuit automatically reconfigures from series to parallel, transitioning to Mode II, and SSHI rectifier begins to operate to extract more power. Measurement results indicate that the proposed circuit successfully builds a  $1.8~{\rm V}~V_{DD}$  power supply with only a  $0.5~{\rm V}$  input open circuit voltage. This demonstrates that the proposed circuit can reduce the required input open circuit voltage by approximately  $3.6\times$ .

## REFERENCES

- D. Khan et al., "A high-efficient wireless power receiver for hybrid energy-harvesting sources," *IEEE Trans. Power Electron.*, vol. 36, no. 10, pp. 11148–11162, Oct. 2021.

- [2] X. Li and Y. Sun, "An SSHI rectifier for triboelectric energy harvesting," *IEEE Trans. Power Electron.*, vol. 35, no. 4, pp. 3663–3678, Apr. 2020.

- [3] W. Peng and S. Du, "The advances in conversion techniques in triboelectric energy harvesting: A review," *IEEE Trans. Circuits Syst. I: Reg. Papers*, vol. 70, no. 7, pp. 3049–3062, Jul. 2023.

- [4] M. Pathak and R. Kumar, "Synchronous pre-biasing of triboelectric nanogenerator for enhanced energy extraction," *IEEE Trans. Power Electron.*, vol. 37, no. 10, pp. 11552–11566, Oct. 2022.

- [5] I. Mandourarakis, V. Gogolou, E. Koutroulis, and S. Siskos, "Integrated maximum power point tracking system for photovoltaic energy harvesting applications," *IEEE Trans. Power Electron.*, vol. 37, no. 8, pp. 9865–9875, Aug. 2022.

- [6] X. Wang, H. Xia, Y. Xia, Y. Ye, G. Shi, and X. Chai, "Energy harvesting and acceleration measuring based on time-division multiplexing operation of a single piezoelectric transducer," *IEEE Trans. Power Electron.*, vol. 38, no. 5, pp. 5644–5648, May 2023.

- [7] X. Yue and S. Du, "A synchronized switch harvesting rectifier with reusable storage capacitors for piezoelectric energy harvesting," *IEEE J. Solid-State Circuits*, vol. 58, no. 9, pp. 2597–2606, Sep. 2023.

- [8] Z. Chen, M.-K. Law, P.-I. Mak, W.-H. Ki, and R. P. Martins, "Fully integrated inductor-less flipping-capacitor rectifier for piezoelectric energy harvesting," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3168–3180, Dec. 2017.

- [9] D. A. Sanchez, J. Leicht, F. Hagedorn, E. Jodka, E. Fazel, and Y. Manoli, "A parallel-SSHI rectifier for piezoelectric energy harvesting of periodic and shock excitations," *IEEE J. Solid-State Circuits*, vol. 51, no. 12, pp. 2867–2879, Dec. 2016.

- [10] A. Shareef, W. L. Goh, S. Narasimalu, and Y. Gao, "A rectifier-less AC–DC interface circuit for ambient energy harvesting from low-voltage piezoelectric transducer array," *IEEE Trans. Power Electron.*, vol. 34, no. 2, pp. 1446–1457, Feb. 2019.

- [11] C.-W. Chen, W. Z. Pranoto, H.-S. Chen, and W.-J. Wu, "A 0.25-m HV-CMOS synchronous inversion and charge extraction interface circuit with a single inductor for piezoelectric energy harvesting," *IEEE Trans. Power Electron.*, vol. 38, no. 12, pp. 15707–15718, Dec. 2023.

- [12] M. Edla, Y. Y. Lim, D. Mikio, and R. V. Padilla, "A single-stage rectifier-less boost converter circuit for piezoelectric energy harvesting systems," *IEEE Trans. Energy Convers.*, vol. 37, no. 1, pp. 505–514, Mar. 2022.

- [13] D. A. Sanchez, J. Leicht, E. Jodka, E. Fazel, and Y. Manoli, "21.2 a 4µW-to-1mW parallel-SSHI rectifier for piezoelectric energy harvesting of periodic and shock excitations with inductor sharing, cold start-up and up to 681% power extraction improvement," in *Proc. IEEE Int. Solid-State Circuits Conf.*, 2016, pp. 366–367.

- [14] X. Yue and S. Du, "Performance optimization of SSHC rectifiers for piezoelectric energy harvesting," *IEEE Trans. Circuits Syst. II: Exp. Briefs*, vol. 70, no. 4, pp. 1560–1564, Apr. 2023.

- [15] S. Du, Y. Jia, C. Zhao, G. A. J. Amaratunga, and A. A. Seshia, "A fully integrated split-electrode SSHC rectifier for piezoelectric energy harvesting," *IEEE J. Solid-State Circuits*, vol. 54, no. 6, pp. 1733–1743, Jun. 2019.

- [16] A. Morel et al., "A shock-optimized SECE integrated circuit," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3420–3433, Dec. 2018.

- [17] E. M. Dalin and S. M. R. Hasan, "A low phase-lag self-powered SECE interface circuit for pressure-type piezoelectric energy-harvesting compatible with COTS pressure sensors," *IEEE Trans. Very Large Scale Integration (VLSI) Syst.*, vol. 31, no. 10, pp. 1634–1638, Oct. 2023.

- [18] S. Du, Y. Jia, C. D. Do, and A. A. Seshia, "An efficient SSHI interface with increased input range for piezoelectric energy harvesting under variable conditions," *IEEE J. Solid-State Circuits*, vol. 51, no. 11, pp. 2729–2742, Nov. 2016.

<sup>\*:</sup> Estimated value. N/R: Not reported.

- [19] Z. Chen, Y. Xia, G. Shi, X. Wang, H. Xia, and Y. Ye, "Self-powered multi-input serial SSHI interface circuit with arbitrary phase difference for piezoelectric energy harvesting," *IEEE Trans. Power Electron.*, vol. 36, no. 8, pp. 9183–9192, Aug. 2021.

- [20] L. Wu, X.-D. Do, S.-G. Lee, and D. S. Ha, "A self-powered and optimal SSHI circuit integrated with an active rectifier for piezoelectric energy harvesting," *IEEE Trans. Circuits Syst. I: Reg. Papers*, vol. 64, no. 3, pp. 537–549, Mar. 2017.

- [21] S. Lu and F. Boussaid, "A highly efficient P-SSHI rectifier for piezoelectric energy harvesting," *IEEE Trans. Power Electron.*, vol. 30, no. 10, pp. 5364–5369. Oct. 2015.

- pp. 5364–5369, Oct. 2015.

[22] Z. Long, P. Li, J. Chen, H. S.-H. Chung, and Z. Yang, "Self-powered single-inductor rectifier-less SSHI array interface with the MPPT technique for piezoelectric energy harvesting," *IEEE Trans. Ind. Electron.*, vol. 69, no. 10, pp. 10172–10181, Oct. 2022.

- [23] Y. Cai and Y. Manoli, "A piezoelectric energy harvester interface circuit with adaptive conjugate impedance matching, self-startup and 71% broader bandwidth," in *Proc. 43rd IEEE Eur. Solid State Circuits Conf.*, 2017, pp. 119–122.

- [24] Y. Gao, D. I. Made, S.-J. Cheng, M. Je, and C.-H. Heng, "An energy-autonomous piezoelectric energy harvester interface circuit with 0.3v startup voltage," in *Proc. IEEE Asian Solid-State Circuits Conf.*, 2013, pp. 445–448.

- [25] T. Martinez, G. Pillonnet, and F. Costa, "A 15-mV inductor-less start-up converter using a piezoelectric transformer for energy harvesting applications," *IEEE Trans. Power Electron.*, vol. 33, no. 3, pp. 2241–2253, Mar. 2018.

- [26] S. Du, G. A. J. Amaratunga, and A. A. Seshia, "A cold-startup SSHI rectifier for piezoelectric energy harvesters with increased open-circuit voltage," *IEEE Trans. Power Electron.*, vol. 34, no. 1, pp. 263–274, Jan. 2019.

- [27] X. Yue and S. Du, "A 2-mode reconfigurable SSHI rectifier with 3.2X lower cold-start requirement for piezoelectric energy harvesting," in *Proc.* 29th IEEE Int. Conf. Electron., Circuits Syst., 2022, pp. 1–4.

- [28] Z. J. Chew and M. Zhu, "Adaptive self-configurable rectifier for extended operating range of piezoelectric energy harvesting," *IEEE Trans. Ind. Electron.*, vol. 67, no. 4, pp. 3267–3276, Apr. 2020.

- [29] X. Wang, L. Qian, X. Wang, G. Shi, H. Xia, and Z. Zhu, "A self-powered BF and S-SSHI hybrid rectifier for multi-PZTs energy harvesting," *IEEE Trans. Power Electron.*, vol. 39, no. 10, pp. 13828–13841, Oct. 2024.

- [30] Z. Chen, Y. Xia, G. Shi, X. Wang, H. Xia, and L. Qian, "Self-powered collaborative energy harvesting interface circuit for stacked multiple piezoelectric elements," *IEEE Trans. Power Electron.*, vol. 39, no. 12, pp. 16814–16825, Dec. 2024.

- [31] J. Xiong, Y. Xia, Z. Chen, H. Xia, and C. Xiao, "Self-powered multi-input hybrid rectifier with arbitrary phase difference and low start-up voltage for piezoelectric energy harvesting," *IEEE Trans. Power Electron.*, vol. 40, no. 3, pp. 4461–4472, Mar. 2025.

- [32] S. Du, Y. Jia, C. Zhao, G. A. J. Amaratunga, and A. A. Seshia, "A nail-size piezoelectric energy harvesting system integrating a MEMS transducer and a CMOS SSHI circuit," *IEEE Sensors J.*, vol. 20, no. 1, pp. 277–285, Jan 2020

- [33] X. Yue, Y. Zou, Z. Chen, J. Liang, and S. Du, "A reconfigurable cold-startup SSHI rectifier with 4x lower input amplitude requirement for piezoelectric energy harvesting," in *Proc. IEEE Int. Symp. Circuits Syst.*, 2022, pp. 649–653.

- [34] Y. Zou, X. Yue, and S. Du, "A nanopower 95.6% efficiency voltage regulator with adaptive supply-switching for energy harvesting applications," in *Proc. IEEE Int. Symp. Circuits Syst.*, 2022, pp. 3557–3561.

- [35] Z. Long et al., "Self-powered SSDCI array interface for multiple piezoelectric energy harvesters," *IEEE Trans. Power Electron.*, vol. 36, no. 8, pp. 9093–9104, Aug. 2021.

- [36] Z. J. Chew, Y. Kuang, and M. Zhu, "Self-powered and self-configurable active rectifier using low voltage controller for wide output range energy harvesters," *IEEE Trans. Power Electron.*, vol. 37, no. 9, pp. 11285–11295, Sep. 2022.

- [37] H. Xia et al., "Self-powered dual-inductor MI-PSSHI-VDR interface circuit for multi-PZTs energy harvesting," *IEEE Trans. Power Electron.*, vol. 37, no. 4, pp. 3753–3762, Apr. 2022.

**Xinling Yue** (Graduate Student Member, IEEE) is currently working toward the Ph.D. degree in microelectronics with the Electronic Instrumentation Laboratory, Delft University of Technology, Delft, The Netherlands.

In December 2020, she joined the Electronic Instrumentation Laboratory, Delft University of Technology. Her current research interests include energy-efficient power management integrated circuits and systems, which include energy harvesting, rectifiers, dc/dc converters, and maximum power point tracking

techniques. Ms. Yue was the recipient of the Best Student Paper Award at the 2022 IEEE International Conference on Electronics Circuits and Systems (ICECS), the Student Travel Grant Awards at the 2022 IEEE International Symposium on Circuits and Systems (ISCAS), the 2023 ISSCC, and the 2023–2024 SSCS predoctoral achievement award.

Sijun Du (Senior Member, IEEE) received the B.Eng. (Hons.) degree in electrical engineering from the University Pierre and Marie Curie (UPMC), Paris, France, in 2011, the M.Sc. (distinction) degree in electrical and electronic engineering from Imperial College, London, U.K., in 2012, and the Ph.D. degree in electrical engineering from the University of Cambridge, Cambridge, U.K., in 2018.

He started his Ph.D. research in October 2014. He was with the Laboratoire d'Informatique de Paris 6 (LIP6), University Pierre and Marie Curie, Paris,

France, and then was an IC engineer, Shanghai, China, between 2012 and 2014. He was a summer engineer intern at Qualcomm Technology, Inc., San Diego, CA, USA, in 2016. He was a postdoctoral researcher at the Department of Electrical Engineering and Computer Sciences (EECS), University of California, Berkeley, CA, USA, from 2018 to 2020. In 2020, he joined the Department of Microelectronics, Delft University of Technology (TU Delft), Delft, The Netherlands, as an Assistant Professor. His current research interests include energy-efficient integrated circuits and systems, including power management integrated circuits (PMIC), energy harvesting, wireless power transfer, and DC/DC converters used in Internet-of-Things (IoT) wireless sensors, wearable electronics, and biomedical devices.

Dr. Du was the recipient of the Dutch Research Council (NWO) Talent Program VENI Grant in 2021 and the co-recipient of the Best Student Paper Award in IEEE ICECS 2022. He is IEEE ICECS Sub-Committee Chair in 2022 and 2024, an IEEE ISSCC Student Research Preview (SRP) Committee Member since 2023, and IEEE ISCAS Sub-Committee Chair in 2025.