# A Highly-Scalable Thermal-Diffusivity-Based Temperature Sensor

J. A. Angevare

## A Highly-Scalable Thermal-Diffusivity-Based Temperature Sensor

# IN 160 nm CMOS FOR THERMAL MONITORING APPLICATIONS

by

### J. A. Angevare

in partial fulfillment of the requirements for the degree of

Master of Science in Microelectronics

at the Electronic Instrumentation Laboratory,

Department of Electrical Engineering,

Delft University of Technology,

to be defended publicly on Thursday December 17, 2013 at 3:00 PM.

| Supervisor:       | Prof. dr. K. A. A. Makinwa   |          |

|-------------------|------------------------------|----------|

| Thesis committee: | Prof. dr. K. A. A. Makinwa,  | TU Delft |

|                   | Dr. F. Sebastiano,           | TU Delft |

|                   | Prof. dr. Ing. L. de Vreede, | TU Delft |

This thesis is confidential and cannot be made public until December 31, 2020.

An electronic version of this thesis is available at http://repository.tudelft.nl/.

## **ABSTRACT**

A highly digital temperature sensor, based on the thermal diffusivity of silicon, for thermal management applications has been reported. Recently, Thermal-Diffusivity based temperature sensors have undergone a radical change from an analog-based readout architecture to a more digital VCO-based one. However the more digital approach led to significantly worse performance, i.e. accuracy and resolution. The proposed sensor uses the same digital approach but achieves much better performance.

The sensor achieves an inaccuracy of  $\pm 2.9$  °C (3 $\sigma$ ) from -35 °C to 125 °C with no trimming and  $\pm 1.2$  °C (3 $\sigma$ ) after a single-point trim, while achieving a resolution of 0.47 °C (rms) at 1 kSa/s. Its compact area (2800  $\mu$ m<sup>2</sup>) is enabled by the adoption of a VCO-based phase-domain ADC. Since 53% of the sensor area is occupied by digital circuitry, the sensor can be easily ported to more advanced CMOS technologies with further area reduction, which makes it well suited for thermal monitoring in microprocessors and other systems-on-chip.

### **ACKNOWLEDGMENTS**

First and foremost I would like to thank Professor Kofi Makinwa for all opportunities, feedback and support given. He is the mastermind behind most ideas and a visionary in executing them. He took me along to San Fransisco and Xiamen, and showed me a good time, not only in San Francisco and Xiamen, but also in Delft. I cannot but have great respect for his ability to come up with new ideas and his passion for his work.

The next person to thank is Uğur Sönmez, my daily supervisor. Every time I've had a problem he came by and helped me. Moreover, I don't think there is a single problem he cannot solve. Also a heart felt thanks to Fabio Sebastiano, who will always make time to help anyone. He has been a great support in reviewing my layout, and has been responsible for writing most of the published conference paper.

I would also like to thank the group at the Electronic Instrumentation Laboratory. I don't think it is ever really apparent what work goes on in the background, nor how important it is for us to be able to do what we do. That's why I want to put in a special thanks to the staff, for helping me with my measurement setup, for maintaining the laboratory equipment and for helping me navigate through all the forms of bureaucracy.

Also a special thanks to the reviewers; Constantino, Junfeng, Lorenzo, Luke, Sining, Uğur, Vincent and Yikun. Also an extra special thanks for Junfeng for being my very thoughtful guide and translator while in China.

Last but not least; a special thanks to my family for their silent support and unwavering trust in me. Without you this entire episode of my life would never even have been possible!

J. A. Angevare Delft, December 2015

## **CONTENTS**

| Lis | t of F                    | gures x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | i                               |

|-----|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 1   | 1.1<br>1.2                | Inction       Intermal Management       Incomparison         CMOS compatible temperature sensors       Incomparison       Incomparison         1.2.1 Bandgap       Incomparison       Incomparison         1.2.2 Resistor       Incomparison       Incomparison         1.2.3 Inverter Delay       Incomparison       Incomparison         1.2.4 Leakage       Incomparison       Incomparison         1.2.5 Thermal Diffusivity       Incomparison       Incomparison         1.2.6 Accuracy vs. Size       Incomparison       Incomparison         Outline       Incomparison       Incomparison | 1<br>2<br>3<br>4<br>4<br>5      |

| 2   | Phas<br>2.1<br>2.2<br>2.3 | -Domain ΣΔ-Modulator       9         ETF       9         Ideal Phase-Domain ΣΔ-Modulator       9         VCO based Phase-Domain ΣΔ-Modulator       12                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                               |

| 3   |                           | In Design       15         ETF       15         3.1.1 Heater       16         3.1.2 Square ETF       17         3.1.3 Silicide       20         CCO and level-shifters       21         Gm stage and bias circuit       22         Phase-Calibration       25         Counter       26         Heater-drive and top-level       30                                                                                                                                                                                                                                                                 | 5<br>7<br>0<br>1<br>2<br>7<br>8 |

| 4   | Meas<br>4.1<br>4.2<br>4.3 | Irements       35         Measurement Setup.       35         Master Curve       35         Results       38         4.3.1 ETF Power       39         4.3.2 CCO tuning frequency       41         4.3.3 Phase Noise and Stability       42         4.3.4 Accuracy       45         4.3.5 Phase-calibration       49         4.3.6 Batch-Batch measurements       51                                                                                                                                                                                                                                | 5<br>7<br>8<br>9<br>1<br>3<br>5 |

| 5   |                           | usion Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |

| X |                             | Contents |

|---|-----------------------------|----------|

|   |                             |          |

| A | Discrete-time noise         | 55       |

|   | A.1 Discrete-time artifacts | 55       |

61

Bibliography

## LIST OF FIGURES

| 1.1  | Temperature sensing principle of BJT based temperature sensors                  | 3  |

|------|---------------------------------------------------------------------------------|----|

| 1.2  | Wien Bridge                                                                     | 4  |

| 1.3  | Pseudo Differential Ring Oscillator                                             | 4  |

| 1.4  | Temperature sensing principle of Thermal-Diffusivity based temperature sensors. | 5  |

| 1.5  | Accuracy vs. Area trend                                                         | 6  |

| 2.1  | Ideal Phase-Domain Sigma-Delta-Modulator Readout.                               | 10 |

| 2.2  | Typical ETF phase response                                                      | 10 |

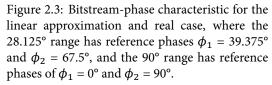

| 2.3  | Cosine non-linearity.                                                           | 11 |

| 2.4  | Cosine non-linearity error                                                      | 11 |

| 2.5  | Analog Phase-Domain Sigma-Delta-Modulator Readout.                              | 12 |

| 2.6  | VCO-Based Phase-Domain Sigma-Delta-Modulator Readout                            | 12 |

| 3.1  | ETF cross-section                                                               | 15 |

| 3.2  | Heater resistor with switches.                                                  | 16 |

| 3.3  | MOSFET Heater                                                                   | 16 |

| 3.4  | Heater efficiency.                                                              | 17 |

| 3.5  | Layout comparison of the three different heaters                                | 17 |

| 3.6  | ETF7 with Dog-Bone heater                                                       | 18 |

| 3.7  | ETF7 square with Dog-Bone heater                                                | 18 |

| 3.8  | ETF3 with NMOS heater and large hot-junction.                                   | 18 |

| 3.9  | ETF7 square with NMOS heater.                                                   | 19 |

| 3.10 | ETF7 square with NMOS heater and large hot-junction                             | 19 |

| 3.11 | Zoom-in of the small silicide hot-junction                                      | 20 |

| 3.12 | Zoom-in of the large silicide hot-junction.                                     | 20 |

| 3.13 | CCO plus tripler                                                                | 20 |

| 3.14 | CCO plus level-shifter                                                          | 20 |

| 3.15 | Typical output waveform of the ring-oscillator.                                 | 22 |

| 3.16 | Levelshifter                                                                    | 22 |

| 3.17 | Duty cycle histogram at 125°C, low input voltage                                | 23 |

| 3.18 | Duty cycle at 125°C, high input voltage                                         | 23 |

| 3.19 | Duty cycle histogram at 27°C, low input voltage.                                | 23 |

|      | Duty cycle at 27°C, high input voltage                                          | 23 |

| 3.21 | Duty cycle histogram at -55°C, low input voltage.                               | 23 |

| 3.22 | Duty cycle at -55°C, high input voltage                                         | 23 |

|      | Gm-stage from the prior art                                                     | 24 |

|      | Gm-stage of current design.                                                     | 24 |

|      | Bias current of constant-Gm-biasing over temperature                            | 25 |

|      | Gm-stage input referred noise                                                   | 25 |

|      | Gm-stage gain                                                                   | 25 |

xii List of Figures

|      | Gm-stage phase response                                                              |       |

|------|--------------------------------------------------------------------------------------|-------|

| 3.29 | Gm gain power-supply sensitivity, at 1.1719 MHz                                      | 25    |

|      | Gm phase response power-supply sensitivity, at 1.1719 MHz                            | 25    |

| 3.31 | Gm + CCO gain histogram at 125°C                                                     | 26    |

|      | Gm + CCO gain histogram at 27°C                                                      | 26    |

| 3.33 | Gm + CCO gain histogram at -55°C                                                     | 26    |

| 3.34 | Trimming histogram at 125°C.                                                         | 26    |

| 3.35 | Trimming histogram at 27°C                                                           | 26    |

| 3.36 | Trimming histogram at -55°C                                                          | 26    |

| 3.37 | Simplified phase-calibration diagram.                                                | 27    |

| 3.38 | Phase-calibration schematic                                                          | 28    |

|      | Detailed phase-calibration diagram                                                   | 28    |

| 3.40 | Improved low-power counter                                                           | 28    |

| 3.41 | 2-Bit Gray-code up/down pre-scaler                                                   | 29    |

| 3.42 | 2-Bit binary up/down counter                                                         | 29    |

|      | Pulse generation circuit.                                                            | 29    |

|      | 4-Bit ripple up/down counter                                                         | 30    |

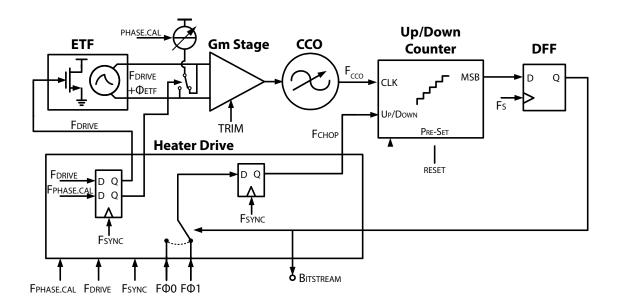

|      | Simplified block-diagram of the temperature sensor.                                  | 31    |

|      | Detailed block-diagram of the temperature sensor                                     | 32    |

|      | Pixel comparison of different temperature sensor designs                             | 33    |

|      |                                                                                      |       |

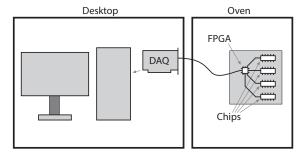

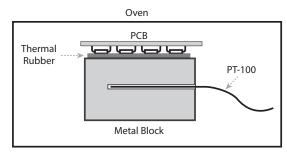

| 4.1  | Simplified schematic overview of the measurement setup                               | 35    |

| 4.2  | Simplified schematic of the thermal connections of the measurement setup             | 35    |

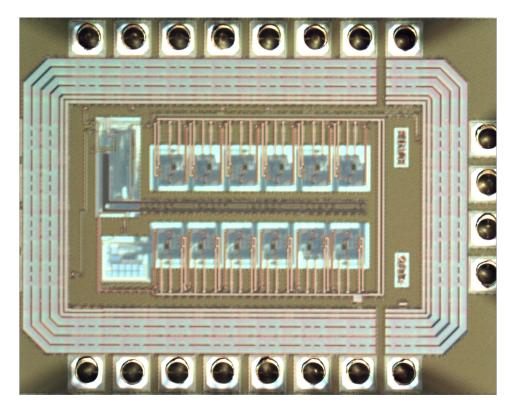

| 4.3  | Die-Graph of the FINCH tape-out                                                      | 36    |

| 4.4  | Graph of pixel with conventional counter and ETF6                                    | 37    |

| 4.5  | Graph of pixel with low-power counter and ETF7                                       | 37    |

| 4.6  | Graph of pixel with conventional counter and ETF7 with MOS heater                    | 37    |

| 4.7  | Graph of pixel with low-power counter and ETF with MOS heater                        | 37    |

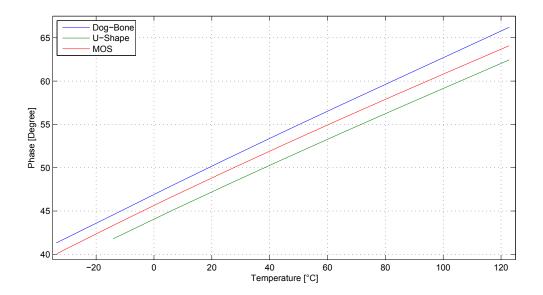

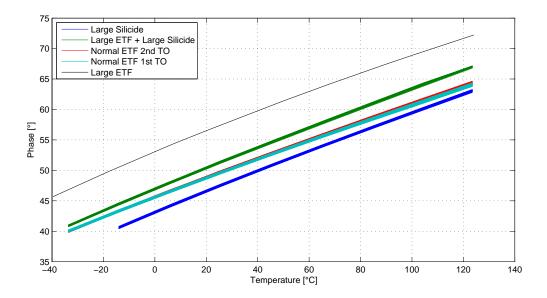

| 4.8  | Phase read-out plots of all three ETF types                                          |       |

| 4.9  | ETF characteristics approximation                                                    | 39    |

| 4.10 | Efficiency of resistive heaters                                                      | 39    |

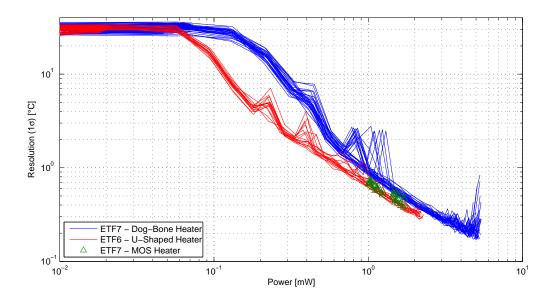

| 4.11 | Resolution over ETF heater power                                                     | 40    |

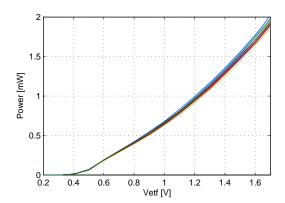

| 4.12 | ETF6 U-Shaped heater power over heater voltages                                      | 40    |

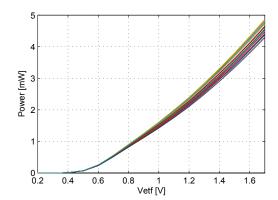

|      | ETF7 Dog-Bone heater power over heater voltages                                      | 40    |

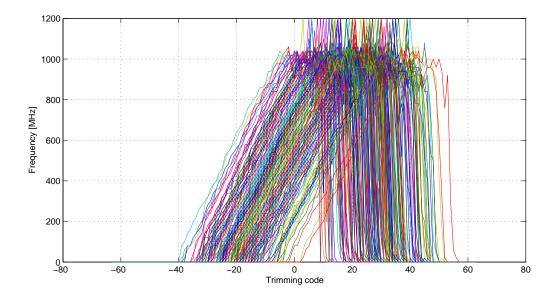

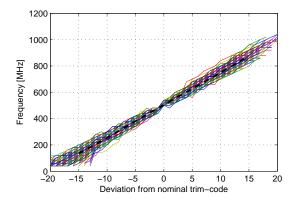

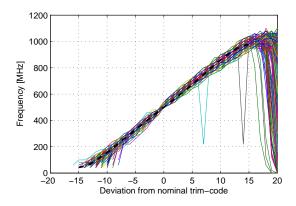

|      | CCO Frequency over trimming codes at 25 °C                                           | 41    |

| 4.15 | Frequency tuning curves at -35 °C                                                    | 42    |

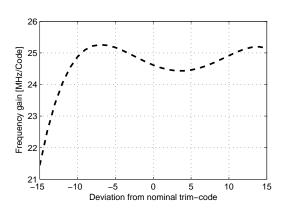

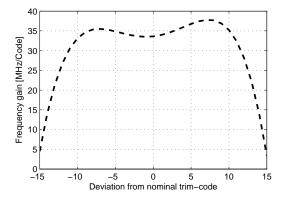

| 4.16 | Frequency tuning, master-curve fitted, gain at -35 °C                                | 42    |

| 4.17 | Frequency tuning curves at 25 °C                                                     | 42    |

| 4.18 | Frequency tuning, master-curve fitted, gain at 25 °C                                 | 42    |

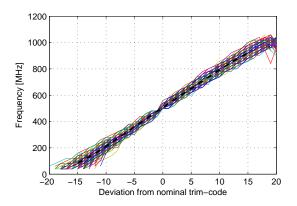

| 4.19 | Frequency tuning curves at 125 °C                                                    | 42    |

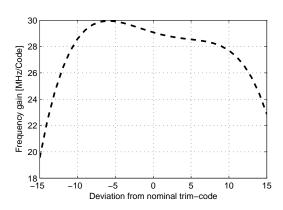

| 4.20 | Frequency tuning, master-curve fitted, gain at 125 °C                                | 42    |

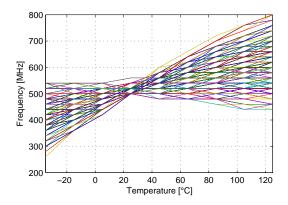

| 4.21 | VCO Temperature sensitivity, for VCO trimmed at 25 °C to 500 MHz                     | 43    |

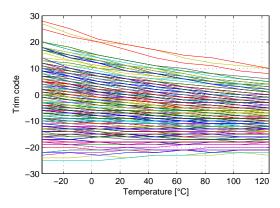

| 4.22 | Trimming codes for VCO's at different temperatures for VCO trimmed to 500 MH         | z. 43 |

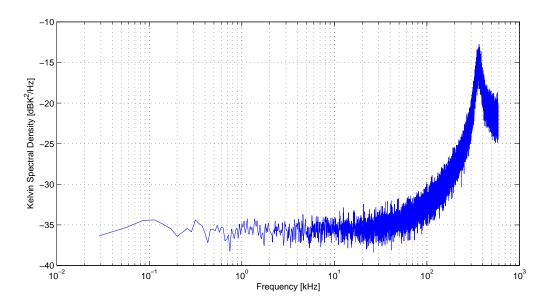

| 4.23 | FFT of the PD $\Sigma\Delta$ Ms bit-stream for 40 960 samples averaged over 25 FFT's | 44    |

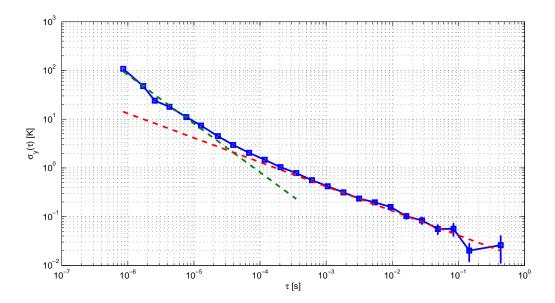

|      | Allan Deviation in Kelvins.                                                          | 44    |

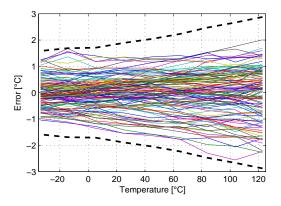

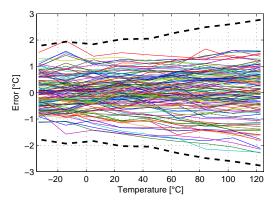

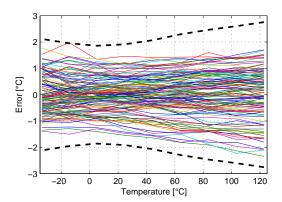

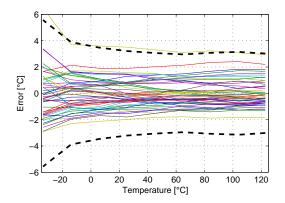

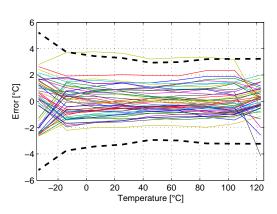

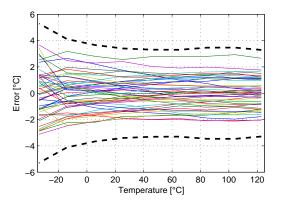

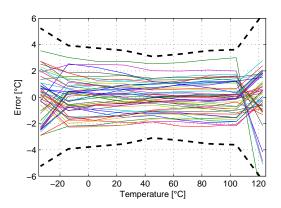

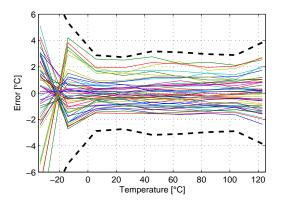

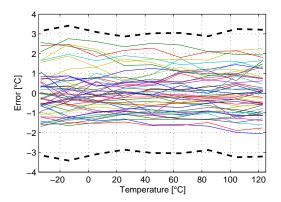

| 4.25 | Error plot of square ETF with MOSFET heater with Low-Power Counter                   | 45    |

List of Figures xiii

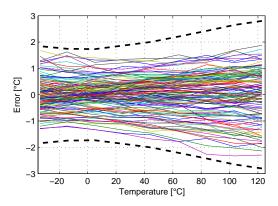

| 4.26       | Error plot of square ETF with MOSFET heater with Low-Power Counter with              |    |

|------------|--------------------------------------------------------------------------------------|----|

|            |                                                                                      | 45 |

| 4.27       |                                                                                      | 45 |

| 4.28       | Error plot of square ETF with MOSFET heater with conventional counter with           |    |

|            |                                                                                      | 45 |

| 4.29       |                                                                                      | 46 |

| 4.30       | Error plot of square ETF with Dog-Bone heater with Low-Power Counter with            |    |

|            |                                                                                      | 46 |

| 4.31       | Error plot of square ETF with Dog-Bone heater with conventional counter              | 46 |

| 4.32       | Error plot of square ETF with Dog-Bone heater with conventional counter with         |    |

|            | fine conversion                                                                      | 46 |

| 4.33       | Error plot of rotund ETF with U-Shaped heater with conventional counter              | 46 |

| 4.34       | Error plot of rotund ETF with U-Shaped heater with conventional counter with         |    |

|            |                                                                                      | 46 |

| 4.35       | Accuracy (3 $\sigma$ ) of ETF6 U-Shaped heater over heater voltages                  | 47 |

| 4.36       | Accuracy (3 $\sigma$ ) of ETF7 Dog-Bone heater over heater voltage                   | 47 |

| 4.37       | Accuracy $(3\sigma)$ of MOS heater over heater voltages                              | 47 |

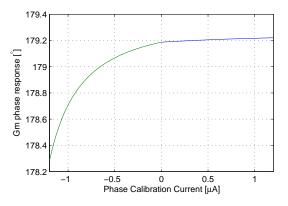

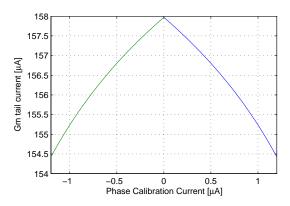

| 4.38       | Gm-stage phase delay at 1.1719 MHz over trimming current                             | 48 |

| 4.39       | Gm-stage phase delay at 1.1719 MHz over trimming current, with folded-cascode        |    |

|            | lacksquare                                                                           | 48 |

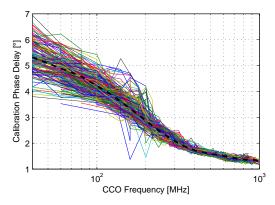

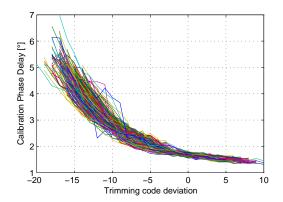

| 4.40       | Calibration delay over CCO trimmed frequency                                         | 48 |

|            |                                                                                      | 48 |

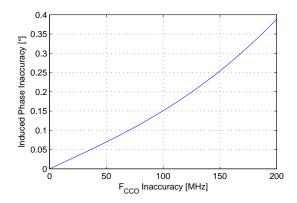

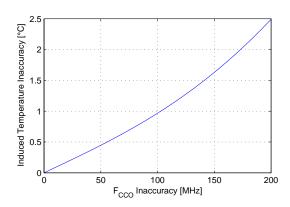

| 4.42       | Induced phase inaccuracy in readout due to inaccuracy in Fcco trimming               | 49 |

| 4.43       | Induced temperature inaccuracy in readout due to inaccuracy in Fcco                  | 49 |

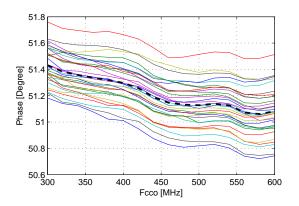

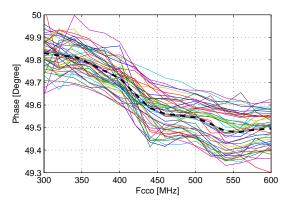

| 4.44       | Phases of ETF7 Dog-Bone heater for different Fcco frequencies.                       | 49 |

| 4.45       | Phases of ETF7 MOS heater for different Fcco frequencies                             | 49 |

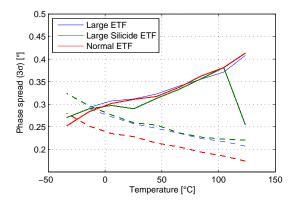

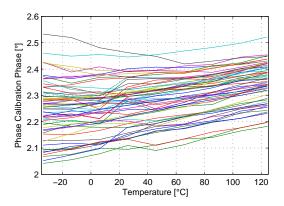

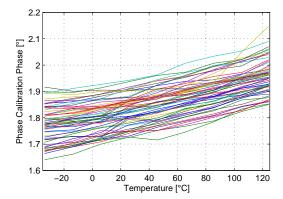

| 4.46       | Measured spread of phase calibration and normal measurement.                         | 50 |

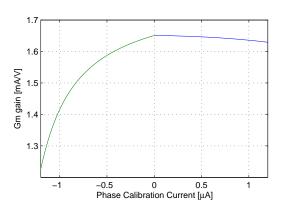

| 4.47       | Gm gain at 1.1719 MHz for different phase-calibration current driving strengths.     | 50 |

| 4.48       | Gm phase response at 1.1719 MHz for different phase-calibration current driv-        |    |

|            | ing strengths                                                                        | 50 |

| 4.49       | Simulated Gm tail current for different phase-calibration current driving strengths. | 50 |

| 4.50       | Phase-calibration for small phase-cal amplitude                                      | 50 |

| 4.51       | Phase-calibration for large phase-cal amplitude                                      | 50 |

| 4.52       | ETF master-curves comparison for 2nd TO                                              | 51 |

| 4.53       | Batch-batch accuracy comparison.                                                     | 52 |

| 5.1        | Improvement for trimming/Fcco dependency in readout                                  | 54 |

| 5.2        | Improvement for phase calibration current strength in readout.                       | 54 |

|            |                                                                                      |    |

| <b>A.1</b> | Simplified linear PD $\Sigma\Delta M$ noise model                                    | 57 |

1

## Introduction

The thermal monitoring of multi-core processors is becoming an increasingly hot topic [1]. With the ever shrinking dimensions of CMOS technologies more and more transistors fit in the same surface area. This has been the main force behind the dramatic reduction in the cost of logical functions. However the energy required to switch a digital gate has not reduced as dramatically as the gate dimensions, resulting in rapidly increasing energy densities, and hence die temperatures, of circuits realized in modern processes.

The result of such on-chip energy densities is that local islands of high temperature, i.e. hot-spots, may be created. Depending on the exact algorithm being executed, such hot-spots may occur in different parts of the chip. This problem has been further aggravated by the recent shift towards distributed processing (such as multi-core architectures).

When die temperatures become excessive, say beyond 75 °C, it may result in reliability issues. For instance, the mobility of charge carriers will decrease, resulting in longer delays. Even worse, at high temperatures MOS devices leak more, which in itself consumes power, resulting in further heating. Finally, since dopant diffusion is exponentially dependent on temperature, too much heat may damage or, at least, dramatically reduce the lifetime of a chip.

All of this adds up to the fact that thermal monitoring of high-performance digital circuitry is a necessity. The next section will explain the requirements of thermal monitoring systems and also the actions which can be taken to avert reliability issues or permanent damage due to overheating.

#### 1.1. THERMAL MANAGEMENT

In order to understand the requirements for thermal management it is necessary to first understand the actions which can be taken to prevent overheating. There are two groups of techniques: the first involves reducing heat production, while the second attempts to balance it. Under the first group fall stop-go policies as well as dynamic voltage and/or frequency scaling (DVFS) techniques. Stop-go policies simply aim to stop the execution of the circuitry that causes overheating, while DVFS techniques reduce circuit performance and so heat production. The second group of techniques, which balance heat-production, make use of the increasing parallelism in high performance digital circuitry by monitoring local heat production and intelligently scheduling the workload. Obviously the last group requires more digital circuitry and/or software but also has the highest performance. The trend in high performance digital

2 1. Introduction

circuits is towards continuous workload balancing, which in turn drives the need for better thermal monitoring.

Irrespective of how overheat prevention is done, there is a requirement to monitor local hot-spots. Since local hot-spots can rapidly increase the local die temperature (time constants are in the order of milliseconds) there is a need for multiple local temperature sensors with millisecond response times. Because many of these sensors are required, their area should be as small as possible. In short, in order to ensure that local die temperatures remain within a given range, quick, accurate and local sensors are required.

However, most integrated temperature sensors must be calibrated to counteract the effect of process spread. In thermal monitoring applications, the need to calibrate multiple sensors results in a significant increase in production cost. It would therefore be nice to have temperature sensors which are accurate enough "out of the box".

From the above, we can conclude that the ideal qualities of a temperature sensor for thermal monitoring are: small area, good untrimmed accuracy and conversion times in the order of (sub)milliseconds.

#### 1.2. CMOS COMPATIBLE TEMPERATURE SENSORS

For thermal monitoring applications, we need to actively monitor the temperature of the die itself. Therefore the temperature sensitive part of the sensor should be as close to, or rather be in the die. Furthermore, costs would be greatly reduced if the sensor could be made with standard CMOS technologies.

Four kinds of temperature sensors satisfy these conditions: bandgap sensors (made with either BJT's, MOSFET's or diodes), resistor-based sensors, (electrical) delay line elements or thermal diffusivity sensors. A quick review will show which of these is most suited for thermal monitoring applications.

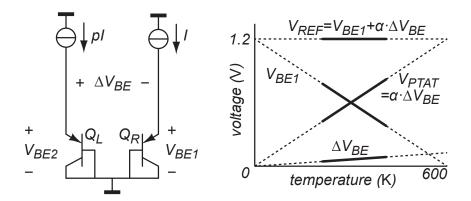

#### 1.2.1. BANDGAP

Traditionally, bandgap sensors are the most widely used and come in a variety of flavors. In [2] a PTAT (proportional to absolute temperature) voltage is digitized with respect to a reference voltage, made from a PTAT and CTAT (complementary to absolute temperature) voltage. In the following, any sensor using a PTAT or CTAT voltage created by either a BJT or MOS device will be referred to as a bandgap sensor. In some cases, external reference voltages may be used, e.g. as in [3].

BJT-based bandgap sensors are the most popular, with MOSFET-based sensors slowly gaining popularity, mainly because they require less headroom. Another factor contributing to this is the fact that modern CMOS processes usually do not provide well-optimized BJTs, but only provide so called parasitic PNPs. These devices make use of the same diffusions required to make a PMOS device: The base is made from the n-well, the emitter is made from the p+drain/source, and the collector is made from the p-type substrate, and so is tied to ground. Since the basic idea behind all bandgap sensors is roughly the same, we will only analyze the more common BJT flavor.

BJT based temperature sensors work by forcing a current through a set of BJT's generating a temperature dependent voltage. This voltage is CTAT by equation (1.1), the difference between

Figure 1.1: Temperature sensing principle of BJT based temperature sensors (remade from [4]).

two of these junctions with different current densities is then (1.2).

$$V_{\rm BE}(T) = \frac{kT}{q} \ln \left( \frac{I_{\rm bias}(T)}{I_{\rm S}(T)} \right) \tag{1.1}$$

$$\Delta V_{\rm BE}(T) = \frac{kT}{q} \ln(p) \tag{1.2}$$

Adding these two values in a correct ratio a temperature independent voltage (better known as a bandgap voltage) can be generated (see figure 1.1). Finally the  $\alpha \cdot \Delta V_{\text{BE}}$  PTAT voltage can be compared against this bandgap voltage to do a temperature reading.

The main downside of bandgap sensors is that they do not benefit from technology scaling, which mainly involves the improvement of lithography. Good BJTs, however, require wll-defined doping profiles. Also newer technologies often don't have 'native' support for BJT's, which must be made as parasitic devices.

Another downside is that BJTs naturally provide a temperature dependent output voltage. With newer technologies, supply voltages decrease at a faster rate than the threshold-voltage, resulting in smaller headroom. Therefore porting a BJT temperature sensor design to a newer technology proves to be far from trivial.

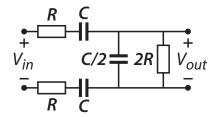

#### 1.2.2. RESISTOR

Resistor based sensors rely on the sensitivity of a resistance to temperature. The temperature sensitive resistor (thermistor) can be used as part of an RC filter, which has the advantage that the readout can now be done in the phase-domain. One such example of a resistive temperature sensor is [5], which uses a Wien-bridge topology. This was (see figure 1.2) used to obtain a reasonably linear phase-shift over a small frequency and temperature range.

However, resistor based temperature sensors are plagued by similar downsides as bandgap sensors. Just like bandgap sensors, resistor based sensors rely heavily on doping for their electrical characteristics, therefore, to minimize spread, they require a larger size. Moreover the temperature dependency of resistors is often very non-linear and spreads from sensor to sensor. Therefore resistive temperature sensors need multi-point trimming to achieve any kind of competitive accuracy; this makes them ill-suited for thermal monitoring applications.

1. Introduction

Figure 1.2: Wien Bridge.

Figure 1.3: Pseudo Differential Ring Oscillator.

#### 1.2.3. Inverter Delay

Another class of temperature sensors is based on inverter (or gate) delay. Usually a ring-oscillator is made, whose oscillation period depends on the threshold-voltage and the charge carrier mobility of MOSFETs, which in turn depends on the temperature. An alternative is to use a TDC to measure the delay of a set of inverters, however TDCs suffer from their own downsides such as large spread, high power consumption and high power supply sensitivity. Even with ideal readout, the temperature dependent delay is still very non-linear and process dependent, therefore temperature sensors based on inverter delay usually need multi-point trimming.

In [6] the authors employ two delay lines, with different biasing, to cancel out this non-linearity and suppress process variation, which is present in both delay lines. Normally the PSRR of inverter delay based sensors is very bad, however the authors claim that, using a pseudo-differential structure (see figure 1.3) and supply regulator, they achieve a good suppression of the supply noise. The requirement for a supply regulator, which is included in the area, makes inverter delay based sensors even less attractive.

#### **1.2.4. LEAKAGE**

Leakage based temperature sensors are often used to measure process variation and/or temperature. Modern technologies suffer from multiple sources of leakage; sub-threshold leakage, gate tunneling, punch-through current and reverse bias current of the drain diffusion diode.

In [7], the authors assume sub-threshold leakage to be dominant, and used that leakage current to make an oscillator. A supply voltage range from 0.5 V to 1.0 V was claimed, however the supply sensitivity was not stated, and since the design uses a ring oscillator, its supply rejection will not be very good. The oscillator period was close to the target for a thermal monitoring application, however the noise for such a measurement was not reported. Although the reported accuracy and area for state-of-the-art leakage based temperature sensors are very good, their downsides, such as poor PSRR and resolution, appear to be too bad to be reported. Both PSRR, because of the high-power high-density digital circuitry surrounding the thermal monitoring sensor, and the detection limit are very important for thermal monitoring applications. Therefore leakage based sensors are also not ideal for this application.

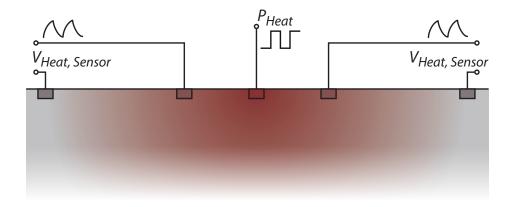

#### 1.2.5. THERMAL DIFFUSIVITY

Thermal-Diffusivity based temperature sensors use the temperature dependency of Thermal-Diffusivity, in other words; the time heat takes to propagate through a material depends on the material's temperature. By generating small heat pulses in the substrate of a chip, a time-delay, based on the thermal-diffusivity of silicon, can be read-out. Because this is in principle a time measurement, TD sensors don't suffer from the shrinking voltage headroom in smaller tech-

Figure 1.4: Temperature sensing principle of Thermal-Diffusivity based temperature sensors.

nologies. Moreover, since electrical delays in smaller technologies become smaller, smart TD sensors should become more accurate. The technique itself benefits from modern technologies since the thermal delay is defined by the purity of silicon combined with the heater/sensor spacing, which is defined by lithography. The temperature sensor required to sense the thermal-delayed signal can be relatively simple, since it only needs to measure an accurate delay and not an accurate temperature, and good time references are usually already present in high performance digital circuitry. All of these factors make thermal diffusivity sensors a promising candidate for thermal monitoring of SoCs.

In order to readout the delayed thermal signal a temperature sensor is needed, however this does not have to end in a 'catch-22' (a vicious loop). By using a thermopile, a differential heat measurement can be performed (see figure 1.4); the 'hot' junction picks up the time delayed heat signal while the 'cold' junction, which is very far away from the heater, stays still. Therefore in TD sensors a thermopile is often used as the sensing element. An added advantage is that multiple thermopiles can be linked together to boost the output signal. The Seebeck coefficient for Silicon and Aluminum is 440  $\mu$ V/K and 3.5  $\mu$ V/K respectively, thus a thermopile made from these materials will have a sensitivity of 436.5  $\mu$ V/K per arm. The thermal diffusivity *D* itself can be approximated by [8]:

$$D \propto 1/T^n \tag{1.3}$$

where  $n \approx 1.8$ . As explained this signal is picked up by the 'hot' junction, after which the phase is digitized and then converted to a temperature value. If the heater is driven by a constant frequency then the conversion of temperature to phase is approximated by [8]:

$$\Phi_{ETF} \propto s\sqrt{f/D} \propto s \cdot T^{n/2}\sqrt{f}$$

(1.4)

where *s* is the spacing between the heater and the 'hot' juctions,  $n \approx 1.8$ , *T* is the temperature and *f* is the frequency at which the heater is driven.

6 1. Introduction

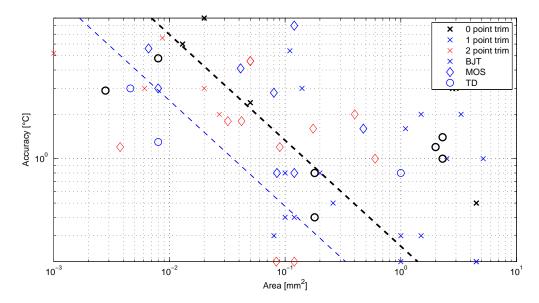

Figure 1.5: Accuracy vs. Area barrier, plotted from a survey on temperature sensors taken from [9]. Black is 0-point trim, blue is 1-point trim, red is 2-point trim (or more). The black line denotes the trend for 0-point trim BJT and MOS devices, the blue line denotes the same for 1-point trim.

#### 1.2.6. ACCURACY VS. SIZE

Last but not least is the accuracy-size trend. To get a certain accuracy in BJT based temperature sensors a certain area is required. This is because BJTs rely on both lithography and doping for their electrical characteristics. While lithography improves very well for newer technologies doping improves at a much slower rate, facilitating the trend of accuracy vs. area. This can be seen in figure 1.5, where a list of temperature sensors from [9] has been plotted. For zero or single point trim only TD sensors punch through the accuracy-area trend.

#### 1.3. OUTLINE

TD temperature sensors targeting thermal management have been made before, most notably [10] and [11]. While [10] uses an analog Gm-C integrator, which requires a large integration capacitance and analog techniques such as gain-boosting to achieve output impedance requirements, [11] is a digital reincarnation, employing a VCO counter combination to replace the analog Gm-C integrator. This approach fits the CMOS scaling story better because it removes the need for the highly analog Gm stage as well as the large integration capacitance, thus reducing the required area.

However in the transition from analog Gm-C integrator to digital VCO counter integrator, some of the performance was lost, see table 1.1. As can be seen in the table there is a big area gain, however, the accuracy and noise take a significant hit. Also, the circuit power consumption went up due to the digital implementation. Considering that for maximum SNR, most of the sensor's power should be used to generate heat pulses, the need to reduce circuit power becomes very clear.

The goal of this research project is to find out where the loss in performance comes from, and then to restore the performance of the analog approach. There is also an additional requirement not to increase the sensor area compared to [11], and if possible to reduce it.

1.3. Outline 7

Table 1.1: TD Sensor evolution from analog readout to digital readout.

|                           | [11]      | [10]      |

|---------------------------|-----------|-----------|

| Area [mm²]                | 0.0046    | 0.008     |

| Inaccuracy, No Trim [°C]  | 6.5 (3σ)  | 2.4 (3σ)  |

| 1-pt. Trim [°C]           | 1.5 (3σ)  | 0.65 (3σ) |

| Temp. Range [°C]          | -10 — 125 | -40 — 125 |

| Resolution [°C]           | 0.6       | 0.21      |

| Speed [kS/s]              | 0.9       | 1         |

| Supply Sensitivity [°C/V] | -         | 1.3       |

| Power [mW]                | 3.6       | 3.1       |

The outline of this thesis is as follows; In chapter 2 the readout, and hence the VCO-based integrator, will be studied in more detail. Then in chapter 3 the design, and hence improvements over previous TD temperature sensors, will be explained. The resulting measurements and explanations thereon will be given in chapter 4. Finally in chapter 5 a conclusion will be drawn and advice for future work will be given.

## Phase-Domain $\Sigma\Delta$ -Modulator

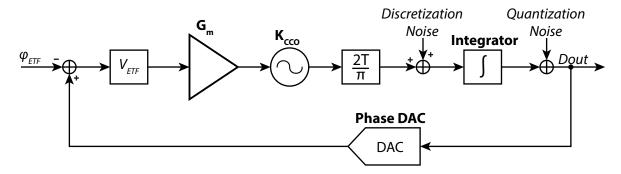

As discussed in the previous chapter, the readout of a TD sensor involves a time measurement, or more specifically, a phase measurement. Depending on the temperature, the thermal diffusivity of silicon will change, and so a periodic heater signal will result in an output signal with changing phase. In order to determine the temperature, this phase needs to be digitized, for this a phase-domain sigma-delta modulator (PD $\Sigma\Delta M$ ) is used. This chapter gives a brief description of the PD $\Sigma\Delta M$  (for more information on the PD $\Sigma\Delta M$  the reader is referred to [12]) with the aim of analyzing quantization artifacts from the VCO-based PD $\Sigma\Delta M$ . First a brief description of the operation of a TD sensor will be given.

#### 2.1. ETF

To measure the temperature using thermal diffusivity, first a heat signal needs to be generated in the silicon, then the delayed temperature signal needs to be picked up. The sensor which does this is called an ETF (Electro Thermal Filter). It typically uses a small diffusion resistance as the heater. Then a number of thermocouples are laid out in a circle around the sensor. Each thermocouple consists of a hot and a cold junction with a non-silicided diffusion resistor in between. The junctions are the contacts between the silicon diffusion resistor and the aluminum metal. If the cold junctions are at a sufficient distance they will not pick up any heat signal from the local heater, then all the heat signal generated will be fully picked up by the thermocouples. Finally, a phase readout can be done to determine the thermal diffusivity, and with that the temperature of the die can be determined.

#### 2.2. Ideal Phase-Domain $\Sigma\Delta$ -Modulator

The most interesting part of the information in the ETF output signal is in its phase. Because of the low ETF output voltages corresponding to the burned power in the heater, and because of the thermal noise of the thermopile resistance, this signal is very noisy. Therefore using edge detection for the phase readout is generally not a good idea [13]. It is better to use a measurement system in which the entire output signal of the ETF is used. This can be done by synchronously demodulating the ETF signal by a periodic signal with an adjustable and known

Figure 2.1: Ideal Phase-Domain Sigma-Delta-Modulator Readout.

Figure 2.2: Typical ETF phase response.

phase. For two sinusoidal waveforms at the same frequency we get:

$$\cos(2\pi f t + \phi_{ETF}) \cdot \cos(2\pi f t + \phi_{demod}) = \frac{1}{2} \left[\cos(\phi_{ETF} - \phi_{demod}) + \cos(2 \cdot 2\pi f t + \phi_{ETF} + \phi_{demod})\right]$$

(2.1)

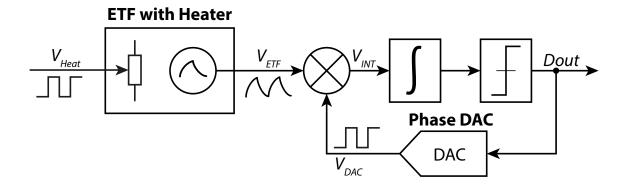

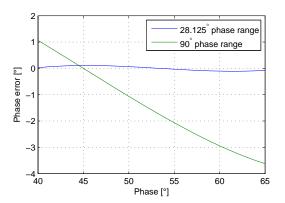

Thus there is a tone at twice the frequency and a DC term. If we integrate this signal for n periods the tone at twice the frequency will be filtered out; we are only left with the DC term. The DC term is dependent on the phase difference between the ETF phase and demodulation phase by a non-linear cosine function. Normally when having non-linear functions the effects of the non-linearity can be mitigated by using an actuator in a feedback loop which drives the input to the non-linear part back to a 'zero' value. In this case having a phase-DAC in a closed  $\Sigma\Delta$  loop has the advantage that the output is digitized at the same time (see Figure 2.1).

The  $\Sigma\Delta$  loop drives the demodulated output  $V_{err}$  back to zero. Since:

$$V_{err} \propto \cos\left(\phi_{ETF} - \phi_{demod}\right) \tag{2.2}$$

Figure 2.4: Cosine non-linearity phase error, where the 28.125° range has reference phases  $\phi_1$  = 39.375° and  $\phi_2$  = 67.5°, and the 90° range has reference phases of  $\phi_1$  = 0° and  $\phi_2$  = 90°.

this means that  $\phi_{demod}$  will be driven to a 90° phase-shift compared to  $\phi_{ETF}$ . However this requires the phase-DAC to have sufficient ENOB to handle the full range of ETF phases and to accommodate a small enough phase resolution to mitigate the cosine non-linearity (2.1). This means that every temperature sensor would require its own full phase-DAC, while if we were to take two phase references to straddle the temperature range then every sensor could use these two phase references. In a 160-nm CMOS technology a phase DAC requires a significant amount of area, taking into account the area used in previous TD sensors (see [10, 11]).

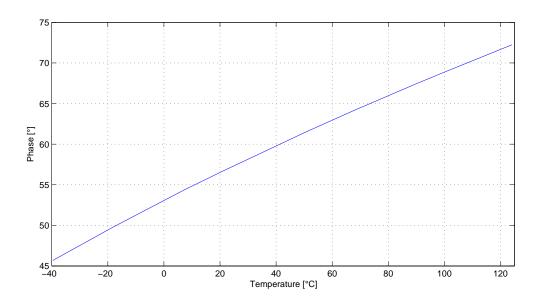

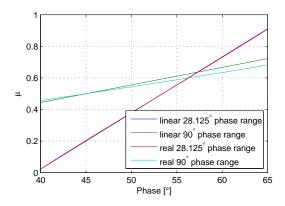

On second thought, however, the non-linearity associated with the use of a 1-bit phase DAC is not a big problem. When making a TD temperature sensor, a non-linear 'master-curve' needs to be generated since the ETF's temperature-to-phase characteristic is not linear anyway (1.4), see figure 2.2 for a typical ETF phase response. Since the non-linearity of the demodulation is fully deterministic it will show up in this master-curve and be mitigated when applying it. The non-linearity arises because the charge-balancing condition at the input of the integrator requires that:

$$\mu \cdot \cos\left(\phi_{ETF} - \phi_0\right) + (1 - \mu) \cdot \cos\left(\phi_{ETF} - \phi_1\right) \approx 0 \tag{2.3}$$

$$\mu \approx \frac{\cos(\phi_1 - \phi_{ETF})}{\cos(\phi_{ETF} - \phi_0) + \cos(\phi_1 - \phi_{ETF})}$$

(2.4)

For  $\phi_0$  and  $\phi_1$  close to a 90° phase shift with  $\phi_{ETF}$  the non-linearity can be neglected and (2.4) can be approximated as:

$$\mu \approx \frac{\phi_1 - 90^{\circ} - \phi_{ETF}}{\phi_1 - \phi_0} \tag{2.5}$$

$$\phi_{ETF} \approx \mu \cdot (\phi_0 - \phi_1) + \phi_1 - 90^{\circ} \tag{2.6}$$

Figure 2.3 shows how the real case (with the cosine non-linearity) looks compared to the ideal linearized case. It does this for two different phase reference settings; a full range of 90° and a smaller range of 28.125° which straddles the temperature range of the sensor. As can be seen in figure 2.4, when setting the two phase references close to the complete phase range of the

Figure 2.5: Analog Phase-Domain Sigma-Delta-Modulator Readout.

Figure 2.6: VCO-Based Phase-Domain Sigma-Delta-Modulator Readout.

sensor for the measured temperature range, the error made by the cosine non-linearity is very small.

In [10] an analog implementation of the figure 2.1 system has been made (see figure 2.5). The downside of this system is that in order to reach the output impedance requirements necessary to avoid excessive integration leakage a telescopic gain-boosted amplifier was needed. Due to the shrinking voltage headroom, this does not port very well to smaller technologies. Also the capacitor, which is about 4.5 pF, takes up a significant amount of area. That is why a more digital VCO-based front-end was designed in [11].

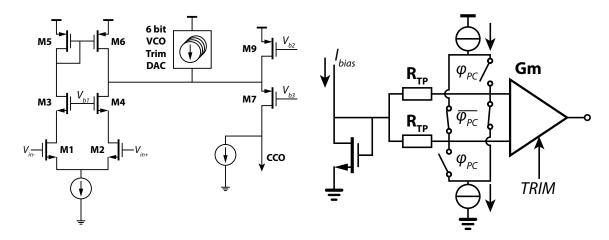

#### 2.3. VCO based Phase-Domain $\Sigma\Delta$ -Modulator

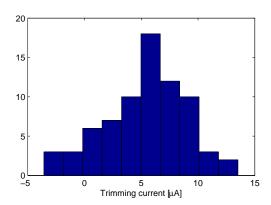

The VCO based readout uses a VCO and counter combination (see figure 2.6) as the integrator implementation of figure 2.1. Effectively what happens is that  $V_{ETF}$  is transformed into  $I_{Gm}$  by the Gm-stage, which is then transformed into a frequency signal  $f_{CCO}$ , which is finally integrated by the counter. The demodulation is done by the up/down action of the counter. Qualitatively this makes sense because a higher  $V_{ETF}$  voltage means a higher current, and hence a higher frequency. A higher frequency on the counter clock means that the counter counts at a higher frequency and has therefore a steeper slope.

Note that this system is highly digital, and scales very well to modern technologies. In fact the only analog part remaining is the Gm-stage. In the new digital readout the counter fundamentally can't leak; which means that the output impedance requirements on the Gm

stage are much relaxed. Therefore a Gm-stage requiring less voltage headroom, which also scales better to smaller technologies, can be employed.

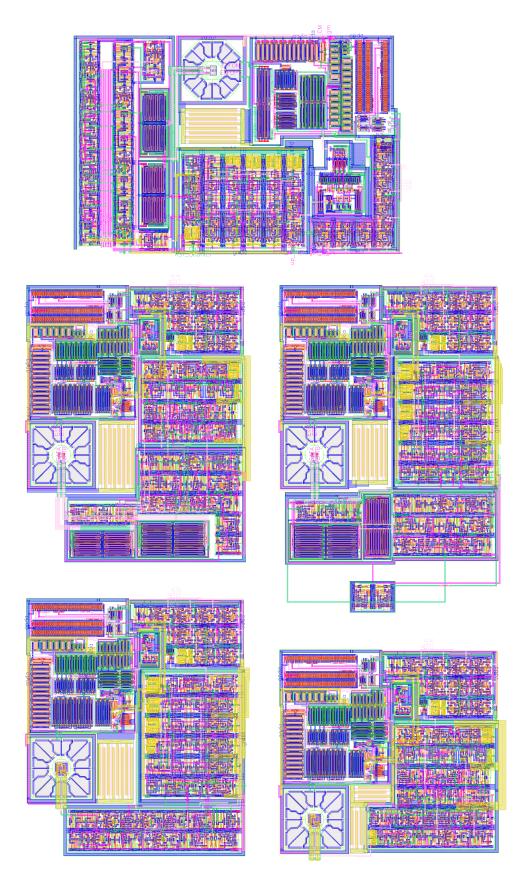

### System Design

For this project two tape-outs have been done. The first one is primarily to improve the VCO-based readout. After this tape-out there was still a performance gap between the new VCO-based readout and the old analog readout. The analog readout used a larger area ETF, to find out if this was the source of the increased inaccuracy and to measure batch-to-batch spread a new tape-out was done.

#### 3.1. ETF

As discussed in the previous, the ETF acts as both a heater and a heat detector. A periodic heating signal locally heats up the die. After a time delay, which depends on the absolute temperature of the silicon, this heat signal is picked up by the heat sensing element, i.e. the thermopile. The thermopile works based on the Seebeck effect, which states that two bi-metalic junctions at different temperatures generate a net difference in electromotive force (EMF). In our case the junction between the silicon and the aluminum interconnect can be considered as this bi-metalic junction. This approximation works since the Seebeck coefficient of metals are very similar, and differ largely from the Seebeck coefficient of silicon.

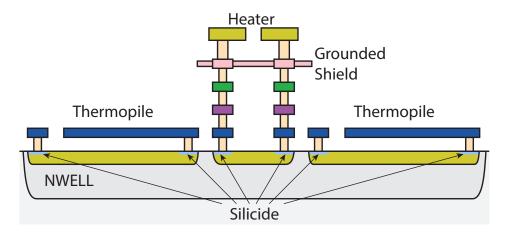

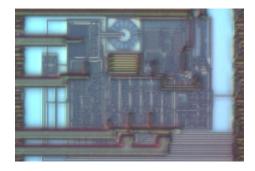

Figure 3.1 shows a cross-section of the ETF. The diffusion resistances of both the heater and the thermopiles are shown in yellow. The complete thermopile is made up of a stack of 16

Figure 3.1: ETF cross-section.

3. System Design

Figure 3.2: Heater resistor with switches.

Figure 3.3: MOSFET Heater.

thermopile resistances to boost the output signal. In the cross section two of these thermopile resistances are shown. The metal interconnects must be as short and low capacitance as possible to minimize the electrical delay. Also the electrical coupling between the heater and thermopile interconnect must be as small as possible to reduce injected phase-shift from the heat drive signal. Therefore the heater interconnect is routed at the highest metal layer and a grounded shield is routed underneath, in figure 3.1 the heater interconnect is routed over the ETF (at metal layer 5) into the back of the paper, at metal layer 4 the grounded shield, which is behind and separate from the vertical columns of the heater interconnect, also runs into the back of the paper.

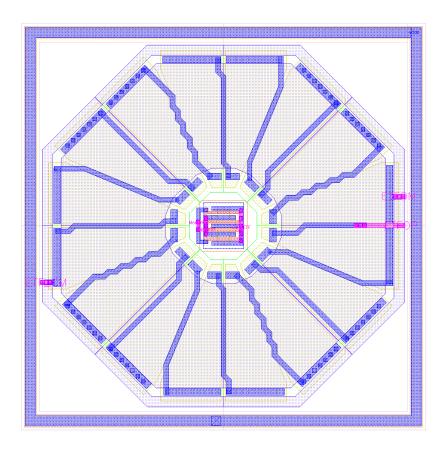

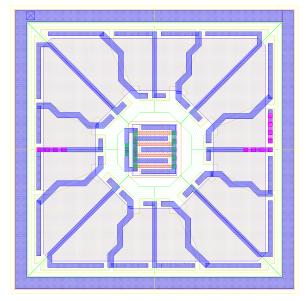

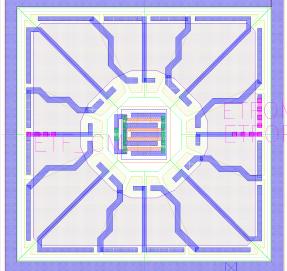

The ETF has 5 connections, two for the heater power, and three for the thermopile. The two outputs of the thermopile are directly connected to a differential pair, and to satisfy its common-mode requirements the middle of the thermopile is biased with a common-mode signal. A top-view can be seen in figures 3.6, 3.7, 3.9, 3.10 and 3.8. Effectively, as seen from the ETF common-mode voltage, there are two arms, each existing of 8 thermopiles, and each going to one of the differential pair input transistors.

#### **3.1.1. HEATER**

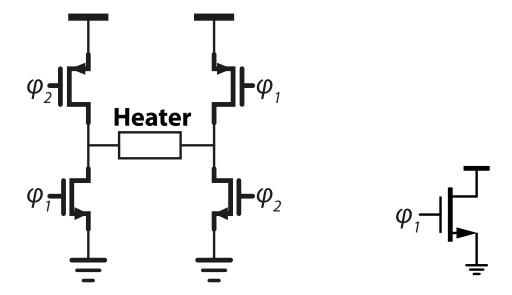

Traditionally the ETF heater has always been made using a diffusion resistance. Because the temperature sensor requires a periodic heat-signal, the heater must be able to turn on and off. This means that we need switches to conduct or stop current going through the resistor. As described above, a grounded shield has been used to minimize the effect of electrical coupling between the thermopile and the heater interconnect. To reduce any adverse effects from electrical coupling the heating signal is chopped such that any DC effects will cancel out. Figure 3.2 shows a schematic of the heater and switches.

Because the resistor needs to burn quite some power (from 1.5 up to 3 mW) it also needs to conduct quite some current (1.6 up to 2 mA). Therefore the switches which need to con-

3.1. ETF

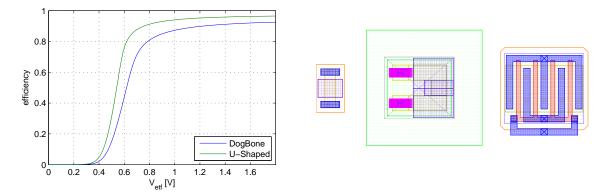

Figure 3.4: Heater efficiency.

Figure 3.5: Layout comparison of the three different heaters. From left to right; DogBone, U-Shaped and MOSFET heater.

duct the heater current must have very low on-resistance, otherwise they will also start to burn power. The immediate effect is that the efficiency of the heater is reduced (the efficiency of the combination of the two different kind of heaters with the heater switches is shown in figure 3.4), however there is a second effect; thermal cross-talk. Because the temperature sensor is so small the heater switches are also necessarily located close to the ETF, and if the switches start burning power at the exact frequency of the PD $\Sigma\Delta M$  it opens up another thermal-path into the ETF. To reduce these effects the switches need to be made large, which goes against the desire to make small temperature sensors. The heater switches size is 270  $\mu m^2$ , which for the smallest presented temperature sensor in this work would be almost 10% of the total area.

Obviously the self-heating of the heater switches is a problem. However, the solution to this problem is staring us in the face. Instead of trying to work around the self-heating of the switches we could also use it to positive effect, i.e. use the switches itself as the primary heat source, see figure 3.3. By using the on-resistance of the switch as a heat source the heater becomes inherently efficient, only the interconnect resistances will still limit the efficiency. Also the area-efficiency trade-of has been removed and  $270 \, \mu m^2$  of area has been saved. To add to that, the driving circuit can become simpler since we don't require any chopping of the power-supply and the switch can still be driven by a digital signal.

For testing purposes versions with the new MOSFET heater and two different resistive heaters; the older U-Shaped and newer Dog-Bone heater, have been taped-out. Figure 3.5 shows a layout comparison of these three heater types.

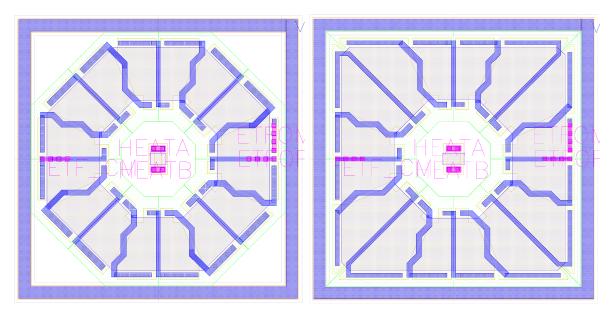

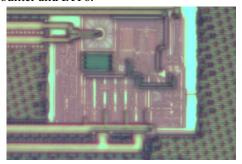

#### 3.1.2. SQUARE ETF

In the prior art (see figure 3.6), the hot-junctions are all at the same distance from the heater and also the cold-junctions are all at the same distance from the heater. This makes sense for the hot-junction as there is a particular distance which optimizes the trade-of for picking up enough heating power and having small phase inaccuracy. The general idea of the cold-junction is that it is so far away that it does not pickup any heat from the local heater, this however is not the ideal spot for the cold-junction. The ideal place is where it still picks-up some of the heating signal from the local heater. The effective heating signal sensed is the difference

3. System Design

Figure 3.6: ETF7 with Dog-Bone heater.

Figure 3.7: ETF7 square with Dog-Bone heater.

Figure 3.8: ETF3 with NMOS heater and large hot-junction.

3.1. ETF

Figure 3.9: ETF7 square with NMOS heater.

Figure 3.10: ETF7 square with NMOS heater and large hot-junction.

between the heat signal of the hot- and cold-junction. Therefore the optimum point for the cold-junction is where, if you were to extend the cold-junction, the increased noise from the increased thermopile resistance would outweigh the increase in effective heat signal. One has off-course to be careful since the cold-junction has a different phase than the hot-junction and the effective heat-signal sensed is the phasor subtraction of both the junctions. Therefore the inaccuracy in the cold-junction could, after the phasor subtraction, still have some significant effect on the total inaccuracy of the sensor.

Another factor to take into account is the area of the ETF, which is what was done in the prior art (see figure 3.6). In this ETF the cold-junctions still pickup plenty of heat signal, and can easily be further extended to get more SNR. In the prior art the ETF was purposely kept small to reduce the area, however there is no need to keep the cold-junctions all at the same distance. Therefore the cold-junctions at the corner of the ETF could easily be extended into the corners of the ETF. This will increase the SNR of the ETF while not consuming more area since this area would otherwise have been wasted. See figure 3.7, 3.9 and 3.10 for a layout of the square ETF.

In [10] a larger ETF has been used than in [11]. The larger ETF, called ETF3, was used in the analog readout, while the smaller ETF7 is only used in the digital readout. ETF7 was used as part of this work, and although the resulting sensors performed much better than [11] the inaccuracy was still larger than [10]. To rule-out the possibility that the spacing of the cold-junctions could be the cause of this increased spread, a new chip, which includes the larger ETF3 employed in the digital readout, has been taped-out. This new chip also includes versions where the silicide area is increased to see the effect of larger hot-junctions, which will be discussed in the following.

20 3. System Design

Figure 3.11: Zoom-in of the small silicide hot-junction.

Figure 3.12: Zoom-in of the large silicide hot-junction.

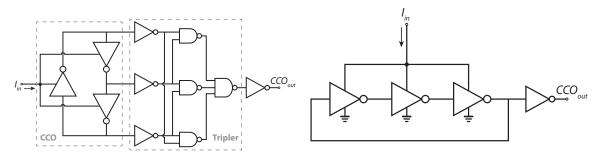

Figure 3.13: CCO plus tripler.

Figure 3.14: CCO plus level-shifter.

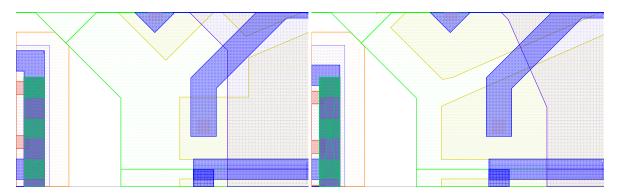

#### 3.1.3. SILICIDE

The junction of the thermopiles involves metal, silicide and doped silicon (see figure 3.1). The silicide is sputtered on the silicon so that the metallic contacts don't form parasitic Schottky diodes at the contact-silicon interface. To have a large net EMF, i.e. to have an effective junction between a metal and silicon, and not an effective junction between a metal and a metal, a silicide protect layer needs to be placed over the ETF thermopile diffusion resistance.

The simple rule-of-thumb states that larger structures produce less mismatch and show less variability, because these small variations will be averaged out. To test if this is also true for the silicide junctions of the ETF we have made versions of the ETF where the hot-junction silicided area has been enlarged. This is done in two ways, first of all if you look at an ETF from prior art (see figure 3.11 for a zoom-in of the small hot-junction), you can see that the active region (in yellow) at the hot-junction has a gap. This gap is left to satisfy the DRC, because it requires the Silicide Protect layer to be orthogonal to the active where the two layers cross. By filling up these gaps and then changing the shape of the silicide protect layer we have managed to satisfy the DRC while increasing the effective hot-junction area (see figure 3.12 for a zoom-in of the new hot-junction). The second way of increasing the hot-junction area is by extending the active further in direction of the heater and extending the start of the silicide protect layer further from the heater, such that the geometrical middle of the hot-junction is still 3.3  $\mu$ m away from the ETF center. For a layout of the new enlarged hot-junction see figures 3.10 and 3.8.

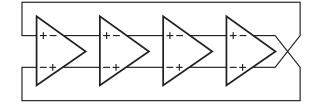

#### 3.2. CCO AND LEVEL-SHIFTERS

The previous design employed a 200 MHz CCO, and a tripler to triple the output frequency, and hence tripple  $K_{CCO}$ , the CCO consisted of a 3-stage ring-oscillator (see figure 3.13). The main problem of the previous design were the level-shifters in combination with the tripler, which did not work. If the level-shifters were more carefully designed the tripler might have worked, however, at these frequencies the duty-cycle at the output of the level-shifter is very important when tripling the frequency through the use of the three digital phases of the ring-oscillator. Not even the CCO of this work, which has been very carefully designed and optimized for corner and Monte-Carlo simulations, satisfies the duty-cycle requirements for a tripler, as can be seen later.

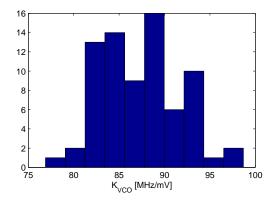

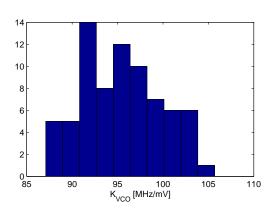

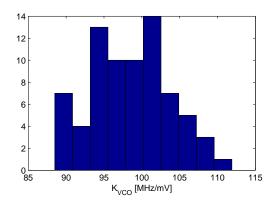

The current to frequency gain of the oscillator is very important. In [11] the total frequency gain was severely limited because the tripler was unreliable and so had to be bypassed. This reduced frequency swing caused a lot more quantization, or discretization noise. This, in turn, was the limiting factor on the temperature resolution. Clearly it is desirable to increase the total ETF voltage to frequency gain, to reach the 90 MHz/mV for which [11] was designed.

A simple charge to frequency model of the oscillator can be made by assuming a constant swing in the CCO. Then for every period of the CCO all stages require enough charge for their gates to reach the CCO output swing. During the other half of the period the CCO stages are discharged, and don't require any charge from the input. Clearly the total capacitance of the CCO nodes is very important for the CCO frequency, and CCO frequency gain:

$$T = \frac{V_{swing} \cdot C_{tot}}{I_{in}} \tag{3.1}$$

Which is to say:

$$\Delta f = \frac{\Delta I_{in}}{V_{swing} \cdot C_{tot}} \tag{3.2}$$

To have a high  $K_{CCO}$  we want small devices with small input capacitance. The downside of this is that parasitic capacitance will be a significant factor in determining the frequency gain, and that all final optimizations must be done on layout extracted models. The upside is that since we are not using a tripler, we only need one CCO phase. This means that two of the three CCO nodes are not loaded by a level-shifter. The single level-shifter must, however, be very carefully designed; a too large load means reduced swing on that CCO node, since the unencumbered nodes run faster and don't leave enough time for the loaded CCO stage to reach full swing.

22 3. System Design

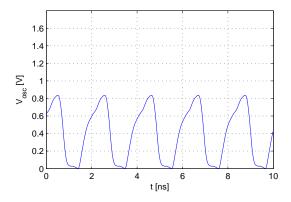

Figure 3.15: Typical output waveform of the ring-oscillator.

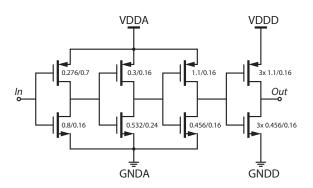

Figure 3.16: Levelshifter

Using minimum size switches for the level-shifter is not possible since the switching threshold of these devices must be somewhere in the middle of the CCO's output swing, which is below half of the 1.8 V power supply, see figure 3.15 for a typical CCO output waveform. Different techniques such as lifting the CCO's output swing away from the ground, e.g. by floating the CCO on top of a diode connected transistor, or shrinking the effective power-supply of the first stage of the level-shifter have been explored. However these techniques were either too slow (such as shrinking the effective power-supply of the level-shifter), or consumed too much area (floating the CCO on a diode connected NMOS). In the end the level-shifter as shown in figure 3.16 was chosen because it was the most robust, with smallest area, and by careful scaling of the gate-length it also achieved good input load. The first three stages of the level-shifter were connected to the analog power-supply to first regenerate the CCO signal into a strong digital signal before introducing the digital supply noise. The CCO was implemented using minimum size inverters. With the small load on only one of the oscillator stages a better current to frequency gain has been achieved, but to reach a wanted 90 MHz/mV we will need more gain from the Gm stage.

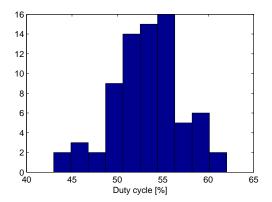

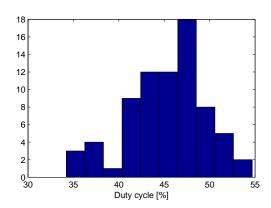

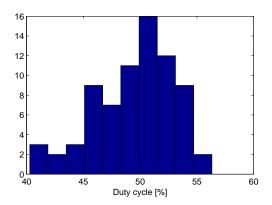

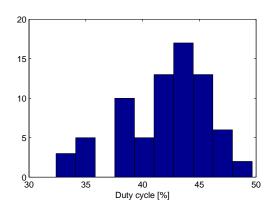

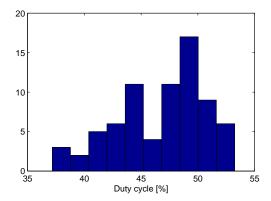

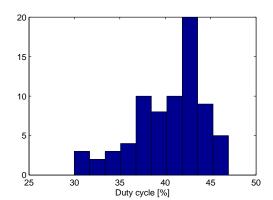

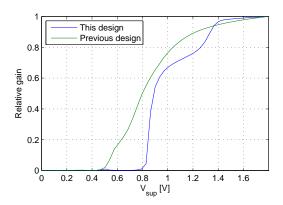

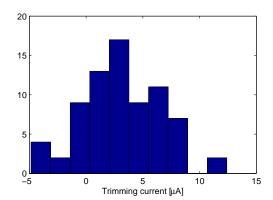

Figures 3.17, 3.18, 3.19, 3.20, 3.21 and 3.22 show the robustness of the CCO and level-shifter. These figures are the result of Monte-Carlo simulations on the Gm-stage and CCO combination after the Gm-stage and CCO combination has been trimmed to 500 MHz. Each of these figures are the result of Monte-Carlo simulations under various conditions, i.e. three different temperatures and two different input voltages which correspond to heater on and off. For all of the Monte-Carlo runs the output swing was fully from rail-to-rail, combined with the duty-cycle staying within 20% — 80% indicating that the level-shifter and CCO are working well.

#### 3.3. GM STAGE AND BIAS CIRCUIT

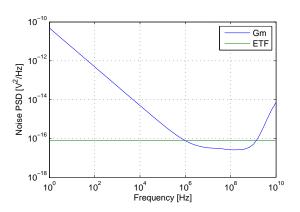

Four things are important to the Gm stage, first the input referred noise must be smaller than that of the ETF. Second the 1/f corner must be below the chopping frequency of 1 MHz. Third the gain, including the CCO gain, must achieve 90 MHz/mV. And last, the inaccuracy in the added phase shift must be small.

The Gm stage in the prior art achieved all these requirements, however the PSRR was very bad, which meant that the analog power-supply needed to be finely tuned to make all tem-

Figure 3.17: Duty cycle histogram at 125°C, low input voltage.

Figure 3.18: Duty cycle at 125°C, high input voltage.

Figure 3.19: Duty cycle histogram at 27°C, low input voltage.

Figure 3.20: Duty cycle at 27°C, high input voltage.

Figure 3.21: Duty cycle histogram at -55°C, low input voltage.

Figure 3.22: Duty cycle at -55°C, high input voltage.

24 3. System Design

Figure 3.23: Gm-stage from the prior art.

Figure 3.24: Gm-stage of current design.

perature sensors work over the temperature range. On top of that, the amplifier in prior art was designed to work in combination with the frequency tripler, thus compared to that we need more effective gain. So the previous design needed an update to achieve a VCO gain of about 90 MHz/mV, while keeping the same noise performance and phase-shift. Furthermore the PSRR needed improving to make the readout more robust and work over a larger range of temperatures.

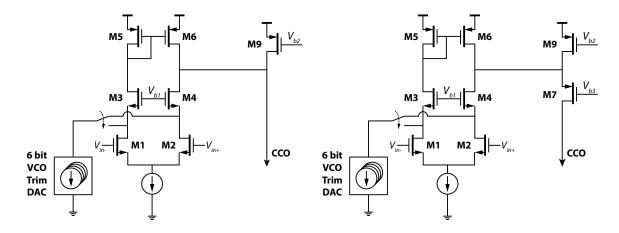

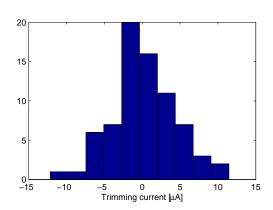

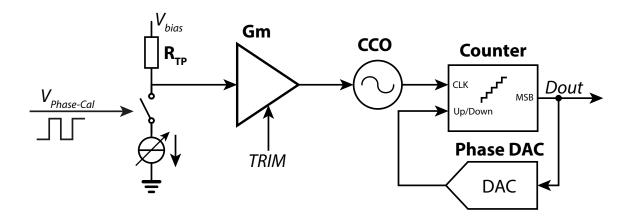

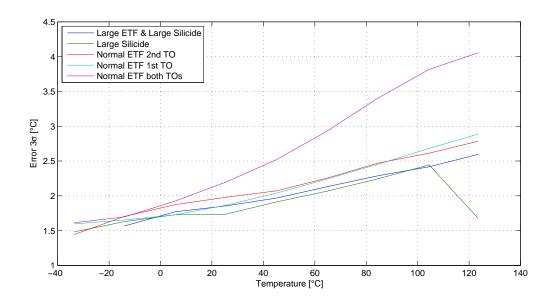

Figure 3.23 shows the schematic of the Gm-stage of the prior art. Transistors M3 and M4 cascode input transistors M1 and M2 in order to reduce the Miller capacitance. Transistor M9 provides an offset current, so that the CCO gets an input current for zero input. A 6-bit trimming DAC is used to trim the Gm and CCO combination to a desired frequency. This is used to compensate for process variation and mismatch. Note that the CCO frequency does not need to be very accurate, hence the current DAC does not even need to be monotonic.

Figure 3.24 shows the schematic of the new Gm-stage. Compared to the previous Gm-stage it adds an extra folded-cascode. This cascode isolates the Gm-stage from the finite impedance of the CCO, thereby increasing the effective gain of the Gm-stage. This helps because the effective impedance of the CCO is reasonably large, indeed in literature the ring-oscillator is often referred to as a VCO because of this. Another small benefit is that the PSRR is improved by the cascode transistor. Transistor M7 does add another pole to the Gm-stage, and although a common-gate stage is inherently faster than a common-source stage, because the current running through transistor M7 is very small the bandwidth of transistor M7 is comparable to that of the input transistors. Simulations show that the phase-response at 1.1719 MHz was not degraded, and so to keep the circuit small and simple it was decided not to use a bleed transistor to feed transistor M7 with extra current.

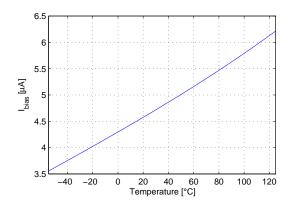

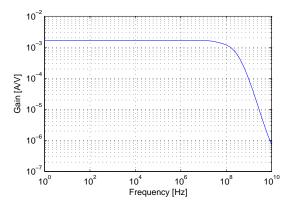

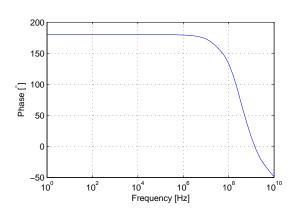

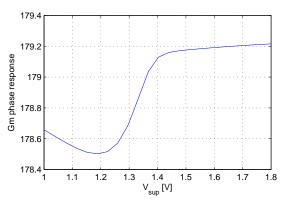

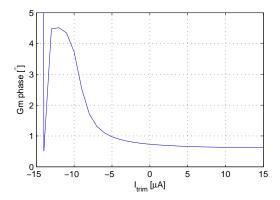

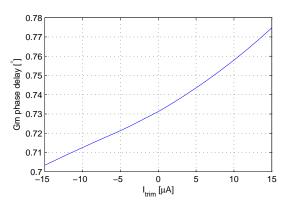

The Gm-stage is biased by a constant Gm biasing circuit, which aims to keep the transistor's current gain constant over temperature. Effectively this means that the bias current depends on the temperature, see figure 3.25. The input referred noise power spectral density of the amplifier is below that of the ETF thermopile resistance, see figure 3.26. The 1/f corner frequency is just below 1.1719 MHz. Since the phase response at the ETF frequency is primarily important, the bandwidth of the amplifier must be high enough to keep readout errors due to Gm phase-response inaccuracies low. In figure 3.27 and 3.28 we can see that the bandwidth is around

Figure 3.25: Bias current of constant-Gm-biasing over temperature.

Figure 3.26: Gm-stage input referred noise.

Figure 3.27: Gm-stage gain.

Figure 3.28: Gm-stage phase response.

Figure 3.29: Gm gain power-supply sensitivity, at 1.1719 MHz.

Figure 3.30: Gm phase response power-supply sensitivity, at 1.1719 MHz.

26 3. System Design

Figure 3.31: Gm + CCO gain histogram at 125°C.

Figure 3.32: Gm + CCO gain histogram at 27°C.

Figure 3.33: Gm + CCO gain histogram at -55°C.

Figure 3.34: Trimming histogram at 125°C.

Figure 3.35: Trimming histogram at 27°C.

Figure 3.36: Trimming histogram at -55°C.

Figure 3.37: Simplified phase-calibration diagram.

100 MHz and the added phase delay at the ETF frequency is about 0.67°. From previous work, this translates into a temperature error of about 4°C, but within a batch the spread is expected to be much smaller. The PSRR has been improved by a factor 2, see figure 3.29. The phase sensitivity to the power-supply (see figure 3.30) is about 0.10°/V, which corresponds to about 0.66°C/V. The gain combination of the amplifier and CCO has been increased by a factor 3, to compensate for the loss of the tripler and to achieve a VCO gain of 90 MHz/mV. All this was done while keeping the current consumption the same.

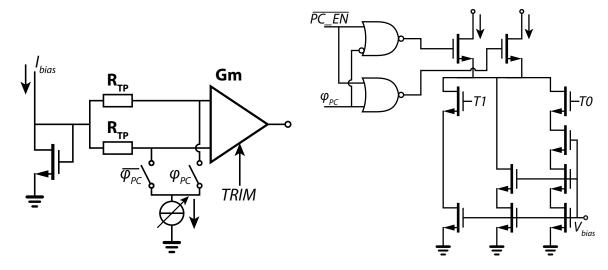

## 3.4. Phase-Calibration

Every delay after the thermopile but before the demodulation, which includes the Gm-stage, and CCO and level-shifter combination, will show-up in the measured phase. If we could measure this electrical delay we could compensate for it. This so called phase-calibration will drive an electrical signal, with known phase, at the input of the Gm-stage (see figure 3.37). Then by measuring the delay as we would measure the ETF delay, we can determine the electrical delay and compensate for it. If the electrical delay spreads due to process variation or due to mismatch we can do a one-time trimming. For temperature dependent delay effects or delay drifts we can compensate with a continuous phase-calibration. Such a continuous phase-calibration requires a low noise conversion not to limit the temperature resolution.

Figure 3.37 shows the basic idea behind the phase-calibration. A periodic current is driven through the thermopile resistance, which creates a periodic voltage input at the Gm-stage. The rest of the readout is similar to a normal ETF phase measurement, only now we know the phase of the phase-calibration. After we know the measured phase we can determine the only unknown quantity, i.e. the electrical phase-delay.

To keep a simple and small biasing circuit it was decided to use only one current source, and to make the phase-calibration signal switch between the left and right arm of the thermopile, see figure 3.38. This does mean that there is a common-mode shift on the thermopile and the Gm-stage, but simulations show that the phase-calibration current was small enough not to disturb the dc-biasing condition of the ETF common-mode voltage.

28 3. System Design

Figure 3.38: Phase-calibration schematic.

Figure 3.39: Detailed phase-calibration diagram.

Figure 3.40: Improved low-power counter.

In figure 3.39 the detailed phase-calibration can be seen. The digital circuitry is placed locally within the analog part to reduce digital coupling into the Gm input. The phase-calibration enable and the phase-calibration phase signals come from the heater-drive. It is important to reduce any noise in the phase-calibration readout such that we can do a phase-calibration for every conversion without reducing the temperature resolution, that is why a large amplitude has been chosen for the phase-calibration signal. A current DAC has been used to make sure that a too large phase-calibration signal amplitude does not render the phase-calibration useless (see T1 and T0 in figure 3.39). The circuit has been simulated for all phase-calibration strengths, and for all strengths the amplifier is working. Simulations show that there is no increase in input referred noise or increase in 1/f noise corner due to the added phase-calibration.

## 3.5. COUNTER

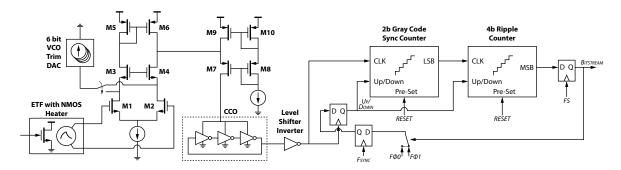

In the prior art, the 6-bit counter, which ran at around 200 MHz, consumed 1.44 mW. But in this design, the timing resolution will be increased by increasing the nominal CCO frequency. This has the added benefit that the CCO works in a more linear region, and at a higher voltage swing. The downside is that, using linear extrapolation, we can expect the counter to consume somewhere around 3 mW, which would be much more than half of the total power consumption. Also, simulations show that the counter only works reliably up to 600 MHz. Therefore the counter needs to be improved to accommodate the full frequency swing under all conditions, and the power consumption needs to be lowered as much as possible.

3.5. Counter 29

Figure 3.41: 2-Bit Gray-code up/down pre-scaler.

Figure 3.42: 2-Bit binary up/down counter.

Figure 3.43: Pulse generation circuit.

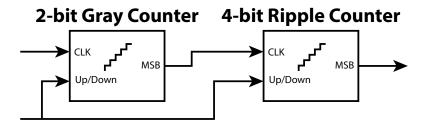

To lower the power consumption the counter has been split in two parts, see figure 3.40. This saves power in the second counter because the first counter, which acts as a pre-scaler, lowers the frequency at which the second counter counts. The pre-scaler still works at the higher frequencies though, which means that this counter must be a fast counter. By making the pre-scaler a 2-bit counter we don't need to think about the carry propagation. The second counter now runs at a quarter of the CCO frequency, which means that its speed requirements are drastically decreased.

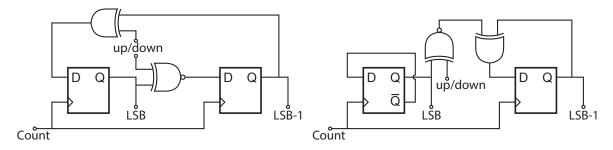

It turns out that by implementing the 2-bit pre-scaler as a Gray-code [14] counter the circuit is inherently faster and has less transitions. The reduced transitions come from the fact that Gray-code only has one bit transition per count. This means that four counts require four bit transitions, while in a binary counter four counts require six bit transitions. Thus by implementing the 2-bit pre-scaler as a Gray-code counter we have reduced the bit transitions by 30%. The speedup comes from the fact that there is no sequence of an xor and xnor gate, see figure 3.41 compared to figure 3.42.

By implementing the 4-bit counter as an binary ripple counter the power consumption can be further reduced. Every next bit in the counter will effectively run at half the frequency, which adds up to an effective clocking saving up to 50%. However implementing a 4-bit up/down ripple counter requires much more logic than for a normal 4-bit up/down counter. The problem comes from the fact that we are putting logic on a clock input, which is edge sensitive, and should be clocked when transitioning between two states. For this transition it doesn't matter if we go back or forth, in both cases the next bit should be toggled. This makes it quite hard for static logic since it should give a rising edge in both cases; going back and forth between the two states. Since this increase in logic drastically increases the counter area, and since the counter area is already quite large compared to the total sensor area it was decided to implement the 4-bit up/down ripple counter using dynamic logic, for which a pulse generator will be used.

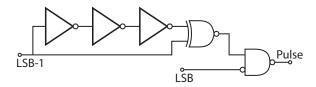

The pulse generator will generate a pulse whenever the pre-scaler switches between the two states where the ripple counter should increment or decrement its state. The pulse generator

3. System Design

Figure 3.44: 4-Bit ripple up/down counter.

is shown in figure 3.43. It relies on an inverter delay line to generate its pulse, this is why additional care was taken during the design; Monte-Carlo simulations were done under different conditions, i.e. frequency and temperature, with extra capacitive loading on all the lines deriving from the pulse generator. It was only after increasing the extra capacitive loading to five times the parasitic capacitance that the circuit started to fail in some Monte-Carlo runs. These tests show that, even though dynamic logic was used, the counter is very reliable.

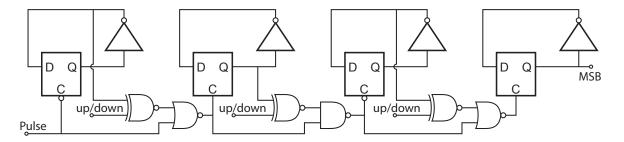

Because every register is now clocked with a short pulse, we don't need positive edge triggered flip-flops. Using level sensitive registers has been the main driving force in reducing the counter area. By careful consideration of the driving strength of all digital components and by careful consideration of which logic element combination to take, the area of the complete counter has been reduced by 20%.

Figure 3.44 show a schematic of the 4-bit ripple counter. The logic of the counter is the gating signal, i.e. the gating signal determines when the register should toggle its output. This is reflected by the fact that every register is fed the inverse of its output on its data input port. Every next stage in the counter now only needs to determine if its register should toggle, and if so let the pulse pass, otherwise it should stop the pulse from propagating. The up/down signal for the ripple counter is a buffer delayed version of the up/down signal in the pre-scaler. The up/down signal in the pre-scaler is resynchronized to the clock signal to avoid any metastability. With all the changes made, the counter works over a higher frequency range, while saving 60% of power compared to the old counter. One important thing to note is that, although not shown in figure 3.42 and 3.44, all registers have a reset port.

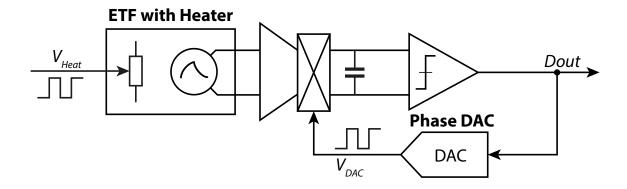

## 3.6. HEATER-DRIVE AND TOP-LEVEL

The heater-drive controls the entire temperature sensor, not only does it generate the signal to drive the heater, but it is responsible for all other driving signals. Phase delays between the driving signals, i.e.  $\phi_{ETF}$ ,  $\phi_{demod}$  and  $\phi_{PC}$ , directly result in measured delays. To minimize delay differences the heater-drive has a high frequency reference clock. All important phase signals are re-clocked with this high frequency clock. For a simplified diagram of the heater-drive see figure 3.45.

The heater-drive must be able to work in three different modes; temperature conversion mode, phase-calibration mode and trimming mode. Each of these modes requires different driving signals. For the temperature conversion the ETF must be driven by a periodic signal, the phase-calibration must be disabled and the phase DAC must multiplex between  $\phi_0$  and  $\phi_1$ , which

Figure 3.45: Simplified block-diagram of the temperature sensor.

are generated outside of the temperature sensor. For the phase-calibration mode the phase-calibration must be enabled and driven by a periodic waveform, while the ETF heater must be turned off and the phase DAC must multiplex between  $\phi_0$  and  $\phi_1$ . For the trimming mode, to account for ETF self-heating effects, the ETF must be driven with a high frequency, such that the filtered ETF output is mostly silent, but has the DC self-heating offset. The phase-calibration must be disabled and the phase DAC must be disabled, which means that the counter only counts up. In this case the counter acts as frequency divider, the divided frequency is send off-chip where an FPGA can determine the frequency and close the trimming loop.

The bias-block and clock generation system are not include in the temperature sensor area. Because the temperature sensor is so small multiple have been placed on one die, which means that they can share these systems. This is similar to real thermal management, where multiple sensors need to monitor the multitude of potential local hot-spots. The clock generation system provides each sensor with the high-frequency reference clock, an ETF input clock and the two reference clocks for the phase DAC. For phase-calibration the ETF input clocking signal serves as phase-calibration signal and is delayed such that the phase references can be put around the electrical delayed phase-calibration signal. The extra delay on the phase-calibration is done because the electrical delay is very small and could be in the dead-zone of the PD $\Sigma\Delta M$ .

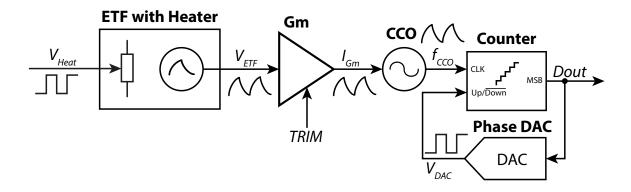

Figure 3.46 shows a detailed block-diagram of the temperature sensor (without the phase-calibration). The ETF, on the left, is connected to the Gm-stage, which in turn drives the CCO. The CCO signal is picked up and regenerated by the level-shifter and is fed to the clock input of the counter. The MSB output of the counter is sampled by the sampling clock and serves as the bit-stream. The loop is closed by selecting either of two reference phases, depending on the bit-stream value, and is used to demodulate the CCO signal, which means it is used for the up/down signal. As discussed above, all phase signals are re-clocked by a high speed reference clock, and the up/down signal is also re-clocked by the counter clock to avoid meta-stability.

3. System Design

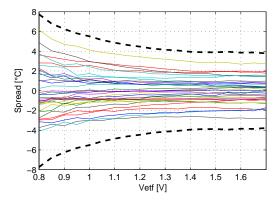

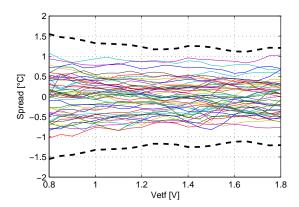

Figure 3.46: Detailed block-diagram of the temperature sensor.