Analysis and Optimization of a Novel Three-Phase Boost-Type PFC Rectifier

echnische Universiteit Del

# Belgian Rectifier

# Analysis and Optimization of a Novel Three-Phase Boost-Type PFC Rectifier

by

# Dimitrios Tsiakos

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Monday September 28, 2020 at 10:00 AM.

Student number: 4804988

Project duration: December, 2019 – September, 2020

Thesis committee: Prof. dr. ir. P. Bauer, TU Delft, supervisor

Dr. Ir. T. B. Soeiro, TU Delft Tu Delft Tu Delft Tu Delft

This thesis is a joint project between Delft University of Technology and Prodrive Technologies.

An electronic version of this thesis is available at http://repository.tudelft.nl/.

## **Abstract**

This project investigates the newly proposed Belgian Rectifier, a novel three-phase boost power factor correction rectifier which is advantageous for AC-to-DC conversion in applications, such as, off-board and on-board chargers for electric vehicles. The Belgian rectifier can achieve very high levels of efficiency and power density, while its components endure much lower stress than in other rectifier topologies. The capacitive midpoint produces a three-level voltage over the switches and inductors, therefore a number of advantages can be pointed out such as low stress of the MOSFETs, low magnetic energy requirement for the inductors and low EMI filtering. Two modulation schemes have been analyzed with regard to component stresses and soft switching and one of them is proposed. The modulation scheme derivation is followed by a full analysis of the converter that consists of steady-state modelling, dynamic closed-loop modelling, component loss and volume modelling. In addition, by sweeping through different parameters in the aforementioned models, a Pareto-front in the efficiency versus power density performance space is created. Thereby, an optimal design can be picked out using multi-objective optimization. Finally, a comparison between the Belgian Rectifier and Six-Switch Rectifier is done to reveal the advantages and disadvantages of the former topology.

Dimitrios Tsiakos Eindhoven, September 2020

# Acknowledgements

First of all, I would like to thank Prof. Bauer for giving me the opportunity to do my master thesis with DCE&S group, for his precious support and guidance throughout this project. I would also like to thank Prof. Soeiro for keeping in touch regularly with my work and for providing me valuable suggestions and advises to boost my progress.

Secondly, I would like to express my gratitude to Prodrive Technologies for jointly participating in this project and for sharing with me significant technical know-how, material resources and facilities. More importantly, I would like to thank my supervisor Jordi Everts whose support was essential and substantial for the completion of this project. Moreover, want to express my appreciation to all my colleagues in Prodrive Technologies who supported me throughout my thesis and with whom I created very pleasant memories of fun and creativity.

Last but not least, I want to say a big thanks to my family and friends who motivated and supported me in every way throughout my studies.

Dimitrios Tsiakos Eindhoven, September 2020

# Contents

|   |                                                                      | duction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                        |

|---|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|   | 1.1                                                                  | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |

|   | 1.2                                                                  | Objective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |

|   | 1.3                                                                  | Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3                                                        |

| 2 | Lite                                                                 | ature review                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5                                                        |

|   | 2.1                                                                  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5                                                        |

|   | 2.2                                                                  | Three-phase boost-type PFC rectifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          |

|   |                                                                      | 2.2.1 Six-switch boost PFC rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |

|   | 2.3                                                                  | Zero-voltage switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |

|   | 2.4                                                                  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

| _ | <b>T</b> I                                                           | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

| 3 |                                                                      | <b>3</b> • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                       |

|   | 3.1                                                                  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |

|   | 3.2                                                                  | Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |

|   |                                                                      | 3.2.1 Conduction states                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

|   | 3.3                                                                  | Average model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

|   |                                                                      | 3.3.1 Modulation 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

|   |                                                                      | 3.3.2 Duty-cycle derivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

|   |                                                                      | 3.3.3 Modulation 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

|   |                                                                      | 3.3.4 Duty-cycle derivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

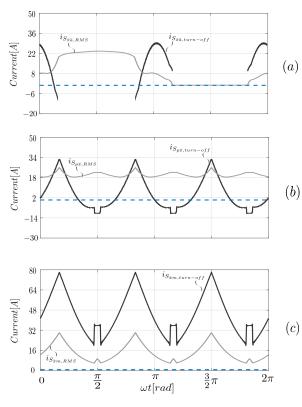

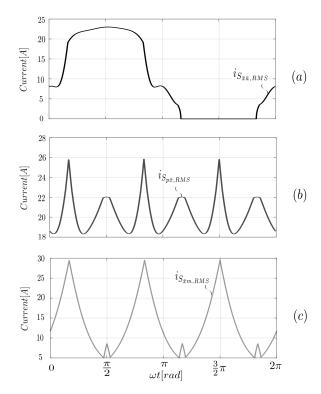

|   | 3.4                                                                  | Semiconductor Stresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |

|   | 3.5                                                                  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23                                                       |

| 4 | Clos                                                                 | ed-loop control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25                                                       |

|   | 4.1                                                                  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25                                                       |

|   | 4.2                                                                  | Control scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25                                                       |

|   | 4.3                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

|   | 4.3                                                                  | Model & results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                       |

|   | 4.4                                                                  | Model & results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

| _ | 4.4                                                                  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29                                                       |

| 5 | 4.4<br>Mul                                                           | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29<br>8 <b>1</b>                                         |

| 5 | 4.4 <b>Mul</b> 5.1                                                   | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29<br><b>31</b><br>31                                    |

| 5 | 4.4 <b>Mul</b> 5.1 5.2                                               | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29<br><b>31</b><br>31                                    |

| 5 | 4.4<br>Mul<br>5.1<br>5.2<br>5.3                                      | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29<br>81<br>81<br>83                                     |

| 5 | 4.4 <b>Mul</b> 5.1 5.2                                               | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29<br>81<br>81<br>83<br>85                               |

| 5 | 4.4<br>Mul<br>5.1<br>5.2<br>5.3                                      | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29<br>81<br>81<br>83<br>85<br>85                         |

| 5 | 4.4<br>Mul<br>5.1<br>5.2<br>5.3                                      | Summary       2         -Physics Component Modelling       3         Introduction       3         Approach       3         Switching model - Fourier analysis       3         Components modelling       3         5.4.1 Semiconductors       3         5.4.2 Inductors       4                                                                                                                                                                                                                                        | 29<br>31<br>31<br>33<br>35<br>35                         |

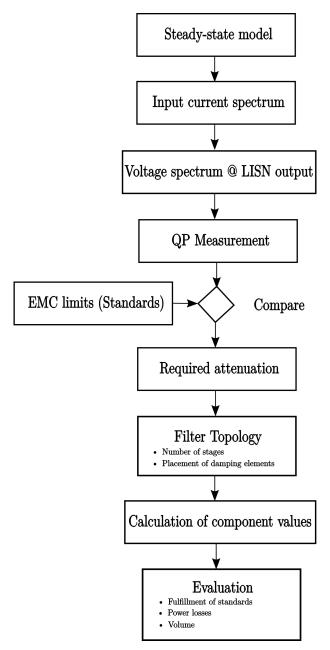

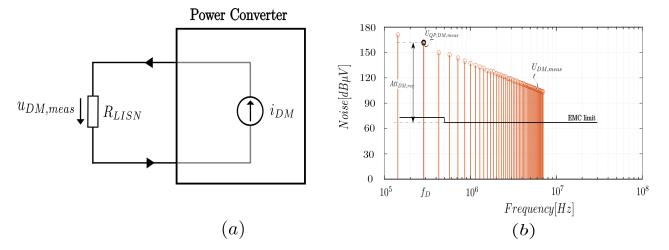

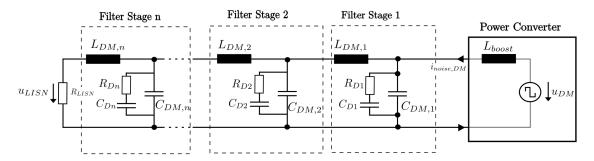

| 5 | 4.4 <b>Mul</b> 5.1 5.2 5.3 5.4                                       | Summary       2         -Physics Component Modelling       3         Introduction       3         Approach       3         Switching model - Fourier analysis       3         Components modelling       3         5.4.1 Semiconductors       3         5.4.2 Inductors       4         5.4.3 EMI filter       4                                                                                                                                                                                                       | 29<br>31<br>31<br>33<br>35<br>35<br>42                   |

| 5 | 4.4 <b>Mul</b> 5.1 5.2 5.3 5.4                                       | Summary       2         -Physics Component Modelling       3         Introduction       3         Approach       3         Switching model - Fourier analysis       3         Components modelling       3         5.4.1 Semiconductors       3         5.4.2 Inductors       3         5.4.3 EMI filter       4         Efficiency & volume       5                                                                                                                                                                   | 29<br>31<br>31<br>33<br>35<br>35<br>42<br>45             |

| 5 | 4.4 <b>Mul</b> 5.1 5.2 5.3 5.4 5.5 5.6                               | Summary       2         -Physics Component Modelling       3         Introduction       3         Approach       3         Switching model - Fourier analysis       3         Components modelling       3         5.4.1 Semiconductors       3         5.4.2 Inductors       4         5.4.3 EMI filter       4         Efficiency & volume       5         Summary       5                                                                                                                                           | 29<br>31<br>31<br>33<br>35<br>35<br>42<br>45             |

| 5 | 4.4 <b>Mul</b> 5.1 5.2 5.3 5.4 5.5 5.6                               | Summary       2         -Physics Component Modelling       3         Introduction       3         Approach       3         Switching model - Fourier analysis       3         Components modelling       3         5.4.1 Semiconductors       3         5.4.2 Inductors       4         5.4.3 EMI filter       4         Efficiency & volume       5         Summary       5         -Objective Optimization       5                                                                                                   | 29<br>31<br>31<br>33<br>35<br>35<br>35<br>35<br>37       |

|   | 4.4<br>Muli<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>6.6<br>Muli<br>6.1 | Summary       2         -Physics Component Modelling       3         Introduction       3         Approach       3         Switching model - Fourier analysis       3         Components modelling       3         5.4.1 Semiconductors       3         5.4.2 Inductors       4         5.4.3 EMI filter       4         Efficiency & volume       5         Summary       5         -Objective Optimization       5         Introduction       5                                                                      | 29<br>31<br>31<br>33<br>35<br>35<br>35<br>37<br>37       |

|   | 4.4<br>Mul<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>6.1<br>6.1<br>6.2   | Summary       2         -Physics Component Modelling       3         Introduction       3         Approach       3         Switching model - Fourier analysis       3         Components modelling       3         5.4.1 Semiconductors       3         5.4.2 Inductors       4         5.4.3 EMI filter       4         Efficiency & volume       5         Summary       5         -Objective Optimization       5         Introduction       5         Virtual prototyping routine       5                          | 29<br>31<br>31<br>33<br>35<br>35<br>35<br>37<br>37       |

|   | 4.4<br>Muli<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>6.6<br>Muli<br>6.1 | Summary       2         -Physics Component Modelling       3         Introduction       3         Approach       3         Switching model - Fourier analysis       3         Components modelling       3         5.4.1 Semiconductors       3         5.4.2 Inductors       4         5.4.3 EMI filter       4         Efficiency & volume       5         Summary       5         -Objective Optimization       5         Introduction       5         Virtual prototyping routine       5         Approach       5 | 29<br>31<br>31<br>33<br>35<br>35<br>35<br>37<br>37<br>37 |

|   | 4.4<br>Mul<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>6.1<br>6.1<br>6.2   | Summary       2         -Physics Component Modelling       3         Introduction       3         Approach       3         Switching model - Fourier analysis       3         Components modelling       3         5.4.1 Semiconductors       3         5.4.2 Inductors       4         5.4.3 EMI filter       4         Efficiency & volume       5         Summary       5         -Objective Optimization       5         Introduction       5         Virtual prototyping routine       5                          | 29<br>31<br>31<br>33<br>35<br>35<br>35<br>37<br>37<br>37 |

| viii | Contents |

|------|----------|

|      |          |

| 7   | Comparison                  | 71              |

|-----|-----------------------------|-----------------|

|     | Comparison 7.1 Introduction | 71              |

|     | 7.2 Semiconductors          |                 |

|     | 7.3 Inductors               | 74              |

|     | 7.4 EMI filter              |                 |

|     | 7.5 Pareto-front            |                 |

|     | 7.6 Summary                 | 77              |

| 8   | Conclusions 8.1 Future work | <b>79</b><br>80 |

| Bil | liography                   | 83              |

1

# Introduction

## 1.1. Background

Globally, the electric car deployment has seen a rapid growth over the last decade, with the global number of electric passenger vehicles surpassing the number of 5 million in 2018, thus a growth of 63% from the previous year. The distribution of this growth, however, is uneven since 45% of the electric cars that circulated on the roads in 2018 were in China - a total of 2.3 million - compared to 39% in 2017. On the other hand, the United States accounted for 22% of the global fleet, and Europe 24%. [1]

The very quick increase of the electric vehicle global market share has a lot of implications for the energy transition. The evolution of the well-to-wheel (WTW) greenhouse emissions from the EV fleet is determined by the combined evolution of the energy used by EVs and the carbon intensity of the electricity generation. Therefore, as the grid becomes less carbon intensive, so do the electric vehicles. It is clear that the benefits of the transport electrification will be greater if the EV deployment takes place in parallel with the decarbonisation of power systems.

On the same time, a rapid rise of the number of charging points across the globe is evident with approximately 5.2 million at the end of 2018, in other words, up to 44% increase from 2017. It is worth noting that the private sector contributed for more than 90% of the 1.6 million installations in 2018.[1]

The growth of the EVs cannot be sustained without the technology advances that are delivering substantial cost cuts. Very crucial technologies that need to be developed are the battery chemistry, the expansion of production capacity in manufacturing plants, as well as the power electronics that facilitate proper electric power conversion to charge the batteries.

The power electronics are part of the charger that supplies energy to the battery. These chargers can be categorized into two groups: the on-board and off-board chargers. The difference between the two is that the former is a part of the EV whereas the latter is part of a charging station. There are similar challenges when designing each of them, with the most important being the efficiency, power density and cost. For the on-board chargers, the size and weight are crucial since they affect directly the performance of the EV.

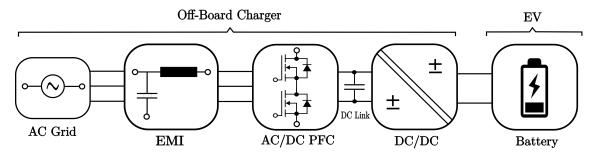

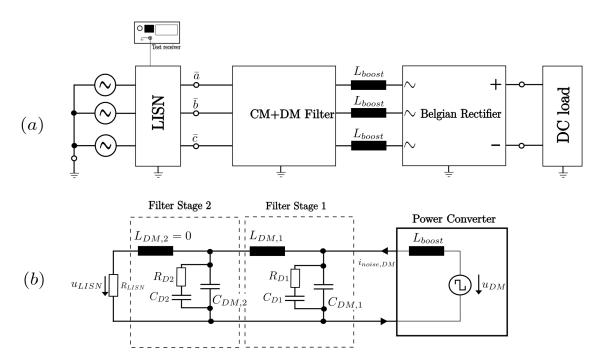

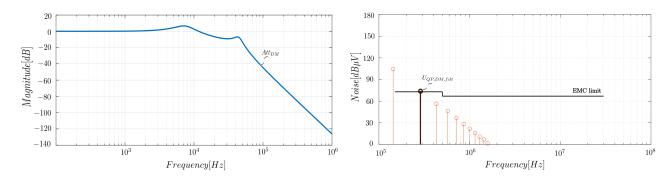

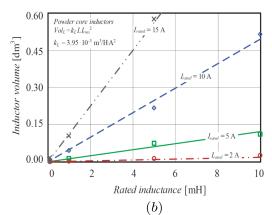

As can be seen in Fig.1.1, the off-board charger's main objective is to convert the electric power from AC-to-DC, therefore it is an intermediate step between the AC grid and the DC input of the battery. The sub-systems of the charger are the EMI filter, the PFC rectifier, the DC-bus and finally, a DC-DC converter that provides the right level of power to the EV battery. Starting from left to right in Fig.1.1, the EMI filter is useful to eliminate the high frequency components of the AC current produced by the HF switching of the PFC rectifier. This is necessary because there are certain IEC standards with whom the charger has to comply. Next, the PFC rectifier converts the electric power from AC-to-DC and at the same time delivers unit power factor. The DC-Link is actually maintaining a constant DC voltage

2 1. Introduction

Figure 1.1: Block diagram of an off-board charger with its main parts.

which is connected to the input of a DC-DC converter. The latter introduces isolation between the grid-rectifier and the battery, as well as the option to increase or decrease the output power according to the charging state of the EV battery.

This work is focused on the investigation of a novel 3-phase PFC rectifier that consists of a semiactive rectification stage and an integrated active boost stage which is called the Belgian Rectifier. The Belgian Rectifier can be used in off-board and on board chargers due to its advantages regarding efficiency, power density, as well as its ability to operate with a 3-phase or 1-phase voltage input [25, 29]. This topology is analyzed mathematically, modelled in steady-state, as well as during dynamic transients and finally, it is compared to another boost-type PFC rectifier, namely the Six-Switch Boost.

## 1.2. Objective

The objective of this project is to model and design a recently proposed boost-type 3-phase PFC rectifier, named the Belgian Rectifier. In particular regarding the efficiency versus power density trade-off, a complete evaluation of the Belgian Rectifier will be conducted and conclusions will be drawn about its advantages for applications in EV chargers. The application however, can also be different such as DC motor drive systems, MRI systems in healthcare and basically all applications that require a constant DC voltage supply.

More specifically, the research objectives of this project are the following:

- Describe the operational principle of the Belgian Rectifier mathematically and derive a proper modulation scheme that provides the smallest possible stresses on the components and as much as possible zero-voltage switching.

- Investigate what are the capabilities of the Belgian Rectifier regarding efficiency and power density for the use case of an off-board charger.

- Compare the Belgian Rectifier to a similar 3-phase boost-type PFC topology to make a final evaluation.

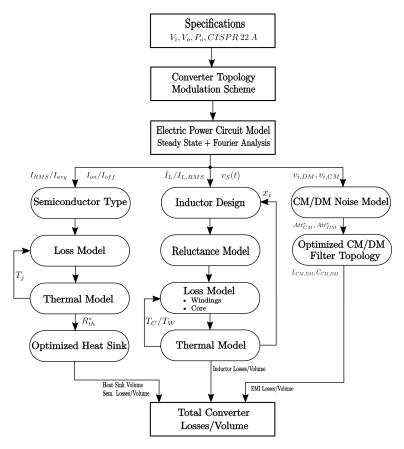

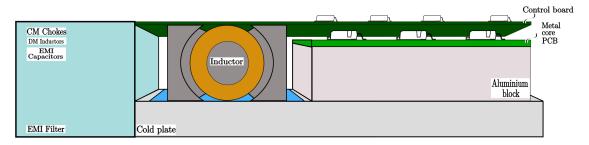

In order to reach these research objectives, a certain methodology has to be followed for the most efficient results. After understanding the operation of the "unconventional" Belgian Rectifier, a steady-state model is formulated. Secondly, the derivation of an appropriate modulation scheme that facilitates low component stresses is derived. Using the derived modulation scheme, all the relevant currents and voltages are calculated analytically through a Matlab model. Furthermore, detailed models for all components' losses and volumes are used and an EMI filter design procedure is followed. Through the aforementioned Matlab models, the expected efficiency and power density of the Belgian Rectifier is calculated and a multi-objective optimization is conducted for a wide global design and component design space. Finally, the Belgian Rectifier is compared in terms of efficiency and power density with the Six-Switch Rectifier.

1.3. Outline 3

#### 1.3. Outline

Apart of the introductory chapter, the thesis report content is presented as follows.

In the *second* chapter, a literature review of relevant subjects is organized. The conventional six-switch boost-type rectifier is described in order to introduce the reader to a topology that is in the same category as the Belgian Rectifier. Secondly, the fundamental concept of zero-voltage switching (ZVS) is explained in detail, in particular how it applies in the operation of the topology under investigation.

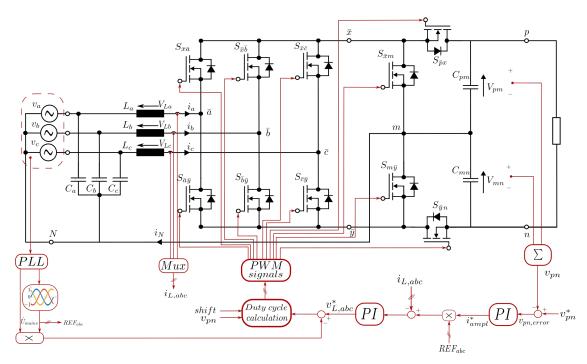

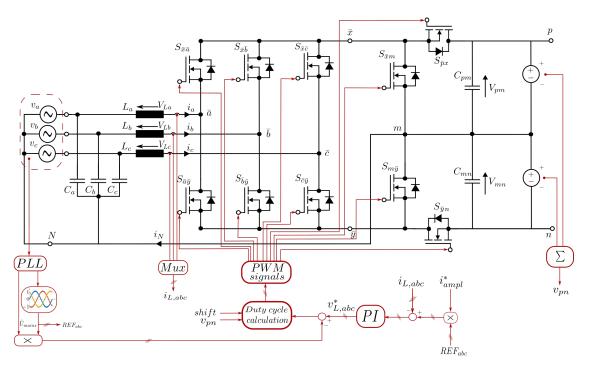

In the *third* chapter, the topology of the Belgian Rectifier is explained in detail. More specifically, by separating the full topology into individual blocks, each one of them is described in terms of functionality. Secondly, in-depth analysis of the operation of the topology is done and an average model is developed. Finally, using the average model, an appropriate modulation scheme is derived and its advantages are explained in terms of semiconductor stresses and switching losses.

In the *fourth* chapter, the closed-loop control is explained. Starting from the control scheme itself, an overview of the strategy that is followed is presented. Moreover, the actual model implemented in Simulink/Matlab is analyzed briefly and finally, the results of that model are shown and discussed.

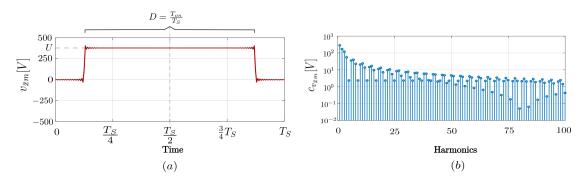

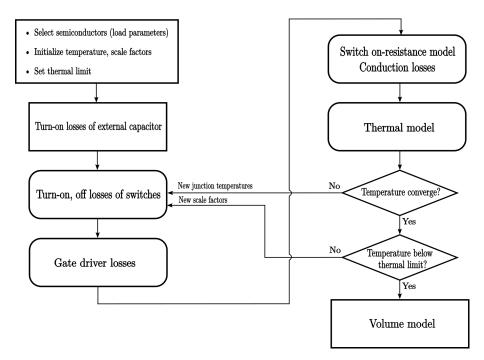

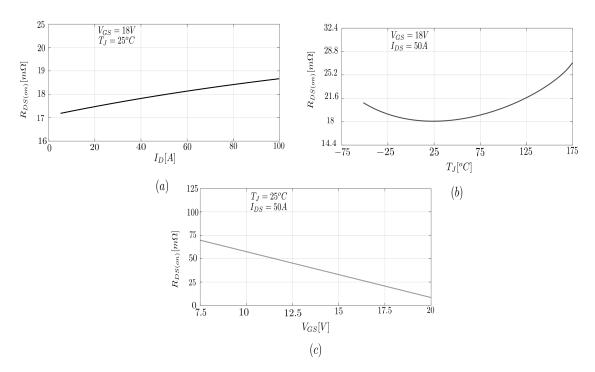

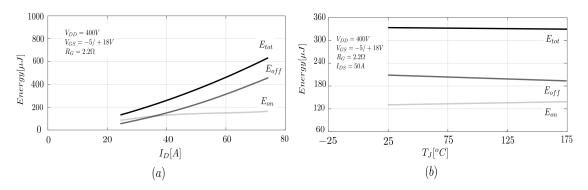

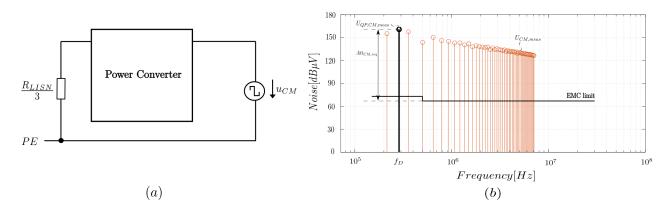

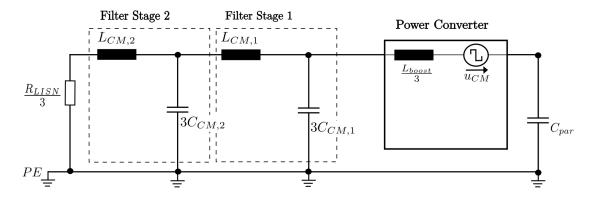

In the *fifth* chapter, the analytical models that are built or used are explained in detail. More specifically, starting from the approach that is followed, the separate models of different components such as the semiconductors, inductors and EMI filter are discussed. Finally, the efficiency and volume models that give an overview of the converter are analyzed in detail.

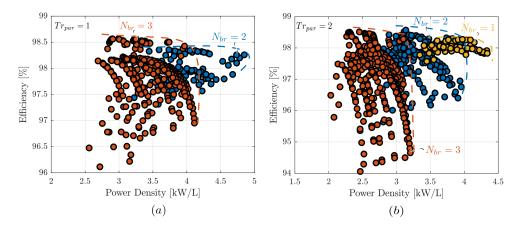

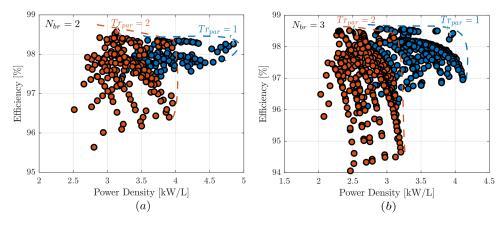

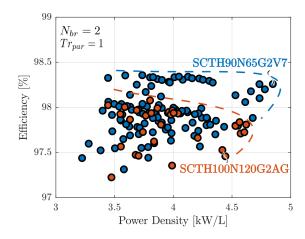

In the *sixth* chapter, the models that are described in chapter 5 are used to create a virtual prototyping routine that gives the optimal design of the converter. The design space of the multi-objective optimization is explained and the optimal performance of the converter regarding efficiency and power density is demonstrated.

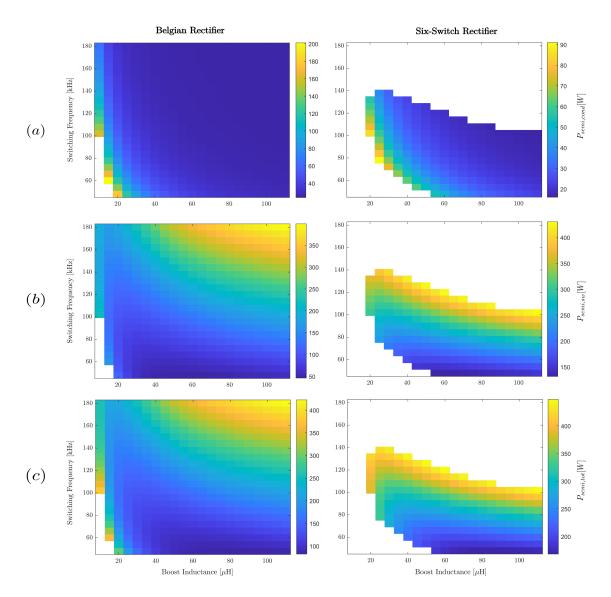

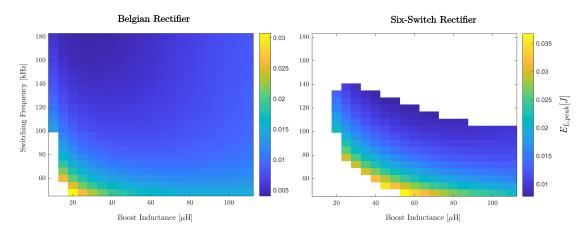

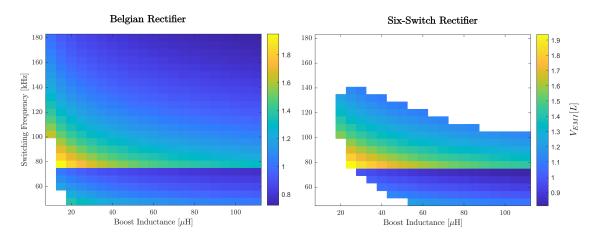

In the *seventh* chapter, the Belgian Rectifier is compared in terms of semiconductor stresses, semiconductor losses, peak stored enerfy of the boost inductors and EMI filter volume with the Six-Switch Rectifier. Therefore, a comparative evaluation is conducted which reveals the advantages of the Belgian Rectifier.

In the *eighth* chapter, the conclusions of this project together with some recommendations are summarized.

# Literature review

#### 2.1. Introduction

In this chapter, a literature review of relevant topics to the Belgian rectifier is provided. The three-phase boost-type PFC rectifiers that are mostly used in the industry like the six-switch boost PFC rectifier and the Vienna rectifier will be presented to introduce the reader with similar topologies and an average model will be formulated for the former. Starting from the basics, the function of the rectifier is to convert the 3-phase AC voltage of the grid into a DC voltage. This project is mostly focused on chargers for battery charging, but the aforementioned rectifiers can be also used in other cases such as wireless charging systems for electric cars or gradient amplifiers for Magnetic Resonance Imaging (MRI) scanners where there is typically a need to create a high-voltage DC bus from a three-phase AC input.

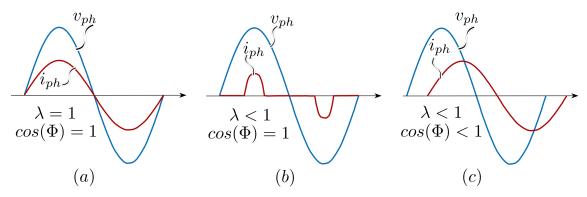

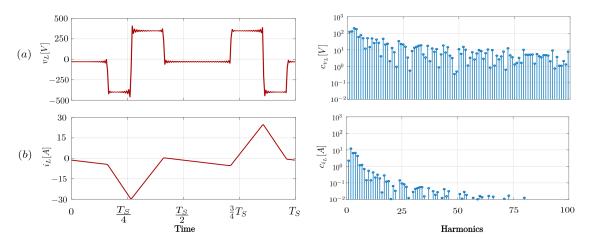

The phase and spectrum of the current that is drawn from the AC side of the converter are significant since they define the power factor which indicates the grid pollution that the converter adds to the grid. In Fig.2.1(a), the desired waveforms of AC voltage and current are presented, whereas Fig.2.1(b),(c) depicts the cases that need to be avoided. The PFC, which stands for power factor correction, makes sure that the power factor of the rectifier is unit, therefore the apparent power is equal to the active power. Moreover, the term "boost-type" in the name of this category of rectifiers means that the output DC voltage is higher than full-wave rectified mains voltage, and there is always a boost circuit that is controlled by pulse width modulation control signals.

Significant for the evaluation of a certain converter is the efficiency and power density. Since the project investigates a topology with high-frequency PWM control, the switching losses play a crucial role for the overall evaluation of that converter. More specifically, in order to increase the power density, the switching frequency needs to be increased, so that the stored energy in the magnetic components is decreased together with their size. But, the switching losses are proportional to the operating frequency, therefore there is a trade-off between switching losses and power density. To tackle this problem, soft switching is often desired in order to minimize the switching losses and be able to increase more the frequency further. In particular, zero-voltage switching is explained in a later section.

## 2.2. Three-phase boost-type PFC rectifiers

The three-phase PFC rectifier systems are classified into hybrid and fully active pulsewidth modulation boost-type and buck-type. This section will focus on the boost-type rectifiers since the Belgian rectifier falls in that category. As can be seen in Fig.1.1, the stages of the power supply to high-power electrical systems such as EV batteries, is executed in two steps, i.e., the rectification and boosting of the AC voltage is conducted by the PFC rectifier and the adaptation of the DC voltage to the load is performed by a DC-DC converter like the DAB which provides galvanic isolation.[12]

In the main objectives of a PFC rectifier, except rectifying the AC voltage to DC, is to draw sinusoidal current from each phase with the same phase as the voltages and with minimal high-frequency distortion. That said, the power factor  $\lambda$ , the fundamental current-to-voltage displacement factor  $cos(\Phi)$  and

6 2. Literature review

Figure 2.1: AC side phase voltage  $v_{ph}$  and phase current  $i_{ph}$  for different values of power factor  $\lambda$  and displacement factor  $\Phi$ .

Figure 2.2: Circuit topologies of (a) Six-switch boost-type PFC rectifier (bidirectional power flow) and (b) Vienna Rectifier (unidirectional power flow).

the total harmonic distortion of the input current  $THD_i$  are the factors that describe the mains behavior. The three quantities are related to each other by the equation

$$\lambda = \frac{1}{\sqrt{1 + THD_i^2}} cos(\Phi) \tag{2.1}$$

In order to limit the voltage distortions that arise from the excitation of resonances in the distribution grid or the voltage drops across the inner inductive mains impedance, a  $THD_i < 5\%$  is required in vehicle charging applications. In other applications such as aircraft power supplies, where high inner mains impedance take place anyway, the limit becomes more stringent to the level of  $THD_i < 3\%$  [12]. The  $THD_i$  can be calculated with the following equation

$$THD_{i} = \frac{\sqrt{\sum_{h_{2}}^{h_{max}} I_{h}^{2}}}{I_{1}} [\%]$$

(2.2)

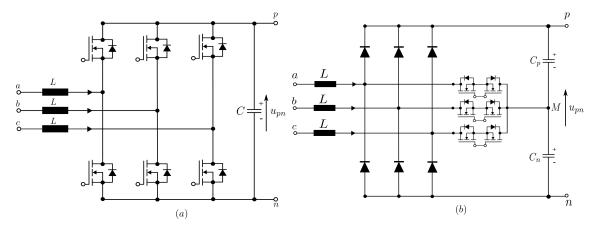

Two of the boost-type rectifiers that are extensively used in the industry are the six-switch boost PFC rectifier and the Vienna rectifier whose topologies can be seen in Fig.2.2. The two topologies that are presented in Fig.2.2 are preferred in the industry for several features, i.e., ohmic fundamental mains behavior, controlled dc output voltage that can be higher than the amplitude of the line-to-line input voltage, no galvanic isolation, circuit topology with phase/bridge symmetry [12], simple modulation and control scheme and the possibility for high efficiency. The first major difference between Vienna and six-switch boost is that the former is a 3-level rectifier and the latter is a 2-level rectifier. That said, the Vienna Rectifier(VR) provides the highest degree of freedom in modulation due to its three-level characteristic. The switching losses of VR are lower than those of six-switch boost since the commutation voltage of the transistors is half of the commutation voltage of the six-switch boost rectifier.

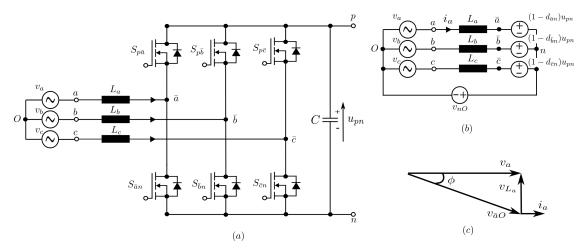

Figure 2.3: (a) Circuit topologies of six-switch boost-type PFC rectifier (bidirectional power flow), (b) Average model of the rectifier and (c) a phasor diagram for phase a.

Thereby, 650-V switches can be used for the VR instead of 1200-V switches. The main advantage of the three-level characteristic of the VR is the lower volume of the boost inductors compared to the two-level six-switch boost rectifier. On the other hand, the advantage of the six-switch boost is the simple structure of its power circuit. However, VR provides smaller volume due to its high power density [27].

#### 2.2.1. Six-switch boost PFC rectifier

In this section, the six-switch boost rectifier will be described and the average model will be derived.[3]. This rectifier is widely used in the industry because of its advantages such as high efficiency and simplicity. The topology of the active six-switch boost-type PFC rectifier that enables bidirectional power flow is shown in Fig.2.3(a). In particular, the voltage over the switches can be formed independent of the current, since for a switched-on MOSFET, the current flows through the transistor or its antiparallel diode at all times. At the bridge leg midpoint a positive or negative voltage can be generated referred to the virtual output voltage midpoint, therefore a two-level PWM voltage is applied which can facilitate the impression of sinusoidal phase currents of any displacement compared to the phase voltages. That said, the sinusoidal currents can be formed in antiphase with the phase voltages, thus achieving the opposite power flow. In that case, the topology can be used in variable speed AC machine drives and can allow to feed back the braking energy into the mains [12].

Therefore, the simplicity combined with the high performance and features such as the bidirection-ality of power flow without the need for a higher number of switches, makes the six-switch boost PFC rectifier a very appealing option for industrial applications. On the other hand, however, the fact that the full DC-bus voltage is switched is translated into high stresses on the semiconductors, as well as the need for larger passive components. The semiconductors need to have a rated voltage higher than DC-bus voltage, therefore the losses will be higher than what would be in semiconductors which are rated to half DC-bus voltage. Moreover, the switching of the full output voltage makes necessary, not only larger boost inductors, but also larger EMI filter. These facts decrease the overall performance and power density of the converter.

#### Average model:

The average model of the six-switch boost-type PFC rectifier is shown in Fig.2.3(b) [3]. Duty-cycle  $d_{\bar{a}n}$  is corresponding to switch  $S_{\bar{a}n}$ , likewise for all the other switches. The average voltages at the nodes  $\bar{a}, \bar{b}, \bar{c}$  to n are shown in (2.3).

$$\begin{cases} \langle v_{\bar{a}n} \rangle = (1 - d_{\bar{a}n}) \cdot u_{pn} \\ \langle v_{\bar{b}n} \rangle = (1 - d_{\bar{a}n}) \cdot u_{pn} \\ \langle v_{\bar{c}n} \rangle = (1 - d_{\bar{a}n}) \cdot u_{pn} \end{cases}$$

$$(2.3)$$

8 2. Literature review

The average voltage over an inductor during a switching cycle is considered to be zero  $v_L=0$ , therefore the average voltage at the nodes  $\bar{a},\bar{b},\bar{c}$  referred to O are shown in (2.4).

$$\begin{cases} \langle v_{\bar{a}O} \rangle = \langle v_a \rangle = \sqrt{2} V_{RMS} \cdot \sin(\omega t) \\ \langle v_{\bar{b}O} \rangle = \langle v_b \rangle = \sqrt{2} V_{RMS} \cdot \sin(\omega t - 120^o) \\ \langle v_{\bar{c}O} \rangle = \langle v_c \rangle = \sqrt{2} V_{RMS} \cdot \sin(\omega t + 120^o) \end{cases}$$

(2.4)

It is assumed that the three-phase system is symmetric, thus

$$v_a + v_b + v_c = 0 = > \langle v_{\bar{q}0} \rangle + \langle v_{\bar{p}0} \rangle + \langle v_{\bar{c}0} \rangle = 0$$

(2.5)

Now, the voltages at nodes  $\bar{a}, \bar{b}, \bar{c}$  referred to the neutral point, are derived from the voltage law in a closed loop as follows

$$\begin{cases} \langle v_{\bar{a}O} \rangle = \langle v_{\bar{a}n} \rangle + \langle v_{nO} \rangle \\ \langle v_{\bar{b}O} \rangle = \langle v_{\bar{b}n} \rangle + \langle v_{nO} \rangle \\ \langle v_{\bar{c}O} \rangle = \langle v_{\bar{c}n} \rangle + \langle v_{nO} \rangle \end{cases}$$

(2.6)

(2.5) together with (2.6) gives

$$-\frac{1}{3}(\langle v_{\bar{a}n}\rangle + \langle v_{\bar{b}n}\rangle + \langle v_{\bar{c}n}\rangle) = \langle v_{no}\rangle$$

(2.7)

Therefore.

$$\begin{cases} \langle v_{a} \rangle = \langle v_{\bar{a}n} \rangle - \frac{1}{3} (\langle v_{\bar{a}n} \rangle + \langle v_{\bar{b}n} \rangle + \langle v_{\bar{c}n} \rangle) \\ \langle v_{b} \rangle = \langle v_{\bar{b}n} \rangle - \frac{1}{3} (\langle v_{\bar{a}n} \rangle + \langle v_{\bar{b}n} \rangle + \langle v_{\bar{c}n} \rangle) \\ \langle v_{c} \rangle = \langle v_{\bar{c}n} \rangle - \frac{1}{3} (\langle v_{\bar{a}n} \rangle + \langle v_{\bar{b}n} \rangle + \langle v_{\bar{c}n} \rangle) \end{cases}$$

$$(2.8)$$

If (2.3) is combined with (2.8), a relationship between the duty cycles and phase voltages can be derived.

$$\begin{bmatrix} -\frac{2}{3} & \frac{1}{3} & \frac{1}{3} \\ \frac{1}{3} & -\frac{2}{3} & \frac{1}{3} \\ \frac{1}{3} & \frac{1}{3} & -\frac{2}{3} \end{bmatrix} \cdot \begin{bmatrix} d_{\bar{a}n} \\ d_{\bar{b}n} \\ d_{\bar{c}n} \end{bmatrix} = \frac{1}{v_{pn}} \begin{bmatrix} \langle v_a \rangle \\ \langle v_b \rangle \\ \langle v_c \rangle \end{bmatrix}$$

(2.9)

(2.9) relates the average duty cycle ratio of the switches to the line voltages. There are infinite solutions to this equation, therefore a possible solution can be:

$$\begin{cases}

d_{\bar{a}n} = K_1 + K_2 \cdot \frac{\langle v_a \rangle}{v_{pn}} \\

d_{\bar{b}n} = K_1 + K_2 \cdot \frac{\langle v_b \rangle}{v_{pn}} \\

d_{\bar{c}n} = K_1 + K_2 \cdot \frac{\langle v_c \rangle}{v_{pn}}

\end{cases}$$

(2.10)

The parameter  $K_2 = -1$  and  $K_1$  can be chosen such that it fulfills the following condition in order to maintain the duty cycles in the range of [0,1].

$$0 \le d_{\bar{a}n} = K_1 - \frac{\langle v_a \rangle}{v_{pn}} \le 1 \tag{2.11}$$

From the above equation, the parameter  $K_1$  is 0.5 for a LF common-mode voltage  $\langle v_{no} \rangle = 0$ . Therefore, the duty cycle and phase voltage relation is the following:

$$\begin{cases} d_{\bar{a}n} = 0.5 - \frac{\langle v_a \rangle}{v_{pn}} \\ d_{\bar{b}n} = 0.5 - \frac{\langle v_b \rangle}{v_{pn}} \\ d_{\bar{c}n} = 0.5 - \frac{\langle v_c \rangle}{v_{pn}} \end{cases}$$

$$(2.12)$$

## 2.3. Zero-voltage switching

SiC MOSFETS and GaN HEMTs have facilitated an increase of the performance of power electronics in general because of the enhanced figure-of-merit [10].

$$FOM = \frac{1}{\sqrt{R_{DS,on} \cdot C_{oss}}} \tag{2.13}$$

Despite the improved performance that these wide-bandgap semiconductors provide, the switching losses increase as the frequency increases, thus it constitutes a limiting factor even for these semiconductors. Therefore, soft-switching is often preferred and, for the design and optimization of a converter, it is important to identify the conditions under which soft switching (i.e. by means of zero-voltage switching) can be achieved.

Figure 2.4: Soft-switching transition of a MOSFET bridge leg: (a) Switch  $S_2$  on and inductor current  $i_L = I_{switch}$ ; (b) switch  $S_2$  turns off and resonant transition initiates with added current path through the voltage source; (c)  $v_2$  has reached the  $V_{in}$  and switch  $S_1$  turns on at zero voltage.

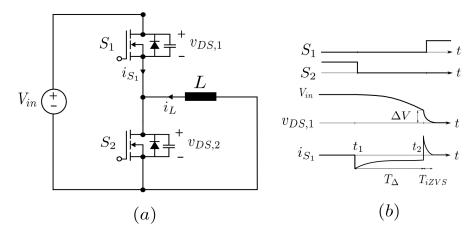

The ZVS process where the switch  $S_2$  turns off and switch  $S_1$  turns on can be seen in Fig.2.4. In order to achieve soft switching the following energy balance has to be valid as can be seen in (2.14) [17].

$$E_{init} + E_{del} = E_{final} + E_{diss} ag{2.14}$$

where  $E_{init}$  is the energy within the system before  $t_1$ ,  $E_{final}$  is the energy after the switching took place,  $E_{del}$  is the energy delivered by the source and  $E_{diss}$  is the energy dissipated during the ZVS - it is considered zero for full softswitching.

$$t < t_1$$

:

As can be seen in Fig.2.4(a), before the switching transition starts happening, the current of the inductor is free-wheeling through switch  $S_2$  which is on. The output capacitance of the switch  $S_1$  is charged to the source voltage  $V_{in}$ . Therefore, the system energy is defined by the energy stored in the inductor L and the paracitic capacitance as follows:

$$E_{init} = E_{oss}(V_{in}) + \frac{1}{2}LI_{switch}^{2}$$

(2.15)

$$t_1 < t < t_2$$

:

When the switch  $S_2$  turns off, the inductor current starts flowing to both parasitic capacitances of the switches  $S_1$  and  $S_2$ , thus discharging the

capacitance  $C_{oss,1}$  and charging  $C_{oss,2}$ . Since both switches of the bridge are assumed to have the same parasitic capacitances, the charging/discharging is considered to finish at the same time  $t_2$  when the inductor current reaches  $i_L = 0A$ . In order to achieve full ZVS, switch  $S_1$  has to be turned on after the corresponding parasitic capacitance has been fully discharged. This resonant transition is illustrated in Fig.2.4(b). That said, the system energy after the transition is:

$$E_{final} = E_{oss}(V_{in}) (2.16)$$

and the energy that was delivered from the source  $V_{in}$  is:

$$E_{del} = -Q_{oss}(V_{in}) \times V_{in} \tag{2.17}$$

10 2. Literature review

$t > t_2$ :

Therefore, in order to accomplish full ZVS the following relation has to be valid:

$$\frac{1}{2}LI_{switch}^2 \ge Q_{oss}(V_{in}) \times V_{in}$$

(2.18)

In other words, for a constant dead-time that is defined beforehand, the current has to be sufficiently negative to discharge fully the parasitic capacitance of the switch which is turning on [17].

## 2.4. Summary

In this section, a literature review of the relevant topics regarding the three-phase boost type PFC rectifiers is given. Starting from the main objectives of the PFC rectifiers, two of the most widely used boost topologies, namely the six-switch boost and the Vienna Rectifier are briefly explained to introduce the reader to this category of converters. The average model of the six-switch rectifier is derived.

Furthermore, the concept of zero-voltage switching is explained by giving an example of a bridge-leg with a voltage source and an inductor whose current is assumed to go to zero.

# The Belgian rectifier

### 3.1. Introduction

In this chapter, the Belgian Rectifier is described in detail. Starting from the structure of this novel topology, its separate parts are presented and explained in terms of functionality and operation. Furthermore, the conduction states of this rectifier are shown and information is provided of why this topology is classified as a three-level PFC rectifier. To continue with, two modulation schemes are examined, the average model for these modulations is formulated mathematically and the duty-cycles are derived. One of the modulation schemes is selected and its advantages are presented. Finally, the component stresses of the semiconductors, soft-switching capabilities are shown and the advantages/disadvantages of the Belgian Rectifier are analysed.

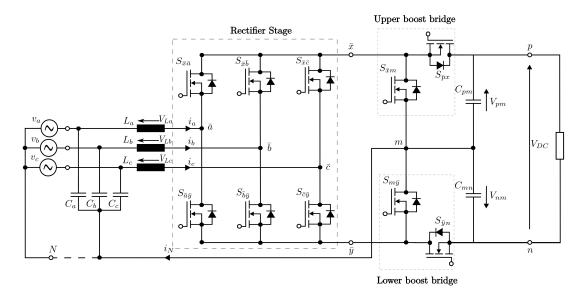

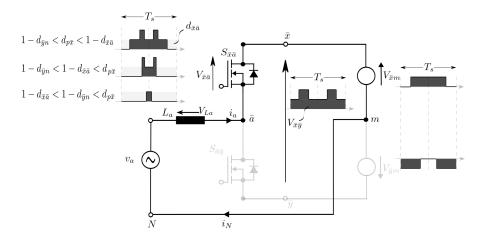

#### 3.2. Structure

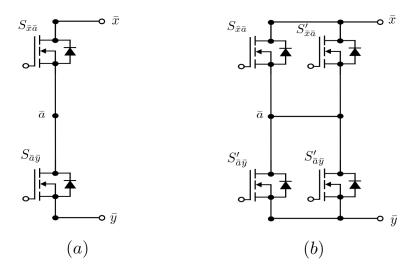

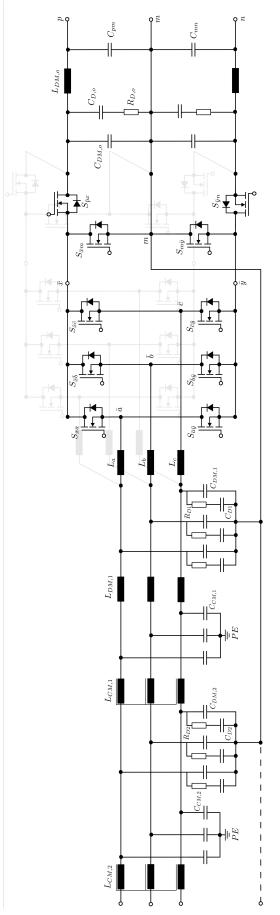

In Fig.3.2, the topology of the Belgian Rectifier is presented. Starting from the left of the topology, there are three boost inductors that are part of a boost circuit which is virtually integrated with a three phase bridge rectifier stage to allow the formation of a pulsed voltage at the rectifier output. The topology consists of ten switching elements (e.g. MOSFETs) which are actively or semi-actively controlled, six of them being part of the semi-active rectifier stage and four of them being part of the top and bottom active boost converters.[6]

#### **Boost bridges:**

The boost circuit semiconductor switches  $S_{p\bar{x}}$ ,  $S_{\bar{x}m}$ ,  $S_{m\bar{y}}$ ,  $S_{\bar{y}n}$  are actively controlled in order to obtain a switched voltage between 0 V and half DC bus voltage of the corresponding capacitor. This facilitates to control the current of two out of three phases, the ones that have the highest and lowest voltage levels. The top and bottom converters can be analyzed independently and their task is to provide the average voltages  $\langle v_{\bar{x}m} \rangle$  and  $\langle v_{\bar{y}m} \rangle$  that can be seen in Fig. 3.3.

#### Rectifier stage:

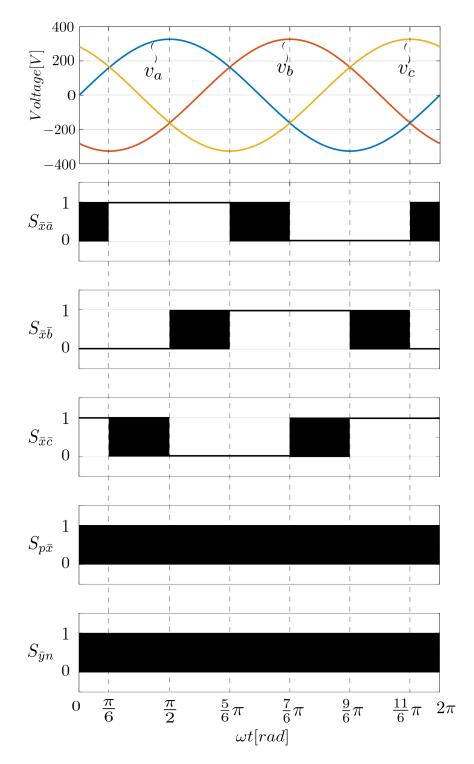

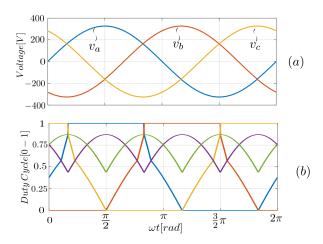

The rectifier stage consists of three bridge-legs  $S_{\bar{x}\bar{a}}$ ,  $S_{\bar{a}\bar{y}}$ ,  $S_{\bar{x}\bar{b}}$ ,  $S_{\bar{b}\bar{y}}$ ,  $S_{\bar{x}\bar{c}}$ ,  $S_{\bar{c}\bar{y}}$ , with each phase connected to the corresponding midpoint  $\bar{a}$ ,  $\bar{b}$ ,  $\bar{c}$ . As mentioned above, the current of two out of three phases with the highest and lowest voltage are controlled by the active boost circuits. The corresponding bridge legs of the rectifier connected to the three-phase input voltage are in selection state. In Fig. 3.1, in the interval  $[\frac{\pi}{2}, \frac{5}{6}\pi]$ , phases A and C have the highest and lowest voltages, respectively. The remaining bridge leg is connected to the third phase which has an intermediate voltage level (phase B in the same interval in Fig.3.1) between the highest and lowest voltages and is actively controlled by PWM modulation in contrary to the other two bridge legs of the rectifier stage.

#### **Boost Inductors:**

Figure 3.1: Phase voltages and switching states (PWM signals) during a  $2\pi$  period of the AC mains voltage.

3.2. Structure

Figure 3.2: Topology of the Belgian Rectifier.

The boost inductors are located between the three-phase AC mains and the rectifier stage. The fact that they are not located after the rectification stage gives the flexibility to exploit the pulsed voltage for the current control to the maximum. It should be noted that the controlling voltage over the inductor is half the DC bus voltage for the phases in selection state and multi-level voltage for the phase with intermediate voltage. This allows for smaller inductors to be used since less magnetic energy is needed to be stored compared to the conventional six-switch boost rectifier.

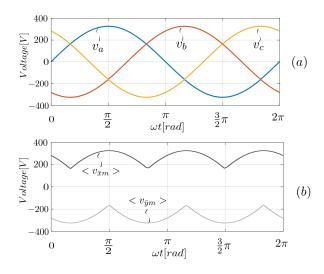

Figure 3.3: (a) Input three-phase AC voltage (b) Average voltages  $\langle v_{\bar{x}m} \rangle$ ,  $\langle v_{\bar{y}m} \rangle$ .

Moreover, an advantage of the Belgian Rectifier is that the boost circuits are actively switching the voltages  $v_{pm}$  and  $v_{nm}$  which are half the DC bus in contrary to the six-switch boost-type rectifier whose bridge legs are actively switching the full DC bus.

#### 3.2.1. Conduction states

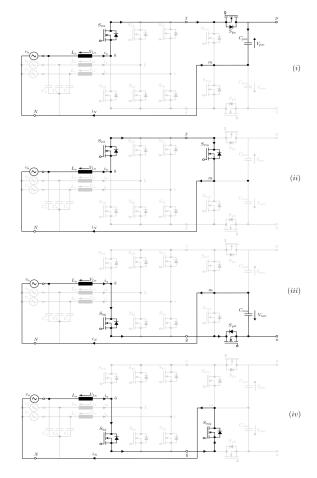

The conduction states of only phase A are shown in Fig.3.4. It can be assumed that the same conduction states are possible for phases B, C and their respective bridge legs in the rectifier stage. As can be seen in Fig.3.4, there are four possible conduction states for phase A. When the top switch  $S_{\bar{\chi}\bar{a}}$  is on, the voltage over the inductor  $L_a$  is determined by the switched voltage  $v_{\bar{\chi}m}$  which can either be 0 V or  $v_{pm}$ , as well as by the phase voltage  $v_{mN}$ .

When the bottom switch  $S_{\bar{a}\bar{y}}$  is on, the voltage over the inductor is dependent on the switched voltage  $v_{\bar{y}m}$  which can either be 0V or  $v_{nm}$ , the phase voltage  $v_a$  and LF common-mode voltage  $v_{mN}$ . It is obvious at this point that the voltage at the midpoint  $v_{\bar{a}m}$  can have three possible values, namely  $v_{\bar{a}m} = v_{nm} = -\frac{v_{DC}}{2}$ ,  $v_{\bar{a}m} = 0$  and  $v_{\bar{a}m} = v_{pm} = \frac{v_{DC}}{2}$ . Therefore, the Belgian Rectifier is a three-level rectifier and enjoys low ripple and component stresses.

Figure 3.4: Possible conduction states considering only phase A.

It is assumed that the voltage  $v_{mN}$  is zero, so that the analysis is more clear for the reader.

$$v_{mN} = 0 \tag{3.1}$$

The voltage over the inductor  $L_a$  for different conduction states is the following:

$$\begin{cases} v_{L_a} = v_a - v_{pm} & \text{for state } (i) \\ v_{L_a} = v_a & \text{for states } (ii), (iv) \\ v_{L_a} = v_a - v_{nm} & \text{for state } (iii) \end{cases}$$

(3.2)

## 3.3. Average model

To derive an average model for the Belgian Rectifier, certain assumption have to be Firstly, the switching frequency  $f_{sw}$ of the semiconductors is considered high frequency (HF) whereas the grid frequency  $f_{grid}$ is considered to be low frequency (LF). Moreover, HF is considered to be much higher than LF  $f_{sw}$ >>  $f_{grid}$ . Therefore, it can be assumed that in a switching cycle, the average voltage over an inductor is zero The methodology that is fol- $\langle v_L \rangle = 0.$ lowed in this mathematical approach starts from the boost circuits and later continues to the rectifier stage. Hence, the boost circuits are the first ones to be analysed in steadystate.

#### **Boost Circuit:**

As aforementioned, the top and bottom boost circuit can be analysed independently from each other. As can be seen in Fig.3.3, the rectified av-

erage voltages  $v_{\bar{x}m}$  and  $v_{\bar{y}m}$  can be defined as follows:

$$\begin{cases} \langle v_{\bar{x}m} \rangle = max(v_a, v_b, v_c) \\ \langle v_{\bar{y}m} \rangle = min(v_a, v_b, v_c) \end{cases}$$

(3.3)

The switching-cycle-averaged values are the following:

$$\begin{cases} v_{pm} = \langle v_{pm} \rangle \\ v_{nm} = \langle v_{nm} \rangle \\ v_{pn} = \langle v_{pn} \rangle = V_{DC} \end{cases}$$

(3.4)

The output DC bus voltage and the separate voltages of bulk capacitors  $v_{pm}$  and  $v_{mn}$ , can be related to the rectified voltages  $v_{\bar{x}m}$  and  $v_{\bar{y}m}$  through the duty cycles as follows:

$$\begin{cases} v_{pm} \cdot d_{p\bar{x}} = \langle v_{\bar{x}m} \rangle \\ v_{nm} \cdot d_{\bar{y}n} = \langle v_{\bar{y}m} \rangle \end{cases}$$

(3.5)

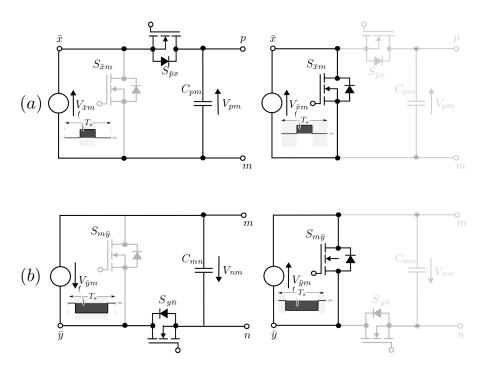

As can be seen in Fig.3.5(a), the voltage  $v_{\bar{x}m}$  is a switched voltage with two levels, 0 V and  $v_{pm}$ . The average voltage  $\langle v_{\bar{x}m} \rangle$  is defined from the duty cycle of the top boost circuit. Voltage  $v_{\bar{y}m}$  (See Fig.3.5(b)) is a switched voltage with two levels as well, specifically 0 V and  $v_{nm}$ . Therefore, the boost circuits are

3.3. Average model 15

Figure 3.5: Switched voltage that is formed by the (a) top boost circuit on the nodes  $\bar{x} - m$  and (b) bottom boost circuit on the nodes  $\bar{y} - m$ .

completely independent and are analysed as such.

Until this point of the analysis, the average model does not depend on the modulation and the phase shift of the PWM pulses, but later in the analysis, these factors contribute to the formulation of different average models and derivation of different duty cycles, particularly for the rectifier bridge leg that is in active PWM switching, which is the case when the corresponding phase voltage is the intermediate voltage. Therefore, two modulations with triangular carrier are examined, only one is chosen and its advantages over the other are pointed out.

#### 3.3.1. Modulation 1

In this section, the modulation is explained by considering only phase A, because the same applies to the other phases with a phase shift of  $120^o$ . As can be seen in Fig.3.6, the voltage at the output nodes  $\bar{x}$  and  $\bar{y}$  of the rectifier stage is the subtraction of voltages  $v_{\bar{x}m}$  and  $v_{\bar{y}m}$ :

$$v_{\bar{x}\bar{y}} = v_{\bar{x}m} - v_{\bar{y}m} \tag{3.6}$$

If it assumed that the bridge leg of phase A is actively switching and its corresponding phase voltage is the intermediate voltage between the highest and lowest voltages as can be seen in the intervals  $[0,\frac{\pi}{6}]$ ,  $[\frac{5}{6}\pi,\frac{7}{6}\pi]$  and  $[\frac{11}{6}\pi,2\pi]$  in Fig.3.1. Then, the voltage over the switch  $S_{\bar{x}\bar{a}}$  is dependent on the voltage  $v_{\bar{x}\bar{y}}$  and the duty-cycle of the switch as can be seen in Fig.3.6. it is evident that there are several possible cases for the average voltage of switch  $S_{\bar{x}\bar{a}}$ , there is switching of a "switched" voltage and not an average one as it happens in other PFC topologies.

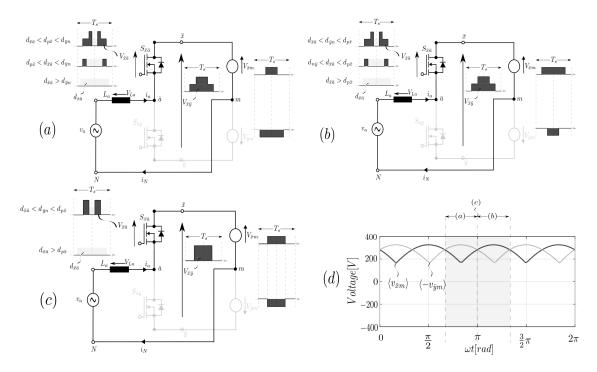

The PWM control signals of interest are the ones of switches  $S_{p\bar{x}}$ ,  $S_{\bar{y}n}$  and  $S_{\bar{x}\bar{a}}$ . In this modulation scheme, the aforementioned PWM pulses are chosen to be aligned and centered as can be seen in Fig.3.6. Three different cases/intervals can be distinguished as can be seen in Fig.3.6(d) and those are the following:

$$\begin{cases} \langle v_{\bar{x}m} \rangle < \langle -v_{\bar{y}m} \rangle & \text{in Fig.3.6 (a)} \\ \langle v_{\bar{x}m} \rangle > \langle -v_{\bar{y}m} \rangle & \text{in Fig.3.6 (b)} \\ \langle v_{\bar{x}m} \rangle = \langle -v_{\bar{y}m} \rangle & \text{in Fig.3.6 (c)} \end{cases}$$

$$(3.7)$$

Figure 3.6: Switched voltages for cases (a)  $\langle v_{\bar{x}m} \rangle < \langle -v_{\bar{y}m} \rangle$  (b)  $\langle v_{\bar{x}m} \rangle > \langle -v_{\bar{y}m} \rangle$  (c)  $\langle v_{\bar{x}m} \rangle = \langle -v_{\bar{y}m} \rangle$  and (d) the relevant intervals.

Starting from the case where  $\langle v_{\bar{x}m} \rangle < \langle -v_{\bar{y}m} \rangle$ . The average voltage over the switch  $S_{\bar{x}\bar{a}}$  depends on the duty cycle of the corresponding switch and the switched voltage of the nodes  $v_{\bar{x}\bar{y}}$ . Three states can be distinguished as can be observed in Fig.3.6(a) on the top left. The average voltage  $\langle v_{\bar{x}\bar{a}} \rangle$  in these states is:

$$\langle v_{\bar{x}\bar{a}} \rangle = \begin{cases} (d_{\bar{y}n} - d_{p\bar{x}}) \cdot v_{mn} + (d_{p\bar{x}} - d_{\bar{x}\bar{a}}) \cdot (v_{pm} + v_{mn}) & \text{for } d_{\bar{x}\bar{a}} < d_{p\bar{x}} < d_{\bar{y}n} \\ (d_{\bar{y}n} - d_{\bar{x}\bar{a}}) \cdot v_{mn} & \text{for } d_{p\bar{x}} < d_{\bar{x}\bar{a}} < d_{\bar{y}n} \\ 0 & \text{for } d_{\bar{x}\bar{a}} > d_{\bar{y}n} > d_{p\bar{x}} \end{cases}$$

(3.8)

For the second case which is depicted in Fig.3.6(b), the average voltage  $\langle v_{\bar{x}\bar{a}} \rangle$  can be calculated as follows:

$$\langle v_{\bar{x}\bar{a}} \rangle = \begin{cases} (d_{p\bar{x}} - d_{\bar{y}n}) \cdot v_{pm} + (d_{\bar{y}n} - d_{\bar{x}\bar{a}}) \cdot (v_{pm} + v_{mn}) & \text{for } d_{\bar{x}\bar{a}} < d_{\bar{y}n} < d_{p\bar{x}} \\ (d_{p\bar{x}} - d_{\bar{x}\bar{a}}) \cdot v_{pm} & \text{for } d_{\bar{y}n} < d_{\bar{x}\bar{a}} < d_{p\bar{x}} \\ 0 & \text{for } d_{\bar{x}\bar{a}} > d_{p\bar{x}} > d_{\bar{y}n} \end{cases}$$

(3.9)

Finally, for the third case which is depicted in Fig.3.6(c), the average voltage  $\langle v_{\bar{x}\bar{a}} \rangle$  can be calculated as follows:

$$\langle v_{\bar{x}\bar{a}} \rangle = \begin{cases} (d_{p\bar{x}} - d_{\bar{x}\bar{a}}) \cdot (v_{pm} + v_{mn}) & \text{for } d_{\bar{x}\bar{a}} < d_{\bar{y}n}, d_{p\bar{x}} \\ 0 & \text{for } d_{\bar{x}\bar{a}} > d_{\bar{y}n}, d_{p\bar{x}} \end{cases}$$

(3.10)

#### 3.3.2. Duty-cycle derivation

The duty cycles of the boost circuits switches  $S_{p\bar{x}}$ ,  $S_{\bar{y}n}$  are simple to derive from (3.5):

$$\begin{cases}

d_{p\bar{x}} = \frac{\langle v_{\bar{x}m} \rangle}{v_{pm}} \\

d_{\bar{y}m} = \frac{\langle v_{\bar{y}m} \rangle}{v_{nm}}

\end{cases}$$

(3.11)

To calculate the duty cycle of switch  $S_{\bar{x}\bar{a}}$ , Kirchhoff's voltage law has to be applied in the closed-loop that is shown in Fig.3.6 as follows:

$$\langle v_{\bar{x}\bar{a}} \rangle + \langle v_a \rangle - \langle v_{\bar{x}m} \rangle = 0 \tag{3.12}$$

3.3. Average model 17

Therefore, from the equations (3.8), (3.9) and (3.10) the following cases of duty cycle  $d_{\tilde{x}\tilde{a}}$  are derived:

$$d_{\bar{\chi}\bar{a}} = \begin{cases} d_{\bar{y}n} - \frac{2(\langle v_{\bar{\chi}m} \rangle - v_a)}{v_{pm} + v_{mn}} & , \text{condition } d_{p\bar{\chi}} < d_{\bar{\chi}\bar{a}} < d_{\bar{y}n} \\ d_{p\bar{\chi}} - \frac{2(\langle v_{\bar{\chi}m} \rangle - v_a) - (d_{\bar{y}n} - d_{p\bar{\chi}}) \cdot (v_{pm} + v_{mn})}{2(v_{pm} + v_{mn})} & , \text{condition } d_{\bar{\chi}\bar{a}} < d_{p\bar{\chi}} < d_{\bar{y}n} \\ d_{p\bar{\chi}} - \frac{2(\langle v_{\bar{\chi}m} \rangle - v_a)}{v_{pm} + v_{mn}} & , \text{condition } d_{\bar{y}n} < d_{\bar{\chi}\bar{a}} < d_{p\bar{\chi}} \\ d_{\bar{y}n} - \frac{2(\langle v_{\bar{\chi}m} \rangle - v_a) - (d_{p\bar{\chi}} - d_{\bar{y}n}) \cdot (v_{pm} + v_{mn})}{2(v_{pm} + v_{mn})} & , \text{condition } d_{\bar{\chi}\bar{a}} < d_{\bar{y}n} < d_{p\bar{\chi}} \\ d_{p\bar{\chi}} - \frac{\langle v_{\bar{\chi}m} \rangle - v_a}{v_{pm} + v_{mn}} & , \text{condition } d_{\bar{\chi}\bar{a}} < d_{\bar{y}n} = d_{p\bar{\chi}} \end{cases}$$

The duty-cycle of switch  $S_{\bar{x}\bar{a}}$  can be calculated using (3.13) and only one of the conditions is true at each time instance of the grid cycle.

Figure 3.7: (a) Phase voltages (b) Duty cycles for switches  $S_{p\bar{x}}$  - purple,  $S_{\bar{y}n}$  - green,  $S_{\bar{x}\bar{a}}$  - blue,  $S_{\bar{x}\bar{b}}$  - red and  $S_{\bar{x}\bar{c}}$  - orange.

In Fig.3.7(b), the duty cycles of all relevant switches are depicted. It can be observed that the duty cycles of the bridge legs are not symmetrical and this brings a number of disadvantages to the operation of the rectifier. The main reason is that the loss distribution in the converter and the semiconductor stresses are uneven and this increases the risk of failure of several components. Moreover, the common-mode noise with unsymmetrical PWM switching is higher, thus requiring a bigger EMI filter that decreases the overall power density and performance of the rectifier. Therefore, a second triangular carrier positioning is investigated to achieve symmetrical duty cycles in the next section.

#### 3.3.3. Modulation 2

In this section, a second modulation scheme with different carrier positioning is presented and compared to the one described in the previous sec-

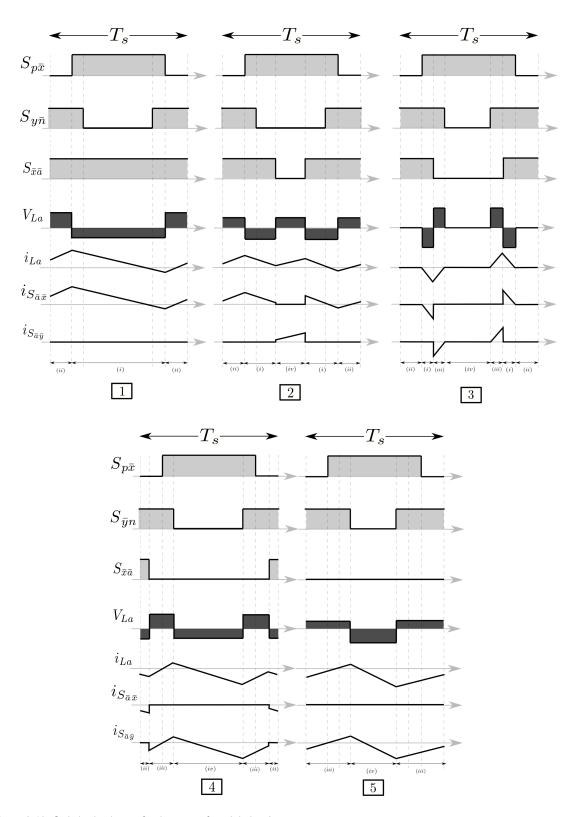

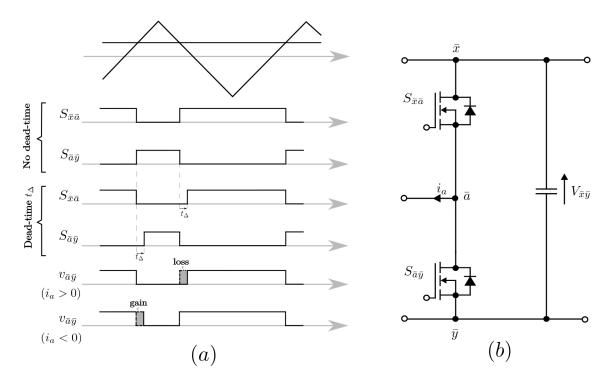

tions. The relevant PWM control pulses are again the ones of the switches  $S_{p\bar{x}}$ ,  $S_{\bar{y}n}$  and  $S_{\bar{x}\bar{a}}$ . In this modulation, the PWM carriers are centered, but the carriers of  $S_{\bar{y}n}$  and  $S_{\bar{x}\bar{a}}$  are in anti-phase compared to the carrier of  $S_{p\bar{x}}$ . This shift can be observed in Fig.3.8.

The voltage at the output nodes of the rectifier stage  $\bar{x}$  and  $\bar{y}$  is the difference of voltages  $v_{\bar{x}m}$  and  $v_{\bar{y}m}$  like in modulation 1, but in this case it is observed that the voltage only has two levels (with double frequency), rather than three. These levels are half and full DC-bus voltage. As can be observed in Fig.3.8 on the top left, the voltage over the switch  $S_{\bar{x}\bar{a}}$  is dependent on its duty cycle and the voltage  $v_{\bar{x}\bar{y}}$  that falls over that switch when it is off. Therefore, the average voltage  $v_{\bar{x}\bar{a}}$  over the switch is the following:

$$\langle v_{\bar{x}\bar{a}} \rangle = \begin{cases} (d_{\bar{y}n} - d_{\bar{x}\bar{a}}) \cdot v_{mn} + d_{p\bar{x}} \cdot v_{pm} & \text{for } 1 - d_{\bar{y}n} < d_{p\bar{x}} < 1 - d_{\bar{x}\bar{a}} \\ (1 - d_{\bar{x}\bar{a}}) \cdot v_{pm} + (d_{\bar{y}n} - d_{\bar{x}\bar{a}}) \cdot v_{mn} & \text{for } 1 - d_{\bar{y}n} < 1 - d_{\bar{x}\bar{a}} < d_{p\bar{x}} \\ (1 - d_{\bar{x}\bar{a}}) \cdot v_{pm} & \text{for } 1 - d_{\bar{x}\bar{a}} < 1 - d_{\bar{y}n} < d_{p\bar{x}} \end{cases}$$

(3.14)

#### 3.3.4. Duty-cycle derivation

As in the previous modulation, the duty cycles of the boost circuit switches  $S_{p\bar{x}}$ ,  $S_{\bar{y}n}$  are simple to derive from (3.5):

$$\begin{cases}

d_{p\bar{x}} = \frac{\langle v_{\bar{x}m} \rangle}{v_{pm}} \\

d_{\bar{y}m} = \frac{\langle v_{\bar{y}m} \rangle}{v_{nm}}

\end{cases}$$

(3.15)

Figure 3.8: Switched voltages for the case of modulation 2.

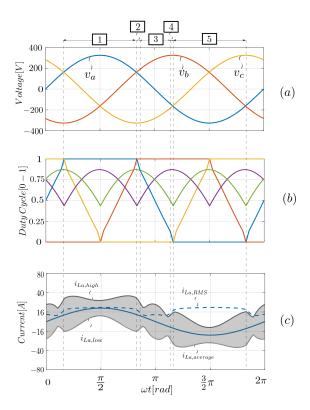

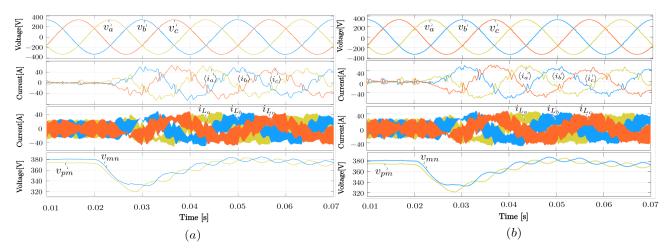

Figure 3.9: (a) Phase voltages (b) Duty cycles for switches  $S_{p\bar{\chi}}$  - purple,  $S_{\bar{\gamma}n}$  - green,  $S_{\bar{\chi}\bar{a}}$  - blue,  $S_{\bar{\chi}\bar{b}}$  - red and  $S_{\bar{\chi}\bar{c}}$  - orange (c) Inductor current for output power  $P_o=22kW$  and output voltage  $V_o=750V$ .

To calculate the duty cycle of switch  $S_{\bar{x}\bar{a}}$ , Kirchhoff's voltage law has to be applied in the closed-loop that is shown in Fig.3.8 as follows:

$$\langle v_{\bar{x}\bar{a}} \rangle = -\langle v_a \rangle + \langle v_{\bar{x}m} \rangle = C$$

(3.16)

The constant C is defined to make the duty cycle equations simpler. From (3.14) the following cases of duty cycle  $d_{\bar{x}\bar{a}}$  are derived:

$$d_{\bar{x}\bar{a}} = \begin{cases} d_{\bar{y}n} + \frac{d_{p\bar{x}} \cdot v_{pm} - C}{v_{mn}} & \text{,condition } 1 - d_{\bar{y}n} < d_{p\bar{x}} < 1 - d_{\bar{x}\bar{a}} \\ \frac{v_{pm} + d_{\bar{y}n} \cdot v_{mn} - C}{(v_{pm} + v_{mn})} & \text{,condition } 1 - d_{\bar{y}n} < 1 - d_{\bar{x}\bar{a}} < d_{p\bar{x}} \\ 1 - \frac{C}{v_{pm}} & \text{,condition } 1 - d_{\bar{x}\bar{a}} < 1 - d_{\bar{y}n} < d_{p\bar{x}} \end{cases}$$

$$(3.17)$$

In Fig.3.9(b), the duty cycles of all relevant switches for the three phases of the rectifier stage and the boost circuits are shown. The duty cycles of the boost circuit PWM pulses are the same as in modulation 1, because the carrier phase shift is not affecting them. On the other hand, the duty cycles of the rectifier stage switches are much different than the ones in modulation 1 as can be seen in Fig.3.7(b). On the contrary to the duty cycles of modulation 1, the ones of modulation 2 present a perfect symmetry which can be translated in a number of benefits. Firstly, the losses and stresses of the semiconductors are evenly distributed in the converter, thus making it more reliable and robust. Furthermore, the commonmode noise is significantly decreased, therefore the filtering requirement is also limited. That said,

the required EMI filter can be smaller which can help improve the power density of the converter. In Fig.3.9(c), the current of the inductor can be seen. The  $i_{La,high}$  and  $i_{La,low}$  are the highest and lowest values of the current for each switching cycle, respectively. Therefore, the grey area between the two waveforms is the HF switched current of the boost inductor  $L_a$  and the LF average inductor current is the  $i_{La,average}$ . The specific current is true for an inductance of  $25\mu H$  and frequency 71.7 kHz. The peak-to-peak inductor current can be increased if the inductance is smaller or if the frequency is lower. This is a way to decrease the switching losses in the converter since more zero-voltage switching is

3.3. Average model

Figure 3.10: Switched voltages for the case of modulation 2.

achieved.

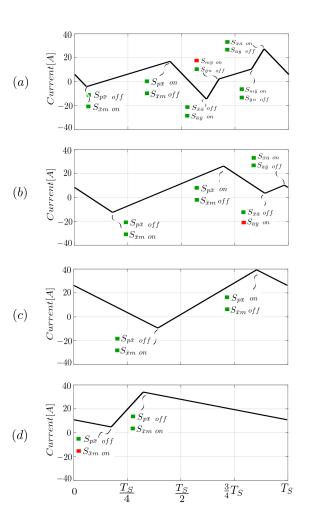

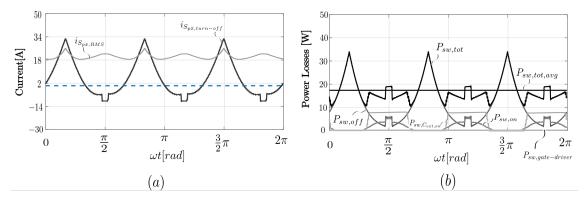

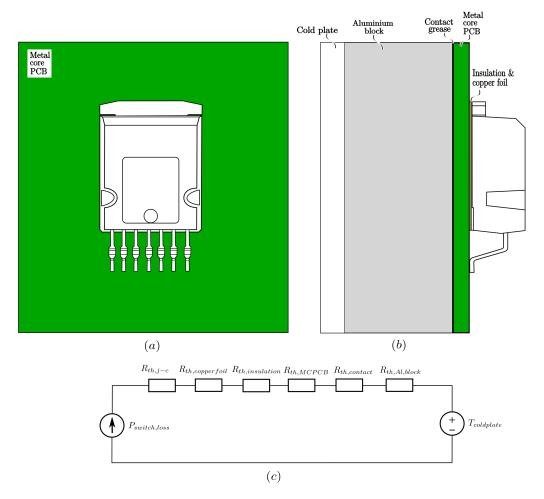

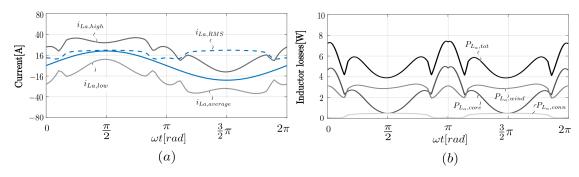

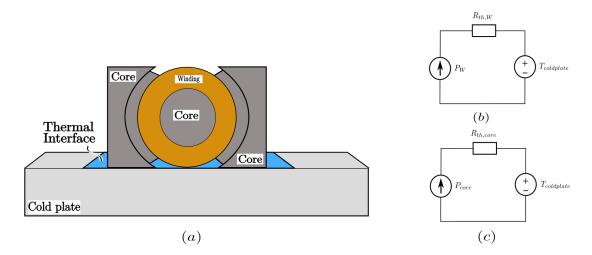

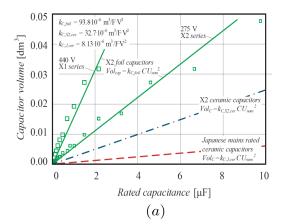

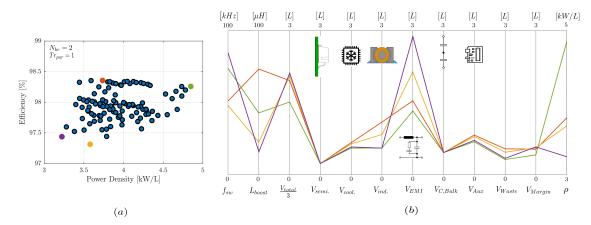

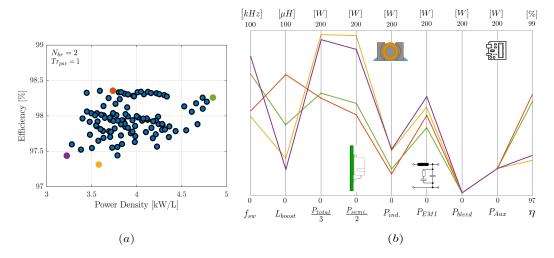

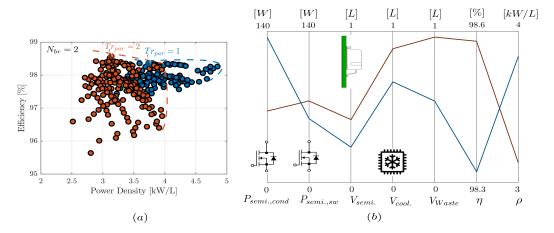

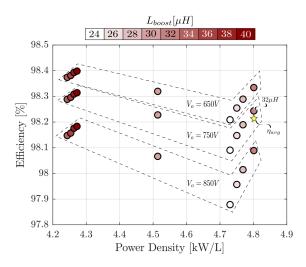

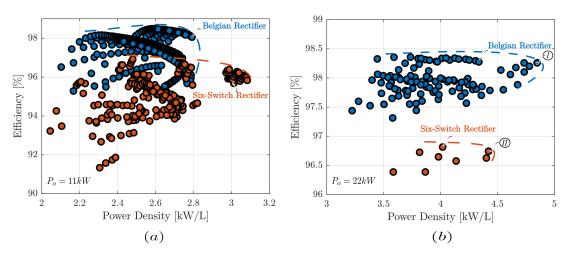

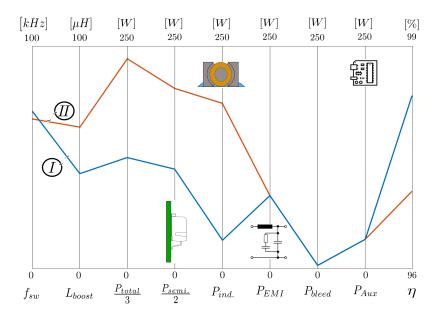

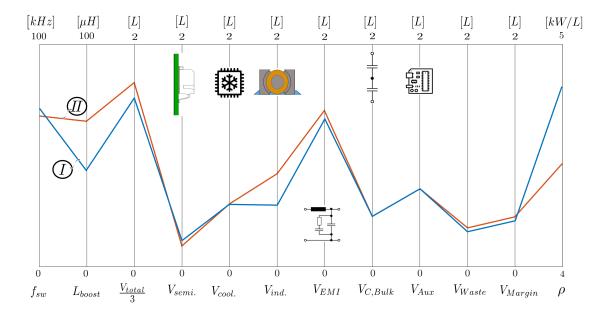

In Fig.3.10, the duty cycles, the voltage over the inductor and the current that flows the bridge leg relevant switches is shown. There are 5 cases that can be analysed and seen in Fig.3.9 and Fig. 3.10. The first case occurs when  $S_{\tilde{x}\tilde{a}}$  is constantly on in selection mode, the second case happens when  $1-d_{\tilde{x}\tilde{a}}<1-d_{\tilde{y}n}< d_{p\tilde{x}}$  is true, the third case appears when  $1-d_{\tilde{y}n}<1-d_{\tilde{x}\tilde{a}}< d_{p\tilde{x}}$  is true, the forth case takes place when  $1-d_{\tilde{y}n}< d_{p\tilde{x}}<1-d_{\tilde{x}\tilde{a}}$  is true and the fifth case arises when  $S_{\tilde{x}\tilde{a}}$  is constantly off in selection mode. Moreover, in the bottom of the waveforms of each case, the conduction state of the switches is indicated as it is specified in Fig.3.4.