# Control Strategy in Parallel AC-DC Re-configurable Links System

# Control Strategy in Parallel AC-DC Re-configurable Links System

A thesis submitted to the Delft University of Technology in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Power Engineering

by

Yang Wu

August 2019

Yang Wu: Control Strategy in Parallel AC-DC Re-configurable Links System (2019)

The work in this thesis was made in the:

DEC&S Group

Department of Electrical Sustainable Energy

Faculty of Electrical Engineering, Mathematics & Computer

Science

Delft University of Technology

Supervisors: Prof.dr. Pavol Bauer

Dr. Thiago Batista Soeiro

Aditya Shekhar

Thesis Committee: Prof.dr. Pavol Bauer DCE&S Group

Dr. Thiago Batista Soeiro DCE&S Group Dr.ir. Jose Rueda Torres IEPG Group

## **ABSTRACT**

Recent studies have shown that energy distribution systems based on hybrid (or parallel) point-to-point AC and DC links are interesting solutions for capacity enhancement and on-line improvement of energy efficiency under specific operating conditions, particularly for high power, medium to high voltage levels and long-enough distances, e.g. > 5 km. Additionally, due to the power controlability provided by the power electronic circuits within the DC links the parallel distribution system can be re-configured through GIS disconnectors operating with improved switching performance. In this work this feature is explored and strategies for the system re-configurations are proposed. These aim to provide a nearly zero current switching for the GIS in order to prevent its deterioration and to extend the number of maneuvers for the typical GIS lifetime.

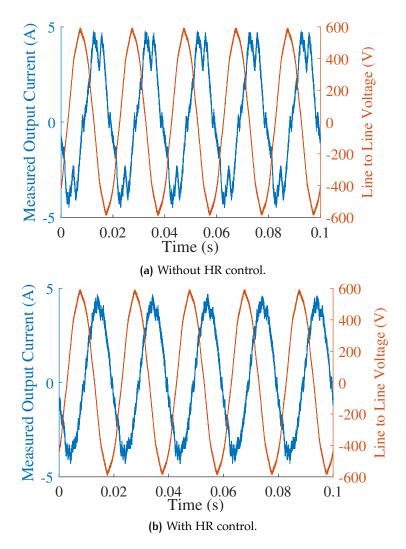

In fact, the proposed re-configuration strategies rely on the DC bus voltage and power controls of a Back-to-Back (B2B) power electronic system constructed with Voltage Source Converters (VSC). Herein, three-wire three-phase two-level VSCs with thrid-order AC harmonic filters (or LCL filter) are adopted in the B2B system. Moreover, Grid-side Current Controls (GCC) for the inner/fast control loops of the front- and back-end circuits are implemented in order to enhance the system performance against grid disturbances. Herein, a notch filter-based GCC scheme with a harmonic rejection control is proposed. This is able to deliver attenuation to the LCL filter resonances while suppressing the harmonics in the grid-side currents originated when the AC voltages are distorted. Interestingly, the parallel AC and DC links provides a low impedance path for the zero-sequence components which can be created by the power electronics, thus the implementation of a Zero-sequence Circulating Current (ZSCC) controller becomes necessary for the proper operation of the system. Hence, ZSCC controllers for the VSCs are used, while both front- and back-end circuits are modulated with constant switching frequency using the conventional sinusoidal PWM strategy.

All in all, results are obtained in both, computational simulations carried out in MAT-LAB/SIMULINK and laboratory experiments performed in a 5 kVA VSC or a B2B circuit, are used to verify the study and to prove the superior performance of the investigated and proposed technical concepts. Herein, more specifically for the re-configuration study of the parallel AC and DC links, the standalone mode control of the receiving-end VSC in the full DC link configuration is investigated and the smooth transition between grid-connected and standalone modes are realized in both simulation and experimental tests.

## ACKNOWLEDGEMENTS

The thesis work has been conducted throughout the 9 months of my MSc thesis and it has been of great significance to me. It has been a fruitful time where I was able to publish my first academic paper. Additionally, I have learned to be more inquisitive and to enjoy the research on power electronics and its feedback control strategy. I particularly value the help from the experienced people that I had the opportunity to work with. The technical discussions and hands-on activities have definitely help me to grow from an academic and practice standpoints.

First of all, I would like to thank Professor Dr. Pavol Bauer for giving me the opportunity to work on this interesting project. Particularly, I would like to thank Dr. Thiago Batista Soeiro, my daily supervisor, who was always open to help me with my questions, and was able to guide me with full enthusiasm and patience.

To Aditya Shekhar, thank you for your academic support and advice since my first project in the group. I am inspired by your ability to concurrently master technical and writing skills, and especially your capability to produce high quality research. Above all, I would like to take you as a model for my future Ph.D career.

Also, I would like to thank the laboratory technicians, especially Harrie Olsthoorn and Joris Koeners. I really appreciate your patient guidance towards me since my first days in the laboratory.

Finally, I must express my very profound gratitude to my parents for supporting me mentally and financially throughout my life, especially the last two years. This accomplishment would not have been possible without them. Thank you.

Yang Wu Delft, Netherlands August 2019

## CONTENTS

| 1 | INTRODUCTION 1                                                     |                                                                           |    |  |  |  |

|---|--------------------------------------------------------------------|---------------------------------------------------------------------------|----|--|--|--|

|   | 1.1                                                                | Motivation                                                                | 1  |  |  |  |

|   |                                                                    | 1.1.1 Hybrid AC-DC links system                                           | 1  |  |  |  |

|   |                                                                    | 1.1.2 Parallel AC and DC Re-configurable Links                            | 2  |  |  |  |

|   |                                                                    | 1.1.3 Re-configuration Strategy                                           | 3  |  |  |  |

|   |                                                                    | 1.1.4 Control of LCL-filtered VSC under Grid Voltage Distortion Condition | 4  |  |  |  |

|   | 1.2                                                                | Specific Objectives                                                       | 4  |  |  |  |

|   | 1.3                                                                | Research Questions and Challenges                                         | 4  |  |  |  |

|   | 1.4                                                                | Main Contributions                                                        | 6  |  |  |  |

|   | 1.5                                                                | Thesis Structure                                                          | 6  |  |  |  |

|   | 1.6                                                                | List of Publications                                                      | 7  |  |  |  |

| 2 | CON                                                                | TROL OF GRID CONNECTED TWO-LEVEL VSC                                      | 8  |  |  |  |

|   | 2.1                                                                | Two-level Voltage Source Converter                                        | 8  |  |  |  |

|   |                                                                    | 2.1.1 Circuitry Structure                                                 | 8  |  |  |  |

|   |                                                                    | 2.1.2 Principles of Operation                                             | 9  |  |  |  |

|   | 2.2                                                                | Model and Control of Grid-connected Two-Level VSC                         | 12 |  |  |  |

|   |                                                                    | 2.2.1 Model in <i>dq</i> – Frame                                          | 12 |  |  |  |

|   |                                                                    | 2.2.2 Control of Grid-connected Three-Phase 2-level VSC                   | 14 |  |  |  |

| 3 | CONTROLLER DESIGN FOR LCL-FILTERED VSC WITH DISTORTED GRID VOLTAGE |                                                                           |    |  |  |  |

|   | 3.1                                                                | Control of LCL-filtered VSC                                               | 29 |  |  |  |

|   |                                                                    | 3.1.1 Influence of LCL Filter                                             | 29 |  |  |  |

|   |                                                                    |                                                                           | 32 |  |  |  |

|   |                                                                    | 3.1.3 Resonance Damping of LCL filter                                     | 35 |  |  |  |

|   |                                                                    | 3.1.4 Controller parameters design                                        | 42 |  |  |  |

|   | 3.2                                                                | Harmonics mitigation in grid-side current under distorted grid voltage    | 53 |  |  |  |

|   |                                                                    | 3.2.1 Grid Impedance Analysis                                             | 54 |  |  |  |

|   |                                                                    | 3.2.2 Harmonics Controller in <i>dq</i> Frame                             | 55 |  |  |  |

|   |                                                                    | 3.2.3 Phase Compensation                                                  | 58 |  |  |  |

|   | 3.3                                                                | Experimental Results                                                      | 64 |  |  |  |

|   |                                                                    | 3.3.1 Verification of Voltage and Power Controller in STACOM mode         | 64 |  |  |  |

|   |                                                                    | 3.3.2 Verification of Harmonics Control                                   | 64 |  |  |  |

| 4 | RE-                                                                | CONFIGURATIONS OF POINT-TO-POINT ENERGY DISTRIBUTION SYSTEM BASED         |    |  |  |  |

|   | 0 N                                                                | ON PARALLEL AC AND DC LINKS                                               |    |  |  |  |

|   | 4.1                                                                |                                                                           | 67 |  |  |  |

|   |                                                                    |                                                                           | 67 |  |  |  |

|   |                                                                    |                                                                           | 69 |  |  |  |

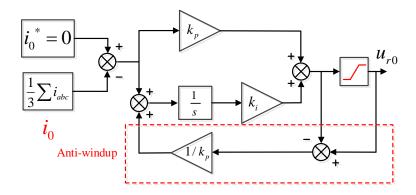

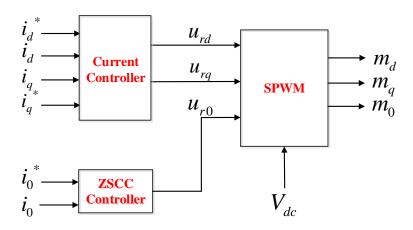

|   | 4.2                                                                | ZSCC Control in Grid-connected Back-to-Back system                        | 71 |  |  |  |

|   |                                                                    | 4.2.1 ZSCC in Parallel VSCs                                               | 71 |  |  |  |

|   |                                                                    | 4.2.2 Suppression of ZSCC                                                 | 73 |  |  |  |

|     | 4.3    | Standa  | lone mode control in Back-to-Back system                              |   | 75 |

|-----|--------|---------|-----------------------------------------------------------------------|---|----|

|     |        | 4.3.1   | Standalone Operation                                                  |   | 75 |

|     |        | 4.3.2   | Voltage Control                                                       |   |    |

|     |        | 4.3.3   | Transition from Grid-connected to Standalone mode                     |   | 77 |

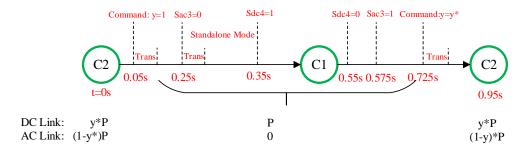

|     | 4.4    | Re-con  | figurations Strategy                                                  |   | 78 |

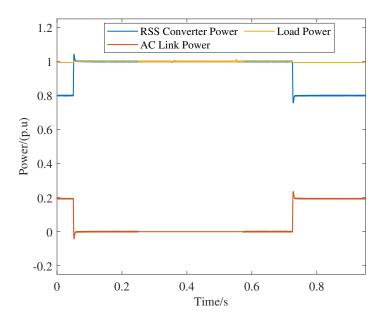

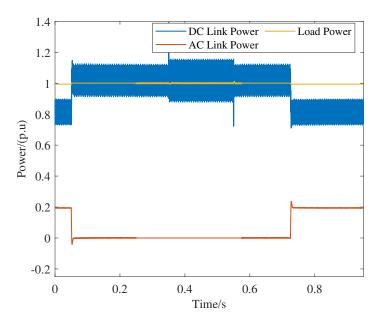

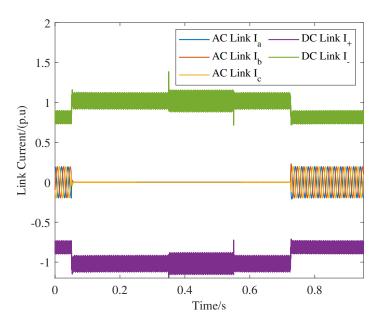

|     | 4.5    | Simula  | tion and Experimental Results                                         |   | 80 |

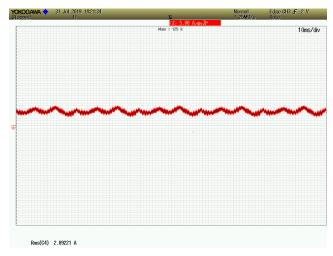

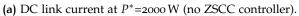

|     |        | 4.5.1   | ZSCC Control Test                                                     |   | 80 |

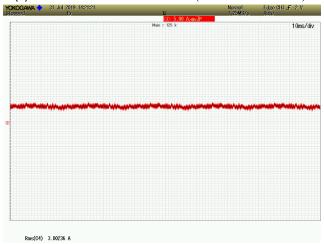

|     |        | 4.5.2   | Grid-connected B2B Test                                               |   | 80 |

|     |        | 4.5.3   | Standalone Mode Test in B2B System                                    |   | 83 |

|     |        | 4.5.4   | Verification of proposed re-configuration strategy in 9 Links System  |   | 83 |

| 5   | CON    | CLUSION | N AND FUTURE WORK                                                     |   | 93 |

|     | 5.1    | Conclu  | ısion                                                                 |   | 93 |

|     | 5.2    | Resear  | ch Questions                                                          |   | 94 |

|     | 5.3    | Future  | Work                                                                  |   | 95 |

|     |        | 5.3.1   | Improvement of the control for the VSC system                         |   | 95 |

|     |        | 5.3.2   | Experimental validation of the control strategy for re-configurations |   | 95 |

| Bil | oliogr | aphy    |                                                                       |   | 95 |

| Α   | APPI   | ENDIX   |                                                                       | 1 | 01 |

# LIST OF FIGURES

| Figure 1.1  | Basic concept of a Point-to-Point parallel AC-DC re-configurable links system | 2                               |

|-------------|-------------------------------------------------------------------------------|---------------------------------|

| Figure 1.2  | Parallel AC-DC re-configurable links system                                   | 3                               |

| Figure 2.1  | Circuity of the Two-level VSC.                                                | 9                               |

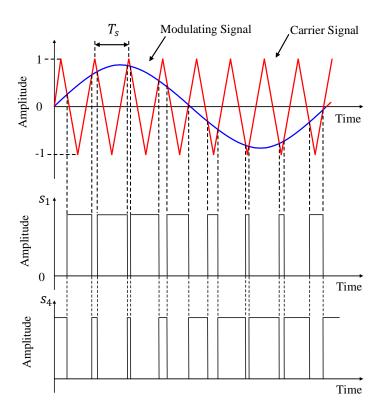

| Figure 2.2  | Signals based on the PWM switching strategy                                   | 10                              |

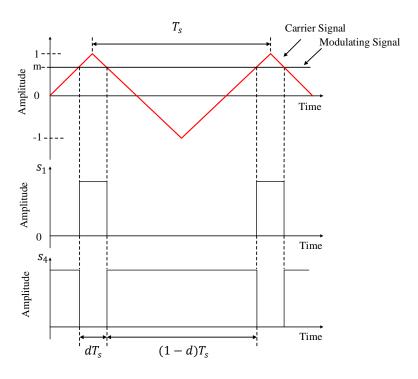

| Figure 2.3  | PWM with a constant modulating signal                                         | 11                              |

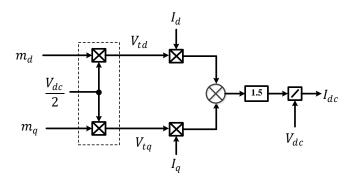

| Figure 2.4  | Control model for the ideal 2-level VSC                                       | 14                              |

| Figure 2.5  | Control diagram of a grid-connected 2-level VSC                               | 15                              |

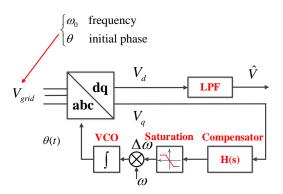

| Figure 2.6  | Schematic diagram of the conventional SRF-PLL                                 | 16                              |

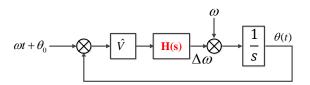

| Figure 2.7  | The closed loop transfer function of SRF-PLL                                  | 16                              |

| Figure 2.8  | Poles of the closed loop transfer function of the SRF-PLL                     | 17                              |

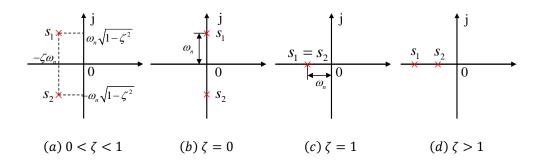

| Figure 2.9  | Bode plot of open-loop transfer function of SRF-PLL with different            | -/                              |

| Figure 2.10 | $\omega_n$                                                                    | 18                              |

| Figure 2.11 | ferent $\omega_n$                                                             | 18                              |

| Figure 2.11 | Bode plot of the open-loop transfer function of the modified SRF-             | 20                              |

| rigure 2.12 | PLL                                                                           | 21                              |

| Figure 2.13 | Bode plot of the closed loop transfer function of the modified SRF-PLL        | 21                              |

| Figure 2.14 | Dynamic response of SRF-PLL to the frequency drop of the grid voltage.        | <ul><li>21</li><li>22</li></ul> |

| Figure 2.15 | Distorted grid voltage in the simulation                                      | 22                              |

| Figure 2.16 | Simulation test of proposed SRF-PLL with $\omega_n$ =200 rad/s: output        |                                 |

| г.          | frequency.                                                                    | 23                              |

| Figure 2.17 | Simulation test of proposed SRF-PLL with $\omega_n$ =20 rad/s: output         |                                 |

| E' 0        | frequency.                                                                    | 23                              |

| Figure 2.18 | Distorted grid voltage in the experiment.                                     | 24                              |

| Figure 2.19 | Experiment test of the proposed SRF-PLL with $\omega_n$ =200 rad/s: out-      |                                 |

| г.          | put frequency.                                                                | 24                              |

| Figure 2.20 | Experiment test of the proposed SRF-PLL with $\omega_n$ =20 rad/s: out-       |                                 |

| П.          | put frequency.                                                                | 25                              |

| Figure 2.21 | Digital controller delay and PWM zero-order hold effect (single update)       | 26                              |

| Figure 2.22 | Simplified current loop transfer function                                     | 27                              |

| Figure 2.23 | Current control diagram in dq-frame                                           | 27                              |

| Figure 2.24 | DC bus voltage control loop transfer function                                 | 28                              |

| Figure 2.25 | DC bus voltage controller diagram                                             | 28                              |

| Figure 3.1  | · · · · · · · · · · · · · · · · · · ·                                         | 30                              |

| Figure 3.2  | Circuit of single-phase grid-connected VSC with LCL                           | 30                              |

| Figure 3.3  | Frequency response of the LCL filter                                          | 31                              |

| Figure 3.4  | Influence of the sampling frequency on CCC                                                            | 34 |

|-------------|-------------------------------------------------------------------------------------------------------|----|

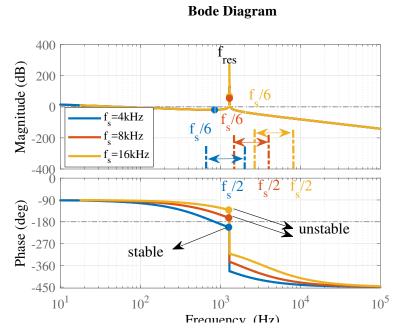

| Figure 3.5  | Influence of the sampling frequency on GCC                                                            |    |

| Figure 3.6  | Current flow of harmonics components                                                                  |    |

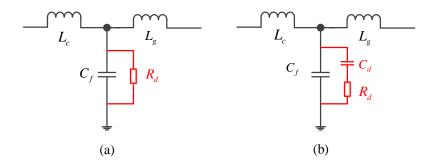

| Figure 3.7  | Exemplary of passive damping placed across $C_f$ : (a) $R_d$ (b) $R_d$ and $C_d$ .                    | 35 |

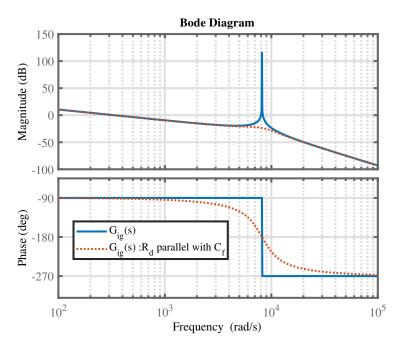

| Figure 3.8  | Bode diagram of the studied <i>LCL</i> filter with passive damping                                    | 36 |

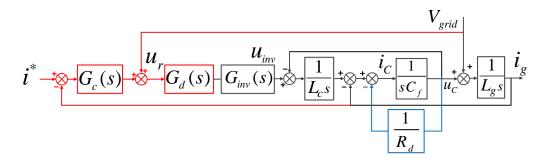

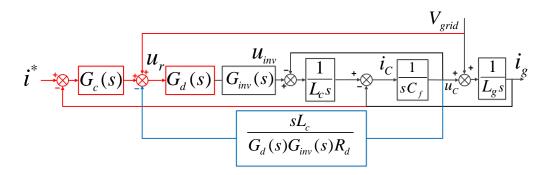

| Figure 3.9  | Current control loop with parallel damping resistor $R_d$                                             | 37 |

| Figure 3.10 | Virtual resistor $R_d$ with the capacitor voltage and current feedback.                               |    |

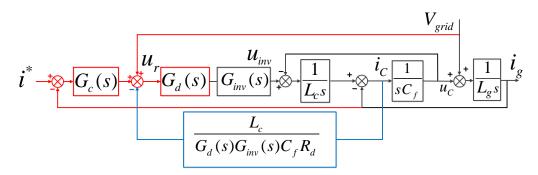

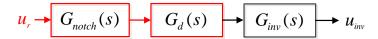

| Figure 3.11 | Notch filter added in the control loop                                                                |    |

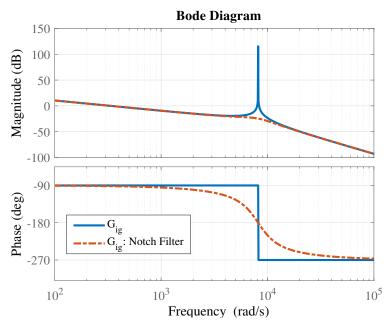

| Figure 3.12 | Bode diagram of LCL plant with notch filter                                                           |    |

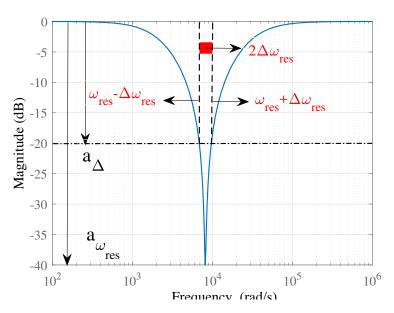

| Figure 3.13 | Design parameters of notch filter                                                                     |    |

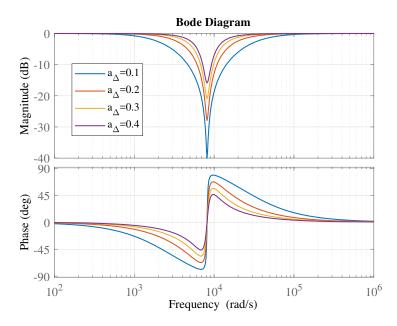

| Figure 3.14 | Influence of $a_{\Delta}$                                                                             |    |

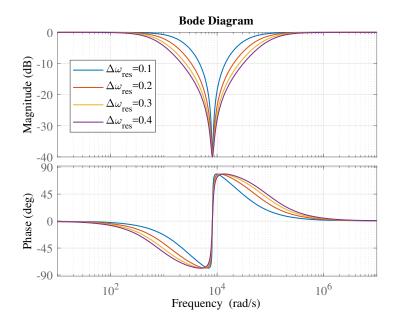

| Figure 3.15 | Influence of $\Delta_{\omega_{res}}$                                                                  | 41 |

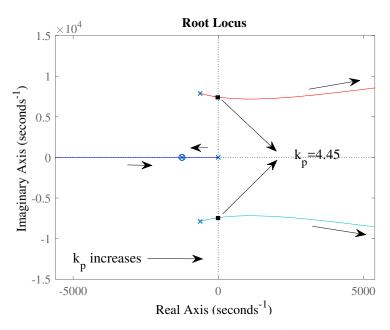

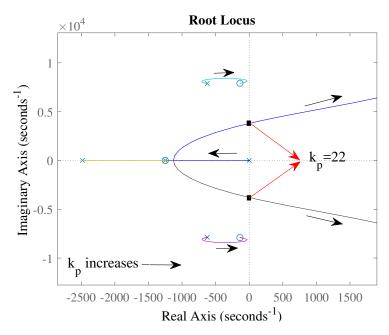

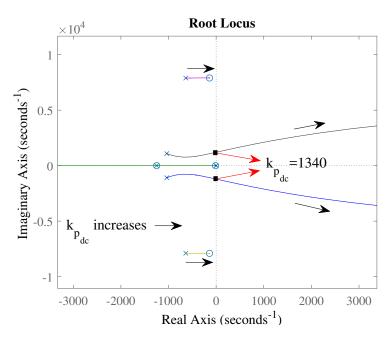

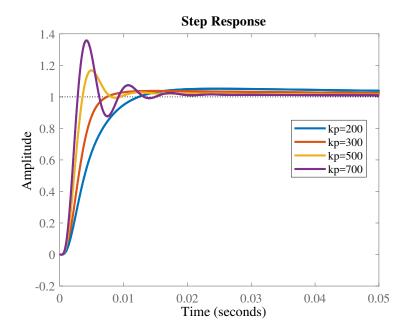

| Figure 3.16 | Root loci: current control loop                                                                       | 43 |

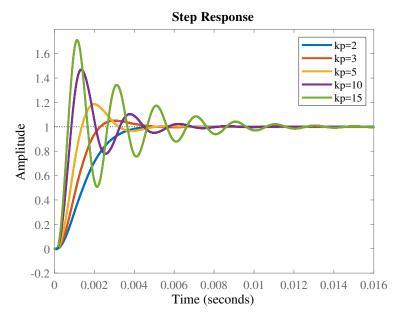

| Figure 3.17 | Step response: current control loop                                                                   | 43 |

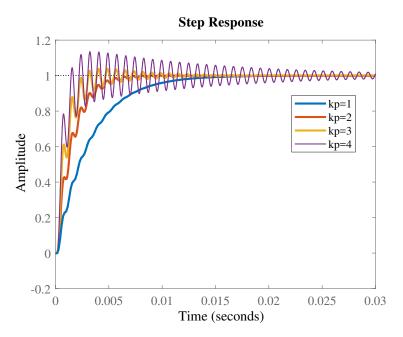

| Figure 3.18 | Root loci: voltage control loop                                                                       | 44 |

| Figure 3.19 | Step response: voltage control loop.                                                                  |    |

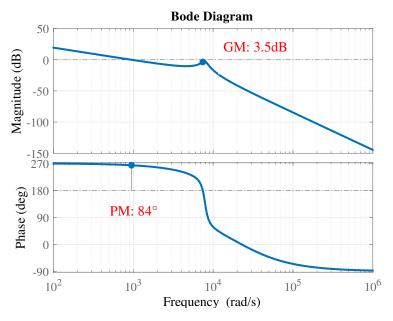

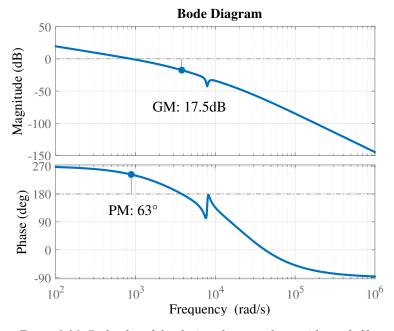

| Figure 3.20 | Bode plot of designed current loop.                                                                   | 45 |

| Figure 3.21 | Bode plot of designed voltage loop.                                                                   |    |

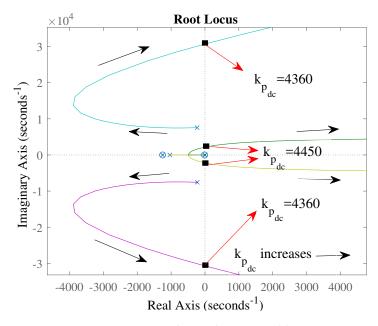

| Figure 3.22 | Root loci: current control loop with notch filter                                                     |    |

| Figure 3.23 | Step response: current control loop with notch filter                                                 |    |

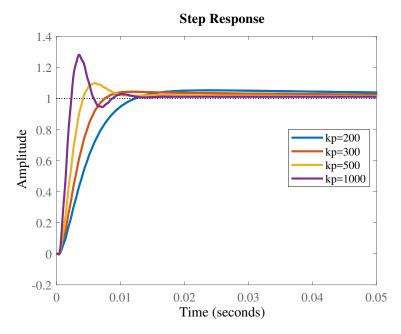

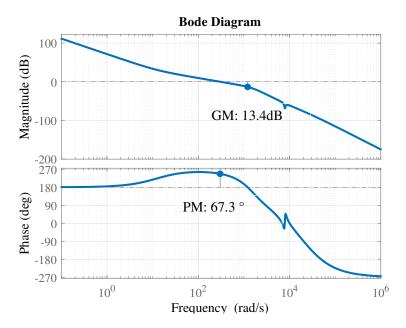

| Figure 3.24 | Root loci: voltage control loop with notch filter                                                     |    |

| Figure 3.25 | Step response: voltage control loop with notch filter                                                 |    |

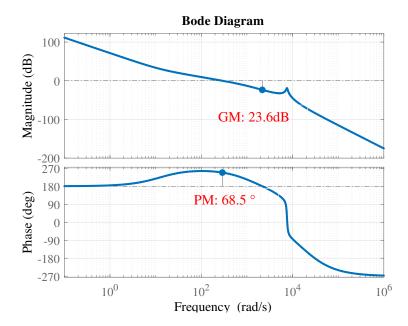

| Figure 3.26 | Bode plot of the designed current loop with notch filter                                              |    |

| Figure 3.27 | Bode plot of the designed voltage loop with notch filter                                              |    |

| Figure 3.28 | Bode plot: the closed loop system of current loop                                                     |    |

| Figure 3.29 | Bode plot: the closed loop system of voltage loop                                                     |    |

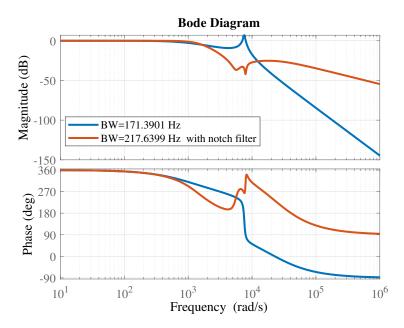

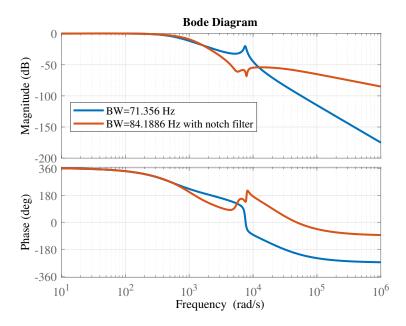

| Figure 3.30 | Influence of notch filter on stability                                                                |    |

| Figure 3.31 | Influence of notch filter on harmonics                                                                |    |

| Figure 3.32 | Phase-to-neutral grid voltage                                                                         | 53 |

| Figure 3.33 | Simplified current control structure                                                                  |    |

| Figure 3.34 | Bode plot of $Z_g$ with PR and PR+HR controller                                                       |    |

| Figure 3.35 | Control structure of PI+HR controller                                                                 |    |

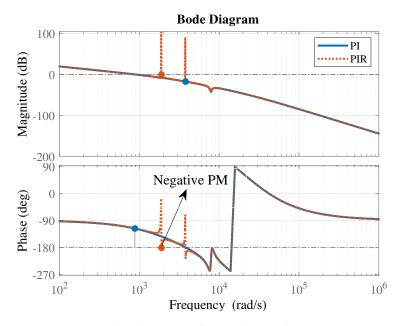

| Figure 3.36 | Bode plot: current loop with PI and PIR compensator                                                   |    |

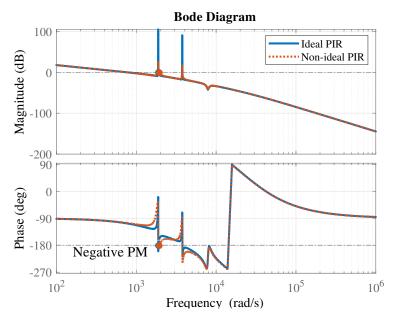

| Figure 3.37 | Bode plot: current loop with ideal and non-ideal PIR compensator                                      |    |

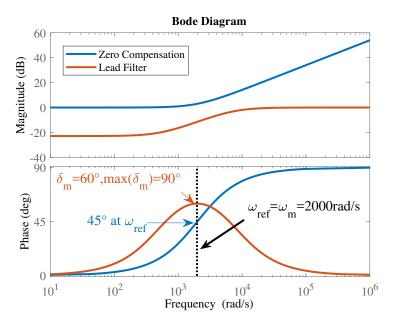

| Figure 3.38 | Bode plot: zero compensation and lead filter                                                          |    |

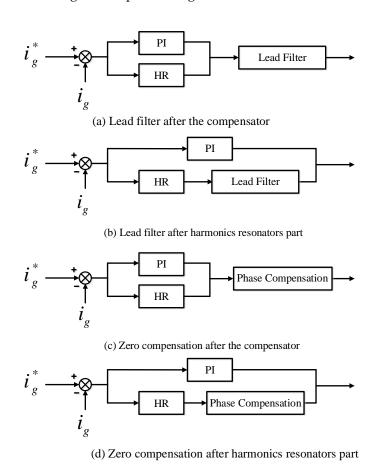

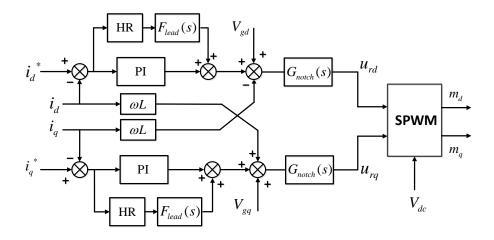

| Figure 3.39 | Structure of different phase compensation cases                                                       |    |

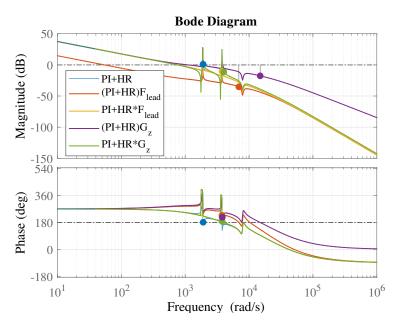

| Figure 3.40 | Bode plot: comparison between different phase compensation cases.                                     | 61 |

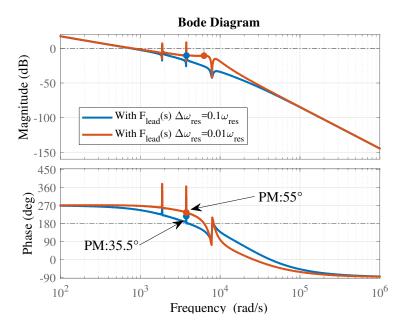

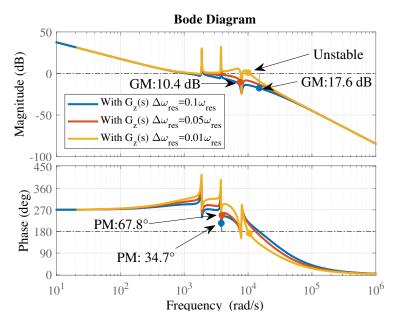

| Figure 3.41 | Bode plot: increased gain of the current loop with the lead filter at                                 |    |

| F:          | the harmonic frequencies with smaller $\Delta \omega_{res}$                                           | 62 |

| Figure 3.42 | Bode plot: increased phase margin of the current loop with the lead                                   |    |

| F:          | filter at the harmonic frequencies with smaller $\Delta \omega_{res}$                                 | 62 |

| Figure 3.43 | Complete control structure of the current loop                                                        | 63 |

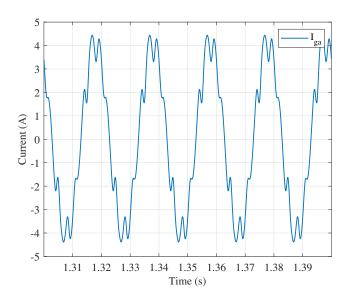

| Figure 3.44 | Grid-side current under the distorted grid (no harmonics control).                                    | 63 |

| Figure 3.45 | Grid-side current under the distorted grid (with harmonics control).                                  | 64 |

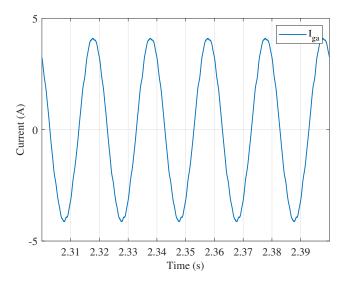

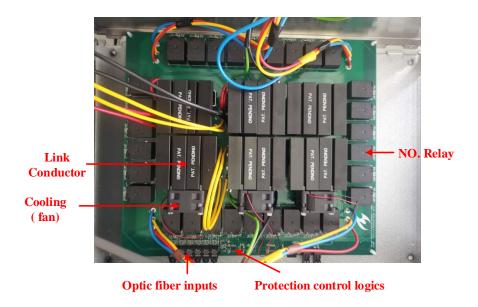

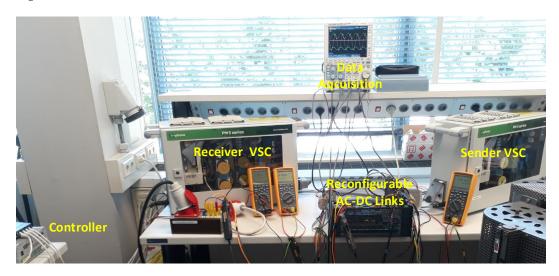

| Figure 3.46 | Experimental setup showing a single grid connected VSC operating as a STATCOM under distorted voltage | 65 |

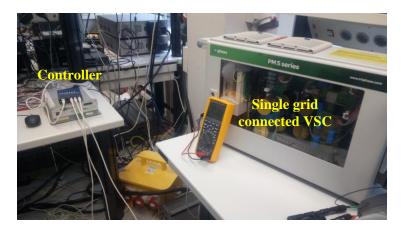

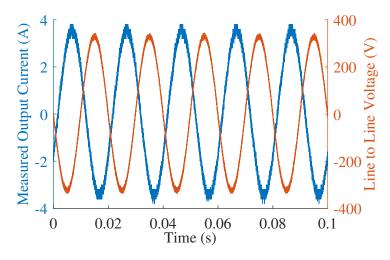

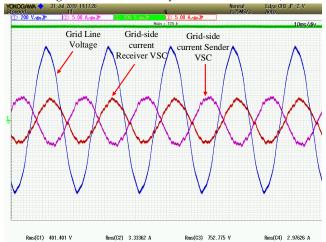

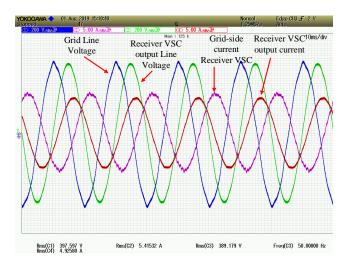

| Figure 3.47 | Measured waveforms with purely sinusoidal 50 Hz grid voltage                                          | 65 |

# LIST OF TABLES

| Table 3.1 | VSC circuit parameters                                          |

|-----------|-----------------------------------------------------------------|

| Table 3.2 | Harmonic components in the grid voltage                         |

| Table 3.3 | Controller parameters                                           |

| Table 4.1 | Number of AC and DC links, mode of control under different con- |

|           | figuration with 6 link conductors                               |

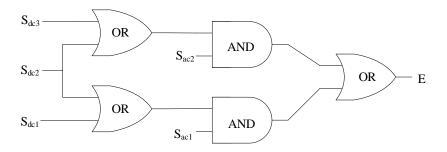

| Table 4.2 | Truth table of NAND logic                                       |

| Table 4.3 | VSC circuit parameters                                          |

## LIST OF SYMBOLS

| $x, p_1$              | The parameter for the lead litter                                       |

|-----------------------|-------------------------------------------------------------------------|

| $\bar{\mathcal{X}}$   | The averaged variable                                                   |

| $\Delta\omega_{res}$  | The resonance band of the notch filter                                  |

| $\delta_m$            | The phase increase of the lead filter                                   |

| λ                     | The integer variable                                                    |

| w                     | The fundamental angular frequency                                       |

| $\omega_m$            | The frequency for the maximum phase increase in the lead filter         |

| $\omega_n$            | The natural frequency of the closed loop system of the SRF-PLL          |

| $\omega_{0,0}$        | The anti-resonance frequency                                            |

| $\omega_{ref}$        | The compensation frequency of the zero compensation                     |

| $w_{res}, f_r$        | es The resonance frequency                                              |

| τ                     | The time constant of the DC bus dynamics                                |

| <del>)</del>          | The phase of the three phase voltage                                    |

| $\theta_0$            | The initial phase of the three phase voltage                            |

| $\widehat{n}_{a,b,c}$ | The peak amplitude of the three phase modulation index                  |

| $\widehat{V}$         | The peak amplitude of the voltage                                       |

| 7                     | The damping ratio of the closed loop system of the SRF-PLL              |

| $\zeta_p,\zeta_z$     | The damping factors in the notch filter                                 |

| $\imath_\Delta$       | The attenuation of the notch filter at the border of the resonance band |

| $a_{\omega_{res}}$    | The attenuation of the notch filter at the resonance frequency          |

| $C_f$                 | The capacitance of the LCL filter                                       |

| $C_p$                 | The DC link capacitor                                                   |

| $C_n$                 | The configuration of the parallel AC-DC system                          |

| 1                     | The duty cycle                                                          |

$D_{1,\dots,6}$ , The anti-parallel diodes in three phase two-level VSC

The natural base

- $f_s$  The switching frequency of the PWM

- $f_{\alpha,\beta}(t)$  The  $\alpha\beta$  representation of the space phasor

- $f_{a,b,c}(t)$  The balanced three phase quantities

- $f_{d,q}(t)$  The dq representation of the space phasor

- $F_{lead}(s)$  The transfer function of the lead filter

- $f_{res}$  The critical frequency

- $G_d(s)$  The digital controller delay

- $G_i(s)$  The closed loop transfer function of the current control

- $G_{v}(s)$  The closed loop transfer function of the power control

- $G_v(s)$  The compensator of the DC link voltage control

- $G_c(s)$  The transfer function of the current controller

- $G_{i_c}(s)$  The transfer function from AC terminal voltage to the converter side current

- $G_{i_g}(s)$  The transfer function from AC terminal voltage to the grid side current

- $G_{notch-PLL}(s)$  The transfer function of the notch filter in the SRF-PLL

- $G_{PI}(s)$  The transfer function of the PI controller in the SRF-PLL

- $G_{PLL}(s)$  The closed loop transfer function of the SRF-PLL

- $G_{PWM}(s)$  The PWM delay

- H(s) The compensator in the SRF-PLL

- $i_{dq}^*$  The current references in dq frame

- *i*<sub>0</sub> The zero-sequence circulating current

- $i_{a,b,c}$  The three phase output currents of the VSC

- $I_{dc}$  The DC side current

- k(s) The compensator of the voltage controller in standalone mode control

- $k_p, k_i$  The proportional and integral gains for current controller

- $k_r$  The resonator gain

- $K_{ipll}$  The integral gain for the PI controller in the SRF-PLL

- $K_{vvll}$  The proportional gain for the PI controller in the SRF-PLL

- $k_{pwm}$  The modulation ratio

- L The coupled inductance of the  $L_g$  and  $L_c$

$L_c$  The converter side inductance of the LCL filter

$L_g$  The grid side inductance of the LCL filter

*m* The amplitude modulation index

$m_{a,b,c}(t)$  The three phase modulation index functions

N The total number of conductor links

$N_{ac}$  The number of conductor links in AC operation

$N_{dc}$  The number of conductor links in DC operation

$P_s^*$  The active power reference

$P_{dc}(t)$  The DC side power

$P_{ext}$  The DC side external power

$P_t(t)$  The AC terminal active power

$Q_s^*$  The reactive power reference

$Q_{1,\dots,6}$ , The active switches in three phase two-level VSC

$Q_t(t)$  The AC terminal reactive power

$R_c$  The converter side resistance of the LCL filter

$R_d$  The damping resistor

$R_g$  The grid side resistance of the LCL filter

s(t) The switching function

$S_{1,2,\dots,6}$ , The switching signals for three phase two-level VSC

$s_{lower}(t)$  The switching function for switch in the lower bridge

$s_{upper}(t)$  The switching function for switch in the upper bridge

$Sac_n$  The three phase AC switches

$Sdc_n$  The ungrounded monopolar DC switches

T The digital control delay

$T_d$  The digital controller delay time

$T_s$  The switching period of the PWM

$V_{d,q}(t)$  The dq representation of the three phase voltage

$V_{dc}$  The DC link voltage of the VSC

$V_{gabc}$  The three phase grid voltage

$V_{ta,b,c}$  The three phase terminal voltages of the VSC

x(t) The time dependent variable

$\overrightarrow{f}(t)$  The space phasor

# 1 INTRODUCTION

#### 1.1 MOTIVATION

#### 1.1.1 Hybrid AC-DC links system.

The difference of Alternating Current (AC) and Direct Current (DC) power transmission has been discussed over many years. AC transmission lines are widely used in modern power systems due to the easy control of voltage step-up and step-down by AC transformers [1]. However, DC transmission has many advantages over AC transmission. For instance, the DC transmission utilizes fewer number of conductors and requires smaller effective conductor cross-section compared with AC transmission because of better utilization of the conductor area (or absence of skin effect). Additionally, the effects of inductance, capacitance and phase angle displacement as well as the synchronizing problems which exist in AC transmission lines are not observed in the DC solutions. Thus, better voltage regulation in DC transmission lines are expected. In the past, the complexity and cost of DC transmissions have hindered its applications, however, recently these limitations have been gradually mitigated with the rapid development of power electronics and other enabling technologies [2, 3]. While High Voltage Direct Current (HVDC) lines have proven benefits in modern long-distance power transmission systems, in the mediumvoltage distribution energy systems many people are skeptical. For example, the distribution network operators (DNOs) have difficulty in adopting DC-based infrastructures because these technologies are less mature than the existing AC grid infrastructure [4]. It has been identified in [4, 5] that greater power transfer capacity can be achieved without major modification of the original power grid by refurbishing the existing AC lines for DC operation, alongside other advantages in terms of efficiency and flexibility in power and voltage control. The enhancement of the power transfer capacity based on the refurbished DC links can offer an interesting solution to the rapidly growing power demand on the aging AC infrastructure.

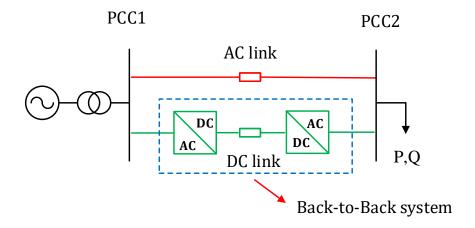

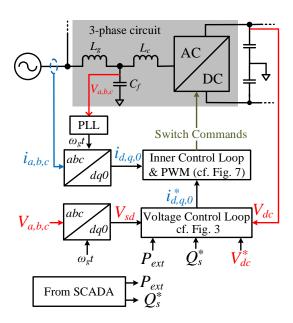

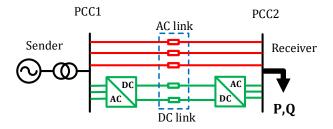

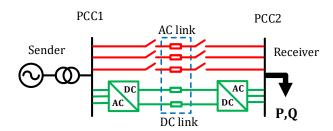

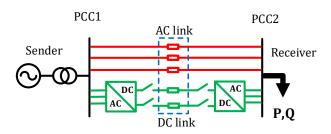

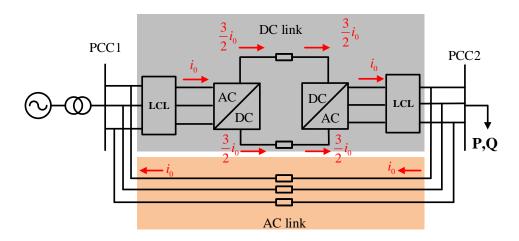

Recent studies on hybrid (or parallel) point-to-point AC and DC distribution links, such as the one depicted in Fig.1.1, have shown interesting performance on capacity enhancement and superior energy distribution efficiency under specific operating conditions, particularly for high power, medium to high voltage level and moderate distribution distances, e.g. 5....20 km, [6]. Back-to-Back (B2B) Voltage Source Converters (VSCs) with long DC buried cables in-between the transmitting- and receiving-end substations are suitable solutions for the DC distribution.

In fact, the parallel operation of AC and DC lines was earliest considered in [7] for HVDC transmission because of the greater flexibility of DC transmission as well as rapid control of the combined system. Some difficulty and challenges have been explored in [8].

Figure 1.1: Basic concept of a Point-to-Point parallel AC-DC re-configurable links system.

#### 1.1.2 Parallel AC and DC Re-configurable Links

As presented in [6], the optimal efficiency configuration in a parallel point-to-point AC and DC links varies according to the load demand and link/cable length, thus the distribution network can be manoeuvred on-line into an optimal configuration in terms of power transfer efficiency. The realization of the system re-configuration relies on the switching devices in both AC and DC links. Circuit breakers and disconnectors are suitable devices for this application. Compared to circuit breakers, switching power requirements for disconnectors is lower but they are of critical importance for substation and grid operation [9]. The use of disconnectors to transfer load currents between parallel conductors have been well documented and reported in [10, 11] The improved Gas-Insulated Switch-Gear (GIS) disconnectors [9] has revealed promising enhancement of the re-ignition behavior and increasing switching performance for bus-transfer switching cases. Such a performance is beneficial for the parallel AC and DC links system as this can be seen as an example of load bus transfer application. Hence, the use of parallel AC and DC re-configurable links system is feasible and it constitutes a promising MV application for future power distribution system.

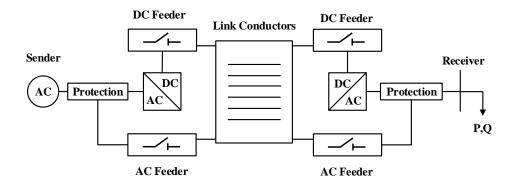

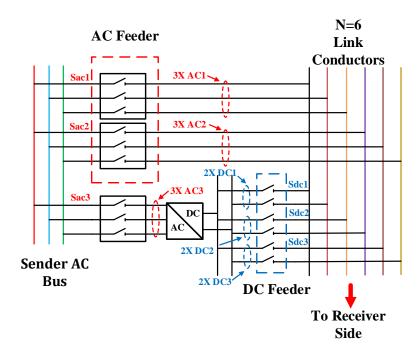

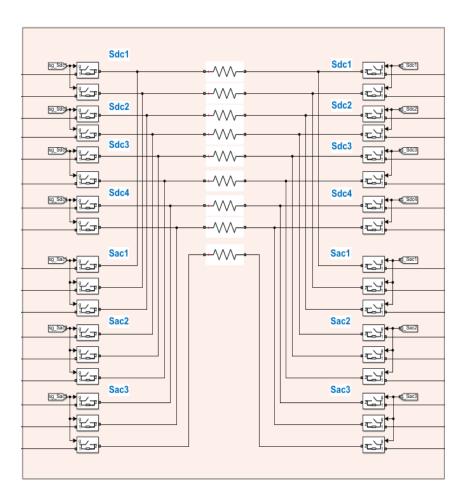

The parallel AC and DC re-configurable links is the key component of the proposed system. Fig.1.2 shows such a energy distribution system implementing six conductor links. Herein, the link conductors are connected to the power electronics and grid through DC and AC feeders, where the reported GIS disconnectors can be adopted to realize improved switching performance. The conductor links are the aforementioned refurbished links which can be operated under both AC and DC conditions. DC power delivery is realized through the DC links once they are connected with the Back-to-Back power converters. The efficiency of the power transfer from complete usage of the DC links also strongly depends on the converters and their respective operational DC-link voltage. Modular Multilevel Converter (MMC) can be chosen as the power converters because

Figure 1.2: Parallel AC-DC re-configurable links system.

of its modularity, scalability, good harmonic performance and higher efficiency [12]. As shown in Fig.1.2, the DC links are connected to only one pair of power converters. For practical implementation of the parallel AC and DC re-configurable links, the choice of number of DC link converter pairs is associated with the desired DC link capacity and the power rating of converter itself, which is also related to the size and cost of the system. Thereby, the choice of DC link converters requires a combined consideration of converter rating, efficiency and cost [13]. Three phase two-level voltage-source converters (VSCs) is adopted in many AC medium and high power applications because of its simplicity and low cost [14]. In medium voltage applications, series connection of IGBTs could be used to achieve higher blocking voltage capability. Therefore, in this thesi, one pair of two-level VSCs is adopted as the back-to-back system.

#### 1.1.3 Re-configuration Strategy

The re-configurations of the studied energy distribution system require the switch-on and -off actions of the adopted switches, for example, the GIS disconnectors or circuit breakers. The devices will experience large stress if they are triggered to be opened without creating a current-zero condition, which may deteriorate the lifetime of the switches and even create an undesired electric arc. In order to avoid this problem, this thesis proposes reconfiguration strategies to provide nearly zero current switching condition in the cables to be disconnected. This is achieved by exploiting the power steering capability of the Back-to-Back VSCs when this is placed in parallel to a AC-link. To be more specific, the idea is to utilize the power controller of the receiving-end VSC to bring the power flow to zero across the links which are to be opened/closed during the desired re-configuration. Hence, the switches have relatively low current in their links while manoeuvring. The expected improved lifetime of the switches under zero current thus make the parallel AC and DC links system feasible for sustainable use and on-line re-configuration.

### 1.1.4 Control of LCL-filtered VSC under Grid Voltage Distortion Condition

Three-wire three-phase two-level VSC with LCL filter is adopted as building block converter for the DC links because of its high-frequency attenuation capability. The control of grid-connected LCL-filtered VSCs requires more sophisticated control when compared with VSCs employed in drives of motors/generators where equivalent single AC inductor filter exists. More specifically, in the former system instability problem can be caused by the LCL filter resonance and/or equivalent grid impedance. Moreover, in practice the grid voltage of energy distribution systems may contain low-order harmonics distortions, which can result in deteriorated waveform in both converter and grid side currents of the LCL filter. Therefore, current harmonics must be controlled under the range recommended by the newly revised IEEE Standard 519-2014. Above all, the precise power and DC link voltage controls for the three phase two-level VSC with LCL filter under grid distortion, should be investigated and realized to serve the proposed re-configuration strategy.

#### SPECIFIC OBJECTIVES 1.2

The objectives of this thesis are listed as follows:

- Achieve controlled sinusoidal grid side converter currents under distorted grid voltage in a parallel operating AC and DC link system.

- Improve the stability of the 2-level VSC under distorted grid voltage.

- Design a notch filter to avoid instability due to resonance associated with the LCL filter of the VSC.

- Develop harmonic resonators with proper phase compensation to improve converter performance under specific low order harmonics (or to improve the THD).

- Realize seamless transition between grid-connected and stand-alone mode control of the VSC.

- Implement online reconfigurations in hybrid AC and DC links system at near zero switching currents.

#### RESEARCH QUESTIONS AND CHALLENGES 1.3

The research questions and the corresponding challenges are:

1. What is the control method and associated gains necessary to achieve sinusoidal currents with low harmonic distortion under distorted grid voltages?

#### **Key Challenges:**

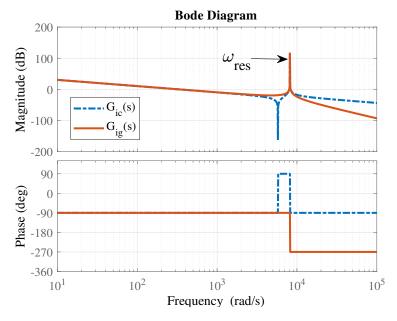

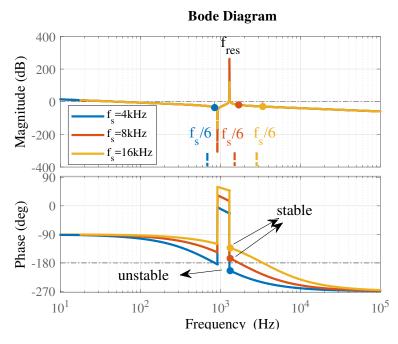

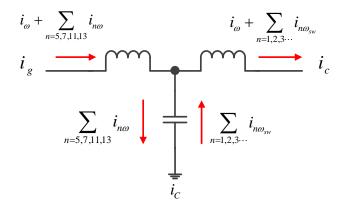

• Filter capacitor of the VSC acts as a sink for the grid harmonic voltages. Therefore, for the current feedback control loop of the power electronics the LCL filter grid side current measurement is preferred over the inverter side current measurement. This choice can have a strong impact on the stable operation of the converter.

- While higher current control loop gain (or Gain Margin) can reject higher order harmonics in the LCL filter grid side current, its choice for stable operation is strictly limited according to the LCL resonance, semiconductor switching and digital sampling frequencies. This is particularly more severe for grid side current control under distorted grid voltage.

- The PLL (phase-lock loop) also influences the harmonics performance of the output current under a distorted grid voltage. For SRF-PLL, the design tradeoff lies in the dynamic response and attenuation capability of harmonic components in the output frequency.

- 2. How to simultaneously improve the stability and output current performance of the VSC under distorted grid voltage?

#### **Key Challenges:**

- If the available control bandwidth does not adequately reject the current harmonics, the simultaneous improvement of harmonic performance and stability needs insight on the required bandwidth and unstable frequency points in the system. Both these aspects can vary according to the grid impedance, harmonic frequencies in the grid voltage and the converter component parameters.

- Several passive and active damping methods are available. The choice for implementation should be made based on available flexibility in modifying the infrastructure, system efficiency and performance constraints.

- 3. What are the design parameters of the notch filter for improving the stability range of the VSC?

## **Key Challenges:**

- While strong LCL filter resonance current attenuation by implementing active damping at theoretical unstable frequency points can make the system stable, the width of the studied notch filter strategy can reduce the closed loop gain in the required controller frequency bandwidth. This design trade-off should be explored in detail.

- The converter and grid parameters that influence operational requirements and unstable regions can vary in practical scenarios. This aspect can put design constraints on achieving acceptable converter operational performance.

- 4. What are the harmonics resonator parameters for increasing the low order harmonics rejection capability of the VSC?

## **Key Challenges:**

While the grid impedance for the low order harmonics can be increased by adding control resonators, the phase reduction of such technique can hinder the feedback control's phase margin which may lead to system instabilities.

- While adding the phase compensation to the resonator can improve the phase reduction while maintaining the same low order harmonics rejection capability, the open loop gain at lower frequency ranges will be decreased by either leadfilter or zero compensation techniques.

- 5. What are the control strategy for the seamless mode transitions?

### **Key Challenges:**

- The standalone mode operation requires a different control structure from gridconnected mode. The transition between the different controller can result in undesirable transients in the VSC system.

- The interface of the LCL filter with the load leads to variation of the characteristics of the system control loop.

- 6. How to ensure a near zero r.m.s switching current during online re-configurations?

#### **Key Challenges:**

- The synchronization between the signals for the circuit switches and VSC mode control is required, otherwise it leads to the mismatch between the control and operation of the VSC.

- The existence of zero-sequence circulating current in the parallel AC and DC system adds complexity in realizing near zero r.m.s switching current.

#### MAIN CONTRIBUTIONS 1.4

The first contribution in this thesis work is to implement the notch-filter based active damping in the grid-side current control together with the tuned resonant controller to remove the currents harmonics caused by grid voltage distortions and to realize a stable voltage and current control in the LCL-filtered two-level VSC.

The second contribution is the realization of the re-configuration of the parallel AC-DC system based on the control strategy to achieve nearly zero current transition in the links disconnecting switches.

#### THESIS STRUCTURE 1.5

Chapter 1 introduces the motivation and objectives of this thesis.

Chapter 2 reports the state-of-art of three phase two-level VSC and it also presents the control structure of the DC-link voltage and power controls, including the design of Synchronous Reference Frame - Phase-Locked Loop (SRF-PLL).

Chapter 3 presents the controller design based on the combined considerations of stability and harmonics performance. The instability problem caused by LCL filter resonance and the choice of controlled current (GCC or CCC) with regard to the delay influence are thoroughly discussed. Moreover, the current controller with notch filter is designed and

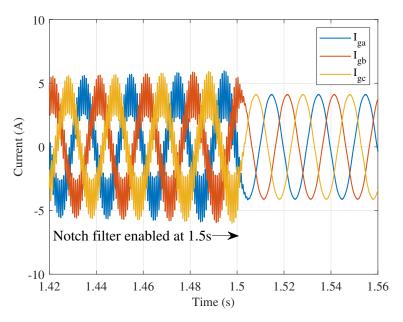

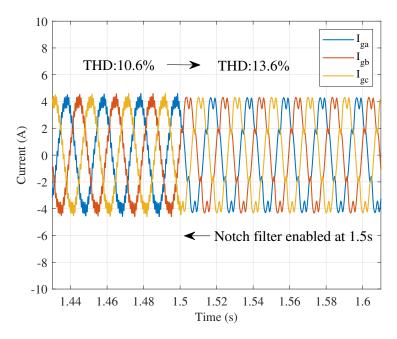

tested. Finally, the composite current controller with notch filter and harmonics control is verified in both simulation and experiments.

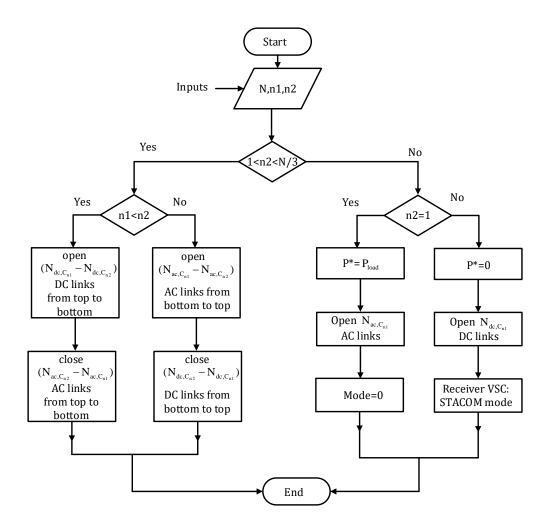

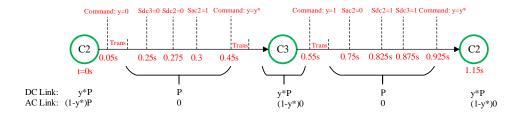

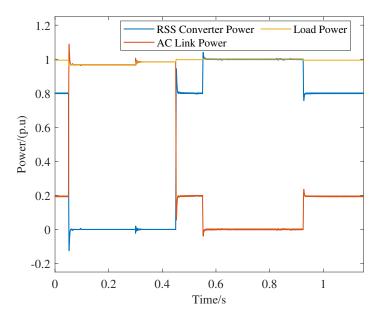

Chapter 4 studies the re-configuration of parallel AC and DC links system. The zerosequence circulating current problem is solved by employing a PI-based ZSCC controller. Additionally, the standalone mode control strategy is presented and the transition between standalone and grid-connected modes is studied. These methods are validated in both simulation and experimental tests. Finally, the re-configuration strategy to provide almost zero current switching for the mechanical switches is realized in the parallel AC and DC re-configurable links system with nine link conductors in simulation.

Chapter 5 presents the conclusion of this thesis work and possible future works.

#### 1.6 LIST OF PUBLICATIONS

- Y Wu, A. Shekhar, T. B. Soeiro and P. Bauer, "Voltage Source Converter Control under Distorted Grid Voltage for Hybrid AC-DC Distribution Links," IECON 2019 -45th Annual Conference of the IEEE Industrial Electronics Society, Lisbon. (Accepted)

- A. Shekhar, L. B. Larumbe, T. B. Soeiro, Y Wu and P. Bauer, "Number of Levels, Arm Inductance and Modulation Trade-offs for High Power Medium Voltage Modular Multilevel Converters," 2019 IEEE ECCE Asia Busan, Korea. (Accepted)

- A. Shekhar, T. B. Soeiro, Y Wu and P. Bauer, "Optimal Power Flow Control in Parallel Operating AC and DC Distribution Links," IEEE Trans. Ind. Electron (Submitted)

# 2 | CONTROL OF GRID CONNECTED TWO-LEVEL VSC

The Back-to-Back (B2B) system composed of two Voltage Source Converters (VSCs) are the fundamental circuit in the re-configurable hybrid AC and DC links. Herein, the conventional two-Level VSC is adopted because of its simplicity and robustness.

The objective of this chapter is to elaborate the control method of the grid-connected two-level VSC. Firstly, the averaged analytic model is introduced in order to describe the principle of operation of the circuit and to analyze the performance of the feedback control schemes commonly employed in VSCs. An improved SRF-PLL with mitigation of negative-sequence fundamental component in the grid voltage is described in this chapter. The power and DC-link voltage controls are described in terms of their equivalent control loop transfer function and respective circuit diagram in *dq*-frame.

#### 2.1 TWO-LEVEL VOLTAGE SOURCE CONVERTER

#### 2.1.1 Circuitry Structure

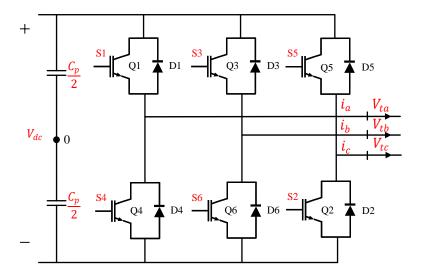

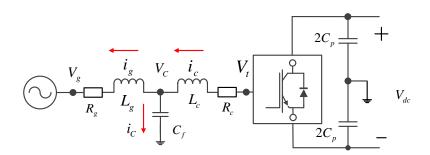

Figure 2.1 shows the circuit schematics of the three phase two-level voltage sourced converter. The circuit employs three identical half-bridge converters, which consists of two controllable power semiconductors with anti-parallel diodes. At the DC side of the VSC, two series connected DC pole capacitor are used to stabilize the DC voltage and to reduce its voltage ripples to an acceptable level for any connected DC load or DC power source. For analysis convenience, the mid-point of the two DC link capacitors is set as the voltage reference point o. Then the AC-side terminal voltage of the converter  $V_{ta,b,c}$  represents the voltage difference between the mid-point of each half-bridge leg and the terminal o. This converter is called two-level VSC because during operation the generated terminal voltage can assume either  $-V_{dc}/2$  or  $V_{dc}/2$ . The converter output currents  $i_{a,b,c}$  flow into the AC system connected to the converter. Generally, filters are adopted between the 2-level VSC and the AC system. AC-side output current is equal to converter output current when a single L filter is used. However, LCL filter instead of a single L filter is chosen for this research because of its superior high frequency harmonics suppression performance. The implementation of LCL filter can bring control challenges in a digital controlled system, mainly because the controlled variable must be converted into a digital number with a limited sampling frequency. This is discussed in Section2.2. The 2-level VSC can operate as a STACOM (static synchronous compensator) [15]. This operation is possible when the DC bus is floating and the converter is absorbing or delivering reactive power to the interfaced AC system. This application will be introduced and implemented in Chapter 4. In inverter mode (or power flow from the DC- to the AC-side), a DC voltage source is connected to the DC-side terminals of the converter while its AC-side is either interfaced

Figure 2.1: Circuity of the Two-level VSC.

with the grid or an AC load. The operation of VSCs in these two cases is called Gridconnected or Standalone mode, respectively. Both operational modes are required in the re-configurations of parallel AC and DC links. Grid-connected control is introduced in this chapter and Standalone mode control will be discussed in Chapter 4.

#### Principles of Operation 2.1.2

The 2-level VSC operates based on the switching states of the upper and lower active semiconductors. The switching function is defined as:

$$s(t) = \begin{cases} 1, & switch - on \ command \\ 0, & switch - of f \ command \end{cases}$$

(2.1)

The switch-on and -off commands are typically generated through a pulse-width modulation (PWM) strategy, e.g. Sinusoidal Pulse-Width Modulation (SPWM) or Space-Vector Pulse-Width Modulation (SV-PWM). Most PWM techniques requires a carrier signal, i.e. a high frequency periodic triangular signal, and a modulating signal with a desired fundamental frequency and amplitude for generating the AC-side terminal voltage. The switching states are determined by comparing the carrier signal with the modulating signal and the intersections of them determine the switching instants. An example of switch signals for Q1 and Q4 is given in Fig.2.2. The switching signals for the active devices in a half-bridge leg are complementary, which has the relation  $s_{upper}(t) + s_{lower}(t) \equiv 1$ . The waveform of the AC-side terminal voltage is determined by the switching functions as shown in eqs. (2.2) and (2.3).

$$V_t(t) = \frac{V_{dc}}{2} (s_{upper}(t) - s_{lower}(t))$$

(2.2)

$$s_{upper}(t) + s_{lower}(t) \equiv 1 \tag{2.3}$$

The bridge currents and power dynamics can be also derived based on the switching functions and these relations are called switched model. Switched model accurately describes the steady-state and dynamic behavior of the converter and also contains high-frequency component information [15]. If elaborated model of the switch cell is available, then the transients and instantaneous information in the VSC can be computed by an analytic model. Additionally, the high-frequency information is dispensable from the control point of view and dynamic analysis since the closed loop control of the VSC usually presents a low-pass characteristics. Herein, the averaged model is preferred when describing the converter dynamics [16].

Figure 2.2: Signals based on the PWM switching strategy.

Therefore for dynamic analysis, the average of a time-dependent variable is defined as its integral average during one switching cycle, as eq. (2.4)

$$\bar{x} = \int_{t-T_s}^t x(\tau)d\tau \tag{2.4}$$

where x(t) is the time-dependent variable and the over-bar denotes the averaged variable. The concept of averaging is introduced in many non-linear systems theory [17] and power electronics literature [18] and [16]. The periodical switched waveform generated by the PWM process will be a pulse waveform with constant duty cycle if a constant modulating

signal is applied, as shown in Fig.2.3. The symbol 'd' denotes the duty cycle and 'm' is the magnitude of the constant modulating signal. The following relation is identified:

$$m = 2d - 1 \tag{2.5}$$

If the averaging operator is applied to the switching function  $s_1(t)$ , then  $\bar{s}_1(t) = d$  holds for the case of constant modulating signal. However, practically, in grid-connected ap-

Figure 2.3: PWM with a constant modulating signal.

plications, the modulating signal is a sinusoidal waveform with fundamental frequency (50Hz or 60Hz), which implies that the generated switched waveform has different duty cycle in each switching cycle. Herein, eq. (2.5) can not be directly applied to the averaging of the switching function with sinusoidal modulating signal. A prerequisite is required here to allow one to include eq. (2.5) in this case, namely the frequency of the carrier signal must be sufficiently larger than that of the modulating signal. This is because the modulating signal during each switching cycle can be regarded as a nearly constant value if the switching frequency is far larger than the modulating signal frequency and then eq. (2.5) can give more accurate results. Generally, switching frequency will be chosen as at least 10 times larger than of that fundamental frequency. For example, during one switching period, eq. (2.4) can be applied to the switching functions  $s_1(t)$  and  $s_4(t)$ , and the following equations are derived:

$$\bar{s}_1(t) = d \tag{2.6}$$

$$\bar{s}_4(t) = 1 - d \tag{2.7}$$

Based on the aforementioned assumption, in each switching period, eq. (2.5) holds for the duty cycle and the value of modulating signal in that period. Take the averaging process of both sides of eq. (2.3) and substitute in eq. (2.5), one gets:

$$\bar{V}_t = \frac{V_{dc}}{2}(2d - 1) = m\frac{V_{dc}}{2} \tag{2.8}$$

where duty cycle d can vary from 0 to 1 while m changes from -1 to 1. As eq. (2.8) illustrates, the magnitude of the averaged AC-side terminal voltage depends on the modulating signal magnitude when the DC link voltage is constant. These relations also apply to phase B and C legs in the two-level VSC. Considering the whole time scope of these averaged variables, the three phase AC-side terminal voltages are expressed as follows:

$$V_{t_a}(t) = m_a(t) \frac{V_{dc}}{2} = \widehat{m}_a \sin(\omega t) \frac{V_{dc}}{2}$$

(2.9)

$$V_{t_b}(t) = m_b(t) \frac{V_{dc}}{2} = \hat{m}_b sin(\omega t - \frac{2\pi}{3}) \frac{V_{dc}}{2}$$

(2.10)

$$V_{t_c}(t) = m_c(t) \frac{V_{dc}}{2} = \widehat{m}_c sin(\omega t + \frac{2\pi}{3}) \frac{V_{dc}}{2}$$

(2.11)

where  $\omega$  is the fundamental angular frequency and the initial phase of the reference terminal voltage is assumed as zero. The DC-side and AC-side quantities of the three phase 2-level VSC are related to each other based on the power balancing, namely DC-side power equals AC-side power when the power losses are neglected:

$$V_{dc}(t)I_{dc}(t) = V_{ta}(t)I_{a}(t) + V_{tb}(t)I_{b}(t) + V_{tc}(t)I_{c}(t)$$

(2.12)

where  $I_{dc}(t)$  and  $I_{a,b,c}(t)$  are the DC and AC-side currents, respectively. This relation is important as it is the bridge between the DC- and AC-side power and it will be used again for deriving the power dynamics of the DC-link voltage control. The averaged model of a non-ideal three phase 2-level VSC includes the effects of the switching and conduction losses of the IGBTs and anti-parallel diodes [15]. For simplicity, an ideal three-phase 2level VSC is assumed here, i.e. linear switching devices and no losses.

#### MODEL AND CONTROL OF GRID-CONNECTED TWO-LEVEL 2.2 **VSC**

#### Model in dq-Frame

The space phasor is the transformed representation of a balanced three phase system:

$$\overrightarrow{f}(t) = \frac{2}{3} \left[ e^{j0} f_a(t) + e^{j\frac{2\pi}{3}} f_b(t) + e^{j\frac{-2\pi}{3}} f_c(t) \right]$$

(2.13)

where  $\overrightarrow{f}(t)$  is the space phasor and  $f_a(t)$ ,  $f_b(t)$ ,  $f_c(t)$  are the balanced three phase quantities. Based on the trigonometric identity and three phase balanced system identity:

$$\cos\theta = \frac{1}{2}(e^{j\theta} + e^{-j\theta}) \tag{2.14}$$

$$e^{j0} + e^{j\frac{2\pi}{3}} + e^{-\frac{2\pi}{3}} \equiv 0 \tag{2.15}$$

One can derive:

$$\overrightarrow{f}(t) = \widehat{f}e^{j(\omega t + \theta_0)} \tag{2.16}$$

where  $\omega$  and  $\theta_0$  are the fundamental angular frequency and the initial phase of the three phase balanced system, respectively.  $\hat{f}$  is the magnitude of the three phase quantities. The space phasor  $\overline{f}(t)$  can be projected to the real and imaginary axis, respectively, and

$$\overrightarrow{f}(t) = f_{\alpha}(t) + jf_{\beta}(t) \tag{2.17}$$

Substituteeq. (2.16) into eq. (2.17), the two components can be written as:

$$f_{\alpha}(t) = \widehat{f}\cos(\omega t + \theta_0) \tag{2.18}$$

$$f_{\beta}(t) = \widehat{f}sin(\omega t + \theta_0) \tag{2.19}$$

The space phasor is decoupled into frame with two orthogonal components and this frame is called  $\alpha\beta$ -frame (or stationary frame). The  $\alpha\beta$ -to dq-frame (rotating frame) is realized by shifting the space phase angle with  $\theta(t)$  clock-wisely as eq. (2.20) shown:

$$f_d(t) + jf_q(t) = (f_\alpha(t) + jf_\beta(t))e^{-j\theta(t)} = \hat{f}e^{j(\omega t + \theta_0 - \theta(t))}$$

(2.20)

If  $\theta(t)$  is chosen as  $\omega t$ , then the space phasor is represented by two orthogonal DC quantities. Practically,  $\theta(t)$  is chosen exactly as  $\omega t + \theta_0$  and the q component becomes zero while the d component has a purely DC value. Vector control ( $\alpha\beta$  or dq) is adopted in the three phase VSCs. While control in  $\alpha\beta$  – frame can decouple the original system (three control loops) into two independent subsystems and track sinusoidal reference, the control in dqframe can track DC references with simpler controller structure. Additionally, control in dq-frame adopts simple integrator in controller to achieve zero steady-state error instead of high order compensators in  $\alpha\beta$ -frame. Therefore, the control of three phase 2-level VSC will be discussed and analyzed in dq-frame. The dq-frame representations of the averaged model eqs. (2.9) to (2.11) are shown below:

$$V_{td}(t) = \frac{V_{dc}}{2} m_d(t) {(2.21)}$$

$$V_{tq}(t) = \frac{V_{dc}}{2} m_q(t) {(2.22)}$$

$$P_{dc}(t) = V_{dc}(t)I_{dc}(t) = P_t(t) = \frac{3}{2}[V_{td}(t)I_d(t) + V_{tq}(t)I_q(t)]$$

(2.23)

$$Q_t(t) = \frac{3}{2} \left[ -V_{td}(t)I_q(t) + V_{tq}(t)I_d(t) \right]$$

(2.24)

The coefficient  $\frac{3}{2}$  comes from the Amplitude-invariant transformation. The coefficient becomes 1 (one) when Power-invariant transformation is adopted [19]. The eqs. (2.21) to (2.24) constitute a control model for the two-level VSC as shown in Fig.2.4

Figure 2.4: Control model for the ideal 2-level VSC.

#### Control of Grid-connected Three-Phase 2-level VSC

There are two main control methods for controlling the AC-side power: voltage-mode control and current-mode control. The first approach is widely used in high-power/voltage applications [20] and the AC-side power is controlled based on the angle and amplitude of the AC-side terminal voltage with respect to the Point of Common Coupling (PCC). Current-model control regulates the AC-side current with a current control loop while the power is controlled based on the generated angle and amplitude of the AC-side currents with respect to the amplitude and angle of the voltage at PCC. The current-mode control hence can protect the VSC against over-current and have better control precision.

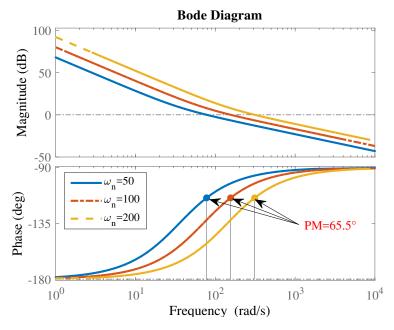

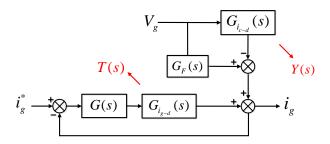

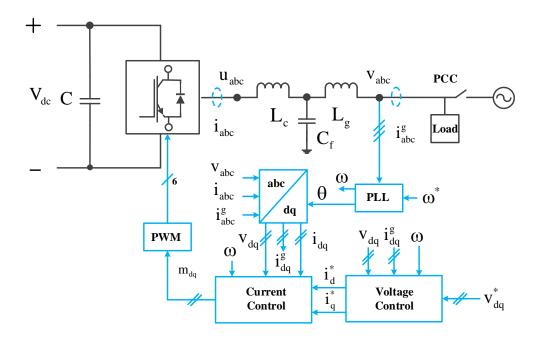

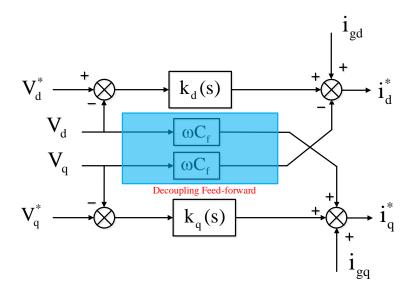

The control of grid-connected 2-level VSCs includes two parts: power control and DC link voltage control, which corresponds to two different operating modes: Inverter mode (power flow from the DC- to AC-side - or DC/AC) and Rectifier mode (power flow from the AC- to AC-side - or AC/DC). The complete control diagram of a 2-level VSC in dqframe is illustrated in Fig.2.5. Phase-Locked Loop (PLL) is required for grid-connected VSC control in both inverter and rectifier modes. The function of the PLL is to realize the synchronization of the converter generated output voltage with the grid in terms of frequency and initial phase. The PLL outputs the dq-frame currents and voltages for the controllers. The Inner current controller is the key part for controlling the AC-side current and, consequently the power flow. The output of the current controller is the generated voltage reference for the modulating signal in the PWM block, which produces the switching signals for the three-phase 2-level VSC. The outer voltage control loop regulates the error between the actual DC voltage and the reference value and its output is regarded as the *d* component of the reference current. In this diagram, the controlled variable is chosen as the grid-side current. Nevertheless, the converter-side current can be also chosen as the controlled variable. The choice of Grid-Side Current Control (GCC) and Converter-Side Current Control (CCC) is discussed in Chapter.3.

#### Phase-Locked Loop Design

Control of the currents in dq-frame is adopted because the control will be simplified into two decoupled subsystems, which means d and q components of the currents can be con-

Figure 2.5: Control diagram of a grid-connected 2-level VSC.

trolled separately. Aside from this, the phase shift done by the abc - dq transformation must be exactly the phase of the grid voltage, otherwise the power to current conversion is not properly decoupled and the active and reactive powers can not be independently controlled. Thereby, the grid voltage synchronization is indispensable to realize this objective. The most widely adopted PLL technique is the Synchronous Reference Frame-PLL (SRF-PLL) as shown in Fig.2.6. As shown in eq. (2.20), if  $\theta(t)$  is controlled exactly as  $\omega t + \theta_0$ , one can obtain:

$$\begin{cases}

V_d = \widehat{V} \\

V_q = 0

\end{cases}$$

(2.25)

The VCO is a re-settable integrator which nullifies its output whenever it reaches  $2\pi$ . Commonly, the grid voltage has a distorted waveform with some low-order harmonics (e.g.  $5^{th}$ , $7^{th}$  and  $11^{th}$ ) and  $V_d$  is not a purely DC value. Thus, a low-pass filter (LPF) is implemented to eliminate the harmonics components and to produce a DC value equal to the amplitude of grid voltage if amplitude-invariant transformation is used. The SRF-PLL regulates  $V_q$  in such a way that the  $V_q$  is controlled at zero, which means  $\theta(t)$  is aligned with  $\omega t + \theta_0$ . If the SRF-PLL tracks the phase with a small error,  $V_q$  can be approximated as:

$$V_q = \widehat{V}sin(\omega t + \theta_0 - \theta(t)) \approx \omega t + \theta_0 - \theta(t)$$

(2.26)

From the control point of view,  $\omega t + \theta_0$  is the reference and  $\theta(t)$  is the actual variable. Hence,  $V_q$  is approximated as the error input of the control system and the closed loop transfer function of the SRF-PLL is depicted in Fig.2.7. The term  $\omega$  is regarded as a disturbance. The compensator should be designed in such a way that the closed loop system can fulfill: 1) zero steady-state error tracking 2) enough phase margin (PM).

Figure 2.6: Schematic diagram of the conventional SRF-PLL.

Figure 2.7: The closed loop transfer function of SRF-PLL.

The design of the compensator is straightforward since the open loop gain has already one integral element. From the control theory [21], at least two integral elements are required for the open loop gain to realize the zero steady-state error when the input is a ramp function of time. Therefore, the compensator must include one integral. PI control is recommended here since it includes one pole at origin. Thus the closed loop transfer function of the SRF-PLL can be written as:

$$G_{PLL}(s) = \frac{\frac{\hat{V}}{s}G_{PI}(s)}{1 + \frac{\hat{V}}{s}G_{PI}(s)} = \frac{\hat{V}G_{PI}(s)}{s + \hat{V}G_{PI}(s)}$$

(2.27)

where  $G_{PI}(s)$  is defined as:

$$G_{PI}(s) = K_{ppll} + \frac{K_{ipll}}{s}$$

(2.28)

Substitute eq. (2.28) into eq. (2.27), the closed loop transfer function becomes:

$$G_{PLL}(s) = \frac{\widehat{V}K_{ppll}s + \widehat{V}K_{ipll}}{s^2 + \widehat{V}K_{ppll}s + \widehat{V}K_{ipll}}$$

$$= \frac{2\zeta\omega_n s + \omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

(2.29)

where  $\omega_n = \sqrt{\hat{V}K_{ipll}}$  and  $\zeta = \frac{K_{ppll}\sqrt{\hat{V}}}{2\sqrt{K_{ipll}}}$ . The closed loop transfer function can be written in standard form of a second order system. The system is stable if the two poles of the closed loop transfer function are located in the Left-Half Plane (LHP). The two poles are solved as:

$$s_{1,2} = -\zeta \omega_n \pm \omega_n \sqrt{\zeta^2 - 1} \tag{2.30}$$

The natural frequency  $\omega_n$  is larger than zero and the damping ratio  $\zeta$  has different possible values depending on the choice of  $K_{pll}$ . The possible distribution of poles in the s-Plane is depicted in Fig.2.8. The closed loop system is marginally stable without damping when

Figure 2.8: Poles of the closed loop transfer function of the SRF-PLL.

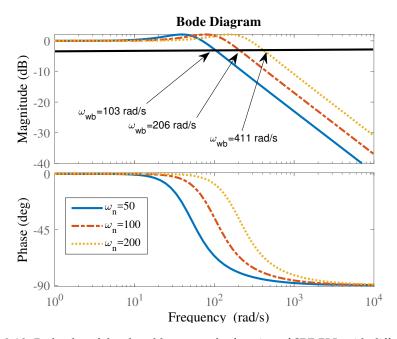

only an integrator is used for compensator. Practically, the system is unstable without any other phase compensation methods under this case. In the over-damped condition ( $\zeta > 1$ ), the response of the closed loop system is quite slow compared with the under-damped condition. Generally, the PI controller parameters should be chosen in such a way that the closed loop transfer function of the SRF-PLL has an under-damped characteristics. The dynamics performance e.g. overshoot and rise time can be adjusted by changing the PI parameters to strategically locate the two conjugate poles [21]. Since the SRF-PLL closed loop system is stable with a PI compensator, the phase margin and the bandwidth are the merits of tuning for the design of the compensator. The natural frequency  $\omega_n$  is related to the closed loop bandwidth when optimal damping ratio  $\zeta = 0.707$  is chosen according to [22]. The bode plot of the open loop transfer function of the SRF-PLL with different parameters and the closed loop bandwidth are shown in Fig.2.9 and 2.10. With the higher natural frequency, the phase margin remains the same while the bandwidth increases.

SRF-PLL can achieve satisfactory performance provided that the grid voltage contains negligible low order harmonics [23]. However, grid voltage inevitably has some harmonic components or negative sequence components under unbalanced condition. Therefore, another important consideration in designing the compensator is the mitigation ability of harmonics and negative sequence components in the PLL output variables  $V_d$  and  $V_q$ . Without the mitigation of the grid distortion, the outputs of the PLL:  $\theta(t)$  and  $\Delta\omega$  will have the fluctuations due to the harmonics and negative sequence components [24], which will be passed onto the the current control.

Since SRF-PLL generally exhibits a low-pass characteristics as shown in Fig.2.10, the high frequency components can be attenuated effectively if the closed loop bandwidth is selected properly. The component of the fundamental negative sequence is of concern because the magnitude of this component is much larger than the other harmonics and it can

Figure 2.9: Bode plot of open-loop transfer function of SRF-PLL with different  $\omega_n$ .

**Figure 2.10**: Bode plot of the closed loop transfer function of SRF-PLL with different  $\omega_n$ .

be further enlarged during a fault such as phase-to-ground fault. Assume that  $V_{gabc}$  represents an unbalanced grid voltage with a negative-sequence fundamental component, as given in eq. (2.31).

$$\begin{split} V_{ga}(t) &= \widehat{V}cos(\omega t + \theta_0) + k_1 \widehat{V}cos(\omega t + \theta_0) \\ V_{gb}(t) &= \widehat{V}cos(\omega t + \theta_0 - \frac{2\pi}{3}) + k_1 \widehat{V}cos(\omega t + \theta_0 - \frac{4\pi}{3}) \\ V_{gc}(t) &= \widehat{V}cos(\omega t + \theta_0 - \frac{4\pi}{3}) + k_1 \widehat{V}cos(\omega t + \theta_0 - \frac{2\pi}{3}) \end{split} \tag{2.31}$$

where  $k_1$  is the amplitude of the negative-sequence fundamental component. Based on eqs. (2.13) and (2.20), one can deduce the space phasor representation of the grid voltage and the dq-frame representation assuming that the SRF-PLL works in steady-state, which means  $\theta(t) = \omega t + \theta_0$ . The space phasor form is

$$\overrightarrow{V}_{g} = \widehat{V}e^{j(\omega t + \theta_0)} + k_1\widehat{V}e^{-j(\omega t + \theta_0)}$$

(2.32)

The *dq*-frame representation is

$$V_{gd} = \hat{V} + k_1 \hat{V} \cos(2\omega t + 2\theta_0)$$

$$V_{gg} = -k_1 \hat{V} \sin(2\omega t + 2\theta_0)$$

(2.33)

This implies that the negative-sequence component becomes a fluctuation with twice fundamental frequency after the abc - dq transformation. There are two possible approaches to eliminate this component in the PLL output. The first approach is to design a SRF-PLL in such a way that the closed loop system has strong low-pass characteristics to reject the frequency  $2\omega$ , which means the bandwidth has to be sacrificed. Another method is to adopted Decoupled Double Synchronous Reference Frame PLL (DDSRF-PLL), which has a decoupling network consisting of two separate SRF-PLL for positive and negativesequence components [25]. To avoid the complicated structure, a notch-filter with the antiresonance frequency at  $2\omega$  can be added to the basic SRF-PLL to eliminate the negativesequence fundamental component, as shown in eq. (2.34)

$$G_{notch-PLL}(s) = \frac{s^2 + 2 * \zeta s + (2\omega)^2}{(s+2\omega)^2}$$

(2.34)

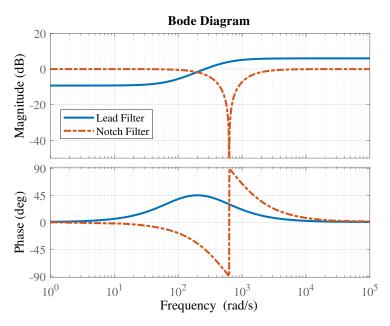

This notch filter provides two conjugate zeros at  $2\omega$  and the double frequency component oscillation will be "notched". The coefficient  $\zeta$  is used to adjust the anti-resonance peak of the notch filter. Note that the phase margin of the SRF-PLL will be greatly influenced by the notch filter, hence it may require a phase compensation method for suggested stability. A lead filter can be adopted here to increase the phase margin of the SRF-PLL with the notch filter [26]. A simple lead filter can provide a maximum phase increase of 90° and it is generally described as:

$$F_{lead}(s) = \frac{s + (p_1/\alpha)}{s + p_1}$$

(2.35)

where

$$\delta_m = \arcsin \frac{\alpha - 1}{\alpha + 1}$$

$$\omega_m = \frac{p_1}{\sqrt{\alpha}}$$

(2.36)

Figure 2.11: Bode plot of the notch and lead filters.

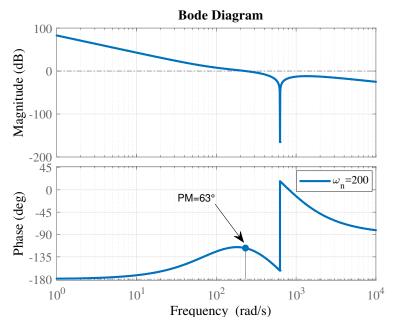

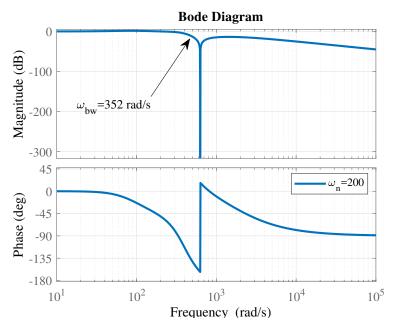

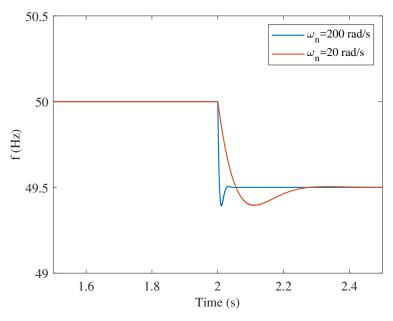

where  $\delta_m$  is the maximum phase of the lead filter and it occurs at frequency  $\omega_m$ . Fig.2.11 shows the frequency response of the notch and lead filters. The bode plot of the open and closed loop transfer function of the modified SRF-PLL is presented in Fig.2.12 and 2.13. The bandwidth of the modified SRF-PLL does not change significantly while maintaining enough phase margin and rejecting the negative-sequence fundamental component. In fact, the notch filter can be added at the harmonic frequency to mitigate the influence of the low order harmonics distortion from the grid voltage. The relation between the controller parameter  $\omega_n$  and the dynamic response of the PLL to the frequency change is verified in the simulation result (Fig.2.14). The grid voltage experiences a 0.5 Hz step down of the frequency at 2 s. The results shows that the SRF-PLL with higher natural frequency has faster response to the frequency change. Therefore, the SRF-PLL controller with higher natural frequency (also bandwidth) is desirable as it can quickly respond to the frequency variation of the grid voltage. The simulation and experimental tests are done in MATLAB/SIMULINK to verify the harmonics mitigation capability of the proposed SRF-PLL under a distorted voltage source (see Table.3.2)

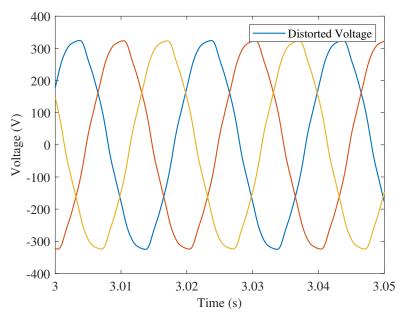

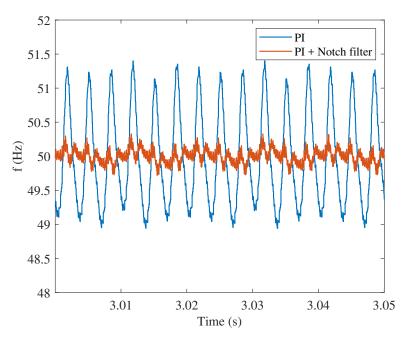

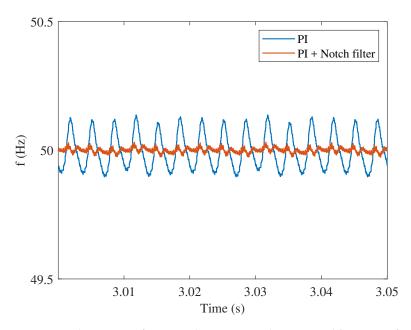

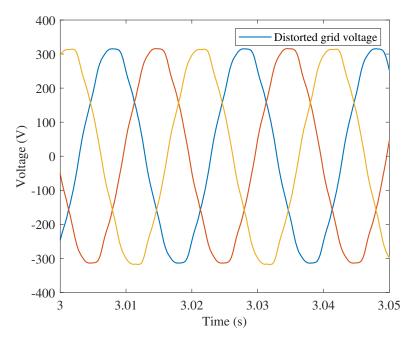

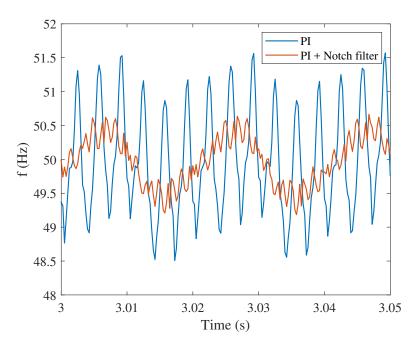

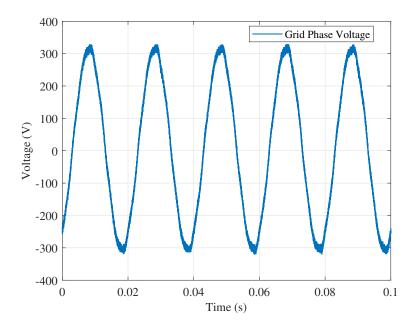

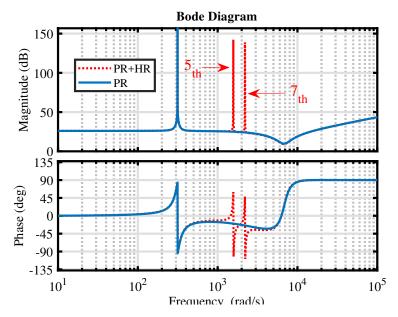

Fig.2.16 and 2.17 show the simulation results of the output frequency of the SRF-PLL with and without notch filter for different PI parameters. The distorted grid in simulation is shown in Fig.2.15 and the main harmonics are the  $5^{th}$  and  $7^{th}$  components.

The results show that with a larger  $\omega_n$ , the SRF-PLL has worse mitigation capability of the harmonics influence from the distorted grid. The implementation of the notch filter at  $6^{th}$  fundamental frequency can significantly reduce the harmonics ripple in the output frequency.

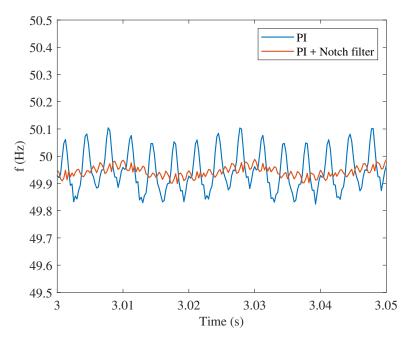

Fig.2.19 and 2.20 show the experimental results of the output frequency of the SRF-PLL with and without notch filter for different PI parameters. The distorted grid is shown

$\textbf{Figure 2.12:} \ \ \textbf{Bode plot of the open-loop transfer function of the modified SRF-PLL.}$

Figure 2.13: Bode plot of the closed loop transfer function of the modified SRF-PLL.

Figure 2.14: Dynamic response of SRF-PLL to the frequency drop of the grid voltage.

Figure 2.15: Distorted grid voltage in the simulation.

The experimental results also validated that the basic SRF-PLL (PI control only) does not have a good harmonics rejection capability. In order to achieve smaller harmonics ripple in the output frequency with basic SRF-PLL, a smaller bandwidth should

**Figure 2.16:** Simulation test of proposed SRF-PLL with  $\omega_n$ =200 rad/s: output frequency.

**Figure 2.17:** Simulation test of proposed SRF-PLL with  $\omega_n$ =20 rad/s: output frequency.

be chosen. The SRF-PLL with notch filter can effectively reduce the harmonics in the output frequency.

Figure 2.18: Distorted grid voltage in the experiment.

**Figure 2.19**: Experiment test of the proposed SRF-PLL with  $\omega_n$ =200 rad/s: output frequency.

**Figure 2.20:** Experiment test of the proposed SRF-PLL with  $\omega_n$ =20 rad/s: output frequency.

# Power Control

Provided that SRF-PLL works in steady-state condition, the current control loop is equivalent to power control loop because the active power and reactive powers are decoupled into separated control of d and q components of the controlled current based on eqs. (2.23) to (2.25). The power references can be converted into current references according to eqs. (2.37) and (2.38)

$$i_d^* = \frac{2}{3V_{gd}} P_s^* \tag{2.37}$$

$$i_q^* = -\frac{2}{3V_{gd}}Q_s^* (2.38)$$

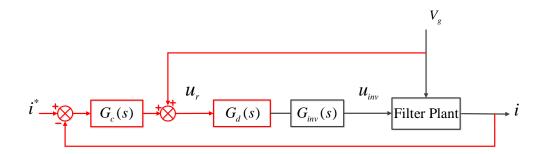

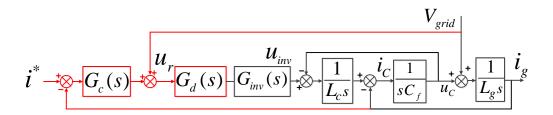

The simplified current control loop without detailed power plant is shown in Fig.2.22. $G_c(s)$ is the current controller and a PI control is adopted for  $G_c(s)$  in dq-frame:

$$G_c(s) = k_p + \frac{k_i}{s} \tag{2.39}$$

$G_d(s)$  represents the digital controller delay due to sampling and computation:

$$G_d(s) = e^{-sT} (2.40)$$

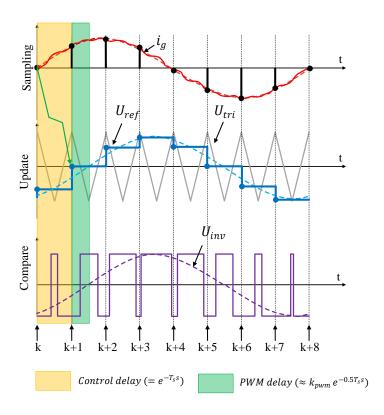

where T is the digital controller sampling period.(i.e.,  $T = T_s = \frac{1}{f_s}$ ) is applicable for typical digital implementations [27].  $G_{inv}(s)$  is the transfer function of the PWM modulator

and is called PWM delay. The PWM delay is approximately modelled as a zero-orderholder (ZOH) and  $G_{inv}$  can be mathematically derived by eq. (2.41) if synchronous PWM sampling is considered [28]:

$$G_{inv}(s) = \frac{1}{T_s} \frac{1 - e^{-sT_s}}{s} k_{pwm} \approx k_{pwm} e^{-0.5sT_s}$$

(2.41)

where  $k_{pwm}$  is the ratio between DC voltage and the amplitude of the triangular carrier. The single sampling and update of the digital controller in PWM process is illustrated in Fig.2.21. The control delay results in the time difference, which is labeled k in Fig.2.21. The total delay in the current control loop becomes  $1.5T_s$  when single update is adopted.

Figure 2.21: Digital controller delay and PWM zero-order hold effect (single update).

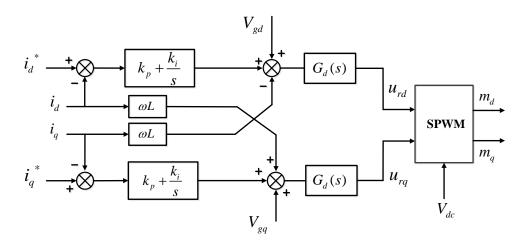

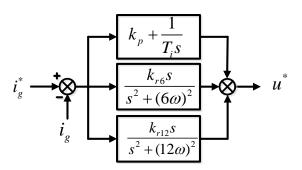

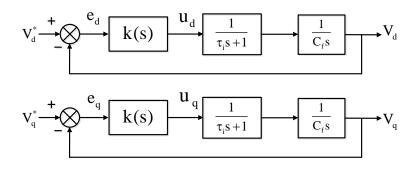

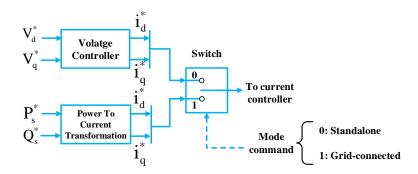

The grid voltage feed-forward is adopted in the current control to improve dynamic response of current to grid voltage disturbances [29]. The control diagram in dq-frame is illustrated in Fig.2.23. As it can be observed from the control diagram, a PI controller is used for the current loop compensator and  $i_d$ ,  $i_d$  are fed to the compensator output to decouple the dq-frame. SPWM technique is adopted in this thesis for the VSC modulation. The controlled current can be either grid-side current or converter-side current in the VSC with LCL filter. The choice of controlled current and the parameters design are discussed in Chapter.3.

Figure 2.22: Simplified current loop transfer function.

Figure 2.23: Current control diagram in *dq*-frame.

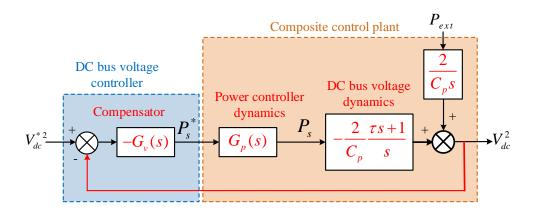

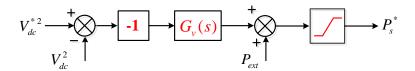

# DC-link Voltage Control