# M.Sc. Thesis

# Temperature-Constrained Power Management Scheme for 3D MPSoC

# Arnica Aggarwal

## Abstract

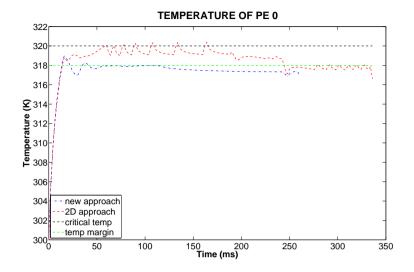

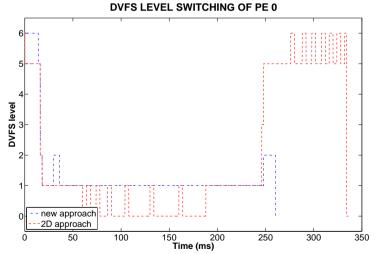

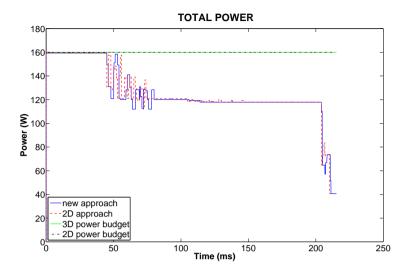

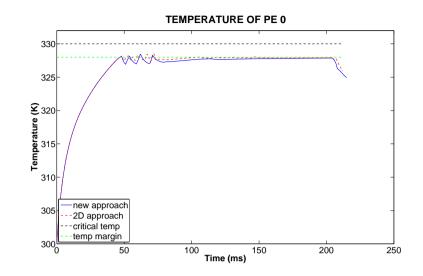

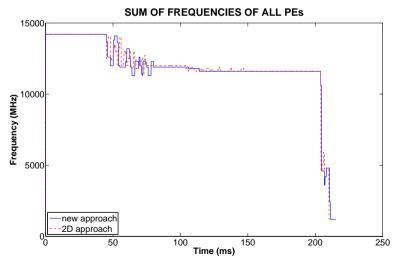

Process technologies are approaching physical limits making further reduction of device size and higher integration challenging. Threedimensional (3D) integration is emerging as an attractive solution to continue the pace of growth of System-on-Chips. Although vertical interconnection between the stacked dies has substantial benefits in terms of electrical performance, higher integration density aggravates the prevailing challenges of power density and consequently microelectronics cooling. This makes consideration of temperature constraints important while designing power management schemes. Dynamic Voltage and Frequency Scaling (DVFS) schemes in two-dimensional (2D) Multi-Processor System-on-Chip (MPSoC) do not consider thermal relation between various Processing Elements (PE) however this cannot be ignored in 3D stacks. In this thesis a new temperature constraint power management scheme for 3D MPSoC is proposed. Thermal relation between PEs is represented by the effective thermal resistance between them. These values along with PE's operating temperature, utilization and positional information are used to generate weights for each PE and voltage island. These weights are then used for scaling and imposing temporary constraints on operating voltage and frequency (V/F) levels of PEs in the stack. While scaling brings temperatures of all PEs below critical limits, imposing constraints on the V/F levels avoids significant fluctuations in operating temperatures. When compared to 2D DVFS, an improvement of up to 19.55% in overall execution time is achieved, temperatures are maintained at a safe margin from critical limits and stability in operating temperatures was observed.

# Temperature-Constrained Power Management Scheme for 3D MPSoC

## THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

ELECTRICAL ENGINEERING

by

Arnica Aggarwal born in Lucknow, India

This work was performed in:

Circuits and Systems Group Department of Microelectronics Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

**Delft University of Technology** Copyright © 2012 Circuits and Systems Group All rights reserved.

## Delft University of Technology Department of Microelectronics

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled **"Temperature-Constrained Power Management Scheme for 3D MP-SoC"** by **Arnica Aggarwal** in partial fulfillment of the requirements for the degree of **Master of Science**.

Dated: 20/12/2011

Chairman:

prof.dr.ir. A.J. van der Veen

Advisor:

dr.ir. T.G.R.M. van Leuken

Committee Members:

dr. Amir Zjajo

dr.ir. Said Hamdioui

# Abstract

Process technologies are approaching physical limits making further reduction of device size and higher integration challenging. Three-dimensional (3D) integration is emerging as an attractive solution to continue the pace of growth of System-on-Chips. Although vertical interconnection between the stacked dies has substantial benefits in terms of electrical performance, higher integration density aggravates the prevailing challenges of power density and consequently microelectronics cooling. This makes consideration of temperature constraints important while designing power management schemes. Dynamic Voltage and Frequency Scaling (DVFS) schemes in two-dimensional (2D) Multi-Processor System-on-Chip (MPSoC) do not consider thermal relation between various Processing Elements (PE) however this cannot be ignored in 3D stacks. In this thesis a new temperature constraint power management scheme for 3D MPSoC is proposed. Thermal relation between PEs is represented by the effective thermal resistance between them. These values along with PE's operating temperature, utilization and positional information are used to generate weights for each PE and voltage island. These weights are then used for scaling and imposing temporary constraints on operating voltage and frequency (V/F) levels of PEs in the stack. While scaling brings temperatures of all PEs below critical limits, imposing constraints on the V/F levels avoids significant fluctuations in operating temperatures. When compared to 2D DVFS, an improvement of up to 19.55% in overall execution time is achieved, temperatures are maintained at a safe margin from critical limits and stability in operating temperatures was observed.

Quoting Napoleon Hill, "Desire is the starting point of all achievement, not a hope, but a keen pulsating desire, which transcends everything." I had a desire when I set out to commence my Masters' study. I had a desire to do well. I had a desire to shape my career, to be the best at what I do, to make my parents proud of me. My work here at TU Delft, for my thesis provided me an ideal stepping stone to help me achieve my desire. However, it was not an easy going. There were numerous hurdles, problems, doubts, confusions. Without the help, support, love and nurturing from a number of people, I would not have reached this day where I can confidently say that I see my dreams coming true.

I would like to give a special thanks to my supervisor, Prof. Rene for providing me with the opportunity to work under his supervision. It was an enriching experience to be able to shape my own thesis. The freedom and the invaluable guidance to carry on the research has helped me to really get into the skin of things and confidently do the things my way. I have emerged a more knowledgeable, experienced and confident individual. Thank you Prof. Rene.

I would like to extend my sincere thanks to Amir Zjajo for discussing my work and providing valuable feedback. It gave a better understanding and clearer picture of things.

Sumeet, Thank you for the endless number of brainstorming sessions, for all your patience and constant motivation. Things always looked simpler after discussing them with you. Thank you, for the times you said "I have to" though it was a choice you made.. for being so humble and for being who you are.

Antoon, for instant help and for patiently fixing the things when I messed them up. Minaksie, for spreading smiles and for quick help with all administrative things.

Aashini, You are the reason that I am here today. When I was scared to look forward, you held my hand and walked along. Thanks for being there.

Radhika, The time we spent together is invaluable. The discussions, chats and gossips, coffees after long working hours, late night work and much more.. Thank you for being around and for not turning my side of the light on..! :)

Sundeep, Thanks for the energy and motivation you instilled in me, no matter what the challenge was, it gave that push. Also, for all the rice and sambhar u cooked :)

Sakshi and Dushyant, near or away, you have always been my strength.

Momi, Pa, Meghna, Prateek, Ajay, thanks for believing in me. Your love and support has always made survival easier and life a better place.

Arnica Aggarwal Delft, The Netherlands 20/12/2011

# Contents

| A        | Abstract v     |         |                                                       |          |  |  |  |  |  |  |

|----------|----------------|---------|-------------------------------------------------------|----------|--|--|--|--|--|--|

| A        | cknov          | wledgn  | nents                                                 | vii      |  |  |  |  |  |  |

| Li       | st of          | Abbre   | eviations                                             | xv       |  |  |  |  |  |  |

| 1        | Intr           | oducti  | ion                                                   | 1        |  |  |  |  |  |  |

|          | 1.1            | Motiva  | ation                                                 | 1        |  |  |  |  |  |  |

|          | 1.2            | Thesis  | Goals                                                 | 2        |  |  |  |  |  |  |

|          | 1.3            | Contri  | ibutions                                              | 2        |  |  |  |  |  |  |

|          | 1.4            | Thesis  | Organization                                          | 3        |  |  |  |  |  |  |

| <b>2</b> | Bac            | kgrour  | nd                                                    | <b>5</b> |  |  |  |  |  |  |

|          | 2.1            | 3D Int  | tegration Technology                                  | 5        |  |  |  |  |  |  |

|          | 2.2            | Power   | Dissipation                                           | 6        |  |  |  |  |  |  |

|          |                | 2.2.1   | Dynamic Power Dissipation                             | 6        |  |  |  |  |  |  |

|          |                | 2.2.2   | Static Power Dissipation                              | 7        |  |  |  |  |  |  |

|          |                | 2.2.3   | Conflict Between Dynamic and Static Power Dissipation | 8        |  |  |  |  |  |  |

|          |                | 2.2.4   | Total Power Dissipation                               | 9        |  |  |  |  |  |  |

|          | 2.3            | Relatio | on Between Power and Temperature                      | 9        |  |  |  |  |  |  |

|          | 2.4            | Therm   | al Modeling                                           | 10       |  |  |  |  |  |  |

|          | 2.5            | Power   | Management Schemes                                    | 13       |  |  |  |  |  |  |

|          |                | 2.5.1   | Voltage Island Partitioning                           | 13       |  |  |  |  |  |  |

|          |                | 2.5.2   | Dynamic Voltage Scaling (DVS)                         | 14       |  |  |  |  |  |  |

|          |                | 2.5.3   | Dynamic Frequency Scaling (DFS)                       | 15       |  |  |  |  |  |  |

|          |                | 2.5.4   | Dynamic Voltage and Frequency Scaling (DVFS)          | 17       |  |  |  |  |  |  |

|          | 2.6            | Relate  | ed Work                                               | 17       |  |  |  |  |  |  |

| 3        | $\mathbf{Sys}$ | tem M   | odeling                                               | 19       |  |  |  |  |  |  |

|          | 3.1            | Overvi  | iew                                                   | 19       |  |  |  |  |  |  |

|          |                | 3.1.1   | Importance of Power Budget                            | 19       |  |  |  |  |  |  |

|          |                | 3.1.2   | Thermal Management Techniques                         | 19       |  |  |  |  |  |  |

|          |                | 3.1.3   | DVFS                                                  | 20       |  |  |  |  |  |  |

|          |                | 3.1.4   | Approaches                                            | 20       |  |  |  |  |  |  |

|          | 3.2            | Contro  | ol Loop and System Modeling                           | 21       |  |  |  |  |  |  |

|          |                | 3.2.1   | Relation between Power and V/F Levels                 | 22       |  |  |  |  |  |  |

|          |                | 3.2.2   | Relation between Temperature and V/F Levels           | 23       |  |  |  |  |  |  |

|          | 3.3            | Summ    | ary                                                   | 33       |  |  |  |  |  |  |

| <b>4</b> | Power Management Scheme 35                |                                                                                                                                                                                                                                                                                                                                               |                                                                      |  |  |  |  |

|----------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|

|          | 4.1                                       | 1 Static Parameters                                                                                                                                                                                                                                                                                                                           |                                                                      |  |  |  |  |

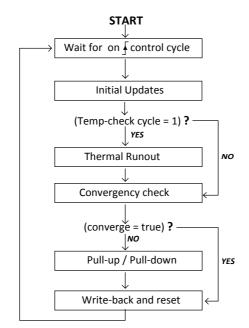

|          | 4.2                                       | Control Algorithm                                                                                                                                                                                                                                                                                                                             | 36                                                                   |  |  |  |  |

|          |                                           | 4.2.1 Initial Updates                                                                                                                                                                                                                                                                                                                         | 37                                                                   |  |  |  |  |

|          |                                           | 4.2.2 Thermal Runout                                                                                                                                                                                                                                                                                                                          | 38                                                                   |  |  |  |  |

|          |                                           | 4.2.3 Convergence Check                                                                                                                                                                                                                                                                                                                       | 40                                                                   |  |  |  |  |

|          |                                           | 4.2.4 Pull Up or Pull Down                                                                                                                                                                                                                                                                                                                    | 40                                                                   |  |  |  |  |

|          |                                           | 4.2.5 Write-Back and Reset                                                                                                                                                                                                                                                                                                                    | 42                                                                   |  |  |  |  |

|          | 4.3                                       | Summary                                                                                                                                                                                                                                                                                                                                       | 42                                                                   |  |  |  |  |

| <b>5</b> | $\mathbf{Res}$                            | ults and Discussion                                                                                                                                                                                                                                                                                                                           | 45                                                                   |  |  |  |  |

|          | 5.1                                       | Simulation Environment                                                                                                                                                                                                                                                                                                                        | 45                                                                   |  |  |  |  |

|          | 5.2                                       | Experimentation                                                                                                                                                                                                                                                                                                                               | 47                                                                   |  |  |  |  |

|          |                                           | -                                                                                                                                                                                                                                                                                                                                             | 48                                                                   |  |  |  |  |

|          |                                           |                                                                                                                                                                                                                                                                                                                                               | 52                                                                   |  |  |  |  |

|          |                                           | 5.2.3 Experiment 3                                                                                                                                                                                                                                                                                                                            | 55                                                                   |  |  |  |  |

|          |                                           |                                                                                                                                                                                                                                                                                                                                               |                                                                      |  |  |  |  |

| 6        | Con                                       | clusions and Future Work                                                                                                                                                                                                                                                                                                                      | 59                                                                   |  |  |  |  |

| 6        | <b>Con</b><br>6.1                         |                                                                                                                                                                                                                                                                                                                                               |                                                                      |  |  |  |  |

| 6        |                                           | Summary                                                                                                                                                                                                                                                                                                                                       |                                                                      |  |  |  |  |

| -        | $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | Summary                                                                                                                                                                                                                                                                                                                                       | 59<br>61                                                             |  |  |  |  |

| -        | $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | Summary                                                                                                                                                                                                                                                                                                                                       | 59<br>61<br><b>63</b>                                                |  |  |  |  |

| -        | 6.1<br>6.2<br><b>3D-</b>                  | Summary       Summary         Future       Work         ICE       Simulator         Introduction       Summary                                                                                                                                                                                                                                | <b>59</b><br>59<br>61<br><b>63</b><br>63                             |  |  |  |  |

| -        | 6.1<br>6.2<br><b>3D-</b><br>A.1           | Summary    Summary      Future Work    Summary      ICE Simulator      Introduction    Stack Description File                                                                                                                                                                                                                                 | 59<br>61<br><b>63</b><br>63                                          |  |  |  |  |

| -        | 6.1<br>6.2<br><b>3D-</b><br>A.1           | Summary                                                                                                                                                                                                                                                                                                                                       | 59<br>61<br>63<br>63<br>63<br>63                                     |  |  |  |  |

| -        | 6.1<br>6.2<br><b>3D-</b><br>A.1           | Summary                                                                                                                                                                                                                                                                                                                                       | 59<br>61<br>63<br>63<br>63<br>63<br>64                               |  |  |  |  |

| -        | 6.1<br>6.2<br><b>3D-</b><br>A.1           | Summary                                                                                                                                                                                                                                                                                                                                       | 59<br>61<br>63<br>63<br>63<br>64<br>65                               |  |  |  |  |

| -        | 6.1<br>6.2<br><b>3D-</b><br>A.1           | Summary                                                                                                                                                                                                                                                                                                                                       | 59<br>61<br>63<br>63<br>63<br>63<br>64<br>65<br>65                   |  |  |  |  |

| -        | 6.1<br>6.2<br><b>3D-</b><br>A.1           | Summary                                                                                                                                                                                                                                                                                                                                       | 59<br>61<br>63<br>63<br>63<br>63<br>63<br>63<br>64<br>65<br>65<br>66 |  |  |  |  |

| -        | 6.1<br>6.2<br><b>3D-</b><br>A.1<br>A.2    | Summary                                                                                                                                                                                                                                                                                                                                       | 59<br>61<br>63<br>63<br>63<br>63<br>63<br>63<br>64<br>65<br>65<br>66 |  |  |  |  |

| -        | 6.1<br>6.2<br><b>3D-</b><br>A.1<br>A.2    | Summary       Future Work         Future Work       Future Work         Introduction       Stack Description File         A.2.1       Materials         A.2.2       Dies         A.2.3       Conventional Air-Cooled Heat Sink         A.2.4       Stack         Floorplan File       Floorplan File         Used stack file       Stack file | 59<br>61<br>63<br>63<br>63<br>63<br>63<br>64<br>65<br>65<br>66<br>66 |  |  |  |  |

| $\begin{array}{c} 2.1 \\ 2.2 \\ 2.3 \\ 2.4 \\ 2.5 \\ 2.6 \\ 2.8 \\ 2.9 \\ 2.10 \\ 2.11 \end{array}$ | 3D integration technology using Through Silicon Via | $5 \\ 6 \\ 7 \\ 8 \\ 11 \\ 11 \\ 14 \\ 15 \\ 15 \\ 16 \\ 16 \\ 10 \\ 10 \\ 10 \\ 10 \\ 10 \\ 10$ |

|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------|

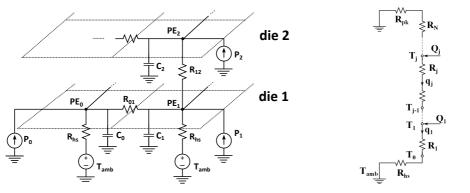

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                              | 3D voltage islands                                  | 20<br>22<br>26<br>26<br>28<br>29                                                                 |

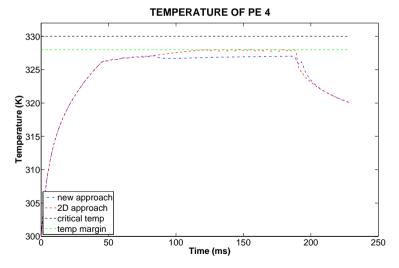

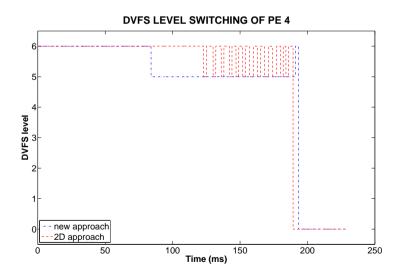

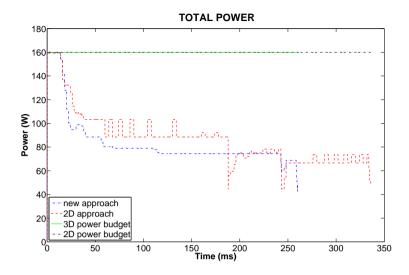

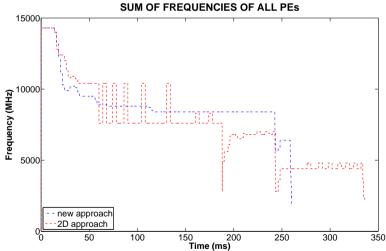

| $\begin{array}{c} 5.13 \\ 5.14 \end{array}$                                                         | Flowchart showing stages in Power Management Block  | $\begin{array}{c} 36 \\ 45 \\ 46 \\ 48 \\ 51 \\ 51 \\ 51 \\ 51 \\ 51 \\ 54 \\ 54 \\ 54$          |

# List of Tables

| 3.1 | Analogy between thermal and electrical parameters                         | 26 |

|-----|---------------------------------------------------------------------------|----|

| 3.2 | Change in temperature (in $K$ ) of PEs due to change in power dissipation |    |

|     | of a PE in a three tier 3D stack                                          | 29 |

| 3.3 | Dimensional and material parameters used for thermal model                | 30 |

| 4.1 | The static information stored beforehand for the use of power manage-     |    |

|     | ment block.                                                               | 35 |

| 4.2 | The dynamic information generated and store by power management           |    |

|     | block during run-time.                                                    | 37 |

| 5.1 | Performance losses with the two approaches in Experiment 2                | 53 |

| 5.2 | Comparison between per-core DVFS and DVFS in voltage islands              | 56 |

# List of Abbreviations

| 2D    | Two-Dimensional                        |

|-------|----------------------------------------|

| 3D    | Three-Dimensional                      |

| DFS   | Dynamic Frequency Scaling              |

| DVFS  | Dynamic Voltage and Frequency Scaling  |

| DVS   | Dynamic Voltage Scaling                |

| F2B   | Face-to-Back                           |

| F2F   | Face-to-Face                           |

| MPSoC | Muti-Processor System-on-Chip          |

| NoC   | Networks-on-Chip                       |

| PCB   | Printed Circuit Board                  |

| PMB   | Power Management Block                 |

| SoC   | System-on-Chip                         |

| TIM   | Thermal Interface Material             |

| TSV   | Through Silicon Via                    |

| V/F   | Voltage Frequency level or DVFS level. |

| VFI   | Voltage Frequency Island               |

|       |                                        |

# 1

# 1.1 Motivation

Miniaturization of microelectronic devices has led to a tremendous improvement in the performance of electronic products. However, scaling down the feature size of a transistor introduces limitations on the interconnect performance, the process variation and the leakage power consumption [1]. Total power dissipation and power density are at the limits of what packaging and cooling solutions can support [2]. Process technologies are approaching physical limits making reduction in device size and higher integration more challenging. 3-Dimensional (3D) Technology, i.e., vertical stacking of multiple silicon layers is emerging as an attractive solution to continue the pace of growth of SoCs. Through Silicon Via (TSV) provides vertical interconnection between the stacked dies which greatly reduces interconnection length and results in a smaller area footprint. Although 3D technology has some clearly established benefits in terms of electrical performance [1,3,4], it aggravates the prevailing challenges of power density [5] and microelectronics cooling [5–7], limiting the performance and the reliability of a stacked chip [7,8]. This makes consideration of temperature constraints important while designing power management schemes.

Reducing the power consumption of System-on-Chip (SoC) and Muti-Processor Systemon-Chip (MPSoC) has become increasingly important and challenging in electronic system designs, especially when powered by batteries. Low power designing approaches are used at every step of the design process, from software to architecture to implementation. Dynamic Voltage and Frequency Scaling (DVFS) is a commonly used architecture-level power management technique that allows a PE to operate at different voltage and frequency levels according to its changing workload [2,9–12]. A temperature constraint power management scheme for two-dimensional (2D) ICs addresses the temperature of each PE independently ignoring the thermal relation between PEs. [13] reported that in a 3D IC, thermal conductance in the vertical direction is 16 times of that in the lateral direction. Also, as the depth of a 3D stack increases, the heat transfer in the lateral direction also becomes prominent. Therefore, thermal relation between the PEs can no longer be ignored. Hence, a temperature constrained power management scheme for a 2D IC cannot be directly implemented in a 3D IC.

This thesis aims to propose a new temperature constrained power management scheme for 3D MPSoCs. It uses utilization factor, instantaneous temperature margin, positional details and area of a PE in a 3D stacked IC for calculating new operating DVFS levels. Utilization factor determines how busy a PE is and instantaneous temperature margin denotes the difference between the critical temperature and its actual temperature. Instantaneous temperature margin is monitored to ensure that each PE operates within the allocated temperature limits. Position of a PE refer to its location in the 3D stack, i.e., how far it is from the heat sink. Position and area also have a significant impact on temperature of a PE and power density in the stack. Hence, the effect of the two are also considered.

# 1.2 Thesis Goals

The differences between 2D power management schemes and an effective scheme for 3D ICs motivates the work presented in this report. The objectives of this thesis are:

- Design an effective temperature constraint power management scheme for 3D MPSoC.

- Include positional and thermal information in the power management scheme in order to address thermal dependencies.

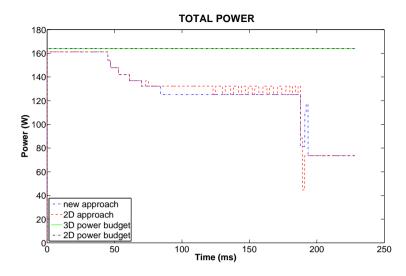

- Keep total power value below the set budget value.

- Effectively maintain temperatures of PEs below critical limits without significant loss in performance.

- Study the effectiveness of 3D islands in a stacked IC.

# **1.3** Contributions

This work presents a new approach for power management scheme in 3D stacked IC and is compared with a 2D DVFS scheme. The main contributions of this work are as follows:

- Various factors like instantaneous temperature margin of a PE, its positional information, area, and thermal relation between PEs are included in the power management scheme. These are used to calculate weights for PEs in order to effectively select a PE for scaling its DVFS level.

- Reduced total execution time by preventing PEs on the deeper tiers from being turned OFF.

- Effectively maintains temperatures at a safe margin below critical temperature and power below the budget value. Keeping temperature at a safe margin from the critical temperature ensures that the temperature never exceeds the critical limit even under unexpected circumstances like noise in power supply and sudden increase in workload of a PE.

- Shows less fluctuations in temperature due to higher stability in operating DVFS levels. To maintain the performance of devices over time, it is important to avoid fluctuations in temperature.

- Approach is effectively implemented on voltage islands as well as per-core level. 3D islands achieved further reduction in execution time when executing similar workloads. Granularity can be manipulated to achieve benefits of both, voltage islands as well as per-core DVFS.

- The effective resistance matrix for the PEs is derived for the target floorplan. Therefore, the location of PEs in the stack does not affect the algorithm of power management scheme.

# 1.4 Thesis Organization

This thesis is organised into the following chapters:

Chaper 2 introduces 3D Integration Technology and basic concepts of power management. Various sources of power dissipation and relation between power and temperature are presented. Power management schemes for 2D MPSoCs and feasibility of extending such schemes to 3D stacks are discussed. Further, thermal modeling of a 3D stacked IC is described and its difference from 2D thermal model is discussed. Lastly, importance of including thermal information in power management of 3D MPSoC is discussed along with a brief discussion on the related work in the field.

Chapter 3 details how the thermal model for the power management control is derived in this work. Heat transfer theory is discussed, a thermal model of a 3D IC is analyzed and the importance of transient analysis is presented, followed by the derived thermal model.

Chapter 4 presents the proposed power management scheme. Implementation of the scheme at voltage island and per-core level is explained. Design details and the complete control algorithm is presented.

Chapter 5 provides the details of simulation environment used for testing the power management scheme. Created testbench to provide inputs to the power management block is described. Details of performance measurements are discussed. Further, the conducted experiments are the obtained results are analyzed. First, a per-core DVFS scheme is demonstrated with lenient temperature constraints. To draw a better comparison, strict temperature constraint is imposed. A comparison is drawn between the new weighted approach and the conventional approach. Followed by the analysis of 3D voltage islands.

Chapter 6 concludes the thesis with a brief discussion on achieved goals and remarks for recommendations for future work.

This chapter introduces 3D Integration Technology and basic concepts of power management. The chapter details sources of power dissipation and relation between power and temperature. Various power management schemes for MPSoCs, feasibility of extending such schemes to 3D stacks and need of dc-dc converters are discussed. This chapter also describes the thermal modeling of a 3D stacked IC, its importance in power management of 3D MPSoC and how it is different from 2D thermal models. The chapter is concluded with a brief discussion on the related work.

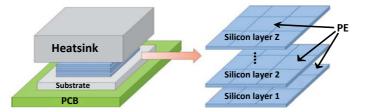

# 2.1 3D Integration Technology

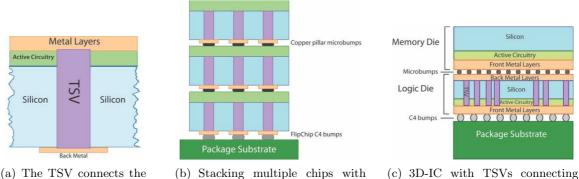

Technology scaling has led to a tremendous improvement in the performance of electronic products over decades. The continuation of this trend seems difficult as several process technologies are approaching physical limits making further reduction of device size more challenging by introducing limitations on the interconnect performance, the process variation and the leakage power consumption [1]. Wires consume more than 30% of the power within a microprocessor [4]. Total power dissipation and power density are at the limits of what packaging and cooling solutions can support [2]. 3D integration technology has attracted significant attention in recent past. An example of a 3D integrated IC is shown in Figure 2.1.

front metal to the back metal layers.

(b) Stacking multiple chips with TSVs together to create a 3D-IC

(c) 3D-IC with TSVs connecting front and back metal layers

Figure 2.1: 3D integration technology using Through Silicon Via(TSV)

Figure 2.1(a) shows how vertical interconnection between the stacked dies is achieved using TSVs which greatly reduced interconnection length and result in a smaller area footprint. It is expected to address interconnect delay related problems and enable integration of heterogeneous technologies [14]. Shorter interconnects would help reduce total power dissipation, but, due to closed packed multi-layer structure, the power density would be significantly high. 3D integration technology thus provides new microarchitecture opportunities to trade-off performance, power and area [4].

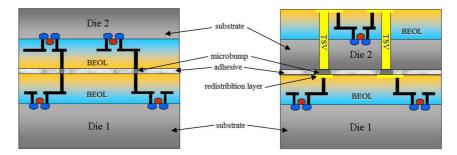

Figure 2.2: Ways of wafer stacking based on the stacking orientation of two device wafers. Left:F2F, Right:F2B [15]

Based on the stacking orientation of two device wafers, there are two different ways of wafer stacking: face-to-face (F2F) and face-to-back (F2B) as shown in Figure 2.2. As the names suggest, in F2F configuration, dies are bonded face-to-face with microbumps, while in F2B configuration, dies are bonded back-to-face and TSVs are used for intertier connections. F2F configuration does not require TSVs for bonding if the stack consists of only two tiers (dies), as seen in Figure 2.2. But, bonding more than two dies requires TSVs to provide through silicon bonding of metal layers and the design no longer remains F2F alone. While in F2B configuration, the structure is homogeneous and symmetric with equal lengths of TSVs for equal bulk thickness. For this reason, a F2B bonding for multiple layered 3D stack is considered in this thesis.

# 2.2 Power Dissipation

CMOS is a predominant process technology for digital circuits. Power dissipation for these circuits can be accurately modeled using equations, even for complex processors [2]. These models along with the knowledge of system architecture can be used to analyze the system for energy and power consumption. There are two main sources of power dissipation - static power and dynamic power. These are explained in the following subsections.

#### 2.2.1 Dynamic Power Dissipation

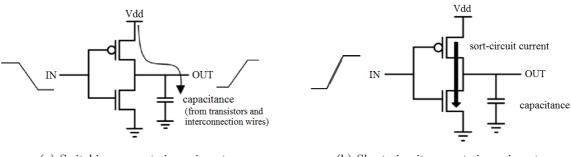

Dynamic power is the power dissipated by the device when it is active i.e., when signals are switching. The two main sources of dynamic power are switching power and power due to short circuit current.

Switching power is the power dissipated in the transistors during charging and discharging of the load capacitor, as shown in Figure 2.3. Switching power can be given

(a) Switching currents in an inverter

(b) Short-circuit currents in an inverter

Figure 2.3: Switching and short-circuit currents in an inverter [2].

by the following expression.

$$P_{switching} = C_{eff} \cdot V_{DD}^2 \cdot f_{clock} \tag{2.1}$$

where,

$$C_{eff} = \alpha.C_L$$

(2.2)

Where,  $\alpha$  is the switching activity,  $C_L$  is the load capacitance,  $V_{DD}$  is the supply voltage and  $f_{clock}$  is the clock frequency.

An input signal always has a finite slope which causes a direct current path between supply and ground for a short period of time during switching. During this period, the PMOS and the NMOS conduct simultaneously. This short circuit current also results in power dissipation, as shown in Figure 2.3(b). Power dissipation due to short-circuit current can be given by the following expression.

$$P_{sc} = t_{sc}.V_{DD}.I_{peak}.f_{clock}$$

$$\tag{2.3}$$

Where,  $t_{sc}$  is the time duration of the short circuit current and  $I_{peak}$  is the internal switching current i.e., the sum of short-circuit current and the current required to change the internal capacitance.

The dynamic power can be given by the following expression.

$$P_{dyn} = P_{switching} + P_{sc} \tag{2.4}$$

$$= (C_{eff} V_{DD}^2 f_{clock}) + (t_{sc} V_{DD} I_{peak} f_{clock})$$

$$(2.5)$$

As long as the short-circuit time( $t_{sc}$ ) of the input signal is kept short, switching power dominates in the above equation. Hence dynamic power can be given by the following equation.

$$P_{dyn} \approx C_{eff} V_{DD}^2 f_{clock} \tag{2.6}$$

The equation shows that dynamic power has direct dependence on  $f_{clock}$  and quadratic dependence on  $V_{DD}$ . Reducing these parameters help reducing dynamic power.

#### 2.2.2 Static Power Dissipation

The static (or leakage) power dissipation in a digital CMOS circuit is associated with maintaining the logic values of internal circuit nodes between the switching events i.e., when signals hold fixed values [16]. It is expressed by the following relationship [16]:

$$P_{static} = I_{static} V_{DD} \tag{2.7}$$

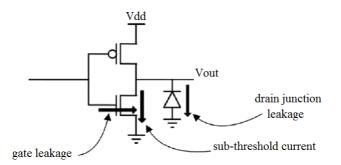

where  $I_{static}$  is the current that flows between the supply rails in the absence of switching activity. Various leakage currents are shown in Figure 2.4. Main sources of leakage current in a CMOS gate are sub-threshold leakage current ( $I_{sub}$ ), gate leakage current and reverse bias leakage current (drain junction leakage) [2].

Figure 2.4: Leakage currents through an inverter [2].

Sub-threshold leakage current occurs when a gate is not turned off completely. Its approximate value can be given by the following equation [2]:

$$I_{sub} = \mu C_{ox} V_{th}^2 \frac{W}{L} \cdot e^{\frac{V_{GS} - V_T}{nV_{th}}}$$

(2.8)

Where  $\mu$  is the carrier mobility,  $C_{ox}$  is the gate capacitance,  $V_{th}$  is the thermal voltage, W and L are the width and the length of the transistor respectively,  $V_{GS}$  is the gate-source voltage,  $V_T$  is the threshold voltage and parameter n is the function of device fabrication process. Thermal threshold is denoted by kT/e where k is Boltzmann constant, T is Temperature and e is the electron charge. The equation shows leakage current increases quadratically with temperature and exponentially with difference between  $V_{GS}$  and  $V_T$  and putting a constraint on reduction in  $V_T$ . This constraint leads to a conflict between dynamic and static power which is discussed in the next subsection. Few of the approaches to minimize leakage current are to use multiple- $V_T$ cells to build circuits and shutting down the power supply to the block when not active.

#### 2.2.3 Conflict Between Dynamic and Static Power Dissipation

Equation 2.6 suggests that reducing  $V_{DD}$  can help achieving a lower dynamic power. But, reducing  $V_{DD}$  (hence  $V_{GS}$ ) has a negative impact on the ON(drive) current of the transistor, thus reducing the speed of the device. A simple approximation of the ON current is presented in the following equation [2].

$$I_{DS} = \mu C_{ox} \frac{W}{L} \cdot \frac{(V_{GS} - V_T)^2}{2}$$

(2.9)

Above equation shows the quadratic dependence of  $I_{DS}$  on  $(V_{GS} - V_T)$ . Hence, to keep up with performance,  $V_T$  should also be reduced when  $V_{GS}$  is reduced. But, in Equation 2.8 shows that  $I_{sub}$  increases exponentially with  $(V_{GS} - V_T)$ . It is important to keep  $(V_{GS} - V_T)$  high for good performance but low for less static power dissipation. This leads to a trade-off and hence putting a limit on the supply and threshold voltage.

#### 2.2.4 Total Power Dissipation

Total power dissipation is the sum of static and dynamic power dissipation. As discussed above, static current can be taken care of during physical implementation of the circuits (e.g., use of Multi- $V_T$  cells). Increasing temperature of the device increases the leakage current hence monitoring and controlling temperature is important to control the leakage current and static power. Each PE in a SoC or MPSoC has a specific critical (threshold) temperature exceeding which can lead to temperature-related reliability issues such as time-dependent dielectric breakdown. In this thesis, static power is not addressed directly, but total power is controlled by taking dynamic power and temperature into account. Temperature is monitored and controlled to limit a PE's temperature below its critical temperature value. Dynamic power is controlled by monitoring the activity rate of the core.

## 2.3 Relation Between Power and Temperature

High operating temperature of a PE has a significant impact on its design [17]. Carrier mobility degrades at higher temperatures making a transistor slower [18]. Resistivity of the interconnect metal is higher at higher temperatures, causing longer interconnect RC delays and degradation in performance. Also, it was seen in Section 2.2, leakage power depends exponentially on operating temperature. Increasing the temperature of a device exponentially decreases its lifetime [17] making a significant impact on its reliability. Hence, it is very important to keep devices below critical temperature making it is an important goal for chip designers.

As discussed in previous sections, technology miniaturization has an unfortunate side effect of increasing power densities which translates into increased heat dissipation. A PE consumes electrical energy and dissipates a part of it during switching of the devices in the form of heat due to the impedance of the electronic circuits. At system-level, temperature of a PE can be controlled by controlling its dynamic power.

Other sources of heat generation in VLSI systems are the leakage energy inside the transistors and electrical current flows through on-chip metal interconnects that connect the transistors. CMOS transistors are not ideal switches. Despite being OFF, they still conduct some amount of current. This leakage current moves charges between power supply and ground, thus drawing energy from the power supply. This energy is wasted without performing useful computation and is dissipated as heat through the resistance in their flow path. In addition to the heat generated inside the transistors, heat is also dissipated when electrical current flows through on-chip metal interconnects

that connect the transistors. This is because the interconnects are not ideal electrical conductors and have finite amount of resistance.

In summary, heat is generated from the silicon active surface due to two factors active switching and leakage. The power consumed by the IC is dissipated in the form of heat in the transistors and interconnects, and are eventually removed to the environment by heat transfer.

Energy and power are related by the following equation.

$$Energy = Power * Time \tag{2.10}$$

As P (power), is the rate of energy consumption and Q, is the rate of heat (energy) dissipation, it can be said that

$$Q = P \tag{2.11}$$

Heat transfer equation, as given in [19] for a volumetric system is shown in Equation 2.12 where  $C_{th}$  is thermal capacity of the material,  $R_{th}$  is the thermal resistance of the material and  $\Delta T$  is the change in temperature of the control volume. The first term on the left hand side in this equation represents the amount of heat stored in the volume and second term represents the loss of heat from the volume due to heat conduction. The term on the right hand side is a translation of dissipated power as seen in Equation 2.11, hence the equation shows the relation between change in temperature of a volume and the power dissipation. This relation will be explored further in the next chapter where thermal model for the 3D stack will be derived for the power management control.

$$C_{th}\frac{dT}{dt} - \frac{\Delta T}{R_{th}} = Q \tag{2.12}$$

## 2.4 Thermal Modeling

Since power dissipated and resulting temperature are co-related<sup>1</sup>, they should be handled simultaneously. To be able to handle temperature effects, an accurate thermal model is necessary. This thesis aims at developing a power management scheme, hence a previously developed thermal simulator is used to develop thermal model. This section discusses previous and related work where thermal models have been developed for use at architecture-level.

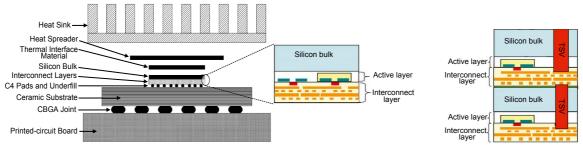

A stacked chip package is illustrated in Figure 2.5(a). The heat is generated in the active layer between silicon bulk and interconnects. There are two heat removal paths for such a package model. The primary heat removal path consists of the silicon bulk, thermal interface material (TIM), heat spreader and the heat sink. A significant amount of heat is also dissipated through the secondary heat removal path, i.e., across interconnect layers, pads and to the printed-circuit board (PCB). 3D-IC designs are similarly

<sup>&</sup>lt;sup>1</sup>Power is dissipated in form of heat, rising the temperature of the device. While rise in temperature increases static power dissipation in the device further increasing the temperature of the device.

(a) Stacked layers in a typical ceramic ball grid array (CBGA) package [17,20].

(b) multiple tiers in 3D-IC design [20].

Figure 2.5: 3D stacked layered structure of a chip package.

stacked-layer structures with multiple silicon bulk, active layer and interconnect layers. Figure 2.5(b) shows a 3D-IC design with two tiers, hence having two active layers. Since heat in generated in active and interconnect layer, as the number of tiers increase, generated heat also increases.

There has been a considerable amount of research in developing compact thermal models for 3D ICs. Works [17] and [5, 21] have developed simulation tools HOTSPOT and 3D-ICE respectively to model temperatures on a chip. Both the works use finitedifference based methods.

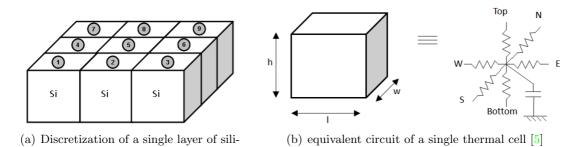

The models are generated by considering that each layer is divided into "thermal cells" as shown in Figure 2.6(a). Each thermal cell of length l, width w and height h, can be modeled as a node containing six resistances representing heat conduction in all six directions, and a capacitance representing heat storage in the cell as shown in Figure 2.6(b).

Figure 2.6: Discretization of a single layer of silicon into thermal cells and equivalent circuit of a single thermal cell.

con [5]

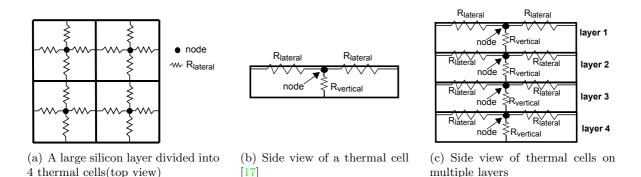

Figure 2.7(a) shows the top view of a large silicon layer divided into 4 thermal cells. Node is considered to be the heat source in a thermal cell. The dimension of these cells determine the accuracy of the resulting thermal model. Smaller the size of the cell,

Figure 2.7: Top and side view of partitioned thermal cells on a silicon layer showing lateral and vertical thermal resistances.

more accurate it is. Figure 2.7(b) shows the side of a layer where the lateral resistance  $(R_{lateral})$  is the thermal resistance on the same layer between adjacent thermal cells, whereas, vertical resistance  $(R_{vertical})$  is the thermal resistance between two thermal cells on adjacent layers. Since 2D-IC has only one pair of active and interconnect layer, therefore only two layers have heat sources. While in 3D-IC, multiple active and interconnect layers provide multiple heat sources in the vertical direction. For example, in Figure 2.7(c), if a heat sink is assumed to be on top of the stack, thermal resistance between a node on layer 4 and the heat sink is more than the thermal resistance between a node on layer 1 and heat sink. This results in a lower transfer of heat from a deeper layer to the heat sink.

The conductance of each thermal resistance and the capacitance of a cell as given in [5, 17] are as follows:

$$g_{top/bottom} = k_{Si} \cdot \frac{l \cdot w}{(h/2)}$$

$$g_{north/south} = k_{Si} \cdot \frac{l \cdot h}{(w/2)}$$

$$g_{east/west} = k_{Si} \cdot \frac{w \cdot h}{(l/2)}$$

$$c_{cell} = C_{vSi} \cdot (l \cdot w \cdot h)$$

$$(2.13)$$

From these equations, it can be seen that conductance depends on the area of crosssection in the direction of heat flow. The cross-sectional area for heat flow in the vertical direction  $(w^*l)$  for a PE will be much larger than that for the flow in lateral direction  $(w^*h \text{ or } l^*h)$ . Therefore, the heat transfer in the vertical direction is more significant than that in the lateral direction. Since dies in a 3D IC are stacked on top of each other, the heat flow from a PE on one die will strongly affect the temperature of the section of a die just above and/or below it. And, all PEs in a 3D stack are thermally connected, hence the temperature of one PE affects the temperature of all other PEs in the stack.

From the above discussion, two important deductions can me made:

- Conductance in the vertical direction is more than that in the lateral direction.

- Farther the heat source from the heat sink, lesser the heat transferred.

The two deductions based on the difference in the thermal models of 3D-IC and 2D-IC show the importance of considering an appropriate thermal model. Both simulators are derived considering stacking of layers and heat transfer in all directions. But, HOTSPOT thermal simulator does not directly address 3D ICs, whereas, 3D-ICE simulator is developed to support multi-processor 3D ICs. Hence 3D-ICE thermal simulator is used for the purpose of thermal simulations and generating conductance matrix for the power management control in this thesis.

## 2.5 Power Management Schemes

So far, importance of power management and simultaneous consideration of thermal management in 3D MPSoCs have been discussed. There are various power management schemes for MPSoCs at architecture-level that are currently used in many designs. This section briefly discusses these power management schemes, feasibility of extending such schemes to 3D MPSoCs and work to this thesis.

#### 2.5.1 Voltage Island Partitioning

It was seen in Equation 2.6 that dynamic power is proportional to  $V_{DD}^2$ . Reducing  $V_{DD}$ in selected blocks can reduce power significantly. It was also seen in ?? that reducing  $V_{DD}$  can increase the delay through the gate making the device slower hence putting a constraint on minimum  $V_{DD}$ . But, the complete chip can be divided into blocks (islands) where each block operates on different supply voltages. Hence, each block has its independent supply voltage. Depending on the voltage reduction, power saving can be achieved with losses in performance. The chip is first divided into multiple small tiles, and then each tile is allocated to an island. Partitioning of the complete chip in islands in known as Voltage Island Partitioning and is shown in Figure 2.8 where 4 tiles are divided amongst 3 voltage islands. It is a widely practiced in 2D chips. For communication between these islands, level shifters are used which result in some power and area overhead. Island partitioning algorithms decide operating voltage level for each tile considering the performance losses, power energy relationship and overheads due to level shifters. More number of islands can achieve finer control over performance loss and power of each tile, but overheads due to level shifters introduces a trade-off between number of islands and power saving. An algorithm for voltage frequency island partitioning for 2D Networks-on-Chip (NoC) is proposed in [22]. It also shows that optimal number of islands for a 3X3, 4X4 and 5X5 mesh network is either 2 or 3. Increasing the number of islands beyond this optimal value does not result in further improvement of power due to overheads.

Voltage assignments to these islands can be static or dynamic. Static voltage assignment assigns a single, fixed voltage level to each island. Figure 2.8 is an example of

Figure 2.8: Voltage island partitioning for a 2X2 network with static voltage assignment [22].

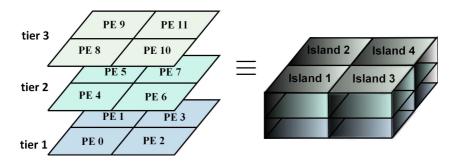

static voltage assignment. Whereas, in dynamic voltage assignment, the islands are allowed to operate at multiple voltages over time. This approach of allowing voltage to scale dynamically is known as Dynamic Voltage Scaling(DVS) and is discussed later in this section. Works [23] and [24] have applied voltage island partitioning on 3D ICs. [24] compares the 2D Voltage Frequency Islands(VFI) and 3D VFI. Since the work uses VFI, each PE in an island operates at same voltage as well as frequency. Whereas, if the two components are made independent, better flexibility can be provided to each PE. Work [24] proposed a post-placement multiple supply voltage assignment method for partitioning voltage islands. The work has considered an example of 3-tiers, and have divided the islands with static voltage assignment such that each island is a 3D block, each comprising sections of each tier.Voltage islands may be effective in case of 3D MPSoCs when groups of PEs run similar workload. Dynamic voltage islands are considered in this thesis.

#### 2.5.2 Dynamic Voltage Scaling (DVS)

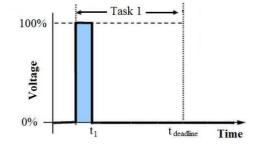

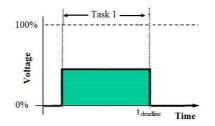

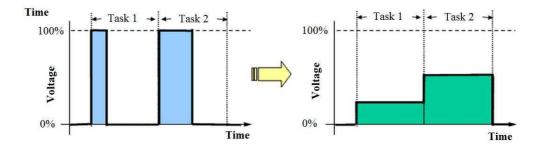

As discussed, lower  $V_{DD}$  reduces power dissipation with some degradation in performance. But, if a PE is allowed to adjust its  $V_{DD}$  dynamically depending on the performance requirement, the degradation in performance can then be maintained within the desirable limits. Figure 2.9(a) shows an example where deadline of a PE's task is time  $t_{deadline}$ , whereas task is completed by time  $t_1$  when the PE is operating at maximum  $V_{DD}$ . If the supply voltage is scaled down as shown in Figure 2.9(b), the task not only completes within the allocated time but also reduces the power dissipation. The advantage of using DVS over fixed voltage islands can be seen in Figure 2.10 where voltage is scaled so as to meet the deadlines and PE is not forced to operate at one operating voltage.

Various algorithms have been used over years to intelligently monitor the processor's utilization and activity, to scale the supply voltage accordingly. DVS can be implemented to each PE independently, or on islands of PE, depending on the target application of the MPSoC. Voltage islands introduce an overhead due to level shifters necessary for communication between islands and so does DVS. Also, enabling DVS requires additional circuitry to allow the islands or individual PEs to have multiple

(a) task 1 having a deadline of  $t_{deadline}$ , operating at 100%  $V_{DD}$  and completes the task in time  $t_1$

(b)  $V_{DD}$  is scaled such that the task utilizes the completes allocated time i.e.,  $t_{deadline}$  resulting in power saving

Figure 2.9: Dynamic Voltage Scaling to achieve power reduction.

Figure 2.10: Example showing efficient utilization of allocated time by dynamically scaling voltage to achieve power reduction [25].

supply voltages, adding to the overheads. This can be done in two ways.

- By having fixed power grids for the supported voltages and allowing the PEs to select the appropriate supply line using switches; or

- Incorporating voltage converters to generate the required voltages dynamically.

Since former approach requires fixed grid for supported voltage levels, there is a constraint on number of supported voltage levels. Whereas, voltage converters can provide more number of operating voltages. Design issues with voltage converters/regulators will be discussed later in this section. In 90nm and below nodes, there is not sufficient headroom to achieve desired power saving using DVS [2]. Hence, addition power saving by scaling  $f_{clock}$  (Equation 2.6) is explored.

#### 2.5.3 Dynamic Frequency Scaling (DFS)

As seen in Equation 2.6, power also depends directly on frequency. But, reducing the frequency leads to increased execution time which relates to performance and energy. The average power value of the PE reduces but the energy saving depends on the type of operation, i.e., memory bound operation or processor bound operation. A memory bound operation spends majority of its execution time in the memory, while a processor

bound operation spends majority of its execution time in the processor. This can be explained with the help of Equation 2.14. Energy is the integral of the power dissipation over execution time which gives the following relationship:

$$P \propto V_{DD}^2 f_{clock}$$

and  $E \propto V_{DD}^2 f_{clock} T_{exe}$  (2.14)

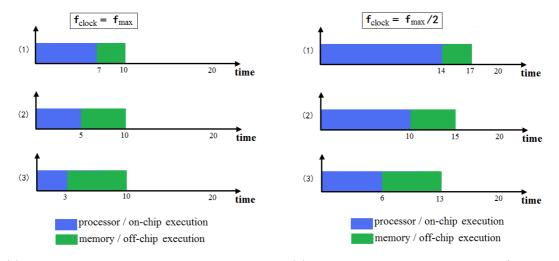

where  $T_{exe}$  is the execution time. For example, if  $f_{clock}$  is reduced to half, the energy saving depends on the product of  $f_{clock}$  and  $T_{exe}$ . Reducing  $f_{clock}$  to half does not mean that  $t_{exe}$  would double because  $t_{exe}$  depends on the type of operation i.e., memory bound or processor bound. This can be explained further with the help of Figure 2.11 where three tasks are shown. In Figure 2.11(a),  $f_{clock}$  is set to the maximum frequency

(a) Three tasks operating at  $f_{max}$  and with equal execution time.

(b) Same set of tasks running at  $f_{max}/2$ . Final execution time depending on whether the execution is processor bound or memory bound.

Figure 2.11: Dynamic Frequency Scaling to achieve power reduction.

of the PE and the three tasks execute in 10 time units where task (1) spends 70% (7 units) in processor execution and rest 30% (3 units) in memory execution. Whereas, when the same task in run with  $f_{clock}$  set to  $f_{max}/2$  i.e., half of previous case, the execution time does not double as can be seen in Figure 2.11(b). This is because only the processor execution time will get doubled and the memory execution time remains the same. So is the case with task (2) and (3). As the task becomes more memory bound, the execution time inside the processor reduces, hence achieving more energy saving. Performance penalty can be given by the following equation:

$$PerformancePenalty(\%) = \frac{increase in execution time}{execution time with maximum frequency} * 100\%$$

(2.15)

DFS is one of the considered approaches in this thesis.

#### 2.5.4 Dynamic Voltage and Frequency Scaling (DVFS)

Reducing the operating frequency in case of DFS also allows reduction in supply voltage. Reducing the supply voltage in combination with frequency is known as Dynamic Voltage and Frequency Scaling (DVFS). As the speed of a device depends on its operating voltage level, this introduce a constraint on maximum frequency for an operating voltage level. A major requirement for implementing an effective DVFS technique is to accurately predict the time-varying processor workload for a given computational task. As seen in Figure 2.11 and Equation 2.15, more energy is saved achieving underperformance when processor utilization is less. Therefore, monitoring a processor workload and adjusting the operating frequency and voltage based on the its utilization factor can achieve significant power saving. That is, decrease or increase the frequency and voltage when the processor utilization is low or high, respectively. DVFS is a popular power management method and is also used as a thermal management scheme to control on-chip temperatures [26] due to power-temperature relationship. Thus DVFS has been used in this thesis to achieve a temperature constrained power management scheme along with DFS and voltage island partitioning.

# 2.6 Related Work

Various power management schemes were discussed in the previous section. DVFS, DFS and voltage island partitioning are used in this thesis to build a temperature constraint power management control for 3D-MPSoC. Voltage and frequency scaling can be done on individual PEs or on islands. Work [27] compares per-core<sup>2</sup> DVFS and chip-wide<sup>3</sup> DVFS. The work shows that systems running heterogeneous workloads can benefit from per-core DVFS schemes. As various PEs running different workloads have different performance requirements allowing these PEs to operate at different voltages and/or frequencies achieves higher power saving. This is due to the fact that the PE with lower workload is allowed to operate at a lower operating voltage and/or frequency, independent of the PE with high performance requirement. Also, it was shown that the applications that are highly processor-bound offer fewer frequency-scaling opportunities and hence not much difference in power reduction can be seen in the per-core DVFS when compared with chip-wide DVFS. This is due to the high instruction execution time spent inside a PE.An intermediate case would be to have voltage/frequency islands where each island can have several PEs that operate on same voltage and/or frequency. Similar approach is considered in [12] where chip is divided into Voltage Frequency Islands (VFIs) and cores in a VFI operate at same voltage and frequency. This work also compares the energy and power reduction achieved with different VFI granularities. The work concludes that, increasing the VFI granularity can offer better flexibility in choosing voltage and frequency levels, but does not necessarily translate into better energy-efficiency. Extending the approach of island partitioning to the 3D IC can be done in two ways. First, by considering 2D islands on dies of a stack. Second, by

<sup>&</sup>lt;sup>2</sup>per-core DVFS refers to the individual setting of the voltage and the frequency levels for the PEs

$<sup>^{3}</sup>$ chip-wide DVFS refers to the single global setting of the voltage and the frequency levels for the complete chip

making islands 3D, i.e., allowing PEs from various dies to form an island. 3D islands can prove to be efficient as the PEs will not only have similar performance requirements but will also be thermally related. Work [24] has proposed a post-placement island partitioning and voltage assignment method for 3D ICs by considering delay caused by power reduction, timing slack, temperature analysis and power density. Islands operating at various supply voltages are used in this thesis to study their effectiveness and to draw a comparison between various approaches.

In [28], a temperature constrained power management scheme for a Chip Multiprocessors (CMPs) using DVFS is proposed but it addresses PEs in a 2D-IC. The temperatures of PEs are considered independently. Since PEs in a 3D stack have strong thermal relation with each other, a 2D temperature constrained power management scheme such as [28] can not be directly extended to 3D chips. Implementation of such a scheme on 3D-IC is studied in this thesis and is compared with the proposed approach. [28] also includes an on-line model estimator for systems with heterogeneous workloads, which is not considered here. [29] analyzes the thermal profile of a 3D stacked MPSoC and proposes an active cool solution using inter-tier liquid cooling along with a DVFS scheme. Sabry et. al. [29] also state that management techniques with passive control elements alone, like DVFS, are incapable of reducing temperature of the 3D stacked MPSoC systems efficiently. They also mention that increased power densities, number of tiers and number of cores increase, raise the temperature of the cores to extreme values in 3D MPSoCs. This results in severe restrictions in high-performance 3D MP-SoC design making other cooling methods for a 3D MPSoC important. These may include inter-tier cooling suggested in [29] or thermal TSVs suggested in [30] or thread scheduling along with schemes like DVFS as proposed in [13]. Nevertheless, considering temperature constraints in power management schemes can provide a support to the thermal management unit for such chips and also ensure that temperature of a PE never crosses the critical limits.

This chapter describes the system modeling for the power management scheme. First, an overview is presented where importance of power budget, thermal management techniques and DVFS are described. Next, the voltage island and per-core DVFS approaches that are considered in this thesis are explained. Further, the used control strategy is presented with the required system modeling and detailed thermal model.

# 3.1 Overview

# 3.1.1 Importance of Power Budget

Power budgets are employed to ensure that actual power consumption of the chip (or constituent logic block) never exceeds the desired fixed value. Operating PEs in an MPSoC at higher voltage or frequency achieves better performance but at the cost of higher power dissipation. These can also lead to unacceptable temperatures on the chip. These thermal and power dissipation problems can be reduced by setting a power budget to the complete chip or on the constituent logic blocks. These budgets restrict the maximum power dissipation of the chip or the logic block at the cost of performance. Excessively low power budgets would lead to higher performance losses.

# 3.1.2 Thermal Management Techniques

Thermal management techniques can be either reactive or proactive. While the former reacts to the current temperature value of the target PE, latter predicts the future temperature value and acts accordingly. Proactive techniques are usually accompanied by task scheduling where the prior information of temperature values are used to assign tasks accordingly. This helps in keeping PEs with higher predicted temperature less active. DVFS schemes use reactive methods in order to serve performance requirements of the PEs and react to the temperature values when necessary. The power management control does not have the information of the tasks being assigned to the PEs and the execution time of an application. Considering a proactive method to predict temperature would require an additional capability of predicting the future temperatures, information of the tasks being assigned along with the additional memory to record previous temperature values. Thus, this work uses a reactive method to keep the temperatures of PEs below the critical values. Such a power management scheme provides an aid to the actual thermal management scheme which may be necessary in a 3D chip.

## 3.1.3 DVFS

In 2D ICs, DVFS is achieved by monitoring the workload of the PEs. If the utilization of a PE (or activity) is high, higher voltage and frequency levels are assigned to it. Opposite is done when the utilization is lower. When a power budget is introduced, the algorithm tries to keep the total chip power below the power budget value by adjusting the voltage/frequency (V/F) of the PEs. When the total chip power falls below the budget value, the V/F levels are increased whereas opposite is done when chip power crosses the budget value. Since density of devices on a chip is increasing, temperature has become a major concern in 2D chips as well. For DVFS with temperature constraints in 2D ICs, the temperature of each PE is monitored independently [28]. The effect of temperature on a PE due to another PE is ignored. This is largely accepted in 2D ICs as heat flow in lateral direction is negligible. But, in case of a 3D IC, temperatures of PEs in a stack are highly interdependent, not only in the vertical direction but also in the lateral direction. Hence, monitoring the activity and the individual temperatures of PEs alone is insufficient. Other parameters should be included in the equation. In order to have less performance losses in a PE, its utilization should be monitored while keeping the total chip power below a set budget value and temperature of PEs under critical temperature values. The temperature of a PE is primarily influenced by its power dissipation, its location within the stack, and in case of heterogeneous system, its area as well.

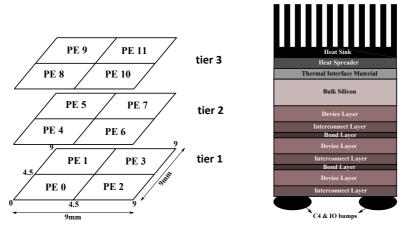

### 3.1.4 Approaches

Two power management approaches are studied and considered: per-core DVFS and DVFS on voltage islands.

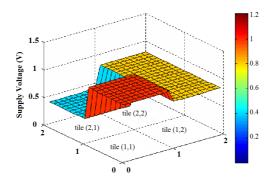

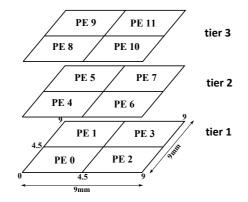

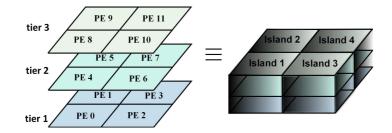

Figure 3.1: 3D voltage islands.

Voltage islands: A stack with PEs is partitioned into 4 islands, as shown in Figure 3.1. A voltage island partitioning and multiple supply voltage assignment technique is presented in [24] considering the delay caused by power reduction, timing slack, temperature analysis and power density. DVFS can be effective on islands if the PEs in an island have similar workloads giving enough opportunities for power saving whereas, if the performance requirements of PEs in an island are different, scaling of V/F levels may highly degrade the performance of active PEs. Voltage island partitioning highly depends on the type of target application that would run on the PEs and the symmetry in their performance requirements. Special voltage island partitioning algorithms should be considered while assigning islands. In this thesis, the islands are partitioned to study the effectiveness of the 3D islands, therefore, to rule out complexities due to difference in performance requirements, PEs in an island are assumed to have same workloads. DVFS along with DFS is considered in the test case. The voltage-frequency (V/F) combinations can be represented as:

(V1,F1), (V1,F2), (V2,F3), (V2,F4), (V3,F5), (V3,F6).

(V1,F1) and (V3,F6) represent the lowest and the highest operating V/F level, respectively. Six frequencies are used paired with only three voltage levels. This is done in order to utilize the benefit of DFS. This proves to be efficient in thermal management as frequency scaling helps reducing peak power, hence reduces the temperature. Scaling only frequency may mean degradation in the performance without significant energy saving. However, as each voltage level allows two frequencies, in order to reduce the temperature of one PE, its frequency can be scaled down without changing frequency levels of other PEs in the island.

*per-core DVFS:* This is a special case of voltage islands where each island consists of only one PE. Increasing the granularity of voltage islands can offer better flexibility in choosing operating voltage and frequency levels. This becomes important in cases where PEs have different workloads. However, this comes at an overhead of additional level shifters and voltage converters. Per-core DVFS allows power management block to choose new operating voltage and frequency levels for individual PEs in order to meet temperature and power constraints. As individual PEs are scaled, the change in power density in most cases would be lesser than that in voltage islands. This may prove to be advantageous when PEs are scaled to higher V/F levels because change in temperature of a PE depends on change on power density. Six voltage-frequency combinations can be represented as:

(V1,F1), (V2,F2), (V3,F3), (V4,F4), (V5,F5), (V6,F6).

(V1,F1) and (V6,F6) represent the lowest and the highest operating V/F level, respectively. Each frequency level is coupled with a unique voltage level.

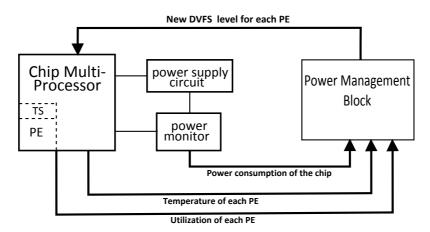

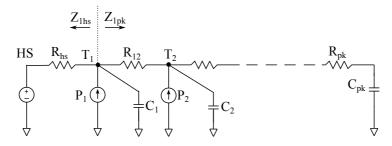

# 3.2 Control Loop and System Modeling

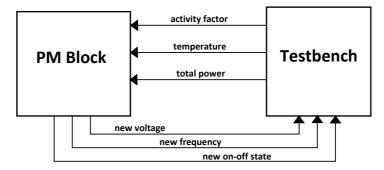

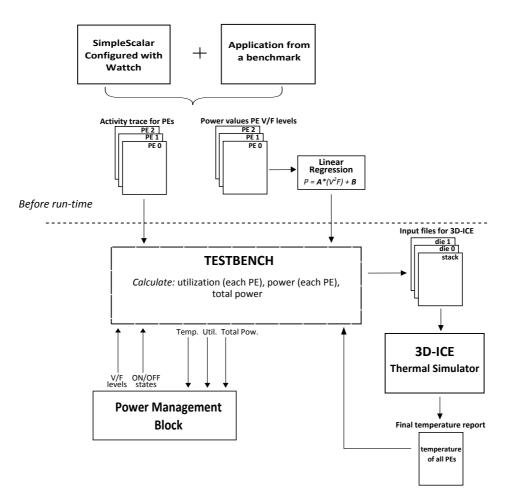

The control loop for power management scheme is shown in Figure 3.2. The Power Management Block (PMB) takes three inputs from the system to decide new DVFS levels for each PE. These inputs are:

- 1. Activity factor (utilization) of each PE. The activity factor (utilization) of each PE in the previous control period is made available to the PMB. This is assumed to be done by the performance monitor on each PE.

- 2. *Temperature of each PE*. Temperature sensor on each PE provides the PMB with the current temperature of each PE.

3. *Total chip power.* A power monitor (e.g. power measurement circuit with the power supply circuit) provides the average chip power to the PMB at certain time intervals.

Figure 3.2: Control loop for power management scheme.

In order to design an effective control, it is important to model the dynamics of the controlled system, i.e., the relation between controlled variable and manipulated variable. The manipulated variable is the operating V/F level while the controlled variables are power and temperature. Hence, the relation between power and V/F levels, and the relation between temperature and V/F levels needs to be modeled.

### 3.2.1 Relation between Power and V/F Levels

DVFS can allow cubic reductions in power density relative to performance loss for each PE in a MPSoC [31]. However, cubic power model may lead to large runtime overhead and high complexity for power management scheme design. However, real MPSoC usually provide a limited DVFS range only, and within this small range, [32, 33] have shown that the relationship between power and DVFS level can be approximated with a linear function. Therefore, the power dissipation of a PE is modeled as

$$P = A * V^2 * F + B \tag{3.1}$$

where A and B are constants, P is power, V and F are voltage and frequency corresponding to a DVFS level. This equation can be looked upon as total power equation where first term denoted the dynamic power while the second term denotes the static power. The value of A varies for different PEs according to the workload as it depends on activity. It can be represented by a generalized value for an intended workload. To remove the constant term and develop a dynamic model equation, the difference equation can be considered.

$$\Delta P = A * \Delta (V^2 * F) \tag{3.2}$$