#### Design of a High-Voltage Arbitrary Waveform Generator for Testing Power Component Insulation

Zhao, W.

DOI

10.4233/uuid:62bcb2ac-1eb8-42f5-b6d2-b05fb67fd4d2

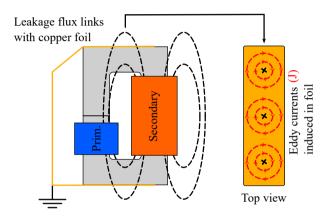

**Publication date**

**Document Version**

Final published version

Citation (APA)

Zhao, W. (2025). Design of a High-Voltage Arbitrary Waveform Generator for Testing Power Component Insulation. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:62bcb2ac-1eb8-42f5-b6d2-b05fb67fd4d2

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy**Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## Design of a High-Voltage Arbitrary Waveform Generator for Testing Power Component Insulation

#### Design of a High-Voltage Arbitrary Waveform Generator for Testing Power Component Insulation

#### Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology, by the authority of the Rector Magnificus, prof. dr. ir. T.H.J.J. van der Hagen, chair of the Board for Doctorates, to be defended publicly on Tuesday 22 April 2025 at 15:00 o'clock

By

#### Weichuan ZHAO

Master of Science in Electrical Engineering, Delft University of Technology, Delft, the Netherlands, Born in Changchun, China.

#### This dissertation has been approved by the promoters

#### Composition of the doctoral committee:

Rector Magnificus, Chairperson

Prof. ir. P.T.M. Vaessen,

Prof. dr. ir. P. Bauer,

Dr. M. Ghaffarian Niasar,

Delft University of Technology, promotor

Delft University of Technology, copromotor

Independent member:

Prof. dr. ir. M. Popov, Delft University of Technology

Prof. dr. ir. G. Rietveld, University of Twente

Prof. dr. R. Ross, Delft University of Technology

Prof. dr. ir. P.C.J.M. van der WieEindhoven University of Technology

len

Dr. Z. Qin Delft University of Technology, reserve member

This TU Delft PhD project IEM39G is funded by TKI Urban Energy with the grant number 1821403, which is highly appreciated.

If the mountain will not come to me Then, I will go to the mountain

# Contents

| Su | mm                       | ar <del>y</del>                                                                                                                                                                                | хi             |

|----|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Pr | efac                     |                                                                                                                                                                                                | xiii           |

| 1  | 1.1<br>1.2<br>1.3<br>1.4 | Background                                                                                                                                                                                     | 4<br>6         |

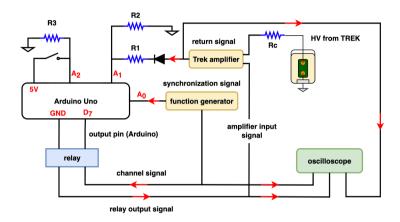

| 2  | 2.1<br>2.2<br>2.3<br>2.4 | Function Generator with Linear HV Amplifier                                                                                                                                                    | 9<br>12<br>13  |

| 3  | 3.1                      | Background                                                                                                                                                                                     | 20<br>22<br>23 |

|    |                          | <ul> <li>3.3.1 Experiments with Two Series-Connected MOSFETs Using the Gate Balancing Core Method</li> <li>3.3.2 Analytical Analysis of Dynamic Voltage Sharing Using the GBC Method</li></ul> |                |

|    | 3.4                      | 3.3.3 Simulation Verification of Dynamic Voltage Sharing Using the GBC Method                                                                                                                  |                |

|    |                          | 3.4.1 Passive Snubber Circuits                                                                                                                                                                 | 34<br>36       |

|    | 3.5                      | on Four Series-Connected SiC MOSFETs  Gate-Drain Zener Clamping Circuits  3.5.1 Experiments with the Optimized Zener Clamping Method and Three Series-Connected MOSFETs.                       | 42             |

viii Contents

|   |     | Design of Isolated HV Gate Drivers                             |     |

|---|-----|----------------------------------------------------------------|-----|

|   | 3.1 | 3.7.1 LTspice Simulations of the Magnetically Isolated HV Gate | 49  |

|   |     | Driver                                                         | 51  |

|   | 3.8 | Summary of Chapter 3                                           |     |

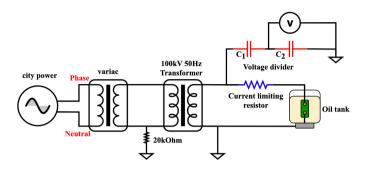

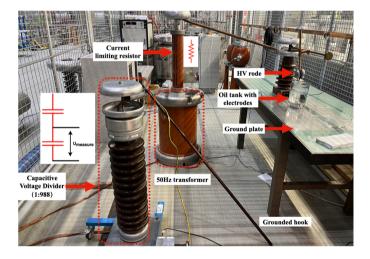

| 4 |     | Γ Insulation System Design                                     | 55  |

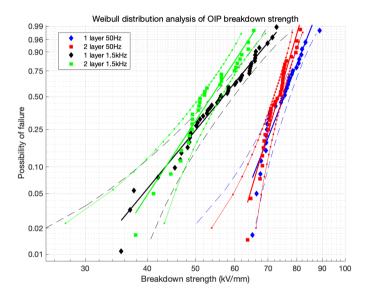

| - |     | Oil-Impregnated Paper Dielectric Investigation                 |     |

|   |     | 4.1.1 OIP Sample Preparation                                   |     |

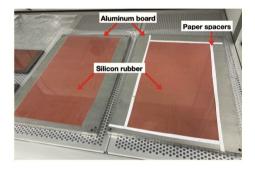

|   |     | 4.1.2 Experimental Set-up Preparation                          |     |

|   |     | 4.1.3 Ramp Sinusoidal Breakdown Tests                          |     |

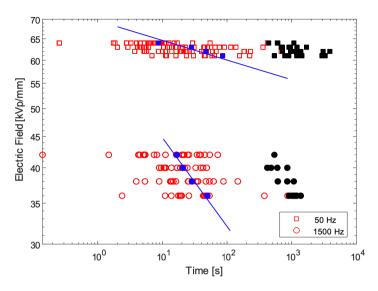

|   |     | 4.1.4 HV Accelerated Aging Tests (Lifetime Tests)              |     |

|   |     | 4.1.5 Summary of Chapter 4.1                                   |     |

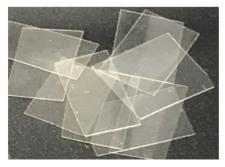

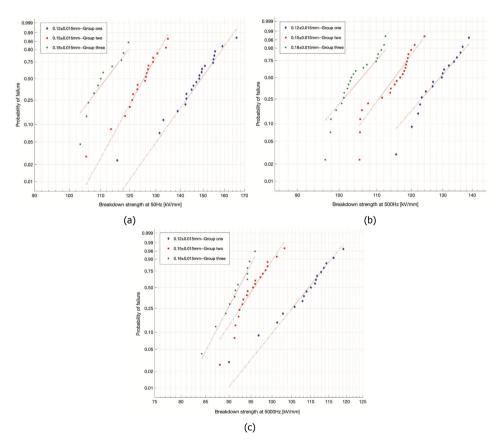

|   | 4.2 | Epoxy Resin Dielectric Investigation                           |     |

|   |     | 4.2.1 Epoxy Resin Sample Preparation                           |     |

|   |     | 4.2.2 Experimental Set-up Preparation                          |     |

|   |     | 4.2.3 Ramp Sinusoidal Breakdown Tests                          | 64  |

|   |     | 4.2.4 Summary of Chapter 4.2                                   | 66  |

|   | 4.3 |                                                                |     |

|   |     | Based Resonant Transformer                                     |     |

|   |     | 4.3.1 Resonant Test System Circuit Analysis                    |     |

|   |     | 4.3.2 Transformer Design Procedure                             |     |

|   |     | 4.3.3 Secondary Insulation Design                              |     |

|   |     | 4.3.4 Experimental Results                                     |     |

|   |     | 4.3.5 Discussion                                               |     |

|   | 4.4 | Summary of Chapter 4                                           | 83  |

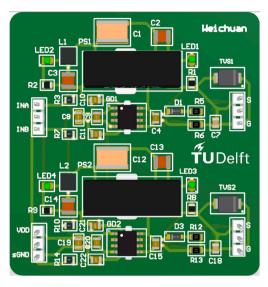

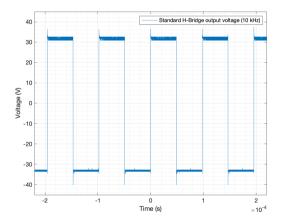

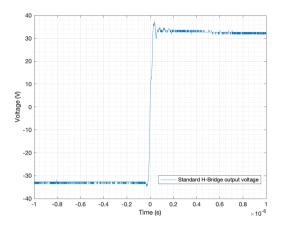

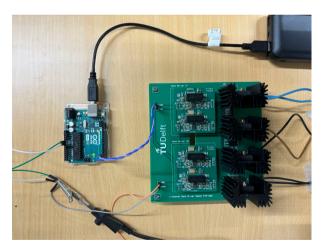

| 5 | PCE | B Design of a Standard H-Bridge                                | 85  |

|   | 5.1 | Standard H-Bridge Design                                       | 85  |

|   | 5.2 | Standard H-Bridge Validations                                  | 90  |

| 6 | Dec | ign of a HV Arbitrary Waveform Generator Using a Modular       |     |

| U |     | caded H-Bridge Topology                                        | 93  |

|   |     | H-Bridge Design                                                |     |

|   |     | 6.1.1 Semiconductor Device Selection                           |     |

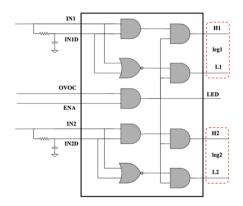

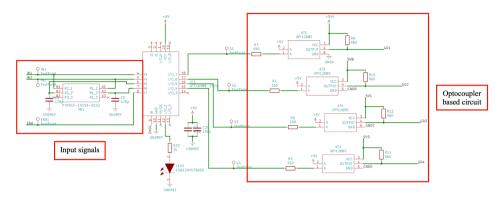

|   |     | 6.1.2 Gate Driver Circuit                                      |     |

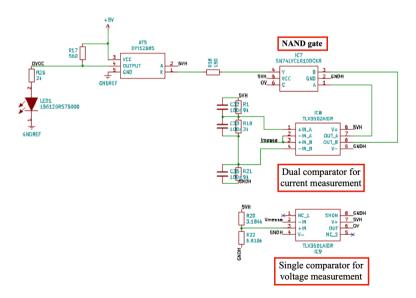

|   |     | 6.1.3 Over-Current Protection                                  |     |

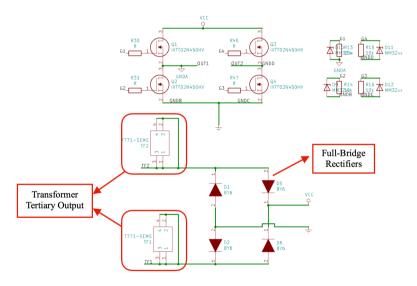

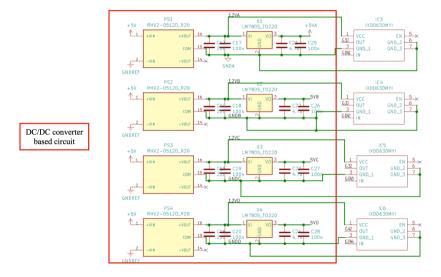

|   | 6.2 | Isolated DC/DC Converter Design                                |     |

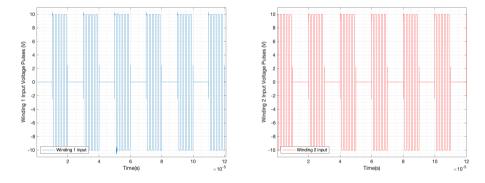

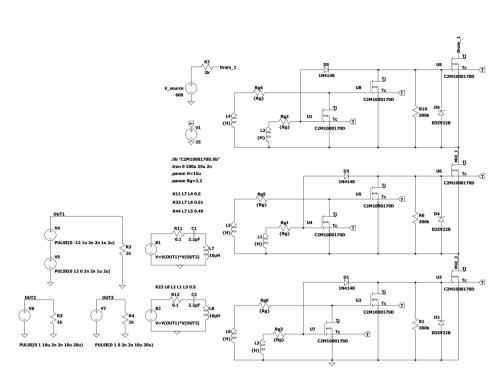

|   |     | 6.2.1 Transformer ZVS Driving Circuit                          | 97  |

|   |     | 6.2.2 Medium-Frequency Transformer Design                      |     |

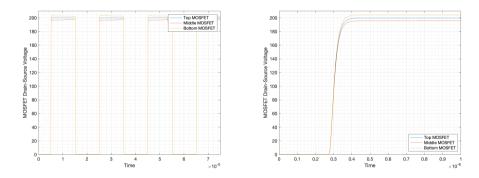

|   | 6.3 | Experimental Results                                           | 103 |

|   | 6.4 | Discussion                                                     | 106 |

|   | 6.5 | Summary of Chapter 6                                           | 108 |

Contents ix

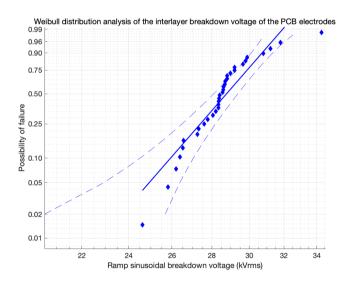

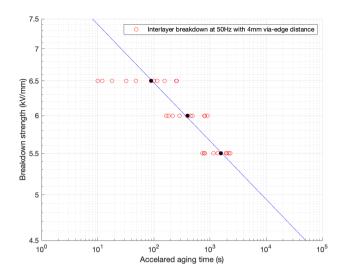

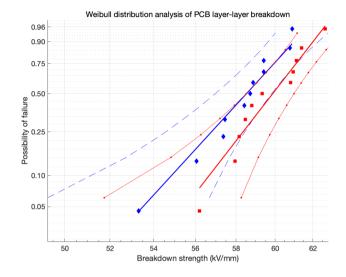

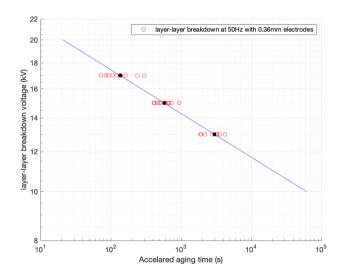

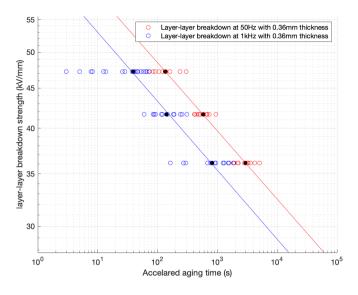

| 7  | 7.1<br>7.2<br>7.3    | Interlayer Breakdown Tests of PCB Electrodes at 50 Hz Layer-Layer Breakdown Tests of PCB Electrodes at 50 Hz Layer-Layer Breakdown Tests of PCB Electrodes at 1 kHz Summary of Chapter 7 | 113<br>115 |  |  |

|----|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

| 8  | Con                  | clusion                                                                                                                                                                                  | 119        |  |  |

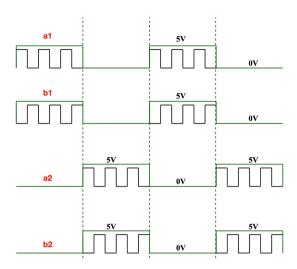

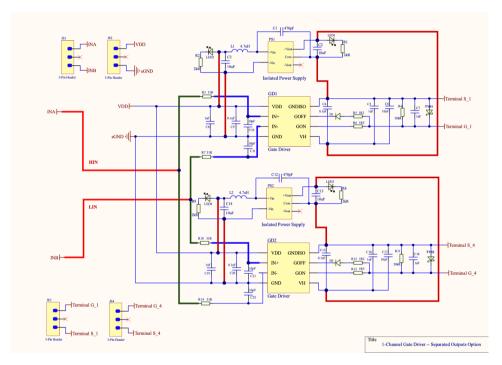

| A  | A.1<br>A.2<br>A.3    | Input Controller & Dead-Time Generation                                                                                                                                                  | 126<br>127 |  |  |

| Ep | ilog                 | ue                                                                                                                                                                                       | 131        |  |  |

| Ac | kno                  | wledgements                                                                                                                                                                              | 133        |  |  |

| Cu | Curriculum Vitæ      |                                                                                                                                                                                          |            |  |  |

| Li | List of Publications |                                                                                                                                                                                          |            |  |  |

| Bi | ibliography          |                                                                                                                                                                                          |            |  |  |

# Summary

The future power grid must accommodate large-scale integration of variable renewable energy sources. Power electronic (PE)-based components, e.g. converters, will play an essential role in the operation of the power system. However, the harmonics and transients generated by these PE-based components can significantly affect the lifetime and reliability of various power system components. These disturbances, particularly harmonics and transients, are challenging to eliminate. Thus, a more effective strategy is to assess the effects and enhance the durability and performance of the system components. To ensure the reliability of critical system components, these should meet stringent specifications and undergo rigorous testing prior to installation. Using a modular cascaded H-bridge (CHB) based high-voltage arbitrary waveform generator (HV-AWG), capable of replicating the dielectric stresses induced by PE components, enables a more accurate assessment of component resilience under operational conditions.

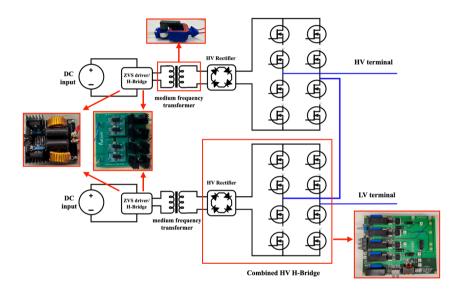

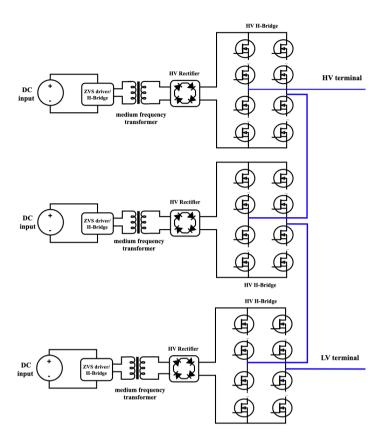

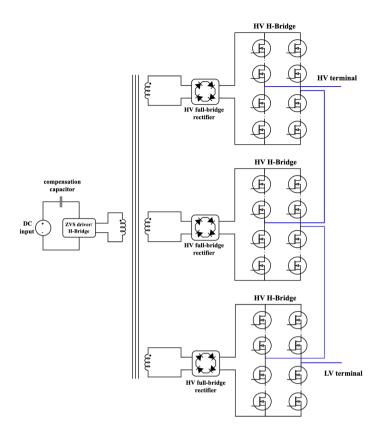

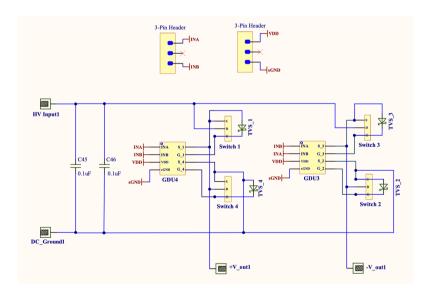

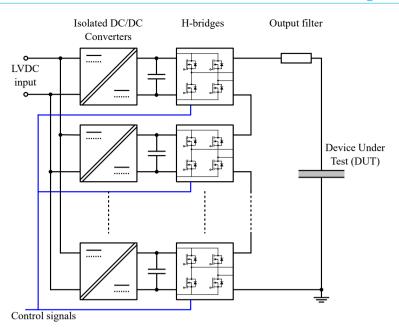

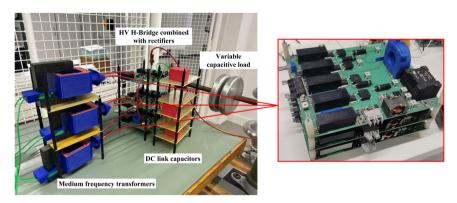

The CHB-based HV-AWG can be divided into several submodules; each module consists of three key components: a driver, a medium-frequency transformer, and an H-bridge equipped with HV rectifiers. Although various types of HV-AWGs exist, the modular CHB-based HV-AWG excels due to its superior high-voltage capability, broad operating frequency bandwidth, simple topology, compact size and low manufacturing costs. To successfully realize the CHB-based HV-AWG design, several technical challenges must be addressed, including the development of the insulation system for the medium-frequency transformer and the design of the high-voltage switch within the H-bridge.

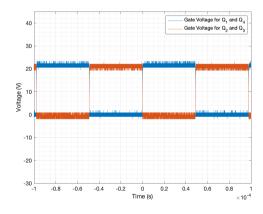

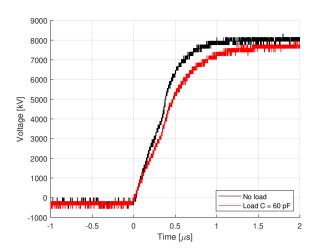

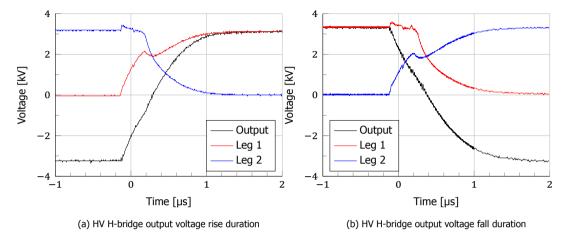

The objective of the PhD project is to design and prototype a CHB-based HV-AWG, aiming for testing the insulation specimens of HV system equipment at voltages up to 8 kV to further enhance the power grid reliability. The primary functions of this prototype are outlined as follows: The CHB-based HV-AWG starts with a low-voltage (LV) DC input, which is supplied to the ZVS driver. The ZVS driver employs a soft-switching technique to drive a medium-frequency transformer, whose primary function is to elevate the input voltage to the required level. The transformer's output is rectified, generating a high-voltage DC (HVDC) output that serves as input for the HV H-bridge. The HV H-bridge then converts this HVDC input into HV pulses, which can be manipulated and controlled via a sophisticated algorithm that cascades the HV pulses to generate a variety of desired waveform shapes. This scalable modular approach, along with the precise control of pulse generation, enables the HV-AWG to create complex waveforms suited for various applications.

The main scientific challenges associated with the realization of a modular cascaded H-bridge-based high-voltage arbitrary waveform generator are:

Medium Frequency Transformer Design with the considerations of trans-

xii Summary

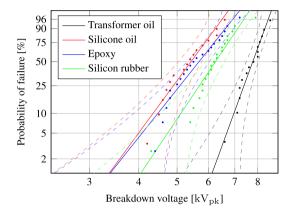

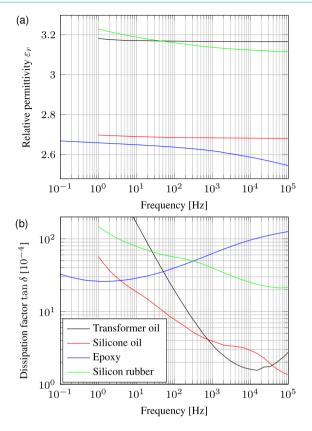

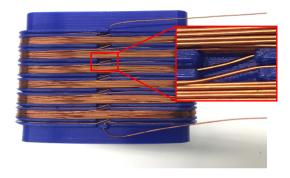

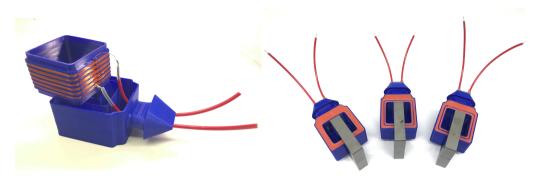

former insulation material and winding configuration selection and transformer secondary design: To ensure sufficient creepage and clearance between the transformer windings, a split-winding configuration is implemented, where the windings are distributed across the two limbs of a U-U core. This configuration allows for more insulation materials between the windings. The secondary winding employs a disc-winding arrangement to enhance its high-voltage capability. Furthermore, an isolation turn is introduced between adjacent winding discs to mitigate the risk of disc-to-disc discharges. Based on Novo-control measurement method, the insulation dielectric properties are measured. After the analysis of the dielectric properties of various insulating materials, including transformer oil, silicone oil, epoxy resin, and silicone rubber, the heat-resistant TFC silicone rubber is selected for the construction of the transformer's insulation system.

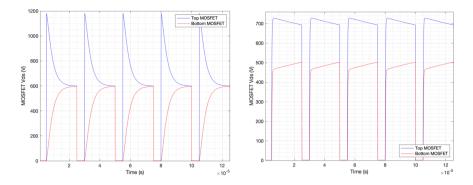

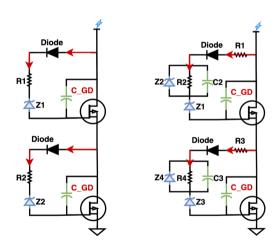

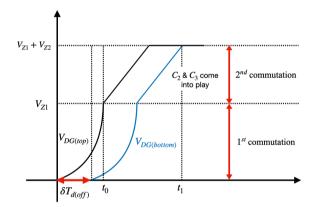

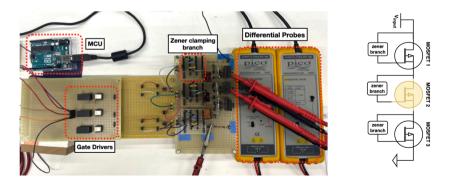

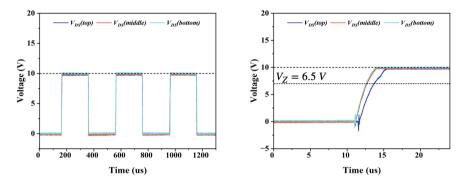

• HV H-Bridge Design with the considerations of power-electronic component selection, HV gate driver design and the voltage sharing of the series-connected MOSFETs. To build the HV H-bridge, SiC MOSFETs are generally preferable owing to their superior performance in high-temperature environments, lower on-resistance, reduced switching losses, and enhanced thermal conductivity. However, SiC MOSFETs have a maximum blocking voltage limitation of 3.3 kV. To meet higher voltage demands, the most straightforward and effective approach is to connect multiple SiC MOSFETs in series. This introduces the challenge of unbalanced drain-source voltage sharing. The voltage balancing techniques — such as gate balancing core method, improved RC snubber methods, and optimized zener clamping method can mitigate this as is demonstrated in this thesis, which is verified by LTSpice simulations. However, they introduce additional costs and result in a bulky prototype due to the need for auxiliary components.

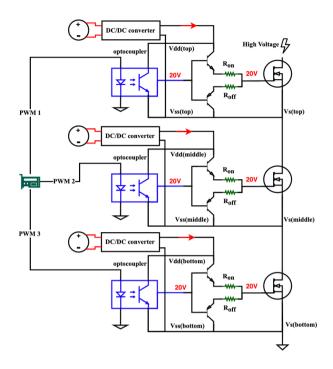

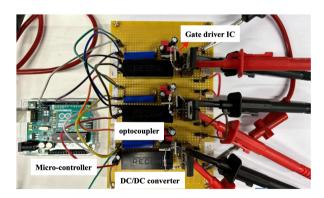

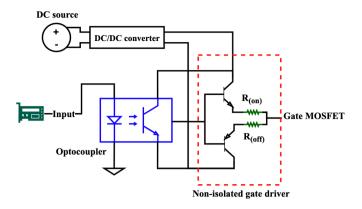

For the prototype, Si MOSFETs, which can offer a maximum blocking voltage of 4.5 kV, are used. To further accommodate high voltage requirements, isolated gate drivers are replaced by non-isolated gate drivers and optocouplers. This modification allows the high voltage to be shifted away from the insulation system of the isolated gate driver to the optocoupler.

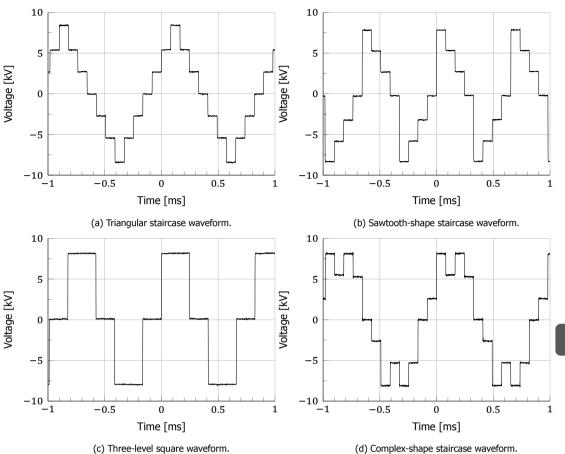

Based on the performed research on the key components, a three-stage modular CHB-based HV-AWG prototype, capable of producing a maximum output voltage of approximately 8.1 kV is realized, constrained by the insulation limits of the optocouplers and DC/DC converters. The generator can produce a variety of waveform shapes, including pulse, sawtooth, and stair patterns by modifying the control algorithm of the HV-AWG. This arbitrary waveform generator serves a platform for insulation samples' aging tests at TU Delft HV lab. To enhance the scalability of the HV-AWG, future research includes cascading the HV H-bridge submodules using fiber optics and integrating control through advanced platforms such as the Typhoon HIL system. Additionally, replacing the medium-frequency transformer with a planar transformer can be considered to achieve a more compact device design.

## **Preface**

During the journey of research, I had a thousand of thoughts to quit. Luckily, I also had a thousand and one thoughts to continue.

Weichuan ZHAO Delft, July 2024

### Introduction

#### 1.1. Background

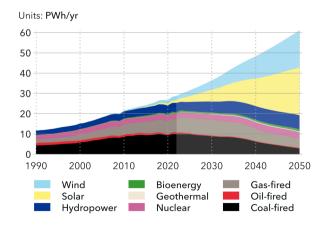

The global economic growth has intensified concerns about the availability of the resources and environmental sustainability, both of which are emerging as significant barriers to the energy transition and sustainable development. The climate change and massive utilization of fossil fuels present a major challenge of achieving a sustainable energy power system. Consequently, the energy sector is undergoing a major global shift, moving from traditional fossil-based energy production to renewable sources such as wind, solar, bioenergy and hydropower, illustrated in Fig. 1.1 [1]. Also, electricity consumption is rising exponentially owing to the increasing electrification of transportation, such as electric vehicles and industry. As a result, the demand for a greener, more affordable, and more accessible high-voltage (HV) power system is expected to gain significant momentum over time.

Figure 1.1: World grid-connected electricity generation by power station type [1]

2 1. Introduction

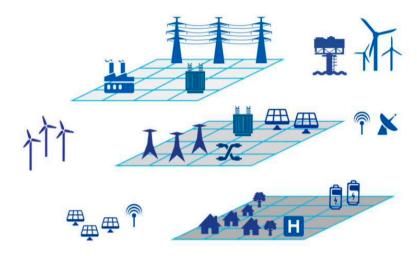

As a large number of renewable energy sources are integrated into various levels of the power grid – HV for generation layer, medium voltage (MV) for transmission layer, and low voltage (LV) for consumption layer, as shown in Fig. 1.2, there will be a substantial growth in the use of power-electronic (PE) based converters for electric power conversion (e.g. DC-to-AC, AC-to-DC), which will gradually dominate the grid. However, due to the fast switching (high dv/dt and di/dt), the PE-based modules will generate a significant amount of high-frequency (HF) harmonics, voltage transients and steep current spikes, which create new electric field stresses on the insulation systems of HV components. Thus, the HV equipment insulation can degrade faster and jeopardize the reliability of grid assets.

Figure 1.2: Renewables in different power grid layers (DNV energy transition outlook 2023)

It is commonly known that the mitigation of these harmonics, transients, spikes and oscillations is complicated because of the unavoidable parasitic parameters present in the PE based converters, which can rapidly charge or discharge owing to the solid-state switching and HF circulating current harmonics [2]. The most economical and practical solution is to improve the insulation quality of the HV components. Before installation, these HV components should be tested under specific and customized HV and HF field strength, which is similar to that occurring in the real power grid. A reliable HV arbitrary waveform generator (HV-AWG) that has the capability to generate such required test signal is highly-required for insulation testing.

The PhD project general objective is to enhance the reliability of HV system components in future power grids by testing their insulation systems under realistic dielectric stress conditions. The specific objective is to design and prototype a modular cascaded H-Bridge (CHB) based HV-AWG for testing the insulation specimens up to 8 kV. The design guidelines will address all critical factors relevant to the full-scale implementation of the HV-AWG. The prototype will consist of three compact

submodules, facilitating ease of integration and storage. Additionally, the expected output performance and the associated control system will be demonstrated.

#### **1.2.** HV Arbitrary Waveform Generator Topologies

Nowadays, with concerted effort, the researchers worldwide have already provided a number of effective approaches for the realization of the HV-AWG, which are listed below. Detailed explanation and comparison of these methods will be provided in Chapter 2.

- The use of commercial-available function generator and HV Trek amplifier

- Non-modular cascaded H-bridge based HV-AWG with medium-frequency transformer (MFT)

- Modular cascaded H-bridge based HV-AWG with MFT

- Modular multilevel converter [3]

- Modular cascaded H-bridge based HV-AWG with flyback supply [4] and [5]

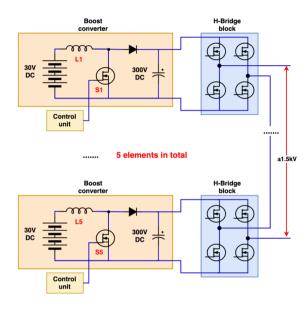

- Modular cascaded H-bridge based HV-AWG with boost supply [6]

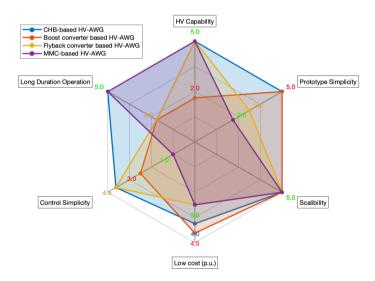

Figure 1.3: Comparison of different HV-AWG topologies

These HV-AWG topologies can be evaluated according to six different criteria: High-Voltage Capability, Prototype Simplicity, Scalability, Low Cost per Unit, Control Algorithm Simplicity and Long Duration Operation Capability. The comparison results are summarized in Fig. 1.3.

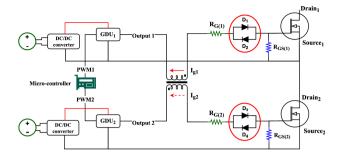

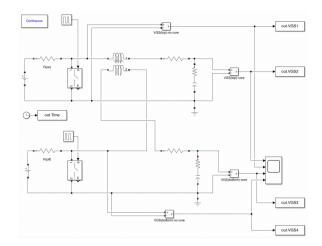

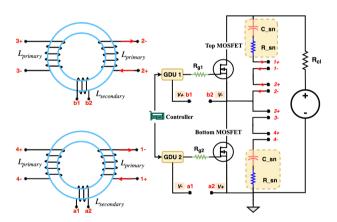

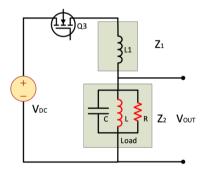

Fig. 1.4 illustrates the schematic of the envisioned modular cascaded H-bridge based HV-AWG with 2 stages, highlighting three critical components: MFT, standard H-bridge or zero-voltage switching (ZVS) driver, and HV H-bridge. To fulfill the design of these components, the following scientific challenges must be tackled.

- MFT design: insulation material selection, winding configuration selection, transformer secondary winding design

- HV H-bridge: PE-based component selection, unbalanced voltage sharing of the series-connected SiC MOSFETs, protection systems, HV gate driver design

Figure 1.4: Modular cascaded H-bridge based HV-AWG topology schematic with indication of the critical components

#### 1.3. PhD Research Questions

According to the background and the aforementioned research challenges, the PhD research questions can be defined as follows:

"What are the important considerations of the 10 kV class insulation system design of the medium frequency transformer (25-40 kHz)"

The following medium frequency transformer design items should be covered: insulation material type selection (HV accelerated aging and ramp breakdown tests under various frequencies and temperatures), MFT core type selection, MFT winding configuration design, thermal management, MFT (HV) secondary winding design and MFT (HV) bushing design.

"Which type of winding configuration is suitable for the medium frequency transformer inside the HV arbitrary waveform generator"

The following items should be covered: the transformer winding arrangements (core, side-by-side shell, concentric and sandwich type [7]), transformer terminal location (double-side placement or middle placement), transformer bushing design, transformer bobbin or bobbin cup design.

Suitable transformer winding configuration should have higher winding breakdown voltage  $U_{bk}$ , higher partial discharge inception voltage  $U_{pd}$ , lower transformer temperature increment, lower manufacturing cost, compact transformer size and ease of implementation.

"What is the best method to deal with the unbalanced voltage sharing of the series-connected switches (e.g. SiC MOSFETs)"

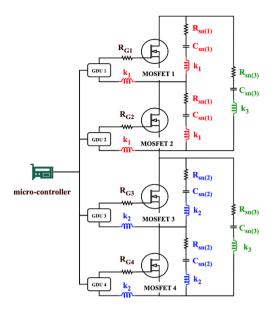

Generally, the HV H-bridge module contains four HV switches (each comprised of series-connected MOSFETs). Due to the variation in the electrical characteristics of the PE-based components such as gate drivers, MOSFETs, optocouplers, regulators and the presence of the unavoidable parasitic capacitances (associated within switches or with respect to ground), unbalanced drain-source voltage sharing occurs.

The improved RC snubber (IMS) methods, zener clamping (ZC) method, gate balancing core (GBC) method and the static balancing method are described and evaluated. The best balancing method should have the following properties: evident improvement of the  $V_{DS}$  sharing of the series-connected MOSFETs, ease of circuit implementation, simple circuit design, low cost and compact prototype size.

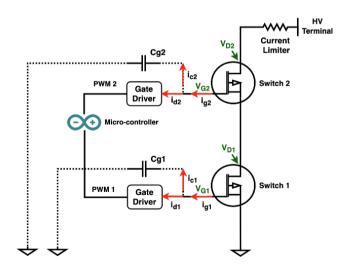

"How to properly design and prototype the HV gate drivers of the series-connected MOSFETs or the Si MOSFETs within the HV H-bridge"

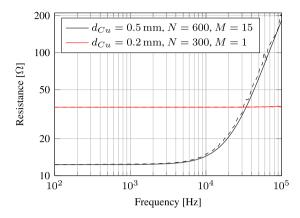

The voltage potential of the gate terminal  $V_{G(i)}$  is similar as that of the source terminal  $V_{S(i)}$ . If the number of the series-connected MOSFETs is large, the gate voltage of the topmost switches close to the input lead are quite high and almost equal to the main input voltage. To avoid breakdown and overheating of the gate drivers, the HV gate drivers are required. The simplest method is to use the non-isolated gate drivers together with the optocouplers and isolated DC/DC converters to built the HV gate driver circuits. The optocouplers and isolated DC/DC converters provide galvanic isolation for the HV and LV. Additionally, the magnetically isolated gate driver represents another method, utilizing two gate-coupled transformers to simultaneously turn on and off the series-connected MOSFETs. However, this technique is still under development in our research group and has not yet reached full maturity.

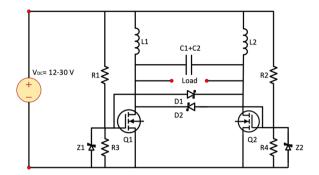

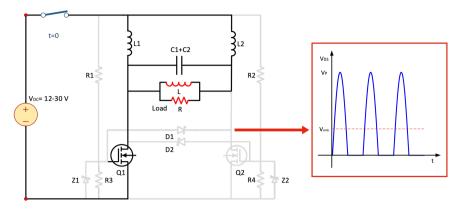

"Which switching topology is suitable to generate the input voltage of the medium frequency transformer"

**Soft-switching topology:** The output voltage and current waveforms of a standard H-bridge are square-shaped. By incorporating additional capacitors and inductors, such as an LLC or LCC resonant tank, between the standard H-bridge and the primary winding of the MFT, the current output waveform can be transformed from square-shaped to sinusoidal. This conversion significantly reduces the di/dt, leading to fewer voltage transients and spikes, which in turn minimizes losses. Additionally, the presence of resonant tank can increase the transformer's output voltage. As an alternative, the zero-voltage switching (ZVS) driver could also be used for soft-switching.

**Hard-switching topology:** If a hard-switching topology is employed, the MFT input will consist of square pulses. This can lead to potential distortion in the MFT output voltage waveform as well as the standard H-bridge waveform. The distortion is caused by (reflected) transients and spikes induced by the high  $\mathrm{d}i/\mathrm{d}t$  on the transformer's primary voltage. Consequently, the use of a hard-switching topology is not recommended.

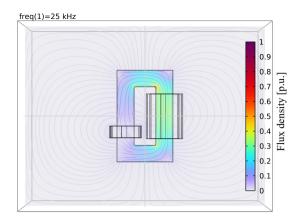

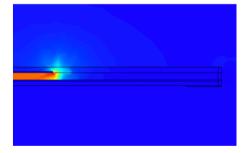

For the MFT design, a thorough review of relevant literature is necessary to establish a clear transformer design procedure. During the design process, COMSOL simulations are required to calculate transformer leakage inductance and the electric field distribution of the HV winding. Additionally, Novo-control measurements should be used to measure the dielectric characteristics (e.g.  $tan\delta$  and  $\epsilon_r$ ) of potential insulation materials such as transformer oil, silicone oil, silicone rubber, and epoxy resin. For the design of the LV and HV H-bridge, Altium Designer are used to create the PCB, and LTspice simulations will be employed to analyze the H-bridge circuit and various balancing methods for the HV switch.

#### 1.4. PhD Contributions

- A PhD thesis that contains comprehensive design guidelines of the cascaded H-bridge based HV-AWG – three key components: HV H-bridge, LV H-bridge, medium frequency transformer.

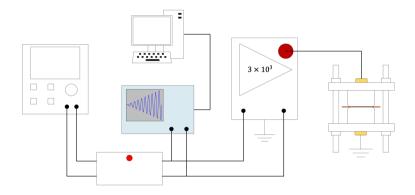

- A validated HV and HF insulation (ramp sinusoidal breakdown and accelerated aging) test platform using a ferrite-based resonant transformer (max.  $23\,\mathrm{kV_{pk}}$  limited by the voltage level of DC source) (**Chapter 4**)

- A reliable and validated medium frequency transformer designed in a compact size with the specifications:  $20-30\,\mathrm{kV_{pk}}$  isolation level and 25-45 kHz working frequency level **(Chapter 4)**

- A validated medium frequency transformer (25–45 kHz) with at least  $10\,\rm kV_{pk}$  insulation level (Chapter 6)

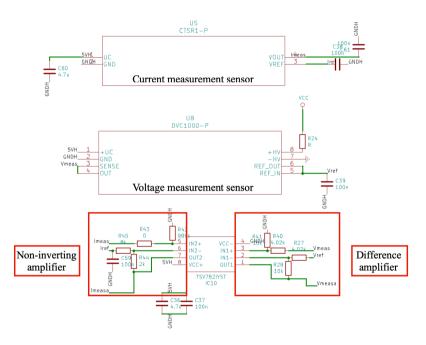

- A validated and calibrated  $2.7\,\mathrm{kV_{pk}}$  and  $0.2\,A_{rms}$  HV H-bridge (Si-MOSFET based) PCB with corresponding current, voltage measurements and overcurrent, over-voltage protections and a validated standard H-bridge (max.  $1\,\mathrm{kV_{pk}}$ ) (Chapter 5 and 6)

- A validated 8 kV-level modular cascaded H-bridge based HV-AWG prototype (3 submodules and 7 voltage levels) (Chapter 6)

#### 1.5. PhD Thesis Layout

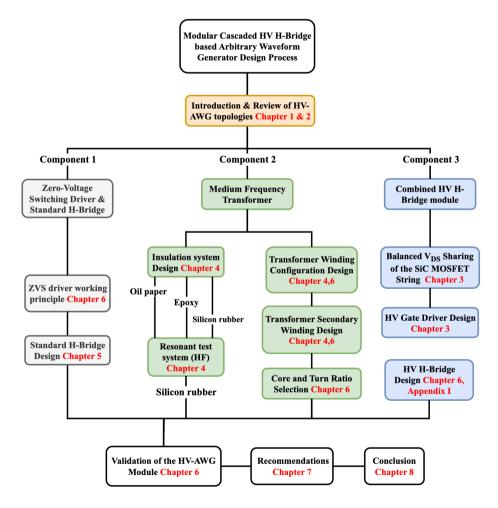

This PhD thesis presents a comprehensive design guidelines for a 3-stage modular cascaded H-bridge-based high-voltage arbitrary waveform generator. The structure of the thesis is shown in Fig. 1.5:

Figure 1.5: The flow chart of the PhD thesis outlines

8

The **first chapter** outlines the context of energy transition and the motivation for developing an arbitrary waveform generator, aimed at testing the insulation systems of HV equipment under realistic electric field strength conditions. **Chapter 2** reviews and compares various existing types of HV arbitrary waveform generators, leading to the identification of the CHB-based HV-AWG as the optimal topology based on performance metrics.

In **Chapter 3**, different methods for balancing the drain-source voltage of SiC MOSFETs in series-connected configurations are explored, evaluated, and compared to assess their suitability for constructing the HV switch of the H-bridge. This research reveals that, although the voltage sharing condition can be improved significantly, the implementation of balancing techniques significantly complicates the HV H-bridge design, ultimately leading to the selection of Si MOSFETs with higher blocking voltages. Additionally, the design of the HV gate driver for triggering the corresponding switch is elaborated in this chapter.

**Chapter 4** focuses on the insulation selection for the required medium-frequency transformer. The dielectric properties of oil-impregnated paper and neat epoxy resin are investigated at relatively low frequencies. However, since the medium-frequency transformer is required to operate above 25 kHz, an alternative test platform capable of performing ramp sinusoidal tests at the target frequency is needed. This chapter introduces the design and prototyping of a resonant test system that meets these specifications. **Chapter 5** presents the design of the standard H-bridge inverter, a key component of the resonant test system.

**Chapter 6** synthesizes the dielectric data obtained through the resonant test system, concluding that silicon rubber is the most suitable insulation material for the medium-frequency transformer. This chapter also details the design process of the medium-frequency transformer, including the selection of the transformer core, turn ratio, winding configuration, and secondary winding, as well as the design of the HV H-bridge, Si MOSFET selection, and protection circuit development. Additionally, validation results are provided, demonstrating that the designed prototype HV-AWG successfully generates arbitrary waveforms.

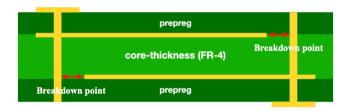

Finally, **Chapter 7** provides the future recommendations, which discusses the challenges in transformer manufacturing, specifically the labor-intensive processes involved in insulation casting and winding wrapping. The planar transformer is explored as a potential alternative to conventional medium-frequency transformers, and preliminary investigations into the insulation properties of FR-4 are conducted. This research may be continued in future work. **Chapter 8** presents a detailed conclusion of the PhD thesis.

# 2

# Existing HV Arbitrary Waveform Generator Topologies

#### 2.1. Function Generator with Linear HV Amplifier

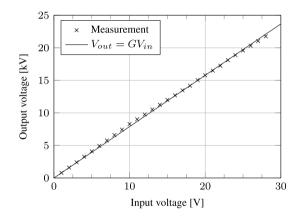

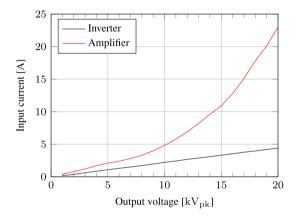

The simplest method to generate the HV and HF arbitrary waveforms is to directly connect a function generator to an HV amplifier. However, the commercially available HV amplifiers have limited frequency bandwidth and voltage ratings [2]. For instance, the HV TREK amplifier in TU Delft HV lab has a maximum voltage limit of  $30\,\mathrm{kV_{pk}}$  and a maximum current limit of  $20\,\mathrm{mA_{rms}}$ . According to formula (2.1), if the sample under test is selected, its equivalent capacitance  $C_{DUT}$  can be considered as a fixed value. The permissible ranges of  $I_{amp}$  and  $U_{amp}$  are also known. As a result, the feasible frequency bandwidth  $f_{max}$  of the TREK amplifier can be obtained.

$$f_{max} = \frac{I_{amp}}{2\pi \cdot U_{amp} \cdot C_{DUT}} \tag{2.1}$$

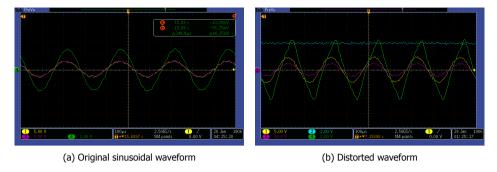

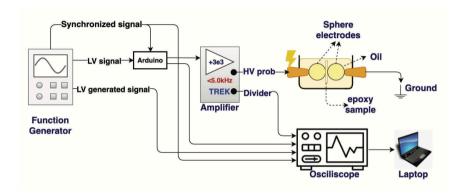

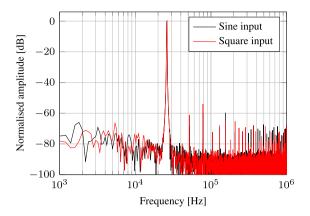

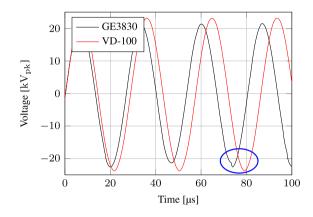

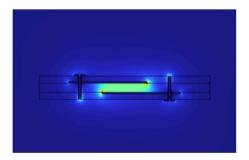

Furthermore, while the function generator of type TENMA 72-14111 can continuously provide the HF arbitrary waveforms at LV levels, sending an HF (>5 kHz) input signal to the TREK amplifier results in a significant distortion of the amplified signal, as illustrated in Fig. 2.1. Due to these limitations and drawbacks, this method is not recommended for producing HF and HV pulses for testing the insulation of HV grid components.

#### 2.2. Cascaded H-Bridge with Flyback Supply

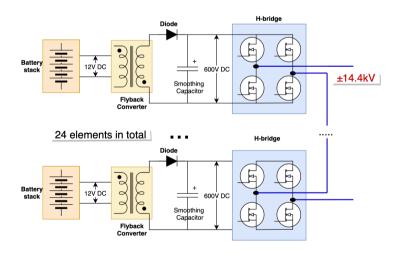

This subsection details the advantages, disadvantages, and working principle of the flyback converter-based HV-AWG. As described in [4] and [5], the HV-AWG is designed using a multi-level cascaded H-bridge topology, as illustrated in Fig. 2.2.

Figure 2.1: Output performance of the Trek amplifier based HV-AWG

The primary advantage of this topology is its modular structure, which relies on duplicating elementary modules. This allows for significant scalability of the AWG output voltage and greatly simplifies the manufacturing process. Additionally, the modular design enhances the reliability of the AWG. The schematic shows that only  $600\,\mathrm{V}$  H-bridges are required, simplifying the prototype design but limiting the output voltage of each submodule. In the referenced work, 24 submodules are connected in series, achieving a maximum output voltage of  $\pm 14.4\,\mathrm{kV}$  and producing up to 49 output voltage levels. However, this results in a really complicated control algorithm for the cascaded H-bridges. In Fig. 2.2, the battery stack serves as the

Figure 2.2: The topology of the modular multilevel flyback converter based HV-AWG

input voltage source for the HV-AWG, providing 12 V that is then boosted to 600 V DC by the flyback converter. However, the battery stack has a notable limitation: its finite energy storage, which restricts its ability to supply continuous power for a long duration. The crucial component of the flyback converter is the HF trans-

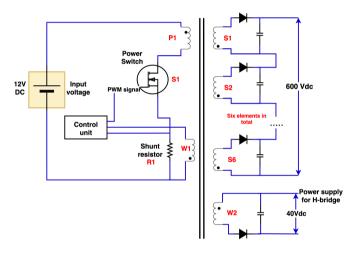

former, which includes one primary winding, six separate secondary windings, and two tertiary windings, as depicted in Fig. 2.3. Designing such a multi-secondary transformer is quite challenging. Without a primary compensation capacitor, the energy transfer efficiency of the transformer is significantly reduced to less than 50 % due to the low coupling factor k. An alternative solution is to use a matrix transformer, described in [8].

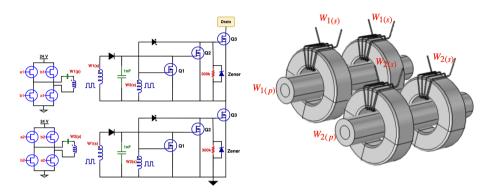

To achieve a stable flyback output, as shown in Fig. 2.3, the secondary winding is regulated using a robust closed-loop control mode. An auxiliary secondary feedback winding  $W_1$ , is required for modular output voltage measurement. Additionally, the shunt resistor  $R_1$  measures the primary current. If a voltage drop  $\Delta V$  is detected on the secondary output by  $W_1$ , the duty cycle of the power switch  $S_1$  can be adjusted to stabilize the 600 V DC output. Furthermore, a seventh secondary winding  $W_2$ , set to 40 V DC output, supplies power to the H-bridge auxiliary control circuits.

Figure 2.3: The flyback converter used to feed the H-bridge block

The HV-AWG consisting of 24 submodules complicates the control algorithm for the cascaded HV H-bridges. To achieve the desired HV output with fewer submodules, the target output voltage for each AWG submodule is designed to be approximately 2-3 kV, with three submodule elements anticipated. The input battery stack (12 V) is replaced by a commercially-available DC source, which offers continuous power and higher voltage amplitude. If the AWG submodule output voltage increases from 600 V to 2-3 kV, the power switches within the H-bridge may reach their maximum blocking voltage, potentially causing breakdown (commercially-available SiC MOSFETs have a voltage limit of 1.7 kV). To mitigate this, multiple switches could be connected in series to distribute the blocking voltage across the switches. However, unbalanced voltage sharing may occur due to unsynchronized gating signals, variations in PE-based component parasitic parameters, and different electrical characteristics. This specific problem will be thoroughly discussed in Chapter 3.

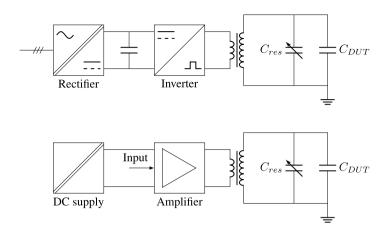

#### **2.3.** Cascaded H-Bridge with Boost Supply

In [6], a boost converter-based HV-AWG was introduced and designed also using a multilevel cascaded H-bridge topology. This subsection elaborates on the AWG working principle, along with its advantages and disadvantages. Contrasting with the topology discussed in Chapter 2.2, the complicated flyback converter is replaced by a simple boost converter, and the HF transformer is eliminated. As a result, the boost converter-based topology, depicted in Fig. 2.4, offers a more compact device size, reduced weight and ease of assembly and integration.

Figure 2.4: The topology of the modular multilevel boost converter based HV-AWG

The initial power source of the HV-AWG prototype is a  $30\,\mathrm{V}\,\mathrm{DC}$  lithium-ion battery stack. Additionally, the introduced DC-DC boost converter amplifies the original input DC voltage  $10\,\mathrm{times}$  to  $300\,\mathrm{V}\,\mathrm{DC}$  (with a duty cycle of 0.9). A large HV smoothing capacitor  $C_{smooth}$  is connected at the end of the boost converter to stabilize the DC output. The final output voltage of this 5-stage prototype is only  $1.5\,\mathrm{kV}$ . In fact, removing the HF transformer did achieve a more compact prototype size compared to the topology shown in Fig. 2.2. However, the boost converter has a limitation in its amplification capacity. If a higher HV-AWG output voltage is required, a larger number of submodules must be cascaded, complicating the control algorithm for the H-bridges. Additionally, the HF transformer provides galvanic isolation between the primary and secondary windings. Without this isolation, a significant voltage difference between the boost converter's input and output increases the risk of breakdown due to discharges and sparks from the secondary to the primary side. For the PhD project, around  $8\,\mathrm{kV}$  HV-AWG output is desired. Thus, this method is not suitable.

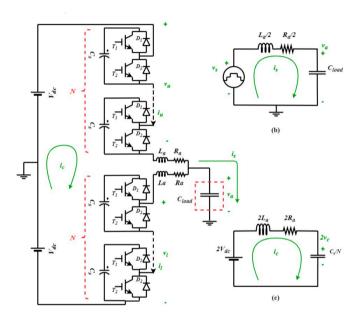

#### 2.4. Modular Multilevel Converter (MMC)

Fig. 2.5 depicts the schematic of the MMC-based HV-AWG [2]. It includes a split DC source  $V_{ac}$ , an AC filter composed of the upper and lower arm inductance  $L_a$ , a capacitive load  $C_{load}$  representing the equivalent electrical model of the HV object, and multiple MMC modules, which can be in either an on-state or off-state. When a module is in the on-state ( $T_1$  ON and  $T_2$  OFF), it generates  $V_{Cs}$  as output. When the module is in the off-state ( $T_1$  OFF and  $T_2$  ON), it is bypassed. By properly controlling the MMC modules through the algorithm, a specific number of  $V_{Cs}$  outputs can be cascaded, generating the HV arbitrary waveform. Notably, there is a series resistance  $R_a$  along with the arm inductances  $L_a$ . This is needed to damp the oscillations caused by the resonance between the arm inductances and the load capacitance.

Advantages of the modular multilevel converter based HV-AWG:

- Flexibility: MMC-based HV-AWG offers high flexibility in generating arbitrary voltage waveforms. Users can specify various parameters such as amplitude, frequency, phase, and waveform shape.

- High Voltage Capability: MMCs are well-suited for HV applications. They

operate at high voltages efficiently, making them suitable for testing and simulation in high voltage power systems.

- Low Harmonic Distortion: MMC-based HV-AWG exhibits low harmonic distortion in the output voltage waveform. This characteristic is advantageous in applications where low distortion is critical.

- Modularity: MMCs are modular in nature, which means they can be easily scaled up or down depending on the application requirements. This modularity facilitates easier maintenance, repair, and expansion compared to traditional converter topologies.

- High Efficiency: MMCs can achieve high efficiency levels, especially at higher voltage levels. This efficiency is crucial in power systems where minimizing losses is essential for overall system performance and energy conservation.

Disadvantages of the modular multilevel converter based HV-AWG:

- Complexity: The control and operation of the MMC-based converters can be more complex compared to traditional converter topologies. This complexity arises owing to the need for sophisticated control algorithms to manage the multiple modular units and ensure proper voltage balancing.

- Cost: MMC-based converters are more expensive to manufacture and implement compared to conventional converter topologies. The higher cost is mainly attributed to the use of multiple power semiconductor devices and complex control systems.

- Component Count: MMCs consist of a large number of PE-based devices (e.g. IGBTs or IGCTs) and passive components like capacitors and inductors. Managing and maintaining a large number of components can increase the risk of component failures and require more extensive monitoring and maintenance procedures.

- **Voltage Balancing:** Achieving proper voltage balancing across the modular units in an MMC can be challenging, especially under dynamic operating conditions. Imbalances in voltage levels can degrade converter performance and lead to increased losses and further leads the converter breakdown.

Figure 2.5: The topology of the modular multilevel converter based HV-AWG [9]

In conclusion, chapters 2.2 to 2.4 present three types of the designed HV-AWG topologies using different modular multilevel converters. Compared to the non-modular case, described in [10], the modular HV-AWG topology offers several significant advantages: high voltage capability, excellent submodule interchangeability, enhanced scalability and reliability of the HV-AWG prototype, as well as ease of integration and manufacturing.

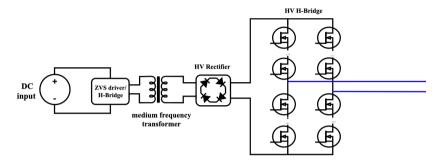

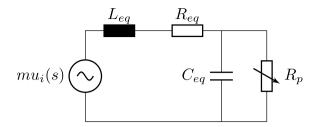

#### **2.5.** Modular Cascaded HV H-Bridge

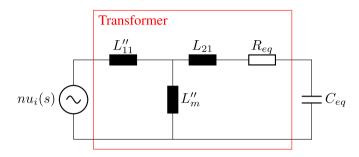

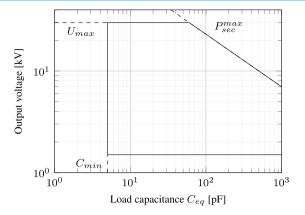

Fig. 2.6 presents the schematic of a submodule of the modular cascaded H-bridge-based HV-AWG, while Fig. 2.7 depicts the full-scale HV-AWG. The transformer can be driven by either a ZVS driver (soft-switching) or a standard H-bridge (hard-switching). Operating at 20-30 kHz, the medium frequency transformer provides

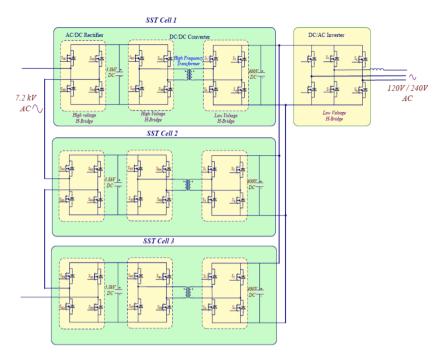

isolation level above 10 kV and steps up its input signal amplitude by a factor of 50. The HF output signals from the transformer are rectified to generate the DC signal (2-3 kV), which is then sent to the HV H-bridge input. This cascaded H-bridge-based HV-AWG design has a similar topology as the solid-state transformer (SST), decipted in Fig. 2.8 [11].

Figure 2.6: Desired cascaded H-bridge based HV-AWG submodule in a soft-switching topology

The modular CHB-based HV-AWG is used to test the insulation of system components, which can be considered as capacitive loads. Consequently, there is only a low output current requirement, up to 5 A [2]. With this low current, less heat is generated in the submodules, allowing for a potentially compact size. However, the transformer insulation system is quite vulnerable, as its permissible electric field strength significantly decreases if the input frequency increases to 20-30 kHz. Therefore, more insulation material is needed to withstand the high voltage, which conflicts with the goal of maintaining a compact size.

Compared to the CHB-based HV-AWG in a soft-switching topology, the hard-switching topology is simpler and cheaper to design owing to its circuit simplicity. Additionally, the hard-switching topology allows for a wider transformer operating frequency  $f_s$ , ranging from several kHz to tens of kHz. However, if the hard-switching topology is chosen, several considerations need to be addressed:

- The severity of LC oscillations caused by the leakage inductance  $L_{k(p)}$  or  $L_{k(s)}$  and parasitic capacitance  $\mathcal{C}_p$  on both sides should be manageable. To reduce the resonance severity, the simplest method is to minimize the primary and secondary leakage inductance and improve the flux linkage coupling by using the coaxial primary and secondary winding layout as described in [11].

- The switching energy loss  $P_{loss}$  of the power switches within the standard H-bridge should be considered. The input parasitic capacitances of the power switches (e.g. MOSFETs) can be hundreds of pF, and some leakage inductance  $L_k$  may also arise from the H-bridge PCB. Electrical energy will dissipate owing to these parasitic parameters within the H-bridge. Although, the CHB-based HV-AWG is used to test HV device insulation systems (capacitive loads), its output current  $I_{HV}$  can reach a few amperes. Under HF applications, the switching energy losses would be considerable.

Figure 2.7: Modular cascaded H-bridge based HV AWG with three submodules in series

- To achieve the same amount of HV-AWG submodule output voltage, a MFT with soft-switching (ZVS driver) can utilize an amplitude-enhanced input signal compared to the one with hard-switching (standard H-bridge). Consequently, fewer transformer secondary turns are needed because the resonant circuit boosts its output gain. This allows for a more compact transformer size.

- If the hard-switching topology is used in HF applications, there will be a large di/dt during the H-bridge transient period, causing significant voltage spikes and disturbances. This results in distortion of the H-bridge output waveform.

Inspired by the transformer inside the flyback converter shown in Fig. 2.3, the non-modular CHB-based HV-AWG topology is proposed, as illustrated in Fig. 2.9. This non-modular topology is suitable only for lower output voltages owing to the limitations of the transformer insulation system. In this schematic, the transformer has one primary and multiple secondary windings, which presents the biggest challenge for this topology. The advantages and drawbacks of this non-modular CHB-based HV-AWG are as follows:

Figure 2.8: The schematic of the solid state transformer [11] with similar scheme as the CHB-based HV-AWG

- Advantages: As shown in Fig. 2.9, the MFT has only one primary winding but several secondary windings. This design allows the manufacturer to reduce the cost associated with multiple primary circuits. Additionally, the output voltage from each transformer secondary winding, which will be rectified and fed to the HV H-bridge, can have exactly identical value.

- Drawbacks: The reliability of this non-modular topology is low. If the primary winding of the MFT fails, the entire arbitrary waveform generator will cease to function. Additionally, heat dissipation in the transformer core and windings will pose a significant problem. Furthermore, the high total output from the secondary windings necessitates a superior transformer insulation system. Last but not least, the coupling between the primary and secondary windings will be very low, requiring an additional primary compensation capacitor.

**In conclusion**, compared to the non-modular CHB based HV-AWG, the modular one has more advantages and should be eventually selected. Compared to the modular boost converter based HV-AWG, the CHB based HV-AWG submodule has higher voltage capability owing to the utilization of the MFT (galvanic isolation between LV and HV side). Also, the battery stack is replaced by the rectified 230 V, which can continuous power the HV-AWG and allow performing long-duration HV

Figure 2.9: Non-modular CHB based HV-AWG with soft-switching topology

and HF insulation aging tests. Comparing to the modular flyback converter based HV-AWG, apart from the replacement of the battery stack, the flyback converter is simplified to a compact MFT together with a LV H-bridge or ZVS driver and the prototype design cost can be reduced. The modular cascaded H-bridge based HV-AWG is selected. The following chapters address the corresponding research questions, with the design details presented in Chapters 4, 5, 6, and Appendix I.

# Balancing Techniques for the H-Bridge HV Switch<sup>1</sup>

#### 3.1. Background

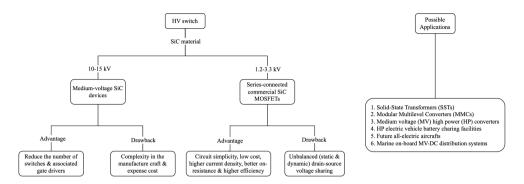

As the integration of renewables into the power grid continues to increase, the deployment of medium-voltage high-power converters, modular multilevel converters [2,12], and solid-state transformers [13,14] will become numerous in the near future. For the next generation of these PE-based systems, high efficiency, high voltage, and high power are essential for a wide range of applications, as summarized in Fig. 3.1. In this context, the role of semiconductor devices with the capability to operate at high switching frequencies, withstand elevated temperatures, and exhibit low switching losses becomes even more important.

Compared to silicon (Si), silicon carbide (SiC) excels in several properties, such as reasonable electron mobility, higher critical field strength and thermal conductivity. Moreover, SiC MOSFETs may have lower on-resistance  $R_{DS(on)}$ , higher blocking voltage, higher operation temperature, and can be used at higher switching frequencies [32]. Compared to IGBTs, SiC MOSFETs have no tail-current characteristics during the turn-off period, which contributes to lower switching losses and shorter turn-off delay.

Currently, MV SiC devices with a maximum blocking voltage of 10-15 kV have sparked significant interest for use in HV applications, although they have not yet been commercialized [33], [34]. The main limitations are the costs and the complexity of device manufacturing and packaging, which currently restrict the commercially available SiC MOSFETs to a maximum blocking voltage of 3.3 kV [35]. Whereas, to overcome this blocking voltage limitation and achieve higher system voltages, it is possible to connect multiple commercially available SiC MOSFETs in

<sup>&</sup>lt;sup>1</sup>W. Zhao, S. Ghafoor, G. W. Lagerweij, G. Rietveld, P. Vaessen, M. G. Niasar, "Comprehensive Investigation of Promising Techniques to Enhance the Voltage Sharing among SiC MOSFET Strings, Supported by Experimental and Simulation Validations", Electronics 13, 1481 (2024).

Figure 3.1: Properties for different types of HV switches (left) and their possible applications (right) [12,15–31]

series. Figure 3.1 provides a detailed overview of the advantages and drawbacks of such SiC MOSFET strings and MV SiC MOSFETs.

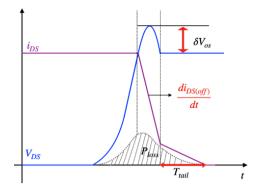

Using multiple low-cost and commercially available SiC MOSFETs in series allows the required HV operation with simple yet mature gate-driving techniques. The major obstacle to implementing the series-connected operation is maintaining an equal voltage distribution across the SiC MOSFET string under all operating and transient conditions. Voltage balancing is essential to achieve equal stressing of the MOSFETs, and consequently high reliability and higher operating voltages without voltage derating. The voltage imbalance is primarily caused by mismatched gate driving signals, the existence of SiC MOSFET intrinsic and external parasitic capacitances and inductances [36], and the variation in SiC MOSFET off-resistance. These factors result in switching delays or time shifts (several ns to tens of ns), variation in  $\mathrm{d} V_{\mathrm{GS}}/\mathrm{d} t$ , and voltage imbalance across the MOSFET string.

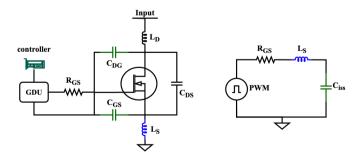

#### **3.1.1.** Factors Influencing Drain-Source Voltage Distribution

The factors that can cause unequal drain-source voltage sharing of the SiC MOSFET string are elaborated in this subsection. A testing circuit composed of two series-connected SiC MOSFETs and one current-limiting resistor is shown in Fig. 3.2, which is used to analyze the impact of various factors on the voltage sharing among the SiC MOSFET string.

**Variation in MOSFET switching delay**  $\delta$   $t_d$ : According to the measured results shown in Table. 3.1, ignoring the other possible factors, the intrinsic variation in the switching delay is not the dominant factor causing  $V_{DS}$  imbalance. Also, part of the variation in  $t_{d(on)}$  and  $t_{d(off)}$  between the measured values and the typical values from datasheets may be due to different measuring conditions. Generally, the variation in MOSFET parasitic parameters is limited if the devices are bought from good manufacturers and selected from the same production batch. However, gate threshold voltage of SiC MOSFET may vary with temperature, and from device

to device. This can contribute to a larger  $\delta t_d$ .

Fifteen measurements of switch type IMW120R220M1H (Infineon) or C3M0280-090D (Wolfspeed) are performed based on [37] and the median is taken as the typical value of  $t_{d(on)}$  and  $t_{d(off)}$ . Among all of the obtained data, the intrinsic variation in  $t_{d(on)}$  and  $t_{d(off)}$  are 2.0 and 2.4 ns (IMW120R220M1H), and 2.3 and 1.6 ns (C3M0280090D).

| Table 3.1: The turn-on and | -off delay of two types ( | of commercially | available SiC MOSFETS |

|----------------------------|---------------------------|-----------------|-----------------------|

|                            |                           |                 |                       |

| SiC MOSFET    | Datasheet   |              |             | Meası             | ırement      |                    |

|---------------|-------------|--------------|-------------|-------------------|--------------|--------------------|

|               | $t_{d(on)}$ | $t_{d(off)}$ | $t_{d(on)}$ | $\deltat_{d(on)}$ | $t_{d(off)}$ | $\deltat_{d(off)}$ |

| IMW120R220M1H | 5.0 ns      | 10.0 ns      | 6.8 ns      | ±2.0 ns           | 12.8 ns      | ±2.4 ns            |

| C3M0280090D   | 5.3 ns      | 8.5 ns       | 7.7 ns      | ±2.3 ns           | 11.6 ns      | ±1.6 ns            |

**Variation in gate driver switching delay**  $\delta \, t_d$ : The variation in switching delay that arises due to variations in the gate driver circuitry, components, and layout (i.e., the external factors) are much more significant than the intrinsic variation of the MOSFET. For example, the maximum switching delay variation  $\delta \, t_{d(max)}$  reported in [38,39] of the isolated gate driver type STGAP2SICSN (e.g.) and that of the non-isolated gate driver type IXDD630MCI (e.g.) is around 40 ns. Moreover, according to [40], that of the opto-coupler type FOD3182 (e.g.) can even reach 160 ns. The value of  $\delta \, t_{d(max)}$  can be reduced by sorting, binning, and matching components, thus reducing the voltage imbalance.

Figure 3.2: Basic schematic for testing two series-connected SiC MOSFETs

**Parasitic capacitances from MOSFET gates to ground**: According to [41], as seen in Fig. 3.2, the  $\mathcal{C}_{gi}$  existing from respective gates to ground is observed as the dominating factor contributing to the unbalanced  $V_{DS}$  sharing among the MOSFET string. If the MOSFETs and driving components were identical, identical sink currents would flow to the drivers  $(i_{ai}=i_{d2})$ . However, due to the difference between the voltages  $V_{Gi}$  with respect to ground, a variation in the gate voltage slopes occurs, which results in a different magnitude of capacitive currents  $i_{ci}$  and creates a difference in total gate currents  $i_{gi}$ , leading to voltage imbalance.

In Fig. 3.2, the total gate current  $i_{gi}$  is the sum of the gate sink current  $i_{di}$  and capacitive current  $i_{ci}$  from the gate to ground. The dv/dt at the gate of the top MOSFET is equal to that at the drain of the bottom MOSFET ( $V_{G2} \approx V_{D1}$ ), while the gate of the bottom MOSFET is almost at ground potential. Thus,  $dv_{G2}/dt$  is higher than  $dv_{G1}/dt$  and the resultant capacitive current  $i_{c2}$  is also larger than  $i_{c1}$ . Moreover, the difference in  $C_{gi}$  from the stacked gate terminals to ground will also play a role in altering the intensity of the total gate current  $i_g$  when the number of the involved MOSFETs is large. For a small number of MOSFETs, the difference in  $C_{gi}$  can be neglected. This shows that even with perfectly matched gate drivers,  $i_{g2} > i_{g1}$ , resulting in faster turn-off of the top MOSFET.

**Variation in MOSFET off-resistance**  $R_{DS(off)}$ : Owing to the presence of the variation in SiC MOSFET  $R_{DS(off)}$ , the static  $V_{DS}$  sharing of the series-connected MOSFETs may be unbalanced. Balancing resistors ought to be connected in parallel with the SiC MOSFETs to achieve balanced static voltage sharing. Furthermore, during the  $V_{DS}$  measurement, the impedance of the differential probes will influence the balancing resistor network, and thus should also be considered.

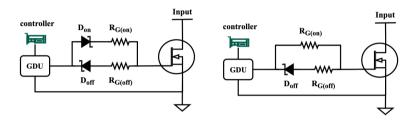

#### **3.1.2.** State-of-the-Art Solutions

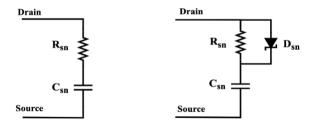

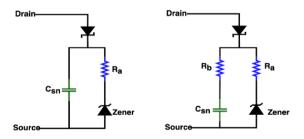

Over the past decades, various solutions have been proposed to improve the voltage sharing between series-connected MOSFETs. These methods can be categorized into static and dynamic balancing. Most challenges are encountered in the dynamic balancing. Some of the proposed solutions are: Zener clamping circuits, passive snubber circuits, and gate signal delay adjustment methods.

To avoid the SiC MOSFET breakdown caused by the unbalanced voltage sharing, the Zener clamping circuit is introduced in [42] and evaluated in [43]. The overvoltage across the MOSFET is eliminated by clamping  $V_{DG}$  through the series-connected Zener diodes whose equivalent reverse breakdown voltage  $V_Z$  is chosen based on the blocking voltage of the MOSFET. In [44], four types of passive snubbers are summarized with thorough principle elaboration. The purpose of introducing these passive snubbers is either to reduce the rise slew rate  $dv_{DS}/dt$  or to clamp the  $V_{DS}$  in such a way that the series-connected MOSFETs can share identical voltages.

The gate signal delay adjustment methods can compensate the delay time variation without slowing down the switching speed. In [45], Kiyoaki reports an important technique named the gate-balancing core (GBC) method which uses gate-coupled magnetic cores to synchronize the SiC MOSFET gate drive currents. In [46], an improved RC snubber method is proposed by S.Chen, which has a combination of the passive snubbers and the gate signal delay adjustment methods. The key

point of this method is the use of a three-port inductor whose primary windings are coupled within two snubber circuits and whose secondary winding is in series with the gate. The induced voltages from the secondary windings will be added to the gate circuits to tune  $V_{GS}$  and achieve identical gate currents.

Reliable and robust voltage balancing techniques must achieve effective voltage balancing, minimize the number of components within the balancing circuit, simplify the gate-side control circuits and introduce minimal switching losses [47]. The purpose of this chapter is to provide a detailed and concise evaluation of various approaches dealing with the unbalanced voltage sharing among the SiC MOSFET string. The pros and cons of each method are discussed and the suitable conditions for the application of each method are provided.

## 3.2. Static Voltage Balancing Method

The factors that can lead to the static voltage imbalance are thoroughly examined, underscoring the significance of this issue. A promising solution is then proposed and validated, to improve the static voltage sharing of the SiC MOSFET string. Additionally, the correct use of differential probes to measure the SiC MOSFET drain-source voltage is explained, an important aspect that can significantly influence the static voltage sharing of the MOSFET string while performing drain-source voltage measurements.

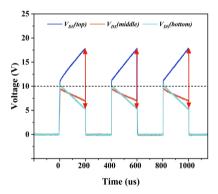

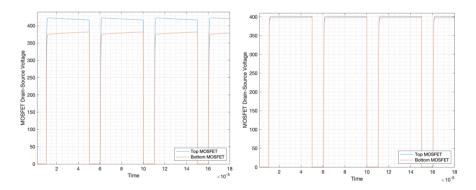

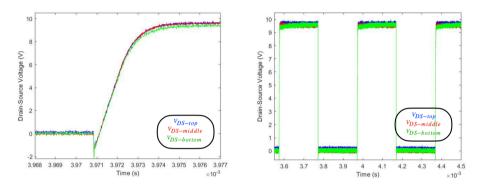

Figure 3.3: Measured unbalanced  $V_{DS}$  sharing of the SiC MOSFET string without (left) and with (right) the identical balancing resistors (500  $k\Omega$ )

As seen in Fig. 3.3 (left), an unbalanced static voltage sharing issue occurs on the three series-connected MOSFETs. This phenomenon can occur due to variation of the off-resistance  $R_{DS(off)}$  of the MOSFETs or the impact of the measurement probe. This issue can be effectively addressed through the utilization of static balancing resistors  $R_{st}$ , which equalizes the voltage stress in the series-connected devices at the cost of increased static power dissipation. The MOSFETs chosen for experiments are of type IMW120R220M1H. From its datasheet, if the applied drain-source voltage is 1.2 kV, the drain leakage current  $I_{DSS}$  varies over two decades (0.2  $\mu A$  to 95  $\mu A$ ) at an ambient temperature of 25 °C. Therefore, the corresponding MOSFET

off-resistance  $R_{DS(off)}$  varies from  $6 G\Omega$  to  $12.6 M\Omega$ .

Generally, the value of the parallel balancing resistor  $R_{st}$  should be selected at least 10 times smaller than the minimum  $R_{DS(off)}$ . The parallel combination of  $R_{st}$  and  $R_{DS(off)}$  will then be dominated by the balancing resistor, reducing the effect of variation in  $R_{DS(off)}$ . The power loss in each balancing resistor is calculated using (3.1). With a derating of 40% and a maximum dissipation of 1 W, a minimum  $R_{st}$  of 500  $k\Omega$  is calculated.

$$P_{st} = \frac{U_{max}^2}{R_{st}} = \frac{(0.6 * V_{DSS})^2}{R_{st}} = \frac{(0.6 * 1200)^2}{500 * 10^3} \approx 1 W$$

(3.1)

During the measurement of MOSFET drain-source voltages, even though the static balancing resistors ( $R_{st} = 500 \, k\Omega$ ) are applied, the static voltages along the SiC MOSFET string are not yet balanced, as shown in Fig. 3.3 (right).

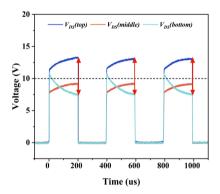

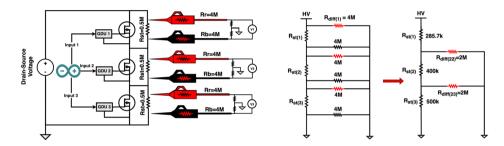

Figure 3.4: Schematic of the  $V_{DS}$  measurement of the three series-connected SiC MOSFETs (left) and the corresponding resistance ladder network (right)

The reason for this phenomenon is that the impedance of the differential probes  $R_r=4\,M\Omega$  and  $R_b=4\,M\Omega$  must be considered as part of the balancing resistor network, as shown in Fig. 3.4 (left), which influences the static voltage sharing. Hence, while observing the drain-source voltage,  $R_{st}$  should be fine-tuned only during the tests to prevent static voltage imbalance. Fig. 3.4 (right) shows the simplification of the resistive network during  $V_{DS}$  measurement. Assuming the value of  $R_{st(3)}$  that is applied across the bottom MOSFET is  $500\,k\Omega$ , the presence of the probe impedance  $R_{diff(23)}$  changes the required value of  $R_{st(2)}$  for the middle switch to  $400\,k\Omega$ , using (3.2). Similarly, the total equivalent resistance for the bottom two MOSFETs combined with  $R_{diff(22)}$  and  $R_{diff(23)}$  is about  $571.4\,k\Omega$ . Therefore, the magnitude of  $R_{st(1)}$  should be half the value of the obtained total equivalent resistance, calculated using (3.3).

$$R_{st(2)} = R_{st(3)} || R_{diff(23)} = 400 k\Omega$$

(3.2)

$$R_{st(1)} = \frac{1}{2} * \left[ (2 \cdot R_{st(2)}) || R_{diff(22)} \right] = 285.7 \, k\Omega$$

(3.3)

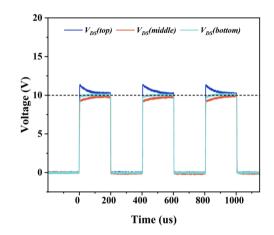

After the application of the tuned static balancing resistors as shown in Fig. 3.4 (right), the balanced static voltage sharing of the MOSFET string can be achieved

(Fig. 3.5). However, due to the existence of the parasitic capacitances and inductances, the unmatched MOSFETs and gate drivers, balanced dynamic voltage sharing is not yet achieved.

Figure 3.5: Measured overall  $V_{DS}$  sharing of the MOSFET string with tuned balancing resistors

The balancing resistors with tuned values are only used to observe the statically balanced  $V_{DS}$  waveforms on the oscilloscope during experiments. If the SiC MOSFET string is used under HV applications, the value of the required balancing resistors should be identical since there is no requirement to measure the drain-source voltages during normal operation.

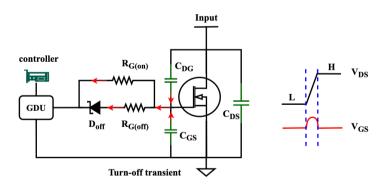

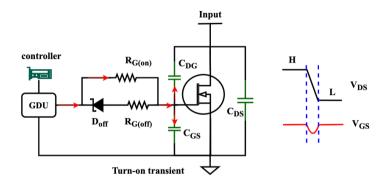

## **3.3.** Gate-Balancing Core (GBC) Method

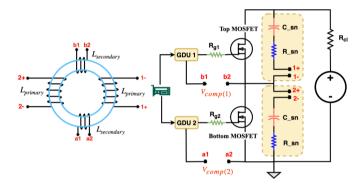

This section evaluates the GBC method to improve the dynamic  $V_{DS}$  sharing in a string of series-connected MOSFETs. This method is based on gate signal delay adjustment. The method is validated by experiments, which are relevant for a SiC MOSFET string with a considerable variation in the turn-off delay  $t_{d(off)}$ . In [45,48], the GBC method is proposed to synchronize mismatched gate currents. The key point of this method is the use of a coupled inductor with a high coupling factor k, which is well-coupled within the adjacent gate circuits of the SiC MOSFET string. The magnetic coupling will impose almost identical gate sink currents ( $I_{g1} \approx I_{g2}$ ), even if a considerable turn-off delay time variation  $\delta t_{d(off)}$  exists.

When a slight turn-off delay  $\delta t_{d(off)}$  is present in the bottom MOSFET, as depicted in Fig. 3.6, the top MOSFET switches off faster. Its gate current  $I_{g1}$  flows through the upper winding of the coupled inductor and returns to the gate driver. The induced current  $I_{g2}$  occurs simultaneously with  $I_{g1}$  on the lower winding through magnetic coupling. If the turns ratio is 1:1 and k is close to 1, the magnitudes of the induced gate current  $I_{g2}$  and the initial sink current  $I_{g1}$  are identical. This synchronization of the gate currents leads to balanced voltage sharing among the series-connected MOSFETs. Fig. 3.7 further illustrates the extension of the GBC method to a higher number of series-connected SiC MOSFETs. The inter-winding

Figure 3.6: Schematic of the two series-connected SiC MOSFETs using the GBC method

insulation requirements are relaxed since inductors are only coupled between consecutive MOSFETs.

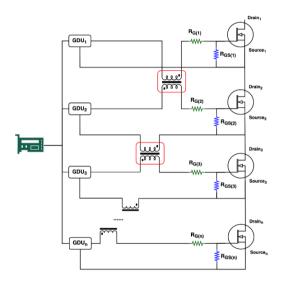

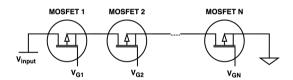

Figure 3.7: Schematic of the multiple series-connected SiC MOSFETs using the GBC method

The coupled inductor leakage inductance  $L_k$  can resonate with the dynamic input capacitance  $C_{iss}$  of the MOSFET. It should be minimized to avoid excessive ringing or oscillations on the transient parts of the gate pulses, which influences the output performance of the MOSFET string. Thus, interleaved inductor construction is recommended. Equations (3.4) and (3.6) are derived to calculate the required magnetizing inductance  $L_m$  and leakage inductance  $L_k$  in case of a particular variation in  $\delta t_{d(off)}$  among the series-connected MOSFETs [45,48].

In (3.4),  $\delta t_{d(off)}$  is the turn-off delay variation of the corresponding SiC MOS-FETs, and  $C_{iss}$  stands for the MOSFET input capacitance. Equation (3.4) is derived based on the assumption that the gate voltage variation  $\delta V_{GS}$  is smaller than 1%

of the input gate voltage  $V_{GS}$ .

$$L_m > \frac{1}{2} \cdot \frac{\delta t_{d(off)}^2}{0.01 \cdot C_{iss}} \tag{3.4}$$

The magnitude of  $\delta V_{GS}$  depends on the amount of discharge  $\delta Q_m$  of  $C_{iss}$  (undelayed) by the magnetizing current  $i_m$  shown in (3.5). Based on the equivalent inductor circuit model, the  $C_{iss}$  of the undelayed switch is discharged by the present magnetizing current  $i_m$  and the gate sink current  $i_g$ . However, the  $C_{iss}$  of the delayed switch is discharged only by  $i_g$ . To synchronize the gate discharge currents, the value of  $L_m$  should be sufficiently large to suppress the magnetizing current  $i_m$ . It should be noted that the total voltage applied on the magnetizing inductance  $L_m$  is  $V_{GS}$  during the turn-off delay period.

$$\delta V_{GS} = \frac{\delta Q_m}{C_{iss(undelayed)}} = \frac{i_{m(pk)} \cdot \delta t_{d(off)}}{2 \cdot C_{iss(undelayed)}}$$

$$i_{m(pk)} = \frac{\delta t_{d(off)} \cdot V_{GS}}{L_m}$$

(3.5)

Combining the formulas in (3.5) eventually leads to (3.4). If the value of  $\delta t_{d(off)}$  is relatively small (e.g., 50 ns), the assumption that  $\delta V_{GS}$  should be smaller than 1% of  $V_{GS}$  leads to a reasonable size of  $L_m$ . However, if the value of  $\delta t_{d(off)}$  is quite large (e.g., 250 ns), the allowable gate voltage mismatch should be increased to avoid having an unrealistically large  $L_m$ . The magnitude of  $\delta V_{GS}$  should then be smaller than 5% of  $V_{GS}$ . Therefore, the denominator of (3.4) is modified as  $0.1C_{iss}$ . Moreover,  $R_g$  stands for the total gate resistance, including the internal resistance of the gate driver.

$$L_k \le \frac{C_{iss} R_g^2}{4\zeta^2} = \frac{C_{iss} R_g^2}{0.64} \tag{3.6}$$

The leakage inductance  $L_k$  of the gate-coupled inductors can be seen as parasitic inductances in the wires between the gate drivers and MOSFETs. The value of  $L_k$  should be designed to prevent the initial and induced gate currents from severe oscillations generated by  $L_k$  and  $C_{iss}$ . The desired tiny  $L_k$  can be difficult to realize if the damping factor  $\zeta$  is chosen to be relatively large ( $\geq 0.7$  in [48]). Usually, the integrated gate driver IC has some internal output resistance of around  $5\,\Omega$ , and an external gate resistance of  $10\,\Omega$  is suggested, leading to a total value of  $R_g=15\,\Omega$ . Assuming  $\zeta$  equals or exceeds 0.4, the required leakage can be realized and the computed k is more than 0.9999.

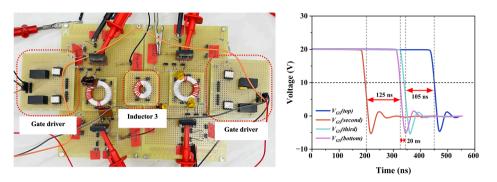

# **3.3.1.** Experiments with Two Series-Connected MOSFETs Using the Gate Balancing Core Method

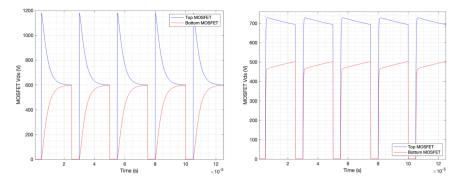

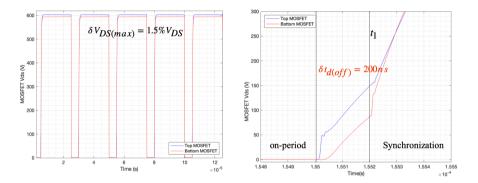

In [45], it is shown that for the case of two series-connected power switches, dynamic  $V_{DS}$  sharing can be achieved with a turn-off delay variation  $\delta t_{d(off)}$  of up

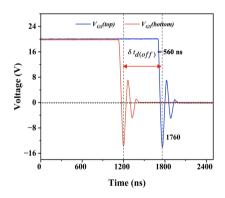

to 80 ns using the GBC method. Experiments are performed to investigate the  $V_{DS}$  sharing when a longer  $\delta t_{d(off)}$  of up to 560 ns exists, further demonstrating the robustness of the GBC method.

Figure 3.8: Experimental set-up of the series-connected SiC MOSFETs using the GBC method

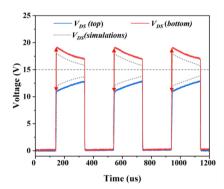

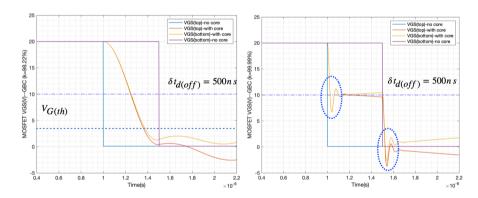

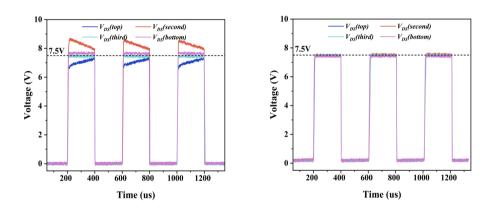

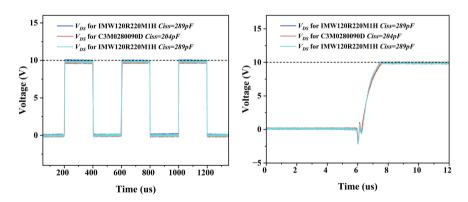

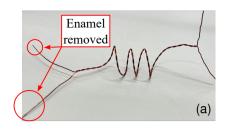

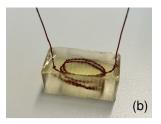

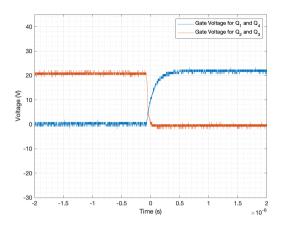

Fig. 3.8 shows the experimental set-up with a two-switch MOSFET string using the GBC method. The switching frequency of this prototype is 2.5 kHz. For the case of two MOSFETs operating in series, compared with the bottom switch, the top one has an additional 560 ns turn-off delay, as shown in Fig. 3.9 (left). The coupled inductor is constructed with interleaved windings, resulting in a coupling factor of k = 99.99%. The winding inductances  $L_{se}$  are 4.71 mH (white) and 4.56 mH (red), while the leakage inductances  $L_k$  are 390 nH (white) and 373 nH (red), shown as detail in Fig. 3.9 (right).

Figure 3.9: Measured  $V_{GS}$  waveforms of the two series-connected MOSFETs during turn-off period without (left) and with the gate-coupled inductor with simulation verification (right)

Fig. 3.9 illustrates how the presence of the gate-coupled inductor influences the gate voltages. Before using the coupled inductor, an extra 560 ns delay results in a noticeable difference in turn-off time. After inserting the coupled inductor in the gate circuits, the gate voltages of the MOSFET string are almost perfectly

synchronized and balanced at half of the input gate voltage. At the end of the delay  $\delta t_{d(off)}$ ,  $V_{GS(top)}$  (delayed) is slightly higher than  $V_{GS(bottom)}$  (undelayed). This will be further explained in Section 3.3.2 using analytical calculations.

The gate voltages balance at  $0.5V_{GS}$  during  $\delta t_{d(off)}$  because the magnetizing inductance is sufficiently large to suppress  $i_m$ . This limits the gate voltage variation to less than 5% of  $V_{GS}$  and  $V_{GS(top)} \approx V_{GS(bottom)}$ . Since the value of  $i_m$  is negligible, if the turns ratio is set to be 1:1, the  $C_{iss}$  of the delayed MOSFET and that of the undelayed MOSFET are discharged by identical gate currents  $i_g$ . Hence, the gate currents of all MOSFETs are synchronized, and the induced voltage  $V_{T(top)}$  is equal to the lower winding voltage  $V_{T(bottom)}$ . According to (3.7), the sum of  $V_{GS(top)}$  and  $V_{GS(bottom)}$  is the input gate voltage. Therefore, the final balance point is  $0.5V_{GS}$ .

$$Delayed: V_{GS} = V_{GS(top)} + V_{T(top)}$$

$$Undelayed: 0 = V_{GS(bottom)} - V_{T(bottom)}$$

(3.7)

The parasitic parameters slightly distort the obtained  $V_{GS}$  waveforms. However, this issue can be tackled by using two reverse-biased placed diodes in series with the external gate resistors [49] circled in red in Fig. 3.6. Moreover, the comparison in Fig. 3.10 demonstrates that the GBC method can significantly improve the  $V_{DS}$  sharing of the SiC MOSFET string in case of the presence of a large  $\delta t_{d(off)}$ .

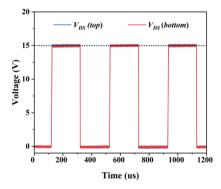

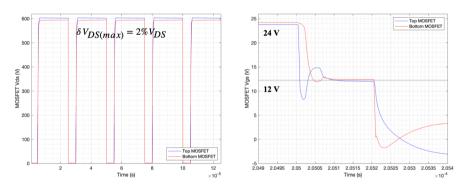

Figure 3.10: Measured  $V_{DS}$  of the MOSFET string with (left) and without coupled inductor with simulation verification (right)

From a commercial perspective, N series-connected SiC MOSFETs require (N-1) coupled inductors, which can be expensive and result in a bulky solution. However, the circuit and gate-side routing are simple, which reduces the cost of components and manufacturing. Moreover, the required insulation level of the gate-coupled coupled inductor is low  $(V_{input}/N)$ ; thus, the cost of each component is reasonable. This means that the GBC method is quite commercially attractive.

# **3.3.2.** Analytical Analysis of Dynamic Voltage Sharing Using the GBC Method

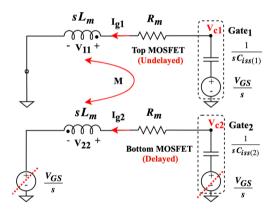

Balanced dynamic voltage sharing of the MOSFET string can be achieved through the GBC method in case of a large  $\delta t_{d(off)}$ , as shown in Fig. 3.10 (left). To better understand the performance of the MOSFET  $V_{GS}$  waveforms during  $\delta t_{d(off)}$  with the gate-coupled inductors, an analytical method is derived based on the equivalent gate circuits of the two series-connected SiC MOSFETs during  $\delta t_{d(off)}$ , as shown in Fig. 3.11.

Compared with the top MOSFET, the bottom one is assumed to have some extra turn-off delay. Therefore, from Fig. 3.11, the bottom MOSFET remains in the on-state. Meanwhile, the top MOSFET is switched off. It can also be noted that the MOSFET gate circuits are simplified as the charged dynamic input capacitors  $(C_{iss(1)} \text{ and } C_{iss(2)})$  circled by black dotted lines. The analytical method is derived for the case with perfect coupling (k=1, similar to the previous experimental case). Consequently, the self-inductance of the windings will become equal to the magnetizing and mutual inductance  $(L_{se} = L_m = M)$ .

Figure 3.11: Equivalent gate circuits of the two series-connected SiC MOSFETs using GBC method

Fig. 3.11 indicates the propagation direction of the gate discharge currents ( $I_{g1}$  and  $I_{g2}$ ) and the polarity of the inductor winding voltages. Due to the difference in polarity, the voltages across the upper ( $V_{11}$ ) and lower ( $V_{22}$ ) winding can be calculated from (3.8).

$$V_{11} = sL_m I_{g1} - sM I_{g2} = sL_m (I_{g1} - I_{g2})$$

$$V_{22} = sL_m I_{g2} - sM I_{g1} = sL_m (I_{g2} - I_{g1})$$

(3.8)

The input voltage of the bottom MOSFET gate circuit is provided by the gate driver (left), and the remaining voltage on  $C_{iss(2)}$  (right) is canceled. Hence, the voltage across the inductor lower winding can be calculated as:  $V_{22} = -I_{g2}$ .

$\left(R_m + \frac{1}{sc_{iss}}\right)$ . The relationship between the gate sink currents  $I_{g1}$  and  $I_{g2}$  is shown in (3.9). Also, the MOSFET gate voltages are calculated using (3.10).

$$\frac{I_{g2}}{I_{g1}} = \frac{sL_m}{sL_m + R_m + \frac{1}{sC_{in}}} \tag{3.9}$$

$$V_{c(i)} = \frac{V_{GS}}{s} - \frac{I_{g(i)}}{sC_{iss(i)}} (i = 1, 2)$$

(3.10)

If the winding resistance  $R_m$  is neglected, the gate discharge current  $I_{g1}$  for the gate circuit of the top switch (undelayed) can be derived using (3.11) and (3.12).

$$\frac{V_{GS}}{s} = V_{11} + I_{g1} \cdot R_m + \frac{I_{g1}}{sC_{iss}}$$

(3.11)

$$I_{g1} = V_{GS} \cdot \frac{C_{iss}(1 + s^2 L_m C_{iss})}{1 + 2s^2 L_m C_{iss}}$$

(3.12)

According to (3.9) and (3.12), the formula of  $I_{g2}$  can be derived as shown in (3.13). After the combination of (3.10) and (3.12), (3.10) and (3.13), the gate voltages of two involved MOSFETs can be derived as (3.14).

$$I_{g2} = V_{GS} \cdot \frac{s^2 L_m C_{iss}^2}{1 + 2s^2 L_m C_{iss}}$$

(3.13)

$$V_{c1} = V_{GS} \cdot \frac{sL_m C_{iss}}{1 + 2s^2 L_m C_{iss}} V_{c2} = V_{GS} \left( \frac{1}{s} - \frac{sL_m C_{iss}}{1 + 2s^2 L_m C_{iss}} \right)$$

(3.14)

Figure 3.12:  $V_{GS}$  curves of the MOSFET string during the turn-off delay with coupled inductor (k = 1)

At the beginning of  $\delta t_{d(off)}$ , the frequency content of the gate voltage waveforms  $(V_{GS(top)})$  and  $V_{GS(bottom)})$  is large, and the gate current  $I_{g1}$  is almost the same as  $I_{g2}$  based on (3.9). Thus, based on (3.10), the value of  $V_{GS(top)}$  should also be the same as  $V_{GS(bottom)}$ . On the other hand, when the high-frequency harmonics decay, the magnitude of  $I_{g2}$  will become smaller than  $I_{g1}$ , and  $V_{GS(bottom)}$  will be larger than  $V_{GS(top)}$ . These obtained results verify that during  $\delta t_{d(off)}$ ,  $V_{GS(bottom)}$  (delayed) first resonates synchronously with  $V_{GS(top)}$  (undelayed) but becomes larger than  $V_{GS(top)}$  after the oscillations, as shown in Fig. 3.12. As a result, the experimental result shown in Fig. 3.9 (right) matches the analytical results.

If the coupling factor k of the inductor is close to 1, the leakage inductance  $L_k$  will be minimal, and the corresponding  $V_{GS}$  oscillation period will also be small. When the oscillations decay, the gate voltage variation  $\delta V_{GS}$  will occur. Conversely, if k is relatively low, the oscillation period  $T_o$  will be much larger, and the gate voltages can be precisely synchronized during the entire period of  $\delta t_{d(off)}$ .

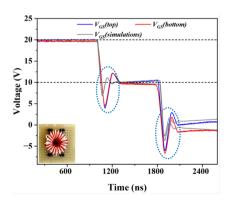

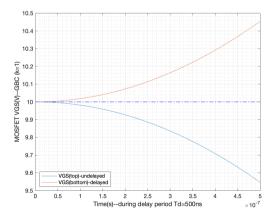

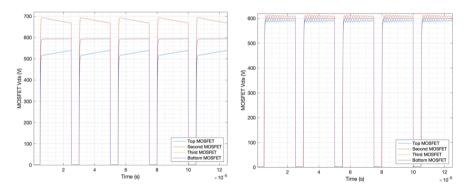

# **3.3.3.** Simulation Verification of Dynamic Voltage Sharing Using the GBC Method

The analytical calculations are verified against the obtained experimental results. The behavior of the  $V_{GS}$  waveforms during the entire  $\delta t_{d(off)}$  is verified using Simulink based on Fig. 3.11, which only focuses on the gate circuits of the SiC MOSFET string. The parameters of the simulation model are all extracted from the experiments: The bottom SiC MOSFET has an extra 500 ns turn-off delay compared to the top MOSFET, and the self-inductance of both inductor windings is 4.56 mH. The dynamic input capacitance of the MOSFETs is 289 pF (IMW120R220M1H).