### Front-End ASICs for 3-D Ultrasound From Beamforming to Digitization

Chen, Chao

10.4233/uuid:a5002bb0-4701-4e33-aef6-3c78d0c9fd70

**Publication date**

**Document Version** Final published version

Citation (APA)

Chen, C. (2018). Front-End ASICs for 3-D Ultrasound: From Beamforming to Digitization. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:a5002bb0-4701-4e33-aef6-3c78d0c9fd70

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Front-End ASICs for 3-D Ultrasound:

# From Beamforming to Digitization

#### Dissertation

for the purpose of obtaining the degree of doctor

at Delft University of Technology

by the authority of the Rector Magnificus, prof.dr.ir. T.H.J.J. van der Hagen,

Chair of the Board for Doctorates

to be defended publicly on

Tuesday 3 April 2018 at 12:30 o'clock

by

#### **Chao CHEN**

Master of Science in Electrical Engineering

Delft University of Technology, The Netherlands

born in Longhai, Fujian Province, P.R. China

This dissertation has been approved by the promotors.

Composition of the doctoral committee:

Rector Magnificus, chairperson

Prof. dr. ir. N. de Jong

Delft University of Technology, promotor

Dr. ir. M.A.P. Pertijs

Delft University of Technology, promotor

Independent members:

Prof. dr. ir. R. Dekker Delft University of Technology

Prof. dr. R. Puers

Dr.ir. P.J.A. Harpe

Eindhoven University of Technology

Prof. dr. S. Cochran

Katholieke Universiteit Leuven, Belgium

Eindhoven University of Technology

University of Glasgow, United Kingdom

Dr. ir. Z. Yu

Institut für Mikroelektronik Stuttgart, Germany

Prof. dr. K.A.A. Makinwa

Delft University of Technology, reserve member

This thesis work is supported by the Dutch Technology Foundation (STW), which is part of the Netherlands Organization for Scientific Research (NWO), and which is partly funded by the Dutch Ministry of Economic Affairs, in the framework of the program MICA: "Miniature ultrasound probe for real-time three-dimensional imaging and monitoring of Cardiac interventions".

Printed by Ridderprint BV | www.ridderprint.nl.

ISBN: 978-94-6299-940-4

Copyright © 2018 by Chao CHEN

All rights reserved. No part of this publication may be reproduced or distributed in any form or by any other means, or stored in a database or retrieval system, without the prior written permission of the author.

致我爱的爸爸妈妈和晓靓

To my beloved parents and Xiaoliang

# TABLE OF CONTENTS

| TABLE OF CONTENTS                                       | I       |

|---------------------------------------------------------|---------|

| INTRODUCTION                                            | 1       |

| 1.1 BACKGROUND AND MOTIVATIONS                          |         |

| 1.2 BASIC PRINCIPLES                                    | 4       |

| 1.3 Challenges                                          |         |

| 1.4 Context of the Research                             | 10      |

| 1.5 Thesis Organization                                 | 12      |

| References                                              | 13      |

| LOW-NOISE AMPLIFIERS FOR ULTRASOUND                     | 17      |

| 2.1 Architecture Choices                                |         |

| 2.2 A COMPACT, LOW-POWER LNA FOR PIEZOELECTRIC TRANSDUC | CERS 23 |

| 2.2.1 Introduction                                      | 23      |

| 2.2.2 LNA Archiecture                                   | 24      |

| 2.2.3 Circuit Implementation                            | 26      |

| 2.2.4 Experimental Results                              | 29      |

| 2.2.5 Conclusions                                       | 33      |

| 2.3 A SINGLE-CABLE LNA READOUT IC FOR PVDF TRANSDUCER   | 33      |

| 2.3.1 Introduction                                      | 33      |

| 2.3.2 Prototype Assembly                                | 35      |

| 2.3.3 Readout IC Design                                 | 36      |

| 2.3.4 Experimental Results                              | 38      |

| 2.3.5 Conclusions                                       |         |

| References                                              |         |

| PZT MATRIX WITH INTEGRATED RECEIVE ASIC                 | 45      |

| 3.1 Introduction                                        |         |

| 3.2 Methods                                             |         |

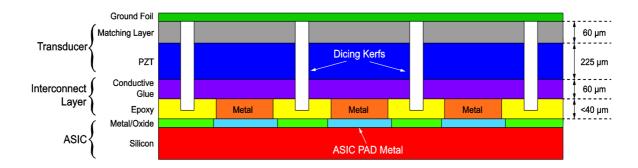

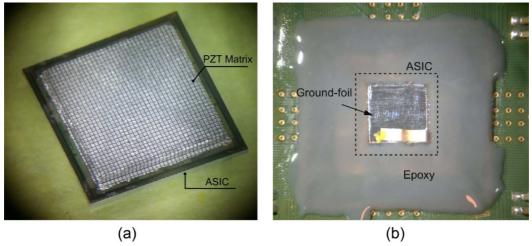

| 3.2.1 Transducer Matrix on CMOS                         |         |

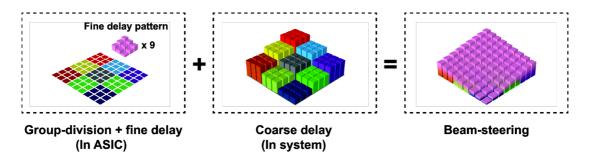

| 3.2.2 Micro-beamforming                                 |         |

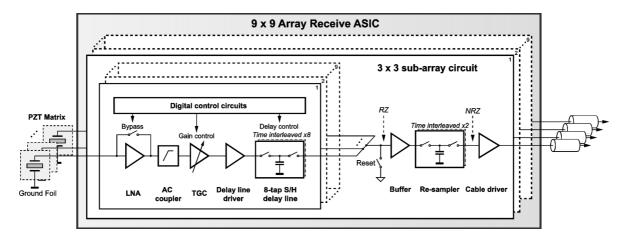

| 3.3 IMPLEMENTATION OF THE RECEIVE ASIC                  |         |

| 3.3.1 Front-end Amplifiers                              |         |

| 3.3.2 Micro-beamformer                                  |         |

| 3.3.3 Auxiliary Circuits                                |         |

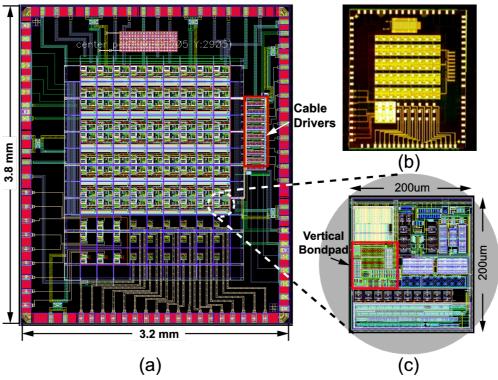

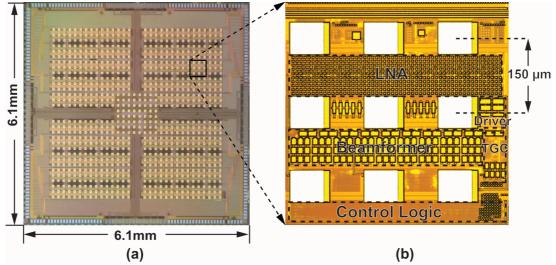

| 3.3.4 Silicon Realization                   | 57       |

|---------------------------------------------|----------|

| 3.4 EXPERIMENTAL RESULTS                    | 58       |

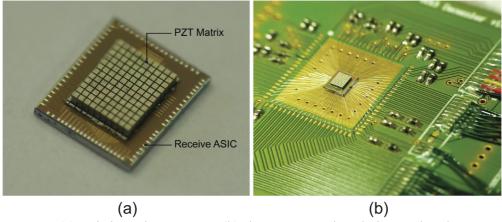

| 3.4.1 Fabricated Prototype                  | 58       |

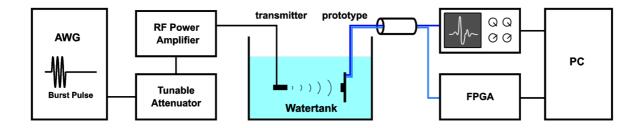

| 3.4.2 Acoustic Measurement Setup            | 58       |

| 3.4.3 Single-element Characterization       | 59       |

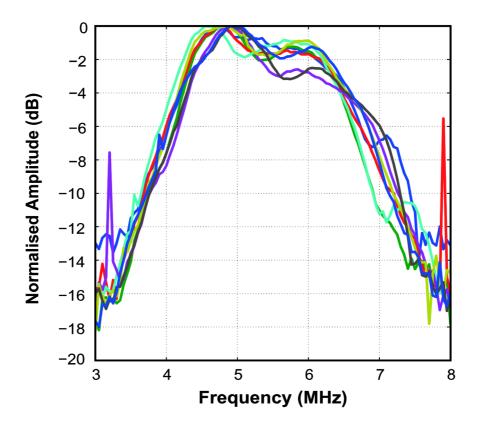

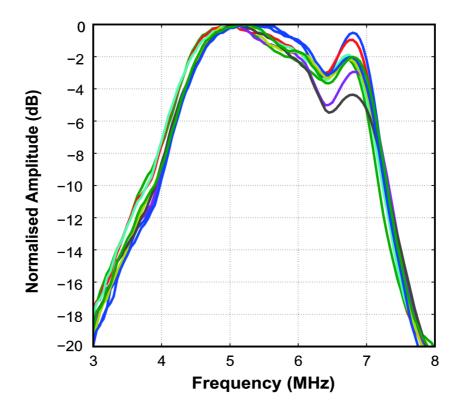

| 3.4.4 Micro-beamforming: Frequency Response | 61       |

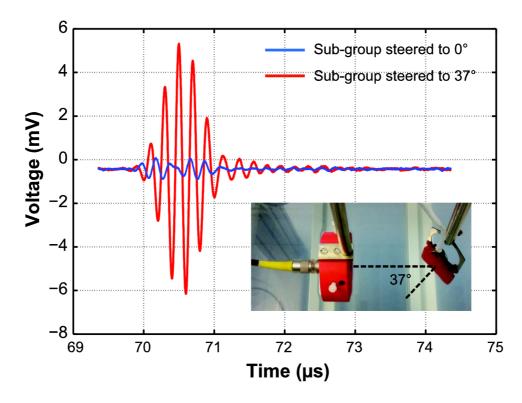

| 3.4.5 Micro-beamforming: Steering Response  | 63       |

| 3.4.6 Dynamic Range                         | 65       |

| 3.5 CONCLUSIONS                             | 67       |

| References                                  | 68       |

| FRONT-END ASIC WITH ANALOG SUBARRAY RX BEAM | MFORMING |

|                                             | 71       |

| 4.1 Introduction                            |          |

| 4.2 System Architecture                     |          |

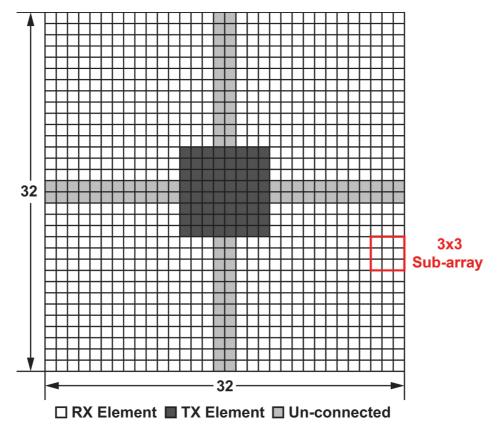

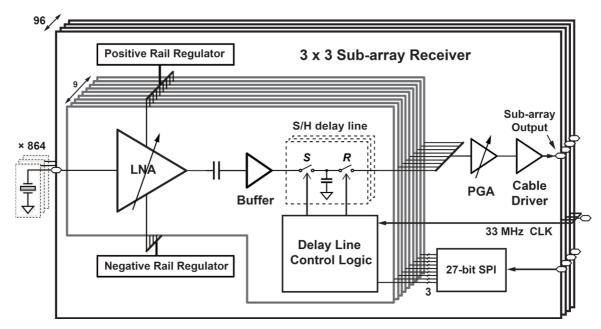

| 4.2.1 Transducer Matrix Configuration       |          |

| 4.2.1 Subarray Beamforming in Receive       |          |

| 4.3 CIRCUIT IMPLEMENTATION                  |          |

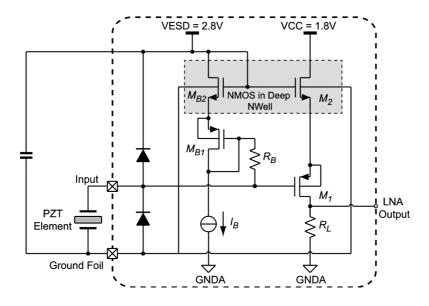

| 4.3.1 LNA                                   |          |

| 4.3.2 Subarray Beamformer                   |          |

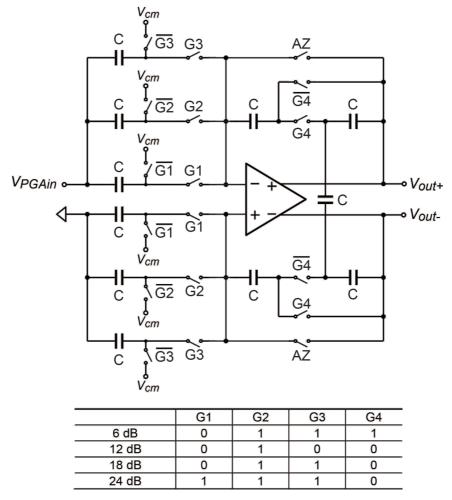

| 4.3.4 PGA                                   |          |

| 4.3.5 Cable Driver                          |          |

| 4.4 EXPERIMENTAL RESULTS                    |          |

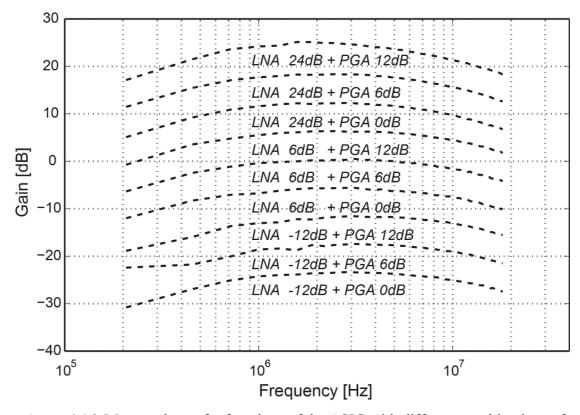

| 4.4.1 Electrical Characterization           |          |

| 4.4.2 Acoustic Experiments                  |          |

| 4.4.3 Imaging results                       |          |

| 4.5 CONCLUSIONS                             |          |

| References                                  |          |

| FRONT-END ASIC WITH INTEGRATED SUBARRAY     |          |

| BEAMFORMING ADC                             | 99       |

| 5.1 Introduction                            |          |

| 5.2 System Architecture                     |          |

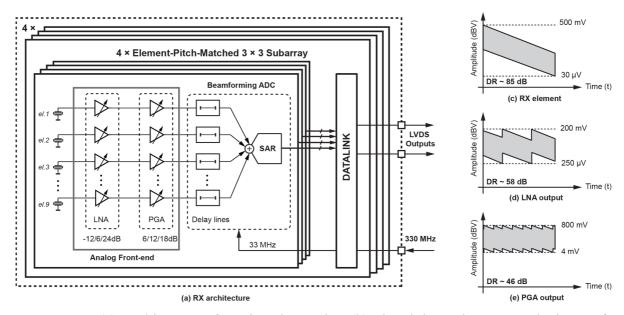

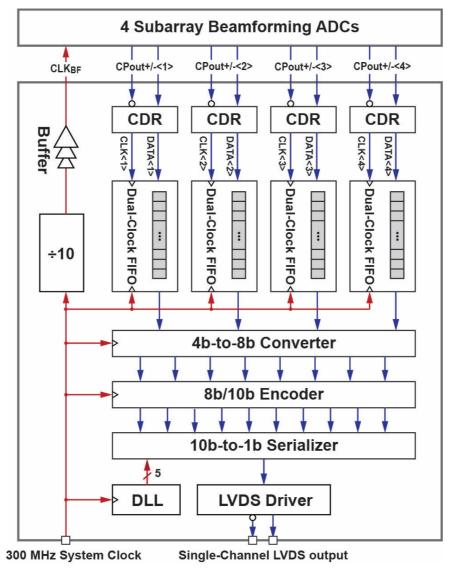

| 5.2.1 Overview                              | 102      |

| 5.2.2 AFE                                   | 103      |

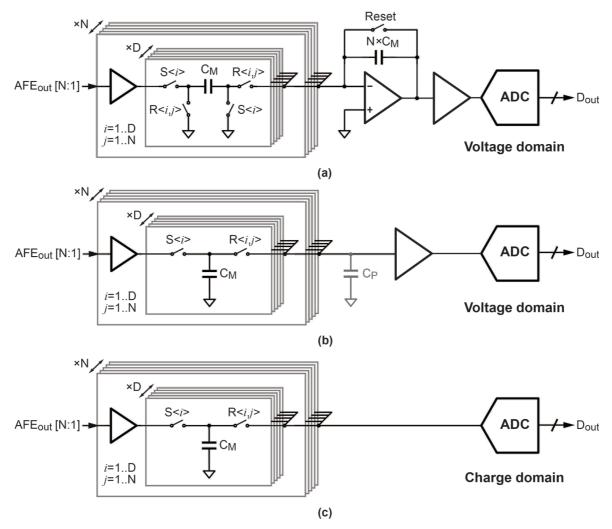

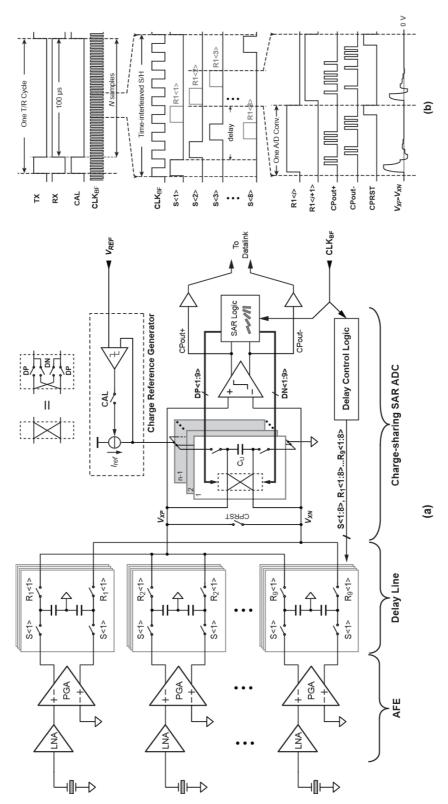

| 5.2.3 Beamforming ADC                       | 104      |

| 5.2.4 Datalink                              | 108      |

| 5.3 CIRCUIT IMPLEMENTATION                  | 109      |

| 5.3    | 3.1 AFE                         | 109 |

|--------|---------------------------------|-----|

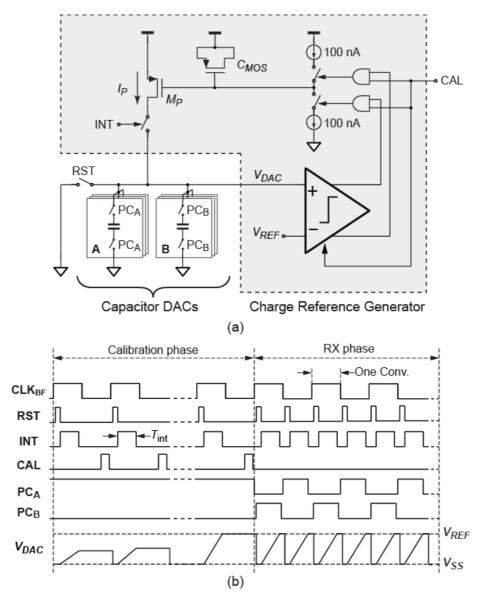

| 5.3    | 3.2 Charge-reference Generation | 111 |

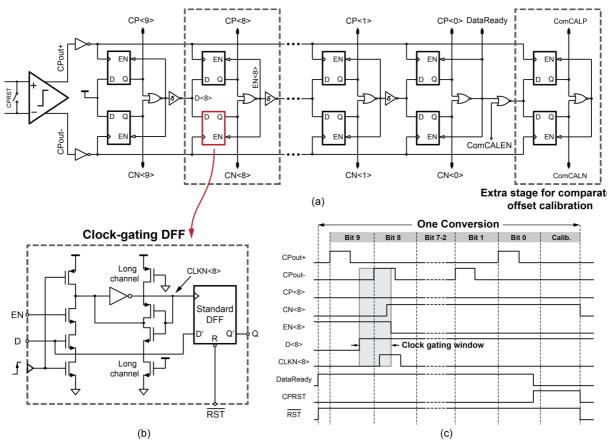

| 5.3    | 3.3 SAR Logic                   | 115 |

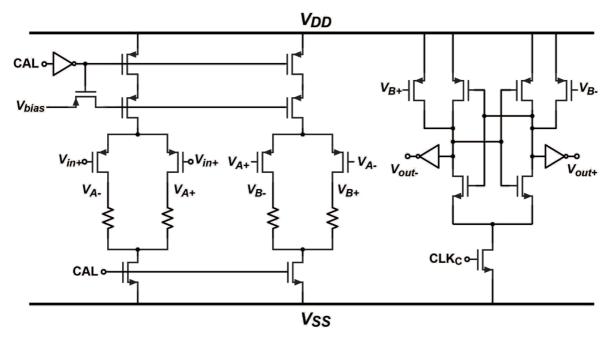

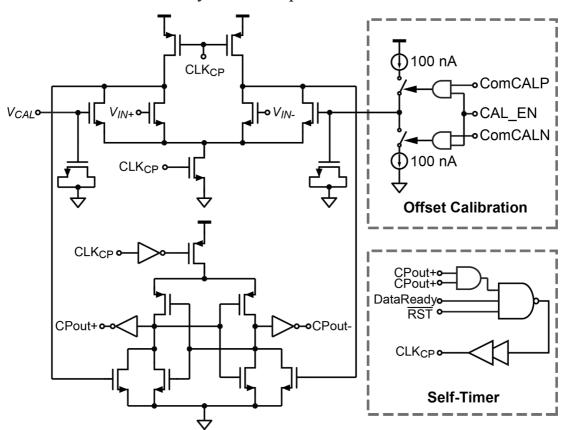

|        | 3.4 Dynamic Comparator          |     |

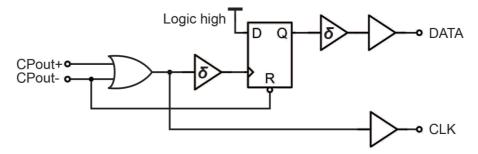

|        | 3.5 CDR and FIFO                |     |

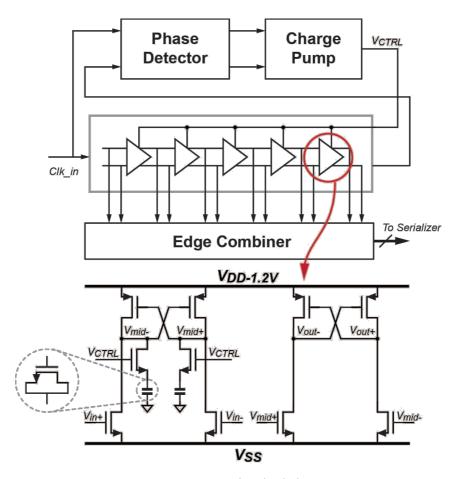

| 5.3    | 3.6 DLL                         | 120 |

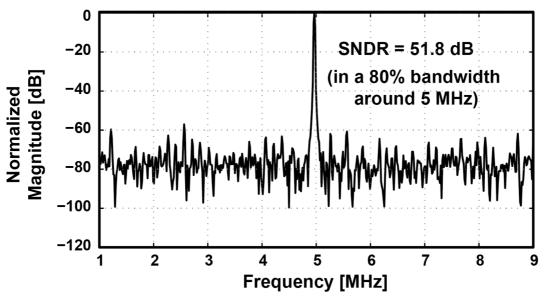

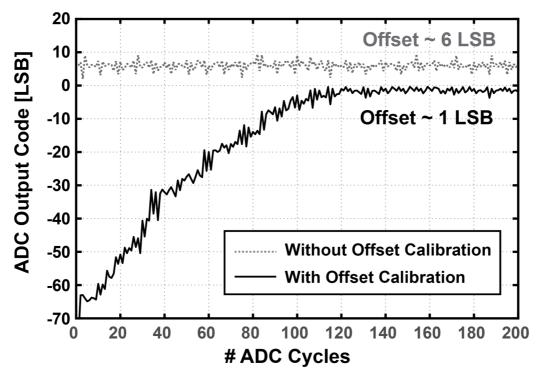

|        | EXPERIMENTAL RESULTS            |     |

|        | 4.1 Electrical Measurements     |     |

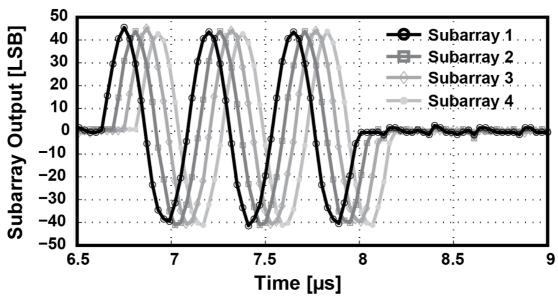

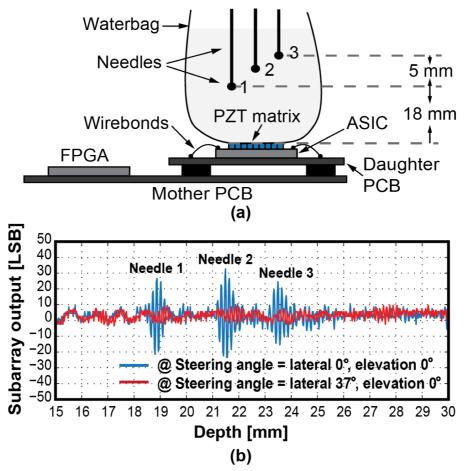

| 5.4    | 4.2 Acoustic Measurements       |     |

| 5.5    | Conclusions                     | 127 |

| Refe   | ERENCES                         | 128 |

| CONC   | CLUSIONS                        | 133 |

| 6.1    | MAIN CONTRIBUTIONS              | 133 |

| 6.2    | Main Findings                   |     |

| 6.3    | FUTURE WORK                     | 136 |

| Refe   | ERENCE                          | 138 |

| SUMN   | MARY                            | 141 |

| SAME   | ENVATTING                       | 145 |

| LIST ( | OF ABBREVIATIONS                | 151 |

| LIST ( | OF PUBLICATIONS                 | 155 |

| ACKN   | NOWLEDGEMENTS                   | 159 |

| ABOU   | UT THE AUTHOR                   | 167 |

### CHAPTER 1

### Introduction

### 1.1 Background and Motivations

The use of sound as a diagnostic tool for cardiology can be traced back to the age of ancient Greece. Medical professionals learned the patients' body conditions by listening into their chests, originally by ears and later with the help of stethoscopes. Although the word "stethoscopes" literally means "looking into the chest" [1], visualization of the human heart with the aid of sound only became possible after the invention of echocardiography in 1953, when Inge Edler and Carl Hertz made their first successful attempt in utilizing inaudible high-frequency sound waves, *i.e.* ultrasound, to create heart images [2]. After half century of evolution, echocardiography has been established as an indispensable imaging modality for cardiologists, while technology innovations, mainly driven by engineers, never stop in reforming this technique and expanding its application scope.

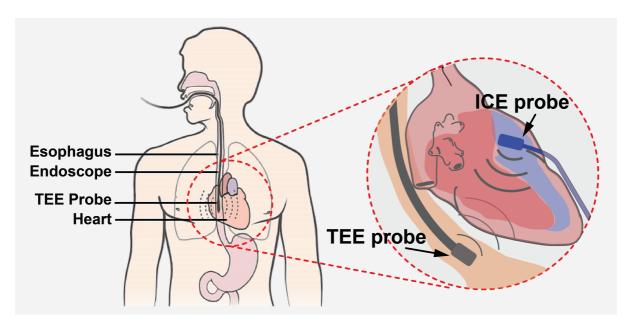

In the 1970s, the introduction of **transesophageal echocardiography (TEE)**, changed the medical practitioners' perspective from "looking into the chest" to "looking inside the chest". In contrast to the routine echocardiography examination methodology, i.e. transthoracic echocardiography (TTE), which has poor accessibility to the authentic information of cardiac structures due to the interference of ribs and lungs, the TEE approach employs an extremely tiny (miniature) ultrasound probe that can be swallowed by the patient and passed into their esophagus (Figure 1.1). Because the heart is directly adjacent to the esophagus wall, such probes are capable of operating with higher-frequency ultrasound, thus enabling heart visualization with superior spatial resolution [3]. Similar technologies have also been applied in other medical imaging regimes, such as transrectal and transvaginal imaging.

**Figure** 1.1. Conceptual illustration of transesophageal echocardiography (TEE) and intracardiac echocardiography (ICE)

The further miniaturization of ultrasound probes continued in expanding the vision of cardiologists. Even earlier than the invention of TEE, catheter-based ultrasound devices have been used in investigating the inner structure of the heart [4]. As shown in Figure 1.1, an ultrasound transducer is mounted at the tip of a catheter and passed into the right heart chambers to capture intracardiac images, thus enabling "looking inside the heart". Such devices, called as **intracardiac echocardiography** (ICE) probes, have been widely used in guiding interventional cardiovascular procedures. Similarly, the interest in detecting and visualizing the vulnerable plaques within the coronary arteries, has stimulated the development of another catheter-based device family, namely **intravascular ultrasound** (IVUS) probes.

The *trans*-<sup>1</sup> and *intra*- device families [5] are collectively referred to as miniature ultrasound probes in this thesis. They share the same physics as their counterparts for external uses (*e.g.* obstetrics ultrasound probes): transmitting an ultrasound wave with a desired frequency into the body, and receiving the resulting echoes, whose intensity and travel time are extracted for image reconstruction. This process is interpreted in Figure 1.2. A cross-sectional (2-D) image in the azimuth

<sup>&</sup>lt;sup>1</sup> Referred to endocavity probes only. For example, transthoracic echocardiography (TTE) and transcranial probes are not 'miniature'.

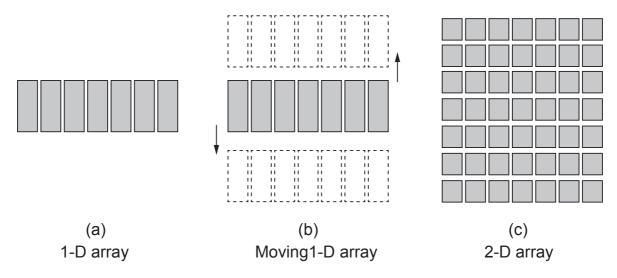

direction (*x-z*) can be obtained with a 1-D transducer array (Figure 1.2a). The capture of a volumetric (3-D) image, however, requires either a moving 1-D array (Figure 1.2b), or a static 2-D array (Figure 1.2c). The former approach combines multiples cross-sectional images (slices) to form a 3-D image by mechanically translating or rotating the 1-D array in the elevation direction [6]. However, the limited transducer motional speed imposes a restriction on the frame-acquisition rate (typically ~10 seconds per frame [5]), thus precluding the possibility of real-time visualization. Instead, a 2-D array, as shown in Figure 1.2c, has an extended capability of steering and/or dynamically focusing in the elevation direction. Therefore, one can use a 2-D array to perform a real-time pyramidal scanning without any mechanical translation, and produce a volumetric dataset, allowing simultaneous display of images at any desired planes<sup>2</sup>. It is referred to as real-time 3-D imaging [7], or 4-D imaging [8] as the time axis is also involved.

**Figure** 1.2. Illustration of different transducer arrays

It is clear that real-time 3-D imaging has significant clinical value for the above-mentioned cardiac imaging applications involving miniature ultrasound probes. For example, a range of key information for accurate diagnosis of cardiac diseases and quality control of interventional surgeries, such as aortic dissections and leakage of valves, are all dynamic 3-D phenomena that are difficult to interpret from 2-D or static 3-D images. For electrophysiology and valve-replacement surgeries, a continuous real-time visual feedback for surgeons is critical to ensure

\_

<sup>&</sup>lt;sup>2</sup> The 3-D image reconstruction and rendering in either software and hardware using the 3-D volume dataset still introduces some latency.

the success of the procedure, which is only possible with the involvement of real-time 3-D TEE or ICE probes.

However, there is still a dramatic gap between the urgent clinical demand and the current technological capabilities. To date, state-of-the-art commercial miniature probes involving fully-sampled 2-D transducer arrays are only available for TEE, such as Philips X7-2t [9] and GE 6VT-D [10]. A common limitation of these probes is their large head volume (in the order of 10 cm³), which is liable to increase the discomfort level of patients or even cause intolerance [11, 12]. In addition, imaging systems equipped with such probes (such as Philips iE33 and GE Vivid-E9) are only able to scan a full volume within several heartbeats, and hence not truly real-time.

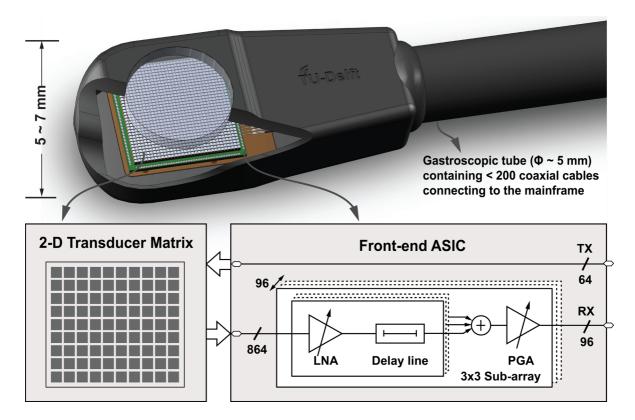

The ultimate objective of this thesis work is to explore the enabling technologies to bridge this technology gap, with the focus on the implementation of ultrasound receivers. Through the combination of existing in-probe ultrasound signal processing approaches and several technical innovations ranging from new integration methods to advanced integrated circuit techniques, a promising solution that paves the way towards the next-generation miniature 3-D ultrasound probes has been obtained. This has been demonstrated by the realization of several prototypes, which will be described and discussed in the following chapters.

### **1.2** Basic Principles

The main technical obstacle in the development of real-time 3-D miniature probes has been clearly aware of from their birth [13]. Table-1.1 summarizes the typical physical parameters of 3-D miniature probes, which clearly manifests the assembly challenge. In conventional 2-D probes, the individual wiring to linear or phased array elements is established by fine-gauge micro-coaxial cables with a typical outer diameter ranging from 0.18 – 0.3 mm. As the number of transducer elements increases with the adoption of a 2-D array, accommodating the required number of cables within gastroscopic tubes or catheters becomes unrealistic [7].

Early efforts made in addressing this problem [14, 15, 16] focused on undersampling the 2-D aperture with sparse arrays. Its basic idea is to select a small fraction of elements from a 2-D array with either periodical [16] or random

TABLE-1.1 Typical Physical Parameters of 3-D Miniature Ultrasound Probes

| Application                         | TEE      | ICE        | IVUS      |

|-------------------------------------|----------|------------|-----------|

| Transducer aperture dimension (2-D) | 5-10 mm  | 2-5 mm     | 1-2 mm    |

| Typical center frequency            | 3-5 MHz  | 5-10 MHz   | 10-20 MHz |

| # Elements                          | > 1000   | 100 - 1000 | < 100     |

| Gastroscopic tube/catheter diameter | ~ 5-7 mm | ~ 3 mm     | < 2 mm    |

| Imaging depth                       | > 10 cm  | 5-10 cm    | < 5 cm    |

[14, 15] distributions, thus reducing the required number of interconnects. However, this comes at the cost of a compromised imaging quality, as the reduced number of transmit or receive transducer elements in utility inevitably leads to a degradation of the signal-to-noise ratio as well as an elevated level of grating-lobes and side-lobes [5]. Such compromises have hampered the clinical acceptance of 3-D imaging with sparse 2-D array transducers.

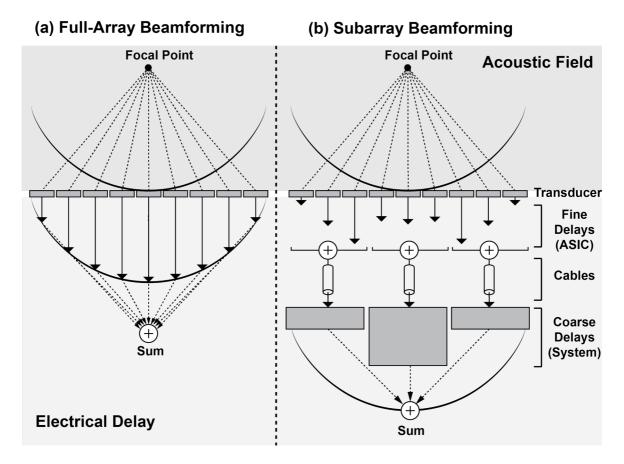

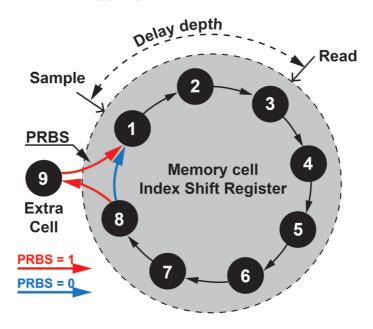

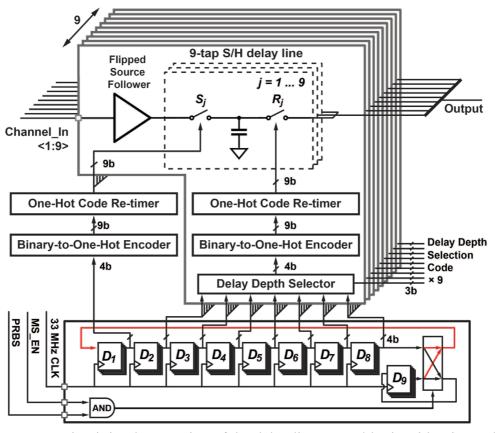

A practical implementation of fully-sampled 2-D arrays in miniature probes was only enabled after the proposal of subarray receive beamforming<sup>3</sup>[17], which allows to realize an order-of-magnitude cable-reduction with the aid of in-probe electronics. The basic principle of subarray beamforming is explained in Figure 1.3. In conventional 2-D imaging with 1-D phased-array transducers (Figure 1.3a), receive beamforming is applied in the back-end imaging system to form an acoustic receive beam focused at, or steered to, any desired point in the target imaging plane. This is achieved by applying appropriate electrical delays to the echo signals received by the individual transducer elements, and coherently add them up together to create a beam. Ideally, an N:1 cable reduction for an Nelement array could be readily achieved by migrating the delay-and-sum (DAS) electronics, a.k.a. the beamformer, into the probe. However, as the required maximum delay increases proportionally with the feature size of the aperture (N for both an N-element 1-D array and an  $N^2$ -element 2-D array), implementing a single-stage beamformer for a 2-D array with 100+ or even 1000+ elements (Table-1.1) would lead to prohibitively long electrical delay lines and hence unacceptable in-probe hardware cost. The concept of subarray beamforming, as shown in Figure 1.3b, was proposed to address this problem. It splits the delay

\_

<sup>&</sup>lt;sup>3</sup> Also referred to as "micro-beamforming", "presteering", "subaperture processing" or "subaperture processing" by different authors.

Figure 1.3. Basic principle of subarray beamforming

for individual elements into two stages: a fine delay with a small step-size but a shorter length, and a coarse delay with a large step-size while covering the full delay range. As such, the required numbers of delay taps in both stages can be both minimized, which significantly simplifies the electronics design. The fine-delay stage can be implemented in the probe with a much more affordable power and area budget, and the coarse-delay stage can be realized in the back-end system that interfaces to the probe with a dramatically reduced number of signal-acquisition channels (typically an order of magnitude lower than  $N^2$  [8, 17, 18]).

The technical foundation of subarray beamforming is the realization of high-density integrated electronics in proximity to the 2-D transducer. In commercial bed-side ultrasound imaging systems [9], the beamforming electronics are built using off-the-shelf multi-channel integrated chips [19] or chipsets [20]. For miniature 3-D probes, however, the extremely limited volume of the probe tip precludes such options. As an alternative, the use of custom-designed front-end application-specific integrated circuits (ASICs) allows a close integration with a

2-D ultrasound transducer as well as performance optimization of the interfacing circuits. As such, it has now become a compelling and indispensable solution for implementing in-probe electronics.

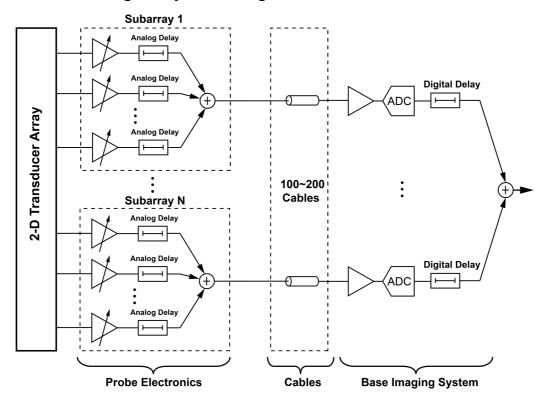

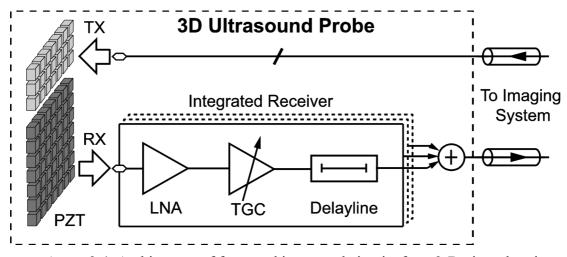

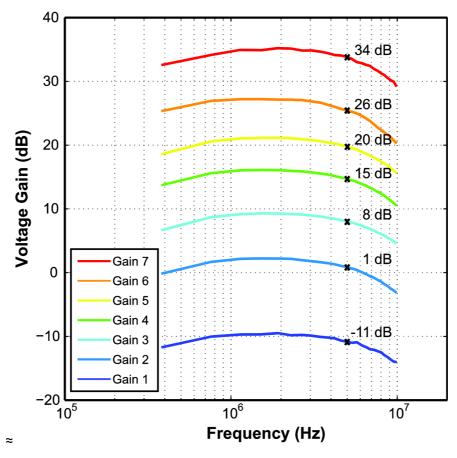

Figure 1.4 illustrates a simplified block diagram of a typical front-end ASIC based on the subarray beamforming framework. Each subarray of the ASIC consists of high-voltage transmitters, which drive the transducer to generate acoustic waves, and low-voltage receivers, which perform both signal conditioning and beamforming on the received echoes. Typically, the signal conditioning circuit incorporates a wide-range (> 40 dB) of programmable gain levels to compensate the propagation attenuation of ultrasound waves, which is crucial for enhancing the dynamic range.

**Figure.** 1.4 Simplified schematic of ultrasound front-end electronics based on the subarray beamforming framework

### 1.3 Challenges

The small form factor of miniature 3-D ultrasound devices, in both the physical size and the heat dissipation budget, defines several stringent physical boundaries for the design of front-end ASICs. The engineering and commercial success of a miniature 3-D ultrasound device depends, to a significant degree, on how well its built-in front-end ASIC adapts to these physical constraints.

The first challenge comes from the dense electrical channel interconnections between the ASIC and the 2-D array transducer. In contrast to conventional approaches based on interposer layers [21], direct transducer-on-chip integration is desired, as it not only helps in down-sizing the probe-tip, but also minimizes the parasitic capacitance added to each transducer element. This calls for an element-matched ASIC layout, with a pitch identical to that of the transducer element. Ideally, the pitch of a 2-D transducer array should not be greater than half of the ultrasound wavelength ( $\lambda/2$ ) at the center frequency. Such requirement ensures a sufficient spatial sampling frequency to avoid elevation of grating lobes in the obtained image [5]. This leads to an element pitch of 200  $\mu$ m or less for typical medical imaging applications, calling for a highly-compact circuit implementation underneath the transducer element.

Another significant concern is the electrical power consumption. As the front-end ASIC, along with the transducer, dissipates heat in the probe-tip, a tight control of its operating power consumption and the associated temperature rise is extremely crucial for avoiding tissue over-heating. The FDA regulations [22] have specified the maximum allowed surface temperature for TEE probes, which sets an upper bound on both the largest transmit power and the self-heating power associated with in-probe electronics. In general, the maximally allowed heat dissipation of a standard 2-D endoscopic probe (TEE) is estimated as 1.0 W [50], and this number does not scale with the number of transducer elements. Therefore, front-end ASICs in miniature 3-D probes have to operate with an even more strict per-element power budget owing to the increased element numbers. For instance, for a 1000-element array for 3-D TEE probes, the averaged power dissipation of circuits interfacing with each element should be limited to about 1 mW, demanding a superior power efficiency in the circuit implementation.

Subarray beamforming makes it possible to reduce the channel count by approximately an order of magnitude, while the pursuit for further channel reduction never ends. The power and area limitations have so far restricted the mainstream development of in-probe on-chip signal processing in the analog domain. While analog subarray beamforming circuits have shown their advantages in achieving better power-efficiency [17], further processing and transmission of the output signals in the analog format could be problematic

owing to their poor immunity to circuit non-idealities and environmental interference. Such problem is exaggerated when more aggressive channel reduction is required to be accomplished within the probe. While a few efforts have been made to improve the efficiency of analog-domain multiplexing, a thorough solution to this problem is to digitize the received signals in the probe and perform the channel-sharing in the robust digital domain. However, this strategy has long been considered impractical [23], as migrating standard analog-to-digital (A/D) conversion topologies for typical sensory systems to ultrasound ASICs would lead to unacceptable power and area overhead. As such, dedicated A/D conversion solutions for ultrasound are called for, which are supposed to save power and area by embracing those unique features of ultrasound transducer and systems, *e.g.* merging the A/D converter with the beamformer and signal conditioning circuits, or taking advantage of the resonance nature of the transducer element.

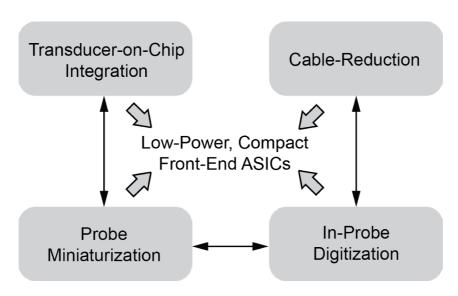

Figure 1.5 summaries the above-mentioned challenges and their interrelations. To address these challenges, both system-level innovations and circuit-level optimizations are required in the development of ultrasound front-end integrated circuits. This is an emerging field requires a solid understanding in both ultrasound transducer physics and solid-state circuit design, which motivates this thesis work.

Figure 1.5 Main challenges in this thesis work

#### 1.4 Context of the Research

The design and fabrication of 2-D transducer arrays for volumetric imaging started in the late 1980s [24]. A lot of pioneering work was done by Smith et al. [7, 13] at Duke University. The lack of feasible dense interconnection solutions forced scientists to adopt sparse arrays at the cost of the imaging quality, which diminished the clinical value of 2-D array transducers. In fact, it did not take long for designers to realize the necessity of implementing in-probe signal processing functions. In 1989 Larson et al. proposed a system-level methodology called distributed phasing [25], which is very similar to the concept of subarray beamforming proposed by Philips [17]. However, only with the advances of modern IC technology in the last two decades were these ideas turned into reality given the strict power and performance constraints of building 2-D arrays in miniature probes.

Prior to the introduction of 2-D arrays, custom-designed integrated chips have been developed to enable electronic steering of linear arrays in devices with extreme size constraints. Black et.al [51] reported the first in-probe ASIC chipset in 1994 for use in an intravascular microprobe. Fabricated in a 3-µm CMOS process, this 4-die chipset was designed to interface with 64 PVDF transducer elements in a linear array. The limited count of elements however, relaxed the power and area constraints and allowed the adoption of standard wire bond techniques to simplify the chip assembly.

The continuously downscaling of CMOS technology provided the possibility for more aggressive integration. Beginning from the early 2000s, a number of research groups made substantial efforts in implementing integrated circuits directly underneath the 2-D transducer array, thus addressing the dense interconnection issue. Interestingly, these progresses came along with the development of another silicon-based technology, namely capacitive micromachined ultrasound transducers (CMUTs) [26, 27]. In 2002, Noble et al. presented the first 2-D CMUT array co-integrated with analog receive amplifiers built in 0.8-µm CMOS [28]. The transmit functionality was later enabled by Daft et al. by monolithically integrating the CMUT with high-voltage switches [29]. Wygant et al. designed and demonstrated a 16×16 CMUT array that was flip-chip bonded to a 0.25-µm CMOS IC incorporating both high-voltage pulsers and

preamplifers [30, 31]. The focus of the research at the time was the integration approach and the performance characterization of the transducer-to-CMOS interface, while the circuit topology and functionality were both kept relatively simple.

The past decade has seen the realization of more advanced signal processing functions in ultrasound front-end ICs. Transmit beamformers were introduced by Wygant et al. to produce steered and focused ultrasound beams from a 2-D CMUT array [32]. Based on this work, Bhuyan et al. reported the successful implementation of large aperture 2-D arrays with 32×32 elements by using different transducer-on-chip assembly approaches [21, 33]. Later on, a colomn-row-parallel ASIC architecture was proposed and demonstrated by Chen et al. to enable flexible 3-D beam-formation [34].

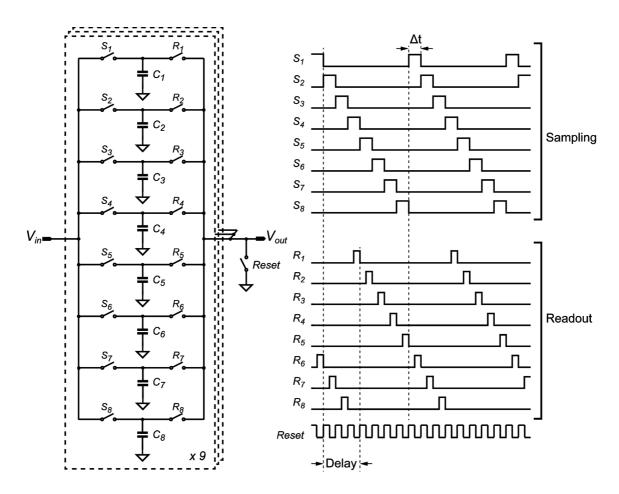

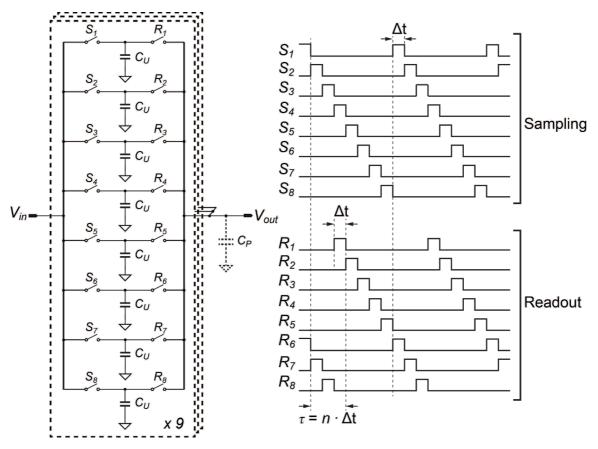

Concurrent with the above advances in transducer-on-chip developments, researchers were also investigating the potential optimization of circuit implementations. Receive beamforming is a challenging ultrasound signal processing function for on-chip realization due to the necessity of maintaining the dynamic range of received information. A variety of analog circuit topologies have been proposed in recent years in pursuit of a compact and power-efficient receive beamformer, such as all-pass filters [35, 36], switched-current [37] [38] and time-interleaved switched-capacitor circuits [18, 39]. The latter approach outperforms in power-efficiency for modest delay resolutions, as the majority of power is dissipated in the digital domain. On the other hand, establishing the beamforming function completely digitally is expected to yield an even higher efficiency, as the generation and control of digital delays could be much more accurate and flexible. However, such approach requires an analog-to-digital converter (ADC) for each transducer element, resulting in significant overhead in both power and area as well as the design challenge. Chen et al. [40] attempted to address these issues by leveraging element-level  $\Delta\Sigma$  modulators in nanoscale CMOS process, while the results were not yet promising. As an alternative, Um et al. [41] proposed an analog-digital-hybrid beamformer architecture to reduce the required number of ADCs, which is also compatible with the subarray beamforming framework.

Besides these system-level explorations, innovative circuit-level solutions for ultrasound IC building blocks keep emerging in recent years. These contributions

cover the design of front-end amplifiers [42] [43], time-gain compensations [44, 45, 46], high-voltage pulsers [42, 47] and ADCs [48, 49].

### 1.5 Thesis Organization

The organization of this thesis is arranged as follows.

In order to optimize the power efficiency of the front-end ASIC, an efficient way to readout the electrical signal produced by the ultrasound transducer is needed. This is developed in **Chapter 2**, where a design-oriented analysis on the optimal architecture choice of front-end amplifiers based on transducer characteristic is established. Two design cases targeting at different types of ultrasound transducers (PZT and PVDF) are reviewed and compared to evaluate the effectiveness of the proposed design methodology.

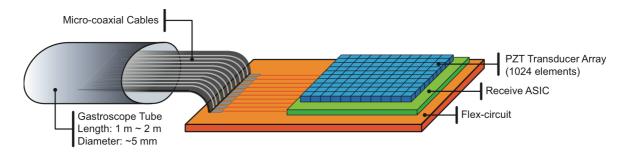

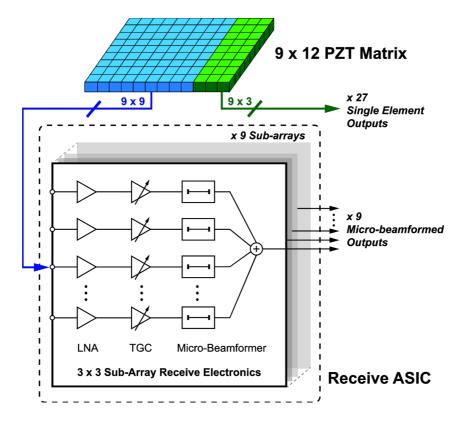

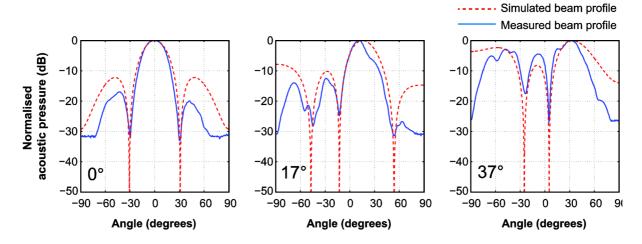

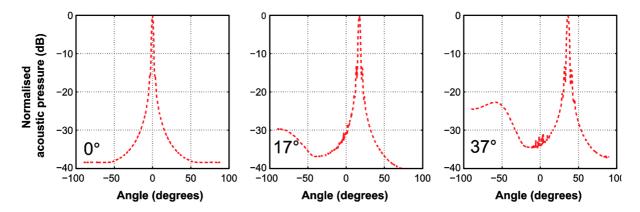

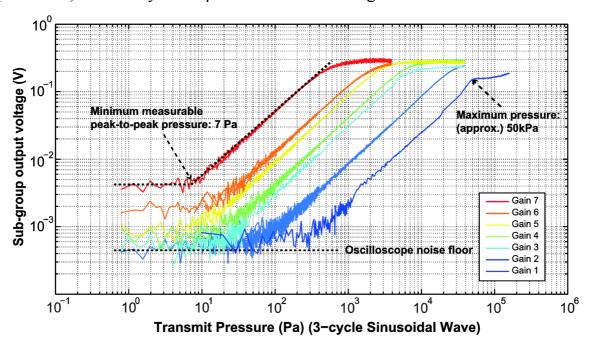

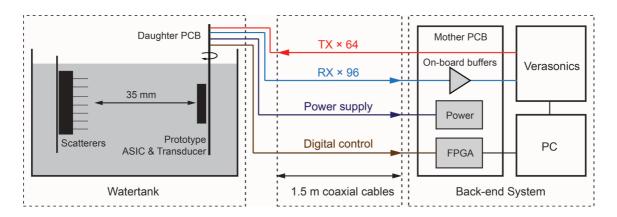

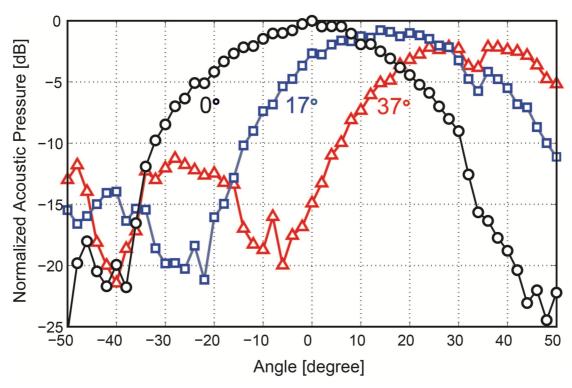

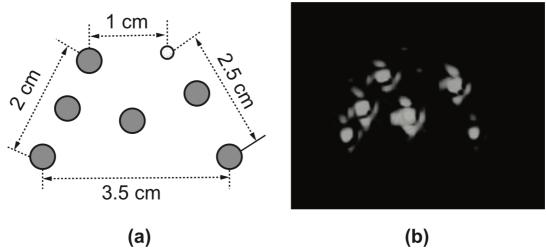

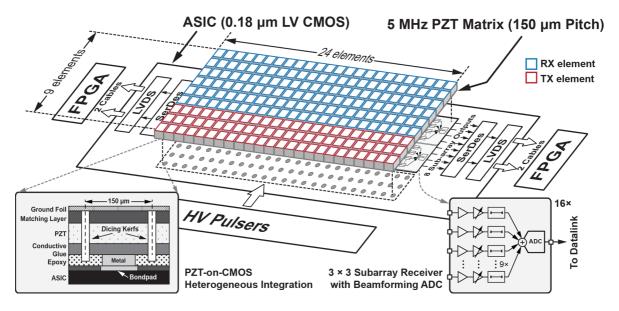

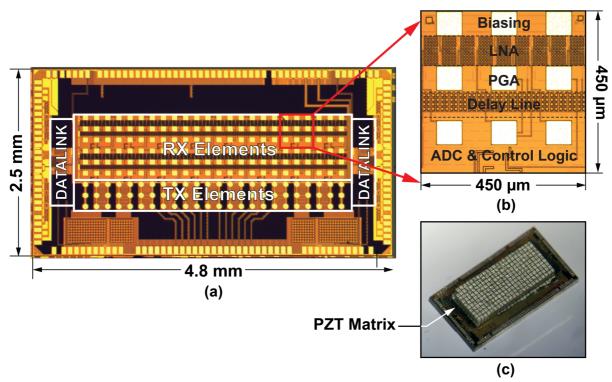

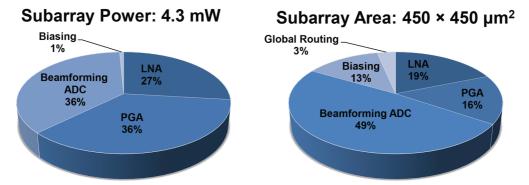

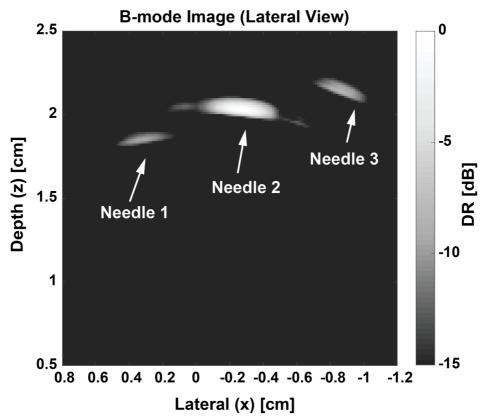

As addressed in Section 1.3, a reliable approach to realize a tight integration of the 2-D transducer array and the silicon chip is key for enabling miniature 3-D ultrasound probes. A PZT-on-CMOS integration scheme is proposed in **Chapter** 3 and demonstrated by a prototype assembly involving a  $9 \times 12$  PZT matrix and an element-matched receive ASIC. This prototype served as the test vehicle not only for the integration scheme, but also for the subarray beamforming circuits integrated in the ASIC. The acoustical beamforming functionality was extensively evaluated by water-tank experiments, showing the effectiveness of this technique.

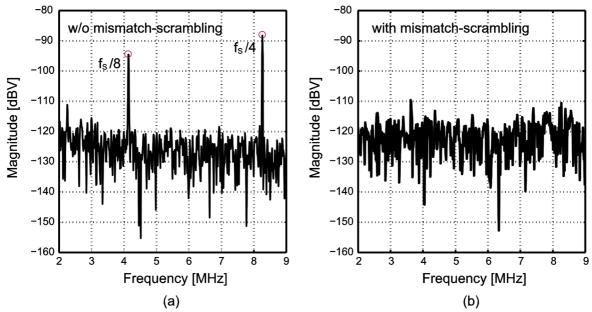

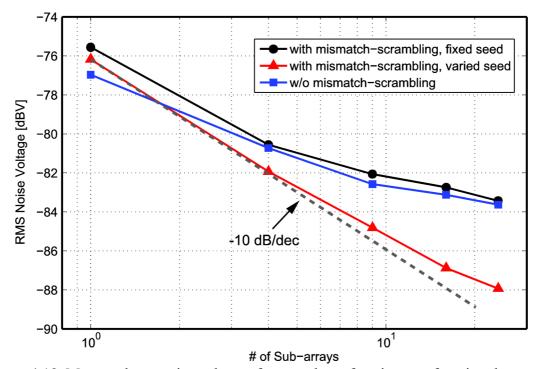

Based on this prototype, a full-blown  $32 \times 32$  front-end ASIC with integrated transducer was developed and described in **Chapter 4**. This ASIC incorporates both transmit and receive capabilities, thus enabling the demonstration of 3-D imaging experiments. With improved designs of all circuit building blocks, this ASIC achieves a record-low receive power-efficiency of 0.27 mW/element. To mitigate the non-idealities of analog subarray beamformers caused by device mismatches, a mismatch-scrambling technique is proposed and demonstrated in this ASIC, which helps in enhancing the dynamic range.

Following the success of the  $32 \times 32$  array ASIC, which operates in the analog domain, we made our attempts in pushing the technology frontier towards a digital miniature 3-D probe.

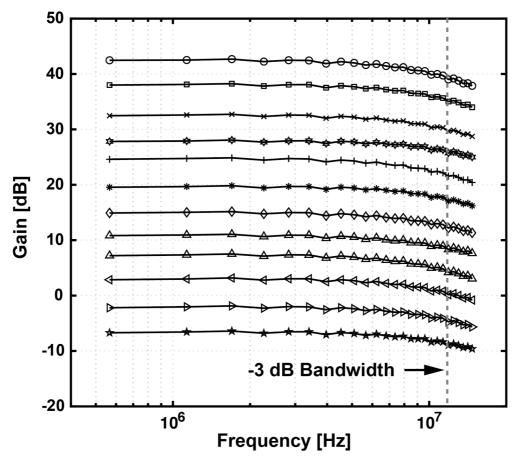

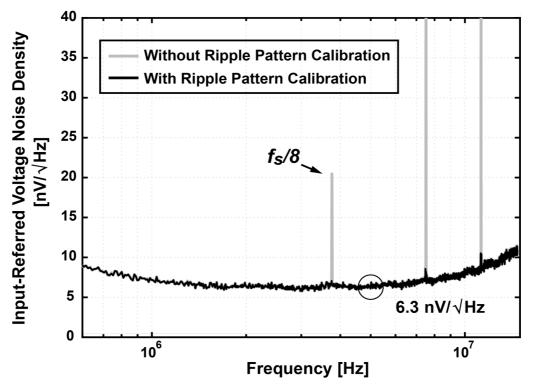

In **Chapter 5**, a beamforming ADC architecture for achieving feasible in-probe digitization is proposed and demonstrated with a  $9 \times 24$  prototype array. High-speed datalinks are employed in combination with subarray beamforming to realize a 36-fold channel-count reduction. This prototype achieves a per-element power consumption of 0.91 mW, which is  $10 \times 100$  lower than prior work incorporating front-end digitization functions.

**Chapter 6** concludes this thesis with discussions and a summary. A vision for the future improvements in both further channel reduction and more aggressive system-on-chip integration is given in a special section.

#### References

- [1] L. Husten. (Jan 2016) The Stethoscope: To Bury, or Praise? -Debate over continued use in face of portable ultrasound rages on. *Cardiology*. Available: <a href="https://www.medpagetoday.com/cardiology/arrhythmias/55688">https://www.medpagetoday.com/cardiology/arrhythmias/55688</a>

- [2] I. Edler and K. Lindstrom, "The history of echocardiography," *Ultrasound in Medicine & Biology*, vol. 30, no. 2, pp. 1565-1644, Dec. 2004.

- [3] E. Agricola, "Transesophageal echocardiography: a complementary view of the heart," *Expert Review of Cardiovascular Therapy 2(1)* pp. 61-75, 2004.

- [4] T. Cieszynski, "Intracardiac method for the investigation of structure of the heart with the aid of ultrasonics," *Arch Immunol Ther Exp (Warsz)*, vol. 8, pp. 551-553, 1960.

- [5] T. Szabo, *Diagnostic Ultrasound Imaging: Inside Out*, 1st Edition ed. Elsevier Academic Press, 2004.

- [6] S. W. Smith, W. Lee, E. D. Light, J. T. Yen, P. Wolf, and S. Idriss, "Two dimensional arrays for 3-D ultrasound imaging," in *IEEE International Ultrasonics Symposium*, 2002, pp. 1545-1553.

- [7] E. D. Light, R. E. Davidsen, J. O. Fiering, T. A. Hruschka, and S. W. Smith, "Progress in Two Dimensional Arrays for Real Time Volumetric Imaging," *Ultrasonic Imaging*, vol. 20, no. 1, pp. 1-15, Feb. 1998.

- [8] D. Wildes *et al.*, "4-D ICE: A 2-D Array Transducer With Integrated ASIC in a 10-Fr Catheter for Real-Time 3-D Intracardiac Echocardiography," *IEEE Trans. Ultrason. Ferro. and Freq. Control*, vol. 63, no. 12, pp. 2159-2173, 2016.

- [9] Philips Healthcare, "An Imaging Revelation: Philips iE33 xMATRIX Echocardiography System Overview," ed, 2010.

- [10] GE Healthcare, "VIVID E9 4D Cardiovascular Ultrasound System,"

- [11] W. G. Daniel *et al.*, "Safety of Transesophageal Echocardiography. A multicenter survey of 10,419 examinations," *Circulation*, vol. 83, no. 3, pp. 817-821, Mar. 1991.

- [12] G. Côté and A. Denault, "Transesophageal echocardiography-related complications," *Can J Anaesth*, vol. 55, no. 9, pp. 622-647, 2008.

- [13] S. W. Smith, R. E. Davidson, C. D. Emery, R. L. Goldberg, E. D. Light, and D. M. Mills, "2-D array transducers for medical ultrasound at Duke University: 1996," in *IEEE International Symposium on Applications of Ferroelectrics (ISAF)*, 1996, pp. 5-11.

[14] P. K. Weber, R. M. Schmitt, B. D. Tylkowski, and J. Steck, "Optimization of random sparse 2-D transducer arrays for 3-D electronic beam steering and focusing," in *IEEE International Ultrasonics Symposium*, 1994, pp. 1503-1506.

- [15] R. Davidsen and S. Smith, "Two-dimensional arrays for medical ultrasound using multilayer flexible circuit interconnection," *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 45, no. 2, pp. 338-348, Mar. 1998.

- [16] S. S. Brunke and G. R. Lockwood, "Broad-bandwidth radiation patterns of sparse twodimensional vernier arrays," *IEEE Trans. Ultrason. Ferro. and Freq. Control*, vol. 44, no. 5, pp. 1101-1109, Sept. 1997.

- [17] B. Savord and R. Solomon, "Fully Sampled Matrix Transducer for Real Time 3D Ultrasonic Imaging," in *Proc. IEEE Ultrasonics Symp.*, 2003, pp. 945-953.

- [18] Y. Katsube *et al.*, "Single-Chip 3072ch 2D Array IC with RX Analog and All-Digital TX Beamformer for 3D Ultrasound Imaging," in *Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, 2017, pp. 458-459.

- [19] Analog Devices, "Octal LNA/VGA/AAF/ADC and Crosspoint Switch," *AD9271 datasheet*, 2009.

- [20] M. I. Fuller, K. Ranganathan, S. Zhou, T. N. Blalock, J. Hossack, and W. F. Walker, "Experimental system prototype of a portable lowcost, c-scan ultrasound imaging device," *IEEE Trans. Biomed. Eng.*, vol. 55, no. 2, pp. 519-530, Feb. 2008.

- [21] A. Bhuyan *et al.*, "3D Volumetric Ultrasound Imaging with a 32'32 CMUT Array Integrated with Front-End ICs Using Flip-Chip Bonding Technology," in *Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, 2013, pp. 396-397.

- [22] U. S. Food and Drug Administration (FDA), "Guidance for Industry and FDA Staff—Information for Manufacturers Seeking Marketing Clearance of Diagnostic Ultrasound Systems and Transducers," Sept. 2008.

- [23] T. M. Carpenter, M. W. Rashid, M. Ghovanloo, D. M. J. Cowell, S. Freear, and L. D. F, "Direct Digital Demultiplexing of Analog TDM Signals for Cable Reduction in Ultrasound Imaging Catheters," *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 63, no. 8, pp. 1078 1085, 2016.

- [24] S. W. Smith, H. G. Pavy, and O. T. v. Ramm, "High-speed ultrasound volumetric imaging system. I. Transducer design and beam steering," *IEEE Trans. Ultrason. Ferro. and Freq. Control*, vol. 38, no. 2, pp. 100-108, Mar. 1991.

- [25] J. D. Larson-III, "2-D phased array ultrasound imaging system with distributed phasing," Patent EP0430450 A3, Nov. 1990.

- [26] O. Oralkan *et al.*, "Capacitive micromachined ultrasonic transducers: next-generation arrays for acoustic imaging?," *IEEE Trans. Ultrason. Ferro. and Freq. Control*, vol. 49, no. 11, pp. 1596-1610, Dec. 2002.

- [27] O. Oralkan *et al.*, "Volumetric ultrasound imaging using 2-D CMUT arrays," *IEEE Trans. Ultrason. Ferro. and Freq. Control*, vol. 50, no. 11, pp. 1581-1594, Dec. 2003.

- [28] R. A. Noble *et al.*, "Low-Temperature Micromachined CMUTs with Fully-Integrated Analogue Front-End Electronics," in *IEEE International Ultrasonics Symposium*, 2002, vol. 2, pp. 1045-1050.

- [29] C. Daft, S. Calmes, D. d. Graca, K. Patel, P. Wagner, and I. Ladabaum, "Microfabricated ultrasonic transducers monolithically integrated with high voltage electronics," in *IEEE International Ultrasonics Symposium*, 2004, pp. 493-496.

- [30] I. O. Wygant *et al.*, "Integrated ultrasonic imaging systems based on CMUT arrays: recent progress," in *IEEE International Ultrasonics Symposium*, 2004, pp. 391-394.

[31] I. O. Wygant *et al.*, "Integration of 2D CMUT arrays with front-end electronics for volumetric ultrasound imaging," *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 55, no. 2, pp. 327-342, Feb. 2008.

- [32] I. O. Wygant *et al.*, "An integrated circuit with transmit beamforming flip-chip bonded to a 2-D CMUT array for 3-D ultrasound imaging," *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 56, no. 10, pp. 2145-2156, Oct. 2009.

- [33] A. Bhuyan *et al.*, "Integrated Circuits for Volumetric Ultrasound Imaging With 2-D CMUT Arrays," *IEEE Trans. Biomed. Circuits Syst.*, vol. 7, no. 6, pp. 796-804, Dec. 2013.

- [34] K. Chen, H.-S. Lee, and C. G. Sodini, "A Column-Row-Parallel ASIC Architecture for 3-D Portable Medical Ultrasonic Imaging," *IEEE J. Solid-State Circuits*, vol. 51, no. 3, pp. 738-751, 2016.

- [35] J. R. Talman, S. L. Garverick, and G. R. Lockwood, "Integrated Circuit for High-Frequency Ultrasound Annular Array," in *IEEE Custom Integrated Circuits Conference (CICC)*, 2003, pp. 447-480.

- [36] G. Gurun, J. S. Zahorian, A. Sisman, M. Karaman, P. E. Halser, and F. L. Degertekin, "An Analog Integrated Circuit Beamformer for High-Frequency Medical Ultrasound Imaging," *IEEE Trans. Biomed. Circuits Syst.*, vol. 6, no. 5, pp. 454-467, Oct. 2012.

- [37] B. Stefanelli, "An analog beam-forming circuit for ultrasound imaging using switched-current delay lines," *IEEE J. Solid-State Circuits*, vol. 35, no. 2, pp. 202-211, Feb. 2000.

- [38] S. Sharma and T. Ytterdal, "In-Probe Ultrasound Beamformer Utilizing Switched-Current Analog RAM," *IEEE Trans. Circuits Syst. II: Express Briefs*, vol. 62, no. 6, pp. 517-521, Jun. 2015.

- [39] Z. Yu, M. A. P. Pertijs, and G. C. M. Meijer, "An ultrasound beamformer using pipeline-operated S/H delay stages and charge-mode summation," *Electron.Lett.*, vol. 47, no. 18, pp. 1011-1012, Sept. 2011.

- [40] M.-C. Chen *et al.*, "A Pixel-Pitch-Matched Ultrasound Receiver for 3D Photoacoustic Imaging with Integrated Delta-Sigma Beamformer in 28nm UTBB FDSOI," in *Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, 2017, pp. 456-457.

- [41] J.-Y. Um *et al.*, "An analog-digital-hybrid single-chip RX beamformer with non-uniform sampling for 2D-CMUT ultrasound imaging to achieve wide dynamic range of delay and small chip area," in *Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap.*, Feb. 2014, pp. 426 427.

- [42] K. Chen, H.-S. Lee, A. P. Chandrakasan, and C. G. Sodini, "Ultrasonic Imaging Transceiver Design for CMUT: A Three-Level 30-Vpp Pulse-Shaping Pulser With Improved Efficiency and a Noise-Optimized Receiver," *IEEE J. Solid-State Circuits*, vol. 48, no. 11, pp. 2734 2745, Oct. 2013.

- [43] M. Sautto *et al.*, "A CMUT transceiver front-end with 100-V TX driver and 1-mW low-noise capacitive feedback RX amplifier in BCD-SOI technology," in *Proc. ESSCIRC*, 2014, pp. 407-410.

- [44] J. Yao *et al.*, "Design of a low power time-gain-compensation amplifier for a 2D piezoelectric ultrasound transducer," in *Proc. IEEE Ultrasonics Symp.*, 2010, pp. 841-844.

- [45] T. Halvorsrod, O. Birkenes, and C. Eichrodt, "A Low-Power Method Adding Continuous Variable Gain to Amplifiers," in *IEEE International Symposium on Circuits and Systems (ISCAS)*, 2005, pp. 1593-1596.

- [46] T. Christen, "A 15-bit 140-μW Scalable-Bandwidth Inverter-Based \Delta \Sigma Modulator for a MEMS Microphone With Digital Output," *IEEE J. Solid-State Circuits*, vol. 48, no. 7, pp. 1605 1614, July 2013.

[47] P. L. Muntal, D. Ø. Larsen, I. H. H. Jørgensen, and E. Bruun, "Integrated reconfigurable high-voltage transmitting circuit for CMUTs," *Analog Integrated Circuits and Signal Processing*, vol. 84, no. 3, pp. 343-352, Jul. 2015.

- [48] Y. Zhang, C.-H. Chen, T. He, and G. C. Temes, "A continuous-time delta-sigma modulator for biomedical ultrasound beamformer using digital ELD compensation and FIR feedback," *IEEE Trans. Circuits Syst. I: Regular Papers*, vol. 62, no. 7, pp. 1689-1698, Jul. 2015.

- [49] K. Kaviani, O. Oralkan, P. Khuri-Yakub, and B. Wooley, "A multichannel pipeline analog-to-digital converter for an integrated 3-D ultrasound imaging system," *IEEE J. Solid-State Circuits*, vol. 38, no. 7, pp. 1266-1270, Jul. 2003.

- [50] C. Chen, *et al.*, "A Prototype PZT Matrix Transducer with Low-Power Integrated Receive ASIC for 3D Transesophageal Echocardiography", *IEEE Trans. Ultrason.*, *Ferroelectr.*, *Freq. Control*, vol. 63, no. 1, pp. 47-59, Jan 2016.

- [51] W.C. Black and D.N. Stephens, "CMOS chip for invasive ultrasound imaging", *IEEE J. Solid-State Circuits*, vol. 29, no. 11, pp. 1381-1387, Nov. 1994.

### CHAPTER 2

### LOW-NOISE AMPLIFIERS FOR ULTRASOUND

#### 2.1 Architecture Choices

In most ultrasound receiver systems<sup>4</sup>, a low-noise amplifier (LNA) is the building block that directly interfaces with the transducer element (possibly through a transmit/receive switch or limiter). By linearly amplifying the echo signals at the very beginning of the receive chain, the LNA reduces the noise contribution from succeeding circuits, and is thus critical in optimizing the noise-power trade-off of the entire receiver system. Depending on the transducer characteristic and the requirement on the output signal type, such amplification can be embodied as a voltage gain [1], a current gain [2], a trans-impedance gain [3], or a transconductance gain [4]. Therefore, a transducer-oriented design strategy for ultrasound LNAs is called for.

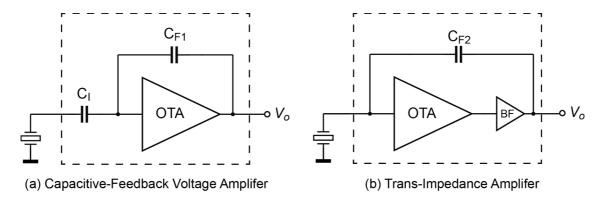

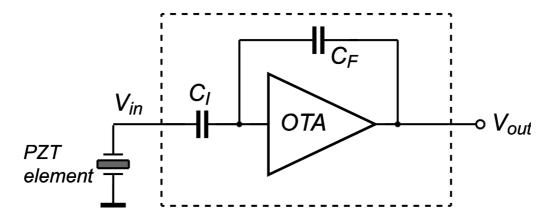

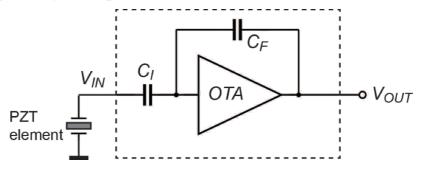

Capacitive-feedback voltage amplifiers (CFA) [5] and trans-impedance amplifiers (TIA) [3, 6, 7] are most commonly-used ultrasound LNA architectures. This section aims at establishing a general comparison of their noise-efficiency<sup>5</sup>, which is expected to provide a guideline in the architecture choice of ultrasound LNAs.

$$NEF = V_{n,in} \cdot \sqrt{P_{LNA}}$$

where  $V_{N,in}$  is the input-referred noise spectral density averaged inside the passband and  $P_{LNA}$  is the total power consumption of the LNA.

<sup>&</sup>lt;sup>4</sup> There are also some exceptional cases. For example, the analog loop-filter of a  $\Delta\Sigma$  modulator can be merged with the ultrasound transducer to construct a hardware-efficient front-end interface [27]. This is however, beyond the scope of this thesis.

<sup>&</sup>lt;sup>5</sup> The definition of the noise-efficiency factor (NEF) for ultrasound LNAs follows K.Chen et al. [6]:

**Figure** 2.1. Architecture of (a) capacitive-feedback voltage amplifier (CFA) and (b)transimpedance amplifiers (TIA).

The basic architectures of a CFA and a TIA are presented in Figure 2.1, respectively. As the basis for the following discussion, some assumptions are listed below:

- To achieve the optimal noise-power trade-off, capacitive feedback is used for both architectures as a capacitive network is noise-free. Note that a capacitive-feedback TIA introduces a 90-degree phase shift to the received echo current and slightly reduces the natural resonance frequency [8], which should be taken into account in system-level design.

- A buffer stage, normally a source follower, is added succeeding to the operational transconductance amplifier (OTA) in the TIA stage to enforce accurate feedback, i.e. providing a sufficiently low output impedance. The power consumption of this buffer stage, and the extra power cost for probably-required frequency compensation, should be taken into account when comparing the noise-efficiency with the CFA, in which no in-loop buffer stage is needed. For applications where the LNA is directly interfaced with the external cable, an extra out-of-loop buffer stage would be also required for the CFA to drive the cable load. However, driving a heavy load using a buffer within the feedback loop probably still requires more power than the doing the same outside the loop, because the buffer in the loop may have to produce a wider bandwidth to maintain the loop stability. In other scenarios, e.g. an ADC sampler or a micro-beamformer following the LNA, the power consumption of the buffer stages should be carefully examined.

• A large feedback resistor is often needed in both architectures for DC biasing purposes, but is omitted in Figure 2.1 for simplicity.

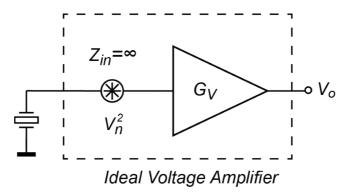

A CFA senses the voltage from the transducer by creating a relatively high inputimpedance; in contrast, a TIA senses the current by establishing a low inputimpedance virtual ground. This difference makes the noise comparison of these two structures not so straightforward at the first glance. In order to make a fair comparison, we use an ideal voltage amplifier as a reference, as shown in Figure 2.2. The idea voltage amplifier model has a voltage gain of  $G_V$  and an infinite input impedance  $Z_{in}$ . The input-referred noise of both structures as shown in Figure 2.1 can be modeled by a voltage noise source  $V_n^2$ .

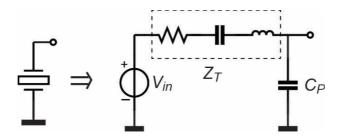

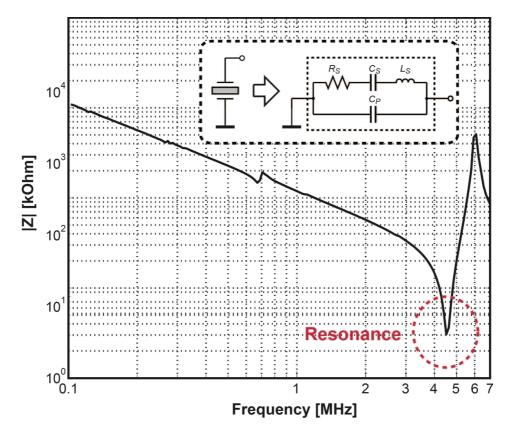

The noise-efficiency of ultrasound LNAs is strongly related to the characteristics of the transducer. In this thesis, we use the lumped Butterworth-Van Dyke electrical model [9] shown in Figure.  $2.3^6$  to mimic the impedance of the transducer, which contains a voltage source  $V_{in}$ , a motion-branch impedance  $Z_T$  formed by a RLC resonance tank, and a parasitic capacitor  $C_P$ . The effectiveness of this electrical model has been successfully demonstrated for a wide range of ultrasound transducers, such as piezoelectric transducers [1], capacitive micro-

Figure 2.2. An ideal voltage amplifier model

Figure 2.3. Equivalent electrical impedance model of an ultrasound transducer

<sup>&</sup>lt;sup>6</sup> Based on Norton's theorem, the same model can also be interpreted as a current voltage  $I_{in}$  in parallel with a motion-branch impedance and a parasitic capacitor, as presented in [1].

machined ultrasound transducers (CMUT) [10] and piezoelectric micromachined ultrasound transducers (PMUT) [4]. By substituting this model into Figure 2.1 to assist the following noise analysis, the signal attenuation due to the finite input impedance of the CFA and the TIA can be taken into account.

Next, we will calculate the equivalent voltage noise density  $V_n^2$  referred to the voltage source  $(V_{in})$  in the transducer model, for both CFA and TIA at the frequency of interest (within a unit bandwidth). To do so, the following assumptions are made:

- The OTA in both structures has an input-referred voltage noise density  $V_{n,OTA}^2$ ;

- The OTA in both structures has a sufficiently open-loop large (A) to enforce an accurate feedback, and a sufficiently wide bandwidth to ensure that the examined frequency point is inside the passband;

- The input parasitic capacitance of the OTA itself is not considered in the following analysis.

#### **CASE-I: TIA:**

The input-referred current noise of the TIA can be calculated as:

$$i_{n,in}^2 = V_{n,OTA}^2 \omega^2 (C_{F2} + C_P)^2$$

(2.1)

Taking the trans-impedance gain as the impedance of  $C_{F2}$ , we have the TIA output voltage noise as:

$$V_{n,out,TIA}^2 = i_{n,in}^2 \cdot \frac{1}{\omega^2 C_{F2}^2} = \left(\frac{C_{F2} + C_P}{C_{F2}}\right)^2 V_{n,OTA}^2$$

(2.2)

Hence the equivalent input-referred voltage noise when referenced to the voltage source in the transducer model is:

$$V_{n,TIA}^{2} = \frac{1}{G_{V,TIA}^{2}} \left(\frac{C_{F2} + C_{P}}{C_{E2}}\right)^{2} V_{n,OTA}^{2}$$

(2.3)

where the equivalent voltage gain of the TIA can be calculated as:

$$G_{V,TIA} = \frac{1}{\omega C_{F2} \cdot \left[ Z_T (1 + \omega C_P Z_{in,TIA}) + Z_{in,TIA} \right]}$$

(2.4)

where  $Z_{in, TIA}$  is the actual input impedance of the TIA, which approximately equals:

$$Z_{in,TIA} = \frac{1}{(1+A)\omega C_{F2}}$$

(2.5)

#### **CASE-II: CFA**

The input-referred voltage noise of the CFA can be calculated as:

$$V_{n,in,CFA}^{2} = \left(1 + \frac{C_{F1}}{C_{I}}\right)^{2} V_{n,OTA}^{2}$$

(2.6)

where  $1 + \frac{C_{F1}}{C_I}$  is the famous "noise gain factor" of the CFA structure.

Taking the mid-band voltage gain as  $\frac{C_I}{C_{F1}}$ , the CFA output voltage noise is:

$$V_{n,out,CFA}^{2} = \left(\frac{C_{I}}{C_{F1}}\right)^{2} \left(1 + \frac{C_{F1}}{C_{I}}\right)^{2} V_{n,OTA}^{2} = \left(1 + \frac{C_{I}}{C_{F1}}\right)^{2} V_{n,OTA}^{2}$$

(2.7)

Therefore we have the equivalent input-referred voltage noise (when referenced to the voltage source in the transduce model) of a CFA as:

$$V_{n,CFA}^{2} = \frac{1}{G_{V,CFA}^{2}} \left( 1 + \frac{C_{I}}{C_{F1}} \right)^{2} V_{n,OTA}^{2}$$

(2.8)

where the equivalent voltage gain of the CFA is:

$$G_{V,CFA} = \frac{1}{Z_{T}(\omega C_{p} + \omega C_{I}) + 1} \frac{C_{I}}{C_{FI}}$$

(2.9)

To compare the noise efficiency, we assume that:

$$G_{VTIA} = G_{VCSA} \tag{2.10}$$

From equation (2.3) and (2.8) we have:

$$\frac{V_{n,TIA}^{2}}{V_{n,CFA}^{2}} = \frac{\left(1 + \frac{C_{p}}{C_{F2}}\right)^{2}}{\left(1 + \frac{C_{I}}{C_{F1}}\right)^{2}}$$

(2.11)

where the parameters  $\frac{C_P}{C_{F2}}$  and  $\frac{C_I}{C_{F1}}$  are constrained by equations (2.4) (2.9) and (2.10).

Equation (2.11), along with equations (2.4) (2.9) (2.10), can be used as a simple criterion for the selection of ultrasound LNA architectures when the power consumption is purely noise-limited (e.g. in high-precision low-frequency ultrasound applications). For example, if

$$Z_T \gg \frac{1}{(1+A)\omega C_{F2}}, C_{F2} \gg \frac{C_P}{1+A}$$

(2.12)

Equation (2.11) can be simplified as:

$$\frac{V_{n,TIA}^{2}}{V_{n,CFA}^{2}} = \left(1 - \frac{C_{I} + \frac{1}{\omega Z_{T}}}{C_{F2} + C_{P} + C_{I} + \frac{1}{\omega Z_{T}}}\right) < 1$$

(2.13)

which suggests that the noise efficiency of the TIA would be always better than that of the CFA. This result agrees with the intuition because the condition (2.12) implies a high-impedance transducer with a relatively small parasitic capacitance. On the other hand, a large transducer parasitic capacitor  $C_P$  will make the TIA structure less attractive.

In the above analysis, we assume that the power consumption of the LNA is limited by the noise requirement, rather than its bandwidth. When we take the bandwidth into account, the impact of  $C_P$  becomes even more significant.  $C_P$  introduces an input pole in the TIA, which limits the bandwidth of the TIA to:

$$BW_{TLA} = \frac{g_m}{2\pi \left(C_P + C_L + \frac{C_P C_L}{C_{F2}}\right)}$$

(2.14)

while the bandwidth of the CFA is approximately:

$$BW_{CSA} \approx \frac{g_m}{2\pi C_I C_L / C_{F1}}$$

(2.15)

where  $g_m$  is the transconductance of the OTA and  $C_L$  is the load capacitance. Equations (2.14) (2.15) emphasize that in high-frequency ultrasound transducers with large parasitic capacitance, CFA is more advantageous than TIA in terms of the power efficiency.

In the following sections, the outcome of the above analysis is applied in the LNA design for specific types of ultrasound transducers, namely piezo-electronic

transducers and PVDF transducers, which reveal different impedance characteristics. A variety of circuit design techniques are also introduced in both case studies to further improve their power and area efficiency.

## 2.2 A Compact, Low-power LNA for Piezoelectric Transducers<sup>7</sup>

#### 2.2.1 Introduction

The increasing clinical need for better visualization of human organs, such as the valves and chambers of the heart, calls for the development of miniature endoscopic and catheter-based ultrasound probes [3, 11, 12]. Such probes will be capable of providing the physician with valuable real-time 3-D images for diagnostic purposes and for guiding interventional procedures, while being more patient-friendly and cost-effective than alternative imaging techniques. The acquisition of 3-D images requires a 2-D transducer array that consists of thousands of elements, and an associated front-end integrated circuit that connects the transducer array with the external imaging system. The strict constraints on the size and power dissipation of the probe tip present a challenge for the design of the front-end electronics. Hence, high power-efficiency and small silicon area become the main design targets for front-end circuits in such probes.

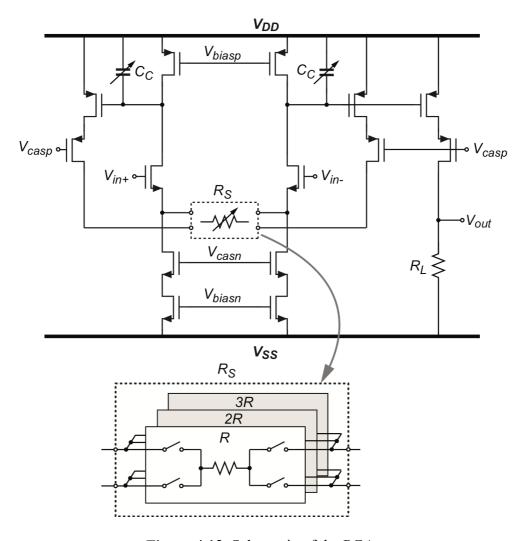

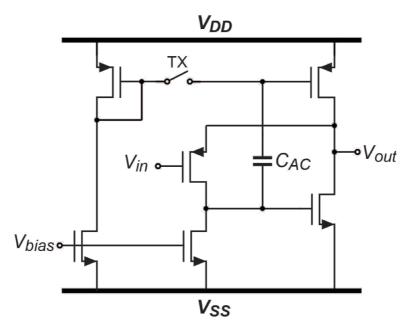

Figure 2.4 shows the architecture of a front-end integrated circuit interfaced with a 2-D piezoelectric transducer array [11]. Compared to capacitive micro-machined ultrasonic transducers (CMUTs), bulk piezoelectric transducers, typically based on PZT, offer a higher sensitivity without the need for a high DC bias voltage, while having a narrower bandwidth [10]. To simplify the implementation of the electronics, we adopt an architecture in which the 2-D transducer is divided into a receive subarray with associated integrated receive circuitry, and a smaller transmit subarray directly wired to an imaging system [11]. The techniques presented in this section, however, are equally applicable to architectures that include local transmit circuits. The receive circuitry for each transducer element consists of a low-noise amplifier (LNA), a programmable-gain amplifier for time-gain compensation (TGC) and delay lines for local beamforming. Among these building blocks, optimizing the LNA is usually the key for minimizing power

<sup>7</sup> This section is based on publication "A Compact 0.135-mW/Channel LNA Array for Piezoelectric Ultrasound Transducers," in *Proc. ESSCIRC 2015*, Sept. 2015, pp. 404-407.

consumption because, in most cases, the majority of the power in the receive circuitry is consumed by the LNA to arrive at an input-referred noise level that is small compared to the transducer's noise.

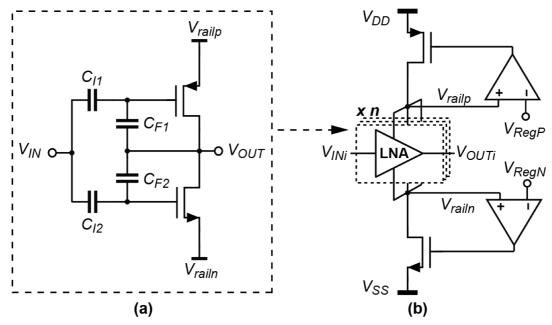

In this work, an ultra-low power LNA array targeted for piezoelectric transducers is presented. It adopts a capacitive feedback topology to provide an accurate and programmable voltage gain for the received transducer signals, while optimizing the noise-power trade-off. Moreover, a single-ended cascoded inverter with local supply regulation is employed as the OTA to further improve the power efficiency. Implemented in a 0.18  $\mu m$  CMOS technology, each LNA channel occupies less than 0.01 mm² of silicon area and consumes only 0.135 mW from a 1.8 V supply. Acoustic measurements have been performed by connecting the LNA array to a PZT matrix on a silicon substrate. The acoustic results show that the design achieves a noise-efficiency-factor (NEF) of 0.22 mPa  $\sqrt{mW/Hz}$ , which is 2.5  $\times$  better than the state-of-the-art [8].

#### 2.2.2 LNA Architecture

The choice of the LNA architecture is dictated by the electrical impedance of the target transducer. Most reported CMUT interface circuits utilize a transimpedance amplifier (TIA) as the LNA [3, 6, 12, 13], with an input-impedance less than the transducer's impedance to sense the motional current. However, similarly-sized bulk PZT transducers, as applied in our work, have a much lower impedance around the center frequency [10], typically a couple of  $k\Omega s$ . This

**Figure** 2.4. Architecture of front-end integrated circuits for a 2-D piezoelectric transducer array.

Figure 2.5. The proposed LNA architecture for piezoelectric transducer

Figure 2.6. Simplified schematic of the inverter-based OTA proposed in [14].

makes the TIA structure less effective, since creating a sufficiently low inputimpedance requires extra power spent on increasing the gain of the amplifier, rather than on reducing noise.

Instead, we propose to use a capacitive-feedback voltage amplifier, as shown in Figure 2.5. It offers a mid-band voltage gain of  $A_M = C_I / C_F$  and a bandwidth determined by the trans-conductance of the operational trans-conductance amplifier (OTA). Its input impedance is dictated by the input capacitor  $C_I$  and can be easily sized to tens of k $\Omega$ s within the bandwidth of interest (1 MHz to 18 MHz), so as to sense the transducer's voltage, rather than its current.

**Figure** 2.7. (a) Capacitor splitting; (b) dual-rail local regulation (bias control circuits not shown for simplicity).

#### 2.2.3 Circuit Implementation

In order to minimize power consumption, the current-efficiency of the OTA has to be maximized, which makes the CMOS inverter an attractive candidate. A straightforward inverter-based implementation is shown in Figure 2.6 [14]. In order to bias the NMOS and PMOS transistors in their optimal region, the input voltage is AC coupled to the gates, while a DC control loop sets the output voltage to the mid-supply.

When applied to the targeted ultrasound application, the circuit of Figure 2.6 has the following limitations. The AC-coupling capacitors and the parasitic capacitor at the input gates form a capacitive divider, which attenuates the input signal and thus increases the input-referred noise of the LNA. Enlarging the AC-coupling capacitors is expensive in terms of the silicon area. Moreover, the circuit suffers from poor power-supply rejection, while in ultrasound probes, the supply lines can be noisy even in the signal band due to the co-integrated digital signal processing circuits. Finally, the feedback amplifier in the DC control loop is always connected to one of the inverter's input nodes, where it adds noise and introduces extra parasitic capacitance.

Here, these problems are solved by applying the following techniques.

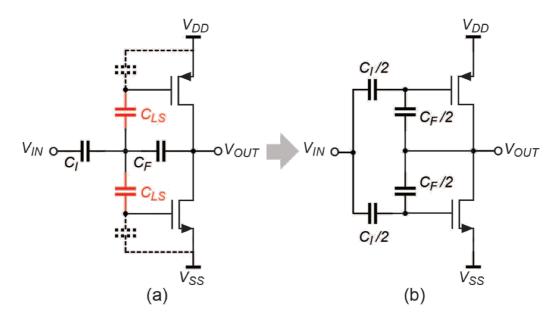

#### Capacitor Splitting

As shown in Figure 2.7a (the DC bias control loop is not shown in this figure for simplicity), the input bias for the NMOS and PMOS transistors can be separated by splitting the input and feedback capacitors into two equal pairs. As such, there is no need for adding extra AC-coupling capacitors. The mid-band gain becomes

$$A'_{M} = \frac{1}{2} \left( \frac{C_{I1}}{C_{F1}} + \frac{C_{I2}}{C_{F2}} \right) = \frac{C_{I}}{C_{F}} = A_{M}$$

(2.16)

where  $C_{I1} / C_{F1} = C_{I2} / C_{F2} = C_I / C_F$ .

In order to maintain the same input impedance, the input capacitors in each halfbranch should also be halved; so are the feedback capacitors. As results, the overall area of capacitors can be kept the same.

#### **Dual-rail Local Regulation**

An effective approach to improve the power-supply-rejection-ratio (PSRR) of an inverter-based amplifier is to regulate its supply lines. In this design, we propose to locally generate two internal power rails for an array of LNAs (Figure 2.7b), so as to reject noise from both the supply and the ground.

Given the fact that the loading currents for both regulators are known and approximately constant, the implementation of the regulators can be kept simple to save both power and area. A capacitor-less low-dropout regulator (LDO) based on a super source-follower [15] is adopted as the topology for both regulators. It

Figure 2.8. Dynamic bias control scheme.

provides sufficient loop gain and thus provides a reasonable PSRR even within the frequency range of the ultrasonic signals.

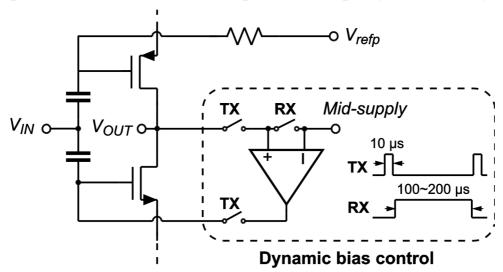

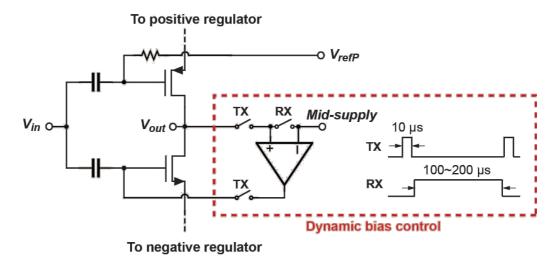

## **Dynamic Bias Control**

To prevent the DC control loop from adding noise during the operation of the LNA, we propose to add switches that periodically activate the loop synchronously with the transmit/receive phases of the ultrasound system, as shown in Figure 2.8. During the transmit phase, when the LNA is inactive, the feedback amplifier is connected to the inverter-based OTA to activate the bias control loop. Thus, the OTA is auto-zeroed, and the settled bias voltage is stored at the gates of the input transistors. After the transmit phase, the feedback amplifier is disconnected from the OTA and has both inputs connected to mid-supply, while the LNA starts receiving the echo signal, operating at the "memorized" bias condition stored on the parasitic capacitors of the input gates. To prevent the bias voltage from drifting, the bias control loop is periodically enabled in each transmit time slot.

The effectiveness of this technique is guaranteed by the relatively short period of transmit/receive cycles in medical ultrasound imaging, which normally ranges from  $100~\mu s$  to  $200~\mu s$ , depending on the imaging depth. The relatively large sizes of the input transistors, needed to reduce flicker-noise, also helps to ensure the robustness of the bias voltages.

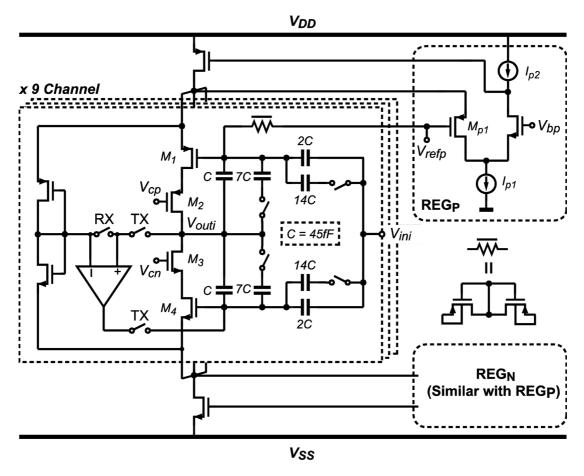

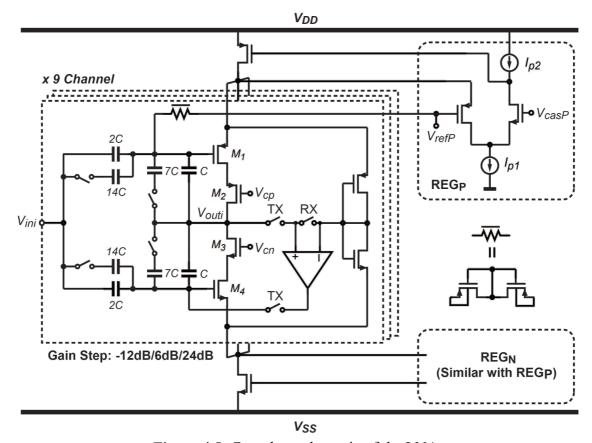

# Complete LNA Circuitry

Figure 2.9 shows the complete schematic of the 9-channel LNA array. By applying the approaches discussed above, a power-efficient and area-compact implementation is obtained. In each LNA channel, a unity-gain-connected inverter, implemented with long-channel transistors and consuming only 0.4  $\mu$ A, is connected between the two regulated supply rails to generate a reference voltage for the bias-control loop. The feedback amplifier is realized as a simple differential pair. It is designed to be able to settle within the transmit time slot (10  $\mu$ s), resulting in a current consumption less than 1  $\mu$ A. The inverter-based OTA is cascoded to ensure an accurate closed-loop gain, and input transistors  $M_I$  and  $M_4$  are biased in the weak-inversion region to enhance their current-efficiency. The bias voltage of  $M_I$  is derived from a diode-generated voltage reference  $V_{refp}$  via a

Figure 2.9. Complete LNA circuitry.

high-impedance pseudo-resistor. The same voltage is applied as the input of the positive-rail regulator. In such a way, the bias current of the OTA is defined by the difference of the reference currents  $(I_{pI} - I_{p2})$  and the dimension ratio of  $M_I$  and  $M_{pI}$ . While operating, 50  $\mu$ A is consumed by each OTA, and 110  $\mu$ A by each of the shared regulators, leading to a total power consumption of 670  $\mu$ A @ 1.8V for 9 channels, corresponding to 0.135 mW per channel.

The cascoded inverter structure has a limited output swing. To enhance the dynamic range of the LNA, a programmable gain function is implemented by including switchable input and feedback capacitors. Three gain levels (24/6/-12 dB) are offered, of which the 24-dB gain is designed to achieve the best noise performance and the highest receive sensitivity.

## 2.2.4 Experimental Results

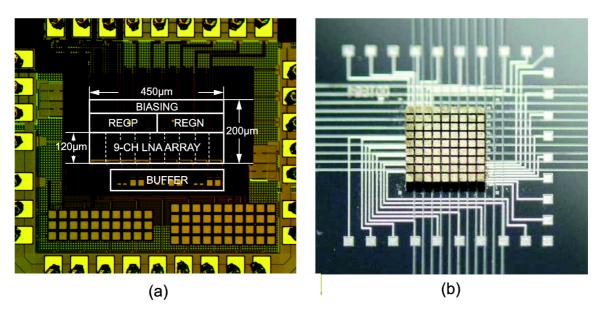

The LNA array has been fabricated in a standard 0.18 µm CMOS technology. Figure 2.10a presents a micro-photograph of the prototype chip. The outputs of the LNA array are multiplexed to three buffers that drive the external cables. The

Figure 2.10. Photograph of (a) the chip and (b) the PZT matrix on a silicon substrate.

core of the chip, including 9 LNAs, 2 regulators and bias circuits, occupies an area of 450  $\mu$ m  $\times$  200  $\mu$ m, which is equivalent to 0.01 mm<sup>2</sup> per channel.

To facilitate the acoustic characterization of the LNA array, a  $10 \times 10$  array of PZT transducers with a 200-µm pitch, built on top of a silicon substrate with metal interconnects (Figure 2.7b), is used to provide 9-channel inputs for the LNA array via PCB traces. The transducer provides a -6 dB bandwidth from 3.2 MHz to 4.8 MHz with a center frequency at 4 MHz.

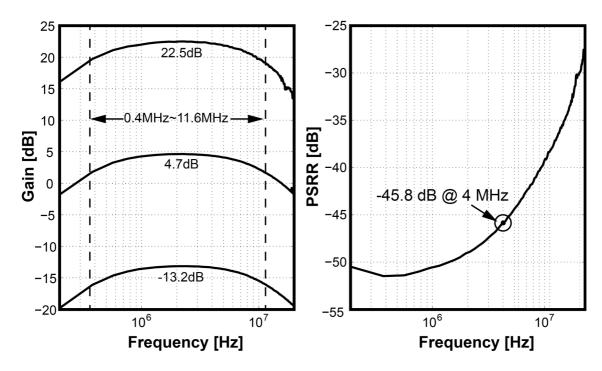

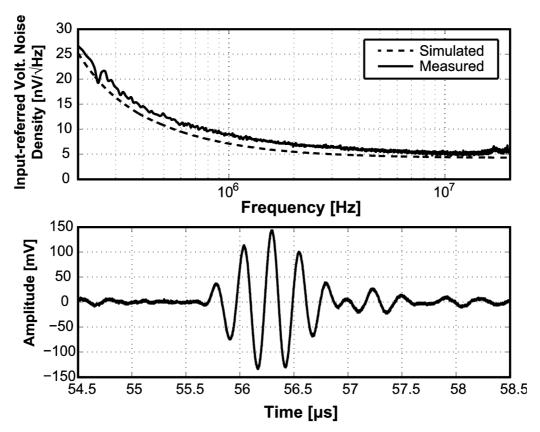

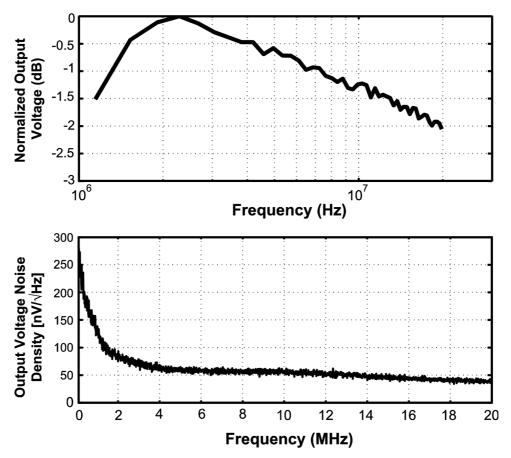

Figure 2.11a shows the measured transfer function of the LNA at different gain settings. The measured mid-band gains at each gain setting are 22.50 dB, 4.65 dB and -13.15 dB respectively, which are approximately 1 dB lower than the designed gains due to attenuation of the output buffers. The measured –3 dB bandwidth is from 0.4 MHz to 11.6 MHz. Figure 2.11b shows the measured PSRR from 200 kHz to 20 MHz. The circuit achieves a PSRR better than -45dB at 4 MHz. Figure 2.12a shows the measured input-referred voltage noise spectrum at the highest gain setting with a comparison to pre-layout simulation results. It is obtained by measuring the LNA output voltage noise and dividing it by the transfer function shown in Figure 2.11a, which indicates an input-referred voltage noise density of 5.9 nV/ $\sqrt{}$ Hz at 4 MHz. The integrated input noise voltage across the LNA bandwidth is 17.7  $\mu$ Vrms. The maximum input voltage is measured as 545 mVpp at the 1 dB compression point with the lowest LNA gain

Figure 2.11. Measured (a) transfer function and (b) PSRR.

setting, where a -40 dB 2<sup>nd</sup>-harmonic distortion is guaranteed. Thus, the circuit achieves an 81 dB overall dynamic range. Moreover, the measured channel-to-channel crosstalk is below -46 dB at 4 MHz.

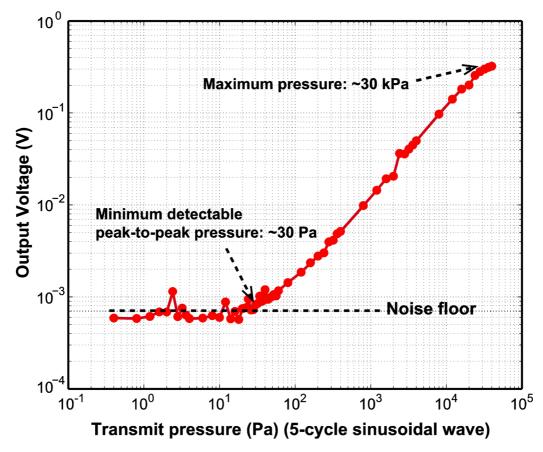

An acoustic measurement involving the LNA array and the PZT matrix has been performed in a water-tank. A calibrated unfocused piezoelectric transducer, placed 8.5 cm away, is used as the source. Figure 2.12b shows the observed signal from a single LNA output with a 1 Vpp 4 MHz 3-cycle burst sinusoidal wave applied to the transmitter. The incident pressure has been measured with a commercial hydrophone, giving an estimated receive sensitivity of 130 mV/kPa at the highest LNA gain setting.

A performance summary and comparison with state-of-the-art ultrasound front-end amplifiers is shown in Table-2.1, including their noise-efficiency factor (NEF) as defined in [6]. The input-referred electrical noise density is translated to acoustic pressure by the receive sensitivity of the transducer to facilitate the comparison with other work. With the lowest power consumption and a comparable input-referred noise, the proposed LNA achieves a NEF that is  $2.5 \times 10^{-5}$  better than the state-of-the-art.

**Figure** 2.12. (a) Measured and simulated input-referred voltage noise spectrum (top); (b) Received acoustic signal at the output of the LNA (bottom).

TABLE-2.1 Performance Summary and Comparison

| 17 ADEL 2.11 CHOTHance Summary and Comparison |                      |                                 |                           |                        |                                    |                           |                                          |                     |

|-----------------------------------------------|----------------------|---------------------------------|---------------------------|------------------------|------------------------------------|---------------------------|------------------------------------------|---------------------|

| Specs                                         | Target<br>Transducer | Element<br>Size<br>(µm ×<br>µm) | LNA<br>Bandwidth<br>(MHz) | Power<br>Cons.<br>(mW) | Receive<br>Sensitivity<br>(mV/kPa) | Dynamic<br>Range*<br>(dB) | Input-<br>referred<br>Noise<br>(mPa/√Hz) | NEF<br>(mPa•√mW/Hz) |

| [3]                                           | 2D-CMUT              | 250 ×<br>250                    | 10                        | 4.0                    | ~70                                | N/A                       | 1.8@5MHz                                 | 3.6                 |

| [12]                                          | 2D-CMUT              | 250 ×<br>250                    | 25                        | 2.4                    | 414                                | N/A                       | 0.9@4.4MHz                               | 1.4                 |

| [6]                                           | 1D-CMUT              | 300 ×<br>3000                   | 5.2                       | 14.3                   | 162                                | 60                        | 0.56@3MHz                                | 2.1                 |

| [13]                                          | 2D-CMUT              | 250 ×<br>250                    | 10.2                      | 1.4                    | 123                                | N/A                       | 2.3@5MHz                                 | 2.7                 |

| [8]                                           | 1D-CMUT              | N/A                             | 39.5                      | 1.0                    | 72                                 | 70                        | 0.55**                                   | 0.55                |

| This<br>work                                  | 2D-PZT               | 200 ×<br>200                    | 11.2                      | 0.135                  | 130                                | 81                        | 0.6@4MHz                                 | 0.22                |

<sup>\*</sup> Defined as the ratio of the maximum input signal at the 1-dB compression point and the minimum input signal at SNR = 0 dB.

<sup>\*\*</sup> Averaged value across the bandwidth from 4.4 MHz to 15.4 MHz.

#### 2.2.5 Conclusions

A power-efficient and compact LNA array for piezoelectric transducers has been presented. It is implemented as a capacitive-feedback voltage amplifier that senses the voltage from the transducer. A single-ended inverter-based OTA with dual-rail regulation and dynamic bias control is employed to achieve an ultra-low power consumption and a record NEF, which has been demonstrated by both electrical and acoustic measurements.

# 2.3 A Single-cable LNA Readout IC for PVDF transducer<sup>8</sup>

#### 2.3.1 Introduction

Cardiovascular diseases (CVD) are the primary cause of death worldwide, leading to more than 30% of the global mortality per year [16]. Among these cardiac deaths, almost half are caused by acute coronary syndromes, which are usually associated with ruptures of vulnerable plaques and thrombosis in the coronary artery. Over the last decades, a variety of imaging modalities have been developed to accurately detect the presence of vulnerable plaques [17]. A recent addition to the range of intravascular imaging techniques, intravascular photoacoustic (IVPA) imaging has proved its capabilities in identifying and locating lipid components in the vessel wall [18], which are the major risk factor for plague rupture [19], with reasonably large imaging depth [20] and high chemical specificity for lipid type [21]. This imaging technique creates an ultrasonic imaging of the optical absorption in atherosclerotic plaques by recording the emitted pressure wave following excitation by a short optical pulse. An established fact is that the frequency range of the photoacoustic (PA) signal is inversely proportional to the dimensions of absorbing structures [20]. Therefore, it is critical to match the transducer sensitivity to the signal frequency content for *in vivo* imaging, which is expected to range from 2 MHz to 15 MHz. However, conventional intravascular ultrasound (IVUS) transducers used in PA imaging systems have a receive bandwidth typically above 20 MHz [22, 23]. Thus, there is a clear need for a broadband and sensitive receiver dedicated for IVPA imaging to capture PA signals in the frequency range from 2 MHz to 15 MHz.

<sup>&</sup>lt;sup>8</sup> This section is based on publication "A Single-Cable PVDF Transducer Readout IC for Intravascular Photoacoustic Imaging," in *Proc. IEEE Ultrasonics Symp. (IUS)*, Oct. 2015.

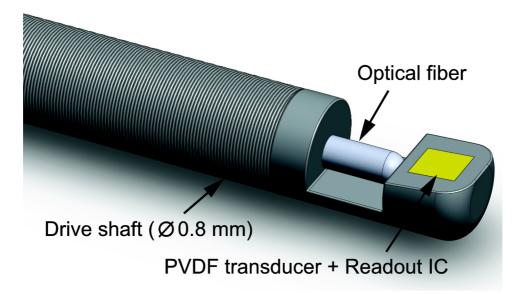

**Figure** 2.13. A conceptual drawing of the IVPA catheter core (without sheath) with the integrated PVDF transducer and readout IC. The target outer diameter of the catheter with sheath is 1 mm.

In this work, we propose to use polyvinylidene fluoride (PVDF) single-element transducers for sensing PA signals. Compared to the PZT ceramics, which are normally used in IVUS imaging, PVDF transducers present broader receiving bandwidth even with small sensing area, thanks to their relatively low acoustic impedance. However, a small PVDF element exhibits a high electrical impedance (>> 1 k $\Omega$ ) and a relatively low capacitance (< 5 pF/mm<sup>2</sup>), while the connecting coaxial cable usually has a low characteristic impedance (>> 50  $\Omega$ ) and a much higher capacitance (> 100 pF/m). As such, the capacitive loading effect of the connecting coaxial cable will result in significant signal attenuation, thus dramatically reducing the sensitivity of the PVDF transducer. To address this problem, a readout integrated circuit (IC) that can be closely integrated with the PVDF transducer and provide the cable-driving capability is called for.

Figure 2.13 shows a conceptual diagram of the proposed IVPA catheter core with a PVDF transducer and a readout IC integrated at the tip. The target outer diameter of the catheter is 1 mm. This constrained space needs to fit an optical fiber, a flexible drive shaft and the electrical wiring required by the readout IC. So far, most reported readout ICs implemented for intravascular ultrasound probes derive their power supply from external voltage sources [22]. Thus, additional electrical connections to the catheter tip are required to transfer supply voltages. Moreover, in order to minimize the voltage drop caused by the DC resistance of cables, the

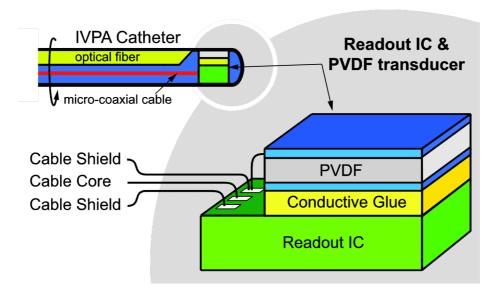

**Figure** 2.14. Architecture of the IVPA catheter and the co-integrated PVDF transducer & readout IC. The readout IC is connected to the coaxial cable via wire-bonds.

core diameter of the supply cable may not be too small (normally > 0.3 mm). Such limitations further reduce the flexibility of the catheter and increase the difficulty of the catheter assembly.

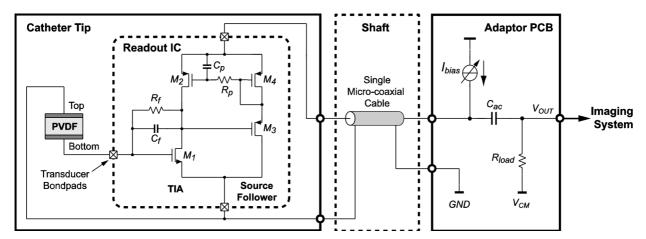

In this section, we present a readout IC that is directly integrated with a single-element PVDF transducer to capture the PA signals. A current-mode powering scheme is applied to eliminate the need for extra supply cables, which helps in reducing the rigidity of the catheter. A capacitive-feedback transimpedance amplifier is adopted as the front-end amplifier to improve the signal-to-noise ratio of received signals. A prototype IC has been designed and fabricated to prove the concept. Its electrical performance has been evaluated. In addition, the acoustic characteristic of the co-integrated readout IC and PVDF transducer have been measured to further demonstrate the effectiveness of the proposed techniques.

# 2.3.2 Prototype Assembly

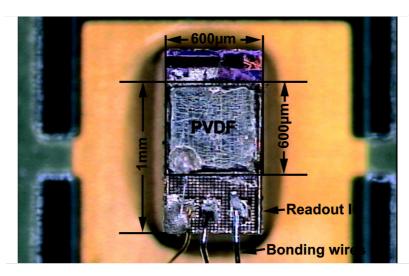

Figure 2.14 illustrates the architecture of the proposed IVPA catheter with the readout IC integrated with a single-element PVDF transducer. A direct interconnection scheme was applied to connect the PVDF element and the readout IC. In our prototype, a layer of electrically-conductive glue was first applied on top of the transducer bondpads of the readout IC, which are designed for electrical contact with the PVDF element. A 52- $\mu$ m-thick PVDF film with electrodes on both sides was cut in a square shape (0.6 mm  $\times$  0.6 mm) using a laser

Figure 2.15 Schematic of the proposed single-cable PVDF transducer readout IC

micromachining workstation. This PVDF element was then directly mounted on top of the readout IC via the conductive glue layer. Thus, the conductive glue layer creates the electrical connection between the readout IC and the PVDF element. The readout IC was then wire-bonded to a flex-circuit, which provides the connection between the IC and the solder-pads for a 1 m single micro-coaxial cable.

# 2.3.3 Readout IC Design

#### System Overview