### M.Sc. Thesis

## Physical design of a 3D router: reducing the number of vertical connections and enabling asynchronous operation

Milovan Vasić

#### Abstract

With the use of multi-core architectures, the Network-on-Chip (NoC) became an important research topic. The most important benefit of a NoC compared to a communication bus is that it is scalable. The heart of the NoC is the router, which provides the communication between different computational units. This component is highly suitable to be a 3D component, which means that the connection can go into a vertical direction. This way the NoC is extended, with the same area footprint. This thesis describes the physical design of the 3D router, where various design problems are solved. An existing router architecture is used as a start-point. One of the problems which this thesis is trying to solve, is the reduction of the number of needed data lines. This is especially useful for the vertical data lines, which are implemented with Through Silicon Vias (TSVs). A TSV has a large footprint compared to a transistor, which means it takes up a lot of chip area. This results in increased cost. The reduction of the data lines is accomplished by the serialization of the data. It is determined that the best serialization ratio is 4. The 3D router is also adjusted for asynchronous operation. This is accomplished with the use of FIFOs, two-flop synchronizers and Gray Encoders.

# Physical design of a 3D router: reducing the number of vertical connections and enabling asynchronous operation

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

MICROELECTRONICS

by

Milovan Vasić born in Vlissingen, the Netherlands

This work was performed in:

Circuits and Systems Group

Department of Microelectronics & Computer Engineering

Faculty of Electrical Engineering, Mathematics and Computer Science

Delft University of Technology

#### **Delft University of Technology**

Copyright  $\odot$  2014 Circuits and Systems Group All rights reserved.

## DELFT UNIVERSITY OF TECHNOLOGY DEPARTMENT OF MICROELECTRONICS & COMPUTER ENGINEERING

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled "Physical design of a 3D router: reducing the number of vertical connections and enabling asynchronous operation" by Milovan Vasić in partial fulfillment of the requirements for the degree of Master of Science.

| Dated: 9 May 2014  |                               |

|--------------------|-------------------------------|

| Chairman:          | Prof.dr.ir. A.J. van der Veen |

|                    | r rondini. And van der veen   |

| Advisors:          |                               |

|                    | Dr.ir. T.G.R.M. van Leuken    |

|                    | Dr.ir. N.P. van der Meijs     |

| Committee Members: |                               |

|                    | Dr.ir. M.R.C.M. Berkelaar     |

|                    | Dr.ir. A.J. van Genderen      |

## Abstract

With the use of multi-core architectures, the Network-on-Chip (NoC) became an important research topic. The most important benefit of a NoC compared to a communication bus is that it is scalable. The heart of the NoC is the router, which provides the communication between different computational units. This component is highly suitable to be a 3D component, which means that the connection can go into a vertical direction. This way the NoC is extended, with the same area footprint. This thesis describes the physical design of the 3D router, where various design problems are solved. An existing router architecture is used as a start-point. One of the problems which this thesis is trying to solve, is the reduction of the number of needed data lines. This is especially useful for the vertical data lines, which are implemented with Through Silicon Vias (TSVs). A TSV has a large footprint compared to a transistor, which means it takes up a lot of chip area. This results in increased cost. The reduction of the data lines is accomplished by the serialization of the data. It is determined that the best serialization ratio is 4. The 3D router is also adjusted for asynchronous operation. This is accomplished with the use of FIFOs, two-flop synchronizers and Gray Encoders.

## Acknowledgments

I want to thank Rene van Leuken for finding me a very interesting topic for doing my master thesis. I wanted to do something in chip design, especially in 3D chip design. This was the perfect opportunity to extend my knowledge on this topic. The road to accomplish this was not easy and it took me some time, but at the end I succeeded. Thank you Rene for the countless times I bumped in your office for questions, and you helped me. This meant a lot to me.

A person who joined later was Michel Berkelaar. I want to thank you for all your support during my master thesis. Not only the educational support you have given me, but especially mental support which I needed from time to time. Because your background lies in the industry, you could teach me a lot of stuff which were hard to find in textbooks. Thank you very much for this.

Sumeet, using your original router design, I had a lot of questions for you. For every question you always took the time to explain it to me. Thank you kindly for that! Radhika, even when you're abroad, and working for a big firm, you have found time to answer me a couple of questions I fired at you. It helped me a lot and thanks for that.

Of course all other teachers, staff members who I might have forgot to mention, thank you for all your support. Also you were a big part of helping me on the way finish my master thesis.

Great thanks goes out to my family, who have always supported me. Without them, I would never have managed to accomplish what I have today. Both of my parents, and both of my brothers, thank you for everything!

Milovan Vasić Delft, The Netherlands 9 May 2014

## Contents

| $\mathbf{A}$ | bstra | ct                                                           | V  |

|--------------|-------|--------------------------------------------------------------|----|

| A            | cknov | wledgments                                                   | vi |

| 1            | Intr  | roduction                                                    | ]  |

|              | 1.1   | Motivation                                                   |    |

|              |       | 1.1.1 Background                                             |    |

|              |       | 1.1.2 Network-on-Chip                                        | 6  |

|              |       | 1.1.3 Design problems 3D router                              | 4  |

|              | 1.2   | Contributions                                                | •  |

|              | 1.3   | Thesis Organization                                          | ۷  |

| 2            | Bac   | kground                                                      | 7  |

|              | 2.1   | Design and Components                                        | ,  |

|              |       | 2.1.1 IC Design Methodology                                  | ,  |

|              |       | 2.1.2 Standard Cell Library                                  | ,  |

|              |       | 2.1.3 Memory                                                 | 10 |

|              |       | 2.1.4 Through Silicon Via                                    | 10 |

|              |       | 2.1.5 3D Implementation                                      | 13 |

|              | 2.2   | Approach                                                     | 15 |

|              |       | 2.2.1 Motivation                                             | 15 |

|              |       | 2.2.2 Components                                             | 16 |

|              | 2.3   | Workflow                                                     | 1  |

| 3            | 3D    | Router                                                       | 2  |

|              | 3.1   | Motivation                                                   | 2  |

|              | 3.2   | Architecture                                                 | 2  |

|              | 3.3   | Memory                                                       | 2  |

|              | 3.4   | Through Silicon Via                                          | 2! |

|              |       | 3.4.1 TSV Design                                             | 26 |

|              | 3.5   | Implementation                                               | 34 |

|              |       | 3.5.1 Implement the RTL HDL code and testbench               | 3  |

|              |       | 3.5.2 Simulation of RTL                                      | 3  |

|              |       | 3.5.3 Synthesis in Design Compiler                           | 35 |

|              |       | 3.5.4 Place and Route in SoC Encounter                       | 36 |

| 4            | Red   | lucing the data lines in vertical direction by serialization | 39 |

|              | 4.1   | Introduction                                                 | 39 |

|              | 4.2   | Serializer                                                   | 40 |

|              | 4.3   | Deserializer                                                 | 4  |

|              | 1 1   | Implementation and timing                                    | 4  |

| 5            | The   | asynchronous working of the router                   | <b>47</b>  |

|--------------|-------|------------------------------------------------------|------------|

|              | 5.1   | Introduction                                         | 47         |

|              | 5.2   | Design of an asynchronous router                     | 47         |

|              |       | 5.2.1 Clocks and resets                              | 47         |

|              |       | 5.2.2 Synchronization                                | 51         |

|              | 5.3   | A note about simulation of synchronizers in ModelSim | 56         |

| 6            | App   | olication and Results                                | 59         |

|              | 6.1   | 2 routers in RTL                                     | 59         |

|              |       | 6.1.1 Design                                         | 59         |

|              |       | 6.1.2 Throughput                                     | 59         |

|              |       | 6.1.3 Latency                                        | 67         |

|              | 6.2   | 1 router after P&R                                   | 67         |

|              |       | 6.2.1 Timing                                         | 67         |

|              |       | 6.2.2 Asynchronous operation                         | 69         |

|              |       | 6.2.3 Area                                           | 70         |

| 7            | Con   | clusion                                              | <b>75</b>  |

|              | 7.1   | Summary                                              | 75         |

|              | 7.2   | Future work                                          | 77         |

| $\mathbf{A}$ | TSV   | timing values for liberty file                       | <b>7</b> 9 |

| В            | 3D :  | router diagram                                       | 81         |

| Bi           | bliog | graphy                                               | 83         |

## List of Figures

| 1.1                                                         | 3D NoC with CPU, network interface and 7-port router                |

|-------------------------------------------------------------|---------------------------------------------------------------------|

| 2.1<br>2.2<br>2.3                                           | ASIC semi-custom design                                             |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7               | Three dimensional 7-port router architecture                        |

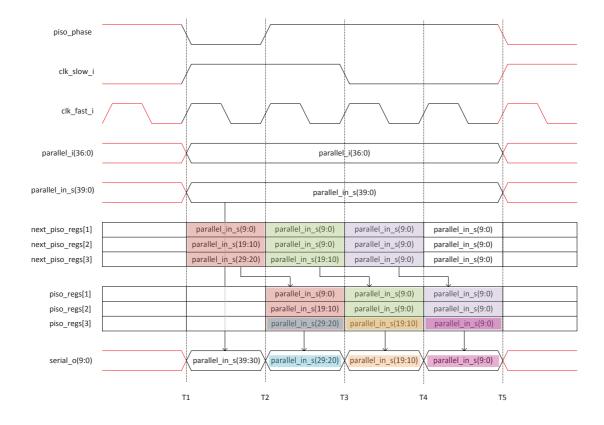

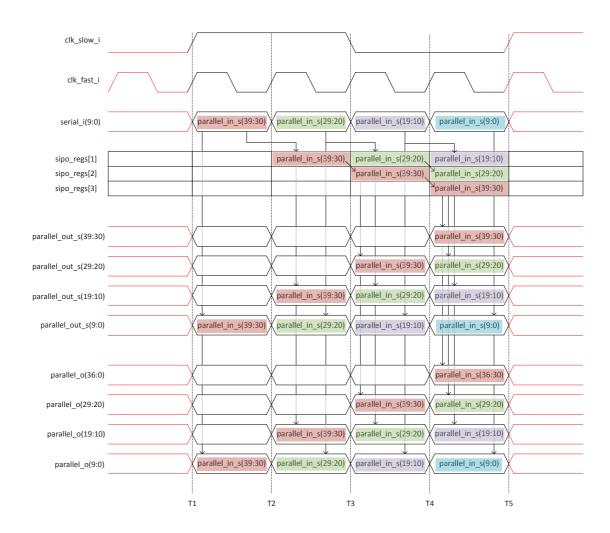

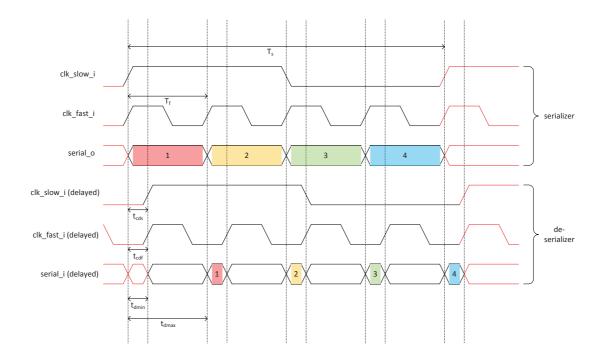

| 4.1<br>4.2<br>4.3                                           | Data serialization timing diagram                                   |

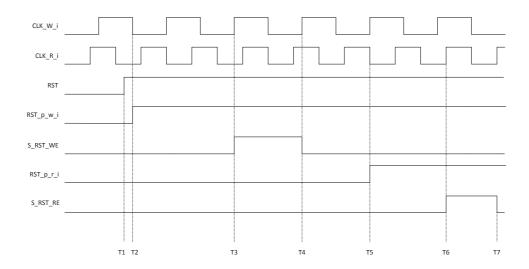

| 5.1<br>5.2<br>5.3<br>5.4                                    | The making of the initialization write and read resets              |

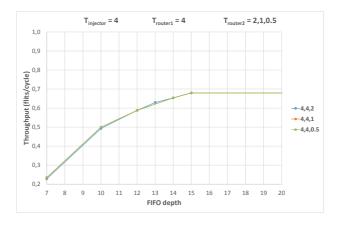

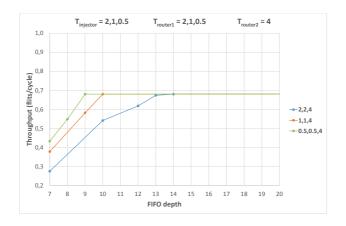

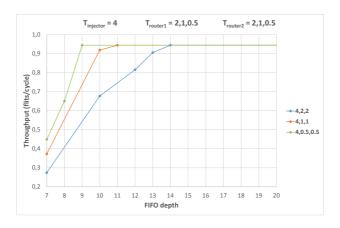

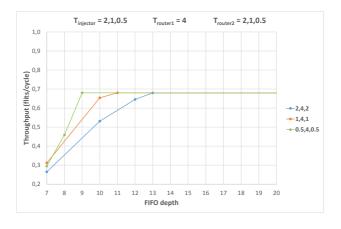

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9 | 2 routers vertically connected                                      |

| B.1                                                         | Complete 3D router diagram with LOCAL and UP input/output port . 82 |

## List of Tables

| 2.1 | Metal information for 1 tier [1]                                           | 13 |

|-----|----------------------------------------------------------------------------|----|

| 3.1 | Memory block specifications                                                | 25 |

| 3.2 | Equation parameters with their symbols                                     | 33 |

| 3.3 | Values for the parasitic components of a TSV                               | 33 |

| 4.1 | Input and output signals serializer                                        | 40 |

| 4.2 | Input and output signals deserializer                                      | 42 |

| 5.1 | Input clocks asynchronous router                                           | 48 |

| 5.2 | Output clocks asynchronous router                                          | 48 |

| 5.3 | Global clocks asynchronous router                                          | 49 |

| 5.4 | Intermediate clocks asynchronous router                                    | 49 |

| 5.5 | Clock groups                                                               | 49 |

| 5.6 | Reset signals                                                              | 50 |

| 6.1 | Tested clock cycle time at which the router is operating properly          | 70 |

| 6.2 | TSV array with different serialization ratios                              | 72 |

| A.1 | Output transition time w.r.t. input transition time and output capacitance | 79 |

| A.2 | Propagation delay w.r.t. input transition time and output capacitance.     | 79 |

Introduction

#### 1.1 Motivation

#### 1.1.1 Background

In current IC technology several problems exist regarding to chip design. They are related to the desire for performance increase, which includes higher speed, lower power dissipation and smaller area. Speed is related to computational performance. The usual method to increase computational performance was to use more transistors. One way to accomplish that was to shrink the channel length (transistor size), which meant more transistors could be put on the same chip area and the computational performance would increase. It also means that the transistors are getting faster and their capacity lower, which also results in an increase in computational performance. A problem with this method is that the channel length of the transistor is already reaching the 10 nm border where various effects come into play. These effects include tunneling and energy quantization [2], which significantly increases the complexity of the operation of the transistor. Another way to increase the number of transistors is to increase the chip area, so more transistors can be put on the chip. The problem with this method is that with the increase of the chip area, the possibility of defects occurring also increases. This means that after manufacturing, the number of working chips will be reduced (low yield), resulting in increased cost.

The demand for increased performance in a chip caused engineers to find different solutions. A trend that could be observed was that engineers began to use multi-core chip design. An advantage of multi-core architectures is that they are suitable for parallel computing, which improve computational performance in general. This type of chips are known as *chip-multi-processor* (CMP). The communication between the different cores is done by communication buses. With the increase in the number of used cores, the complexity of the buses increases, resulting in long and complex interconnections [3]. This causes the delay, power dissipation and occupied chip area to become larger. The delay results in decrease of the throughput. Because more cores cause problems for the communication buses, this system is not suitable for scalability. Because transistors were shrinking much faster then wires, wires became the larger component of the two, resulting in longer delays and increased power dissipation [4]. The connection in a chip was usually based on point-to-point connections. With the increasing complexity of chips, it became increasingly hard to obey the real-time constraints in point-to-point connections [5] which were needed to let the design work properly.

#### 1.1.2 Network-on-Chip

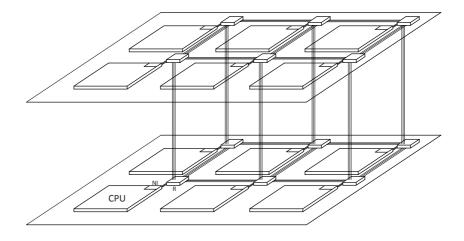

A solution for the communication problems, which is extensively researched, is the Network-On-Chip (NoC). A NoC provides the communication between different computational units, like CPU's. It consists of routers, which are connected to each other in a mesh, and where different computational units are connected to them through a Network Interface (NI). Using a NoC instead of a communication bus solves the complex wiring problem. Because the computational blocks are only connected to their router, and since the router determines the communication protocol, no long wiring is needed, and no complex real-time constraints need to be obeyed. An advantage of a NoC is that it is scalable, which means more routers could be added together with their computational units, without degradation of performance. This NoC can be extended with 3D routers, enabling 3D chip design which is done by the vertical connections of the 3D router. With a 3D router, which serves as a 3D component, multiple meshes can be stacked on top of each other, increasing the computational performance without increase of the chip area. Two meshes stacked on top of each other are shown in Figure 1.1.

There already is a 3D router design by S. Kumar [6] which can serve as a 3D component. The router had initially 5 ports (north, south, east, west, local). This was extended by two additional vertical ports (up, down) which made this a 3D component. Every port can send and receive 37-bit data flits. For this design a RTL model is available, which simulates correctly, but there is no physical design available. In order to be able to use this 3D component for 3D chip design, some design problems like timing, placement and physical implementation of the vertical connections should be solved. After this, physical design can be done.

#### 1.1.3 Design problems 3D router

One of the design problems in the router design by S. Kumar, is that it uses 37-bit wide data lines for all the input/output ports. This means that every port consists of 37 lines for the input and 37 lines for the output. On every clock cycle of the router, one bit is sent through a data line. Because this data line has a very small delay compared to the clock cycle on which the router is operating, a bit can be sent at a much faster interval, compared to the clock cycle of the router. In this way the capacity of a data line is more efficiently utilized. If the interval for sending a bit through a data line would be decreased, more bits could be transported, which means fewer data lines would be needed in order to transport an equal amount of bits.

Another problem in the router design by S. Kumar is that it only works in one clock domain. This means that when used in an unmodified NoC configuration, all the routers should operate on the same clock frequency. This is hard to achieve, especially between two routers sitting on different tiers. A solution has to be found which enables the operation in different clock domains.

The physical design problems that arise when using the router design of S. Kumar, are the need for *Trough Silicon Vias* (*TSVs*) for every data line in the vertical direction. As explained earlier, there are 37 input and output data lines in each direction. Because a TSV has a large footprint compared to a transistor, a lot of chip area will be needed

in order to accommodate all the TSVs which will result in cost increase. If the number of needed TSVs could be reduced, less area would be taken by them, resulting in lower costs.

This thesis is trying to solve the above mentioned problems by using a new design methodology. The design problems of the router by S. Kumar which this thesis is trying to solve are:

- Low utilization of the capacity in the data lines

- Communication between multiple clock domains

- Large footprint of needed TSVs

#### 1.2 Contributions

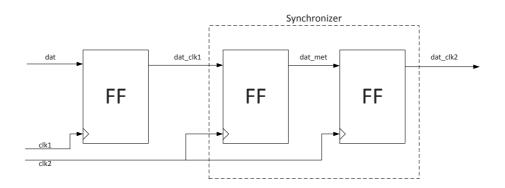

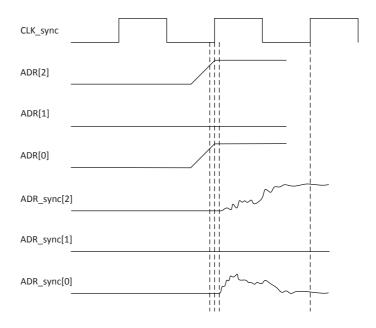

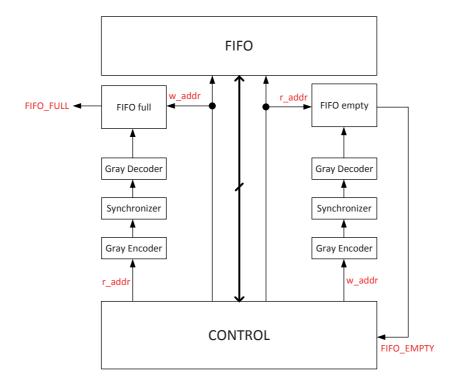

This thesis concentrates on the reduction of the needed data lines in the vertical direction in order to improve the throughput of the data lines, and to reduce the number of needed TSVs because of their footprint. The technique which is used, is serialization/de-serialization. For this an existing design of a serializer/de-serializer is used [5] and implemented in the 3D router. This design makes use of two clocks, which ensures that the serialization and de-serialization is done without the need of additional clock cycles. Some timing problems are solved in order to ensure valid operation of the serializer/de-serializer. To enable operation in multiple clock domains, the FIFO from the router, which consists of a two-port register file, is used together with two-flop synchronizers and Gray encoders [7].

A physical design is made for the adjusted 3D router. The design of choice is an ASIC semi-custom design, which consist of a standard cell library and some macro's. The standard cell library is composed of the 45 nm Nangate Open Cell Library. For the FIFO, macro blocks are used, which consist of 55 nm Faraday memory blocks (two-port register files). These blocks are adjusted for the 45 nm grid. The EDA tools which are used for physical design are Synopsys Design Compiler for synthesis and Cadence SoC Encounter for place&route. For the TSV a macro is made, which is composed of a RTL model, an abstract layout model (LEF file) and a timing model (Liberty file) which is based on the work of R. Jagtap [8]. Because it is intended to let the router operate on as high a clock frequency as possible, some timing optimization steps are performed.

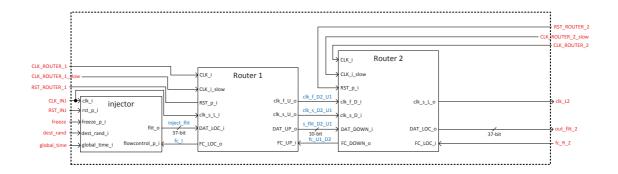

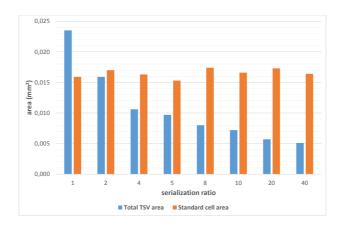

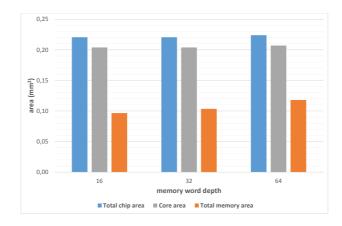

At the end, two asynchronous routers with a serializer and de-serializer in between are connected through their vertical interconnections, which forms a basic NoC. To test the operation of this design, an injector with a large test coverage is used, made as a vhdl testbench, which emulates a real computational unit like a CPU core (ARM, Micro-Blaze, X86, etc.). When connecting several 3D routers on all sides, a complete mesh is made which looks like Figure 1.1. In this thesis only two vertically connected routers are tested, because this forms the most complex communication where the serialized data lines are tested, together with the asynchronous operation of the two routers. The floorplan which is used is kept the same, where the number of TSVs are changed, dependent on the serialization ratio of the data in the vertical direction. Also different memory sizes are tested to see how they impact the area of the chip. In the

end there is an overview of different results, like the throughput, latency, complete chip area, memory area and TSV area, together with the timing results. This way it can be determined how the different topologies and serialization factors influence the occupied chip area and performance.

The significant contributions of this thesis include:

- Reduction of data lines in the vertical direction of a 3D router

- Enable operation of a 3D NoC in multiple clock domains

- Physical design of a 3D router

- Timing optimization in physical design of a 3D router

#### 1.3 Thesis Organization

The thesis is organized in the following way:

- Chapter 2 will describe some background information, compare similar previous implementations and discuss what will be improved in this implementation.

- Chapter 3 will describe the design steps on how to make a physical design of a 3-dimensional router with 7 ports, where the 2 vertical ports are made with the use of TSVs. First the architecture of the router [6] and then the implementation of it will be explained. The implementation of the memory and TSVs into the design will be discussed with the help of the used design flow and the needed EDA tools.

- Chapter 4 will describe the design of the serializer and de-serializer [5], together with the implementation into the design. Some solutions to timing problems will be given at the end of this chapter.

- Chapter 5 will describe the design of an asynchronous router using FIFO's, two-flop synchronizers and Gray encoders [7].

- Chapter 6 will describe the performance of two vertically connected asynchronous 3D routers where the data which is flowing in the vertical direction is serialized. Also the timing results will be given for 1 3D router with different serialization ratios.

Chapter 7 includes the concluding remarks and recommendations for future work.

Figure 1.1: 3D NoC with CPU, network interface and 7-port router  $\,$

Background

The design of a complete three dimensional chip is a long and complicated process. For an engineer it is important to divide the design into several manageable parts and decide on how to implement them. Each part can be implemented in a different way, which means that a good balance has to be found between different implementations that suit all the requirements with the lowest cost.

To understand the 3D router design and the choices made here, it is important that some background information is given on this subject. This chapter gives some background information about the implementation of 3D chip design. First the most important parts in 3D chip design will be described, after which a link will be made to the 3D router design. A complete workflow for this design will be given at the end of this chapter.

#### 2.1 Design and Components

This section describes the different implementation parts of 3D IC design and the needed components. First a general description is given on the implementation of IC design. After that the standard cell library, memory and TSV will be discussed. At the end some 3D implementations will be described and compared. This information mainly serves to provide more insight in the complete process of the 3D router design, and to understand why some decisions are made.

#### 2.1.1 IC Design Methodology

An engineer has to decide which technology he wants to use. Whether it be an ASIC (Application-Specific Integrated Circuit) design or a FPGA (Field-programmable gate array) design, a full-custom design or a semi-custom design. This choice will depend on the constraints set before. An ASIC design is highly suitable for designs with a specific function. The 3D router has such a specific function, which makes it perfect for ASIC design. An ASIC design can be full-custom or semi-custom.

A full-custom design is the fastest design, but it is also the most complicated one, and the design time is the longest. In this type of design all of the transistors are shaped and placed by hand. With the access to the transistor design itself, which is the main building block of any digital circuit, a designer has the freedom to chose different layouts for different small circuits, and to chose the most efficient placement. This also means the designer should keep in mind the different design rules. Design rules specify different constraints like minimum-width and minimum-spacing requirements between objects on the same or different layers [4]. The drawback of full-custom design is, that it is time consuming, which translates automatically into high costs. This type of

Figure 2.1: ASIC semi-custom design

design is mainly suitable for specific performance-critical modules which can be reused in different designs. Another important area where full-custom design is used, is for developing standard cells which are used in semi-custom design, or for analog blocks in analog design.

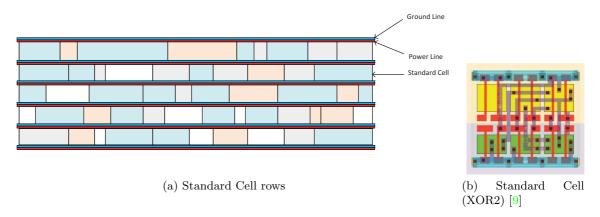

A semi-custom design is another possibility for designing ASIC. There is some performance degradation which can be accepted, while at the other hand the design time is reduced. An semi-custom design consists primarily of standard cells and macro blocks. Standard cells are usually available from different vendors, who make a standard cell library. A standard cell is a cell with a predefined height and adjustable width. This cell consist of a logical gate, i.e. NOR, NAND, INV, DFF, etc. At the top of the cell, there is a power line, where at the bottom of the cell, there is a ground line. The standard cells are made full-custom, to have the best possible characteristics. The designer who is using these standard cells, doesn't have to worry about the inside of the cells. The most important characteristics are the cell delay and power dissipation. These cells are placed in rows, with power lines at the top of the row, and ground lines at the bottom. In Figure 2.1a different rows can be observed with power/ground lines and standard cells. In Figure 2.1b a layout of a XOR2 standard cell can be observed. Because of it's efficient use and good performance, semi-custom design is highly suitable for the 3D router design.

Macro blocks form another important part of a semi-custom design. Using standard cells is attractive for random logic functions, but it's quite inefficient for more complex parts like memory, DSP's, etc. [4]. These parts can be designed in a more efficient way, by using a specific structure that is suitable for it. This ensures the customized implementations will outperform standard cell design by a wide margin. There are two types of macro cells, the hard macro cell and the soft macro.

The hard macro is a module with a given functionality and a predefined physical design [4]. An ASIC designer should not worry about the inside of this block, but only about the input/output characteristics and power consumption, just like with a standard cell. The advantage of a hard macro is, that the design itself is very efficient, and that a block can be reused more times. A disadvantage would be that when a hard

macro is designed for a particular technology, it will only work with that technology. It is very hard to port a hard macro to another technology. An area where a macro block is highly usable is when making a design with a regular structure. Here the same components are used over and over again, and put into a regular structure. A good example of this is a memory block. When designing a memory block, there is a basic building block, which can be extended into a regular structure for a desired memory size. Generators are usually made for this purpose. Such a generator will create a macro block with the help of some input arguments. For example, these arguments can be the desired address size or word size.

The soft macro cell is a module with given functionality, but without specific physical implementation. The placement and wiring will determine the timing of that block, which means that they can change every time a new synthesis and placement&routing is ran. Compared with a hard macro, it has a disadvantage that it doesn't use full-custom design, which is important when using high performing blocks like memories. The advantage is that it's not technology specific, and that it can be ported to other technologies quite easily.

#### 2.1.2 Standard Cell Library

For the logic in the 3D router design, a standard cell library has to be chosen. These libraries are usually designed by IC vendors. They develop their own cells, characterize them, and sell them to other companies for implementation. Libraries are made with the help of a *Process Design Kit (PDK)*. A PDK is a bundle of files which describes different aspects of transistors needed to design standard cells. These files consist of design rules, simulation models for transistors and layout information for transistors. With these files, standard cells can be made, and in the end a complete library of these cells can be constructed.

The case here is, to chose the best possible library which will support the different aspects of the 3D router design. The most important aspect the chosen library should have, is support for 3D design. This means it should have support for TSVs. Another important aspect is that it should be made in a small process technology. The third aspect would be that it is available for free. One Standard Cell Library that was qualified for the above mentioned conditions, was the Nangate Open Cell Library. The purpose of this library is to provide research, testing, and exploring of different EDA flows [10]. The library is generated with the Nangate Library Creator, and the 45 nm FreePDK Base Kit from North Carolina State University (NCSU), and it is characterized with the *Predictive Technology Model (PTM)* from Arizona State University. The only drawback of this library is, that it has not industrial grade performance, because it was generated using a non-optimized Open PDK [10]. This is not a real problem, because the most important aspect of this thesis is to make a functional 3D router design, in real technology, and that it should work. The design flow and the different optimization steps in such a physical implementation are one of the main aspects of this thesis.

The support for 3D design is not directly incorporated into the Nangate Standard Cell Library, but it is supported by the PDK which is used to make this library. This PDK contains the technology library, which supplies tech files, display resources, design

rules and scripts to permit layout design and rule checking for a generic 45 nm process [11]. Because in this design flow primarily the Standard Cell Library will be used, only the relevant part of the PDK will be discussed, which is the TSV implementation.

In Section 2.1.4 some background information on TSV will be given, and different technologies will be discussed, and in the end, a comparison will be made with the one from the NCSU PDK.

#### 2.1.3 Memory

For every input port of the 3D router, a memory block is needed. This memory block will be used as an input buffer. It should obey the different constraints needed for the input buffers, like word depth, and address length. Later on in Chapter 5 it will be explained how this memory can be used to separate two clock domains. The available memory is a 55 nm synchronous, two port register file from Faraday. In section Section 3.3 the exact specs will be given and explained in the context of the complete 3D router design. The model is given in several files. An HDL file, a LEF file and a liberty file are all needed for the simulation, place&route and timing information.

The only problem with this memory block is, that it's based on 55 nm technology, instead of 45 nm technology like the Nangate Standard Cell Library. The reason for using 55 nm technology is because this was the closest available memory technology compared to the 45 nm of the Nangate Standard Cell Library. This was solved by some modifications explained in chapter Chapter 3.

#### 2.1.4 Through Silicon Via

A TSV is a vertical connection which is made into silicon. First a hole is etched into the silicon, and then it's filled with a metal like aluminum, tungsten, wolfram, etc. There are basically three steps which are used for the complete 3D process: via drilling and filling, wafer thinning and backside metallisation [12]. The positive side of TSV's is that it enables vertical interconnections, and allows the stacking of different dies. This enables the reduction of the chip footprint, and at the same time improves the performance due to the vertical interconnections.

To be able to use TSVs in 3D IC design, first a better understanding of the TSV should be obtained. In this section some background information will be given on this subject, like size, used materials, placement, and reliability. At the end a comparison will be given with the TSV model from the NCSU FreePDK, which will be used as a reference design. Later on in chapter Chapter 3 the implementation of the TSV will be discussed, which will be based on the work by R. Jagtap [8].

#### 2.1.4.1 Size

A TSV can have different diameters and different pitch. The smaller the diameter is, the smaller the pitch, and the denser the design. This means also the larger the diameter, the larger the pitch and the more sparse the design. The problem with TSVs is that it cannot shrink the same way like transistors do. This is why TSVs are far bigger than transistors. On of the reasons the TSV cannot be shrunk under a certain

size is if the diameter of a TSV is shrunk, the wafer thickness should also be smaller, because of via filling reasons [12]. [12] states that when using TSV's with the diameter of 10 nm and less, the density can go high as  $10000 \ TSV/mm^2$ . Nevertheless, very small diameter TSVs have been designed where  $4 \ nm$  wide TSV have been patterned with lithography using  $3.2 \ \mu m$  thick photo-resist [13].

A new technology which enables TSVs with a diameter in the order of  $50 \ nm$  is monolithic 3D integration. This technology splits NMOS and PMOS transistors in each standard cell into two device tiers. Thanks to the extremely small size of the inter tier vias, ultra fine-grained vertical integration of devices and interconnects are enabled [14].

#### 2.1.4.2 Placement

The placement of TSVs on a chip determines the reliability and speed. For example, a regular placement of TSVs improves the exposure quality of the lithographic process and therefore improves the yield [15]. On the other end, the *keep-out-zone* (KOZ) is an area outside of the TSV, where no transistor can be because of reliability issues. But because of this, the pitch of the TSV's becomes larger, so does the area which will be covered by TSV's and KOZ. The reliability issues related to KOZ are explained in Section 2.1.4.3. R. Jagtap compares several TSV placement topologies, and states that area and performance wise, the shielded and isolated topologies are preferred [8].

#### 2.1.4.3 Reliability

Reliability is an important aspect in developing TSV's to enable maximum performance and high current demands trough the stacked package. [16] states that there are two critical interfaces on high density TSV with diameters below 10  $\mu m$ . The first one is the transition between TSV and first metal level of Band End of Line (BEoL)—which is a thin metallization having a thickness below 0.25  $\mu m$ . The second one is the transition between TSV and backside redistribution level—a thick metallization of about 1 to 5  $\mu m$ . A thick metal process should be expected to increase the EM robustness, based on current density considerations. This is not the case due to void nucleation occurring right at TiN interface of TSV instead of opposite SiN capping layer. Because of this, any thickness increase of metal level in order to increase the electromigration robustness, should be considered carefully, because of void nucleation interface and void growth.

[17, 18] states that there are three levels of partitioning granularity. There is core level integration, block level integration, gate-level integration and transistor level integration. Current IC technologies support TSV diameters down to 5  $\mu m$ . Alignment precision is very important in stacking tiers.

When using TSV's, there is a redundancy problem. If one TSV fails in a chip, the complete chip stops working, which means such a failure can cause an increase in cost and decreases in yield as the number of dies to be stacked increases [17, 18]. With one redundant TSV allocated to one TSV block, the proposed structure leads to 90% and 95% recovery rates for TSV blocks of size 50 and 25, respectively.

Presently, most 3-D IC processes require each tier to be less than 100  $\mu m$  thick [15]. There is a significant difference in thermal expansion between Copper and Silicon,

which can cause significant stresses at the interface during thermal processing [19, 20]. These thermal stresses can cause mechanical stresses in the channels of the n-MOS and p-MOS devices, which will result in an increase or decrease of the drain current of the MOS devices. Because of this, a KOZ can be formed around the TSV, to minimize this effect. The KOZ for an TSV is defined as an area around the TSV where the variation in the drain current is below a certain threshold. Equation (2.1) shows the connection between the KOZ area and the TSV diameter.

$$\frac{KOZ_1}{KOZ_2} = \left(\frac{\phi_1}{\phi_2}\right)^2 \tag{2.1}$$

When scaling the TSV diameter, the KOZ area reduces quadratically. Because of this, it is very important do reduce the TSV diameter.

[21] used a Bosch-process for making TSV's with a depth of 40  $\mu m$  and a diameter of 5.2  $\mu m$ . If a transistor is placed parallel from the TSV, the effect is enhanced, and if it is placed perpendicular, this effect gets smaller. The KOZ for a large matrix of TSVs is over 200  $\mu m$  for analog circuits and 20  $\mu m$  for digital circuits.

Coefficient of thermal expansion (CTE) mismatch between the conducting metal in TSV and silicon substrate can generate thermal stress inside and around TSVs [22]. For TSV interfacial crack, larger landing pad size is not beneficial. A landing pad is used to connect a TSV to a metal layer in a tier. The smallest defects occur when the TSVs are placed 90°, because the tensile and compressive stress from each aggressor TSV cancels out at the victim TSV location. There is a high angular dependency in a small pitch region. If the pitch exceeds 15  $\mu m$ , angle impact is almost negligible. Array type placement causes the lowest stress. It is best to use block placement in the design. This agrees to the highest degree with the findings of R. Jagtap, where the bundle topology and shielded topology (same as bundle, only with ground TSVs between signal TSVs because of capacitive coupling issues) are chosen as the best one [8].

#### 2.1.4.4 Comparison with NCSU FreePDK TSV

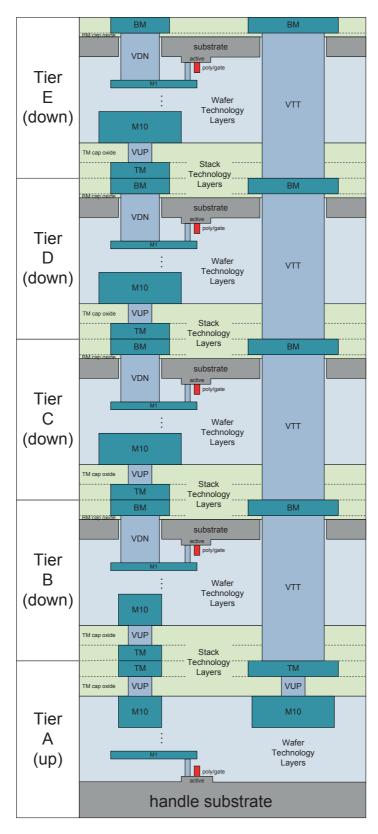

Table 2.1 shows the different dimensions of the metal layers in a tier, which are part of a stacked 3D IC design. This is illustrated in Figure 2.2. In this process, the TSV is created out of different metal layers. All the metal layers stacked on top of each other, will form a vertical connection. Every metal layer has it's own minimum dimensions. But because all these layers are stacked on top of each other, the layer with the largest dimension will determine the dimension of the complete TSV. In this case this dimension pertains to the gate oxide, substrate and back metal, which is 6000 nm or 6  $\mu m$ . Compared with the TSV sizes in Section 2.1.4.1, 6  $\mu m$  is acceptable. Also the TSV size which is used in [8] of 4  $\mu m$  is of comparable magnitude. Only the technology from [13] and [14], which uses TSV's with a diameter of 10 nm and less are far smaller. But these technologies are not suitable for this router design, because of the lack of standard cells which support this kind of implementation.

The material used for the NCSU FreePDK TSV is not important in this design process. The only thing that matters, is that the dimensions of the TSV are known and obeyed. Because of this, the will be no further discussion about the TSV material.

For the placement of TSVs, several topologies can be used. In section Section 2.1.4.3 it is stated that an array type of placement is the most suitable for high reliability. Performance wise this is good enough to be used in this particular design. When using the TSV dimensions from the NCSU FreePDK technology, the operation should be acceptable. Implementing the KOZ shouldn't be a big problem, because of the used placing of TSVs. More details on the TSV and KOZ area will be given in chapter Chapter 6.

Table 2.1: Metal information for 1 tier [1]

| Name               | Pitch (Width/Space) (nm) | Thickness (nm) | Via dimension (nm) |

|--------------------|--------------------------|----------------|--------------------|

| Top Metal          | 1600 (800/800)           | 1000           | -                  |

| TM Cap Oxide       | -                        | 1000           | 800                |

| ILD 9              | -                        | 2000           | 800                |

| Global (9-10)      | 1600 (800/800)           | 2000           | -                  |

| ILD (7-8)          | -                        | 820            | 400                |

| ThinGlobal (7-8)   | 800 (400/400)            | 800            | -                  |

| ILD 4-6            | -                        | 290            | 140                |

| Semi-global        | 280 (140/140)            | 280            | -                  |

| ILD 2-3            | -                        | 120            | 70                 |

| Intermediate (2-3) | 140 (70/70)              | 140            | -                  |

| ILD 1              | -                        | 120            | 65                 |

| Metal 1            | 130 (65/65)              | 130            | -                  |

| Poly-Dielectric    | -                        | 85             | 65                 |

| Poly               | 125 (50/75)              | 85             | -                  |

| Gate Oxide         | -                        | 200            | 6000               |

| Substrate          | -                        | 40000          | 6000               |

| BM Cap Oxide       | -                        | 200            | 6000               |

| Back Metal         | 1600 (800/800)           | 1000           | -                  |

#### 2.1.5 3D Implementation

When having a multi-core design using a NoC as an interconnect, a three dimensional implementation could be very suitable. First a decision has to be made how to implement this 3D technology. As stated in Section 2.1, the use of TSVs is the solution. There are several ways of implementing these vertical interconnections. All of them are based on at what level the TSV will be implemented. A description of the most used implementations is given:

**3D-SIP** [23] The most straightforward solution is to stack different dies on top of each other, and to make the interconnections with bond wire at the peripheral pins. This defined as a 3D system in a package (3D-SIP). The problem with this kind of implementation is that the number of available interconnects (pins) is too low for an complicated and fast design. Because of this reason, this implementation is not used a lot in current designs.

Figure 2.2: Metal Cross-Section Diagram [1]

- **3D-SoC** [23] Another implementation is with the use of internal vertical interconnections. This implementation is based on *Trough Silicon Via (TSV)*, which is an interconnection with low capacity and resistance. The the interconnections are made on block level. Different blocks are interconnected with each other with TSV's and the number of available interconnections is much higher than the 3D-SIP implementation. This implementation is defined as 3D System on a Chip (3D-SoC).

- **3D-IC** [23] 3D interconnection at the lowest level (transistor level) is called 3D-integrated circuit (3D-IC). Here the interconnects are made locally, where the global interconnections stay 2D. In this technology, the number of 3D interconnections per unit area are the highest. This implementation is used only in very high performance designs.

When comparing these different 3D implementations, the 3D-SoC implementation seems to be the most suitable for the 3D router design. A 3D NoC consists primarily of 3D routers which can be seen as blocks, and have those two vertical interconnections made with TSVs. With the 3D-SoC implementation, a mesh of 3D routers (and attached CPU's) can be made, which is shown in Figure 1.1.

#### 2.2 Approach

Now that most components have been described, a way has to be found to combine them, and design a complete digital system, in this case a 3D router. The fact is that there are a lot of different ways to design a complete system, but it is important to find one which will suite a particular design the best possible way and also be developed in an efficient way.

The first thing that has to be decided upon, is the architecture of the system. The architecture can determine for example if the design will be a single-core design or a multi-core design. It can determine if it will be a single clock-cycle design or a multi-clock-cycle design.

Right after this comes the implementation. As stated in previous sections, the implementation is very broad, because a design can be very complex and consists out of several specialized blocks. These block can be digital, analog, low power, high performance, they can be placed on the same die or they can be placed on different dies. The digital system can be improved by extending the architecture, which will use more transistors, which in turn will make the design larger and more complicated. Another way to improve the design is to use multiple cores, and let them communicate with each other. These cores can be similar, or they can be different cores with different functions.

#### 2.2.1 Motivation

The motivation for this type of design comes from several problems that exist in current chips. The first one is the communication problem, where all the communication is done by direct interconnection. This can give some performance overhead. A trend

that can be observed today is that digital systems get multiple cores or many different digital blocks on the same die. This takes up a lot of area, and it is even hard from a technological perspective to make these different blocks on the same die. Also the large amount of complex wiring is causing some problems.

To solve the first problem, a NoC is introduced. A NoC gives support for multi-core designs, and multi-block designs. It enables a network of different cores that all communicate with each other in a efficient way where the large amount of complex wiring is reduced. Also it enables scalability, which enables adding or removing different digital cores and/or blocks. This can be of interest when extending or changing the design.

Because of the many different cores and blocks on a die, the die can get very large. It should be possible to stack the different cores on top of each other. This is made possible with the introduction of TSVs, which are vertical interconnections, and enable the interconnection in three dimensions. In this way, the chip area can be reduced and the communication can be improved because of these fast vertical interconnections.

An advantage of the NoC and 3D integration is that they can work flawlessly together. A NoC is made out of routers, which are connected to each other and to other CPU cores and blocks. If these routers are enhanced by vertical interconnections which enables a design of a three dimensional mesh of routers, so the NoC becomes 3D. As stated above, this in turn will enable the reduction of area size, scalability and speed improvement in the interconnection.

The drawback of this 3D design approach is that every vertical signal needs one TSV. In Section 2.1.4.1 it's explained that a TSV is a lot larger than a transistor, which means the TSVs will occupy a lot of area. The vertical signals needed can go up to a number above 160. It is essential to reduce this number of TSVs. This will be explained in chapter Chapter 4.

When making an asynchronous three dimensional design based on a 3D router, several constraints should be met. These constraints are:

- The NoC should be scalable

- It should work in 3 dimensions

- The power usage should be as low as possible

- The 3D routers should be able to operate in different clock domains

- The number of vertical lines/TSVs should be reduced

#### 2.2.2 Components

Eventually the 3D NoC will consist of the following components:

**3D router** This router will be the heart of the NoC, and will have 7 ports (north, south, east, west, local, up, down). It will be able to make horizontal as vertical connections, and form a 3D connected mesh like in Figure 1.1.

- Serializer The serializer serves to reduce the number of vertical signals which are going through TSVs to another stack, meaning the number of TSVs needed will decrease.

- **De-serializer** The de-serializer serves to recover the serialized signals coming out of he TSVs in another stack, so they can be used in the new 3D router.

- Synchronization Unit The synchronization unit consist of two-flop synchronizers and Gray encoders. It synchronizes the read and write pointers from the FIFO, enabling asynchronous operation of the 3D router.

- **Network Interface** The network interface is the interface which will provide the connection between the CPU and the router through the local port.

- Computational Unit The computational unit can be every type of CPU, DSP, etc. It receives data from the NoC or sends data to the NoC.

In this thesis, only a basic 3D NoC will be made out of two 3D routers, with a serializer and deserializer in between. The network interface will be left out, as well as the computational unit. Instead, this will be simulated with a injector, made in a testbench, which is able to inject flits with different injection rates and injection sizes to various network addresses. A real computational unit combined with a network interface should be able to connect to the 3D router(s), and the design should operate flawlessly.

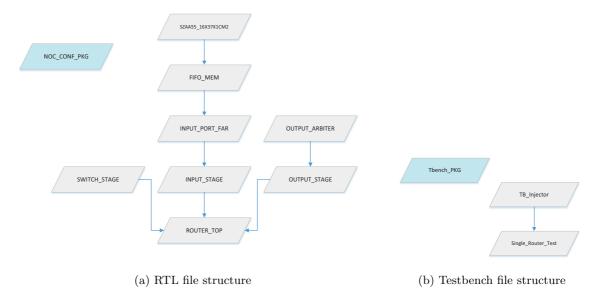

#### 2.3 Workflow

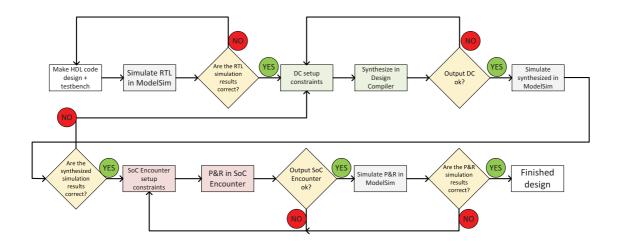

The first thing to do will be the design of the router. A suitable architecture should be chosen for this design which will work well with the rest of the components. Also a serializer/deserializer combination should be included for the reduction of vertical interconnections, together with synchronizers to enable the asynchronous working of the router. Second, TSV's should be designed which can be incorporated into the router design so the up and the down port can be made with it. Third, a design flow should be chosen where this design can be implemented in. For the synthesis Synopsys Design Compiler (DC) is chosen. The main reason for this is, that the current design flow at the faculty already uses this tool. Nonetheless it is highly optimizable and customizable for the designers needs. For placement and routing Cadence Soc Encounter (Encounter) is used, for the same above mentioned reasons. The simulation tool for HDL code is Mentor Graphics ModelSim (ModelSim). In Figure 2.3 a flow chart is given with all the steps in the design process. These steps will be described in the following paragraphs.

#### Step 1: Make HDL code design + testbench

First the logical behavior of the design must be specified in an HDL language. This language can be VHDL or Verilog. This logical behavior is usually described in the RTL level of abstraction, because it's most suitable for clocked designs. A complete design can consist of more sub-designs, and the usual method would be to make separate HDL

codes for each sub-design, and use these sub-designs into other designs higher in the hierarchy. To test this logical behavior of a system, a testbench must be specified. A testbench is basically also a description in HDL which supplies the top-level design with stimulus signals. A good testbench is one which tests all the relevant inputs.

#### Step 2a: Simulate RTL code in ModelSim

To simulate the RTL code, it must be first compiled. The order of compiling must be; first the lowest levels of abstraction, and then the higher levels. The reason for this is, that a higher level code, which uses a lower level code, cannot be compiled before the lower level code is compiled. In a simulator like ModelSim, the testbench is specified which has to be simulated, and different settings can be set. Then the simulation can be run, and the results will appear like waveforms. It can be chosen which input/output signals has to be shown, and which intermediate signals. This type of simulation only simulates the logical behavior. No delays will yet be specified.

#### Step 2b: See if the simulation results of the RTL code are correct

When the simulation is finished, the waveforms of the chosen signals can be studied. Here it can be observed if the logical behavior of the RTL code is correct. If there are signals that are false, or even worse, unknown, the RTL code has to be changed. And the simulation has to be ran again.

#### Step 3: Set DC setup constraints

Now that the RTL code is logically valid, it should be synthesized into design which exist of only the standard cells and macro's from the different libraries. For this a tool is needed like Design Compiler. Design Compiler can be ran in graphical mode, and in batch mode. Batch mode is more efficient, especially because scripts can be used to run the tool. These scripts are written in the TCL language. In these scripts different needed files have to be specified. Also various constraints have to be specified, like clock speed, clock latency, input/output delay, etc. These constraints will determine the final synthesized design.

#### Step 4a: Synthesize in Design Compiler

After all the scrips have been finished, they can be executed, and all the commands with their respectively constraints will be executed. In turn the Design Compiler will map the RTL design on the standard cells and macro's from the available library.

## Step 4b: Look at the output reports from Design Compiler and see if it meets the constraints

Different output reports will be generated by Design Compiler, ranging from the number of gates used, to the amount of area used, to different timing reports that are the most important reports. The timing reports specify the paths between two clocked devices (registers and/or memories) or between the input/output en other clocked devices,

with the largest negative slack. In the scripts, special commands can be given which paths should be put into the timing reports. This is for debug purposes. If the timing is correct, it should be simulated for correction. If not, the constraints should be adjusted or the RTL code should be changed.

#### Step 5a: Simulate synthesized code in Modelsim

This is basically the same step as step 2a, only here the synthesized code is simulated together with a *SDF* (standard delay format) file. The synthesized code is a structural description of the design, with all the standard cells and macro's (memory blocks) connected to each other in the best possible way, for a functional and fastest design. The SDF file contains of delay values for the used standard cells, and the interconnect delays are guessed, because Design Compiler doesn't contain any interconnect information. These delay values are annotated into the synthesized design, and it is simulated.

#### Step 5b: See if the simulation results of the synthesized code are correct

As in step 2b, the waveforms can be seen, only this time with the delay information available. Again, if there are signals that are false, of unknown, something can be wrong with the simulation settings or synthesis settings.

#### Step 6: Set SoC Encounter setup constraints

Now that the synthesized code is valid, it should be placed and routed. Here the real interconnect delay values will be calculated and extracted. For this a tool like SoC Encounter is needed. This tool can also be run in graphical mode, and in batch mode. Also here scripts can be used which are made in the TCL language. Here different commands and constraints are specified which have to be executed. These constraints will determine the final placed and routed design.

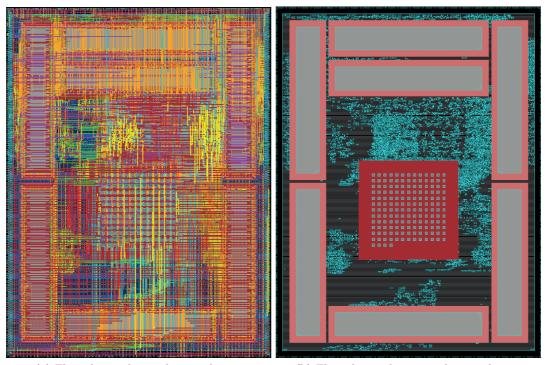

#### Step 7a: Perform place&route in SoC Encounter

Apart of the constraints that have to be specified in the scripts, and various TCL commands, there are some things that have to be done manually. One of these things is the placing of the macro blocks and the inclusion of power rings, lines and stripes. This has to be done in the graphical way. A good thing about it is, that when these things are done the first time, the TCL commands used by encounter to do the placing and the power design can be found and used in a script for future execution. After the execution of the scripts, and eventual manual adjustment of the macro placement and inclusion of the power, SoC Encounter will place all the standard cells and macros into a real die, and interconnect them with signal lines and power lines.

## Step 7b: Look at the output reports from SoC Encounter and see if it meets the constraints

SoC Encounter gives output reports with various information like Design Compiler does in step 4b. The timing reports here are also the most important, because it shows if the design will work at the specified clock speed. If all these reports are satisfactory, it should be simulated for correction. If not, some design constraints or placement has to be changed to meet the specified constraints.

#### Step 8a: Simulate after place&route the final code in ModelSim

Here the simulation of the placed and routed design is done, together with the SDF file. Only this time the SDF file contains real interconnection delays, so this simulation should be the most comprehensive.

#### Step 8b: See if the simulation results of the final code are correct

These results are of a 'real' design, which is placed and routed, and where real delay values are used for simulation. If these simulation results are correct, this design is valid, and can be taped out or used as a macro block for another design.

Figure 2.3: Flow chart of the design steps

3D Router

This chapter describes the basic design of the 3D router, which is the main building block of a 3D NoC. This excludes the serializer/describing and synchronizers, which will be discussed in chapter Chapter 4 and Chapter 5. First a short motivation will be given on the design methodology for the 3D router in Section 3.1. The architecture of the 3D router is described in Section 3.2, followed by the description of the memory and the through silicon via in Section 3.3 and Section 3.4. In Section 3.5 a detailed physical implementation is given of the basic 3D router design.

## 3.1 Motivation

The 3D router is the heart of the 3D NoC. It routes all the signals from source to destination, so all the attached computational units are able to communicate with each other in an efficient way. When designing this 3D router, it is very important that it is suitable for the complete system, which includes the complete 3D NoC and the attached computational units.

This chapter is about the design of the 3D router, using existing technology and tools. The emphasis will be on the implementation of the TSVs, because this is a novelty in the design process. This implementation of the TSVs will not be conventional, in the sense that the end result won't be able to be taped out as a physical chip. The TSV implementation will be based on an abstract representation, which will suffice for synthesis, placement&routing. For real implementation of the TSV, this physical representation can be changed into a real one, but the timing shouldn't change much.

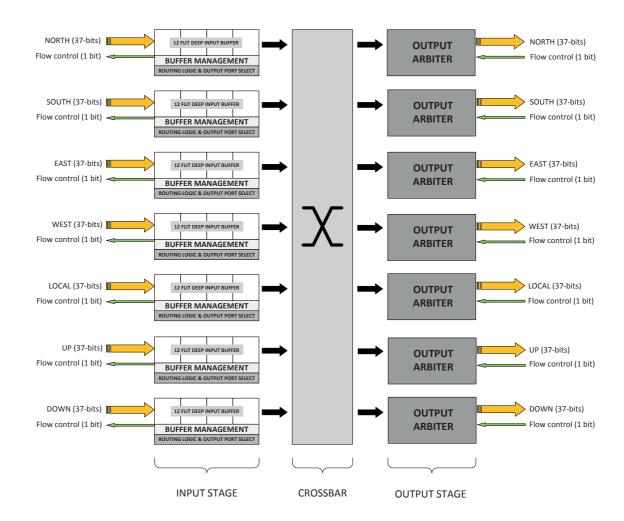

## 3.2 Architecture

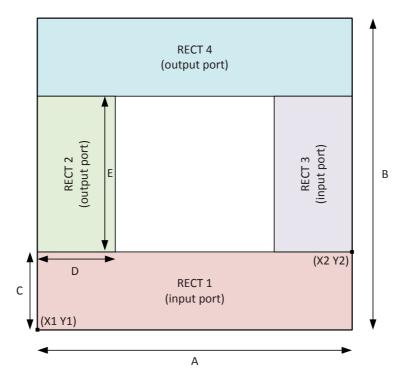

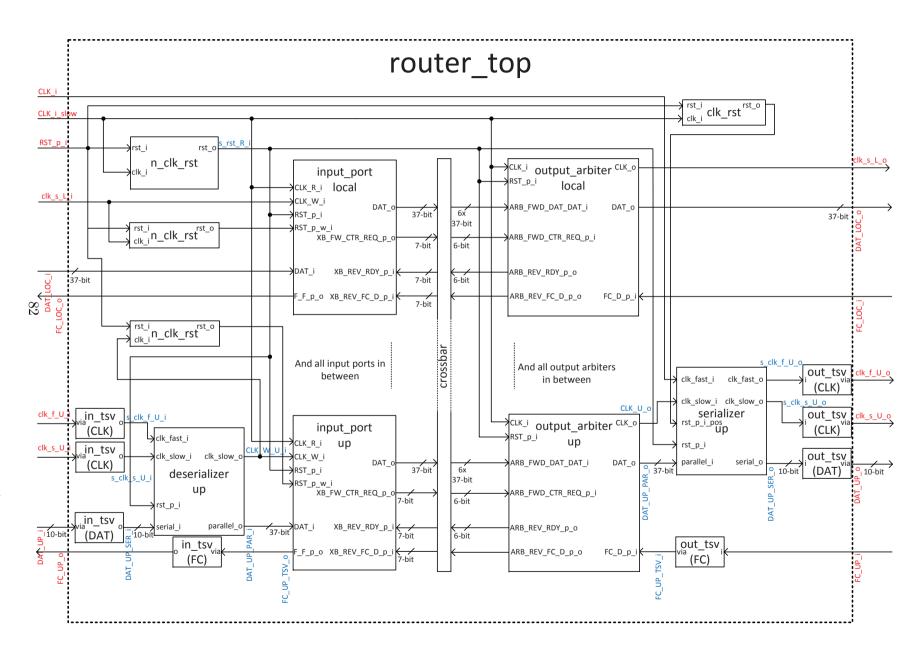

The first step of the router design is to chose a suitable architecture. This architecture should be able to support the specific function of this router, which means it should also be able to work in 3D. The architecture of choice is the input buffered wormhole router which is designed by S. Kumar [6]. This architecture was built initially for a 2D 5-port router with the possibility to extend it to a 3D 7-port router. With small adjustments in the RTL code, the two extra ports (UP and DOWN) were added so a fully functional 3D router was obtained. In this chapter the 7-port router will be discussed, which means the two extra ports will function as vertical interconnects for up and down communication and will be implemented with TSVs. This router is developed in-house at TU Delft as a part of the TMFab project by S. Kumar, so this router is easily obtainable and many documents are available for extra information needed for it's ASIC implementation. The architecture is shown in Figure 3.1, where

all the different components are pointed out, and the input and output signals are shown.

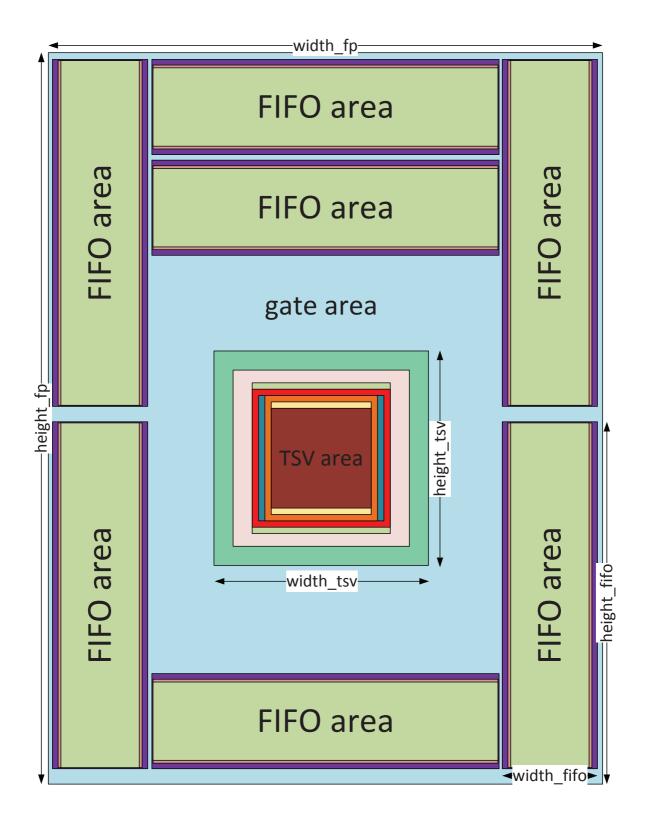

Figure 3.1: Three dimensional 7-port router architecture

The input stage consists of the 7 input ports (each port for one direction), where each input port consists of a input buffer part, buffer management part, and the routing logic&output port select part. The output stage consists of 7 output arbiters (each arbiter for one direction). Between the input stage and output stage, there is a ordinary crossbar which links the input ports with the output arbiters. At each input port, there is a 37-bit wide input signal, and a 1-bit output signal. At each output arbiter, there is a 37-bit wide output signal, and a 1-bit input signal. The 37-bit signals are data bits, and the 1-bit signals are the flow control bits.

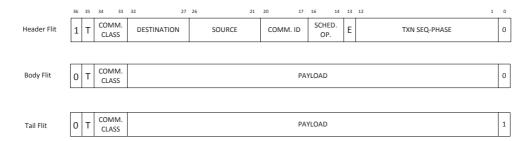

The used architecture uses wormhole routing for routing data packets across the network. These data packets are divided into flits. Each flit consist of 37 bits. That is the reason the complete NoC supports 37-bit input and output links interconnecting nodes. Each flit consists of a header flit, a body flit and a tail flit. The main task of

the header flit is to carry the destination address for the complete packet. The body flit contains the payload data, just like the tail flit, where the tail flit is the last one, and marks the end of the packet. This division of flit types enables the data to be send flit by flit, without waiting for each other at each node. This means first the header flit is routed across the different routers, where all the other flits simply follow the header. Because there is no waiting for other flits at each node, this improves the routing time significantly. The different flits are specified in Figure 3.2.

Figure 3.2: Packet Format

Each tile has a unique *Local Network Address*, where a tile consists of a router and a computational unit which is connected to the local port of the router using a network interface. This address serves to identify each tile. When a header flit arrives at a router, and it's destination address matches the local network address of the tile, this flit together with the other flits are transferred to this particular router and its computational unit, where further processing is performed.

Network packets may contain up to 64 bytes of payload data. This payload data is transferred as 37-bit flits, where each flit contains 4 bytes of the payload data. This means a network packet can be at most 17 flits long (16 flits for the payload and 1 header flit).

The routing algorithm used in this three dimensional router is based on Z-X-Y routing, which means the data is first routed in the Z direction, and subsequently in the X and Y direction. This ensures that the packets injected into the network are transferred directly to their destination layer through the TSVs, which will reduce the congestion in the layer meshes. In the end, this algorithm prevents the incoming packets from being routed through the same port as where they were received at.

In this architecture each packet is routed independently through the network, so it eliminates the need for a connection set up. If a packet is injected into the network, eventually it will reach its destination flit by flit. There are also situations when a link at a router is busy, so a flit has to wait at that router. And when that link is free, it can be processed to the next router. In the mean time this flit has to be put in some kind of buffer. The buffer has a certain pre-specified size, which means only a limited number of flits can be stored there and eventually it can fill up. When this happens, the occupation of the input buffer should get under a certain threshold before processing next flits through this particular input port. For this purpose there is a flow control mechanism which ensures that flits are never dropped, thereby eliminating the need for retransmission. This is implemented by a flow control bit, which gets high when the occupation of the downstream input port buffer gets to a specified threshold value.

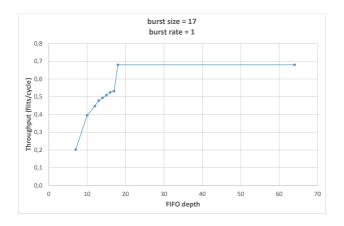

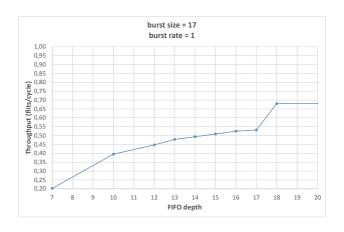

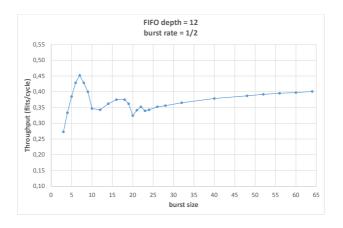

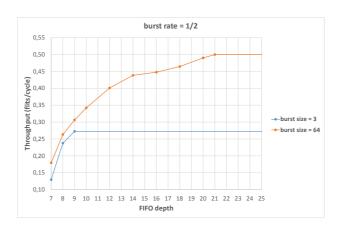

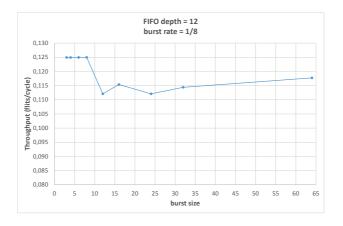

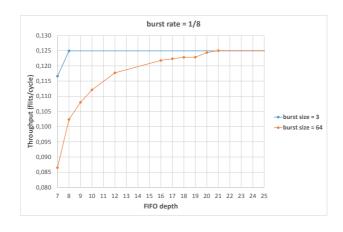

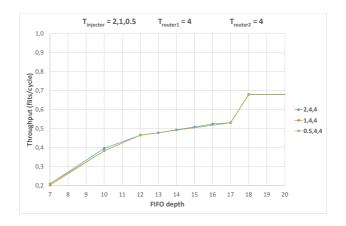

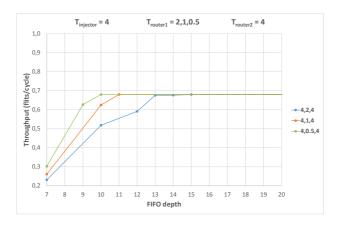

This value is computed by N-2. In this particular router the value of N is 12. N is the number of input buffer slots each 37-bits wide, which means in every slot, 1 flit can be put. The value of N is determined from simulations by examining the variation in average end-to-end latency and throughput with increasing input buffer depth [6]. In Section 6.1.2 the FIFO depth will be changed to test it's influence on the throughput of two routers connected to each other. The pipelined nature of the router induces a two-cycle latency for transmission stalls in the event of congestion at a downstream router.

The output arbiters use a *Round Robin* arbitration scheme, which ensures fair and best effort service to all input ports. Because the routing algorithm prevents the packets being routed the same port they arrived at, each output arbiter will poll only 6 of the inputs. When a header flit arrives at the input port, the Routing Logic & Output Port Select part raises a request to the appropriate output arbiter. If the requested output port is idle, and the downstream input port has free input buffers left, the arbiter grants the request by asserting the Drain signal for the input buffer. After this, the round robin arbitration is deactivated until the tail flit is passed through the output port. Hereby the integration of the routed packets is ensured, and it prevents the flits from other packets mixing in the output stream.

Subsequently the input port waits for access to the output port, which means keeping its request lines asserted and input buffers stalled. If the input buffers become empty while flits are advancing through the router, the output arbiter sets the link as idle while maintaining the round robin arbitration in the deactivated state. This state holds until the tail flit has advanced and the complete packet has been routed. After completion, the arbiter asserts the Next signal and resumes round robin arbitration to service the next waiting input stream.

This type of router has a minimum fall through latency of four cycles.

# 3.3 Memory

First the input buffer should be implemented by a real memory block. For this the 55 nm synchronous, two port register file from Faraday is chosen, as stated in Section 2.1.3. The specifications are given in Table 3.1. In the router design, it is determined that each input buffer should be at least 12 flits deep and 37 bits wide [6]. This means the memory should be 12 words deep and 37 bits wide. The number of words is determined by the address length, as seen in (3.1), where W is the number of words and A the address length.

$$W = 2^A \tag{3.1}$$

Because the number of words can only be a power of two, a value of 16 is chosen, where 4 words will stay unused. The word width is exactly the same as specified in the architecture. For testing purposes, memory blocks with different word depths will be used in Chapter 6.

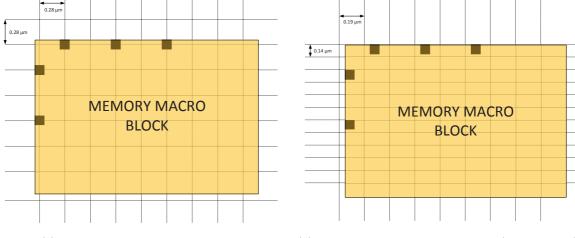

The problem with this memory block is that it is made in the 55 nm technology instead of the 45 nm technology used by the Nangate standard cells. Some adjustments should be made in the LEF file, which describes the physical properties of the block in

Table 3.1: Memory block specifications

| Physical length       | $226.8~\mu m$        |

|-----------------------|----------------------|

| Physical width        | $36 \ \mu m$         |

| Number of words       | 16                   |

| Bits per word         | 37                   |

| Address length        | 4                    |

| Write cycle time (WC) | 1.25  ns             |

| Write cycle time (BC) | $0.49~\mathrm{ns}$   |

| Read cycle time (WC)  | $1.25 \mathrm{\ ns}$ |

| Read cycle time (BC)  | $0.49~\mathrm{ns}$   |

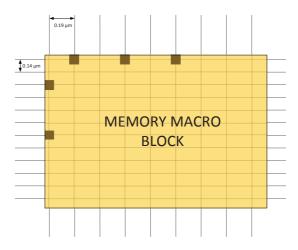

an abstract way. It is important to explain that all the cells, blocks and routing layers sit on an grid. Every technology has it's own grid, which means the Nangate library and Faraday library use different grids. The Faraday routing grid is 0.28 micron in both the X and Y direction, where the Nangate routing grid is 0.19 micron in the X direction and 0.14 micron in the Y direction. Because this is an ASIC semi-custom design, it means only abstract descriptions are used for the different blocks and cells. In this particular case it means that the coordinates of the memory pins should be adjusted in such a way that they align with the same grid as the Nangate standard cells. After this is done, all the blocks and cells including the memory can be routed. This doesn't mean that it's sufficient for fabrication, because the transistors in the memory block are still in 55 nm technology. This adjustment is only meant to enable the routing of the memory blocks in the place&route tool. In Figure 3.3 three memory blocks are given on a specified grid. Figure 3.3a describes the original situation where the memory block sits on a Faraday routing grid, which means all the pins are on the grid. Figure 3.3b describes the non-adjusted memory block sitting in a Nangate routing grid, where the pins are not sitting on the grid. Figure 3.3c shows the adjusted memory block for the Nangate routing grid where the pins are perfectly snapped on the grid. The adjustment of the memory pin coordinates is done by hand.

# 3.4 Through Silicon Via

The TSV is the component which enables the vertical ports of the router. In Section 2.1.4 some background information is given about the technology needed for TSV design. At the end of that section, the available TSV technology from the NCSU FreePDK library is discussed. This section will focus on the implementation of the TSV using the findings of R. Jagtap [8]. Because the TSV dimensions from the NCSU FreePDK library are comparable with the TSV dimensions in [8], and a lot of information is given about the timing and placement of TSVs, these findings will be used for the implementation and calculation of TSVs in this thesis.

First the implementation of this technology into the design flow will be discussed, where the TSV should be designed in such a way, that it can be implemented by the tools into the design. Subsequently the placement of the TSVs will be discussed in the

(a) Memory block on a Faraday grid

(b) Memory block on a Nangate grid (non-adjusted)

(c) Memory block on a Nangate grid (adjusted)

Figure 3.3: Memory block grid adjustment

router design.

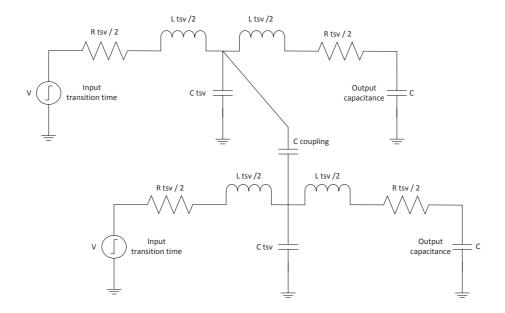

## 3.4.1 TSV Design

First the TSV has to be designed, which later can be incorporated into the router design. In Section 2.1.4.4 the technology from the NCSU FreePDK3D45 PDK is explained, and together with the findings from [8] they form a good foundation which the TSV design will be based on. The NCSU FreePDK3D45 PDK is a design kit compiler for stacked dies (i.e. 3D-ICs) in a predictive 45 nm technology [24]. This kit contains the basics of what is needed to perform schematic entry, SPICE simulation, layout, DRC, and LVS checks. The design flow assumes a stackup like in [1]. Because in this design the most important aspect is the timing and floorplan analysis, the TSV can be made in a more abstract way, so all these files from the PDK are not really needed. The

only thing of importance here is that the TSV area specifications are comparable with the PDK. So when a future designer wants to use all the PDK files, the synthesis and place&route step can be done without large modifications. It is chosen to design the TSV in an abstract way, and to incorporate the timing information from R. Jagtap [8]. In this design process, first the specifications of the TSV need to be pointed out. The specification which is important for this design is basically the diameter of the TSV. The diameter is 4  $\mu m$ , which is the used diameter for the TSVs of R. Jagtap. This means that this will be the constraint that will be used in the TSV design. The files that are needed for the design are listed as follows:

- An HDL description, which is needed by the synthesis for determining the logical functionality and connection

- LEF file, which is needed by the place&route for determining its physical form and layout

- Timing information, which is needed for timing simulation

### 3.4.1.1 TSV HDL Description

For a TSV to be used, it should somehow be incorporated into the complete router design. This means that it should be modeled in a HDL. Because a TSV is not an ordinary component with an input and output port, a special construction has to be made which describes the behavior of the TSV. A current component which comes to mind with similar properties, is the chip pad. A chip pad is also a stack of metals, which can be used as an input or output to the outside world. In this sense, the TSV is the same thing, only in this case the outside world is the other stack (UP or DOWN) to which this TSV will be connected to.

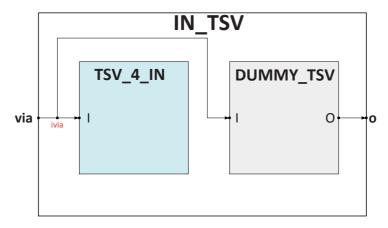

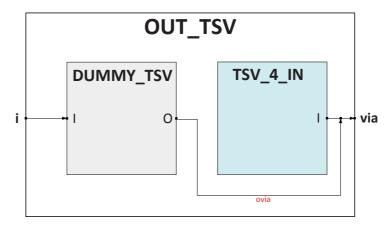

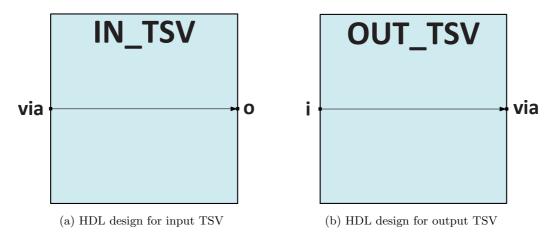

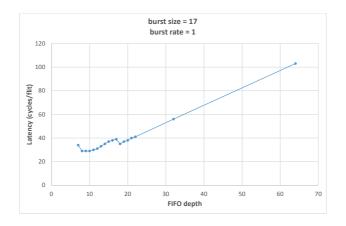

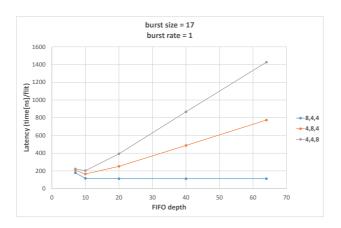

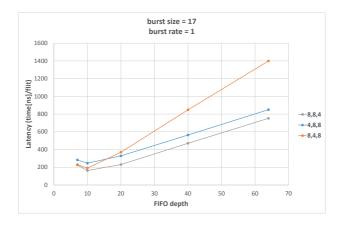

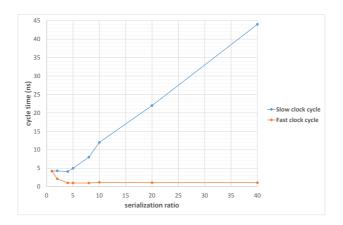

This HDL description is needed for simulation purposes, and for synthesis and place&route purposes. For simulation purposes it is necessary that the TSV is connected to the vertical input and output ports of the router. This means that a vertical output signal from the router should go into a TSV, which in turn means the TSV should have an input port. But at simulation, this output port should be read out from the TSV, so the TSV should have also an output port.