# Carrier-based Generalized Discontinuous PWM Strategy for Single-Phase Three-Legs **Active Power Decoupling Converters**

Xu, Junzhong; Soeiro, Thiago Batista; Gao, Fei; Tang, Houjun; Bauer, Pavol

DOI

10.1109/TIE.2020.3038099

**Publication date**

**Document Version** Accepted author manuscript

Published in

IEEE Transactions on Industrial Electronics

Citation (APA)

Xu, J., Soeiro, T. B., Gao, F., Tang, H., & Bauer, P. (2021). Carrier-based Generalized Discontinuous PWM Strategy for Single-Phase Three-Legs Active Power Decoupling Converters. *IEEE Transactions on Industrial Electronics*, *68*(11), 11609-11613. Article 9264683. https://doi.org/10.1109/TIE.2020.3038099

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Carrier-based Generalized Discontinuous PWM Strategy for Single-Phase Three-Legs Active Power Decoupling Converters

Junzhong Xu, Student Member, IEEE, Thiago Batista Soeiro, Senior Member, IEEE, Fei Gao, Member, IEEE, Houjun Tang, and Pavol Bauer, Senior Member, IEEE

Abstract—Three-legs active power decoupling converters are widely studied in the single-phase grid-connected systems to enhance the circuit lifetime by creating an alternative path for the typical existing DC-side power pulsating ripple. Therefore, this reduces the requirement of smoothing DC capacitors allowing compact designs even with the implementation of long life metalized film technology. In this paper, to allow enhancement of the system power density by improving power conversion efficiency and thus reducing the requirement of thermal management of the semiconductors, a carrier-based generalized discontinuous PWM strategy is proposed. This method detects the converter AC currents and AC reference voltages to determine the optimum clamped duration in each one of the three bridge-legs, which will minimize the converter overall switching losses. The proposed modulation method is analyzed and validated on a PLECS simulation and a 2kVA single-phase three-legs active power decoupling converter.

Index Terms—Single-phase, active power decoupling (APD), discontinuous pulse width modulation (DPWM).

# I. INTRODUCTION

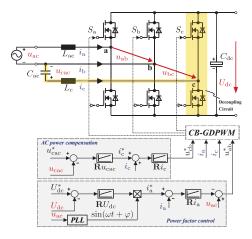

The inherent ripple power in the conventional full-bridge based single-phase AC-DC converter results in an undesirable low-frequency voltage ripple on the DC-link which can degrade the system performance in terms of AC current distortion, and reliability [1]. To address this significant issue, a single-phase three-legs converter operated with an intrinsic active power decoupling (APD) circuit (c.f. Fig. 1) was proposed in [1]-[4]. This comprises the conventional fullbridge AC-DC converter and an auxiliary bridge-leg offering an alternative path for the DC ripple power to flow through additional energy storage components at the AC side. This enables a considerable reduction on the requirement of smoothing electrolytic capacitors on the DC-link [5]-[8]. This particular concept has attracted considerable attention in recent years because when compared to other APD circuits it has reduced components count, lower semiconductor losses, and less current and voltage stresses on the added storage capacitor

Manuscript received July 20, 2020; revised October 09, 2020; accepted October 30, 2020. (Corresponding author: Fei Gao.)

Junzhong Xu, Fei Gao, and Houjun Tang are with the Department of Electrical Engineering, Shanghai Jiao Tong University, Shanghai 200240, China, and also with the Key Laboratory of Control of Power Transmission and Conversion, Ministry of Education, Shanghai 200240, China (e-mail: junzhongxu@sjtu.edu.cn, fei.gao@sjtu.edu.cn, hjtang@sjtu.edu.cn).

Thiago Batista Soeiro and Pavol Bauer are with the Department of Electrical and Computer Engineering, Delft University of Technology, 2628CD Delft, South Holland, The Netherlands (e-mail: T.Batistasoeiro@tudelft.nl, P.Bauer@tudelft.nl).

Fig. 1. Three-legs active power decoupling converter circuit.

$C_{\rm ac}$  [7], [8]. However, as for all other APD circuits, the additional auxiliary power decoupling functionality incorporates extra power losses to the AC-DC converter which will lower the power conversion efficiency when compared to the conventional full-bridge converter.

To relieve this problem, this work proposes a carrierbased generalized discontinuous pulse width modulation (CB-GDPWM) strategy for the single-phase three-legs APD converter. The topology circuit and its corresponding control scheme [5]-[8] are shown in Fig. 1. The proposed algorithm is able to adjust the clamping interval in which the switches of the bridge-legs stop switching based on the instantaneous value of the phase currents and reference voltages. With such a characteristic, the proposed strategy can realize the minimum switching losses action at any instant, thus improving the power efficiency and power density of the system, e.g. by reducing the semiconductor thermal management requirements. It is noted that in the literature available today the modulation strategies studied in the three-legs APD converters are based on the continuous PWM methods, e.g., space-vector PWM (SVPWM) and sinusoidal PWM (SPWM) [5]-[7]. To the best of the authors' knowledge, no literature work has applied discontinuous PWM (DPWM) methods into the single-phase AC-DC converter with APD functionality. Different from the existing DPWM strategies [9]-[12] which are widely studied in balanced and symmetric three-phase three-wire applications, such as in motor drives and grid-tied converters, herein, in a three-legs single-phase AC-DC implementation, the reference voltages seen by each bridge-leg of the system are naturally unbalanced and asymmetrical, and the peak value of the AC current is particularly difficult to predict.

In this paper, the proposed CB-GDPWM strategy is studied

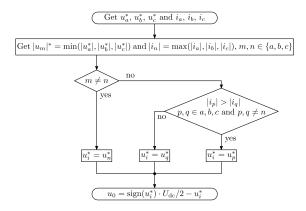

Fig. 2. Flow chat of the proposed CB-GDPWM to decide the zero-sequence signal of the modulation waveform.

and compared with the SVPWM [5] and the classical DPWM method, i.e., DPWM1, which is initially proposed for the three-phase balanced system in [9]. The benchmarking is carried out considering power conversion efficiency, DC rms current value, and AC current total harmonic distortion (THD), using both PLECS based simulation and experiments in a 2 kVA single-phase three-legs APD converter. Herein, to verify the practicability of the proposed method the circuit is operated as a rectifier, processing active and reactive power, and solely processing reactive power in STATCOM mode.

### II. Working Principle of The Proposed Method

The proposed CB-GDPWM is based on the general control structure with power factor control and AC power compensation [5], [6], where the magnitude and phase of the voltage across the added capacitor  $C_{\rm ac}$  ( $u_{\rm cac}^*$ ), as  $U_{\rm cac}$  and  $\theta_{\rm cac}$ , are determined by (1) - (4) [5], so the APD circuit is able to absorb the double-frequency ripple across the DC-bus:

$$U_{\rm cac} = \sqrt{P_{\rm ab\_2\omega} \left(\frac{1}{\omega C_{ac}} - \omega L_c\right)} \tag{1}$$

$$\theta_{\rm cac} = 0.5\varphi_{\rm ab} \tag{2}$$

$$P_{{\rm ab}\_2\omega} = \sqrt{(U_{\rm ac}I_{\rm a})^2 + (\omega L_{\rm ac}I_{\rm a}^2)^2 + 2\omega L_{\rm ac}U_{\rm ac}I_{\rm a}^3\sin\varphi} \ \ (3)$$

$$\varphi_{ab} = \arctan \frac{-U_{ac}I_{a}\cos\varphi - \omega L_{ac}I_{a}^{2}\sin(2\varphi)}{U_{ac}I_{a}\sin\varphi - \omega L_{ac}I_{a}^{2}\cos(2\varphi)}$$

(4)

herein,  $U_{\rm ac}$  and  $I_{\rm a}$  are the peak value of the grid voltage and current, respectively;  $\omega$  is the grid angular frequency;  $C_{\rm ac}$  is the AC capacitor used as part of the auxiliary energy storage of the power converter;  $L_{\rm ac}$  and  $L_c$  are the inductors which are connected to the phase leg a and c;  $\varphi$  is the phase angle between  $u_{\rm ac}$  and  $i_{\rm a}$ .

The proposed CB-GDPWM modulator depends not only on the converter reference line-to-line voltages  $(u_{ab}^*$  and  $u_{cb}^*$ ) but also on the phase currents passing through the converter  $(i_{\rm a},i_{\rm c},$  and  $i_{\rm b}=-i_{\rm a}-i_{\rm c})$ . Firstly, the converter reference voltages  $(u_{\rm a}^*,u_{\rm b}^*,$  and  $u_{\rm c}^*)$  can be determined by:

$$\begin{cases} u_{\rm a}^* = u_{\rm a}^+ + u_{\rm a}^- = \frac{2u_{ab}^* - u_{cb}^*}{3} \\ u_{\rm b}^* = u_{\rm b}^+ + u_{\rm b}^- = \frac{-u_{ab}^* - u_{cb}^*}{3} \\ u_{\rm c}^* = u_{\rm c}^+ + u_{\rm c}^- = \frac{-u_{ab}^* + 2u_{cb}^*}{3} \end{cases}$$

(5)

$$u^* + u^* + u^* = 0 ag{6}$$

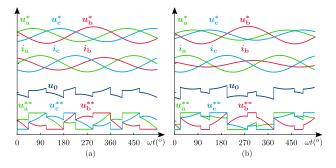

Fig. 3. Simplified illustration of the proposed CB-GDPWM: rectifier mode at (a)  $\varphi=0^\circ$ , and (b)  $\varphi=45^\circ$ .

where,  $u_x^+$  and  $u_x^-$  ( $x \in \{a,b,c\}$ ) are the positive and negative sequence components of each converter reference voltage. Due to the three-phase three-wire system without zero-sequence component, the relation in (6) is still valid. Thereafter, the zero-sequence signal of the modulation waveform can be determined by:

$$u_0 = \text{sign}(u_i^*) \cdot U_{dc}/2 - u_i^* \qquad i \in \{a, b, c\}$$

(7)

where,  $u_i^*$  is the selected reference voltage to be clamped. The principle of  $u_i^*$  selection is illustrated in Fig. 2. If the magnitude of the phase reference voltage with maximum phase current is not lower than the other two phases, this reference voltage is selected as  $u_i^*$ . Otherwise, one of the other phase reference voltages with larger current magnitude is used. Finally, the modulation waveforms  $u_a^{**}$ ,  $u_b^{**}$ , and  $u_c^{**}$  of the CB-GDPWM method are obtained to be compared with the PWM triangular carriers:

$$u_x^{**} = u_x^* + u_0 \qquad x \in \{a, b, c\}.$$

(8)

Fig. 3 shows the simplified illustration of the proposed PWM method in the APD converter operating with different  $\varphi$  in rectifier mode. If the instantaneous value of current is lower when the switching device is acting, the switching loss will also be lower [9]. It is indicated that not only the reference voltages, but also the measured converter currents are important to determine the optimal clamped intervals in the CB-GDPWM strategy. If only the voltage references are used to choose the clamping region as the method proposed in [9], i.e., without the information of the converter current, the obtained DPWM strategy can not achieve the performance of minimum switching losses, because the clamped switches are not always matched with the phase-leg with the maximum current [10]. By using only the measured currents, the phase reference with minimum voltage magnitude and maximum phase current magnitude can be selected, which will cause the problem of over-modulation in another phase and affect the waveform quality.

Therefore, the clamped interval of the proposed method for each phase can be placed around the highest value of the converter current whose corresponding reference voltage is allowed to be clamped. This will lead to an optimal reduction of the semiconductor switching losses.

# III. SIMULATION AND EXPERIMENTAL RESULTS

To verify the effectiveness of the proposed CB-GDPWM, a PLECS based circuit simulation and a 2 kVA single-phase

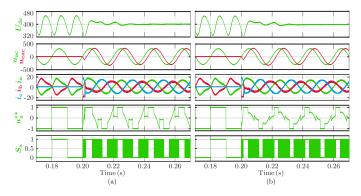

Fig. 4. Simulation results of the transient responses when enabling the active power decoupling at t=0.2 s with: (a) CB-GDPWM (b) DPWM1.

three-legs power conversion system controlled by the Texas Instruments TMS320F28379D based on the Fig. 1 control diagram is designed. In both simulation and experiments, the rms value of the input grid voltage is  $220\,\mathrm{V_{rms}}/50\,\mathrm{Hz}$  (purely sinusoidal without distortion); the output DC voltage is  $400\,\mathrm{V}$ ; the switching frequency  $f_s$  is set as  $40\,\mathrm{kHz}$ ; SiC MOSFETs from Wolfspeed C3M0120090J [13] are used; the grid side inductance is  $L_{\rm ac}=1.44\,\mathrm{mH}$  and that for the AC capacitor side is  $L_{\rm c}=1.15\,\mathrm{mH}$ ; the DC capacitance is  $135\,\mu\mathrm{F}$ ; the AC capacitance is designed to be  $130\,\mu\mathrm{F}$  based on (9), where  $U_{\rm cac(max)}=U_{\rm ac}=220\,\mathrm{V}$ , and  $S_{\rm max}=2\,\mathrm{kVA}$  is the maximum apparent power that the converter is designed to process. Traditional SVPWM and DPWM1 methods are benchmarked in this section, whose zero-sequence signal generation can be found in [5], [8], [9].

$$C_{\rm ac} = \frac{S_{\rm max}}{\omega U_{\rm cac(max)}^2} \tag{9}$$

#### A. Simulation Results

Fig. 4 shows the simulation results of the transient responses when the APD controller is enabled at  $t=0.2\,\mathrm{s}$  with CB-GDPWM and DPWM1 operating at  $\varphi=0^{\mathrm{o}}$ . A resistive load of  $80\,\Omega$  is connected on the DC side, and the total output power at this moment is  $2\,\mathrm{kW}$ . It can be seen that the traditional DPWM methods can also be applied into the three-legs APD converter with proper zero-sequence signal injection. However, the position and length of the clamped time of  $S_{\mathrm{a}}$  for DPWM1 in Fig. 4(b) are different from that for the CB-GDPWM in Fig. 4(a), because the clamped phase of DPWM1 is only decided by the reference signal with the largest voltage magnitude.

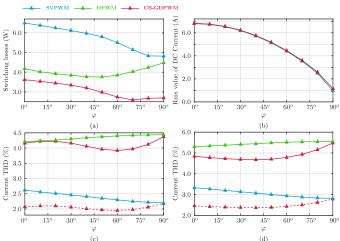

Fig. 5 presents the performance comparison in terms of switching losses, DC current, and AC current THD obtained in the circuit simulation. The apparent power is kept constant by current control loop with the setting up of the grid current rms reference value  $i_{\rm a}$  as 9.09  $A_{\rm rms}$ . In Fig. 5(a), the switching energies for turn-on  $(E_{\rm on})$ , turn-off  $(E_{\rm off})$  and diode reverse-recovery  $(E_{\rm rr})$  from the data-sheet [13] are built into the loss model of the switches in the simulation. As expected, the switching losses for CB-GDPWM is lower than that for SVPWM and DPWM1 over all  $\varphi$  range. Fig. 5(b) shows the influence of different PWM methods on the DC rms current. It can be seen that the obtained values are almost the same,

Fig. 5. Performance comparison of (a) switching losses, (b) DC current, (c) current THD for  $i_a$ , (d) current THD for  $i_c$ .

Fig. 6. Experimental setup.

because DPWM methods do not use another active vectors to replace the zero vectors, hence it results in a low impact on the DC side current ripple [12]. Fig. 5(c) and Fig. 5(d) compare the current THD of  $i_a$  and  $i_c$ , respectively. SVPWM has the lowest current THD value among all PWM methods, while DPWM1 is relatively larger than that for the CB-GDPWM. However, as seen in Fig. 5(a), the CB-GDPWM method is able to reduce nearly 50% of the switching losses in comparison with the SVPWM, which means the  $f_s$  of CB-GDPWM can be doubled under equivalent total system switching losses. As a result, the current THD of the circuit implementing the CB-GDPWM with doubled  $f_s$  [dotted line in Fig. 5(c) and Fig. 5(d)] becomes lower than that for SVPWM.

# B. Experimental Results

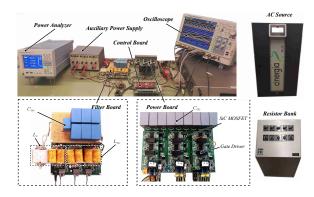

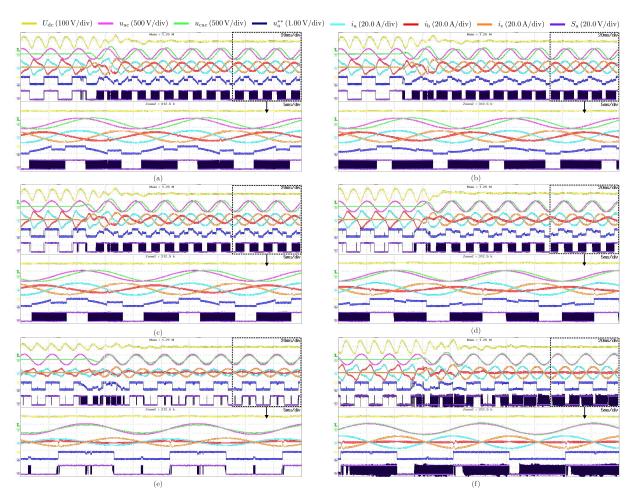

The experimental setup is shown in Fig. 6. The average DC voltage in all experimental cases is controlled at 400V. Fig. 7 shows the experimental results of the converter with the proposed CB-GDPWM working as rectifier and STATCOM cases with the waveforms before and after the APD circuit is enabled to work with an apparent power of  $S_{\rm o}\approx 2\,\rm kVA$ . Fig. 7(a) and Fig. 7(b) are the experimental results for CB-GDPWM and DPWM1 at  $\varphi=0^{\circ}$  with the restive load of  $80\,\Omega$ . Fig. 7(c) and Fig. 7(d) are the experimental results for the CB-GDPWM at  $\varphi=15^{\circ}$  and  $\varphi=45^{\circ}$ , where the resistance of the load is changed to  $83\,\Omega$  and  $113\,\Omega$  respectively to keep

Fig. 7. Experimental results of the APD converter, rectifier mode at  $S_{\rm o}\approx 2\,{\rm kVA}$  with (a) CB-GDPWM,  $\varphi=0^{\circ}$ , (b) DPWM1,  $\varphi=0^{\circ}$ , (c) CB-GDPWM,  $\varphi=15^{\circ}$ , (d) CB-GDPWM,  $\varphi=45^{\circ}$ , and STATCOM mode with (e) CB-GDPWM,  $I_{\rm a}=5A_{\rm rms}$ , (f) CB-GDPWM,  $I_{\rm a}=10A_{\rm rms}$ . Note that the zoom function of the oscilloscope is used to show the details of the highlighted section of the experimental waveforms.

TABLE I

COMPARISON OF THE MEASURED EXPERIMENTAL RESULTS

| Mode             | φ   | PWM   | THD    | $\Delta P$ | Efficiency |

|------------------|-----|-------|--------|------------|------------|

| Rectifier        | 0°  | SVPWM | 2.19 % | 62.9 W     | 96.9 %     |

|                  |     | DPWM1 | 2.92 % | 52.8 W     | 97.4 %     |

|                  |     | GDPWM | 2.74 % | 49.7 W     | 97.6 %     |

|                  | 15° | SVPWM | 2.05 % | 57.2 W     | 97.0 %     |

|                  |     | DPWM1 | 3.12 % | 48.7 W     | 97.5 %     |

|                  |     | GDPWM | 2.96 % | 46.3 W     | 97.6 %     |

|                  | 45° | SVPWM | 1.95 % | 55.9 W     | 96.2 %     |

|                  |     | DPWM1 | 3.38 % | 46.1 W     | 96.8 %     |

|                  |     | GDPWM | 2.52 % | 44.5 W     | 97.0 %     |

| STATCOM<br>@5 A  | 90° | SVPWM | 2.58 % | 32.6 W     | -          |

|                  |     | DPWM1 | 4.07 % | 27.3 W     | -          |

| STATCOM<br>@10 A |     | GDPWM | 3.94 % | 25.1 W     | -          |

|                  | 90° | SVPWM | 1.26 % | 57.3 W     | -          |

|                  |     | DPWM1 | 3.31 % | 53.3 W     | -          |

|                  |     | GDPWM | 2.96 % | 45.6 W     | -          |

$S_{\rm o}\approx 2\,\rm kVA.$  Fig. 7(e) and Fig. 7(f) are the experimental results for STATCOM mode with CB-GDPWM, where  $\varphi$  is fixed at  $90^{\circ}$  with two different settings of output currents,  $5\,A_{\rm rms}$  and  $10\,A_{\rm rms}.$

The results in Fig. 7 demonstrate that the average DC voltage in all cases is stable at 400 V. It can be seen that without the APD circuit, the voltage ripple at the DC-link is particularly high with the implemented 135  $\mu$ F DC capacitor, which comprises a relatively low value of smoothing DC capacitance. This DC voltage ripple deteriorates the performance of the current control loop and the AC side current becomes distorted. By enabling the APD circuit with the AC power compensation components, the ripple in the DC voltage reduces remarkably and the AC current waveform shape improves as well. Note that the proposed CB-GDPWM method can adapt well to the changes of the set phase angle  $\varphi$ , and the switching signal  $S_{\rm a}$  is clamped along different intervals with different duration depending on the currents. The APD converter can also work well in the experiment with DPWM1. As predicted in the simulation, the clamped duration time of  $S_a$  for DPWM1 in Fig. 7(a) is shorter than that for the proposed CB-GDPWM method, and is not around the peek current of  $i_a$ . It is noted that with both studied DPWM methods, it exists a small distortion on  $i_c$  and  $i_b$ , because these methods generate low-frequency harmonic components in  $u_{\rm cb}$  which can be close to the resonance frequency of the AC storage components, i.e.,  $L_c$  and  $C_{\rm ac}$ . This is also

found in balanced three-phase three-wire AC-DC converters as shown in [14], [15]. However, the current distortion in the studied single-phase circuit is confined within the APD circuit and the bridge-leg b, as seen in  $i_c$  and  $i_b$ . Therefore, there is no noticeable distortion to the grid side current  $i_a$  in all experimental cases, as seen in Fig. 7. All experiments verify the feasibility of the proposed CB-GDPWM working with the APD converter and it proves the adaptive character of the proposed modulator.

Table. I shows the power losses and the efficiency of the APD converter working with SVPWM, DPWM1, and the proposed CB-GDPWM for both rectifier and STATCOM modes. The total power losses  $\Delta P = P_{\rm in} - P_{\rm out}$ , current THD, and the power efficiency are measured by the power analyzer YOKO-GAWA WT500. The difference between the real power flowing into the converter and that out of the converter can be regarded as an estimation of the total losses in the converter, including the switching devices and filters. For STATCOM mode, the output active power is zero, thus the measured input active power represents the circuit loss. As shown in Table. I, with DPWM methods, the power efficiency of the converter can be improved remarkably compared to the commonly employed SVPWM method, and the proposed CB-GDPWM is able to further reduce the losses and increase the power efficiency in comparison with DPWM1. Moreover, with the implementation of DPWM methods, the current THD will be increased for all cases. Since only the harmonics components below the 50<sup>th</sup> order are considered in the power analyzer, the measured current THD results are lower than the one obtained from the simulation results in Fig. 5. It can be seen that the current THD for the CB-GDPWM method is generally better than DPWM1, and the difference between CB-GDPWM and SVPWM is relatively small in the experiments. All experimental cases show the reduced power losses with CB-GDPWM based APD converter, which confirms the validity and superiority of the proposed modulation method.

#### IV. CONCLUSION

This work has proposed a CB-GDPWM for a single-phase three-legs active power decoupling converter. The proposed method is based on the detection of the current position relative to the reference AC voltage. This modulator adaptively clamps the switching device that conducts the largest current whose reference voltage can be clamped at any instant, which leads to the optimum clamped duration to obtain a minimum switching losses. The experimental results not only verified the effectiveness of the proposed method, but also showed its superior performance over the conventional SVPWM and DPWM1 studied in the existing literature.

### REFERENCES

- Y. Sun, Y. Liu, M. Su, W. Xiong, and J. Yang, "Review of active power decoupling topologies in single-phase systems," *IEEE Trans. Power Electron.*, vol. 31, no. 7, pp. 4778–4794, 2016.

- [2] W. Qi, S. Li, S. Tan, and S. Y. Hui, "Design considerations for voltage sensorless control of a pfc single-phase rectifier without electrolytic capacitors," *IEEE Trans. Ind. Electron.*, vol. 67, no. 3, pp. 1878–1889, 2020.

- [3] S. Bhowmick and L. Umanand, "Design and analysis of the low device stress active power decoupling for single-phase grid connection for a wide range of power factor," *IEEE J. Emerg. Sel. Topics in Power Electron.*, vol. 6, no. 4, pp. 1921–1931, 2018.

- [4] Y. Liu, Y. Sun, and M. Su, "A control method for bridgeless cuk/sepic pfc rectifier to achieve power decoupling," *IEEE Trans. Ind. Electron.*, vol. 64, no. 9, pp. 7272–7276, 2017.

- [5] R. Chen, Y. Liu, and F. Z. Peng, "Dc capacitor-less inverter for single-phase power conversion with minimum voltage and current stress," *IEEE Trans. Power Electron.*, vol. 30, no. 10, pp. 5499–5507, 2015.

- [6] H. Wu, S. Wong, C. K. Tse, and Q. Chen, "Control and modulation of bidirectional single-phase AC-DC three-phase-leg SPWM converters with active power decoupling and minimal storage capacitance," *IEEE Trans. Power Electron.*, vol. 31, no. 6, pp. 4226–4240, 2016.

- [7] H. Li, K. Zhang, H. Zhao, S. Fan, and J. Xiong, "Active power decoupling for high-power single-phase pwm rectifiers," *IEEE Trans. Power Electron.*, vol. 28, no. 3, pp. 1308–1319, 2013.

- [8] Z. Qin, Y. Tang, P. C. Loh, and F. Blaabjerg, "Benchmark of ac and dc active power decoupling circuits for second-order harmonic mitigation in kilowatt-scale single-phase inverters," *IEEE J. Emerg. Sel. Topics in Power Electron.*, vol. 4, no. 1, pp. 15–25, 2016.

- [9] A. M. Hava, R. J. Kerkman, and T. A. Lipo, "A high-performance generalized discontinuous PWM algorithm," *IEEE Trans. Ind. Appl.*, vol. 34, no. 5, pp. 1059–1071, Sep. 1998.

- [10] T. D. Nguyen, J. Hobraiche, N. Patin, G. Friedrich, and J. P. Vilain, "A direct digital technique implementation of general discontinuous pulse width modulation strategy," *IEEE Trans. Ind. Electron.*, vol. 58, no. 9, pp. 4445–4454, Sep. 2011.

- [11] S. L. An, X. D. Sun, Q. Zhang, Y. R. Zhong, and B. Y. Ren, "Study on the novel generalized discontinuous SVPWM strategies for threephase voltage source inverters," *IEEE Trans. Ind. Inf.*, vol. 9, no. 2, pp. 781–789, May. 2013.

- [12] J. Xu, J. Han, Y. Wang, S. Habib, and H. Tang, "A novel scalar PWM method to reduce leakage current in three-phase two-level transformer-less grid-connected VSIs," *IEEE Trans. Ind. Electron.*, vol. 67, no. 5, pp. 3788–3797, May. 2020.

- [13] Datasheet of C3M0120090J, CREE Power Applications, Durham, NC, USA, Jan. 2018. [Online]. Available: https://www.wolfspeed.com/ media/downloads/834/C3M0120090J.pdf

- [14] C. Vadstrup, X. Wang, and F. Blaabjerg, "Lc-filter resonance cancellation with dpwm inverters in adjustable speed drives," in 2015 IEEE Energy Conversion Congress and Exposition (ECCE), pp. 2208–2214, 2015.

- [15] H. Kim and S. Sul, "Voltage reference modification scheme for resonance suppression in lcl-filtered inverters with discontinuous pwm method," in 2018 International Power Electronics Conference (IPEC-Niigata 2018 ECCE Asia), pp. 521–527, 2018.