## Master of Science Thesis

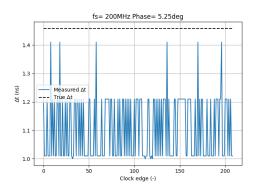

Time of Flight Measurements over Optical Communication Using Field-Programmable Gate Array Multi-Gigabit Transceivers

Tijs Palings

## Master of Science Thesis

#### Time of Flight Measurements over Optical Communication Using Field-Programmable Gate Array Multi-Gigabit Transceivers

by

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on 30th of November 2023.

Student number:4657098Project duration:March 23, 2023 – November 30, 2023Thesis committee:Dr. J. Guo,TU Delft, ChairmanDr. S. Speretta,TU Delft, Daily SupervisorDr. Ir. J. BouwmeesterTU Delft, Examiner

Cover: laser satellite communication concept art by TS2 space

An electronic version of this thesis is available at http://repository.tudelft.nl/.

## Preface

This thesis report represents the final deliverable in order to obtain a Master of Science Degree in Aerospace Engineering with as specialization Space Engineering at Delft University of Technology. The reports contains the design, tests and analysis of several optical communication systems. They concern systems built with a field-programmable gate array (FPGA) for communication and signal processing and acquisition. These systems aim to incrementally increase in complexity such that limits can be identified as the thesis progresses and points of improvement can be implemented or identified.

It is the culmination of over 6 years worth of material and skills acquired at the TU Delft. Before the thesis I had little to no practical experience with FPGAs, printed circuit boards or laser communication for that matter. But with the set of skills I've managed to acquire over the years, I've stepped out of my comfort zone and approached the problem head on from the beginning. I was a bit overwhelmed at first, but managed to break down the problem to tackle it bit by bit. Which is what a good engineer should be able to do in my opinion, and I feel like I've managed to do exactly that in this thesis.

I would like to thank my dad for always supporting me whenever and wherever I needed, Marceline for all the support and kindness she provided me day and night, making the sun shine just a little brighter.

A special thanks to TNO for finding time to let us do measurements with their test setup in Scheveningen.

Most of all I would like to thank Stefano Speretta and Rashika Jain for their critical feedback, the weekly meetings and their time and effort they put in me and my work during the thesis. I genuinely enjoyed the collaboration and appreciate the opportunity you have provided to me. I'd approached you with the wish to do a more practical thesis and practical it was. Thank you for the opportunity.

Tijs Palings Delft, November 2023

## Summary

Since the early '80s, continuous efforts to realize laser communication for deep-space communication began. Due to the immature and inefficient nature of these then-new technologies, they were barely implemented. Despite this, researchers and engineers recognized their potential, leading to a surge in research activity over the years. This effort has since yielded significant progress in satellite communications, with some systems proven in flight.

Laser communication systems achieve orders of magnitude higher data rates compared to their Radio Frequency (RF) counterpart, while being more compact and requiring less power to function [1] [2]–[4]. These high data rates are necessary for modern, data-heavy systems in deep space, such as synthetic aperture radar, multispectral/hyperspectral imaging, and high-definition video transmission [5]. These systems require between 1 Mbps and 1 Gbps for acceptable operations [5].

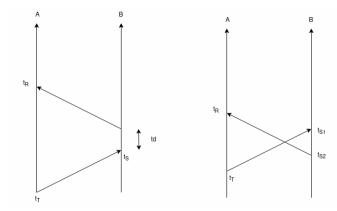

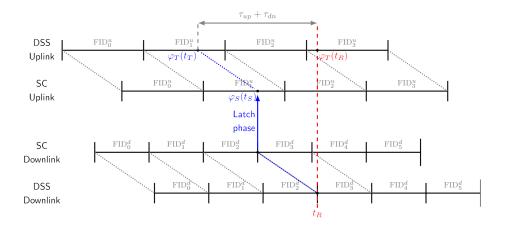

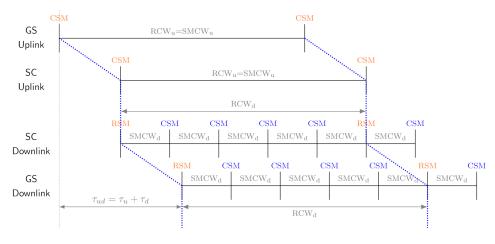

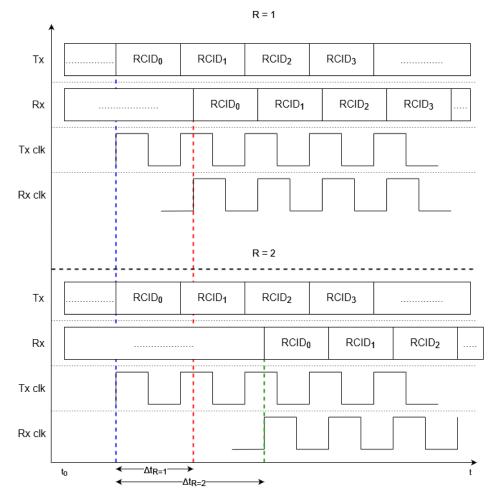

Part of the communication subsystem is performing range measurements for orbital determination. Normally this is done using multiple RF frequencies, where a dedicated ranging signal is sent for a period of time, in which several range measurements are obtained. This means that the normal data stream is set to a halt for the duration of this period. For optical systems of the other hand this is not the case. The necessary information required to perform range measurements can be embedded into the normal data structure [6] instead.

In terms of optical communication, there exist Commercial Off-The-Shelf (COTS) components that are often used in networking that could be used to mimic, test and parameterize satellite laser communication. With the use of an Field Programmable Gate Array (FPGA), its on-board Multi-Gigabit Transceiver (MGT) and Small Form-factor Pluggable (SFP) modules, a satellite laser communication system can be reconstructed of which the performance can be parameterized that are comparable to what would be achievable in orbit. Furthermore it provides the opportunity to research constraints, outside influences and parameters that influence the accuracy and precision of such systems. This thesis aims to study these exact features by incrementally increasing complexity, starting from a relatively basic system to a more complex system that fully embeds optical communication, identifying limits and constraints as complexity increases.

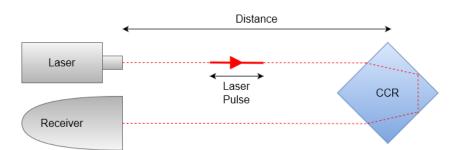

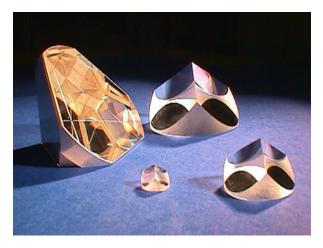

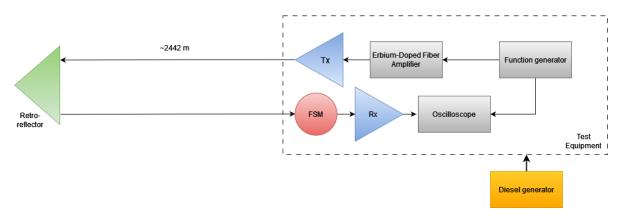

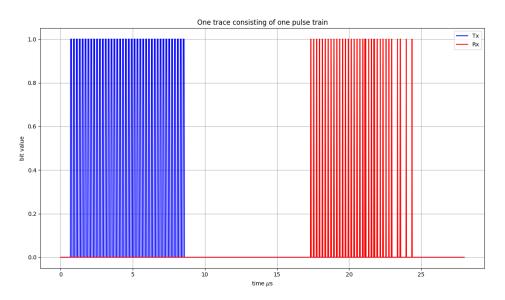

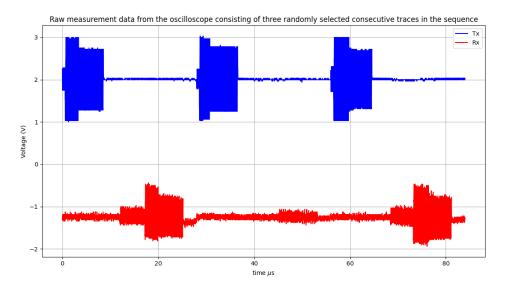

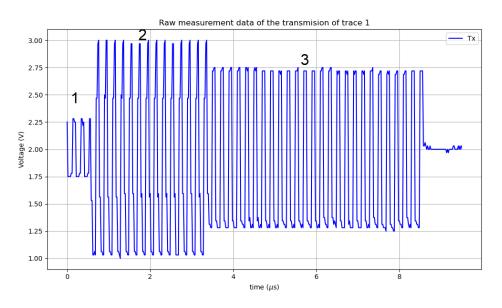

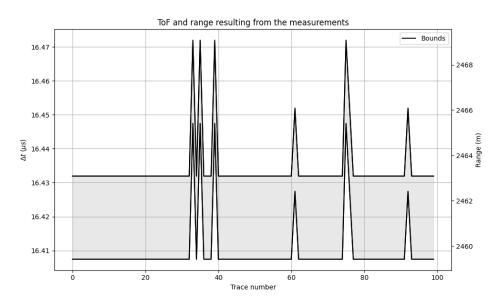

To start, a free-space laser ranging experiment is conducted with a test setup provided by and in collaboration with Toegepast-Natuurwetenschappelijk Onderzoek (TNO). It is important to conduct this experiment as it shows the effects of free-space on the Signal to Noise Ratio (SNR) and what could be expected when performing range measurements though an atmosphere. This is a passive laser ranging experiment as no real communication is involved, rather a set of 40 pulses lasting a total of 8 µs is transmitted towards a retro-reflector. The reflection is captured and based on the time of arrival and the time of transmission, the Time of Flight (ToF) can be measured. The retro-reflector is located at a distance of roughly 2442 m from the transmitter and receiver. From the ToF measurements a distance between 2459.73 m and 2463 m were observed, the standard deviation of these measurements was 1.26 m and a measurement uncertainty of 6 m. For this test, there was no time for proper calibration, hence the large residual on the range measurement.

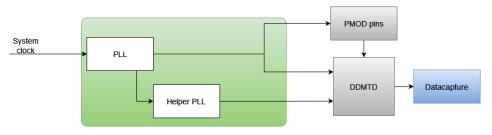

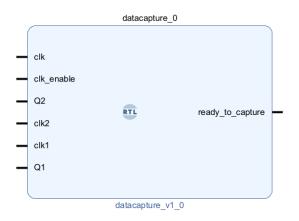

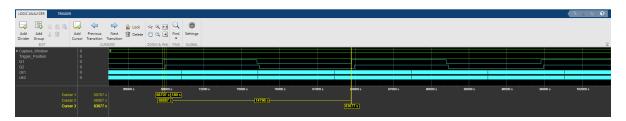

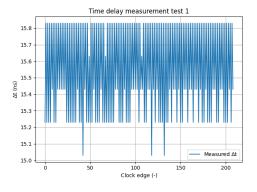

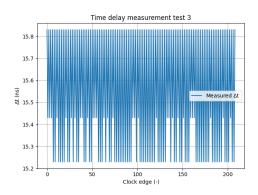

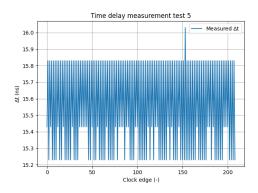

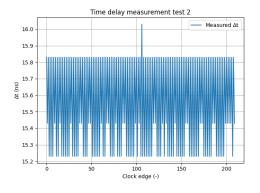

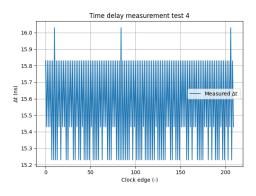

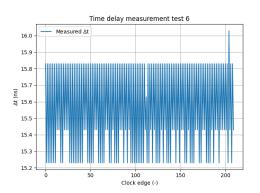

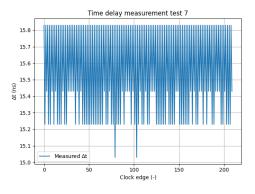

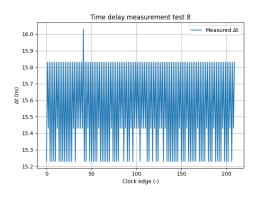

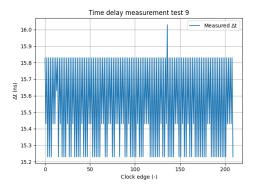

This test demonstrated the basic constraints in retrieving a range measurement. As no communication is embedded, the accuracy depends mainly on the accuracy by which the time of arrival and transmission of photons can be registered. To improve this measurement accuracy, an FPGA was programmed that is capable of much higher transmission speeds and sampling frequencies. The first constraint from the previous test however is tackled by conducting a calibration of the internal delay of the system. An internal delay of 15.83 ns was measured with a standard deviation of 275.5 ps with the use of Digital Dual Mixer Time Difference (DDMTD). This is remarkable, as this allows for a significantly higher measurement resolution of 0.01 ns, compared to the 5 ns sampling period. During the execution of the test, it could quickly be concluded that these values do not accurately represent the internal delay of the MGT.

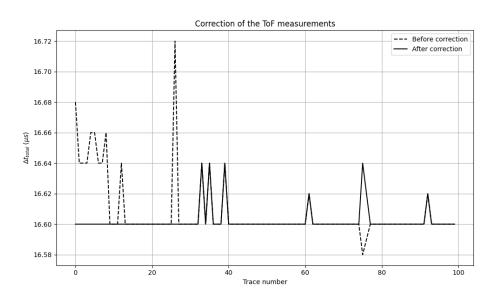

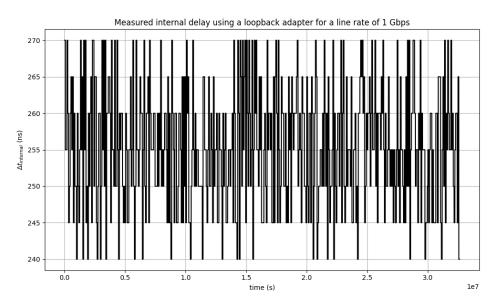

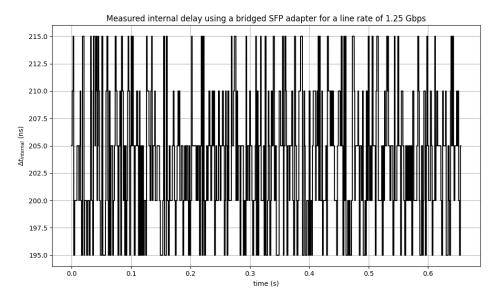

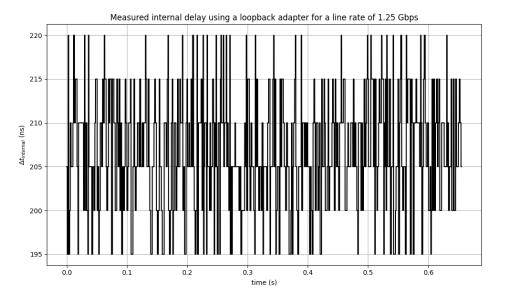

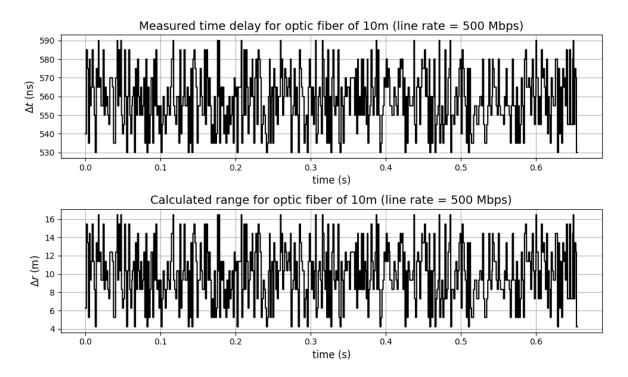

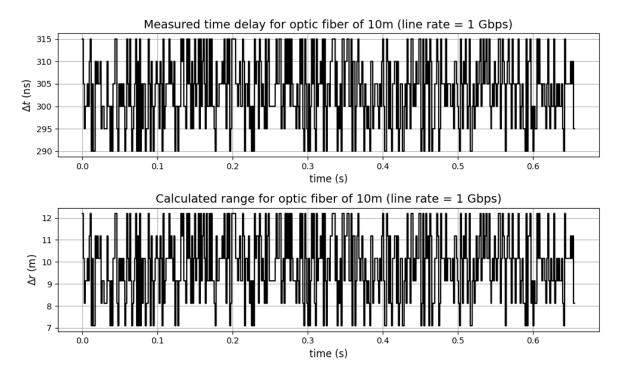

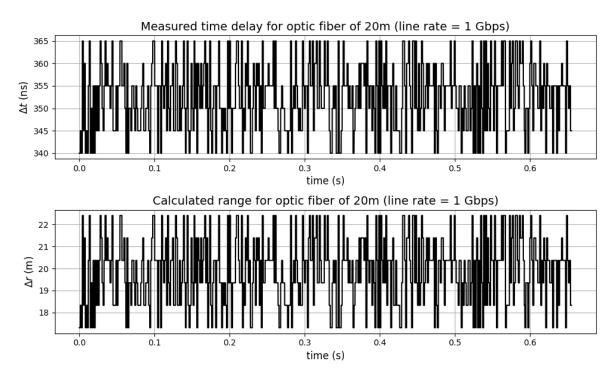

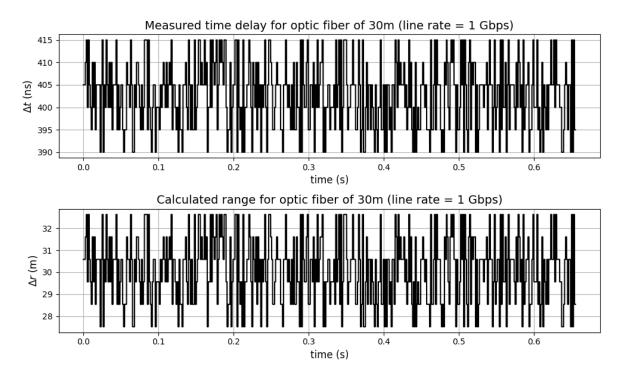

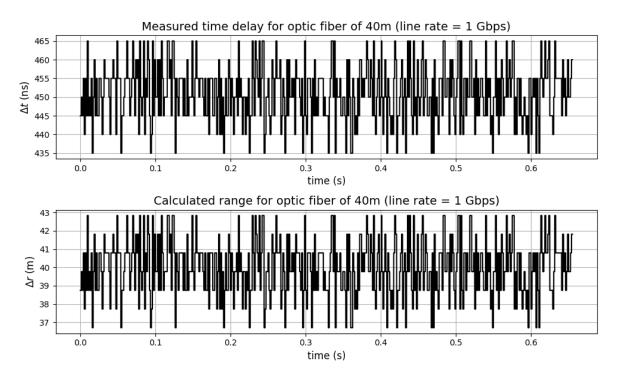

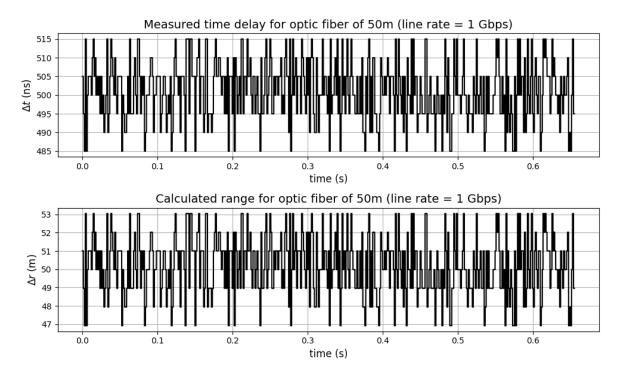

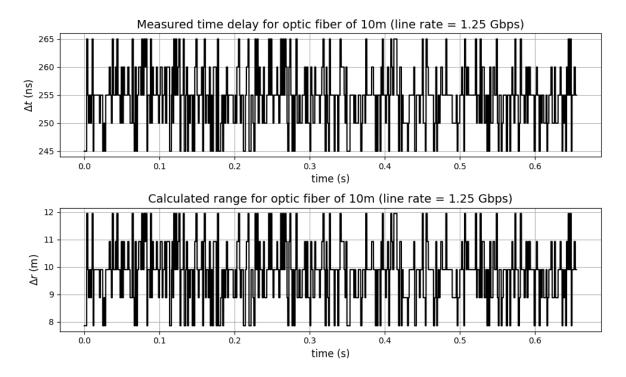

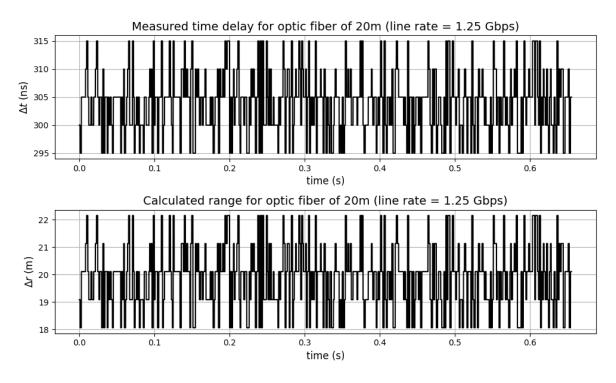

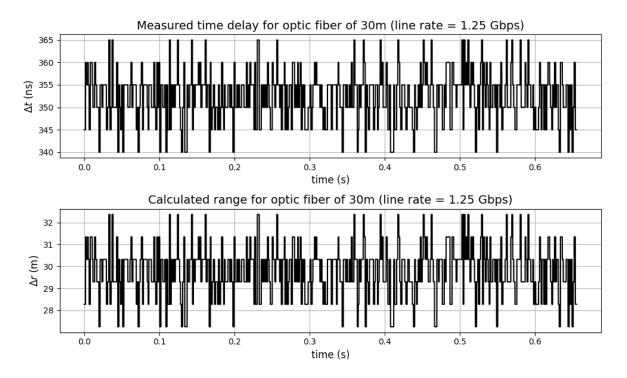

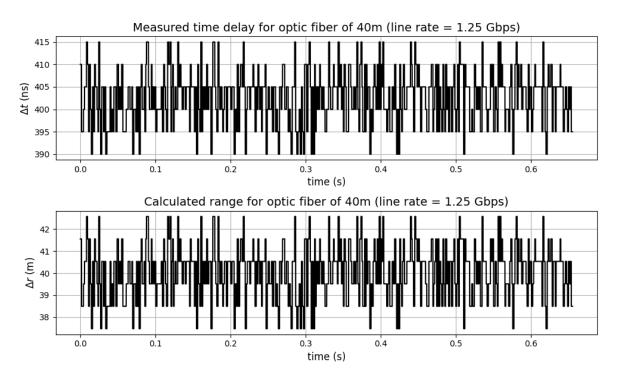

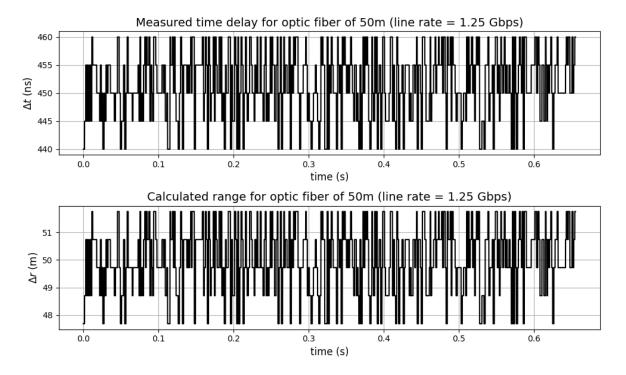

Although the General Purpose Input Output (GPIO) from the previous experiment has proven to be stable and easy to control, the experiment that follows must include the MGT firmware. Thus the next steps are aimed at quantifying the internal delay caused by the MGT as well as perform range measurements on optic fiber cables with the use of FPGA transceivers. It was shown that the internal delay of the MGT was not constant, rather it consists of a deterministic and stochastic part, due to a bug embedded in the firmware. Due to the time limits imposed on the thesis, the bug could not be resolved in time. Nonetheless it could be quantified and it was determined that it is dependent on the line rate of the FPGA. Range measurements are conducted in 5 different optic fiber lengths, with three different line rates. The results of these tests are displayed in table 1.

| r <sub>target</sub> (m | n) µ(m)<br>@ 500<br>Mbps | μ (m)<br>@ 1<br>Gbps | μ (m)<br>@ 1.25<br>Gbps | <sup>♂</sup> fiber<br>(m) @<br>500<br>Mbps | <sup>σ</sup> fiber<br>(m)<br>@ 1<br>Gbps | <sup>♂</sup> fiber<br>(m) @<br>1.25<br>Gbsp | σ(ns)<br>@ 500<br>Mbps | σ (ns)<br>@ 1<br>Gbps | σ (ns)<br>@ 1.25<br>Gbps |

|------------------------|--------------------------|----------------------|-------------------------|--------------------------------------------|------------------------------------------|---------------------------------------------|------------------------|-----------------------|--------------------------|

| 10                     | 9.927                    | 8.758                | 9.804                   | 3.228                                      | 1.591                                    | 1.146                                       | 15.804                 | 7.791                 | 5.611                    |

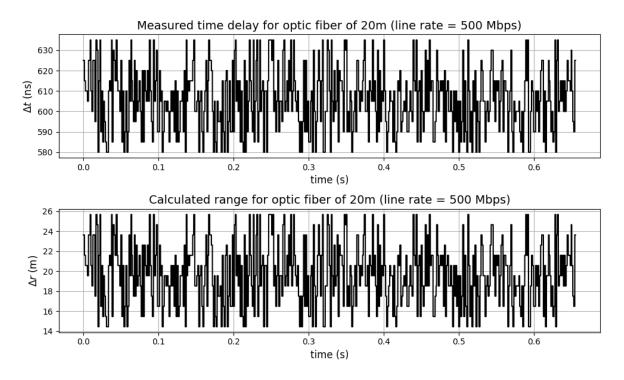

| 20                     | 19.652                   | 18.802               | 19.891                  | 3.199                                      | 1.588                                    | 1.203                                       | 15.666                 | 7.775                 | 5.893                    |

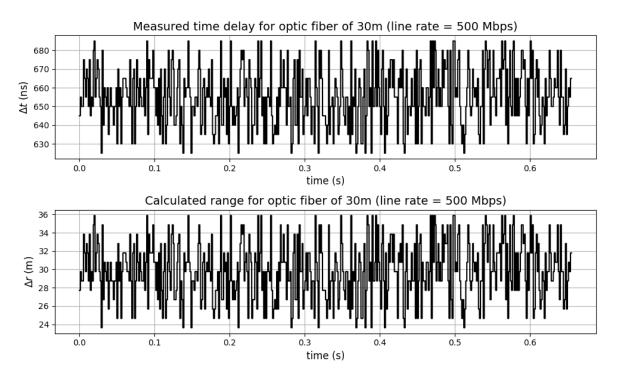

| 30                     | 29.847                   | 28.962               | 29.778                  | 3.243                                      | 1.585                                    | 1.217                                       | 15.884                 | 7.759                 | 5.957                    |

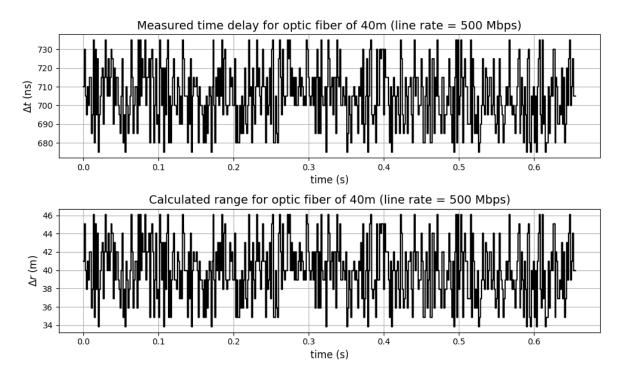

| 40                     | 39.968                   | 38.911               | 40.024                  | 3.331                                      | 1.594                                    | 1.289                                       | 16.311                 | 7.807                 | 6.312                    |

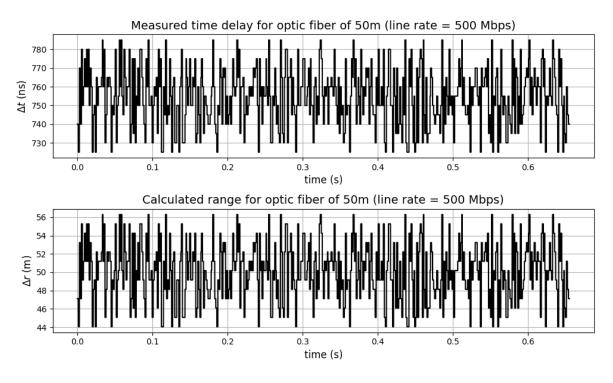

| 50                     | 50.064                   | 50.178               | 50.001                  | 3.268                                      | 1.657                                    | 1.275                                       | 16.003                 | 8.116                 | 6.245                    |

Table 1: Summary of the range measurements results as a function of line rate

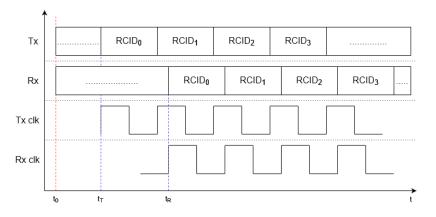

It could be concluded that the average standard deviation on a range measurement is dependent on the line rate, which is 3.235 m for a line rate of 500 Mbps, 1.618 m for a line rate of 1 Gbps and 1.226 m for a line rate of 1.25 Gbps. These standard deviations are a direct result of the bug within the firmware likely due to misconfiguration of the MGT firmware, causing occasional resets in the Gigabit Transceiver Type-H (GTH), randomizing the phase difference between the transmitter and the receiver clock. It is expected that these standard deviations drop significantly whenever the phase lock is constant during a transmission.

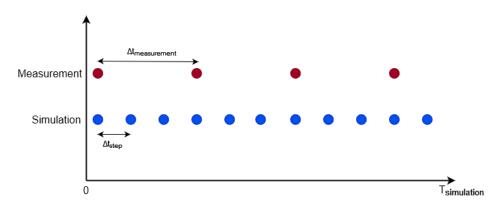

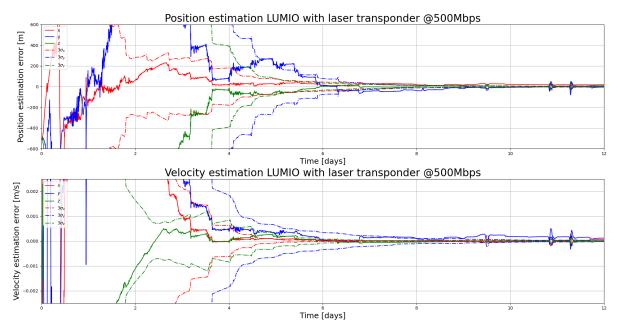

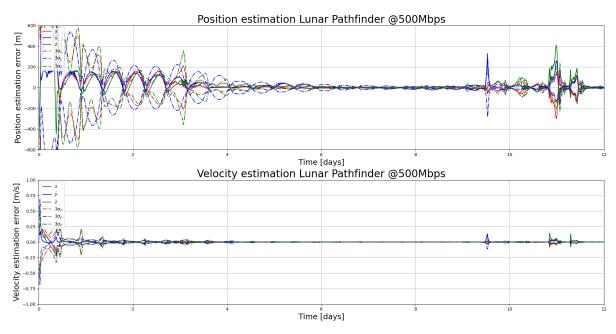

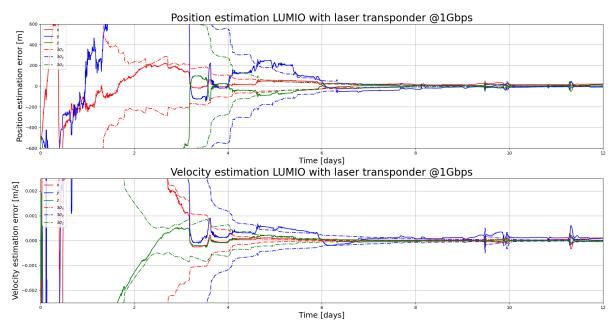

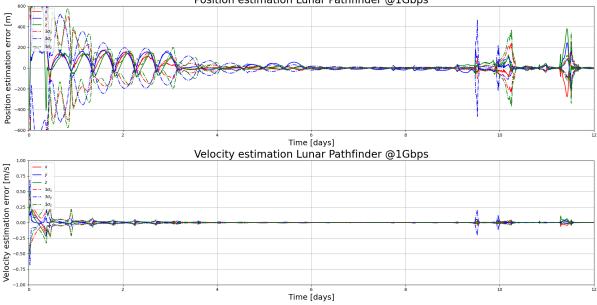

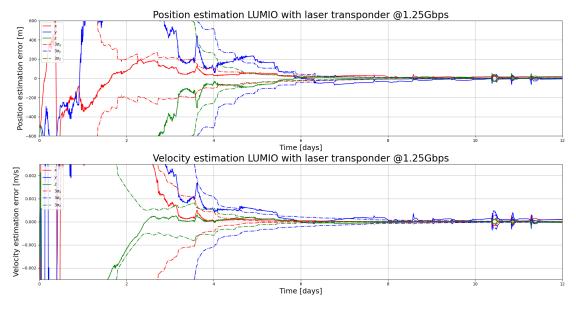

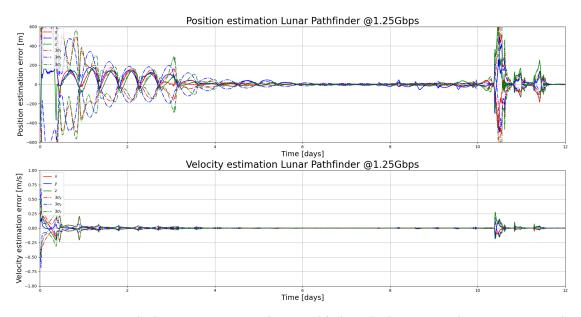

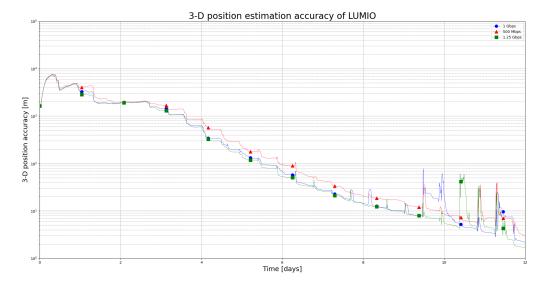

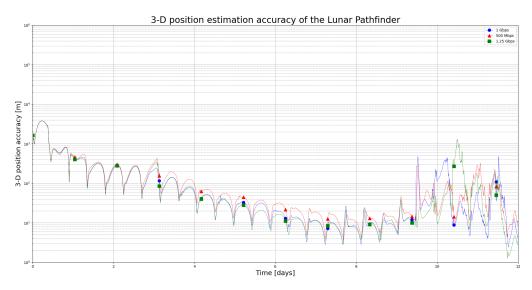

These systems are simulated to fly on Lunar Meteoroid Impact Observer (LUMIO) and Lunar Pathfinder using an orbital simulation made by [7] using Tudatpy kernels. The aforementioned standard deviations are substituted as noise values in in the simulation and the positional error estimates were recorded. The limitation of the simulation were however that the high measurement rates of the FPGA configurations, which are 25, 50 and 62.5 million measurements per second with the current data stream, were not attainable due to the discretization errors that occur on the floating point values of the small time step values required. To avoid this, the standard deviation is divided by the square root of the number of samples per measurement time step. For a measurement times step of 5 min and a measurement rate of 10 Hz, the standard deviations were divided by  $\sqrt{3000}$ . An integration time step of 5 s. The positional error converged to below 10 m after roughly 10 days for a line rate of 500 Mbps and 9 days for the line rates of 1 and 1.25 Gbps.

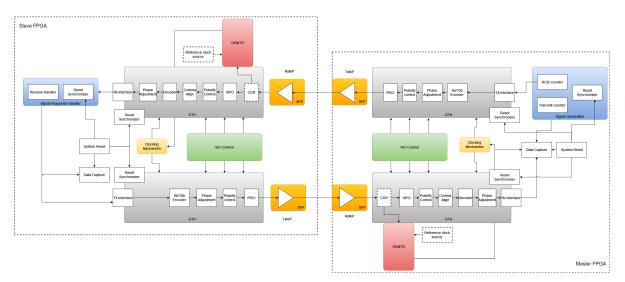

The main constraint that has been identified, besides the obvious system bug, is the rate at which the signals can be observed within the FPGA. The second experiment trivially circumvents this by using DDMTD to allow for a resolution smaller than the sampling clock permits. Ideally this is implemented into the system where the MGT is used for communication. A proposal for this implementation is made to finalize the system to create a system of two FPGA terminals capable of performing synchronous laser communication ranging measurements. A DDMTD is implemented on both terminals responsible for the sub-picosecond timing distribution. This device, often used by setups requiring picosecond or lower levels of phase stability are often used by Conseil Européen pour la Recherche Nucléaire (CERN) [8]–[10]. Implementing this Printed Circuit Board (PCB) within the design, under the assumption that the current system as is is fully debugged, accurate phase comparisons can be conducted and the timing of the system can be properly distributed to measure the range more accurately.

## Contents

| Pr | reface                                                                                                                                                                                                                                                                                                                                                                                                                                                                | i                                                                                                                      |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Su | ammary                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ii                                                                                                                     |

| N  | omenclature                                                                                                                                                                                                                                                                                                                                                                                                                                                           | xii                                                                                                                    |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                        |

| Ι  | General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                      |

| 1  | Introduction1.1Background and rationale1.2Research Questions and Objective1.3Hardware & Software1.4Report structure                                                                                                                                                                                                                                                                                                                                                   | 2<br>2<br>3<br>3<br>4                                                                                                  |

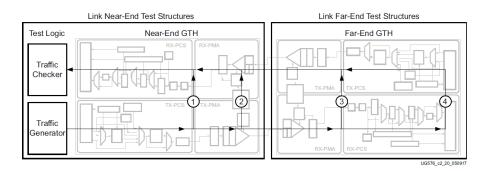

| 2  | Literature Review         2.1       Optical telemetry ranging prerequisites         2.1.1       Range Ambiguity and Range Resolution         2.1.2       Phase definition         2.1       Phase definition         2.2       Passive optical ranging         2.2.1       Signal loss         2.3       Active optical ranging         2.3.1       CCSDS data protocol         2.4       Digital Dual Mixer Time Difference         2.5       Principle of operation | 6<br>6<br>7<br>7<br>8<br>9<br>9<br>11<br>11                                                                            |

| 3  | Methodology         3.1       Requirements         3.2       Methodical Approach                                                                                                                                                                                                                                                                                                                                                                                      | <b>14</b><br>14<br>15                                                                                                  |

| II | Free-space laser ranging                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18                                                                                                                     |

| 4  | Free-Space Laser Ranging Measurements         4.1 Objective and Goals         4.2 System Set-up         4.3 Method         4.3.1 Post-Processing         4.3.2 Range Calculation         4.3.3 Atmospheric Correction         4.4 Results         4.5 Conclusion         4.6 Discussion         4.7 Recommendations                                                                                                                                                   | <ol> <li>19</li> <li>19</li> <li>22</li> <li>27</li> <li>28</li> <li>29</li> <li>32</li> <li>33</li> <li>34</li> </ol> |

| II | I FPGA Laser Communication Ranging Experiments                                                                                                                                                                                                                                                                                                                                                                                                                        | 35                                                                                                                     |

| 5  | Internal FPGA Signal Delay Measurements         5.1       Objective and Goals         5.2       System Design         5.2.1       Field-Programmable Gate Array                                                                                                                                                                                                                                                                                                       | <b>36</b><br>36<br>37<br>37                                                                                            |

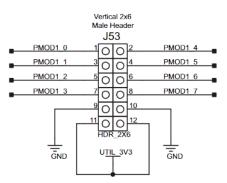

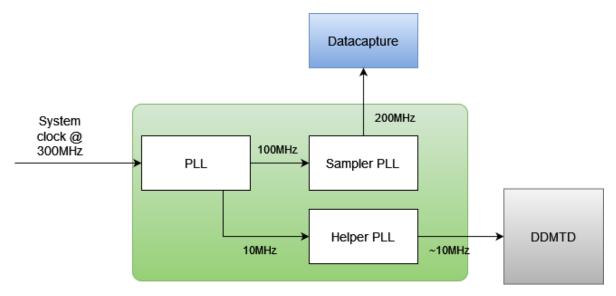

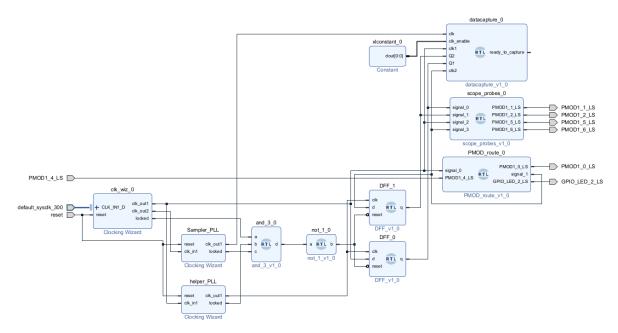

|                                                                                             | 5.2.2<br>5.2.3<br>5.2.4                                                                                                                                                              | System Model       Data-Acquisition Firmware       DDMTD Phase Detection Firmware                                                                | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                             | 5.2.5<br>5.2.6                                                                                                                                                                       | System Clocks                                                                                                                                    | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.3                                                                                         | Metho                                                                                                                                                                                | od                                                                                                                                               | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                             |                                                                                                                                                                                      | 0 11                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| - 1                                                                                         | 5.3.3                                                                                                                                                                                | Signal Routing                                                                                                                                   | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

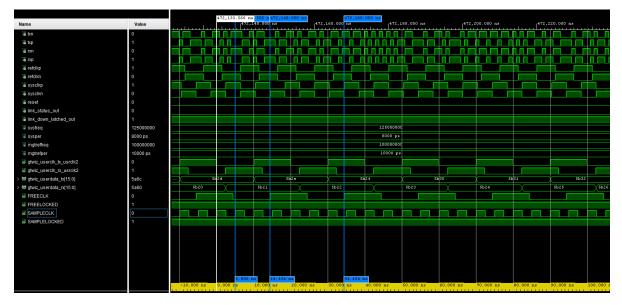

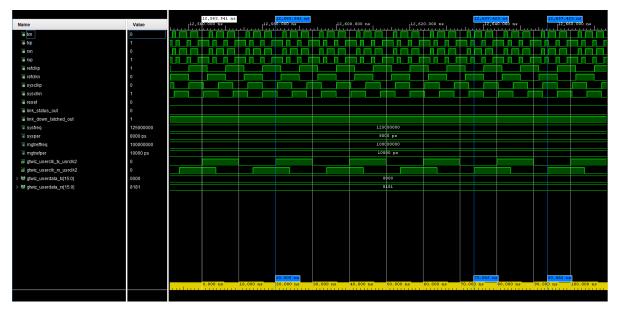

| 5.4                                                                                         | 5.4.1                                                                                                                                                                                | System tests                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 55                                                                                          | 5.4.2<br>Valida                                                                                                                                                                      | Performance Tests                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

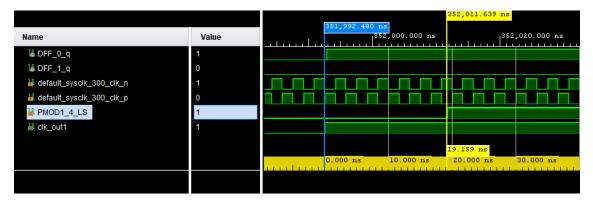

| 5.5                                                                                         | 5.5.1                                                                                                                                                                                | Data Acquisition Validation                                                                                                                      | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                             | 5.5.2<br>5.5.3                                                                                                                                                                       |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.6<br>5.7                                                                                  |                                                                                                                                                                                      | ts                                                                                                                                               | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.7<br>5.8                                                                                  | Discus                                                                                                                                                                               | ssion                                                                                                                                            | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.9                                                                                         |                                                                                                                                                                                      |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

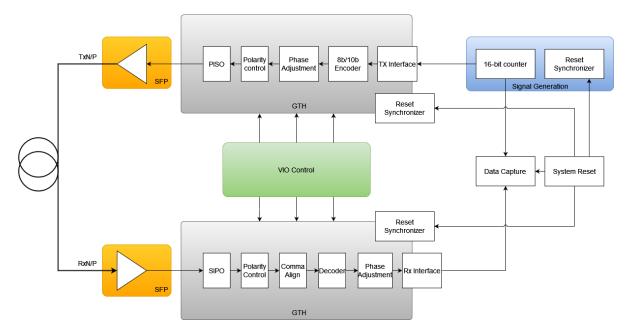

|                                                                                             |                                                                                                                                                                                      |                                                                                                                                                  | <b>60</b><br>60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.2                                                                                         |                                                                                                                                                                                      |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

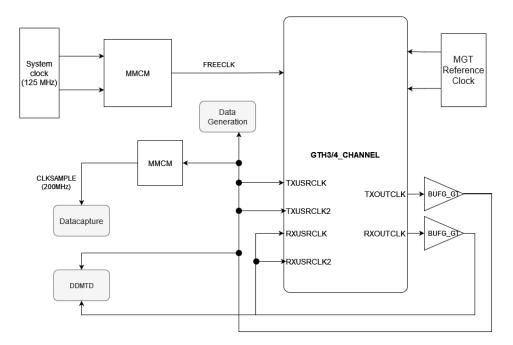

| 6.3                                                                                         | 2                                                                                                                                                                                    | 0                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

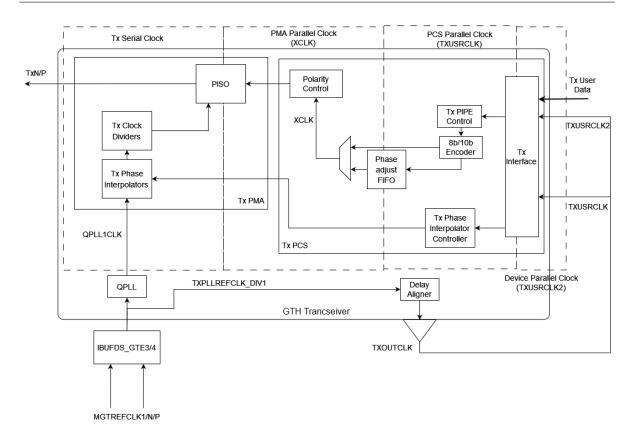

|                                                                                             | 6.3.2                                                                                                                                                                                | System Clocking                                                                                                                                  | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                             | 6.3.3<br>6 3 4                                                                                                                                                                       |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

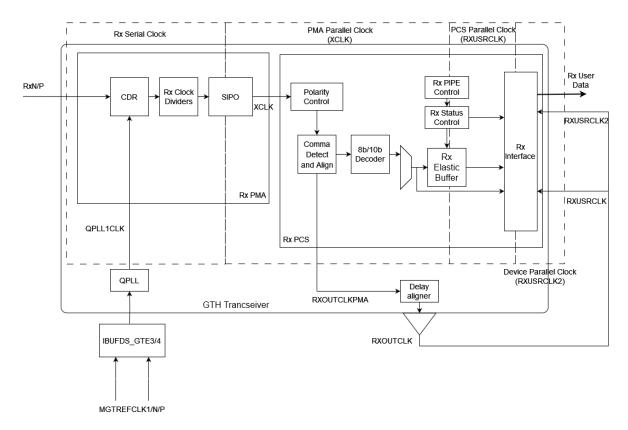

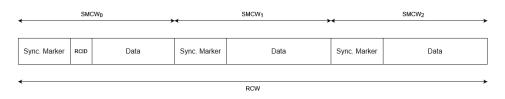

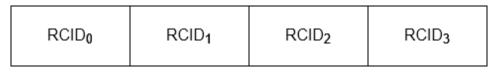

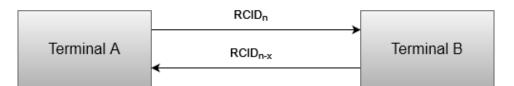

|                                                                                             | 6.3.5                                                                                                                                                                                | 8b/10b line encoding and word alignment                                                                                                          | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

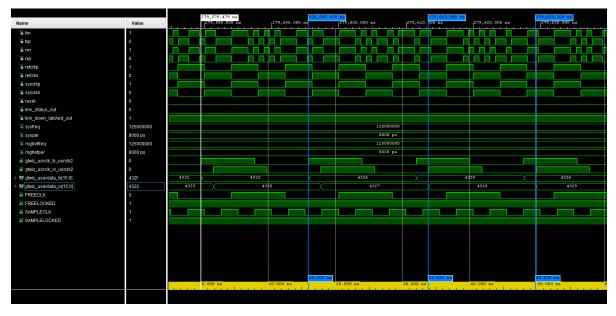

| 6.4                                                                                         |                                                                                                                                                                                      |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                             | 6.4.1<br>6.4.2                                                                                                                                                                       |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                             | 6.4.3                                                                                                                                                                                | Calibration                                                                                                                                      | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.5                                                                                         |                                                                                                                                                                                      |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                             | 6.5.1                                                                                                                                                                                | System Tests                                                                                                                                     | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.6                                                                                         |                                                                                                                                                                                      |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                             | 6.6.1                                                                                                                                                                                | System Validation                                                                                                                                | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.7                                                                                         |                                                                                                                                                                                      | System Calibration                                                                                                                               | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                             |                                                                                                                                                                                      | ts                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

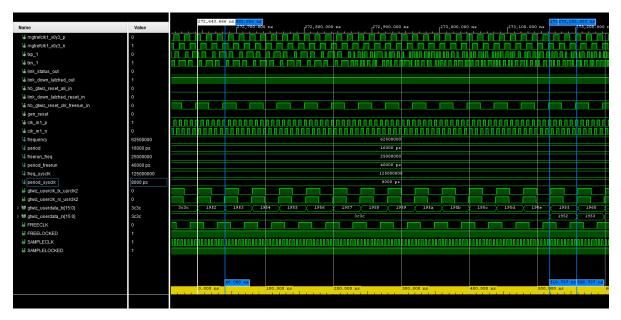

|                                                                                             | 6.7.1                                                                                                                                                                                | ts                                                                                                                                               | 94<br>94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

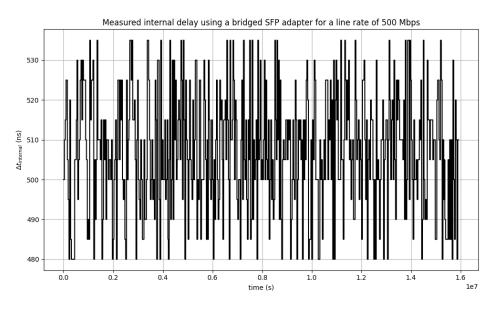

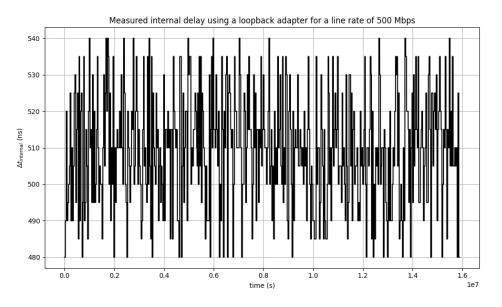

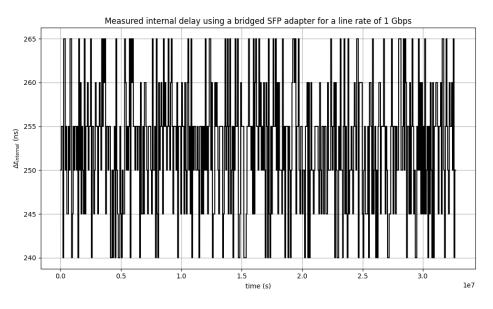

|                                                                                             | 6.7.1<br>6.7.2                                                                                                                                                                       | Test 1: 500 Mbps                                                                                                                                 | 94<br>94<br>97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                             | 6.7.1<br>6.7.2<br>6.7.3                                                                                                                                                              | Test 1: 500 Mbps                                                                                                                                 | 94<br>94<br>97<br>100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.8                                                                                         | 6.7.1<br>6.7.2<br>6.7.3<br>In-Ork<br>6.8.1                                                                                                                                           | Test 1: 500 Mbps                                                                                                                                 | 94<br>94<br>97<br>100<br>103<br>104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.8                                                                                         | 6.7.1<br>6.7.2<br>6.7.3<br>In-Ork<br>6.8.1<br>6.8.2                                                                                                                                  | Test 1: 500 MbpsTest 2: 1 GbpsTest 3: 1.25 Gbpsbit System PerformanceObservation SetupSimulation Results                                         | 94<br>94<br>97<br>100<br>103<br>104<br>105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.8<br>6.9                                                                                  | 6.7.1<br>6.7.2<br>6.7.3<br>In-Orb<br>6.8.1<br>6.8.2<br>Conclu                                                                                                                        | Test 1: 500 Mbps                                                                                                                                 | 94<br>94<br>97<br>100<br>103<br>104<br>105<br>110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.8<br>6.9<br>6.10                                                                          | 6.7.1<br>6.7.2<br>6.7.3<br>In-Ort<br>6.8.1<br>6.8.2<br>Conclu                                                                                                                        | Test 1: 500 MbpsTest 2: 1 GbpsTest 3: 1.25 Gbpsbit System PerformanceObservation SetupSimulation Results                                         | 94<br>94<br>97<br>100<br>103<br>104<br>105<br>110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

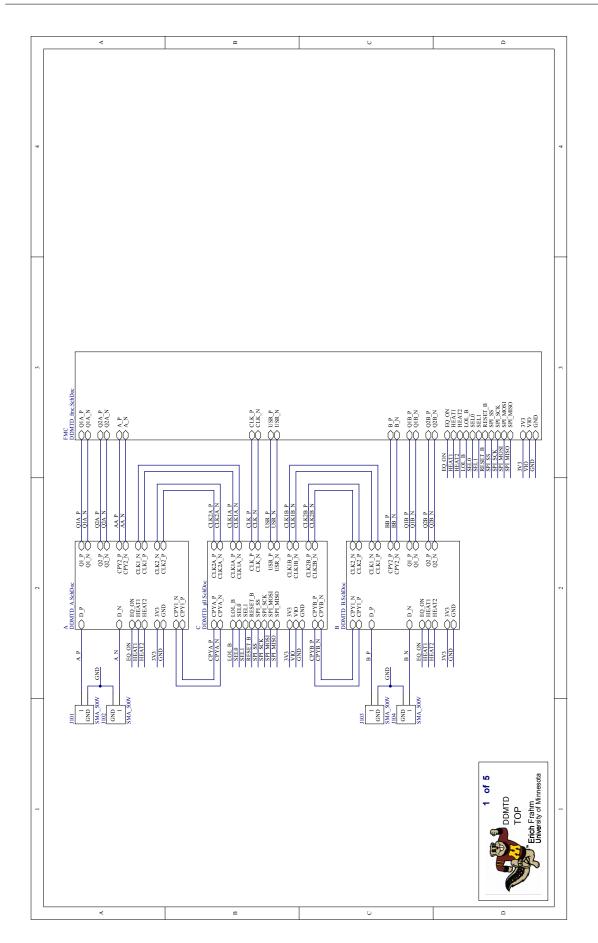

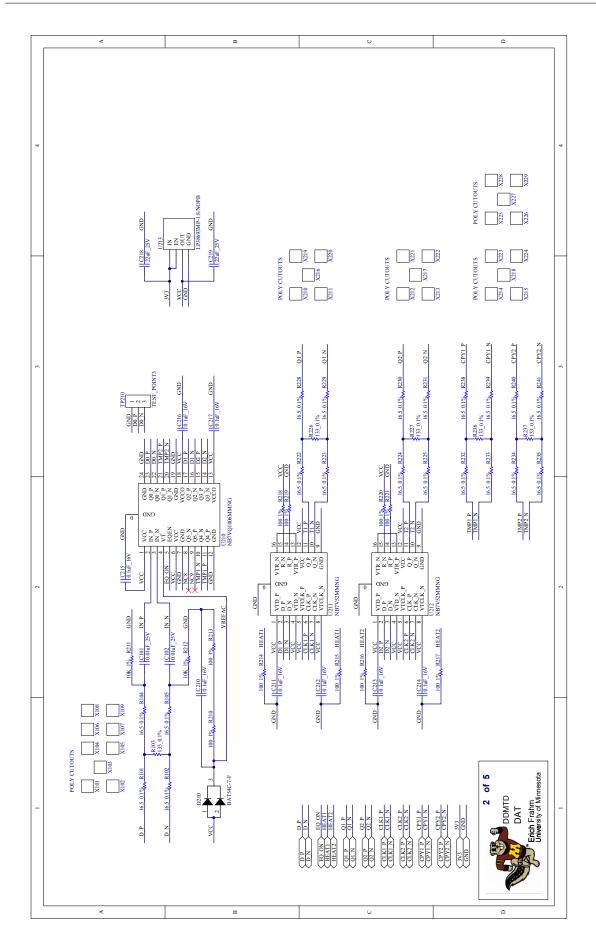

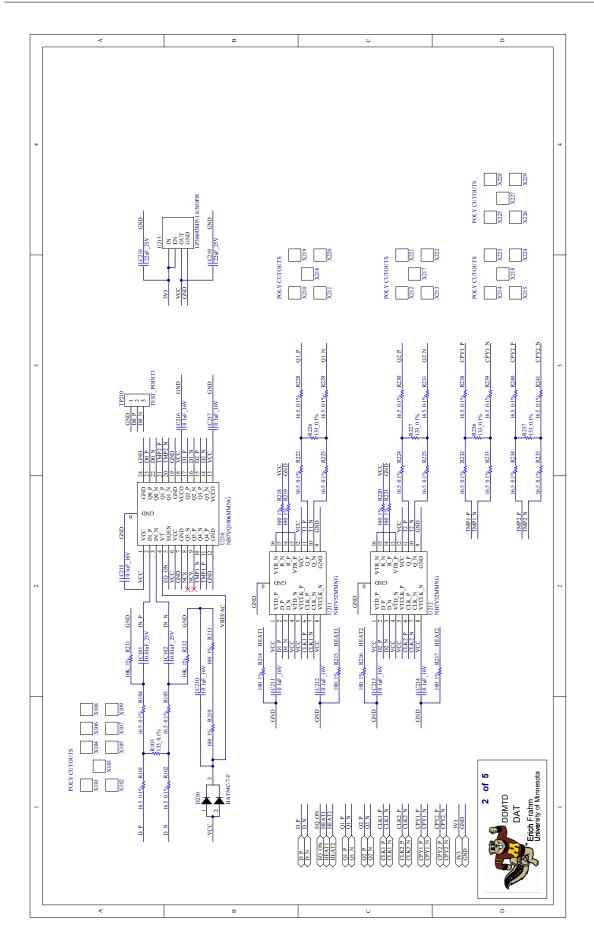

| <ul><li>6.8</li><li>6.9</li><li>6.10</li><li>6.11</li><li>Lase</li></ul>                    | 6.7.1<br>6.7.2<br>6.7.3<br>In-Ork<br>6.8.1<br>6.8.2<br>Conclu<br>Discus<br>Recom                                                                                                     | Test 1: 500 MbpsTest 2: 1 GbpsTest 3: 1.25 Gbpsbit System PerformanceObservation SetupSimulation Resultsusionsional Phase Comparison using DDMTD | 94<br>94<br>97<br>100<br>103<br>104<br>105<br>110<br>112<br>113<br><b>116</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <ul> <li>6.8</li> <li>6.9</li> <li>6.10</li> <li>6.11</li> <li>Lase</li> <li>7.1</li> </ul> | 6.7.1<br>6.7.2<br>6.7.3<br>In-Ort<br>6.8.1<br>6.8.2<br>Conclu<br>Discus<br>Recom                                                                                                     | Test 1: 500 Mbps                                                                                                                                 | 94<br>94<br>97<br>100<br>103<br>104<br>105<br>110<br>112<br>113<br><b>116</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <ul><li>6.8</li><li>6.9</li><li>6.10</li><li>6.11</li><li>Lase</li></ul>                    | 6.7.1<br>6.7.2<br>6.7.3<br>In-Ort<br>6.8.1<br>6.8.2<br>Conclu<br>Discus<br>Recom                                                                                                     | Test 1: 500 MbpsTest 2: 1 GbpsTest 3: 1.25 Gbpsbit System PerformanceObservation SetupSimulation Resultsusionsional Phase Comparison using DDMTD | 94<br>97<br>100<br>103<br>104<br>105<br>110<br>112<br>113<br><b>116</b><br>116<br>116<br>117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

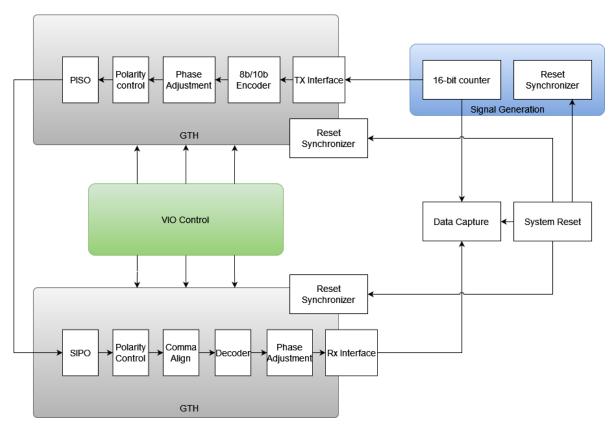

|                                                                                             | <ul> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> <li>5.9</li> <li>Lase</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul> | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                             | 5.2.3       Ďata-Acquisition Firmware         5.2.4       DDMTD Phase Detection Firmware         5.2.5       System Clocks         5.2.6       General Firmware Description         5.3       Method         5.3.1       Signal type         5.3.2       Phase Detection         5.3.3       Signal Routing         5.4       Verification         5.4.1       System tests         5.4.2       Performance Tests         5.5       Validation         5.5.1       Data Acquisition Validation         5.5.2       Performance Validation & Analysis         5.5.3       Resolving ambiguity         5.6       Results         5.7       Conclusion         5.8       Discussion         5.9       Recommendations         Laser Signal Loopback over Optic Fiber         6.1       Objectives and Goals         6.2       System Design         6.3.1       System Model         6.3.2       System Model         6.3.3       GTH and Clock Domain Crossing         6.3.4       Signal data generation         6.3.5       8b/10b line encoding and word alignment         6.4       Method |

|    | 7.3Conclusion7.4Recommendations                                |     |

|----|----------------------------------------------------------------|-----|

| 8  | General Conclusion                                             | 120 |

| Re | eferences                                                      | 124 |

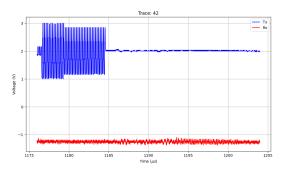

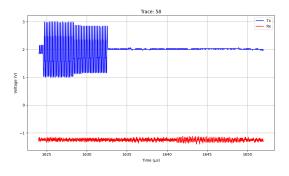

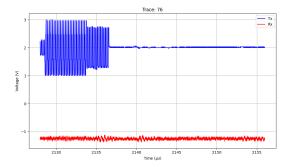

| Α  | Gaussian distribution characteristics of each individual trace | 126 |

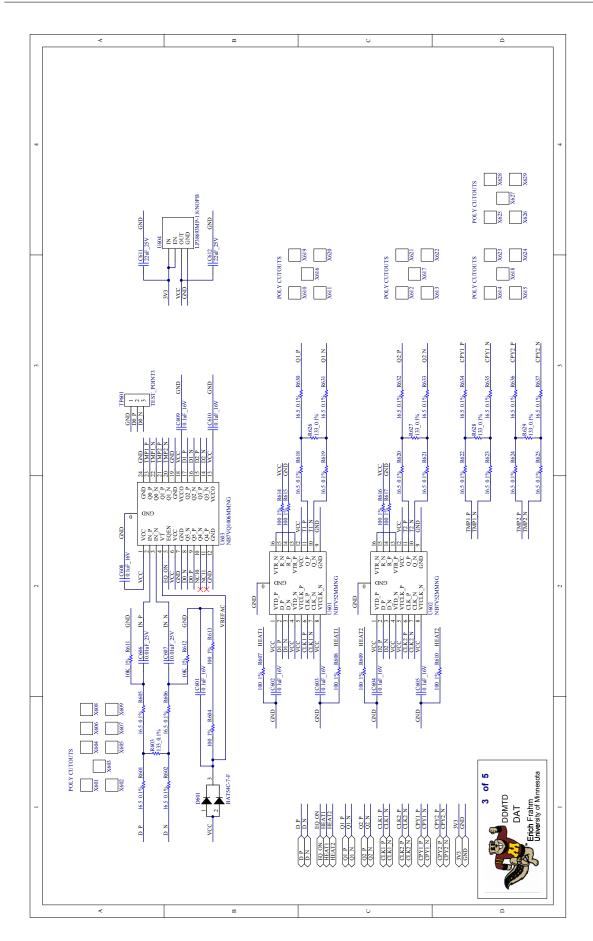

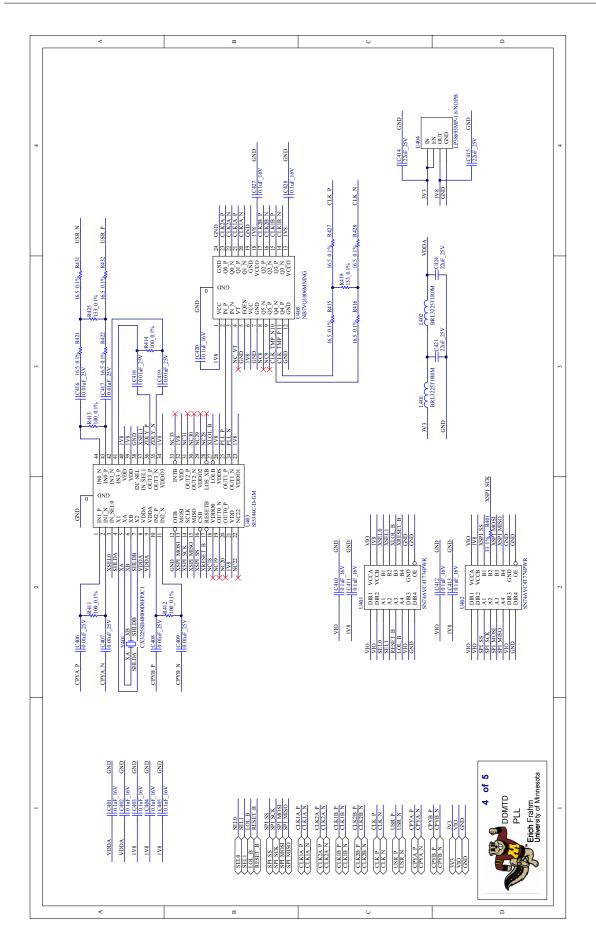

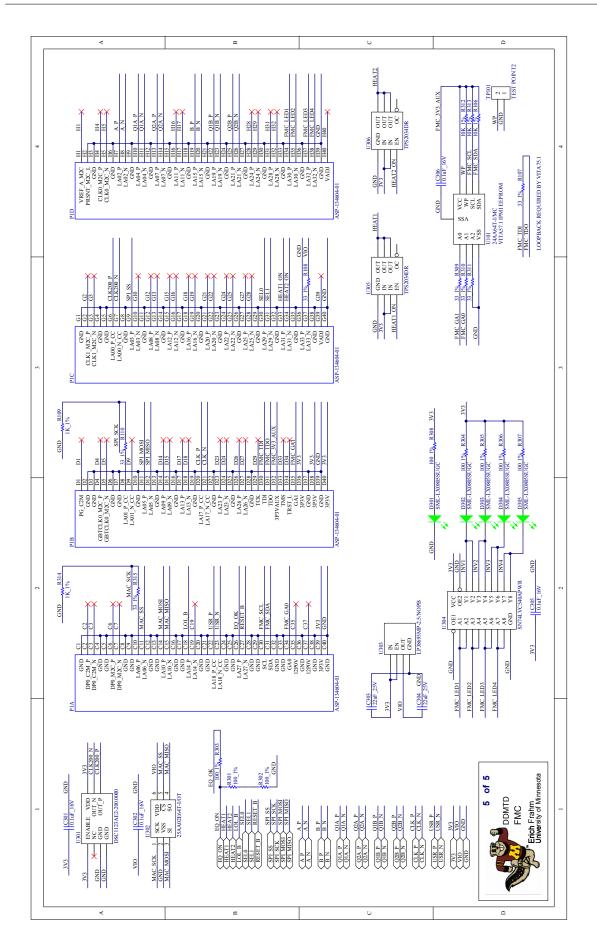

| B  | DDMTD Schematics                                               | 129 |

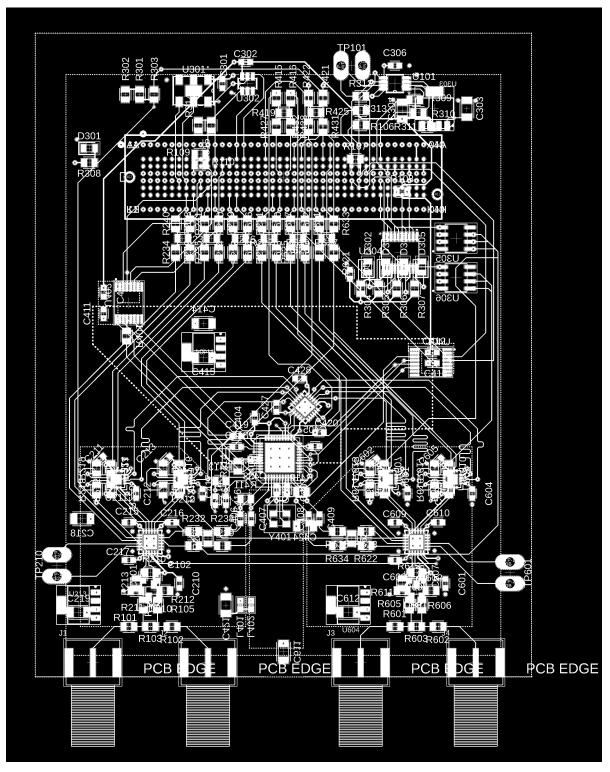

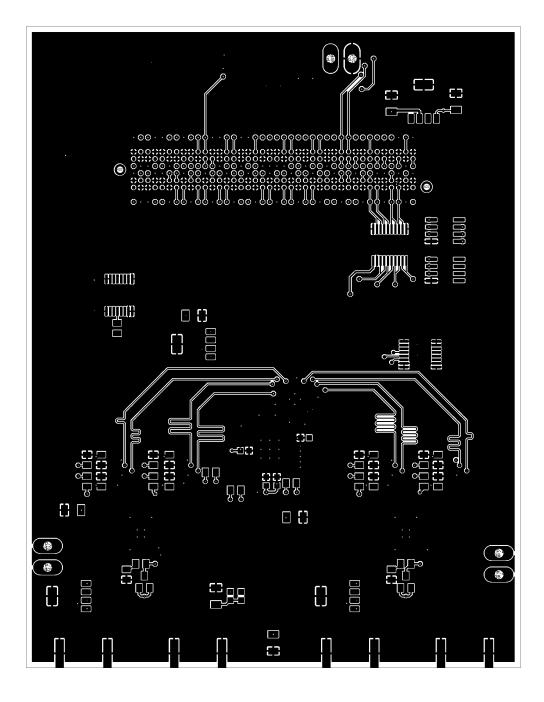

| С  | DDMTD PCB                                                      | 136 |

## List of Figures

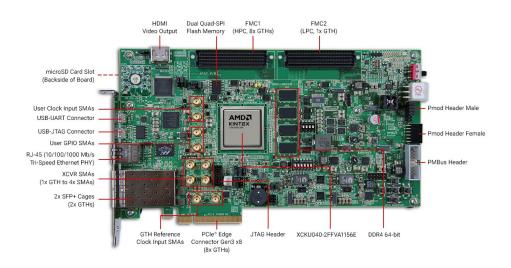

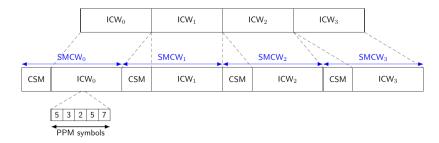

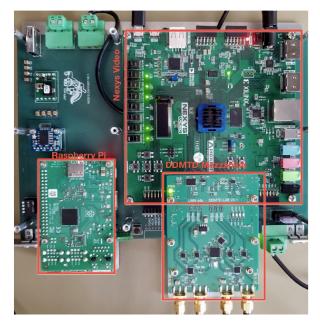

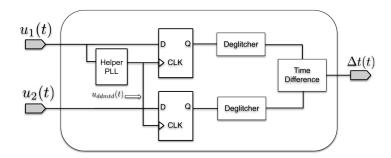

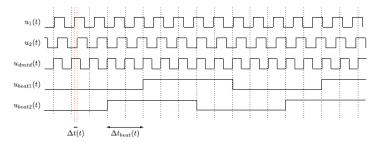

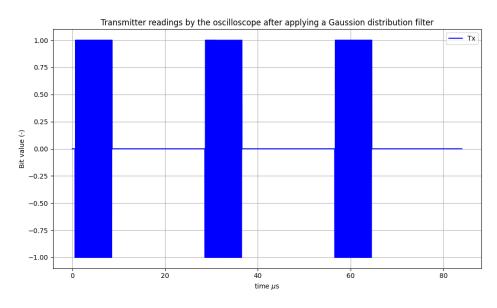

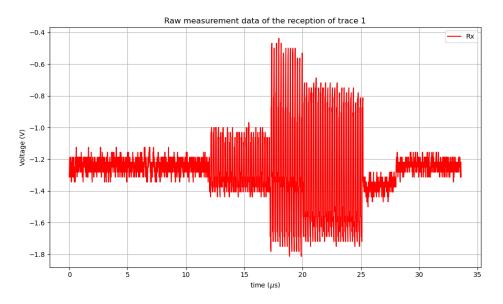

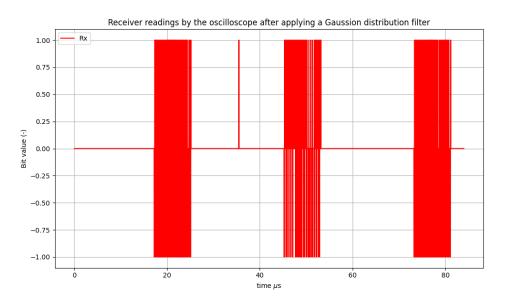

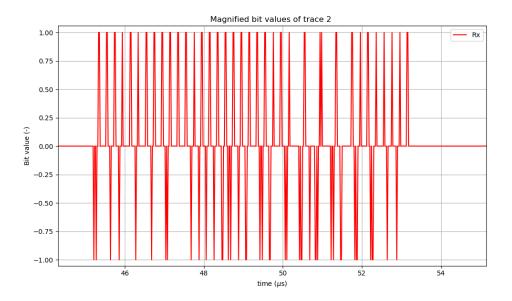

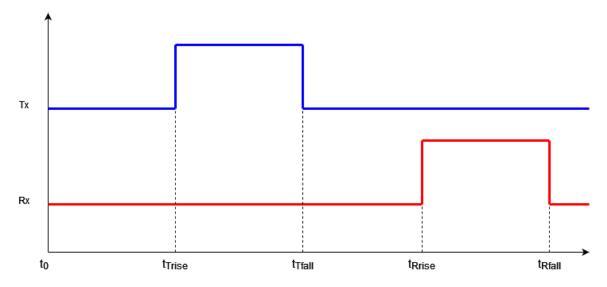

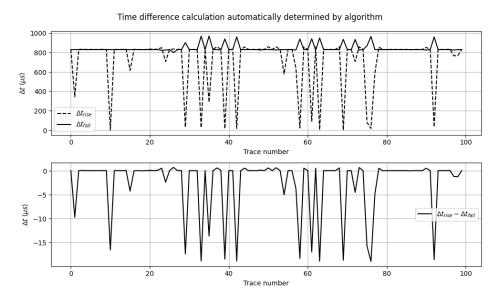

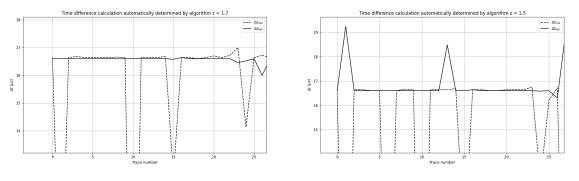

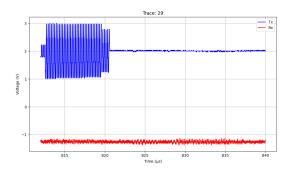

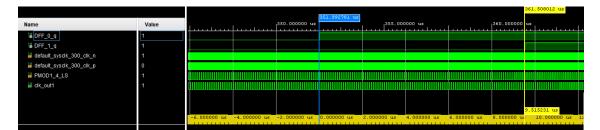

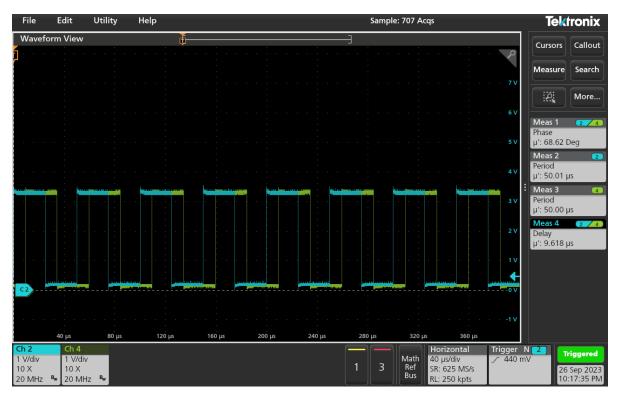

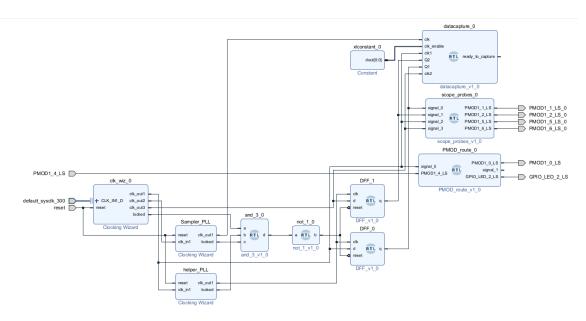

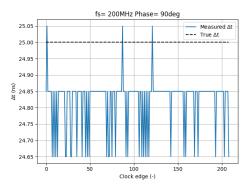

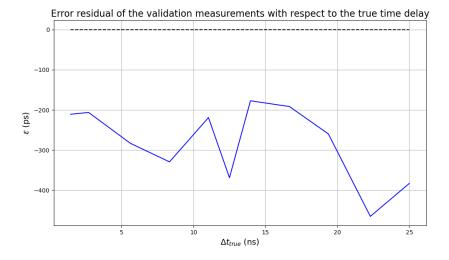

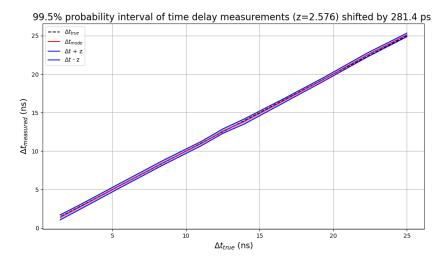

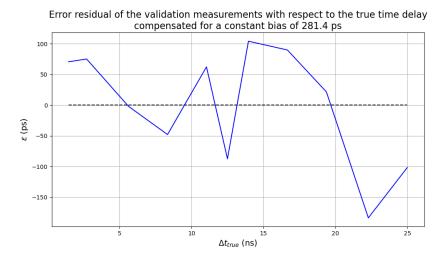

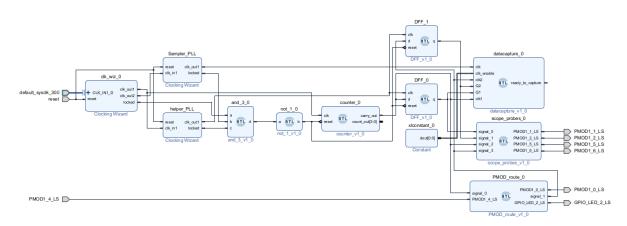

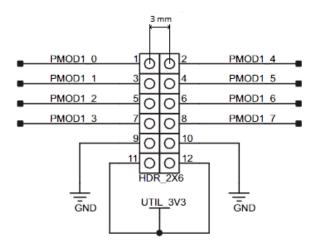

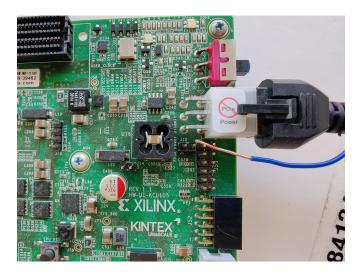

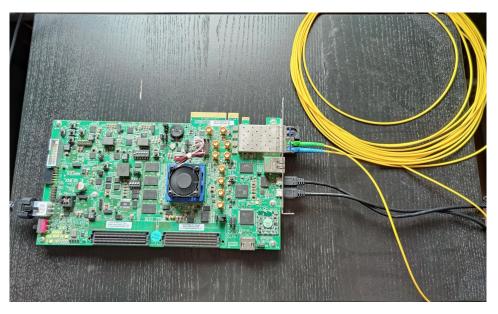

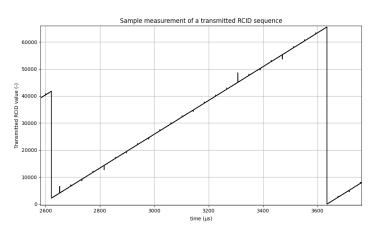

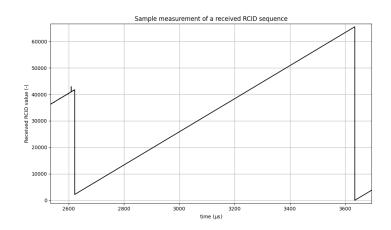

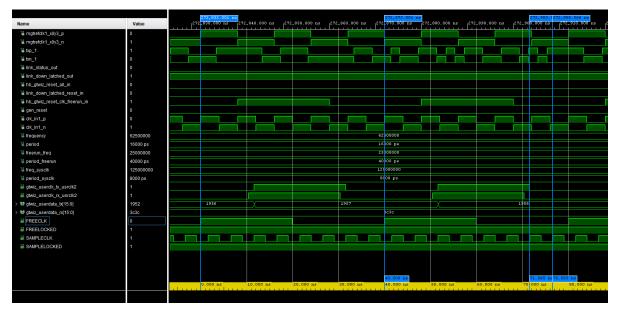

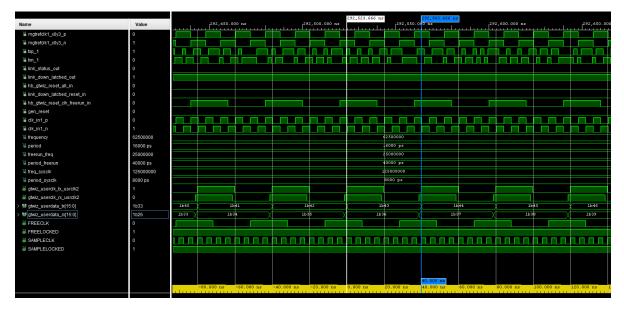

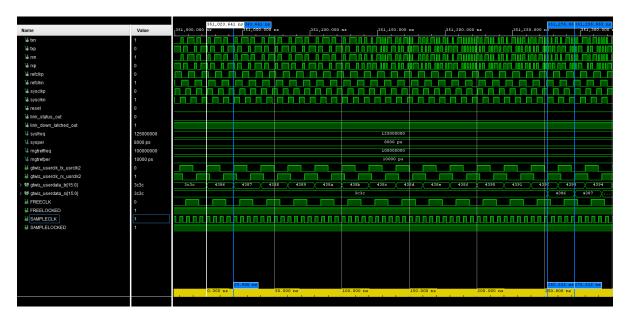

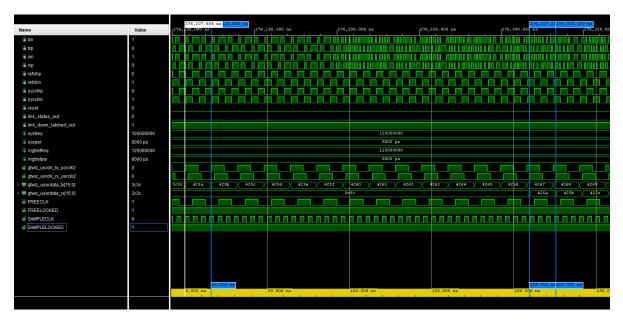

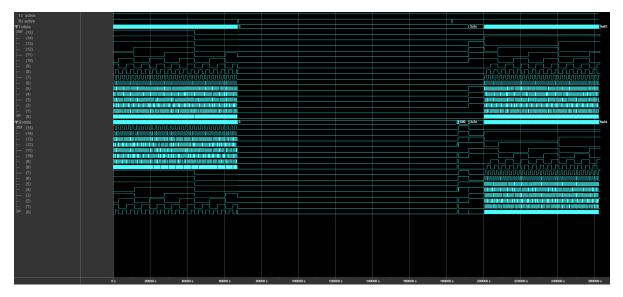

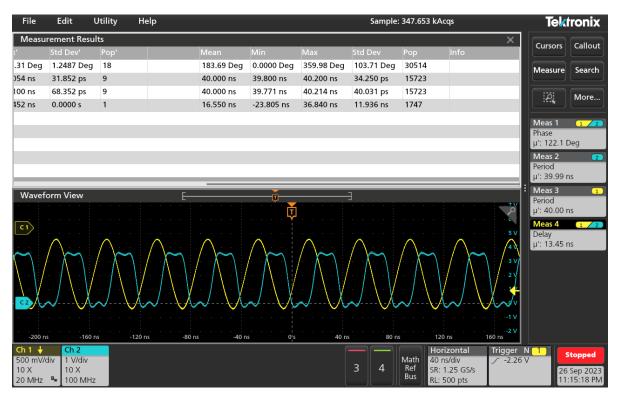

| 1.1        | AMD Kintex UltraScale FPGA KCU105 Evaluation Kit layout <sup>1</sup>                                                                                                                                                                                    | 4       |