# Asymmetric Attestation Protocol for Constrained IoT Devices

# Asymmetric Attestation Protocol for Constrained IoT Devices

By

Nikolaos Skartsilas

In partial fulfilment of the requirements for the degree of:

**Master of Science**

in Embedded Systems

at the Delft University of Technology,

Faculty of Electrical Engineering, Mathematics and Computer Science (EEMCS),

to be defended publicly on December 17, 2025, at 14:00 PM.

Supervisor: Dr.ir. M. Taouil MSc, TU Delft

Thesis committee: Dr.ir. M. Taouil MSc, TU Delft

Prof.dr. K.G. (Koen) Langendoen, TU Delft

*An electronic version of this thesis is available at <http://repository.tudelft.nl/>.*

# Preface

This thesis was conducted in collaboration with **Intrinsic ID** and addresses security mechanisms for resource-constrained embedded systems. The work combines protocol design, security analysis, and a prototype implementation to evaluate the feasibility of a DICE-rooted, certificate-based asymmetric attestation approach on microcontroller-class devices.

Due to confidentiality constraints associated with the industrial development environment at Intrinsic ID, the complete prototype source code and certain implementation-specific artifacts cannot be included in this report. To support scientific evaluation, the thesis documents the design through explicit assumptions and requirements, protocol flows, pseudocode-level descriptions, and quantitative measurements on representative hardware.

# Contents

|                                                       |           |

|-------------------------------------------------------|-----------|

| <b>Preface</b>                                        | <b>5</b>  |

| <b>Abstract</b>                                       | <b>8</b>  |

| <b>List of Figures</b>                                | <b>9</b>  |

| <b>List of Tables</b>                                 | <b>11</b> |

| <b>Acknowledgments</b>                                | <b>12</b> |

| <b>1 Introduction</b>                                 | <b>13</b> |

| 1.1 Motivation                                        | 13        |

| 1.2 State of the Art                                  | 14        |

| 1.3 Main Contributions                                | 16        |

| 1.4 Thesis Outline                                    | 17        |

| <b>2 Background</b>                                   | <b>18</b> |

| 2.1 Embedded Systems Security                         | 18        |

| 2.1.1 Information Security                            | 19        |

| 2.1.2 Device Security                                 | 21        |

| 2.2 Cryptography                                      | 23        |

| 2.2.1 Symmetric Cryptography                          | 25        |

| 2.2.2 Public Key Cryptography                         | 25        |

| 2.2.3 Hash Functions and Message Authentication Codes | 27        |

| 2.3 Public Key Infrastructure                         | 28        |

| 2.3.1 PKI Components                                  | 28        |

| 2.3.2 Trust Models                                    | 30        |

| 2.4 Transport layer Security                          | 32        |

| 2.5 Device Identifier Composition Engine              | 34        |

| <b>3 System Architecture and Protocol Design</b>      | <b>38</b> |

| 3.1 Design Approach                                   | 38        |

| 3.2 Design Objectives and Requirements                | 40        |

| 3.2.1 Design Objectives                               | 40        |

| 3.2.2 Requirement Analysis                            | 41        |

| 3.3 Protocol Design                                   | 43        |

| 3.3.1 System Architecture                             | 44        |

| 3.3.2 Protocol Functional Flows                       | 48        |

| 3.3.3 Protocol Security Analysis                      | 52        |

| <b>4 Implementation and Results</b>                   | <b>56</b> |

| 4.1 System Architecture and Design Exploration        | 56        |

| 4.1.1 High-Level Architecture                         | 56        |

|                     |                                        |           |

|---------------------|----------------------------------------|-----------|

| 4.1.2               | Design Space Exploration               | 59        |

| 4.2                 | Prototype Development                  | 63        |

| 4.2.1               | Proof of Concept Implementation        | 63        |

| 4.2.2               | Embedded Implementation                | 66        |

| 4.3                 | Empirical Evaluation and Discussion    | 68        |

| 4.3.1               | Measurement Limitations and Challenges | 68        |

| 4.3.2               | Cycle Count and Stack Usage Analysis   | 68        |

| 4.3.3               | Analysis and Discussion                | 71        |

| <b>5</b>            | <b>Conclusions</b>                     | <b>71</b> |

| 5.1                 | Thesis Summary                         | 73        |

| 5.2                 | Future Work                            | 74        |

| <b>Bibliography</b> |                                        | <b>76</b> |

# Abstract

*The evolution of computing systems, particularly in the Internet of Things (IoT), has emphasized openness to support innovation, but this same openness introduces critical security challenges. Modern cyber-attacks are increasingly sophisticated and persistent, exposing the limitations of traditional software-only defenses. IoT devices, often deployed in hostile environments and subject to stringent constraints in power, memory, and cost, lack the robust security mechanisms required for trust and resilience, especially as the demand for remote software updates grows.*

*To address these challenges, this thesis proposes a scalable and cost-effective security architecture that supports hardware-rooted identity, remote attestation, and secure device updates for resource-constrained embedded devices. The design is grounded in modest hardware assumptions compatible with commercial IoT platforms. A statistically unique, device-specific secret anchors the root of trust, enabling verifiable software identity throughout the device lifecycle. Building on the Device Identifier Composition Engine (DICE) standard, an asymmetric attestation protocol is developed specifically for constrained environments.*

*The architecture is validated through a prototype implementation on an STM32 microcontroller, demonstrating secure remote attestation via server communication. Performance measurements, including clock cycles and memory utilization, alongside a structured security analysis offer insight into the feasibility and resilience of the proposed solution. This work contributes to the advancement of DICE-based architectures by providing a practical and secure framework for verifying software execution in trusted IoT devices.*

# List of Figures

Figure 1.1: Connected IoT Devices Forecast by 2025 [5]

Figure 2.1: The C.I.A triad of Information Security

Figure 2.2: Device Security Techniques

Figure 2.3: Cryptographic Encryption/Decryption

Figure 2.4: Classification of Cryptographic Algorithms

Figure 2.5: Symmetric cryptography

Figure 2.6: Public Key cryptography

Figure 2.7: User authentication scheme

Figure 2.8: Message Authentication Code (MAC) usage

Figure 2.9: Certificate chain of Trust

Figure 2.10: Hierarchical trust model

Figure 2.11: TLS Handshake protocol

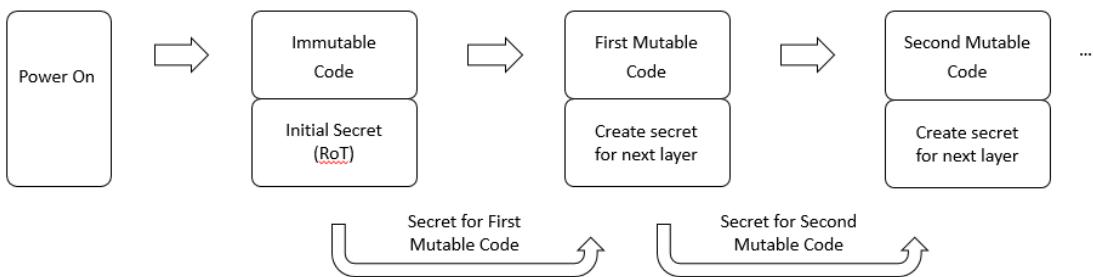

Figure 2.12: DICE boot model

Figure 2.13: Layer code change

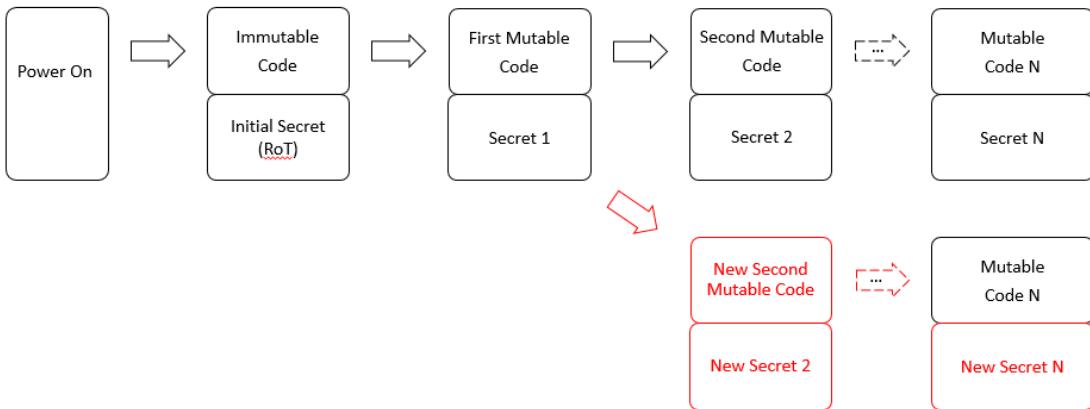

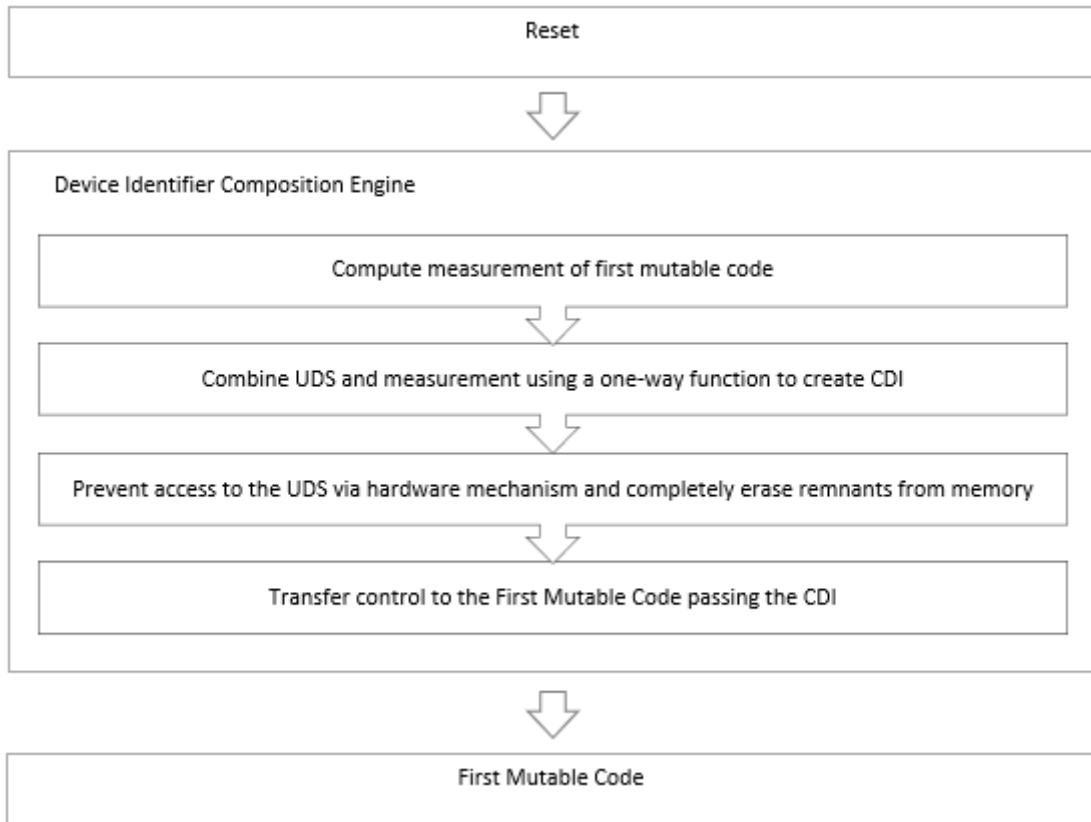

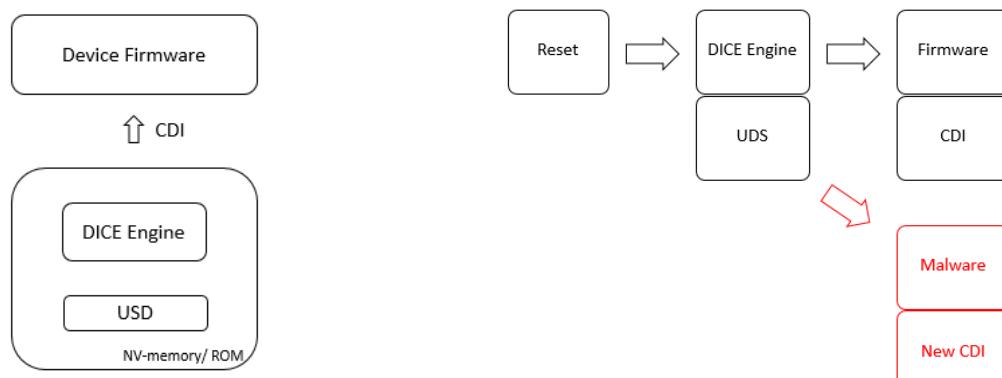

Figure 2.14: DICE Engine

Figure 2.15: DICE Engine layer and firmware

Figure 2.16: Malware attack scenario

Figure 3.1: Waterfall Model for Sequential Software Development

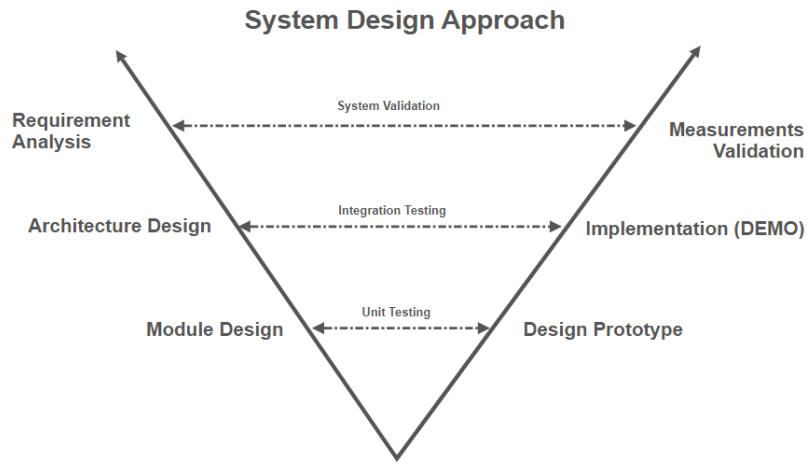

Figure 3.2: General Testing V-Model for Security-Critical IoT Systems

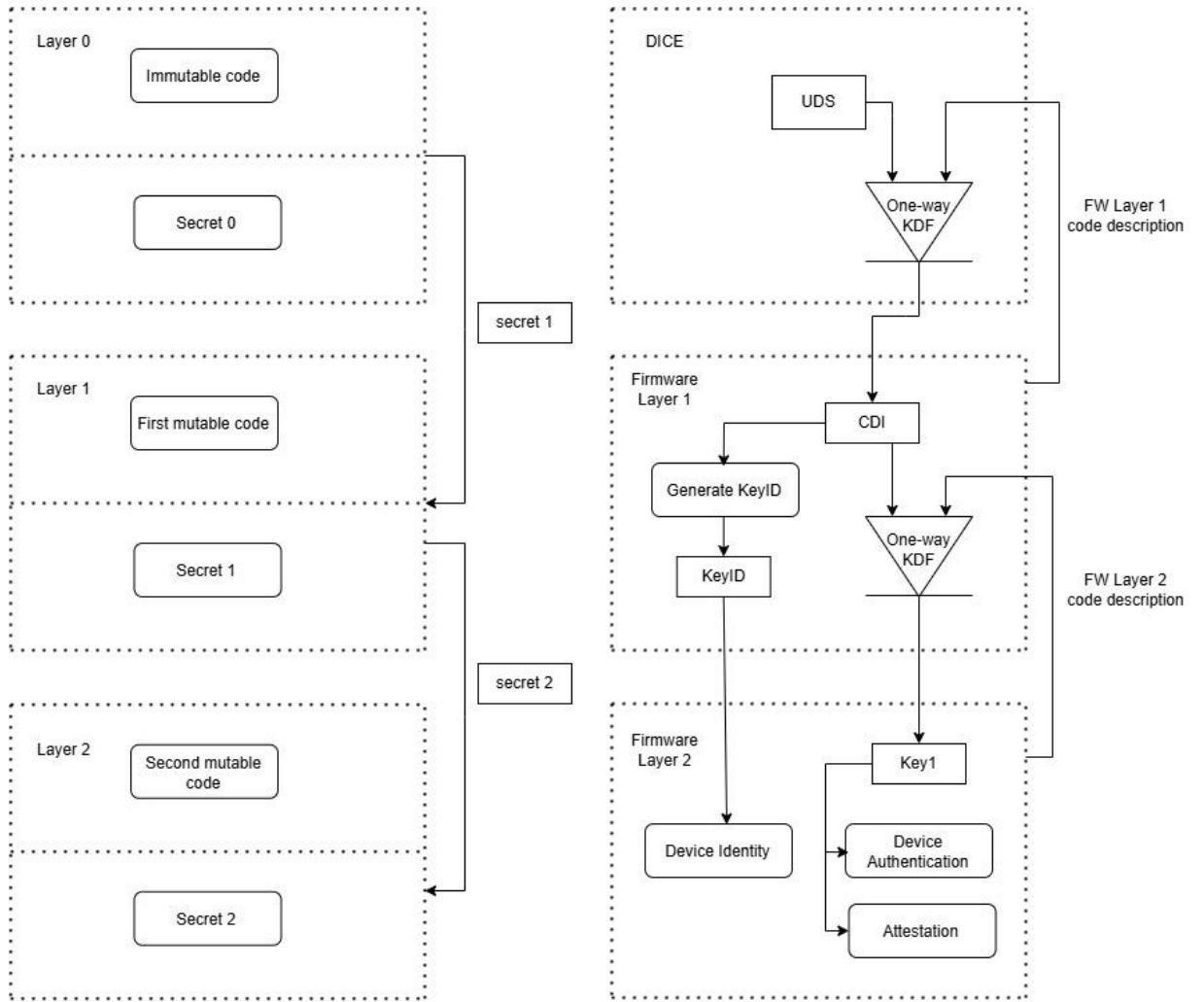

Figure 3.3: Layered Boot Process in DICE-Based Architecture

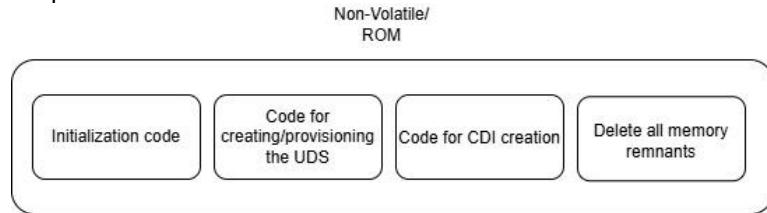

Figure 3.4: Internal Components of the DICE Engine

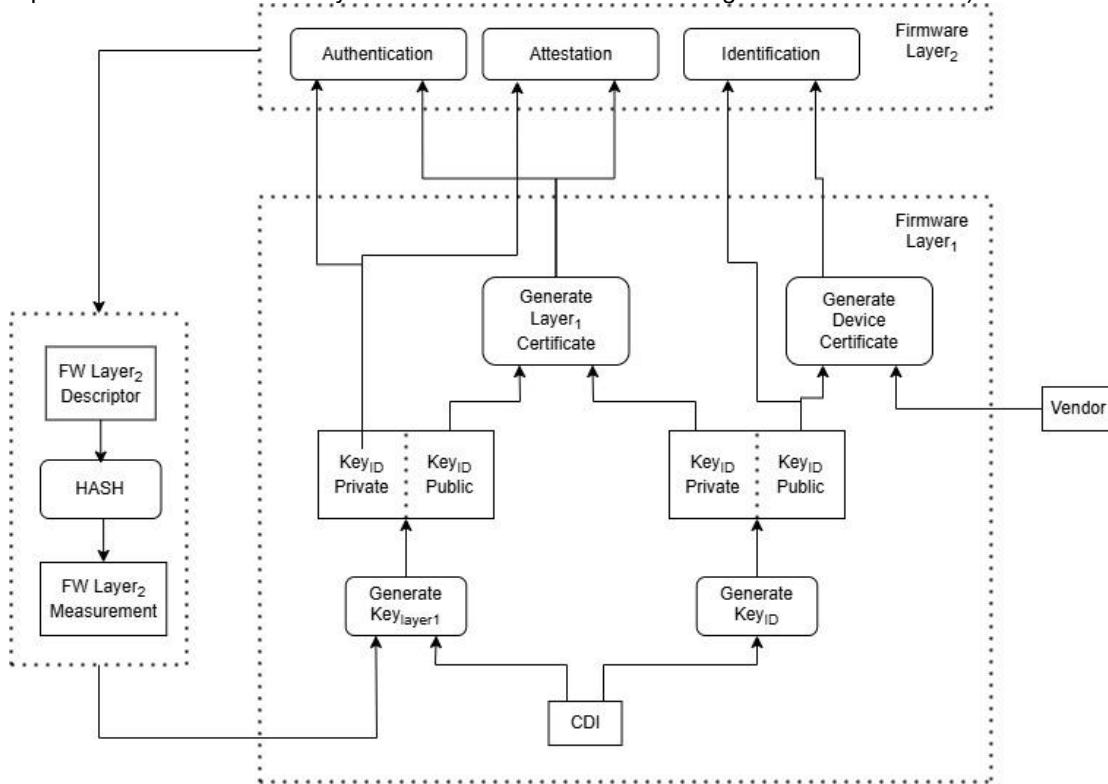

Figure 3.5: Structure of Firmware Layer 1

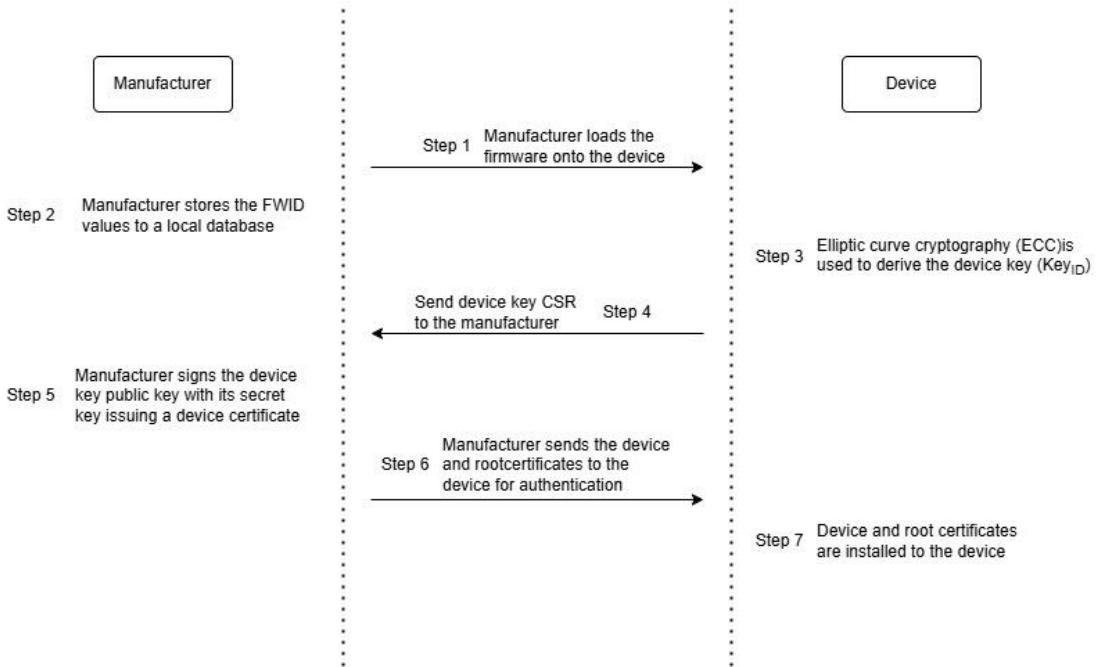

Figure 3.6: Protocol Manufacturing Phase Flow

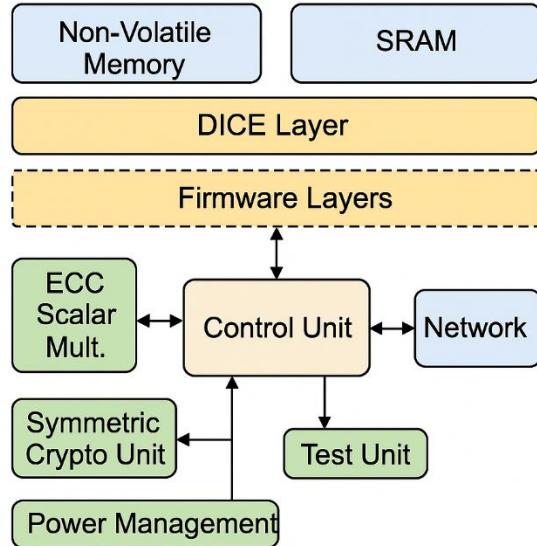

Figure 4.1: High-level system architecture

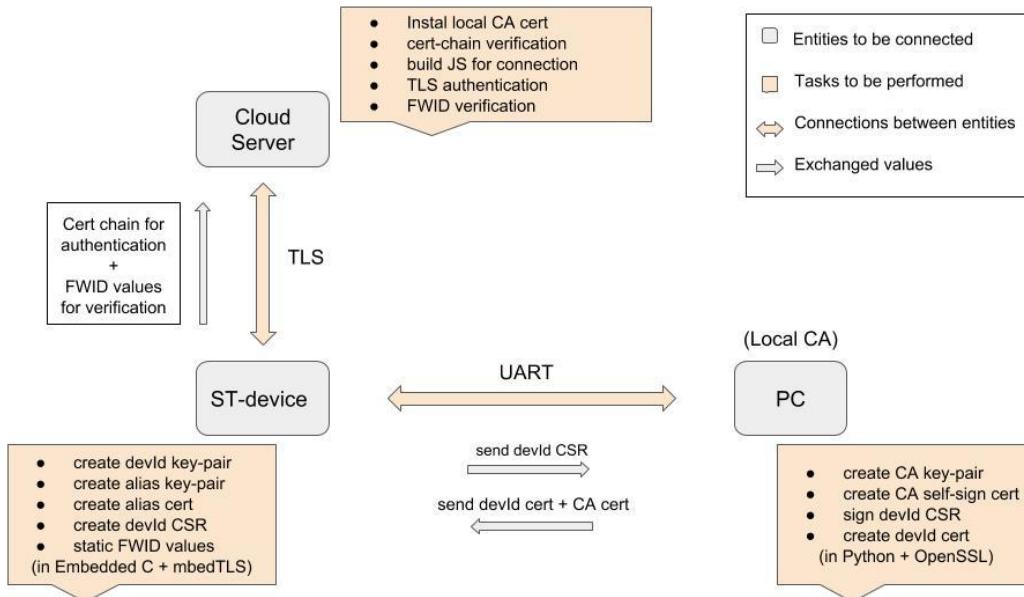

Figure 4.2: Demonstrator scenario

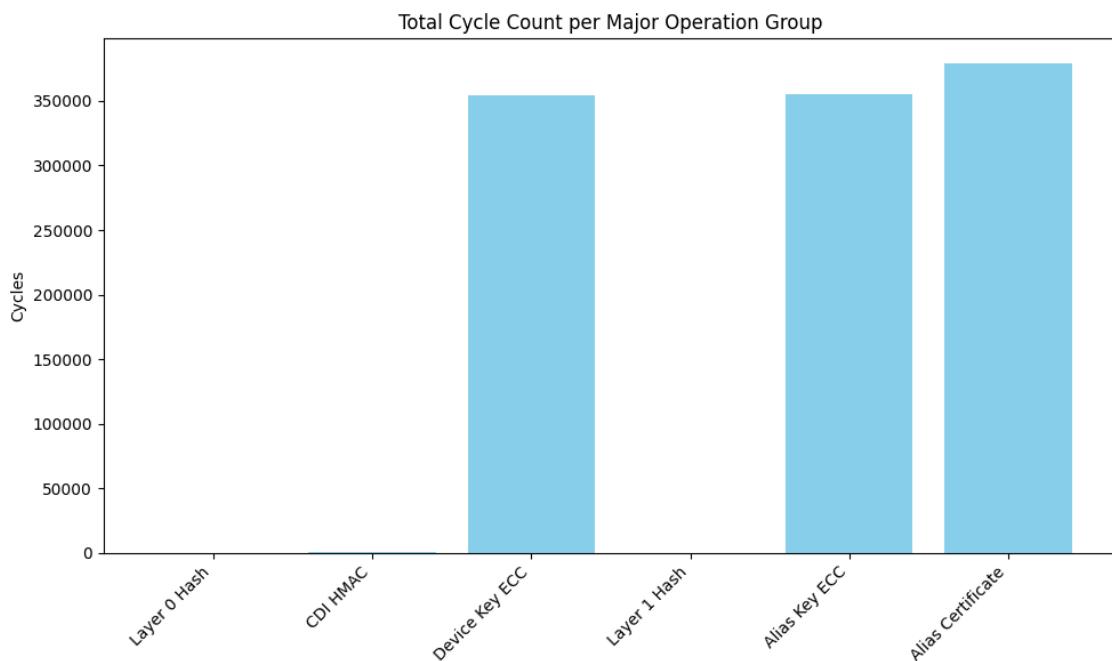

Figure 4.3: Total CPU cycle cost per cryptographic operation

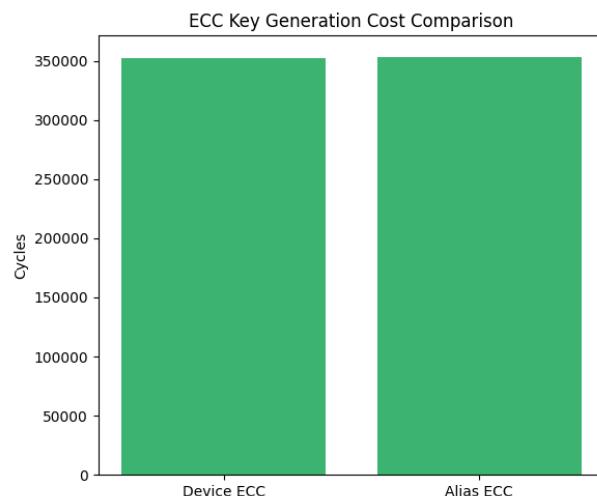

Figure 4.4: Internal breakdown of ECC key generation for DeviceID and Layer keys

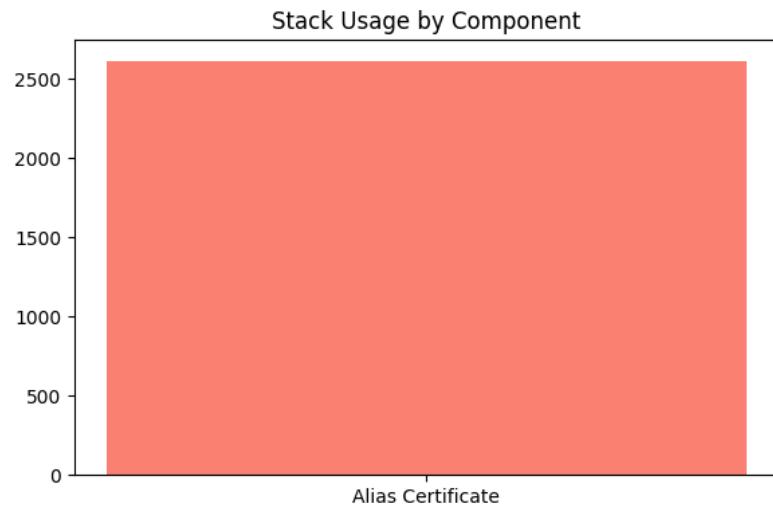

Figure 4.5: Stack memory usage for selected cryptographic operations

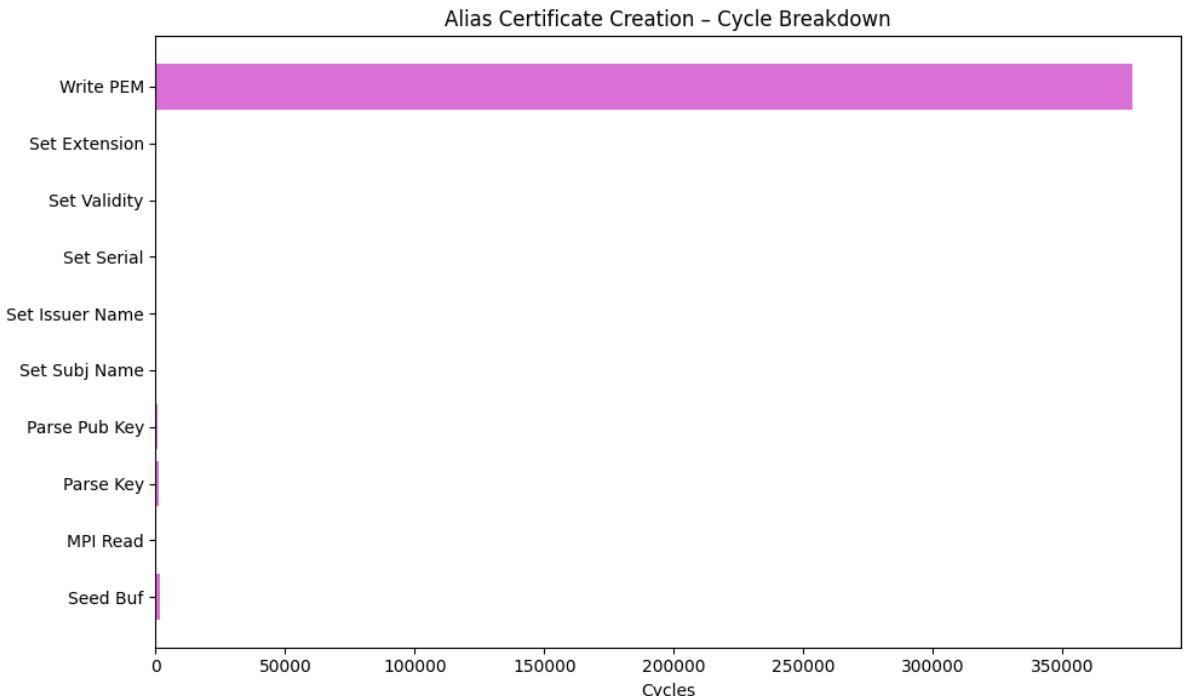

Figure 4.6: Cycle breakdown of alias certificate creation using mbedTLS routines

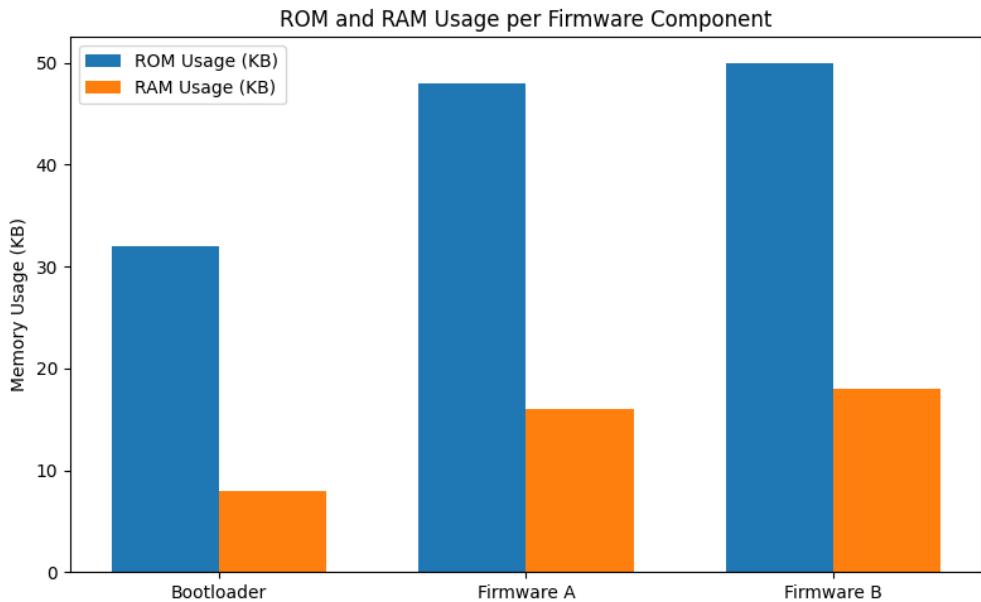

Figure 4.7: Summary of stack and code memory usage across components

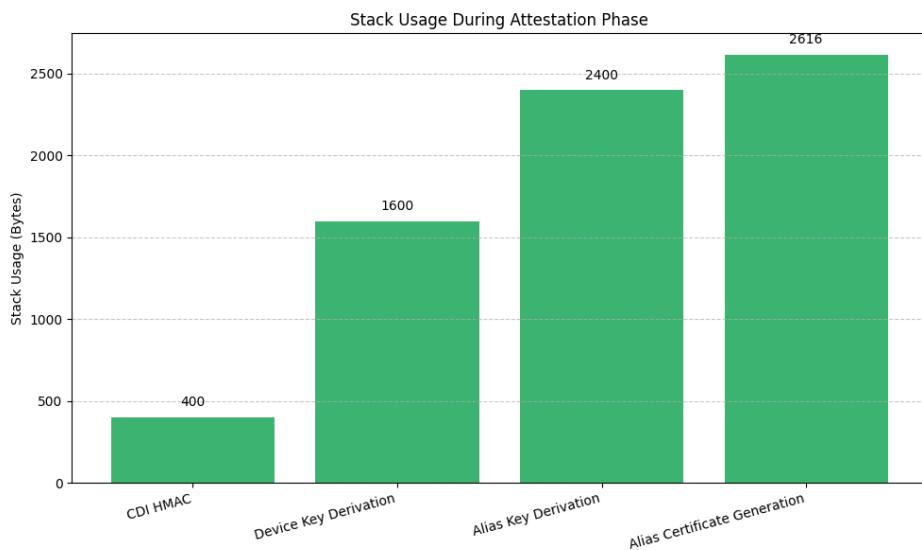

Figure 4.8: Stack usage across attestation stages (DICE-based prototype)

# List of Tables

Table 3.1: maps the design phases adopted in this work to the main contributions (MC) introduced in Section 1.3:

Table 3.1: Mapping of Design Phases to Main Contributions

Table 3.2: System Requirements

Table 3.3: Security Capability Mapping and Corresponding Requirements

Table 3.4: Structure of Device and Layer Certificates with FWID Extension

Table 3.5: Threat matrix using STRIDE

Table 3.6: Asset protection table

Table 3.7: Mapping of security capabilities to system requirements

# Acknowledgments

I would like to express my sincere gratitude to my academic supervisors and committee members, Dr.ir. Mottaqiallah Taouil and Prof.dr. Koen Langendoen, for their guidance, feedback, and support throughout this thesis.

This work was conducted in collaboration with Intrinsic ID. I would particularly like to thank my company supervisor, Georgios Selimis, for his mentorship, technical input, and continuous support during the implementation and evaluation phases. I also thank my colleagues at Intrinsic ID for the constructive discussions and assistance.

Finally, I would like to thank my family, my friends, and Ifigeneia for their encouragement and support throughout my studies.

# 1 Introduction

*This chapter concerns the motivation around this thesis, presents a summary of research studies that constitute the state of the art, describes the main contributions of the work done and provides an outline for the rest of the thesis. First, Section 1.1 refers to the importance of the rising sector of the Internet of Things (IoT), highlighting the need for effective security strategies against sophisticated attacks and threats. This section also describes the security challenges derived from such threats towards establishing a robust holistic security solution for end-to-end IoT nodes. Section 1.2 investigates past and present security solutions spanning many disciplines from software to hardware, focusing on attestation schemes. Section 1.3 describes the main contributions of this study, while Section 1.4 concludes the chapter with a short description of the other chapters of this thesis.*

## 1.1 Motivation

The proliferation of open, autonomous embedded systems connected via the Internet or other networks has led to the emergence of the Internet of Things (IoT). The global deployment of IoT devices now numbers in billions. According to Gartner, 5.8 billion enterprise and automotive IoT endpoints were projected to be in use by the end of 2020 [1]. Forecasts suggest this growth will continue, with IDC anticipating that IoT devices will generate 79.4 zettabytes of data annually by 2025 [2]. McKinsey Digital further estimates that IoT could contribute up to \$11 trillion annually to the global economy by 2025, potentially boosting corporate profits by 21% as early as 2022 [3]. These projections have incentivized major firms to invest in innovative IoT technologies that enhance business processes and improve operational efficiency. In particular, Industrial IoT (IIoT) has gained traction by promoting automation and leveraging big data analytics to reduce costs and enhance customer insights.

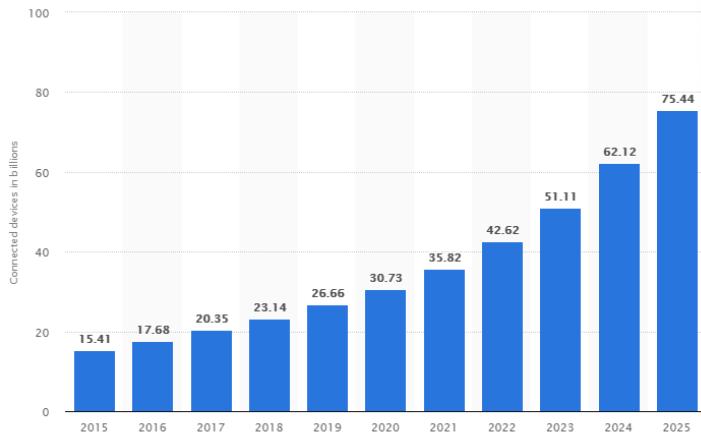

The IoT infrastructure is characterized by an openness that facilitates innovation but also presents substantial security challenges. This openness makes IoT systems attractive targets for cybercriminals, who exploit systemic vulnerabilities [4]. As shown in Figure 1.1, the expected surge in connected devices will only increase the attack surface. Ensuring the reliable and secure operation of IoT systems has thus become an increasingly complex and challenging task. Common wireless communication technologies, such as Bluetooth and Wi-Fi, possess known vulnerabilities that can be exploited by adversaries [6]. Further complicating matters are the resource constraints and physical inaccessibility of many IoT deployments, which hinder the implementation of robust security protections [7].

An expanded attack surface increases the risk of system compromise, yet many organizations fail to prioritize security due to limited expertise or budget constraints [8]. As a result, device manufacturers must prioritize security as a design imperative, not an afterthought. The heterogeneity of IoT ecosystems further complicates security: the threats concerning industrial sensors differ considerably from those affecting smart appliances or consumer wearables [9]. Privacy violations, intellectual property theft, impersonation, and device cloning are among the diverse threats IoT devices face. Notably, IoT systems can be compromised even without network connectivity. Security attacks span multiple domains, ranging from software-level exploits to direct hardware manipulation targeting the device's physical components. In 2015, security researchers successfully demonstrated remote hijacking of vehicle systems, manipulating functions ranging from braking to infotainment [10]. Financial and operational damage from such incidents is substantial for major companies, some of which report recovery costs exceeding \$500,000 per breach [11]. Healthcare institutions have also been targeted,

with ransomware attacks encrypting critical patient data and demanding payment for its release [12]. High-profile hardware vulnerabilities like Meltdown and Spectre further underscore the risks inherent in modern computing architectures [13].

Figure 1.1 Connected IoT Devices Forecast by 2025 [5]

As connectivity among IoT devices grows, the risk of malware-based attacks increases significantly. A single infected device can spread malware to others in the network, triggering a chain reaction that may compromise sensitive system information. The absence of strong security mechanisms at the device level can make such infections especially damaging. Although previous research has explored the types of malware threats IoT systems face, relatively little attention has been given to developing effective countermeasures for infected or compromised IoT devices.

Preserving privacy and ensuring security in IoT systems entails a range of technical and procedural challenges. First, trust must be established across the entire lifecycle of each device, from development and manufacturing to deployment and decommissioning [14]. Equally important is the protection of secrets within embedded devices. Secure key storage and tamper-resistant provisioning mechanisms are essential. Although modern cryptographic algorithms can address many system-level vulnerabilities, long-term security remains elusive, particularly in the case of side-channel attacks and speculative execution flaws. Firmware updates represent another vector of vulnerability, exposing IoT endpoints to attack if not secured properly. Physical tampering and the lack of standardized defenses further complicate secure system design. Standardization efforts, while necessary, progress slowly and often lag behind emerging threats. To reduce liability and improve resilience, security considerations must be integrated into the design phase of IoT products. The next section surveys existing security solutions that form the state of the art in protecting embedded IoT systems.

## 1.2 State of the Art

The challenges outlined in the previous section have motivated researchers to explore security techniques aimed at preventing malicious adversaries from compromising critical operations in IoT systems. This section reviews existing security solutions for protecting IoT endpoint devices, with an emphasis on attestation techniques.

Memory protection is a common hardware-based countermeasure, involving the use of Memory Protection Units (MPUs) [15] and Memory Management Units (MMUs) [16] to prevent unauthorized access to sensitive memory regions by unprivileged software components. Early solutions, such as the segmentation mechanism introduced in Intel's 80286 architecture, linked memory segments to privilege levels, thereby enforcing access restrictions. More recently, Execution-Aware

Memory Protection (EA-MPU) [17] has been proposed to associate code segments with specific data regions, allowing for finer-grained isolation of software modules within a trusted runtime environment. Remote attestation is a foundational technique for verifying the internal state of an untrusted device (the *prover*) by a trusted entity (the *verifier*) [18]. It enables use cases such as secure firmware updates, patch validation, and system integrity checks across embedded platforms. Attestation protocols generally fall into three categories: (1) software-based, (2) hardware-based, and (3) hybrid schemes.

Software-based attestation techniques leverage platform constraints to detect unauthorized modifications. One notable example is Pioneer, proposed by Seshadri et al. in 2005 [19], which implements a software-based attestation technique by computing memory checksums using a verifier-specified algorithm. The design introduces intentional timing overhead to detect unauthorized modifications, as deviations in execution time can reveal compromise of the attestation code or underlying memory state. Similar methods have been adapted for various embedded platforms [20–23]. Despite their conceptual appeal, software-only attestation schemes remain vulnerable to attacks and typically depend on restrictive assumptions about the adversary's capabilities. These include the requirement of exclusive one-to-one communication between the verifier and the prover, which prohibits third-party attestation and reduces protocol flexibility. Moreover, the lack of persistent secret storage on the device necessitates such constraints. To address these shortcomings, some proposals introduce minimal hardware extensions for securely storing cryptographic secrets [24], [25]. However, even lightweight trust anchors often demand exclusive access to system resources, making it infeasible to support multiple trusted execution environments concurrently. As a result, software-based attestation schemes are generally unsuitable for deployment in realistic, multi-context IoT scenarios.

Hardware-based attestation schemes gained early traction with mechanisms such as Secure Boot [26], introduced by Arbaugh et al. in 1997. Secure Boot verifies the integrity of system components at startup using a trusted bootloader that hashes memory content and compares it with a signed reference hash stored in ROM. Another widely adopted mechanism is the Trusted Platform Module (TPM) [27], which extends this principle using Platform Configuration Registers (PCRs) for securely storing integrity measurements. TPM-enabled systems establish trust through early boot processes, supported by the BIOS. Several experimental TPM-based approaches have been studied [28–30]. Commercial alternatives, such as ARM TrustZone [31], implement secure execution environments via a set of privileged registers and isolated on-chip memory. However, these static root-of-trust models do not adequately protect against runtime attacks such as Return-Oriented Programming (ROP) [32]. Addressing these threats requires dynamic root-of-trust architectures that provide runtime integrity verification [33]. These approaches do not provide dynamic root of trust, while the cost of the TPM module is prohibitive for low-end embedded devices.

Dynamic Root of Trust (DRT) architectures extend TPM specifications and has been implemented by vendors such as Intel and AMD [34, 35]. These systems dynamically isolate memory regions and use CPU instructions to reset PCRs and measure memory contents during execution. While TrustZone is primarily based on secure boot, it has also been repurposed to support DRT functionality [36, 37]. McCune et al. introduced *Flicker* [38], a system architecture that utilizes Intel TXT and AMD SVM technologies to establish a dynamic root of trust on commodity computing platforms. Flicker ensures the secure execution of a minimal, isolated code segment, referred to as a Piece of Application Logic (PAL), even when critical system components such as the BIOS, operating system, or DMA subsystems are compromised by an adversary. Building on this foundation, *TrustVisor* was later proposed by McCune et al. [39] as an enhancement that integrates a minimal hypervisor to reduce performance overhead while maintaining strong isolation guarantees for PALs. Despite their robustness, these architectures rely heavily on platform-specific hardware features and impose

significant resource demands, making them impractical for constrained IoT environments. Other research efforts have explored trust establishment in remote systems using similar principles [40], [41].

To overcome the limitations of pure software and heavyweight hardware schemes, hybrid attestation approaches have been proposed. The Software-Protected Module (SPM), introduced by Strackx et al. [42], represents an early hardware-supported process isolation mechanism built atop a static root of trust. It achieves software compartmentalization by loading and measuring protected application logic into designated secure memory regions, referred to as “vaults.” While SPM offers strong isolation guarantees, it is primarily designed for high-end platforms equipped with Memory Management Units (MMUs) or Memory Protection Units (MPUs), limiting its feasibility on low-cost embedded systems. To overcome these constraints, Sancus [43] extends the SPM paradigm for low-end microcontrollers, achieving secure module isolation without relying on trusted software stacks. It supports remote attestation and inter-module message authentication via specialized hardware instructions. Similarly, SMART, proposed by El Defrawy et al. [44], introduces a minimalist hardware-software co-design for dynamic root-of-trust establishment on devices lacking MMUs or TPMs. SMART requires modest hardware modifications to the system’s microcontroller to achieve attestation and memory integrity verification. TrustLite [45] builds upon this concept by integrating an Execution-Aware Memory Protection Unit (EA-MPU), enabling fine-grained isolation of lightweight software modules, referred to as “trustlets.” The platform also supports secure boot, ensuring the authenticity and confidentiality of trustlet code. More recent research has proposed further refinements of these lightweight architectures to support remote attestation and secure execution in severely resource-constrained embedded environments [46-48].

England et al. [49] demonstrated that even a minimal feature, such as a hardware-locked secret accessible only by boot ROM, can provide sufficient guarantees for boot-time attestation. Building on this insight, the Trusted Computing Group introduced the Device Identifier Composition Engine (DICE) [50], a lightweight attestation framework tailored for resource-constrained IoT devices. Its feasibility has been validated in multiple studies [51, 52].

### 1.3 Main Contributions

Building on the review of attestation methods in the previous section, this thesis identifies a critical gap in existing research: the absence of a unified, lightweight, and hardware-constrained security architecture capable of establishing trust across the full IoT device lifecycle. Although prior work addresses specific aspects, such as resilient transmission protocols or cryptographic primitives, few approaches integrate these into a cohesive end-to-end solution that begins at the silicon level and extends to cloud-based service infrastructure. This continuity of trust is essential, particularly for IoT environments characterized by limited computational resources, minimal silicon capabilities, and cost-sensitive deployment constraints.

This study proposes an end-to-end attestation architecture that maps robust security mechanisms onto commercially available hardware, enabling trust establishment from device provisioning to remote authentication. A key requirement addressed is the development of a device-specific authentication mechanism, grounded in a dedicated hardware-derived value, that enables secure interaction with remote cloud infrastructures. By combining minimal hardware trust anchors with proven cryptographic methods, the proposed design facilitates the creation of a cryptographically strong device identity and supports the secure delivery and verification of firmware updates.

The primary contributions of this thesis are as follows:

1. **Design of an Asymmetric Attestation Protocol**

A lightweight attestation protocol tailored for resource-constrained IoT nodes is proposed. It combines secure boot, proven cryptographic primitives, and the Device Identifier Composition Engine (DICE) standard to create an adaptable architecture. At its core, the protocol derives a cryptographic identity from a statistically unique hardware root of trust. It also incorporates an authentication mechanism for device-to-cloud communication via TLS and supports secure, over-the-air firmware updates with integrated data protection.

2. **Security Analysis and Threat Modeling**

A qualitative security evaluation is conducted based on the STRIDE threat modeling methodology. The analysis identifies potential threats across system components and communication interfaces, characterizing attacker capabilities, risk impact, and attack scalability. Based on this assessment, targeted countermeasures are formulated to address each identified vulnerability.

3. **Prototype Implementation on Embedded Hardware**

The proposed attestation protocol is implemented on a commercial STM32 Nucleo-74LG board, which features a 32-bit ARM Cortex-M4 microcontroller. This prototype serves as a proof of concept, demonstrating the feasibility of deploying the security architecture on low-power embedded platforms.

4. **Quantitative Evaluation and Performance Metrics**

The final implementation is evaluated in terms of runtime performance and memory footprint. Metrics such as clock cycle overhead and memory utilization are measured to assess the practicality of deploying the protocol on real-world resource-constrained devices.

## 1.4 Thesis Outline

The remainder of this thesis is structured as follows:

- **Chapter 2** presents essential background on security in edge-to-edge IoT systems. It introduces core principles and countermeasures against security threats, encompassing cryptographic algorithms, resilient communication protocols, hardware security features, and attestation techniques. Special attention is given to lightweight and silicon-efficient architectures, with a focus on the Device Identifier Composition Engine (DICE) as a representative model for cryptographically agile trust anchors.

- **Chapter 3** introduces the design of a security protocol for asymmetric remote attestation tailored to resource-constrained IoT devices. It begins with a V-Model-inspired design methodology, followed by a structured analysis of the system's functional, non-functional, and security requirements. The chapter details the protocol's layered architecture, including key derivation and operational flows across the device lifecycle. It concludes with a threat modeling assessment based on the STRIDE framework to evaluate the design's resilience against adversarial threats.

- **Chapter 4** describes the implementation and evaluation of a prototype that realizes the proposed protocol on a commercial STM32 microcontroller. Implementation details, design decisions, and performance metrics, such as memory usage and execution overhead, are presented to assess the feasibility of the architecture.

- **Chapter 5** summarizes the key findings and contributions of this work. It also discusses identified limitations and suggests potential directions for future research.

## 2 Background

*This chapter provides foundational background on security principles, techniques, and technologies relevant to embedded systems. Section 2.1 introduces core concepts in embedded systems security, distinguishing between information security, which encompasses confidentiality, integrity, and authentication, and device security, which pertains to the protection of platforms responsible for processing sensitive data. Section 2.2 explores the role of cryptographic techniques in building secure systems, emphasizing the evolution and application of modern encryption schemes. Section 2.3 reviews authentication mechanisms and trust models underpinning Public Key Infrastructure (PKI), while Section 2.4 examines the Transport Layer Security (TLS) protocol as a cornerstone for secure communication between clients and servers. Finally, Section 2.5 presents the Device Identifier Composition Engine (DICE), a lightweight, cryptographically agile attestation framework designed for resource-constrained embedded devices.*

### 2.1 Embedded Systems Security

An embedded system is a computing system designed for implementing dedicated functions within a larger system, electrical or mechanical [53]. It is a combination of computer hardware, software and optionally mechanical parts, referring to any computing system other than general purpose or mainframe computers [54]. Embedded systems run real-time operating systems (RTOS) that are aiming to control device-dedicated applications with real-time computing constraints. The low manufacturing cost of embedded systems makes them highly beneficial in a variety of intelligent and industrial application domains such as automotive electronics, factory automation, smart homes, transportation, commerce and finance, healthcare and many others [55]. Embedded systems are considered either closed or open depending on which level they communicate and share information with one another [56]. Within a closed system, devices interact only with devices that are part of that system, often through protocols and standards designed exclusively for the needs of the closed system. For example, modern cars are equipped with smart sensing and control systems that communicate and exchange information among these systems. However, the communicated data is not shared with other systems or devices outside of the car, for example the car manufacturer. Embedded systems connected with other devices or systems through a network are considered open embedded systems. Open embedded systems exchange data with other devices and systems using open communication standards and protocols for purposes such as information sharing.

The increasing number of embedded devices connected to the Internet formulates the Internet of Things (IoT). There does not exist only one definition as to what comprises the “Internet of Things”. According to [57], the IoT refers to a set of embedded devices or “things” that are embedded with software, sensors, and network and are capable of communicating data with one another. The “things” can use their communication protocols, although some sort of Internet connection may be necessary at some point. The term “Internet” does not necessarily refer to communication via Internet protocols. Apart from connecting embedded devices to the Internet, the IoT allows these devices to collect and exchange data. Data communication provides the IoT endpoint devices with flexibility minimizing the need for physical connectivity and manual intervention. The exchanged data, for example, the raw measurements of a humidity sensor are not of great value and do not produce any useful knowledge when examined individually. However, the manipulation of these data via filtering and contextualizing processes provides in-depth knowledge about the system, its users, the environment, and its objectives. Adding context to the exchanged raw information, patterns can be created containing information about a particular activity of the device. Categorization and processing of these data also

provide information regarding the repetition of certain processes. Finally, the organization of data provides valuable information regarding the relationships formulated between different pieces of information.

The growing deployment of interconnected systems renders necessary the increased protection of computer systems, networks and communication data, against sophisticated attacks from malicious cybercriminals, ensuring the security and reliability of the information systems. Interconnected embedded systems face important security challenges related to their resource constrained nature. Their limited processing capabilities, the battery-driven power, the wireless network connectivity, and the remote control of their software, render these devices vulnerable against attackers. These attacks may compromise important security properties resulting in loss of control of embedded systems. Therefore, the security of embedded systems is considered end-to-end, starting from the physical endpoint devices that receive and transmit data, to hubs and gateways layer that aggregate the edge devices to the large network, to cloud-based systems that store and analyze the data provided by the edge nodes. This section focuses on two important types of embedded systems security: (1) the information security, and (2) the device or platform security.

### **2.1.1 Information Security**

The practice of protecting information and the systems that use, store, or transmit that information is defined as cybersecurity [58]. Cybersecurity is also known as information security and concerns the mitigation of security risks by preventing unauthorized access, use, or modification of information data [59]. According to Pipkin in the “Information security: protecting the global enterprise”, information security is the process of protecting the intellectual property of a company or organization [60]. The primary focus of information security is balancing the security risks by providing information assurances and by defining a set of security goals [61]. These goals are the result of a security analysis called risk management process and include a variety of security attributes and guidelines that span multiple disciplines based on the security model in use. Risk management involves the identification of information assets and potential threats, a risk evaluation of the impact of the identifying threats, a valid mitigation plan to address these risks, and the selection and implementation of appropriate security techniques [62].

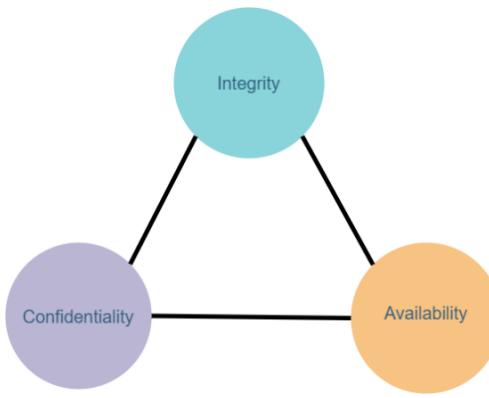

One of the first security models in information security is the “Guidelines for the Security Systems and Networks” that was proposed by the Organization for Economic Cooperation and Development (OECD) in 1992. According to this model, there are nine security principles to consider, including awareness, responsibility, response, ethics, democracy, risk management, security design and implementation, security management and reassessment [63]. In 1998, Donn Parker in his MSc thesis with the title “The Parkerian Hexad” proposed the six elements of information [64], while in 2004, the National Institute of Standards and Technology (NIST) proposed 33 fundamental principles in their study “Engineering Principles for Information Technology Security” [65]. Another suggested security model is the information security management maturity standard O-ISM3, published by the Open Group [66]. According to this model, a set of management policies is proposed after the definition of the required security targets. Information security focuses on the balanced protection of the confidentiality, integrity, and availability of data, three of the most important attributes of information [67]. Together they formulate the C.I.A. triangle, a well-known and widely accepted security standard for computer security (Figure 2.1). The C.I.A. triangle is also referred to as the A.I.C triad to avoid confusion with the intelligence agency in the USA.

Figure 2.1 The C.I.A triad of Information Security

### Confidentiality

Confidentiality is a security principle referring to the concealment of valuable information or resources in sensitive areas such as governance and industries [68]. Government services often apply classification systems that restrict the access to sensitive content to classified personnel [69]. The appearance of such systems is traced back in the mid-nineteenth century when the British Government published the “*Official Secret Act*”, a document concerning diplomatic espionage and information disclosure [70]. Similar principles apply to the industry sector where companies protect their intellectual property by preventing competitors from gaining access to design information regarding their products. Confidentiality also refers to the fact that sometimes revealing the information is more important than the information itself. For example, the reveal that a company secretly monitors its employees is more important than the findings of such an action. Another important aspect of confidentiality is hiding critical systems and resources that an entity may not wish to be used without proper authorization. Examples of compromised confidentiality are password theft and email phishing. Protection of sensitive information concerns the definition of strict access policies that arrange the data into categories, according to the type of personnel that has access to it and their sensitivity level. Common confidentiality policies include biometric verification, two-factor authentication and traditional Unix-file access control lists. However, mechanisms that enforce confidentiality in a system should be trusted that they supply the correct verification data.

### Integrity

Integrity constitutes a basic security element of information security that refers to the trustworthiness and accuracy of data resources and is responsible for protecting sensitive data against unauthorized alterations [71]. Integrity concerns not only the integrity of the data but the integrity of its source, a method often referred to as authentication. The reliability of the source of the information plays a vital role for a system to gain credibility and trust. For example, the credibility of the source of any news in a newspaper or magazine determines if the news is fake or not. Integrity mechanisms can be classified into two categories, detection mechanisms and prevention mechanisms. Integrity detection mechanisms report whether an information is trusted, or an integrity violation exists. Detection mechanisms use analysis tools to detect possible violations and report any corruption that may occur. Prevention mechanisms deny any unauthorized attempt to alter sensible data, or any attempt to alter data in unauthorized ways. Modifications or deletions from authorized users should be performed with caution in order to avoid unintentional or malicious alterations. For example, a company’s authorized employee tries to embezzle money instead of moving it into a trusted account.

## Availability

Availability refers to the last component of the triad and concerns the ability of data to be present and available when needed [72]. Systems with high availability aim to remain available at all times and at all costs, preventing failures and disruptions. This requires the design of a statistical model that analyzes the patterns of use and the existence of mechanisms able to act on these patterns. Ensuring availability involves protection against denial-of-service-attacks. In these kinds of attacks, a malicious attacker may deliberately deny access to services or information by making the system unavailable. Denial-of-service attacks have proven to be quite challenging to detect. The analyst should be able to determine if any unusual change in patterns of use is due to normal malfunctions or deliberate manipulation of the system resources by the adversary.

Although the CIA triad provides notable security policies for the information technology, it is debatable whether it can keep up with the latest technological developments and distinguish security from privacy [73]. The CIA triad gives the impression of a holistic security solution that is the answer to most of the security problems. However, it tends to ignore other equally important factors and therefore it should be considered only as a part of a broader security approach.

### 2.1.2 Device Security

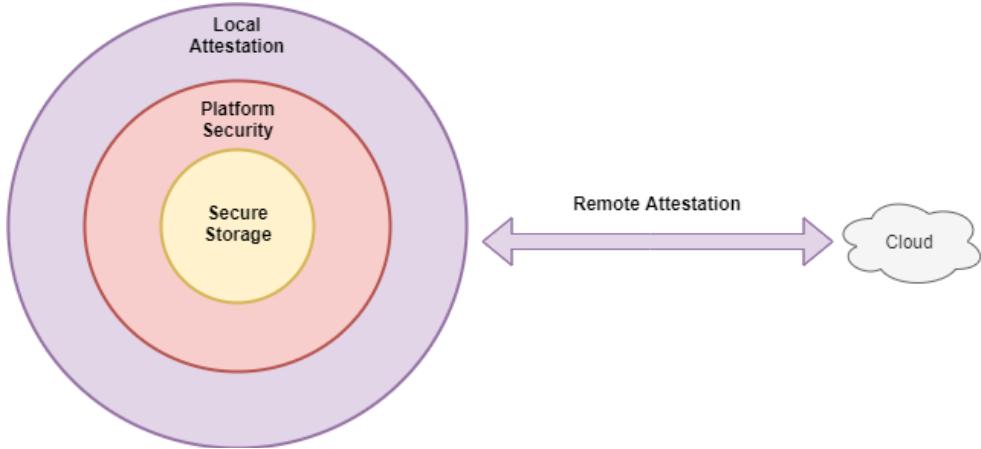

Designing a trustworthy security approach for interconnected embedded devices goes beyond satisfying the basic principles of information security, such as confidentiality, integrity, availability, and non-repudiation, and extends to the device itself. Device security involves a range of security solutions that protect device resources and sensitive data from physical tampering, network attacks, and unauthorized access by malicious adversaries. These solutions vary from software protection techniques targeting remotely accessible devices to physical protection mechanisms that secure platform sensitive information. The rapid proliferation and deployment of embedded devices renders the design of device security solutions quite challenging. This section presents an overview of effective device security techniques and methods in a layered fashion, where each layer corresponds to the protection of a specific security feature. Figure 2.2 illustrates three device security layers: (1) secure storage of key device security components, (2) memory protection and secure boot mechanisms known as platform security, and (3) remote attestation authentication schemes that ensure code integrity when connecting to a remote cloud provider.

#### Secure Storage

Secure storage is an important device security mechanism that stores confidential data and cryptographic secret keys, namely the Root of Trust (RoT). The RoT is the basis of the device's unique identity, and it is inherently trusted every time the device is booted or reset [74]. At startup, the generation and provisioning of an immutable root secret must be ensured in order to establish reliable device authentication and secure communication. The generated root secret is typically encrypted and stored in non-volatile memory units, such as One Time Programmable (OTP) memory. One of the main benefits of OTP memory units is that they are programmable in a secure environment during device manufacturing. However, the provisioning of the root key during manufacturing lurks the risk of potential secret leakage to third parties. Physical Unclonable Functions (PUFs) is a flexible key provisioning solution aiming to circumvent this limitation. PUFs are electronic design components that exploit the unique silicon properties of individual integrated circuits (ICs) to create a statistically unique identity bound to the device [75]. The trusted generation and provisioning of the root keys ensures that the key material is unique and specific to the device, non-cloneable, non-modifiable by malicious adversaries, and unknown to non-authenticated third parties.

Figure 2.2 Device Security Techniques

### Platform Security

The second layer of device security involves the enforcement of access control mechanisms and secure booting processes to enhance trustworthiness within the device. The first prevents unauthorized third parties from accessing sensitive device resources, while the latter ensures the integrity and authenticity of device firmware. It is important that access control mechanisms are implemented at all levels, both user and system. On a user level, authentication is ensured using simple methods, such as PIN entry, or even biometric identifiers, such as fingerprints or facial patterns [76]. On a system level, it is essential to mitigate the risk of unauthorized usage from malicious adversaries by providing protected access to System on Chip (SoC) busses and interfaces. The Memory Protection Unit (MPU) is an embedded system component that prevents access to confidential data stored in memory, by setting access permissions and attributes to specified memory regions [77]. Secure boot is the part of platform security responsible for validating the authenticity and integrity of the code running on the device [78]. A secure boot process involves trusted bootloaders, strong encryption schemes, and secure storage units, which ensure that only authorized firmware is executed when the device powers up. A typical example of code authentication is the storage of firmware in flash memory, executed by a trusted bootloader during boot.

### Attestation

The last layer of device security concerns a process that verifies the identity of the internal state of an embedded device, namely attestation [79]. Architectures equipped with attestation capabilities provide adequate security guarantees of the attested software state of the device to a trusted third party, called verifier. Attestation can be classified as local and remote attestation. The first refers to an intra-platform mechanism, where application modules running on the same platform verify and authenticate their respective software images with one another. An example of local attestation is the Intel SGX Report mechanism that provides confidentiality, code integrity, and strong protection within the device [80]. Remote attestation involves an external trusted verifier entity for verifying the integrity of the code running on the device. Attestation is typically performed by calculating a code measurement of the attested software module and by sending it to the trusted third entity during manufacturing. The verifier may request the module code measurement at any time verifying its validity. A number of remote and local attestation solutions have been proposed by academia including software-based schemes, hardware-based protocols, and hybrid techniques. Attestation schemes are useful tools for a variety of services related to embedded devices such as over-the-air (OTA) software updates and patches, memory reset, and malware replacement.

## 2.2 Cryptography

This section provides the reader with useful background information regarding the terms and concepts behind basic cryptographic methods and techniques. Also, a detailed description of various cryptographic algorithms is given along with examples of their applications in numerous areas of information security. Cryptographic systems provide solutions towards mitigating the security threats and attacks present in embedded systems.

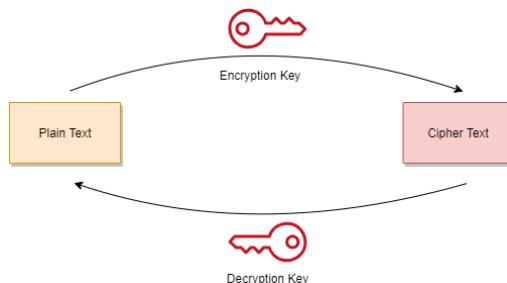

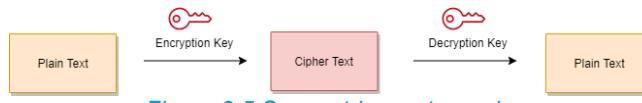

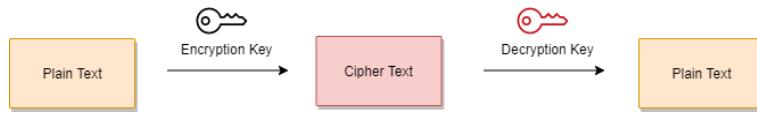

Cryptography can be described as the method of concealing information during communication, in the presence of malicious entities called adversaries [81]. The prefix “*crypt-*” of the term derives from the Greek word “*kryptos*” and means hidden or secret, while the suffix “-*graphy*” originates from the word “*graphein*”, which stands for writing or script in Greek [82]. Cryptography is closely associated with encryption, a technique of transforming ordinary information, called plaintext, into an unintelligible form called ciphertext [83]. Another term for encryption, though less common, is encipherment, with decipherment or decryption standing for the opposite procedure. Both encryption and decryption rely upon a cipher, a procedure of well-defined steps known as algorithm and a piece of information, called key. The key is a secret value known only to the parties that communicate, the absence of which makes it impossible to decrypt ciphertext into plaintext and vice-versa (Figure 2.3). The communicating parties share the secret key with one another, a cryptographic method called key exchange or key establishment [84]. Key exchange together with a finite set of plaintexts, ciphertexts, keys, encryption and decryption algorithms constitute a cryptosystem. Cryptosystems can be classified into two kinds, symmetric and asymmetric. Symmetric systems use the same key to encrypt and decrypt the transmitted message. Asymmetric systems, on the other hand, use a public key to encrypt a message and a private secret key to decrypt it. In the crypto field, the common nomenclature for two communicating parties is usually “*Bob*” and “*Alice*”, while a malicious third party is referred to as “*Malory*”, an eavesdropper as “*Eve*” and a trusted party as “*Trend*”.

Figure 2.3 Cryptographic Encryption/Decryption

Cryptography is also related to the terms of cryptology and cryptanalysis. Cryptanalysis refers to the science of analyzing a cryptographic scheme aiming to expose possible vulnerabilities. It is performed either by searching for loopholes in the mathematical basis of the cipher or by finding logical flaws in its design [85]. A famous example of cryptanalysis is the breaking of the Enigma machine, the encryption device developed and used for encrypting military operations during the World War II [86]. Cryptology refers to a broader term that encompasses both cryptography and cryptanalysis, including designing of ciphers, key exchange techniques and cryptanalysis tools [87]. Applications of cryptography span multiple disciplines from electronic commerce and wireless payments to military communications and digital crypto currencies. Although cryptography has proven a powerful weapon against malicious adversaries, it is also being used as a tool for espionage, forcing several governments to constrain its use.

The attempt to establish message confidentiality in communications dates back to the ancient world, where political diplomats and military emissaries understood the necessity of a mechanism capable of concealing valuable information from the enemy. Sensitive messages were transported in safe boxes and were protected against tampering by armed envoys. The first proof of the use of cryptography is an encrypted text curved in stone in the Old Kingdom of Egypt at 1900 B.C. [88]. However, the true nature of that message remains a mystery to researchers. Stenography was a well-known method of information concealment, used by the Ancient Greeks and Persians of the fifth century B.C. and involved the use of microdots, invisible ink and merge of words with images [89]. Other classical cryptographic methods are transportation ciphers and substitution ciphers. Transportation ciphers refer to rearrangement of the order of the letters in a message, while substitution ciphers allow the replacement of groups of letters with other letters. The most famous substitution cipher is the Caesar cipher, where each letter in the plain text is shifted three positions further down the alphabet [90]. Most of these ciphers became vulnerable to cryptanalysis after the discovery of frequency analysis by the Arab mathematician Al-Kindi in the 9th century as they were based on the premise that the adversary has no knowledge of the cipher itself [91]. It was until the 19th century when Auguste Kerckhoffs claimed that a cryptographic scheme should remain secret even in the unwanted case of leak to the adversary, formulating the Kerckhoffs's principle. Kerckhoffs's principle was restated by the founder of information theory, Claude Shannon, formulating the fundamental theory of theoretical cryptography, the Shannon's Maxim [92].

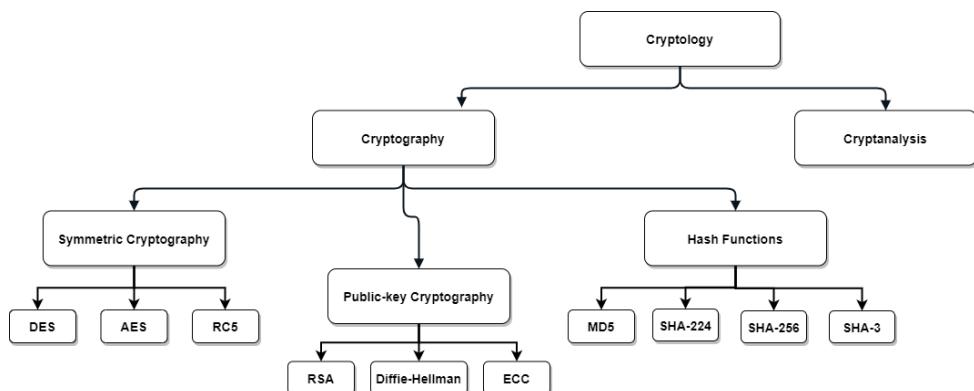

By the end of the twentieth century, rapid advancements in telecommunications, electronics and computing systems led to revolution in the communications sector. Computing systems have become smaller, more powerful and cheaper and are able to communicate and exchange information via interconnected networks. Modern Cryptography constitutes a vital aspect of secure communications and is related to main principles of information security such as confidentiality, data integrity, system availability, authentication and non-repudiation. Modern cryptographic systems are based on mathematical algorithms and computer science principles rendering the breaking of such systems computationally exhausting and impractical, as it would require unlimited computing power and resources. The biggest challenge of these algorithms is the growing concerns regarding the processing power of future quantum computing systems and their ability to break many of the current cryptography encryption standards. Quantum computing systems make use of the quantum bits capable of representing both zero and one and performing two calculations at once, hence being computationally more powerful [93]. The cryptographic algorithms of modern cryptography are categorized into three types, based on the number of keys used for encryption and decryption, namely secret key of symmetric cryptography, public-key or asymmetric cryptography and hash functions (Figure 2.4).

Figure 2.4 Classification of Cryptographic Algorithms

### 2.2.1 Symmetric Cryptography

Symmetric or secret key cryptography refers to information concealing methods where both communication entities share a single key for both encryption and decryption providing privacy and confidentiality (Figure 2.5). The secure key distribution between the two communicating entities is known as the key distribution problem, a limitation of symmetric cryptography [94]. Cryptographic schemes that follow this type of cryptography are classified into two categories, namely stream ciphers and block ciphers. Stream ciphers encrypt a single bit of plaintext at a time, using a relatively long stream of pseudorandom bits as key material. This pseudorandom generator needs to remain unpredictable so that the derived key gets to change constantly. Although stream ciphers do not propagate transmission errors, their periodic nature causes a repetition of the keystream, a vulnerability known to potential attackers [95]. A well-known application stream cipher is One-Time Pad, an ideal cipher that performs pure random key generation achieving maximum secrecy [96]. In contrast to stream ciphers, block ciphers are encryption schemes using a fixed size block of data for encryption at a time. The size of plaintext block is the same as the ciphertext block and varies from 64 bits to 128 and 256 bits. In cases of shorter size of plaintext bits, padding schemes are used [97]. A well-known block cipher is the Feistel cipher, where the encryption and decryption stages are similar causing a considerable reduction in size of code.

Figure 2.5 Symmetric cryptography

The majority of symmetric algorithms used today for secure communications are designed by cryptographers and mathematicians aiming to render the decryption of ciphertext infeasible without the possession of the appropriate encryption key. One of the most well-known and well-studied symmetric algorithms is the Data Encryption Standard (DES), designed by the National Bureau of Standards (NBS) in 1977 for governmental purposes [98]. The DES algorithm is a complex block cipher with key size of 56 bits and block size of 64 bits, designed for fast hardware implementations. In 1998 the NSA managed to break the DES algorithm using brute-force attack, exposing a mathematical backdoor in its design. This fact motivated the academic community to propose a DES variant called triple-DES that made the DES algorithm more robust [99]. However, the security implications of DES led the NSA to introduce a new cryptosystem called Advanced Encryption Standard (AES). The AES describes a 128-bit block cipher that features a key with 128, 192 and 256 bits and became a standard in December 2001 [100]. Other important symmetric ciphers that are considered secure are ChaCha20 and RC5 [101]. Although the sufficient key size for a symmetric algorithm to be considered as secure is between 112 and 128 bits, advances in quantum cryptography come as a threat to the level of security these algorithms possess.

### 2.2.2 Public Key Cryptography

Public-key cryptography, also referred to as asymmetric key cryptography, is a revolutionary cryptographic scheme proposed by Martin Hellman and Whitfield Diffie in 1976 aiming to mitigate the shortcomings of symmetric key cryptography regarding key distribution. The basic principle of asymmetric cryptography concerns the generation of a cryptographically related key pair consisting of a freely distributed part called public key and a secret part called private key, where it is computationally infeasible to derive one from the other [102]. While one key is used for plaintext encryption, the other is used for decrypting the ciphertext, regardless of which key is applied first (Figure 2.6). Public-key cryptography also concerns a user authentication mechanism that proves the identity of the message

sender. In essence, one communication entity (“Alice”) encrypts information using its private key, while the other entity (“Bob”) is capable of decrypting it, using the freely shared public key of *Alice*. In the described scenario, the sending entity cannot deny the sending of the message satisfying the non-repudiation security principle. Diffie and Hellman proven the feasibility of asymmetric cryptography by introducing the Diffie-Hellman key exchange protocol, where the two communicating parties should first agree upon a shared encryption key [103].

Figure 2.6 Public Key cryptography

The first successful attempt of an asymmetric scheme is the RSA algorithm that took its name from the initials of its creators, namely Ronald Rivest, Adi Shamir and Leonard Adleman, three notable MIT mathematicians [104]. RSA spans a wide range of uses from key exchange and digital signatures to encryption of small data blocks. The derived key pair is the product of two prime numbers with length of 100 or more bits each, yielding in a very large number  $n$ . Although it is difficult for an attacker to determine the prime factors of  $n$ , the advancements of modern computing systems to factorize large numbers, are becoming a potential threat to the algorithm. In 2005, a test aiming to factor a 200-digit number was performed and took almost 50 years in computation time, while in 2009 Kleinjung claimed that factoring a 1024-bit RSA number would require almost one thousand years. Apart from the RSA, Diffie and Hellman proposed their own asymmetric cryptography suitable for key exchange. Another approach to public key cryptography is the Elliptic-curve Cryptography (ECC) which is based upon elliptic curves over finite fields. ECC uses smaller keys in comparison with RSA is suitable for resource constrained devices such as endpoint IoT devices [105]. ECC algorithms are suitable for key agreement and digital signatures and may be used in combination with symmetric encryption schemes. An example of such a scheme is the Elliptic-curve Diffie-Hellman (ECDH) key agreement protocol proposed by Diffie and Hellman [106]. Finally, the Digital Signature Algorithm (DSA) refers to digital signature capabilities with X.509 standard to be the most used format of this algorithm [107].

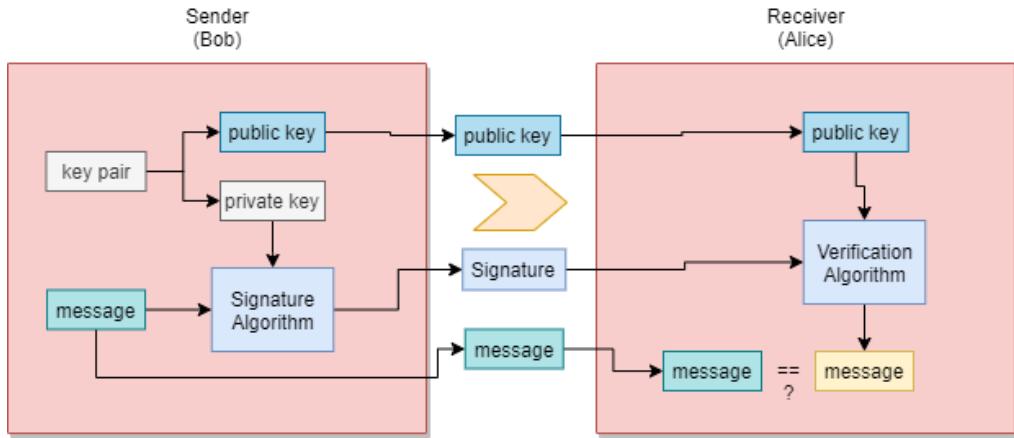

An important element of public key cryptography is a mathematical scheme for validating the authenticity of digital documents and messages, called digital signature. Digital signatures provide strong authentication and message integrity capabilities, enhancing the trust between two communication entities. Digital signatures are part of cryptographic methods and techniques applied in various applications such as online financial transactions, internet banking and software distribution [108]. A user authentication example using digital signatures is illustrated in Figure 2.7, where two communication parties validate one another. The sender entity “Bob” sends a message to the verifier entity “Alice”, together with a digital signature that proves the authenticity of his identity. “Bob” feeds the message data to a signature algorithm and signs it with his private key, called encryption key. The produced digital signature is appended to the message and then both are sent to the receiver entity. The message receiver “Alice” verifies the authenticity of “Bob” by decrypting the received signature with the freely distributed public key of “Bob”. This key is called verification key and is adamant towards the signature decryption. In case the resulting message value is different, “Alice” may correctly assume that the received message has been forged by a malicious adversary. On the contrary, if the signature gets verified by “Alice”, that means that non-repudiation is provided as only “Bob” could be the sender of the message.

Figure 2.7 User authentication scheme

### 2.2.3 Hash Functions and Message Authentication Codes

Hash functions constitute the third type of modern cryptographic algorithms known also as one-way functions and message digests. Hash functions are capable of encrypting plaintext data irreversibly without the use of encryption keys by computing a fixed-length hash value of the plaintext. Any change in the message contexts will effectively result in the calculation of a completely different hash value, ensuring data integrity [109]. Cryptographic hash functions add a layer of security by verifying the authenticity of received data from an unknown source. Hash functions span a wide range of applications from digital fingerprints on sensitive file data to deployments in operating systems for password encryption purposes. A well-studied family of hash algorithms is the Message Digest (MD) algorithms that produce a 128-bit hash value regardless of the message length. MD4 is a well-known example of the MD family developed by Rivest for fast processing in software that is now broken [110]. After the appearance of vulnerabilities in the MD4 algorithm, an improved cryptographic scheme was introduced by Hans Dobbertin in 1996, under the name MD5 in his work *"Cryptanalysis of MD5 Compress"* [111]. The US national Security Agency (NSA) developed another important hash function family, the Secure Hash Algorithm standard (SHA) [112]. SHA-1 is the first deployed algorithm of the SHA family that produces a 160-bit hash value for data encryption. SHA-2 family was proposed by the NSA as an improvement to the SHA-1 family after reports of attacks against it. SHA-2 comprises of five algorithms namely SHA-1 plus, SHA-224, SHA-256, SHA-384 and SHA-512. Each one of the aforementioned algorithms is able to produce hash values of length 224, 256, 384 and 512 respectively. However, vulnerabilities in the SHA-2 family led NSA to introduce a third family that is called SHA-3 in 2012 [113].

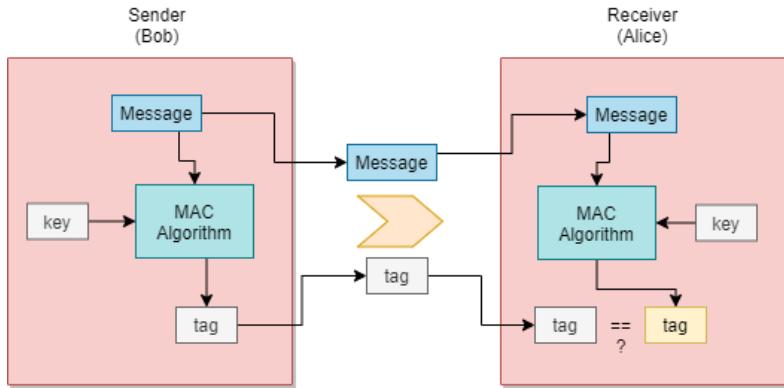

A similar integrity measurement scheme to the hash functions is the Message Authentication Codes (MACs). A MAC refers to a symmetric cryptographic technique capable of providing message authentication. Similar to hash, a MAC function encrypts an arbitrary long input of data into a fixed output using a key. A MAC consists of three algorithms, a key generator algorithm responsible for selection of a suitable key, a signing algorithm that returns a tag of the selected key and the message and a verifying algorithm that accepts or rejects the message [114]. In the example of Figure 2.8, the sending entity *"Bob"* creates a tag of the message that he wants to communicate with the receiving party *"Alice"*, using a key and a signing mac algorithm. The message together with the generated tag are send to *"Alice"*, who tries to generate her tag of the received message using the same key. The data integrity of the message is verified by an algorithm which compares the two tags and validates any possible tampering or alteration of the message. A special type of message authentication code is the hash-based MAC called HMAC. The HMAC uses a cryptographic hash function and a secret key for verifying the integrity of the data and authenticating the message.

Figure 2.8 Message Authentication Code (MAC) usage

## 2.3 Public Key Infrastructure

Today an increasing number of companies are using the Internet as a platform to conduct their business transactions, including retail sales, marketing, and business-to-business operations. Although e-commerce has become an important tool for modern companies, it poses significant security and integrity issues. Online transactions differ from the traditional face-to-face business model and therefore require the development of robust security mechanisms. Symmetric cryptography is an ideal solution for data encryption, ensuring the confidentiality and privacy of the transaction data. Public key cryptography offers user authentication and non-repudiation, allowing companies and customers to validate their respective identities. Finally, hash functions and MACs provide data integrity, enhancing confidence between customers and enterprises. However, proper implementation of security requires more than sound cryptography. It involves the establishment of trust among the communication entities. Public key infrastructure (PKI) is a framework based on public key cryptography, that provides trustworthy digital communications over a network [115]. In cryptography, the PKI refers to the binding of public keys with digital identities of entities such as people or companies. PKI is an essential component of the overall system security strategy and a foundation element of network security.

### 2.3.1 PKI Components

This section demonstrates the key components of PKI facilitating trusted communications with confidentiality, integrity and non-repudiation among the communication parties. PKI involves public key certificates, certificate authorities, registration authorities, registration and insurance certificate policies, a centralized certificate management system, certificate chains, and hardware security modules.

#### Digital Certificates

In the dynamic environment of e-commerce, online transactions are performed among digital representations of physical entities such as people or organizations. These digital entities need to prove the authenticity of their identity while communicating with one another over a network. In PKI, digital identities are represented by digital documents called public key certificates or identity certificates. Public key certificates certify the binding of a digital identity to its public key, allowing another entity to validate the identity of the certificate owner. Digital certificates secure confidential information with encrypting methods and sign public keys with digital signatures, ensuring tamper protection. Typically, a certificate contains the public key of an entity, identifying information regarding the certificate owner, the name of the certificate issuer and the expiration date of the certificate. The certificate owner is called subject entity and usually differs from the issuer. However, there are certificates called self-issued certificates, where the two fields are identical. Additional information included in a digital certificate are

the types of cryptographic algorithms used, policies that describe how the certificate may be used, a serial number of the certificate, and a digital signature of the issuing entity of the certificate. Perhaps the most common used format for digital certificates is described by the IETF X.509 standard in the RFC 2459 document [116]. However, there is no single definition of digital certificates which allow vendors and users to generate their own version of digital certificates. Public key certificates are widely used to authenticate HTTPS-based websites, where web browsers validate the authenticity of a HTTPS web server, ensuring that there are no eavesdroppers during the client-server communication. However, digital certificates are vulnerable against treats and attacks from malicious adversaries. For example, a web browser may not notify a user in case of changes in the certificate provider or expiration date.

### **Certificate Authorities**

The foundation element of PKI is a trusted third party called certificate authority (CA), responsible for issuing, signing, and storing digital certificates [117]. Examples of certificate authorities are a company that issues certificates to its employees or an internet service issuing certificates to its users. An end-user requesting a digital certificate from a certificate authority creates a certificate signing request (CSR), which contains the public key of the end-user and useful identity information such as the name of the certificate owner. The CSR is digitally signed with the private key of the certificate owner and is sent to a certificate authority called registration authority (RA). Registration authorities are responsible for accepting or rejecting requests for digital certificates and authenticating the subject entities of these requests. The authentication process involves the decryption of the end-user signature, incorporated in the CSR, using the public key of the end-user. Subsequently, an RA performs due diligence tests on the end-entity, examining the subject name, validity date and other important identity information. Although RAs constitute an important PKI element, they are not entitled to sign or issue digital certificates. After validating the end-user authenticity, a certificate authority signs the certificate request with its secret signing key, issuing a digital certificate. The issued certificates should be unique for constantly valid maintaining the trustworthiness provided by the CA. The validation mechanism of issued certificates is performed by a PKI entity called validation authority (VA). Common validation techniques involve the revocation of compromised or lost keys and the protection of public and private keys. Revocation information regarding invalid certificates is provided via the Online Certificate Status Protocol (OCSP) and Certificate Revocation Lists (CRLs). Prominent certificate authorities currently available in the market include DigiCert and Sectigo [118]. Common problems with certificate authorities involve purchases of cheap, low quality certificates from end-entities, dropping the quality of the certificate chain. Another CA vulnerability is unexpected changes to the built-in list of root-certificates provided to all web browsers by certified organizations. Such changes might be performed by inexperienced or even malicious developers resulting in erroneous certificates.

### **Chain of Trust**

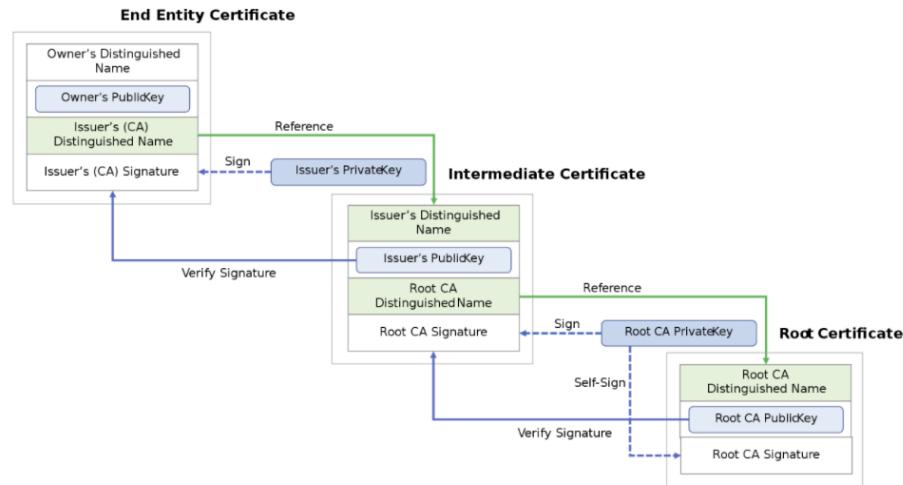

Certificate authorities enhance the validation capabilities of their authentication mechanism by establishing trust relationships with other CAs. A well-known method to achieve that is the use of certificate chain or chain of trust. Chain of trust refers to a list of certificates that authenticate one another in a hierarchical manner [119]. Starting from an end-entity, certificates are issued and signed by certificates higher in the certificate hierarchy, using the secret key corresponding to the next certificate in the chain. The authentication process involves the verification of the signature of the target certificate using the corresponding public key of the next certificate, until the last certificate in the chain is reached. The last certificate in the chain is a self-signed certificate which is inherently trusted by users. This certificate is called root certificate and is the trust anchor of the chain of trust. In case the

root certificate gets compromised by a malicious adversary, then all certificates issued by the root CA will be affected, resulting in re-issuing of new certificates, the validity of which will be questionable. Therefore, it is important for root CAs to use intermediate authorities to sign and issue end-entity certificates. A useful schema representing a chain of trust between three certificates is illustrated in Figure 2.9.

Figure 2.9 Certificate chain of Trust

### Hardware Security Module

The trustworthiness of a Certificate Authority (CA) critically depends on the secure generation, storage, and usage of its private keys, operations typically performed within a **Hardware Security Module (HSM)**. An HSM is a tamper-resistant cryptographic processor that generates, stores, and executes cryptographic functions, such as digital signing and key management, entirely within its secure hardware perimeter, ensuring that private keys never leave the protected environment [120]. These devices are often certified under standards like FIPS 140-2/3 and are widely used in environments requiring high assurance, including internet banking, Public Key Infrastructure (PKI) applications, and cryptocurrency systems.

### 2.3.2 Trust Models

The public key infrastructure involves security policies and methods equipped with authentication capabilities, in order to establish trust within a system. The trust relationships developed in the PKI framework are a result of a collection of rules known as trust models. In this section an overview of three well-known examples of trust models is presented.

#### Hierarchical Model

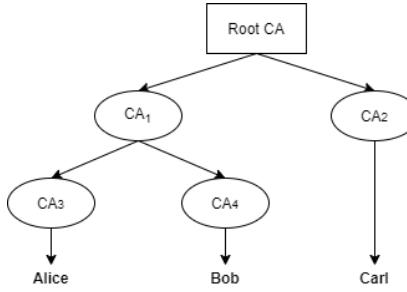

The most common implementation of the PKI is the hierarchical trust model. It refers to a tree model consisting of a number of certificate authorities and end-entities, arranged in a hierarchical manner [121]. The root node of the tree is called root CA, while the inner nodes are referred to as intermediate or subordinate CAs and the leaves as end-entities. The root CA is the PKI trust anchor and usually issues a self-signed certificate containing the public key used to verify certificates issued by the root CA. in the hierarchical model, trust is established via a certification path. This path consists of a sequence of certificates that authenticate certificates next in the hierarchy based on information provided from certificates higher in the tree. An example user authentication is described in Figure 2.10.

In this PKI framework, “Alice”, “Bob” and “Carl” are certified end-entities from different CAs. The end-entities “Alice” and “Bob” trust each other as they share a common issuing CA. Although “Alice” and “Carl” have different issuing certificate entities, they share a common root CA. In order for “Alice” to establish trust relationship with “Carl”, she needs to verify the certification path of “Carl”. The certification path consists of a self-signed certificate of the root CA, a signed certificate of the intermediate CA2 by the root CA, and the end-entity certificate of “Carl” signed by CA2. Since “Alice” inherently trusts the root CA, she subsequently trusts the intermediate CA2 and the end-entity “Carl”.

Figure 2.10 Hierarchical trust model

A tiered hierarchy with multiple CAs offers a high level of control mitigating the risk of trust violation. However, the number of intermediate CAs increases the administrative effort required to maintain the hierarchy and thus increases the risk. This can be very practical in the Internet environment where multiple users are connected to a web server. If the trustworthiness of the server gets compromised, all users are notified at once and refused access. However, this can be very impractical in e-commerce transactions where communication is on a one-on-one basis. On the other hand, a flat hierarchy using a single CA as trust anchor is more flexible and requires less administrative effort. The drawback of this hierarchy type is corruption of the entire certificate chain, in case of a failure in the root CA.

### Peer-to-peer Model

The most basic PKI trust model is the direct or peer-to-peer model. In this model, there is no intermediate trusted third party and end-entities establish trust with one another on a direct manner [122]. Each end-entity relies on a local CA to issue its certificate, creating a local trust domain. In the local domain, the end-entity can verify the validity of the local CA signature, using the public key of that CA. The direct connection between the end-entity and the local CA ensures the secure provision of the CA’s public key to the end-entity. An example of a direct communication within a trust domain is the installation of software updates from a Linux server located on the Internet to a local machine. The server public key is usually provisioned either in the Linux distribution or in a CD or DVD, ensuring protection against theft from a malicious adversary. This model offers flexibility, making the extension of trust domain quite convenient. However, the increasing number of local CAs makes the manageability of the system quite challenging. Therefore, the peer-to-peer trust model is not an ideal candidate for e-commerce or web browsing. A variation of the peer-to-peer trust model is the cross-certification model. This model allows the CAs of two different trust domains to authenticate the public key to one another, creating a bidirectional trust.

### Web of Trust

In cryptography, the term web of trust refers to decentralized systems where end-entities authenticate one another without using trusted third parties. Contrary to the hierarchical PKI model, no third party ensures the integrity and authenticity of an end-entity. End-entities are allowed to specify the validity of their certificate by indicating the number of trusted signatures placed on that certificate. The web of

trust works better with small groups of end-entities who have preexisting trust relationships. However, it does not scale well with big numbers of end nodes being unsuitable for e-commerce transactions [123]. The web of trust is applicable to a variety of well-known systems such as the PGP, GnuPG and other OpenPGP-related systems. Pretty Good Privacy (PGP) is a private e-mail scheme based on public key methods. A communication entity maintains a list of all trusted public keys of the entities that the entity trusts, formulating a web of trustworthy users. For example, the user “Bob” may obtain the public key of user “Alice” via an e-mail or a server containing the public key of “Alice”. “Bob” is not aware of the validity of the stored key and therefore assumes that it is valid. Trust among users is established on a one-to-one basis. For example, the fact that user “Carol” claims that he has a copy of “Alice’s” key in his database, does not necessarily mean that “Bob” should trust that key, even though he trusts “Alice”. An important characteristic of this model is that trust establishment is not transitional and there is no chain of trust among the users of the web.

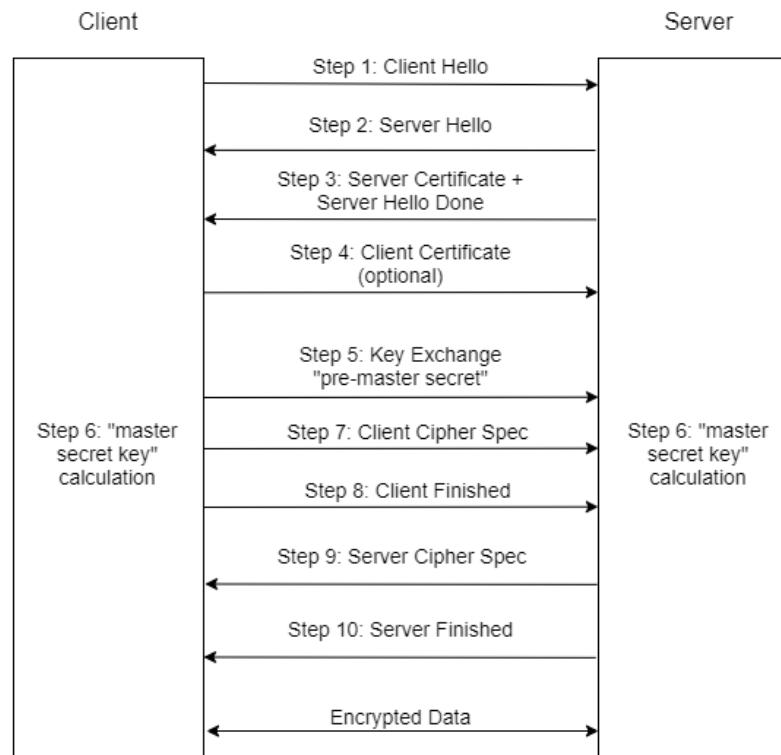

## 2.4 Transport layer Security