## A PVT-Robust Open-loop Gm-Ratio ×16 Gain Residue Amplifier for >1 GS/s Pipelined ADCs

Dias, Diogo; Goes, João; Costa, Tiago

DOI

10.1109/ISCAS58744.2024.10558154

Publication date

**Document Version**Final published version

Published in

ISCAS 2024 - IEEE International Symposium on Circuits and Systems

Citation (APA)

Dias, D., Goes, J., & Costa, T. (2024). A PVT-Robust Open-loop Gm-Ratio ×16 Gain Residue Amplifier for >1 GS/s Pipelined ADCs. In *ISCAS 2024 - IEEE International Symposium on Circuits and Systems* (Proceedings - IEEE International Symposium on Circuits and Systems). IEEE. https://doi.org/10.1109/ISCAS58744.2024.10558154

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# A PVT-Robust Open-loop Gm-Ratio $\times 16$ Gain Residue Amplifier for >1 GS/s Pipelined ADCs

Diogo Dias, João Goes

Department of Electrical and Computers Engineering

School of Science and Technology

NOVA University of Lisbon

Almada, Portugal

das.dias@campus.fct.unl.pt, goes@fct.unl.pt

Tiago Costa

Department of Microelectronics

Faculty of Electrical Eng., Mathematics and Computer Science

Delft University of Technology

Delft, The Netherlands

t.m.l.dacosta@tudelft.nl

Abstract—This work presents the design and simulation of a PVT-robust x16 gain dynamic open-loop inverter-based Gm-ratio residue-amplifier for high-speed SAR-assisted pipeline ADCs. The amplifier is designed in a 28 nm standard bulk CMOS process with a regulated 0.9 V power supply and simulated across a -20°C to 85°C temperature range. It achieves a power dissipation of 1.67 mW at 1.3 GHz, corresponding to a power-speed ratio of 1.28 mW/GHz, with less than  $\pm 5\%$  gain variation throughout all temperature corners in typical conditions.

Index Terms—pipeline analog-to-digital converter (ADC), PVT-robust residue amplifier, gm-ratio residue amplifier

#### I. INTRODUCTION

Successive-approximations-register (SAR) assisted pipeline analog-to-digital converters (ADCs) enable moderate-to-high resolution and conversion-rate applications while improving the energy efficiency that pipeline ADCs typically exhibit [1]. A first-stage with higher resolution enabled by a fast SAR-ADC facilitates the linearity improvement of pipeline ADCs. However, this makes the design of a residue-amplifier (RA) with a accurate DC-gain challenging.

RA DC-gain inaccuracies due to process-voltage-supplytemperature (PVT) variations severely impact the resolution of the ADC. Digital calibration techniques can compensate for PVT-variations, but require the interruption of the conversion process, limiting conversion-rates. It also requires additional circuitry, increasing complexity and power dissipation [2], [3]. Analog PVT compensation schemes using DC bias sensing and control provide an alternative to digital calibration. Classic closed-loop static OTA designs offer PVT-robust RAs through negative feedback but have lower energy efficiency at high conversion rates [4]. Dynamic open-loop amplifiers achieve higher energy efficiency and conversion speeds but are more sensitive to PVT-variations due to the lack of common-mode control. Additional analog circuitry can be used to implement PVT-dependent settling time at the expense of introducing device mismatch issues [5-7]. Multistage closed-loop dynamic amplifier topologies, such as ring amplifiers and floatinginverter amplifiers (FIAs), offer PVT-robust RA architectures but have lower energy efficiency and stability issues at high

This work was financed by national grants from UI/BD/153604/2022, and funded through the UIDB/00066/2020 project.

speeds [2], [3], [8]. Open-loop dynamic gm-ratio residueamplifiers (GGRA) enable energy-efficient high-speed RAs with accurate gain but still require digital reference-trimming strategies to mitigate the lack of DC gain accuracy throughout PVT corners [9], [10]. Additionally, due to the devices' lower output impedance, achieving moderate-to-high DC gains in GGRAs requires aggressive power dissipation and area tradeoffs at advanced technology nodes. Power dissipation can be minimised through the use of minimum channel-length (Lch) devices in high-speed channels, but requires disproportional channel-width (Wch) ratios within GGRA architectures to compensate for the lack of DC gain, leading to additional distortion, power dissipation, and die-area. Increasing the output impedance of each stage within GGRAs can thus lead to lower power-dissipation and smaller die area. Three approaches can be used to increase the output impedance of inverter-based OTAs: 1) sacrificing bandwidth and power dissipation for longer channel lengths, 2) sacrificing voltage headroom and output swing for the use of cascode devices, 3) using a harmonic-injection cross-coupled pair (HXCP) as a negative resistor at the output of the inverter-based OTA at the expense of additional power-dissipation [11].

This work presents a PVT-robust ×16 gain dynamic open-loop inverter-based GGRA. It comprises common-mode feed-forward (CMFF) and feedback (CMFB) networks to address PVT-variations-related CM shifts and DC gain errors. An HXCP is used to lower the RA's output conductance without reducing its output voltage swing, leading to higher DC gain with lower power-dissipation and die area, while also compensating for the additional output load caused by CMFF and CMFB networks. The document is divided into five sections: overall pipelined-SAR ADC architecture and RA specifications (Section II), study and design methodology of the proposed RA (Section III), discussion of the simulation results (Section IV), and conclusions and a comparison with the current state-of-the-art (Section V).

### II. SAR-ASSISTED PIPELINE ADC ARCHITECTURE OVERVIEW

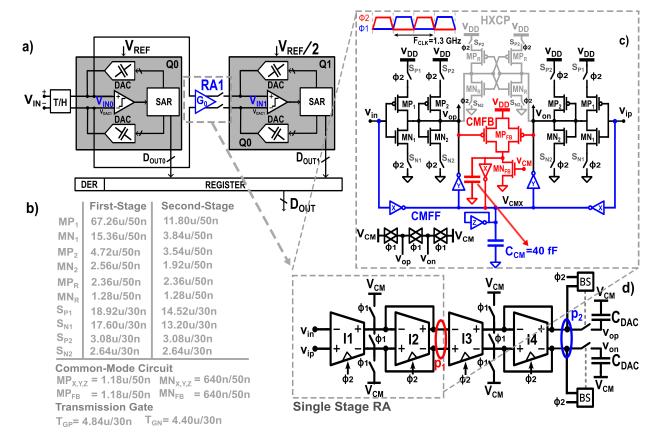

A 12-bit SAR-assisted 2-stage pipeline ADC is shown in Fig.1 a). It comprises a 6-bit front-end SAR-ADC quantizer

Fig. 1. a) 12-bit SAR-Assisted Pipeline ADC architecture, b) Gm-Ratio two-stage RA sizings, c) Proposed inverter-based Gm cell using common-mode feedback and feedforward circuits, d) Gm-Ratio two-stage RA block-architecture. The non-explicit bulk terminals of the PMOS and NMOS devices indicate that the bulks are connected to  $V_{\rm DD}$  and  $V_{\rm SS}$ , respectively.

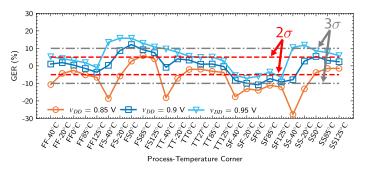

(Q0) with 1-bit redundancy, followed by a 7-bit back-end quantizer (Q1). The  $\times 16$  DC gain of the RA complements with the  $\times 2$  gain of Q1's DAC to achieve the required  $\times 32$  gain. Limitted by the kT/C noise constraints to ensure the target effective number of bits (ENOB) of > 9.0 bits, the total load capacitances of Q0 and Q1's DAC are 640 fF and 40 fF, respectively. Accounting for voltage supply variations, the gain-error-ratio (GER) limits for the RA are bound to  $\pm$  5% ( $3\sigma$ ), to facilitate the achievement of the target ENOB.

#### III. PROPOSED RESIDUE AMPLIFIER

#### A. Common-mode Feedback and Feedforward

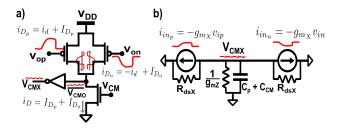

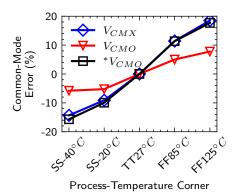

The RA (Fig.1 d)) is implemented by cascading two GGRA stages (Fig.1 c)). The design features core devices only. The common-mode feedforward circuit (CMFF) and common-mode feedback circuit (CMFB) are represented in Fig.1 c) in blue and red, respectively. The CMFF and CMFB circuits provide a negative CM feedback directly applied to the  $V_{\rm op}$  and  $V_{\rm on}$  nodes through the Y inverters (IY). CM voltage variations due to PVT-variations are compensated through the shared  $V_{CMX}$  node, as depicted in Fig.2 c). The CMFF is implemented through inverters X (IX), cancelling out their output AC currents at the  $V_{\rm CMX}$  node, as represented in Fig.2 b). The CMFB is implemented through devices MPFB

and  $\mathrm{MN_{FB}}$ , operating in the saturation region and cancelling out their channel AC currents, as shown in Fig.2 a). The resulting DC current establishes a  $\overline{\mathrm{V_{CMO}}}$  DC voltage with the opposite dynamic of the output CM voltage (V<sub>CMO</sub>) at the drain of  $\mathrm{MN_{FB}}$ . The Z inverter (IZ) introduces a CM pole  $s_{P_{CM}} \approx -g_{m_Z}/C_{CM}$ , filtering out unwanted, switching-related, high-frequency harmonics from  $V_{CMX}$ .

#### B. Single-Stage Analysis

1) PVT-Variations Sensitivity Analysis: The gain of a single stage k of the RA  $(A_{Vk}(s))$  is shown in (1), obtained using the small-signals model circuit in Fig.1 c).

$$A_{Vk}(s) = -2 \frac{G_{mk,1} - C_{dgk,1}s}{G_{mk,2} + g_o - G_{mk,R} + s(C_{Lk} + C_{Pk})}$$

(1)

where  $G_{m\,k,1}$  and  $G_{m\,k,2}$  are the transconductances of the first and second inverter of the RA, respectively,  $g_o$  is the total output conductance of the stage,  $G_{m\,k,R}$  is the transconductance of the HXCP's IR inverter,  $C_{L\,k}$  is the load capacitance of the stage and  $C_{P\,k}$  is the total parasitic capacitance at the output node.

The sensitivity of  $A_{Vk}(0)$  against channel transconductance  $(G_m)$  variations of each OTA is shown in (2). This result was

Fig. 2. a) Common-mode feedback circuit, b) Equivalent small-signal model of the common-mode feedforward circuit.

used to study the impact of PVT-variations on the DC gain of

$$\begin{split} S_{G_{m}}^{A_{V\,k}(0)} &= \frac{\partial A_{V\,k}(0)}{\partial G_{m\,k,1}} \frac{G_{m\,k,1}}{A_{V\,k}(0)} + \frac{\partial A_{V\,k}(0)}{\partial G_{m_{K}}} \frac{G_{m\,k,2}}{A_{V\,k}(0)} + \\ &+ \frac{\partial A_{V\,k}(0)}{\partial G_{m\,k,R}} \frac{G_{m\,k,R}}{A_{V\,k}(0)} = \frac{g_{o}}{G_{m\,k,2} + g_{o} - G_{m\,k,R}} \end{split} \tag{2}$$

Equation (2) shows that reducing the output conductance  $g_o$ by increasing  $L_{ch}$  or boosting  $G_{m\,k,2}$  by enlarging the OTA's  $W_{ch}$  decreases  $|S_{G_m}^{A_{V\,k}(0)}|$ , being in conformity Pelgrom's Law [12]. However, increasing  $G_{m\,k,R}$  increases PVT variations in each stage's DC gain. Moderately scaling up HXCP's devices is needed to reduce die area and power-dissipation, allowing scale-down of the RA's main devices  $(M1 - M4)_{AB}$ .

2) Non Linear Distortion and Noise: Careful CM pole placement and proper reset transmission gate sizing facilitates differential DC offset spur cancelling. Even harmonics are eliminated from the differential output signal. In such conditions, a single RA stage's total harmonic distortion (THD) is dominated by the third-order harmonic distortion (HD3) within its bandwidth, as expressed (3).

$$HD_3 \approx \left| \eta / \left( 3 \eta + \frac{4 \left( G_{m \, k, 2} - G_{m \, k, R} + \frac{G_{m \, k, 1}}{A_{V \, k}(0)} \right)}{\left( A_{in} A_{V \, k}(0) \right)^2} \right) \right|$$

(3)

where  $\eta = G_{m\,k,2}^{(3)} - G_{m\,k,R}^{(3)} + \frac{G_{m\,k,1}^{(3)}}{(A_{V\,k}(0))^3}$ ,  $G_{m\,X}^{(3)} = \frac{1}{3}\left(g_{m\,3_{N\,X}} + g_{m\,3_{P\,X}}\right)$  and  $g_{m\,3_{N\,X}}$  is modelled using the FKV transition model.

Eq. (3) shows that increasing the transconductance of each inverter will extend the bandwidth of the stage, decreasing the settling-time, and consequently decreasing HD3. On the other hand, increasing the DC gain of each stage (either by increasing  $G_{mk,R}$  or the  $L_{CH}$  of the CMOS devices) will limit its bandwidth, leading to an increase in HD3.

$$Vn_{i}^{2} = \int_{0}^{\infty} \frac{S_{V_{o}}(f)}{|A_{Vk}(f)|^{2}} df \approx \frac{S_{V_{o}}(0)}{|A_{Vk}(0)|^{2}} \left[\Delta f\right]_{0}^{\frac{\pi}{2}GBW} =$$

$$= \frac{Tk_{B} \left(\gamma_{n} + \gamma_{p}\right)}{C_{Lk} + C_{Pk}} \left(1 + \frac{(G_{mk,2} + G_{mk,R})}{G_{mk,1}}\right) (V^{2})$$

$$(4)$$

The total input-referred output noise of a single stage is shown in (4), where  $\gamma_n$  and  $\gamma_p$  are the thermal noise coefficients of the NMOS and PMOS devices, respectively,

Fig. 3. Simulation behaviour of the CMFB and CMFF circuits.  $*V_{\rm CMO}$  is the uncontrolled output CM voltage,  $V_{\rm CMO}$  is the controlled output CM voltage and  $V_{\rm CMX}$  is the resulting CM node controlling the output CM voltage.

T is the temperature in Kelvin,  $k_B$  is the Boltzmann constant. While the dynamic RA is not immune to jitter noise, it amplifies a sampled input residue voltage with a much lower frequency than the RA's clock phases  $(F_{CLK})$ . Hence, jitter noise is disregarded in this analysis. Flicker noise contributions  $(v_{\rm nf}^2 \propto (WLF_{\rm CLK})^{-1})$  are also negligible due to the high  $F_{\rm CLK}$  and wide gate area used for each main inverter device. Thus, the main noise contribution is due to sampled thermal noise multiplied by an excess noise factor (ENF)  $\Gamma = \left(1 + \frac{(G_{m\,k,2} + G_{m\,k,R})}{G_{m\,k,1}}\right)$ . Increasing  $G_{m\,k,R}$  to boost the DC gain of each stage results in a higher ENF. Careful sizing of the HXCP's devices is thus required to avoid excessive distortion and noise contributions.

#### C. Design Methodology

The proposed RA presents a total open loop gain of  $G(s) = A_{v,1}(s) A_{v,2}(s)$ , featuring a pole at the first and second stage's output,  $s_{p1}$  and  $s_{p2}$  respectively. The GBW of the RA is determined using a dominant pole approximation GBW =  $|G(0)|f_{p2}$ , where  $f_{p2}$  denotes the second stage's pole frequency. In this scope, GBW  $\geq 10 f_{\rm p2}$  and  $f_{\rm p2} \geq$  $[1.5-2.5]\,F_{CLK}$  are the specifications used to establish the required settling-time at  $F_S/2$ .

A minimum channel length of  $L_{CH} = 50 \text{ nm}$  is used for inverter devices, offering the best balance between intrinsic gain, gain accuracy, and speed under PVT conditions. NMOS and PMOS switches have a minimum channel length of  $L_{CH} = 30 \text{ nm}$ . Key design steps involve creating a minimumsize inverter I<sub>U</sub> with dimensions that align its trip-point  $(V_{Trip})$  with the common-mode voltage  $(V_{CM} = \frac{V_{DD} + V_{SS}}{2})$ . A scaling factor  $M_X$  can thus be used to represent a scaled-up version of I<sub>U</sub>, simplifying the design of the system.

To minimize  $Vn_i^2$  and achieve a dominant pole approximation, the first stage's weights must be scaled higher than the second stage's to ensure  $f_{\rm p1} \geq [1.5-2.0]\,{\rm GBW}$ . Increasing the gain of the first stage in relation to the second reduces the power-dissipation and noise contribution of the RA. The DC gain is designed to achieve a [-20%; -15%] gain error, further corrected by increasing W<sub>ch</sub> of HXCP devices.

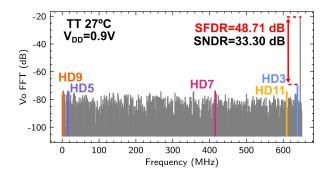

Fig. 4. 1024 points FFT simulation results, obtained for a nominal  $V_{\rm DD}=0.9~{\rm V}$  at  $f_{in}=F_S/2~{\rm Hz}$ , for a typical process corner (TT) at the temperature of  $T=27^{\circ}{\rm C}$ .

Two bootstrapped switches are added to the RA outputs to allow ADC pipelining operations and maintain linearity during its tracking and amplification-phase (phase  $\Phi 2$ ) [13]. Precise design of  $S_P$  and  $S_N$  switches is crucial to limit the supply voltage deviation from the devices' sources to under 10 mV, preventing differential DC offset, common-mode ripple, and distortion.

#### IV. SIMULATION RESULTS DISCUSSION

A 1.3 GHz clock signal with a 50% duty cycle generated non-overlapping RA clock phases. DC gain and GER were determined from samples taken at the end of RA amplification (phase  $\Phi 2$ ). A fast fourier transform (FFT) analysis of the differential output voltage provided SNDR, SFDR, and gain measurements within a simulation time window of 0.8 ns to 807.7 ns using 1024 frequency bins (Fig. 4). The proposed RA dissipates 1.67 mW at 1.3 GHz in typical conditions, yielding a power-to-speed ratio of 1.28 mW/GHz. This ratio is the lowest among RAs with DC gain above  $\times 10$  in channels exceeding 1 GS/s, as shown in Table I.

#### A. PVT-variations simulation results

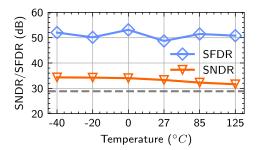

Schematic PVT simulations covered all extreme NMOS-PMOS process corners for three supply voltages (0.85V, 0.9V, 0.95V) and temperatures ranging from -40°C to 125°C. The gain error ratio (GER) was computed through the relative error in relation to the RA's nominal gain of  $\times 16$ . The RA achieved an SFDR of 48.71 dB, with stable SNDR above 28.85 dB, removing the ADC linearity bottleneck, enabling it to achieve an ENOB above 9.5 bits (Fig.4 and Fig.5). The DC gain only collapses at the lowest voltage supply and temperature, due to the collapse of the transconductances. However, it remains within  $\pm 5\%$  limits for the FF, SS, and TT process corners across temperature for the nominal voltage supply. FS and SF corners showed higher and lower DC gain, respectively, but are still within a  $2\sigma$  GER threshold. High NMOS charged-carriers mobility and a large M<sub>N1</sub> to M<sub>N2</sub> ratio for high open-loop DC gain severely impact the RA's settled DC gain. Lower DC gains with reduced transconductance ratios enhance process variation robustness.

Fig. 5. Simulated spurious-free dynamic-range (SFDR) and signal-to-noise and distortion ratio (SNDR), obtained at  $f_{in} = F_S/2$  Hz for a typical process-voltage-supply-temperature corner (TT,  $V_{\rm DD} = 0.9$  V, T = 27 °C).

Fig. 6. Simulation results of the GER of the proposed RA across PVT corners at  $f_{in}=F_S/2$  Hz.

#### V. CONCLUSIONS

This work introduces a  $\times 16$  gain PVT-robust open-loop inverter-based Gm-ratio RA for high-speed pipelined ADCs. It's implemented in a 28 nm standard CMOS process with a 0.9 V power supply. It employs HXCP to minimize output conductance's impact on DC gain, achieving nominal gain with more relaxed die area and power-dissipation tradeoffs. Simulations across PVT corners ranging between the target design temperature of -20°C to 85°C show less than  $\pm 5\%$  gain variation under typical conditions. The RA dissipates 1.67 mW at 1.3 GHz, yielding a power-speed ratio of 1.28 mW/GHz, setting a benchmark for RAs with a DC gain above  $\times 10$ .

TABLE I STATE-OF-THE-ART COMPARISON.

|                | [6]*       | [9]**      | [10]**     | This Work* |

|----------------|------------|------------|------------|------------|

| Process (nm)   | 28         | 40         | 28         | 28         |

| Supply         |            |            |            |            |

| Voltage (V)    | 0.9        | 1.2        | 1.0        | 0.9        |

| Nominal        |            |            |            |            |

| Gain (V/V)     | 6          | 12         | 8          | 16         |

| Temp.          |            |            |            |            |

| Range (°C)     | [-40, 125] | [-40, 125] | [-40, 125] | [-20, 85]  |

| GER-Temp.      |            |            |            |            |

| Ratio (%/°C)   | 0.018      | 0.121      | 0.010      | 0.028      |

| Power-Speed    |            |            |            |            |

| Ratio (mW/GHz) | 0.55       | 4.30       | 4.59       | 1.28       |

| Calibrated     | No         | No***      | No***      | No         |

#### REFERENCES

- [1] C. C. Lee and M. P. Flynn, "A 12b 50ms/s 3.5mw sar assisted 2-stage pipeline adc," in 2010 Symposium on VLSI Circuits, 2010, pp. 239–240.

- [2] Y. Chen, J. Wang, H. Hu, F. Ye, and J. Ren, "A 200ms/s, 11 bit sar-assisted pipeline adc with bias-enhanced ring amplifier," in 2017 IEEE International Symposium on Circuits and Systems (ISCAS), 2017, pp. 1-4

- [3] J.-C. Wang and T.-H. Kuo, "A 72-db sndr 130-ms/s 0.8-mw pipelined-sar adc using a distributed averaging correlated level shifting ring amplifier," *IEEE Journal of Solid-State Circuits*, vol. 57, no. 12, pp. 3794–3803, 2022.

- [4] H.-Y. Lee, B. Lee, and U.-K. Moon, "A 31.3fj/conversion-step 70.4db sndr 30ms/s 1.2v two-step pipelined adc in 0.13μm cmos," in 2012 IEEE International Solid-State Circuits Conference, 2012, pp. 474–476.

- [5] H. Huang, S. Sarkar, B. Elies, and Y. Chiu, "28.4 a 12b 330ms/s pipelined-sar adc with pvt-stabilized dynamic amplifier achieving ¡1db sndr variation," in 2017 IEEE International Solid-State Circuits Conference (ISSCC), 2017, pp. 472–473.

- [6] J. Goes, B. Tardivel, J. de Melo, and J. Marques, "A temperature-compensated class-ab parametric residue amplifier for sar-assisted pipeline adcs," in 2020 IEEE International Symposium on Circuits and Systems (ISCAS), 2020, pp. 1–5.

- [7] W. Jiang, Y. Zhu, M. Zhang, C.-H. Chan, and R. P. Martins, "A temperature-stabilized single-channel 1-gs/s 60-db sndr sar-assisted pipelined adc with dynamic gm-r-based amplifier," *IEEE Journal of Solid-State Circuits*, vol. 55, no. 2, pp. 322–332, 2020.

- [8] X. Tang, X. Yang, J. Liu, W. Shi, D. Z. Pan, and N. Sun, "27.4 a 0.4-to-40ms/s 75.7db-sndr fully dynamic event-driven pipelined adc with 3-stage cascoded floating inverter amplifier," in 2021 IEEE International Solid- State Circuits Conference (ISSCC), vol. 64, 2021, pp. 376–378.

- [9] X. Guo, R. Chen, R. Xu, B. Li, and Z. Q. Chen, "A calibration-free 13b 625ms/s tri-state pipelined-sar adc with pvt-insensitive inverter-based residue amplifier," in 2022 IEEE Custom Integrated Circuits Conference (CICC), 2022, pp. 01–02.

- [10] Y. Cao, M. Zhang, Y. Zhu, C.-H. Chan, and R. P. Martins, "10.3 a single-channel 12b 2gs/s pvt-robust pipelined adc with critically damped ring amplifier and time-domain quantizer," in 2023 IEEE International Solid-State Circuits Conference (ISSCC), 2023, pp. 9–11.

- [11] L. Fang, T. Fu, X. Wen, and P. Gui, "A 12-b 1-gs/s 61-db sndr pipelined-sar adc with inverter-based residual amplifier and tunable harmonic-injecting cross-coupled-pair for distortion cancelation achieving 6.3 fj/conv-step," *IEEE Solid-State Circuits Letters*, vol. 5, pp. 194–197, 2022.

- [12] M. Pelgrom, A. Duinmaijer, and A. Welbers, "Matching properties of mos transistors," *IEEE Journal of Solid-State Circuits*, vol. 24, no. 5, pp. 1433–1439, 1989.

- [13] C.-C. Liu, S.-J. Chang, G.-Y. Huang, and Y.-Z. Lin, "A 10-bit 50-ms/s sar adc with a monotonic capacitor switching procedure," *IEEE Journal* of Solid-State Circuits, vol. 45, no. 4, pp. 731–740, 2010.