# High Density Integrated Capacitors for Smart Catheters and Implants

Ву

#### Jeroen Naaborg

in partial fulfilment of the requirements for the degree of

#### Master of Science

in Biomedical Engineering

at the Delft University of Technology, to be defended publicly on Thursday August 22, 2019 at 16:00.

Supervisor: Prof. dr. ir. Ronald Dekker

Thesis committee: Prof. dr. ir. Ronald Dekker (Chair)

Prof. dr. P. M. Sarro Prof. dr. ir. W.A. Serdijn

An electronic version of this thesis is available at http://repository.tudelft.nl/.

### **Abstract**

The Flex-to-Rigid (F2R) technology platform is an interconnect platform to integrate heterogeneous electronic systems and devices onto a partially flexible chip for minimally invasive medical instruments. This technology platform allows for the integration of micro electro-mechanical systems (MEMS) and integrated circuits (IC) on a chip in a planar plane, which can later be folded into any arbitrary shape. Downscaling of the technology and the increasing number of integrated components in the F2R platform have a high impact on the power distribution and consequently on the signal integrity. It is widely accepted that one of the most powerful strategies to encounter signal integrity problems is to use decoupling capacitors. However, there is an inherent trade-off between the capacitance and size of a capacitor.

This thesis is focused on the development on high density capacitors for the integration in the F2R technology platform. One of the objectives was to increase the capacitance density. Because there is limited space available on the F2R chip, additional area to increase the capacitance is found in the depth of the silicon. By etching multiple trenches into the silicon, a capacitance density increase by a factor of 10 is obtained. To even further increase the capacitance, the use of a silicon dioxide — silicon nitride — silicon dioxide multilayer (ONO) dielectric is reviewed. Moreover, a first step has been made in the fabrication of high breakdown voltage and low breakdown voltage parts in this dielectric layer.

A second objective was to deliver the capacitors as a "building block" that can be implemented in the F2R process flow. Therefore, the process needs to be compatible with the standard IC and MEMS technologies that are available in the Philips Innovation Service cleanroom. The steps of the fabrication process are verified and where needed optimized, and a dedicated mask set is designed for the fabrication of the capacitors. With this mask set, the so called trench capacitors have been made. These test devices are characterized in terms of breakdown voltage and capacitance. It is found that the capacitance density can be increased by an order of magnitude with the introduction of trenches to the test devices. In addition, the advantage of a multilayer dielectric compared to a single layer dielectric is shown.

## Preface

This thesis concludes my master Biomedical Engineering degree. During this project, I worked at Philips research on the integration of high density capacitors in the Flex-to-Rigid (F2R) technology platform. The idea of doing my thesis on the subject of smart catheters and implantable devices, although it was not my field, came after attending an inspiring lecture by Ronald Dekker. Discovering the world of microfabrication was however a really nice experience, stimulated by the helpful people in the Philips Innovation Service cleanroom.

First of all, I would like to thank my supervisor Ronald Dekker for his assistance during the thesis and the opportunity of doing this project. Besides that I have learned a lot, I also enjoyed working at Philips. Secondly, I would like to thank Eugene Timmering for his guidance in the cleanroom and refreshing coffee. Furthermore, my thanks goes to Jian Li, Carlo Eugeni, Marcus Louwerse, Vincent Henneken and Johan Klootwijk for the enlightening discussion we had. To conclude I would like to thank my parents, the Sunday dinners together with grandpa were and will always be something to look forward to.

J. Naaborg

Eindhoven, August 22, 2019

# Nomenclature

AC Alternating Current

BOE Buffered Oxide Etch

CAD Coronary Atrial Disease

CCP Capacitively Coupled Plasma

CMUT Capacitive Micro-machined Ultrasound Transducers

CVD Chemical Vapor Deposition

DC Direct Current

DRIE Deep Reactive Ion Etching

EPD End Point Detection

F2R Flex-to-Rigid

FEM Focus Exposure Matrix

HARMS High-Aspect Ratio Microstructures

IC integrated circuit

ICP Inductively Coupled Plasma

IVUS Intravascular Ultrasound

LPCVD Low Pressure Chemical Vapor Deposition

LTO Low Temperature Oxidation

MCM Multi-Chip Modules

MEMS micro electro-mechanical systems

MFC Mass Flow Controllers

ONO Oxide-Nitride-Oxide

PCI Percutaneous Coronary Intervention

PEB Post Exposure Bake

PECVD Plasma Enhanced Chemical Vapor Deposition

PINS Philips Innovation Service

Poly-Si Polycrystalline Silicon

PSG Phosphosilicate Glass

PSV Philips Sport Vereniging

PVD Physical Vapor Deposition

RF Radiofrequency

RIE Reactive Ion Etching

SEM Scanning Electron Microscope

TEOS tetraethylorthosilicate

# Contents

| Abstract                                                |    |

|---------------------------------------------------------|----|

| Preface                                                 |    |

| Nomenclature                                            |    |

| Contents                                                |    |

|                                                         |    |

| 1. Introduction                                         |    |

| 1.1 Coronary Atrial Disease (CAD)                       |    |

| 1.2 Flex-to-Rigid (F2R)                                 |    |

| 1.2.1 F2R process flow                                  |    |

| 1.2.3 Decoupling capacitors                             |    |

| 1.3 Aim of the thesis                                   | 6  |

| 1.4 Organization of the Thesis                          | 6  |

| 2. Trench Capacitors for IVUS                           |    |

| 2.1 Introduction                                        |    |

| 2.2 Requirements                                        |    |

| 2.3 Breakdown voltage                                   |    |

| 2.3.1 Fabrication of low and high voltage capacitors    |    |

| 2.4 Decoupling capacitance                              |    |

| 2.4.1 Capacitance increase through trenches             |    |

| 2.4.2 Capacitance increase through stacked dielectrics  |    |

| 2.5 Conclusion                                          | 18 |

| 3. Trench capacitor process flow and mask design        | 19 |

| 3.1 Introduction                                        | 19 |

| 3.2 Process flow                                        | 19 |

| 3.2.1 Trench etch                                       |    |

| 3.2.2 Dielectric and top electrode deposition           |    |

| 3.2.3 Trench closing and bond pad deposition            |    |

| 3.3 Mask Design                                         |    |

| 3.3.1 Introduction                                      |    |

| 3.3.2 TRC overall layout                                |    |

| 4. Process development                                  | 31 |

| 4.1 Introduction                                        |    |

| 4.2 DRIE etch for high aspect ratio microscale trenches |    |

| 4.2.1 Oxide hard mask for DRIE                          |    |

| 4.2.2 DRIE etch for HARM trenches                       |    |

| 4.2.3 Conclusion                                        | 39 |

| 1.2 Dielectric denocition and natternina                | 20 |

| 4.4 Fabrication of the polycrystalline silicon top electrode                                                                                                                                            | 43 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.5 Photoresist reflow to improve silicon dioxide coverage                                                                                                                                              | 45 |

| 4.6 Silicon dioxide deposition for trench closing                                                                                                                                                       | 46 |

| 5. Characterization                                                                                                                                                                                     | 49 |

| 5.1 Introduction                                                                                                                                                                                        | 49 |

| 5.2 Measurement set up                                                                                                                                                                                  | 50 |

| 5.3 Sheet resistance and contact resistance characterization                                                                                                                                            |    |

| 5.4 I-V Characteristics                                                                                                                                                                                 |    |

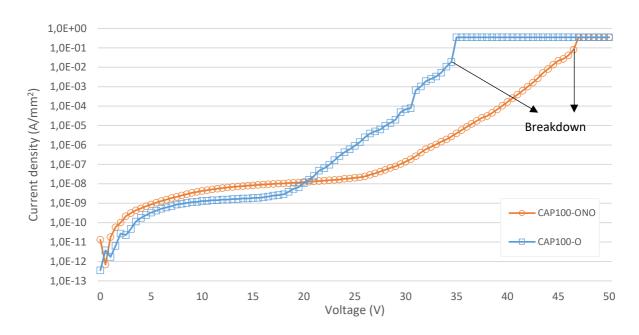

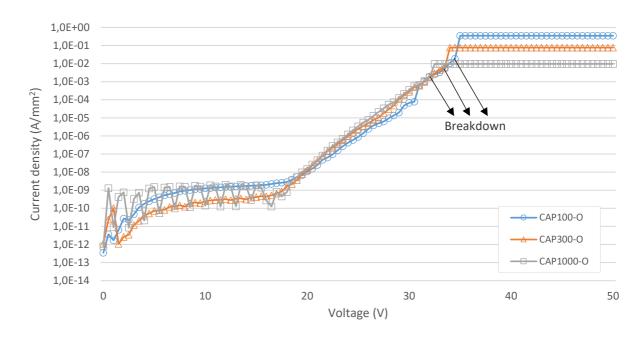

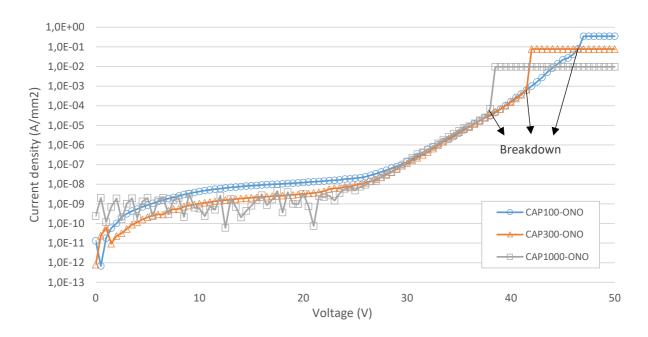

| 5.4.1 Comparison between a single layer and multilayer dielectric plate capacitor                                                                                                                       |    |

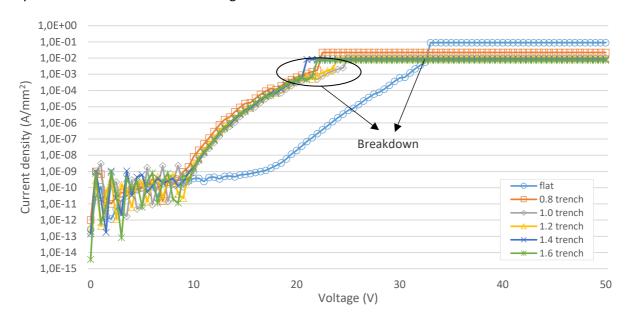

| 5.4.2 Extrinsic properties of a single layer and a multilayer dielectric plate capacitor                                                                                                                |    |

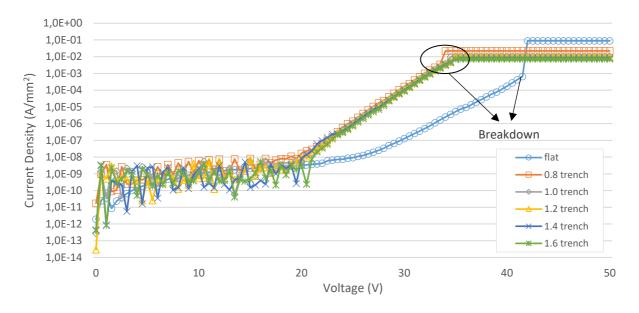

| 5.4.3. Influence of the introduction of trenches.                                                                                                                                                       |    |

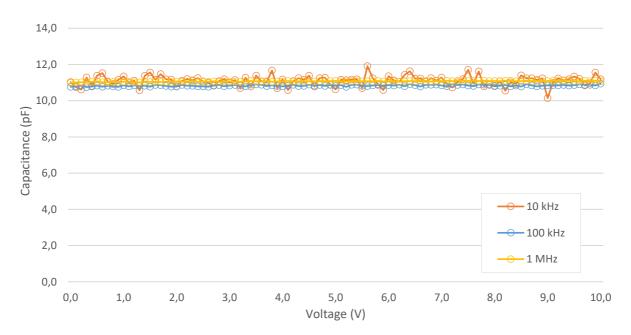

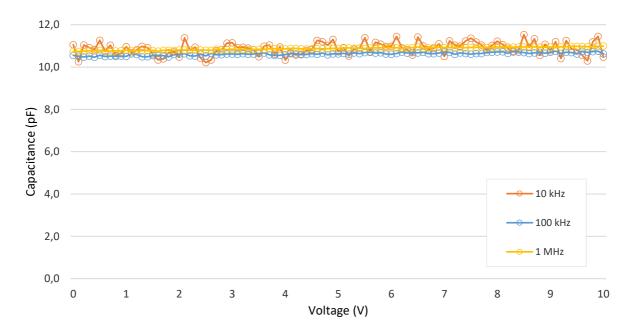

| 5.5 C-V Characteristic                                                                                                                                                                                  |    |

| 5.5.1 Capacitance for different areas for a single layer and multilayer dielectric plate capacitor  5.5.2. Capacitance for different areas for a single layer and multilayer dielectric plate capacitor |    |

| 5.5.3. Influence of the introduction of trenches.                                                                                                                                                       |    |

| 5.6 Conclusion                                                                                                                                                                                          | 58 |

| 6. Conclusion                                                                                                                                                                                           | 61 |

|                                                                                                                                                                                                         |    |

| Bibliography                                                                                                                                                                                            | 63 |

| A. Flowchart                                                                                                                                                                                            | 67 |

| B Process Optimization                                                                                                                                                                                  | 71 |

| B.1 Chemical Vapor Deposition                                                                                                                                                                           | 71 |

| B.2 Photolithography                                                                                                                                                                                    | 72 |

| B.3 Dry Etching                                                                                                                                                                                         | 72 |

| B.4 Wet processing                                                                                                                                                                                      | 74 |

| B.5 Oxidation                                                                                                                                                                                           | 75 |

| B.6 Doping by diffusion                                                                                                                                                                                 | 75 |

| C. Mask Design                                                                                                                                                                                          | 77 |

| C.1 Reticle design                                                                                                                                                                                      | 77 |

| C.2 Trench capacitors                                                                                                                                                                                   | 78 |

| D. Process Optimization                                                                                                                                                                                 | 81 |

| D.1 Process optimization                                                                                                                                                                                | 81 |

| E. Appendix                                                                                                                                                                                             | 83 |

# 1. Introduction

#### 1.1 Coronary Atrial Disease (CAD)

For decades, Coronary Atrial Disease (CAD) has been the leading cause of death worldwide with 9.4 million deaths per year and the prediction is that this number will steadily increase in the coming years[1], [2]. CAD is characterized by a partially or totally blockage of the blood flow to the heart due to a narrowing of the coronary arteries. The cause of this narrowing is the accumulation of atheromatous plaques on the arterial wall, called a stenosis. The reduction of blood flow leads to a lack of oxygen for the heart muscles, resulting in chest pain, shortness of breath, a heart attack or a thrombosis when the plaque breaks loose from the vessel wall.

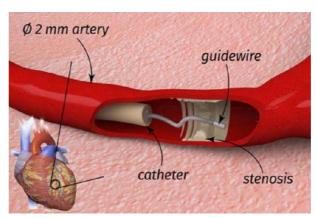

The effects of CAD can be minimized by a healthy lifestyle or with appropriate medication [3]. However, in the case of a severe stenosis, an operation might be necessarily. An often-used method for the diagnosis and treatment of a stenosis is percutaneous coronary intervention (PCI) [4]. A visualization of PCI is shown in Fig 1.1. PCI is a minimally invasive treatment method where a guidewire is inserted in the cardiovascular system and navigated to the location of the intervention. Next, a balloon catheter is slid over the guidewire and inflated at the location of the stenosis. By compressing the plaque against the arterial wall, the vessel is opened and the blood flow is restored. A stent can be placed to keep the vessel dilated.

Figure 1.1. Visualization of percutaneous coronary intervention to treat CAD. A guidewire is inserted and navigated to the location of the stenosis, followed by a treatment catheter that slides over the guidewire [5].

A critical step during PCI is the determination of the severity and location of the stenosis. The current standard method for gathering this information is X-ray angiography [4]. This method is similar to PCI. A guidewire is inserted in the artery, followed by a catheter that slides over the guidewire. With the help of fluoroscopy and a radio-opaque contrast agent, an image of the artery is created. The drawbacks of this imaging technique are; 1) the created 2D image cannot provide enough detail, as the stenosis is a 3D problem; 2) the exposure of radiation to the patient and medical staff and 3) the lack of information regarding the nature of the stenosis. In the past, the blocking percentage of a stenosis used to be decisive for acute clinical events, while recent studies have revealed that compositions and structures are more determinative for operation [6].

A complementary methodology to image the coronary arteries is to use intravascular ultrasound (IVUS). With highly minimized and integrated ultrasound transducers (piezoelectric or CMUT), it applies ultrasound techniques inside the blood vessels. By mapping out the cross section of the coronary arteries, the IVUS technology allows 3D visualizations of the stenosis. These 3D visualizations help to determine the amount of

stenosis that is built up inside the coronary artery, which gives more insight and perspective for the diagnosis. However, the IVUS catheters used today are all manufactured with outdated and obsolete technologies, which limit their image resolutions. The lack of a good image quality forms a barrier for a high accuracy diagnosis of the stenosis and precise information regarding the nature of the plaque.

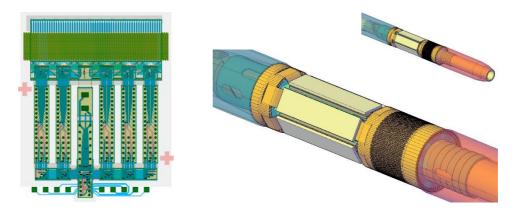

New microfabrication technologies have enabled improvement of the IVUS image quality. With the introduction of the Flex-to-Rigid (F2R) technology into the IVUS catheter manufacture process, it has become possible to integrate more ultrasound transducer elements onto the tip of an IVUS catheter. Additionally, recent studies have proposed IVUS technology integration into a guidewire (Ø360  $\mu$ m) [4], [5]. This eliminates the need for a large diameter catheter (Ø1.2 mm). Consequently, the clinical intervention is less invasive and the investigation of smaller arteries is possible. Moreover, F2R also helps to digitize the electrical system in the catheter tip, which significantly improves the signal quality and image frame rate.

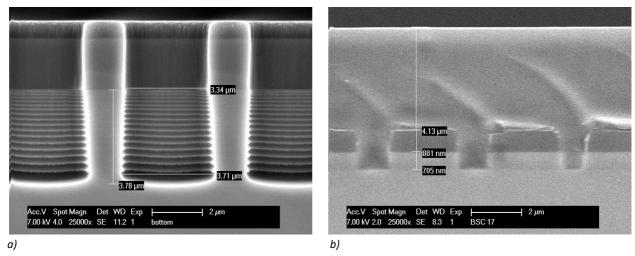

#### 1.2 Flex-to-Rigid (F2R)

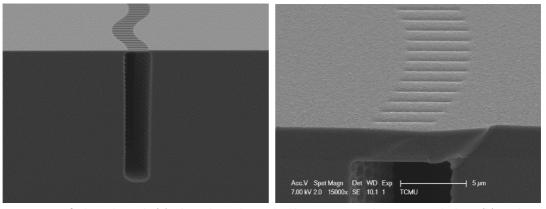

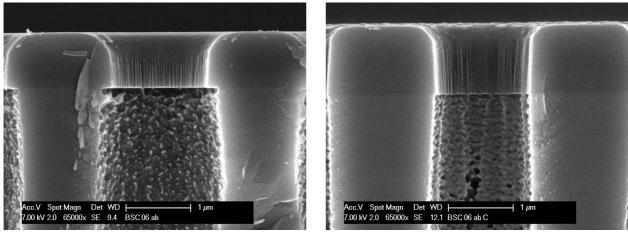

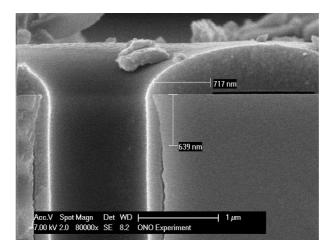

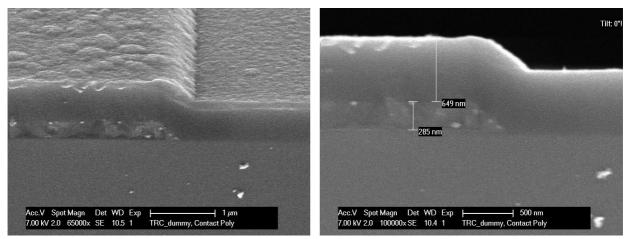

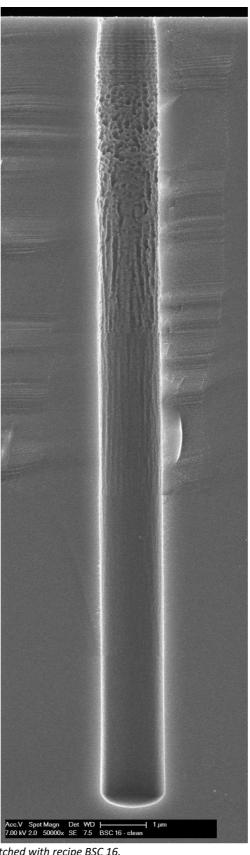

The Flex-to-Rigid (F2R) technology is an interconnect platform to integrate heterogeneous electronic systems and devices onto a partially flexible chip for minimally invasive medical instruments. This technology platform allows for the integration of the micro electro-mechanical systems (MEMS) and integrated circuits (IC) on a chip in a planar environment, which can later be folded into any arbitrary shape. The folding characteristic of the chip is established by the formation of rigid silicon islands that are connected by flexible interconnects. These separate silicon islands are isolated by the "buried trenches". "Buried trenches" in the F2R platform are developed to precisely define the dimensions of separated silicon islands. For the fabrication of buried trenches, a silicon dioxide sub-micro mesh mask with small holes or squares is first created. A deep reactive ion etch (DRIE) step (Appendix B.2) with negative etch slope then etches the Si substrate from underneath the masks. During the DRIE step, the etched trenches merge into bigger trenches underneath the oxide mesh at a certain point due to the DRIE negative etch slope. A thick silicon dioxide is applied to close the holes in the oxide mesh mask and flatten the substrate surface for further process. These closed merged bigger trenches, the "buried trenches", define the silicon island dimensions with very high accuracy. A scanning electron microscope (SEM) image of a buried trench is shown in Fig 1.2. Within the flexible interconnects, metal interconnects are embedded to function as an electrical connection between the electrical systems on the different silicon islands. By placing the metal layer in the neutral stress plane of the polymer stacks, very high flexibility is obtained in the interconnects. A simplified version of the F2R process flow is explained in the following section.

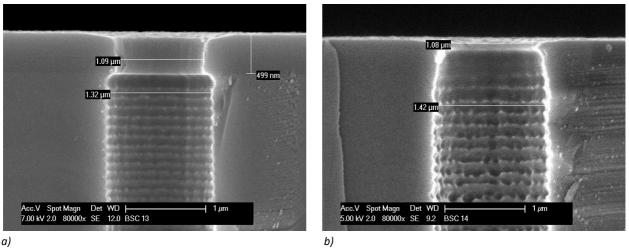

Figure 1.2. SEM images of a buried trench. (a) A buried trench is etched by DRIE step with negative etch slope. (b) Mesh mask of a buried trench that is closed by a 700 nm thick layer of silicon dioxide [7].

#### 1.2.1 F2R process flow

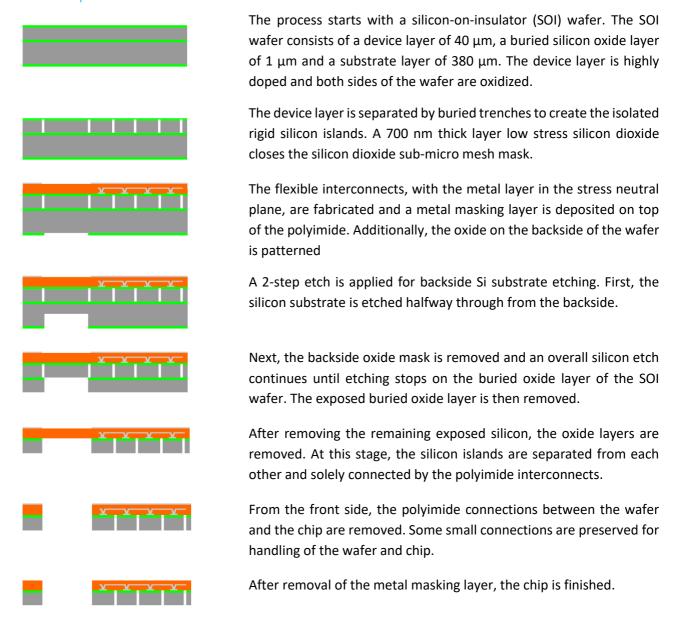

Figure 1.3. Simplified process flow of the F2R technology.

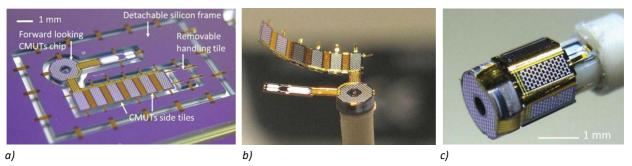

The folding characteristics of F2R process makes it ideal for the fabrication of minimally invasive medical instruments such as catheters and guidewires [8]. Fig 1.4 shows an F2R device in a wafer after fabrication (a), the same F2R device removed from the wafer (b) and the F2R device folded around the tip of a catheter (c). In combination with MEMS ultrasound transducer technology, F2R can be a powerful tool for accurate imaging of the arteries.

Figure 1.4. Folding of a F2R device, a) the device attached to the wafer, b) the device removed from the wafer and c) the device folded around the tip of a catheter [8].

#### 1.2.2 Capacitive Micro-machined Ultrasound Transducers (CMUTs)

The F2R technology enables the integration of Capacitive Micro-machined Ultrasound Transducers (CMUTs) on the tip of an IVUS catheter. In the past, piezoelectric ultrasound transducers used to be the standard in IVUS. However, CMUTs have significant benefits compared to piezoelectric transducers. Compared to piezoelectric transducers, CMUTs offer: 1) a larger bandwidth and the possibility for scaling to higher frequencies, 2) reduced fabrication and assembly costs, hence more suitable for massive production and 3) easier integration with other electronic systems [9]. All these characteristics make CMUTs more attractive to IVUS technology.

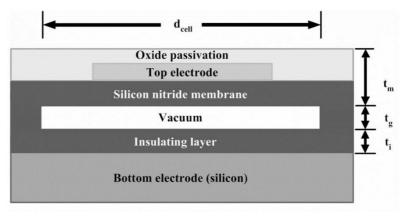

CMUTs are transducer elements that can act both as a transmitter and as a receiver for ultrasound waves. The principle of a CMUT is based on a capacitor cell. A vacuum cavity is sandwiched by a membrane with a top electrode and a bottom electrode, which is often integrated in the substrate. A direct current (DC) voltage is applied over the top and bottom electrode. The DC-bias voltage causes the membrane to collapse towards the bottom electrode. By applying an alternating voltage, the CMUT generates vibrations in the membrane that produces ultrasound waves. Visa versa, the membrane is also able to generate an output current signal when it receives an ultrasound wave. A schematic cross section of a CMUT cell is given in Fig 1.5.

Figure 1.5. Schematic cross section of a CMUT Cell [9].

The image quality, or resolution, generated with CMUTs is characterized by two parameters: the axial resolution and the lateral resolution. The resolutions are given by equation 1.1 and 1.2,

$$Axial\ resolution = \frac{0.5c}{Bandwidth} \tag{1.1}$$

$$Lateral \ resolution = \frac{Depth \ \lambda}{Array \ size} \tag{1.2}$$

where c is the speed of sound in the tissue (1484 m/s) and  $\lambda$  is the ultrasound wavelength (37 $\mu$ m) [10]. To improve the image resolution, an increase in the transducer's operating frequency and the transducer array size is needed. A larger array size is established by increasing the number of elements. This requires a higher current supply. A consequence of the increased current supply and frequency is the generation of noise on the power-supply grid due to switching currents, called Delta-I noise. This problem can be mitigated by locating the power source as close as possible to the circuit. For catheters, this is practically impossible. Another very effective method to reduce the noise is to use decoupling capacitors, which act as a temporary power source [11]–[13].

#### 1.2.3 Decoupling capacitors

The integration of the sensors and data transfer elements in the F2R platform has a high impact on the power distribution and consequently on the signal integrity. One of the most important issues in today's deep submicron designs is signal integrity [14]. Signal integrity can be compromised by various source. One of the main causes for signal degradation is Delta-I noise, caused by a sudden change in the amount of current that is drawn by the components in the circuit. This change in current can cause a momentary drop or surge in the voltage over the power distribution bus [15]. The voltage variation is given by equation 1.3,

$$\Delta V = L \frac{\delta I}{\delta t} \tag{1.3}$$

where  $\Delta V$  is variation in the power supply level, L is the effective wire inductance of the power busses,  $\delta I$  is the current change during transition and  $\delta t$  is the rise or fall time of the transition [14]–[16]. It is widely accepted that one of the most powerful strategies to encounter the delta-I noise problem is to use decoupling capacitors[13].

A capacitor is a passive electric component that can store electrical energy in the form of charge. The most commonly used capacitor is the parallel-plate capacitor, which consist of two conductors separated by a non-conducting medium. Applying a voltage difference over the capacitor causes one conductor to collect a negative charge and the other conductor to collect a positive charge. When the power source is removed and the circuit is opened, the charge is stored in the capacitor. By closing the circuit, the charge will generate a current flow through the circuit, which can be used to deliver power to a device.

A decoupling capacitor act as charge reservoir for switching circuits and reduces the effect of Delta-I noise. Most of today's multichip modules (MCM's) use surface-mounted stand-alone decoupling capacitors. However, these surface-mounted devices have their drawbacks. In-substrate integrated decoupling capacitors encounter most of the drawbacks by offering: 1) better electrical performance, 2) increased packaging efficiency, 3) better capacitance efficiency and 4) elimination of separate packaging and assembly to the board [13]. In in-substrate integrated capacitors, the silicon substrate is doped to function as the bottom electrode. A dielectric and top electrode layer are deposited on top to form the capacitor.

#### Trench capacitors

Although the in-substrate integrated capacitors are preferred for integration onto the F2R platform with other electrical systems, there is a very realistic problem: there is only a limited amount of surface area available in the catheter due to its small size. Therefore, a method to increase the capacitor functional area is found by expending the capacitors into the third dimension i.e. in the depth of the silicon islands. The idea of etching into the silicon in order to enlarge the functional area is not new and was first patented by Texas Instruments in 1976 [17]. Nowadays, these structures are frequently seen in the field of semiconductors and carry the name "trench capacitors".

#### 1.3 Aim of the thesis

In summary, CMUTs in combination with the F2R technology platform enable the downscaling of IVUS catheters while maintaining, or even improving, the image quality. Furthermore, improving the image resolution, generated by CMUT transducers, requires an increase in ultrasound frequency. Equation 1.3 shows that this results in an increase in delta-I noise. With these trends in mind, the integration of decoupling capacitors in the F2R technology is an interesting option.

The first objective of this thesis is the theoretical investigation for trench capacitors. A mathematical relation is provided that illustrates the capacitance's dependency on different geometrical parameters and the influence of different dielectric materials is investigated. Furthermore, a design solution to meet the requirements regarding the breakdown voltage is proposed. The theoretical ideas are tested and verified in the Philips Innovation Services (PInS) cleanroom.

The second objective of the work is to develop trench capacitors that can be implemented, as a building block, in the existing F2R process flow. For the fabrication of the trench capacitors, a new dedicated mask set with and accompanying flowchart is designed. Furthermore, the process flow for the trench capacitors and the process steps are verified and, where needed, optimized. The fabrication processes and results are presented and further work about the integration of the decoupling capacitors in the F2R flow is discussed.

#### 1.4 Organization of the Thesis

In Chapter 2, a mathematical relation between the trench geometry and the capacitance density is presented and a comparison is made between a single layer dielectric and a multilayer dielectric. Chapter 3 described the process flow and mask design. The process optimization of processes that needed more attention is shown in Chapter 4. In Chapter 5 the electrical characterization is presented. Finally, the Thesis is concluded in Chapter 6.

# 2. Trench Capacitors for IVUS

#### 2.1 Introduction

To improve the image quality of the next generation IVUS catheters, additional decoupling capacitors are needed to meet the electrical demands of the CMUT elements and digital systems. Currently, surface-mounted stand-alone decoupling capacitors are flip chip bonded on the IVUS chip. However, in terms of performance and functionality, in-substrate integrated decoupling capacitors are preferred and these decoupling capacitors should be integrated as close to the CMUTs and digital systems as possible. In the IVUS F2R platform, six silicon islands with dimensions of 2600 um by 500  $\mu$ m are designed as carrier substrates for ASICs (Fig. 2.1). Interconnects and contact pads are fabricated on the island surfaces and ASICs are flip-chipped directly onto these islands. Therefore, the silicon islands seem to be the ideal location to integrate the in-substrate decoupling capacitors. To effectively increase the in-substrate capacitance, trench capacitors are applied instead of plate capacitors. Trench capacitors increase the functional surface area by drilling trenches into the third dimension, i.e. the depth of the 40  $\mu$ m thick silicon island. With stacked dielectric layers to improve relative dielectric permittivity, the capacitance can even be further enhanced.

Figure 2.1. Illustration of the IVUS catheter showing the six silicon islands [7].

This chapter describes the theoretical approach of the decoupling trench capacitors integration in the F2R platform in terms of electrical characteristics. First, the requirements for of breakdown voltage and capacitance are calculated. Next, the theoretical solution to meet the requirements in terms of breakdown is explained. Finally, two approaches to increase the capacitance are reviewed. A mathematical relation between the trench geometrical parameters and the decoupling capacitance in derived, followed by a comparison between a multilayer dielectric and a single layer dielectric.

#### 2.2 Requirements

The IVUS electrical system requires two different decoupling capacitors for two different purposes. First, a decoupling capacitor is needed to provide the peak currents drawn by the electrical system that is connected to the ASICs. This system operates at 3.3 V. Secondly, a decoupling capacitor is needed to prevent crosstalk to arise between the CMUT elements. This decoupling capacitor serve another purpose and the main requirement is the ability to withstand a voltage in the range of 35 V. Because of the likelihood of thin dielectric layers to deviate from the known electrical properties, an above average safety margin of three is taken into account in the first design of the trench capacitors. Therefore, the required breakdown voltages are

determined at 10 V for the low voltage capacitors and 100 V for the high voltage capacitors. In the remainder of this work, the corresponding decoupling capacitors are referred to as low voltage capacitors and high voltage capacitors respectively. Since the requirements for the high voltage capacitors are not very stringent, this chapter will address the estimation of the majority of the required value for the low voltage capacitors.

The exact operation specifications for the IVUS electrical system that is connected to the ASICs are hard to determine. However, a very realistic estimation of the values can be made. The following calculations are based on the estimated values, which are determined in consultation with the electrical system designers of the IVUS catheter at Philips.

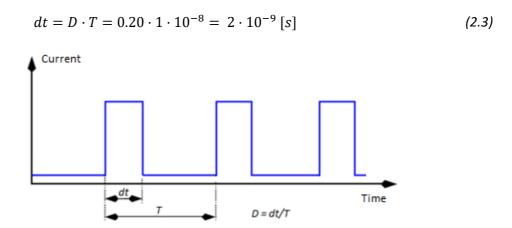

For an IVUS catheter, operating at an ultrasound frequency of 30 MHz, which is sampled at 2.5 times the ultrasound frequency, the typical ASIC clock frequency (f) will be in the range of 100 MHz, and peak currents are expected up to 25 mA. To calculate the capacitance from the above-mentioned parameters by equation 2.1, first the charge drawn by the electrical system (dQ) and potential difference (dV) are calculated.

$$C = \frac{dQ}{dV} [F] \tag{2.1}$$

$$dQ = I(t) \cdot dt [C] \tag{2.2}$$

The change in the amount of charge follows from the peak current (I(t)) and the pulse duration (dt). Maximum peak currents are estimated at 25 mA. The pulse duration is defined as the time the peak current is drawn by the system and is calculated from the duty cycle (D) and the total period (T), which is defined by 1/f. The pulse duration follows from the duty cycle of the period. The duty cycle in the IVUS electrical system is estimated at 20%.

Figure 2.2. Illustration of a pulse duration (dt), period (T) and duty cycle (D) [18].

The change in charge is calculated by implementing the current and the period in equation 2.4.

$$dQ = I(t) \cdot dt = 25 \cdot 10^{-3} \cdot 2 \cdot 10^{-9} = 50 \cdot 10^{-12} [C]$$

(2.4)

The potential difference (dV) can be interpret as the acceptable voltage fluctuation over the electrical system. Generally, the acceptable potential difference is set as a fraction of the voltage and follows from  $dV = n \cdot V$  with n typically in the range of 0.05 [11]. A realistic acceptable fluctuation in the IVUS system is 0.1 V.

From the potential difference and the change in the amount of charge the capacitance is calculated.

$$C = \frac{50 \cdot 10^{-11}}{0.1} = 500 \cdot 10^{-12} [F]$$

(2.5)

The required target capacitance for optimal function of the IVUS electrical system is 500 pF.

#### 2.3 Breakdown voltage

As explained in the section 1.2.3, capacitors are passive electric components that can store electrical energy in the form of charge. One of the main properties that characterize a capacitor is the breakdown voltage, or the dielectric breakdown. Generally, the design or selection of a capacitor start with the breakdown voltage. The dielectric breakdown of an insulator is defined as the moment where the dielectric starts to conduct, which is an irreversible phenomena. Therefore, it is crucial that the capacitor is able to meet the breakdown requirements. The dielectric breakdown is strongly related to the exact processing details during the manufacturing of these layers [19]. However, in first approximation the breakdown of a dielectric layer can be characterized by the maximum electric field at breakdown ( $E_{bd}$ ) that can be applied to the dielectric before breakdown occurs. From the thickness of the dielectric layer ( $t_{di}$ ) and the maximum electric field the maximum voltage ( $v_{bd}$ ) that can be applied over the dielectric can be estimated from:

$$V_{bd} = E_{bd} \cdot t_{di} \ [V] \tag{2.6}$$

The minimum thickness of the dielectric layer for a given working voltage is then found by:

$$t_{di} = \frac{V_{bd}}{E_{bd}} \quad [cm] \tag{2.7}$$

Note that the equation 2.6 is merely an indication. For an accurate estimation of the breakdown voltage, the effective dielectric thickness should be used instead of the physical thickness [20]. The effective dielectric thickness compensates for extrinsic defects.

#### 2.3.1 Fabrication of low and high voltage capacitors

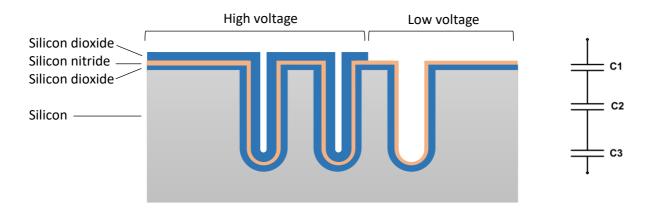

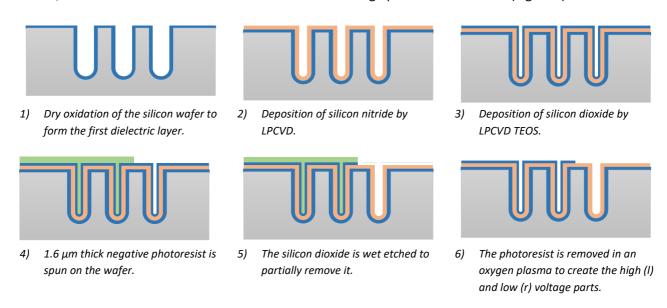

For the integration of low and high voltage capacitors in the F2R platform, two separate capacitors can be fabricated with different dielectric thicknesses. A thick dielectric layer for the high voltage capacitor and a thin dielectric layer for the low voltage capacitor. However, fabrication wise it is expensive to fabricate two separate dielectric layers independently from each other on one wafer. The use of a multilayer stacked dielectric offers the potential of fabricating the low and high voltage capacitors by the deposition of a triple layer dielectric and partially remove the top dielectric layer (Fig 2.3). With this method, low voltage and high voltage parts are created in the dielectric with the use of just one extra lithography mask. The dielectric layer thicknesses can be tuned to obtain a breakdown voltage of 100 V in the high voltage part and a breakdown voltage of 10 V in the low voltage part.

A commonly used multilayer stacked dielectric is a combination of silicon dioxide, silicon nitride and silicon dioxide, which is further discussed in section 2.3.2. For the best performance in terms of capacitance, the thickness of the first silicon dioxide layer is set at 5 nm [21].

Figure 2.3. Illustration of the multilayer high and low voltage dielectric and on the right the equivalent circuit of a triple layer dielectric.

According to the capacitance equation V = Q / C, the voltage follows from dividing the charge by the capacitance. In a multilayer dielectric, the dielectric layers are placed in series (Fig 2.3). The charge over the three layers is equal and therefore, the voltage over the layers is inversely proportional to the capacitance (equation 2.8), where C is given by equation 2.9. The total voltage over the dielectric layer is found by the sum of the voltages over the individual layers (equation 2.9)

$$V_1 = V_{tot} \cdot \frac{C_2}{C_1 + C_2} \quad [V] \tag{2.8}$$

$$V_{tot} = V_1 + V_2 + \cdots [V] (2.9)$$

The design of the ONO dielectric starts with conforming the thickness of the first two layers to meet the required 10 V breakdown voltage. Next, the thickness of the second silicon dioxide layer, which is later added to withstand the 100 V breakdown voltage, is calculated.

#### Approach

The starting point for the design of the multilayer dielectric is the required breakdown voltage. This voltage dictates the total (acceptable) voltage in equation 2.9. From the thickness of the first silicon dioxide layer and the electric field at breakdown of silicon dioxide, the maximum acceptable voltage over this layer is calculated using equation 2.6. The voltage over the nitride then simply follows subtracting the voltage over the silicon dioxide from the total voltage (equation 2.9). The capacitance in equation 2.8 relates to the thickness of the dielectric layers:

$$C = \frac{\varepsilon_0 \cdot \varepsilon_r \cdot A_{fun}}{t_{di}} \quad [V] \tag{2.10}$$

Where  $\varepsilon_0$  is the electric constant in vacuum,  $\varepsilon_r$  the relative dielectric constant of the dielectric material, t the thickness of the dielectric layer and  $A_{fun}$  is the functional area of the capacitor. The relative dielectric constants for silicon dioxide and silicon nitride are 3.9 and 7.9, respectively [22]. Therefore, the thickness of the silicon

nitride is obtained by rewriting equation 2.11 in equation 2.12. Since A and  $\varepsilon_0$  are equal for the dielectric layers, these terms are cancelled from the equation. Rewriting equation 2.11 to the thickness of the nitride results in:

$$V_{ni} = V_{tot} \cdot \frac{\frac{\varepsilon_{ox} \cdot \varepsilon_{o} \cdot A}{t_{ox}}}{\frac{\varepsilon_{ni} \cdot \varepsilon_{o} \cdot A}{t_{ni}} + \frac{\varepsilon_{ox} \cdot \varepsilon_{o} \cdot A}{t_{ox}}} [V]$$

(2.11)

$$t_{ni} = \frac{\varepsilon_{ni}}{\frac{\varepsilon_{ox}}{t_{ox}} \cdot \left(\frac{V_{tot}}{V_{ni}} - 1\right)} \quad [V]$$

(2.12)

The thickness of the second layer silicon dioxide to fabricate the high voltage capacitors can be found by first calculating the capacitance of the low voltage dielectric part. A stacked dielectric layer is interpreted as a series capacitance and the capacitance of the combined dielectric layers is calculated according to equation 2.13.

$$\frac{1}{C_{tot}} = \frac{1}{C_1} + \frac{1}{C_2} + \frac{1}{C_3} + \dots [F]$$

(2.13)

It is known that the low voltage part of the dielectric has a breakdown voltage of 10 V. Therefore, the added dielectric layer must withstand the remaining 90 V breakdown voltage. Since the voltage distribution is inversely proportional to the capacitance, the capacitance must be decreased a factor of 9 to increase the voltage by this same factor. The thickness of the silicon dioxide is then calculated by solving equation 2.10 for this capacitance.

#### Results and discussion

The required breakdown voltage of the low voltage dielectric is 10 V. Literature reports an electric field strength of approximately 1 V/nm for both silicon dioxide and silicon nitride [23]. However, several studies have shown the applicability of the empirical relation  $E_{bd} = 20/\varepsilon_r^{1/2}$ , which indicates a decrease in the dielectric breakdown for an increasing relative dielectric constant [24]. Since this relation is not proven, the calculations in this work are based on 1 V/nm electric field strength. From equation 2.6, a maximum acceptable voltage in the silicon dioxide of 5 V is calculated, the consequent acceptable voltage over the silicon nitride layer is also 5 V.

Solving equation 2.12 for the required breakdown voltages, silicon dioxide thickness and relative dielectric constants results in a required layer thickness of 10 nm for the silicon nitride. The breakdown voltage of the silicon nitride is verified with equation 2.6. Since the silicon nitride is expected to breakdown at 10 V, which is twice the applied voltage of 5 V, this layer thickness is sufficient to prevent the silicon nitride to breakdown. Moreover, it secures the maximum field in the silicon dioxide to remain below 5 V. Therefore, a 5 nm silicon dioxide – 10 nm silicon nitride configuration seems to be a proper configuration for the low voltage capacitor.

To determine the thickness of the second silicon dioxide layer, first the capacitance of the low voltage part is calculated. The capacitance of each individual layer is calculated using equation 2.10. The electric constant in vacuum is  $8.85 \cdot 10^{-12}$  F/m. The total capacitance of the combined dielectric layers according to equation 2.13 is  $3.5 \text{ nF/mm}^2$ . Therefore, the second layer silicon dioxide must have a maximum capacitance of 390 pF/mm<sup>2</sup> to

account for 90% of the applied voltage. The thickness of the dielectric layer follows from equation 2.10 and is determined at 88.5 nm.

As mentioned in the requirements section, the breakdown voltages are overestimated and consequently, valuable capacitance is sacrificed. Therefore, it is advisable to revise these requirements when more insight is obtained regarding the behavior of the dielectric layers.

#### Conclusion

According to the calculations, the combination of 5 nm silicon dioxide, 10.1 nm silicon nitride and 88.5 nm silicon dioxide layer is suitable for the fabrication of low and high voltage parts in one dielectric layer. The three layers together achieve a breakdown voltage of 100 V and a capacitance density of 350 pF/mm<sup>2</sup>. By removing the second silicon dioxide layer, the breakdown voltage is reduced to 10 V and the capacitance density increased to 3.4 nF/mm<sup>2</sup>.

#### 2.4 Decoupling capacitance

The second main characteristic of a capacitor is the capacitance. The capacitance of a capacitor is the ratio of the change of electrical charge (dQ) to the corresponding electrical potential difference (dV) (equation 2.14). The capacitance in expressed in Farad, or more frequently used, nanofarad or picofarad.

$$C = \frac{dQ}{dV} [F] \tag{2.14}$$

The design of the decoupling trench capacitor for the IVUS catheter integration finds its origin in the same principle as the parallel-plate capacitor. The parallel-plate capacitor consists of a top and a bottom electrode, separated by a dielectric layer. The mathematical expression of the capacitance of a parallel-plate capacitor is given by equation 2.10. Since the breakdown voltage of a capacitor is determinative for the thickness of the dielectric layer, other solutions to increase the capacitance are investigated. This section describes two solutions to increase the capacitance. First, the capacitance increase by adding trenches is calculated, followed by a comparison of a single layer dielectric with a multilayer dielectric.

#### 2.4.1 Capacitance increase through trenches

As previously mentioned, to increase the capacitance an increase in the functional area is found in the depth of the silicon islands by etching multiple trenches. This section describes the theoretical approach to calculate the capacitance increase based on a simple grid orientation. A comparison is made between flat capacitors and trench capacitors.

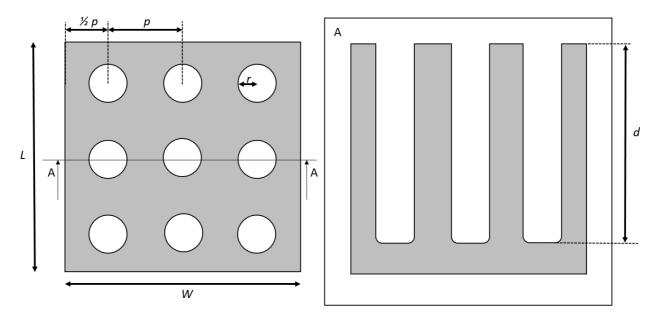

Figure 2.4. Illustration of the grid structure that is used for the theoretical approach to calculate the capacitance.

With the assumption of a straight wall profile and a flat bottom of the trench, the area of the trench walls directly adds up to the functional area of the capacitor. In the situation where the trenches are placed in a simple grid orientation (Fig 2.4) the functional area is given by equation 2.16.

$$A_{fun} = L \cdot W + \left( \left( \frac{L}{p} \cdot \frac{W}{p} \right) \cdot 2 \cdot \pi \cdot r \cdot d \right) [m^2]$$

(2.15)

Where L and W are the length and the width of the grid resp. and p the pitch between the trenches. r is the trench radius and d the trench depth. Substituting equation 2.15 in equation 2.10 results in the capacitance for the trench capacitors:

$$C = \frac{\varepsilon_0 \cdot \varepsilon_r \cdot \left(L \cdot W + \left(\left(\frac{L}{p} \cdot \frac{W}{p}\right) \cdot 2 \cdot \pi \cdot r \cdot d\right)\right)}{t_{di}} [F]$$

(2.16)

It is Interesting to derive is the capacitance density ( $C_{den}$ ) thus the capacitance per unit surface area. The capacitance density is obtained by dividing equation 2.10 and 2.16 by the surface area,  $A_{sur}$ . For the flat capacitors this results in equation 2.17 since  $A_{fun}$  and  $A_{sur}$  are equal and cancel each other out.

$$C_{den} = \frac{\varepsilon_0 \cdot \varepsilon_r}{t_{di}} [F/m^2]$$

(2.17)

Dividing equation 2.16 by the surface area results in equation 2.18. Because  $A_{sur}$  equals  $L \cdot W$ , this equation is simplified (equation 2.19). The elimination of L and W makes the calculations independent of the surface dimensions of the capacitor.

$$C_{den} = \frac{\varepsilon_0 \cdot \varepsilon_r \cdot \left(L \cdot W + \left(\left(\frac{L}{p} \cdot \frac{W}{p}\right) \cdot 2 \cdot \pi \cdot r \cdot d\right)\right)}{t_{di} \cdot A_{sur}} [F/m^2], \qquad r < \frac{1}{2}p$$

(2.18)

$$C_{den} = \frac{\varepsilon_0 \cdot \varepsilon_r}{t_{di}} \cdot \left(1 + \frac{2 \cdot \pi \cdot r \cdot d}{p^2}\right) [F/m^2], \qquad r < \frac{1}{2}p$$

(2.19)

Trenches with a radius that is larger than half the pitch will start to overlap each other and merge into one slit, thereby sacrificing functional area. Therefore, equation 2.18 and 2.19 are only valid for the boundary condition  $r < \frac{1}{2}p$ .

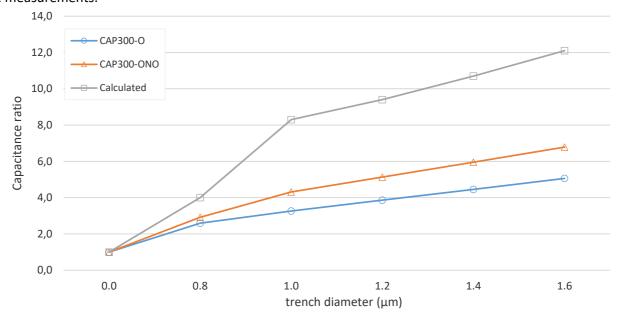

#### Results and discussion

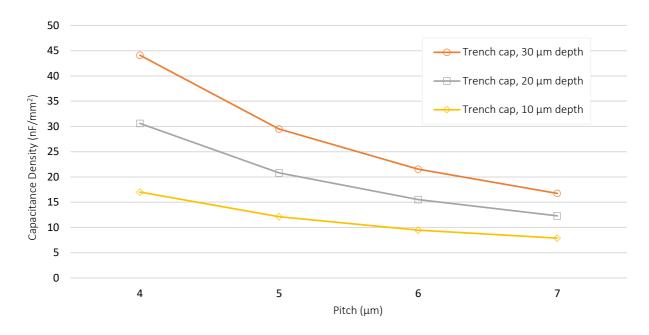

Equation 2.10 and 2.19 are calculated and plotted for different values of the pitch, radius and depth to gain insight in the advantage of trench capacitors over the flat capacitors. The electric constant in vacuum is  $8.85 \cdot 10^{-12}$  F/m. The relative dielectric constant is dimensionless and for silicon dioxide 3.9 [22]. The thickness of the dielectric layer is set at 10 nm to meet the 10 V breakdown voltage (equation 2.6). The radius, depth and pitch values are chosen based on what is needed and producible for the integration in the F2R.

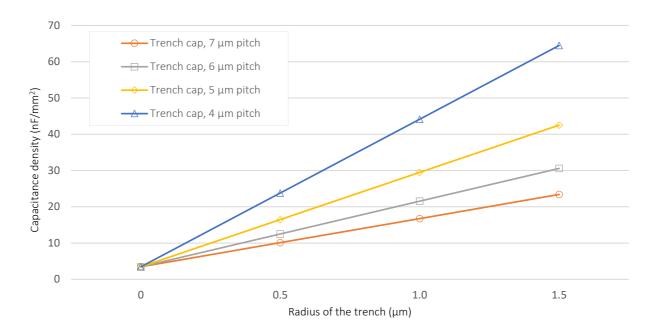

#### Variation in pitch and radius

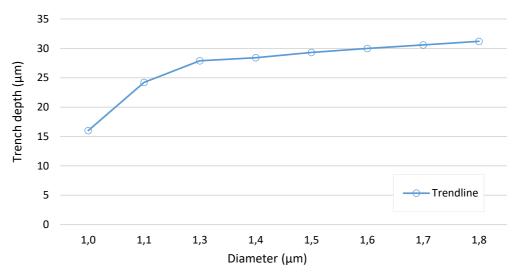

Equation 2.10 and 2.19 are calculated and plotted with different radii and pitch of the trench capacitors, while keeping the depth of the trench fixed at 30  $\mu$ m. To avoid rigidity issues in the 40  $\mu$ m thick silicon island, the depth of the trench is limited at 30  $\mu$ m. Table 2.1 shows the results of the calculation of the relation between the radii of the trenches and the capacitance density for different pitch variations. The data is plotted in Fig 2.5 and 2.6.

#### Capacitance density (nF/mm<sup>2</sup>)

|             |     |     |      | Pitch (μm) |      |      |

|-------------|-----|-----|------|------------|------|------|

| S           |     | 0   | 7    | 6          | 5    | 4    |

| adius<br>') | 0   | 3.5 | -    | -          | -    | -    |

| - E         | 0.5 | -   | 10.1 | 12.5       | 16.5 | 23.8 |

| rench<br>(µ | 1.0 | -   | 16.7 | 21.5       | 29.5 | 44.1 |

| 7           | 1.5 | -   | 23.4 | 30.6       | 42.5 | 64.5 |

Table 2.1. Capacitance density for different trench radii and pitches.

Figure 2.5. Relation between the capacitance density and different trench radii for varying pitches.

Figure 2.6. Relation between the capacitance density and different pitches for varying trench radii.

Fig 2.5 shows the linear relation between the trench radius and the capacitance density. Reflecting back on equation 2.19 this is expected. The equation shows an almost direct proportionality of the capacitance density to the radius since the first term in the equation ( $\varepsilon_0 \cdot \varepsilon_r$ ) is negligible compared to the second term for the above-mentioned dimensions. However, when the pitch is increased to disproportionate dimensions compared to the radius, the first term starts to dominate. Fig 2.6 shows the parabolic relation between the pitch distance and the capacitance density for fixed trench radii, which is in line with term  $p^2$  in equation 2.19.

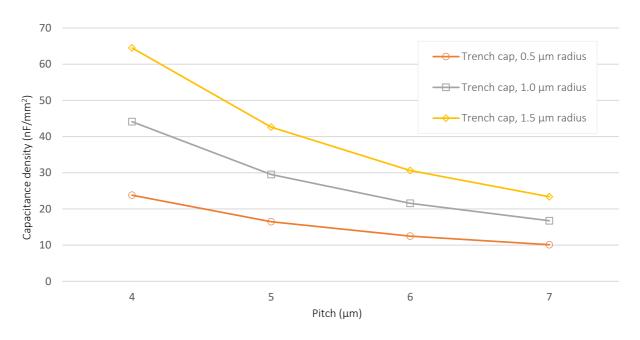

#### Variation in pitch and depth

Equation 2.10 and 2.19 are plotted for different depths of the trenches and different pitch dimensions while keeping the trench radius fixed at 1.0  $\mu$ m. Table 2.2 shows the results of the calculation of the relation between the depth of the trench and the capacitance density for different pitch variations. The data is plotted in Fig 2.7 and 2.8.

#### Capacitance density (nF/mm<sup>2</sup>)

|              |    |     |      | Pitch (μm) |      |      |

|--------------|----|-----|------|------------|------|------|

| , (          |    | 0   | 7    | 6          | 5    | 4    |

| depth<br>n)  | 0  | 3.5 | -    | -          | -    | -    |

|              | 10 | -   | 7.9  | 9.5        | 12.1 | 17.0 |

| rench<br>(µr | 20 | -   | 12.3 | 15.5       | 20.8 | 30.6 |

| _            | 30 | -   | 16.7 | 21.5       | 20.5 | 44.1 |

Table 2.2. Capacitance density for different trench depth and pitch.

Figure 2.7. Relation between the capacitance density and different trench depth for varying pitches.

Figure 2.8. Relation between the capacitance density and different pitches for varying trench depths.

Fig 2.7 shows the linear relation between the trench depth and the capacitance density. Again, reflecting back on equation 2.19 this is expected. The equation shows the same direct proportionality of the capacitance density to the depth as to the radius. However, as mentioned before, the depth is limited since the silicon islands in the F2R flow only have a thickness of 40  $\mu$ m. Trenches deeper than 30  $\mu$ m are likely to cause problems in the rigidity of the silicon islands. Fig 2.8 shows the parabolic relation between the pitch distance and the capacitance density for fixed trench depth, which is in line with  $p^2$  in equation 2.15.

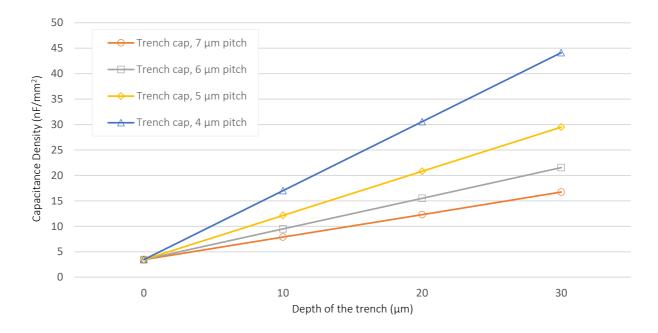

#### Conclusion

To conclude the capacitance calculations, a relation between the geometrical parameters and the capacitance density is found. The model shows; 1) the linearity of the capacitance density to the trench radius and trench diameter for a fixed pitch and 2) the parabolic relation between the capacitance density and the pitch for fixed trench radii and trench depth. The model shows a theoretical increase in capacitance density from 3.5 nF/mm² for the flat capacitor to 64.1 nF/mm² for the optimal capacitor configuration with a pitch of 4  $\mu$ m, a trench depth of 30  $\mu$ m, a trench radius of 1.5  $\mu$ m and a 10 nm thick silicon dioxide dielectric. This means a maximum capacitance density increase by a factor of 18.

#### 2.4.2 Capacitance increase through stacked dielectrics

To increase the capacitance even further, the relative dielectric constant can be increased. Silicon dioxide has been the dominant dielectric throughout the history of IC production due to its unique compatibility with silicon IC manufacturing and the huge wealth of experience in industry in the reliable and repeatable production of this dielectric [19]. When the silicon dioxide thickness is scaled down to thicknesses of 5 nm or less, direct tunneling starts to limit the use of silicon dioxide in MOS devices. In order to increase the capacitance, research has been conducted towards dielectric materials with higher relative dielectric constant  $\varepsilon_r$ , the so-called high-k dielectrics, especially in the field of thin-film transistors. In literature the terms k and  $\varepsilon_r$ , are used interchangeably, in this work the relative dielectric constant is referred to as  $\varepsilon_r$ . Equation 2.10 shows the direct proportionality of the capacitance to the relative dielectric constant.

LPCVD silicon nitride is a dielectric that is commonly available in most micro fabrication facilities and which has a relatively high dielectric constant of 7.9. However, the interface between silicon nitride and silicon is not very well defined and can result in leakage currents and reduced breakdown voltages. A commonly used method to mitigate these issues is to line the silicon nitride layer with thin silicon oxide layers, resulting in a so called oxide-nitride-oxide (ONO) multilayered dielectric. Generally, a minimum of 5 nm silicon dioxide is needed for a reliable ONO dielectric [21].

To get a feeling for the increase in capacitance density that can be obtained by the use of an ONO stack instead of a pure oxide dielectric, a 25 nm thick silicon dielectric was compared with a 5-10-10 nm ONO stack. In the case of the silicon oxide layer the capacitance density is calculated to be 1.4 nF/mm<sup>2</sup>. In the case of the ONO stack the capacitance density is calculated to be 1.7 nF/mm<sup>2</sup>. Note that although the dielectric breakdown and the thickness of the layer is equal, an improvement in capacitance density is established.

#### 2.5 Conclusion

The previous chapter has demonstrate the possibility to simplify the fabrication of low and high voltage capacitors by using a multilayer ONO dielectric. Next, the advantage of a trench capacitor over a plate capacitor is shown and the benefits of using a multilayered ONO dielectric is shown compared to a single layer dielectric.

# 3. Trench capacitor process flow and mask design

#### 3.1 Introduction

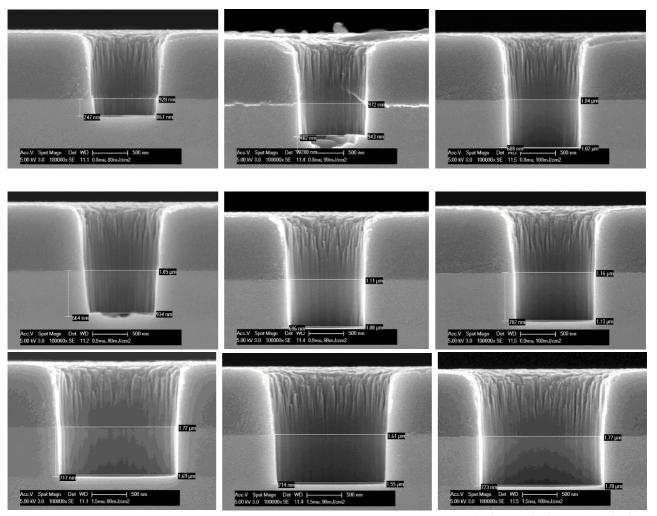

For the fabrication of the trench capacitors, a dedicated flowchart and mask set is design. Apart from the initial idea and the conditions that follow from the required integration in the F2R flow, little of the processing was defined. Therefore, numerous small experiments, so called shortloops, were performed to optimize the fabrication process. Many of the experiments were verified by one or two iteration steps. However, some processes needed more attention to achieve the desired result. These processes are discussed in Chapter 4. The combination of the process steps result in a device specific process flow, which can be seen as the blueprint for the fabrication of the trench capacitors. The designed process includes five photolithography steps that require five corresponding mask layers. This chapter first describes the fabrication of the trench capacitors, and choices that are made regarding the processing are discussed. Secondly, the mask set, which is designed for the fabrication process, is explained.

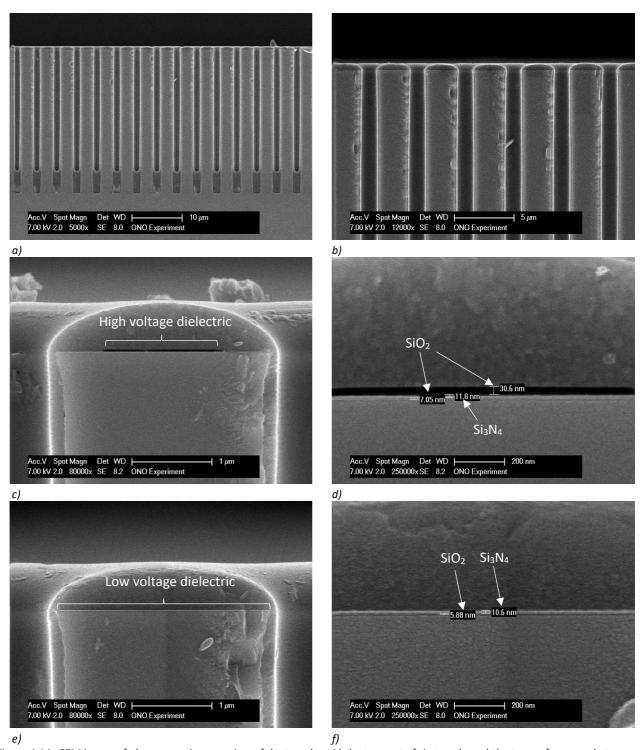

#### 3.2 Process flow

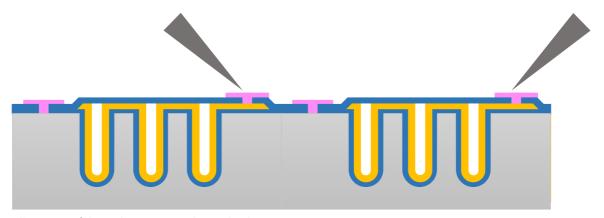

The process flow for the trench capacitors describes the fabrication process from plane wafer to measurable devices. The process flow is accompanied with a dedicated flowchart, which can be found in the appendix section A. Due to the high aspect ratio of the trenches, it is difficult to visualize an on-scale representation of the trench capacitors. Therefore, the illustrations in the process flow in this section are schematic cross-sections and do not correspond to the real life dimensions and scales. Three off-scale trenches represent the trench field in the capacitor. In addition, the thickness of the layers is off-scale because some layers would disappear from the illustration in a true-to-life representation. The footnotes refer to corresponding sections in the appendix B for extensive information regarding the process technology that is involved in the fabrication. The process flow is split in three sections, called technical stages; 1) trench etch, 2) deposition of the dielectric and top electrode and 3) closing of the trench and bond pads deposition.

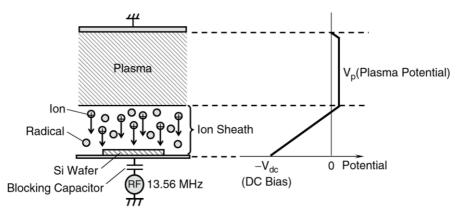

# 3.2.1 Trench etch The fabrication of the trench capacitor starts with a highly arsenic doped n-type silicon wafer. The silicon substrate functions as the bottom electrode of the capacitor and therefore a low resistivity is required. the resistance of the doped silicon substrate is in the range from 1 to 3 m $\Omega$ -cm The wafer is first cleaned in a Cintillio cleaning tool. Next, a 700 nm thick layer of silicon dioxide is deposited using PECVD¹. The silicon dioxide will function as a hard mask to pattern the silicon substrate.

19

<sup>&</sup>lt;sup>1</sup> Section 9.2.1

To pattern the silicon dioxide, a 1300 nm thick layer HPR504 in spin coated onto the wafer and patterned by a photolithography step . The focus for the lithography is fixed and the exposure energy doses was determined at  $100 \, \text{mJ/cm}^2$ . To pattern the photoresist the TRC\_TRENCH mask is used.

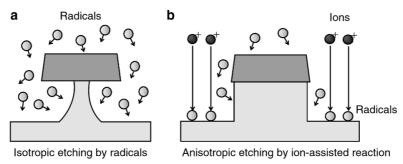

A dry etch step transfers the pattern from the photoresist into the silicon dioxide. The process development for dry etching the silicon dioxide and the Deep Reactive Ion Etch (DRIE) for the trenches in the silicon substrate are explained in chapter 4.

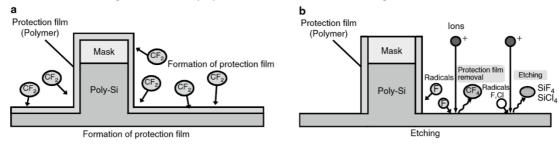

The trenches in the silicon substrate are etched using the a special DRIE process, the so called BOSCH process<sup>3</sup>. In addition, the duration of the BOSCH process removes the photoresist from the wafer.

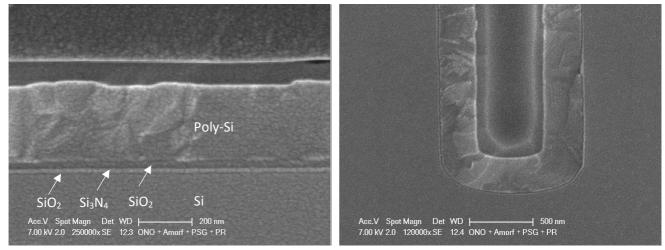

#### 3.2.2 Dielectric and top electrode deposition

Two different dielectric layers are studied in the development of the trench capacitor. First, a silicon dioxide layer and second, a silicon dioxide – silicon nitride – silicon dioxide (ONO) multilayer dielectric. The thickness of the dielectric layers can be adjusted to the required breakdown voltage and capacitance. To fabricate the low and high voltage parts in the multilayer dielectric, the top silicon dioxide is partially removed, as explained in section 2.3.1. This technical stage first describes the fabrication of the silicon dioxide single layer dielectric, followed by the ONO multilayer dielectric and the creation of the low and high voltage parts in the dielectric. Subsequently, The process flow continues with the deposition of the top electrode.

<sup>&</sup>lt;sup>2</sup> B.2 Photolithography

<sup>&</sup>lt;sup>3</sup> B.3 Dry Etching

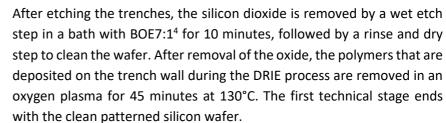

<sup>&</sup>lt;sup>4</sup> B.4 Wet Processing

### Single layer silicon dioxide dielectric

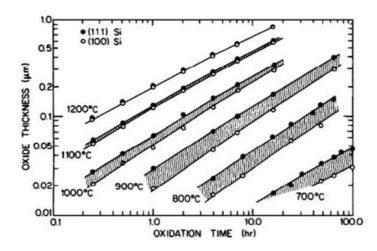

Before deposition of the dielectric layer and top electrode, the wafer is cleaned to prevent contamination of the furnace tubes. In addition, the native oxide is removed by an etch wet etch step in BOE7:1. After cleaning, a layer of silicon dioxide is thermally grown<sup>5</sup> on the wafer at 850°C. Is layer is deposited by dry oxidation. The thickness of the silicon dioxide is chosen according to the required breakdown voltage and capacitance.

# Multilayer ONO stacked dielectric

As with the single layer dielectric, before deposition of the first dielectric layer the wafer is cleaned. After cleaning, first a layer of silicon dioxide is thermally grown<sup>5</sup> at 850°C.

Onto the silicon dioxide layer, a silicon nitride layer is deposited using LPCVD<sup>1</sup>.

The second layer of silicon dioxide is deposited using LPCVD TEOS<sup>1</sup> and can chosen according to the required breakdown voltage for the high voltage part of the dielectric layer.

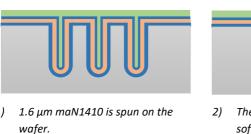

To pattern the top silicon dioxide layer, a negative photoresist is spin coated onto the wafer. Because it is difficult to illuminate a positive photoresist to the bottom of the trench in order to be able to expose and develop it<sup>2</sup>, a negative photoresist is used. For this photoresist the unexposed resist will be removed during developing. To pattern the photoresist the TRC\_ONO mask is used.

For the fabrication of the low voltage part in the dielectric, the top silicon dioxide is removed by a wet etch step in a bath with BOE7:1. The etch times is determined by the chosen layer thickness.

To remove the photoresist from the trenches after etching the silicon dioxide, the wafer is cleaned in an oxygen plasma for 45 minutes at 130°C.

After fabrication of the dielectric layer, the top electrode is applied. In the remainder of the process flow, the single layer silicon dioxide dielectric is used in the illustrations.

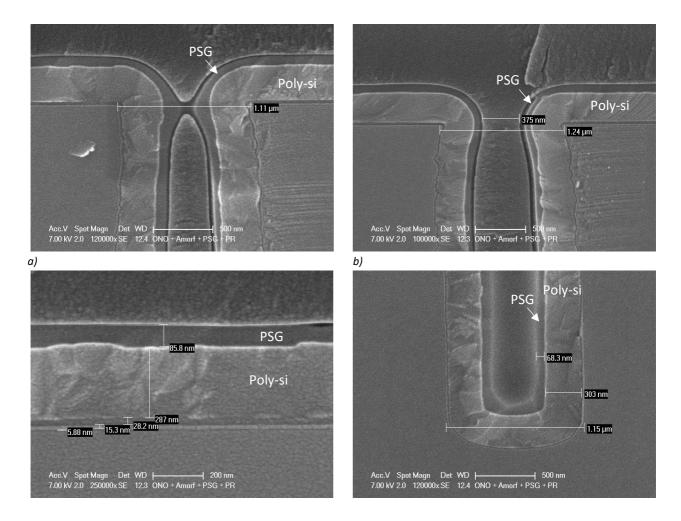

The top electrode of the capacitor is a 400 nm thick layer of doped polycrystalline silicon (Poly-Si). Details regarding the electrical properties of the Poly-Si are described in chapter 4. To obtain the Poly-Si layer, first a 400 nm thick amorphous silicon layer is deposited by LPCVD.

Next, a 100 nm thick layer of phosphosilicate glass<sup>1</sup> (PSG) is deposited as a solid dopant source. A 30 minutes anneal step at 1000°C migrates the dopant atoms from the PSG into the amorphous silicon<sup>6</sup>. The elevated temperature causes the crystals in the amorphous silicon to rearrange and thereby forming polycrystalline silicon.

After the anneal, the PSG is removed using BOE7:1 for 90 seconds<sup>4</sup>. A sheet resistivity of  $^{\sim}1$  m $\Omega$ ·cm is obtained in the Poly-Si layer.

To pattern the Poly-Si, a 1300nm thick layer of HPR504 is spin coated onto the wafer and patterned by a photolithography step, using a focus of -0.3  $\mu$ m and exposure energy doses of 120 mJ/cm<sup>2</sup>. To pattern the photoresist the TRC\_POLY mask is used.

To improve the step coverage of the silicon dioxide that will later be deposited over the Poly-Si, the photoresist is baked on a hot plate at 150°C for 120 seconds after development. The bake cause the photoresist to reflow, which creates a slope of ~45° at the edges of the photoresist.

A dry etch process pattern the Poly-Si. During the etch, the slope in the photoresist is transferred into the Poly-Si.

After etching of the Poly-Si, the photoresist is stripped in an oxygen plasma for 45 minutes at 130°C. The etch recipe to pattern the Poly-si lands on the dielectric layer, it is possible that very thin dielectric layers are removed in this process step despite the selectivity of the etch recipe.

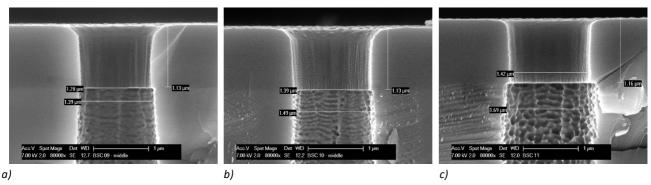

# 3.2.3 Trench closing and bond pad deposition

After deposition of the dielectric and top electrode, the trench capacitors are closed. Closing of the trenches is crucial to prevent damage to the capacitors by the etch process for the buried trenches in the F2R process flow, as discussed in section 1.2. Using PECVD<sup>1</sup>, a 700 nm thick layer very low stress silicon dioxide closes the trenches.

After deposition of the silicon dioxide, a 1300nm thick layer of HPR504 is spun onto the wafer and patterned by a photolithography step. The focus for the lithography is -0.3  $\mu m$  and the exposure energy doses in determined at 150 mJ/cm. To pattern the silicon dioxide the TRC\_CONTACT mask is used.

Next, the silicon dioxide is opened by a dry etch step to create contacts to the Poly-Si and the silicon substrate.

The photoresist is stripped in an oxygen plasma for 5 minutes.

1  $\mu$ m AlCu1% is deposited for the formation of bond pads. The small amount of copper in the aluminum expands the lifetime of aluminum by encountering damage due to electro migration in the aluminum layer [25]. Before deposition of the aluminum, the wafer is dipped in a bath of hydrogen fluoride (HF) and rinsed to remove the native oxide on the surface to improve the contact resistance of the metal to the silicon<sup>4</sup>.

To pattern the bond pads, 1300nm HPR504 is spin coated on the wafer and patterned by a photolithography step. The focus for the lithography is -0.3  $\mu$ m and the exposure energy doses in determined at 150 mJ/cm. To pattern the silicon dioxide the TRC\_AL mask is used.

To pattern the bond pads, 1300nm HPR504 is spin coated onto the wafer and patterned by photolithography. The focus for the lithography is -0.3  $\mu m$  and the exposure energy doses in determined at 150 mJ/cm. To pattern the silicon dioxide the TRC\_ AL mask is used.

# 3.3 Mask Design

# 3.3.1 Introduction

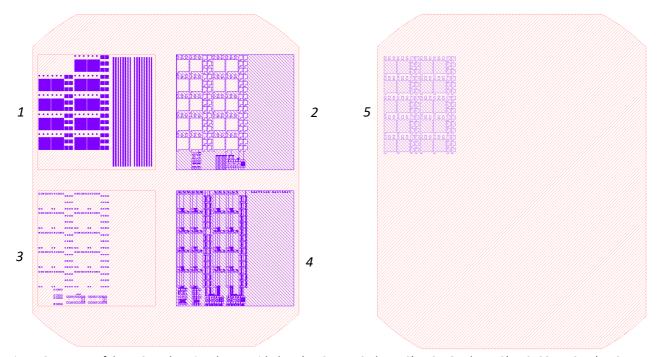

The TRC mask set can be considered as the starting point for the decoupling capacitors. The purpose of this mask set is to fabricate trench capacitors to verify the theoretically predicted capacitance values and to provide insight in the critical dimensions for the capacitor design. It was decided to design a new mask set for the production of the trench capacitors because there was no mask set available in the PInS cleanroom that could provide the required structures. This chapter describes the layout of the mask set and explains the different layers of the mask. Extensive information regarding the reticle information and mask design is given in section C

# 3.3.2 TRC overall layout

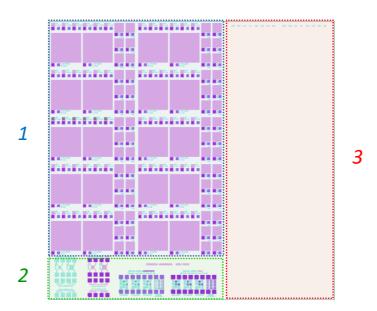

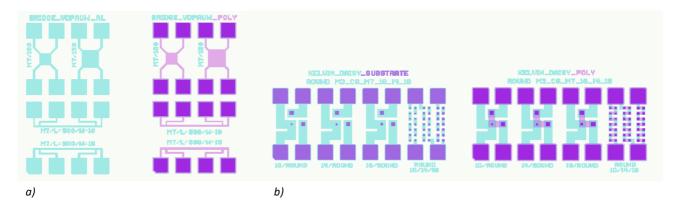

The TRC mask set can be divided in three areas. Fig 3.1 shows the design with the three different areas indicated by the numbers and corresponding blue, green and red shaded areas. The first area, shaded blue, is designed to measure different capacitor designs. The second area, shaded green, includes structures to measure the sheet resistance and contact resistance of the used materials in the capacitors like the aluminum and Poly-Si. The third area, shaded red, provides insight in the operation window regarding to the diameters for the trenches.

Figure 3.1, TRC Mask design with three different areas; 1) an area with capacitors, shaded blue, 2) test structures to test sheet and contact resistance, shaded green and 3) columns with different hole sizes for the investigation of the optimal trench size, shaded red.

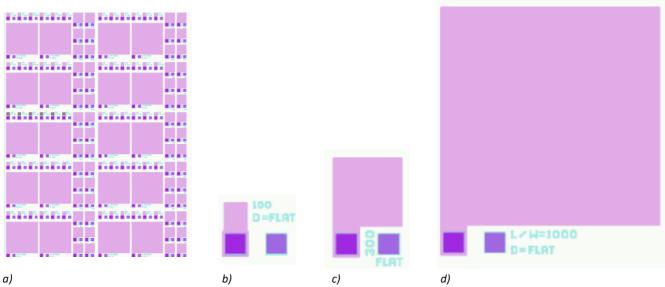

# Trench capacitors

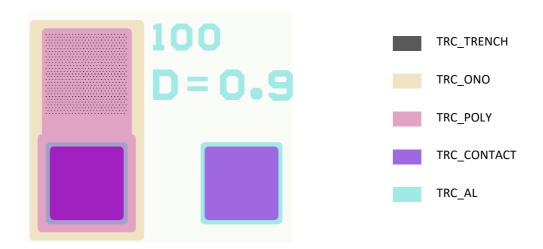

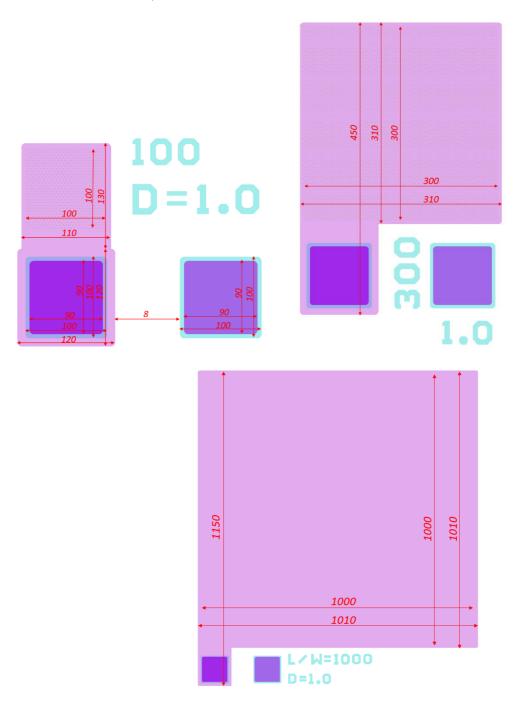

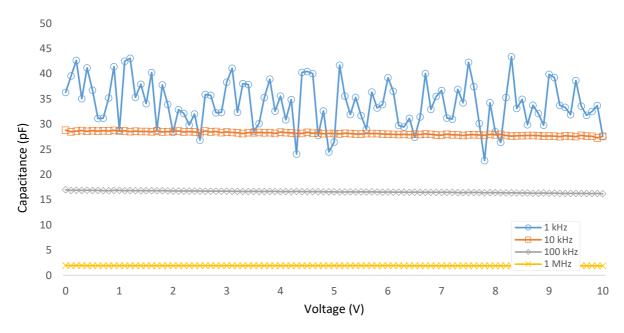

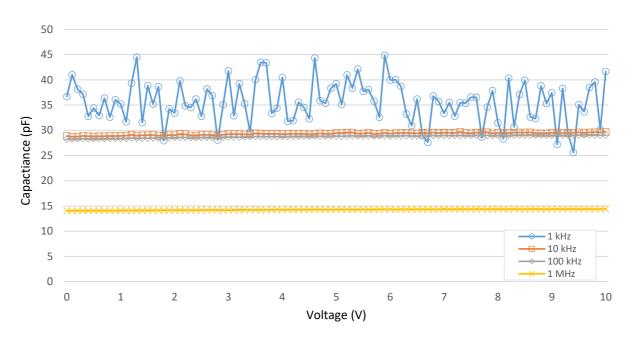

The area with capacitors is designed to measure different configurations of the capacitors (Fig 3.2a). The TRC mask set includes three different sized capacitors. The capacitors are indicated with the numbers 100, 300 and 1000, as shown in Fig 3.2b, 3.2c and 3.2d. The number refers to the length and width of the area in the capacitor where trenches can be applied. In the remainder of this work, these capacitors are labeled as CAP100, CAP300 and CAP1000, respectively. The variation in area size enables testing of the scalability of the capacitors.

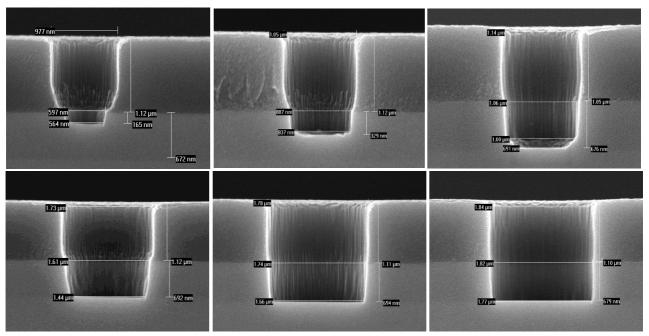

To gain insight in the influence of the trenches on the breakdown voltage and capacitance of the capacitor, trenches are applied to the CAP100, CAP300 and CAP1000 capacitors. The diameter of the holes on the mask to fabricate the trenches varies from 0.8 to 1.6  $\mu$ m. In appendix section C.2, a detailed overview of the variation in trenches over the capacitors and the exact dimensions of the test devices is presented.

Figure 3.2. Illustration of; a) the topography of the capacitors, b) the CAP100, c) the CAP300 and d) CAP1000.

### Van der Pauw and Kelvin structures

The working principle of a capacitor is based on an insulating layer between two conducting plates. In an ideal capacitor, the thickness of the dielectric layer is the only parameter that influences the electrical behavior, and the capacitance is therefore directly inversely proportional to the thickness of the dielectric. However, in reality several other factors influence the electrical behavior as well [19]. The series resistances in the material that is used for the electrodes and the contact resistance between two materials are factors that influence the working of the capacitor. For accurate information regarding the performance of the capacitor, it is important to gain insights in the series resistances. Van der Pauw structures and Kelvin structures are included on the TRC mask set to provide insight into different sheet resistances and contact resistances.

By performing a Van der Pauw measurement, a four-point probe system is placed around the perimeter of a sample (Fig 3.3a). When a current is applied over two adjacent probes, the voltage can be measured over the other two probes and the resistance can be calculated. Van der Pauw found that the relation between the voltage, current and sheet resistance may be written as [26]:

$$R = 4.53 \cdot \frac{V}{I} \tag{3.1}$$

The electrical resistance can be written proportional to the length l, cross section area A, or  $w \cdot t$ , and specific resistivity  $\rho$  of the material (equation 3.2).

$$R = \rho \frac{l}{A} = \rho \frac{l}{w \cdot t} \tag{3.2}$$

The specific resistivity is expressed in  $\Omega \cdot cm$  and is inversely proportional to the electronic charge e, the carrier mobility  $\mu$  and the carrier concentration n (equation 3.3). For semiconductors the carrier concentration can be either the electrons (n-type) or holes (p-type) concentration.

$$\rho = \frac{1}{n \cdot e \cdot \mu} \tag{3.3}$$

The sheet resistance  $R_s$  is the resistance per unit area and expressed in  $\Omega$ /square (equation3.4). The sheet resistance is equal to the resistivity of the material divided by the thickness of the layer.

$$R_S = \frac{\rho}{t} \tag{3.4}$$

Van der Pauw structures are designed to have equal length and width. Therefore, the measured resistance is the same as the sheet resistance (equation 3.5).

$$R = R_s = \frac{\rho}{t} \tag{3.5}$$

The Van der Pauw measurement can be used to determine the resistivity of the material when the thickness of the layer is known or can be used to determine the thickness of the layer when the resistivity of the material is known.

Kelvin structures measure the contact resistance of metal-semiconductor junctions. Two probes are placed on an upper material layer and two probes are placed on an underlying layer (Fig 3.3b). The four-point measurement is carried out by forcing a current between a probe connected to an upper material and a probe connected to the bottom material. The voltage is then measured between two other probes and the specific contact resistance is calculated from the voltage, current and contact surface (equation 3.6).

$$\rho_c = R_c \cdot A_c \tag{3.6}$$

Figure 3.3. a) Van der Pauw structures and b) Kelvin structures.

In the case of the trench capacitor, there are several factors that can influence the capacitance, for example;

1) the resistivity of the aluminum, Poly-Si and silicon substrate and 2) the contact resistance between the Poly-Si and aluminum, and between the silicon substrate and aluminum. With the above-mentioned structures, information regarding these values can be obtained.

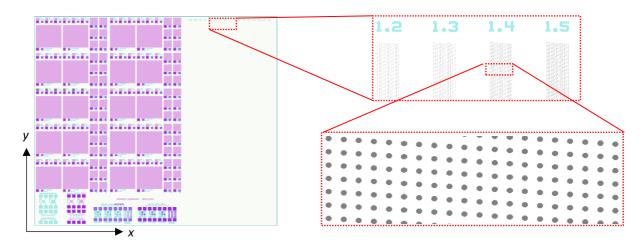

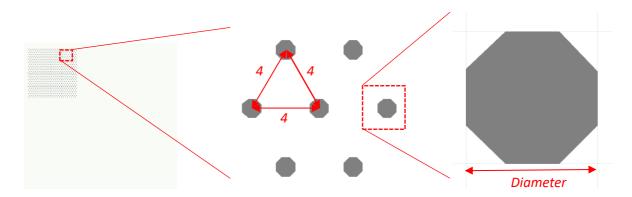

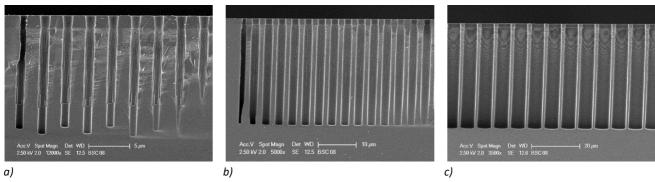

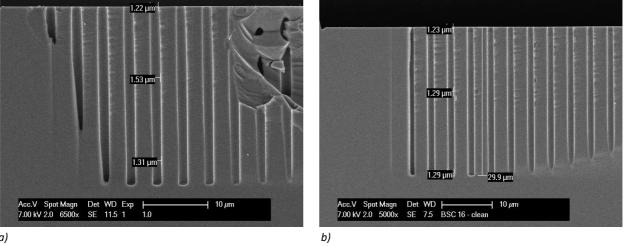

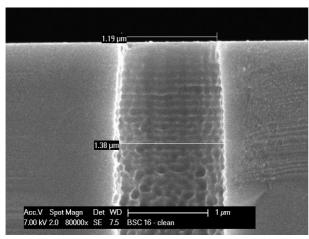

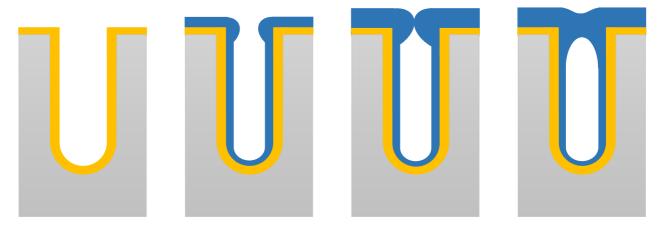

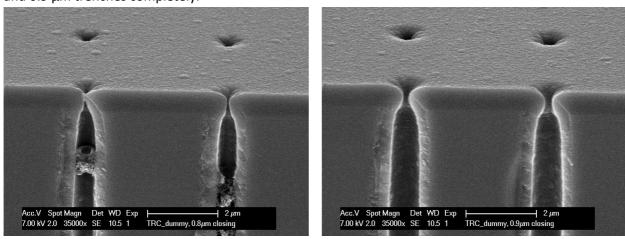

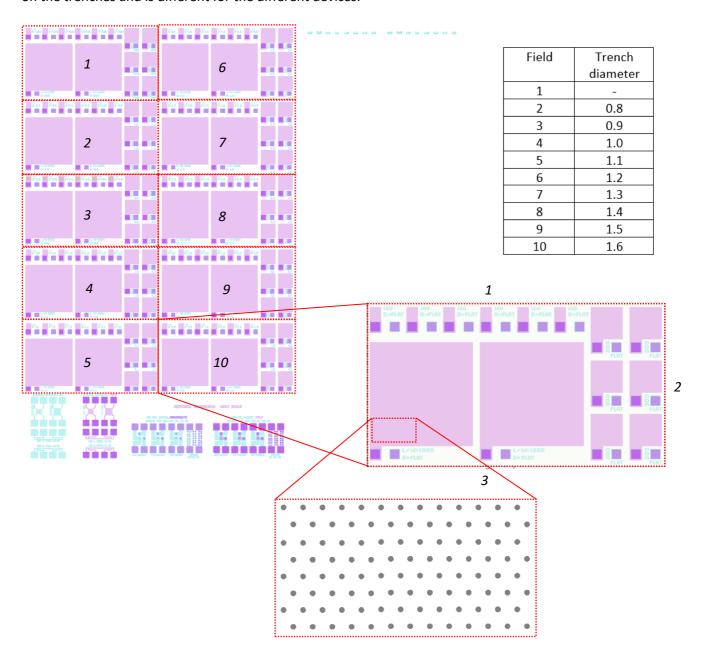

#### Diameter test structures

An important step in the process flow of the trench capacitors is the closing of the trenches by a 700 nm thick very low stress silicon dioxide layer. This layer will function as the hard mask for the etching of the buried trenches in the F2R process as described in section 1.2.1. When the trenches are not closed, the etch process to etch the buried trenches will damage the capacitor. The diameter of the trench is a crucial parameter in the design of the trench capacitors. The silicon dioxide layer cannot close an oversized trench. On the other hand, an undersized trench causes problems with the deposition of the dielectric layer and top electrode inside the trench. Furthermore, experiments have shown the complexity to fabricate (sub)micron trenches. To determine the optimal trench diameter, long columns with holes of varying diameters are designed on the mask. The diameter varies from  $0.8 \, \mu m$  to  $1.5 \, \mu m$ . The coverage of the dielectric layers and top electrode inside the trench and the closing of the trench by the applied silicon dioxide is verified by cleaving the sample and investigating the cross-section. The direction of a cross-section through the sample is determined by the crystal orientation. The crystal orientation causes a silicon wafer to break in the <110> direction. This orientation corresponds to the x and y axis of the mask design. To increase the chance of a successful cross-sectional cleavage through a hole when the wafer is broken according to the x axis, each column is slightly shifted in the y direction (Fig 3.4).

Figure~3.4.~Illustration~of~the~columns~with~holes~of~different~diameter~to~provide~insight~in~the~optimal~trench~diameter.

#### 3.3.3 TRC Mask set

The mask set is a five layer masks set, divided over two reticles, as described in table 3.1. This section describes the different layers of the mask. Fig 3.6 shows an image of the CAP100 on the mask with a legend that indicates the different mask layers.

| Name        | Layer | Reticle                   | Mask type  |

|-------------|-------|---------------------------|------------|

| TRC_TRENCH  | 1     | TrenchCaps / 051218-JNG01 | Clear tone |

| TRC_POLY    | 2     | TrenchCaps / 051218-JNG01 | Clear tone |

| TRC_CONTACT | 3     | TrenchCaps / 051218-JNG01 | Clear tone |

| TRC_AL      | 4     | TrenchCaps / 051218-JNG01 | Clear tone |

| TRC_ONO     | 5     | CBOX-OXIDE / 150319-JNG01 | Clear tone |

Table 3.1, TRC mask information

#### TRC\_TENCH mask

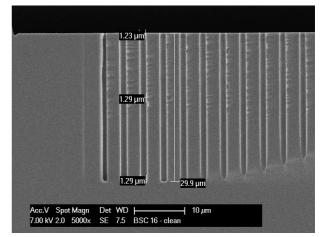

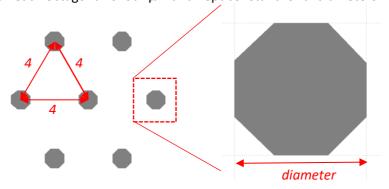

The TRC\_TRENCH mask is the layer to pattern the silicon dioxide that forms the hard mask for the DRIE process to etch the trenches in the silicon substrate. The mask contains the columns with holes to investigate optimal trench diameter and the fields with trenches that are applied to the capacitors. The holes for the capacitors are orientated in a centered rectangular lattice at a pitch of 4  $\mu$ m (Fig 3.5). To reduce the computer file size, the holes have an octagonal shape. The photolithography and etch processes in the cleanroom round the corners of the octagonal shape. The result is a circular hole in the silicon dioxide.

Figure 3.5. Image of the columns with holes of different diameter to test the trench size.

# TRC\_POLY mask

After etching of the trenches and the deposition of the dielectric layer and the Poly-Si, the Poly-Si is patterned with the TRC\_POLY mask layer. Since the Poly-Si is the top electrode of the capacitors, the dimensions of the Poly-Si are determinative for the calculations of the absolute capacitance and the dimensions of the TRC\_POLY mask layer are determinative for the calculation of the capacitance per footprint area. The TRC\_POLY mask layer does also include structures that are integrated in the Van der Pauw and Kelvin structures to measure the characteristics of the Poly-Si and the aluminum-poly contacts.

# TRC CONTACT and TRC AL mask

The purpose of the TRC\_CONTACT mask is to open the silicon dioxide layer that is applied to close the trenches. The opening provides a contact between 1) the aluminum and the Poly-Si top electrode and 2) the aluminum and the silicon substrate, which functions as the bottom electrode. After opening of the silicon dioxide, a layer of aluminum is deposited. The TRC\_AL mask layer patterns the aluminum to create the bond pads.

# TRC\_ONO mask

The fifth mask layer, which is located on the second reticle, is designed to fabricate the low and high voltage parts in the ONO dielectric layer. The top silicon dioxide layer of the ONO is patterned using the TRC\_ONO mask layer. Where the other four mask layers are used in combination with a positive photoresist, this mask layer used with a negative photoresist. Therefore, the open mask areas are the areas where the silicon dioxide is preserved.

Figure 3.6, Illustration of the combined mask layers for the CAP100 with 0.9  $\mu m$  holes.

# 4. Process development

# 4.1 Introduction

In the previous chapter the process flow and mask design were explained. The process flow for the trench capacitors consist of 94 individual process steps. The fabrication of the trench capacitors is step-by-step executed in Philips Innovation Service (PInS) cleanroom. A part of the fabrication is performed using established processes that are well understood. These processes are verified by one or two experiments to confirm their performance. However, some fabrication steps required more attention to achieve the desired result. Reasons to further investigate a specific topic can be 1) to obtain insight in the interaction of different parameters within one process or 2) the interaction with consecutive process steps.

This chapter first describes the development of a dedicated etch recipe to etch 1.2  $\mu$ m wide, high aspect ratio trenches. Next, the dielectric deposition and patterning of this dielectric are explained, followed by the PSG deposition and doping of the Poly-Si and the patterning of the Poly-Si. Finally, the process to close the trench is reviewed.

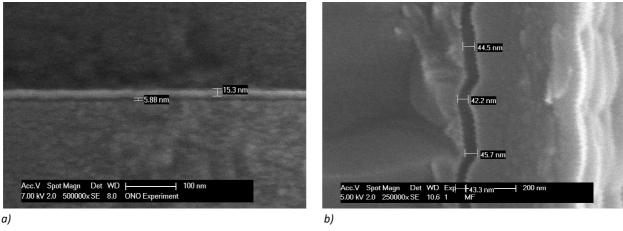

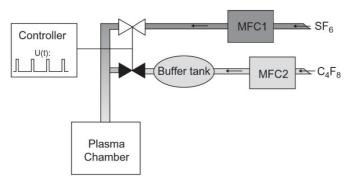

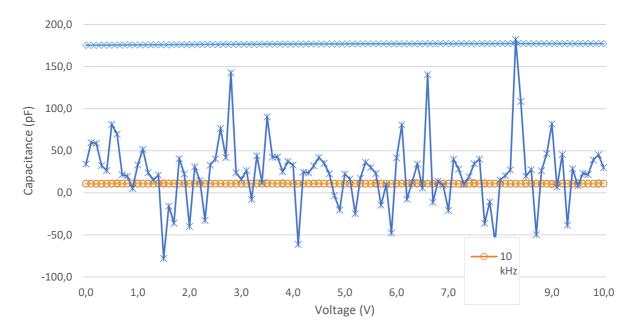

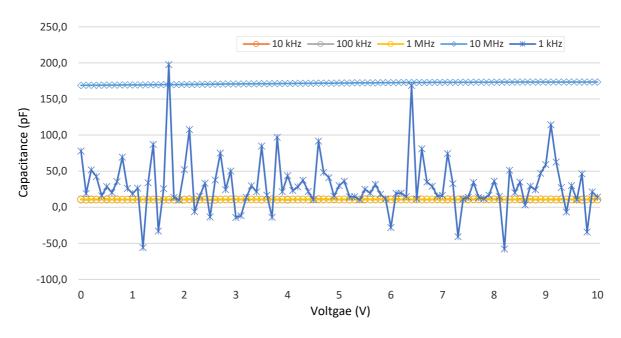

# 4.2 DRIE etch for high aspect ratio microscale trenches