# Towards Real-time SAR

Georgios Pinitas

### Towards Real-time SAR

Master's Thesis in Embedded Systems

Parallel and Distributed Systems group

Faculty of Electrical Engineering, Mathematics, and Computer Science

Delft University of Technology

Georgios Pinitas

1st July 2014

### **Author**

Georgios Pinitas

### Title

Towards Real-time SAR

# $\begin{array}{c} \textbf{MSc presentation} \\ \textbf{July } 10^{th}, 2014 \end{array}$

### **Graduation Committee**

Prof. Dr. Ir. H. J. Sips (Chair) Delft University of Technology Dr. Ir. Ana Lucia Varbanescu (Supervisor) Vrije Universiteit Amsterdam

M.P.G. (Mattern) Otten MSc TNO

Delft University of Technology Dr. Przemyslaw Pawelczak

#### **Abstract**

Nowadays, multiple different architectures exist, each one offering a performance boost on applications of different nature. Specialized and multicore computing is clearly mainstream, most application are ported or redesigned in order to expose any level of parallelism. Thus, new software and programming infrastructures have been introduced to help programmers exploit the benefits multi-core and specialized computing have to offer.

Radars are widely used for a variety of reasons. Their ability to operate in almost every weather condition, day and night, makes them an attractive solution. Synthetic Aperture Radar (SAR) is a radar infrastructure capable of creating high resolution spatial images. Most SAR processing chains operate on the frequency domain for lower computational demands, but the multi-core era has made time-domain processing feasible. Time-domain SAR processing can be quite demanding in terms of computational power for large problem sizes but overcomes formulation problems that frequency-domain algorithms face.

In this thesis, we investigated the possibility of achieving real-time performance on a SAR system, operating on the time-domain. For these purposes, the basic processing chain of such a system is analysed, implemented and optimized.

Overall, we manage to achieve real-time performance for different output dimensions mainly targeting Unmanned Aerial Vehicles (UAVs) and airborne solutions that operate under computational and power constraints. Furthermore, a hardware mapping of the computational components is proposed for their efficient execution. Moreover, we observe that multiple data rate reduction operations can be performed and still retain an acceptable Quality of System (QoS). Finally, the back-projection algorithm is optimized achieving a peak performance of 40 Giga Back-projections per second using a single hardware accelerator.

## **Preface**

From the very beginning of my postgraduate studies I was particularly intrigued by High Performance and Heterogeneous Computing. I am really glad that I had the opportunity to do my thesis in a relevant topic which also included some aspects of Embedded Systems. Doing something that you really like can only be followed by joy, independent of the difficulties that may emerge. This thesis was performed in collaboration with TNO. I hope that this work will help radar engineers and researchers by giving insights for future radar designs.

The completion of this undertaking could not have been possible without the support of so many people. Foremost, I would like to express my deepest thanks to my supervisor and mentor *Dr. Ana Lucia Varbanescu*, for her continuous support and help. Her patience, guidance and knowledge helped me throughout my postgraduate studies and my thesis. One could not have imagined having a better advisor. Further, I wish to express my gratitude to *Mr. Matern Otten* from TNO, for his help on topics I had no relevant experience. Without his help and immense knowledge this thesis would not have been feasible. Moreover, I would like to thank *Mr. Miguel Caro Cuenca* and *Mr. Wouter Vlothuizen* for their insightful conversations and their every day support. I would like also to acknowledge *Dr. Henk Sips* and *Dr. Przemyslaw Pawelczak* for being part of my graduation committee. Finally, I would like to thank *my family and friends*, I feel really blessed to have them in my life. Needless to say that this thesis is dedicated to them.

Georgios Pinitas

Delft, The Netherlands 1st July 2014

# **Contents**

| Pr                                 | eface                 |         |                                                       | v  |  |

|------------------------------------|-----------------------|---------|-------------------------------------------------------|----|--|

| 1                                  | Intr                  | oductio | on .                                                  | 1  |  |

|                                    | 1.1                   | Conte   | xt                                                    | 1  |  |

|                                    | 1.2                   |         | rch Questions                                         | 2  |  |

|                                    | 1.3                   |         | ibutions                                              | 2  |  |

|                                    | 1.4                   |         | s Organization                                        | 3  |  |

| 2                                  | Bac                   | kgroun  | d                                                     | 5  |  |

|                                    | 2.1                   | Paralle | elism                                                 | 5  |  |

|                                    |                       | 2.1.1   | Amdhal's Law                                          | 5  |  |

|                                    |                       | 2.1.2   | Models of Parallel Computation                        | 6  |  |

|                                    | 2.2                   | Hetero  | ogeneous Computing: A Hardware Approach               | 7  |  |

|                                    |                       | 2.2.1   | General Purpose Processors (GPP)                      | 8  |  |

|                                    |                       | 2.2.2   | Digital Signal Processor (DSP)                        | 9  |  |

|                                    |                       | 2.2.3   | General-purpose computing on Graphics Processing Unit |    |  |

|                                    |                       |         | (GPGPU)                                               | 11 |  |

|                                    |                       | 2.2.4   | Field-programmable Gate Array (FPGA)                  | 12 |  |

| 2.3 Parallel Programming Languages |                       |         |                                                       | 13 |  |

|                                    |                       | 2.3.1   | Open Computing Language (OpenCL)                      | 13 |  |

|                                    |                       | 2.3.2   | Compute Unified Device Architecture (CUDA)            | 14 |  |

|                                    |                       | 2.3.3   | Open Multi-Processing (OpenMP)                        | 16 |  |

|                                    |                       | 2.3.4   | Message Passing Interface (MPI)                       | 16 |  |

|                                    | 2.4 Real-time Systems |         |                                                       |    |  |

|                                    |                       | 2.4.1   | What Real-time Means                                  | 17 |  |

|                                    |                       | 2.4.2   | Types of Real-time Tasks                              | 17 |  |

|                                    |                       | 2.4.3   | Features of Real-time Systems                         | 18 |  |

|                                    | 2.5                   | Synthe  | etic Aperture Radar (SAR)                             | 18 |  |

|                                    |                       | 2.5.1   | Radar Principles                                      | 19 |  |

|                                    |                       | 2.5.2   | SAR Principles                                        | 20 |  |

| 3 | Soft       | ware Architecture            | 25        |

|---|------------|------------------------------|-----------|

|   | 3.1        | Processing Requirements      | 25        |

|   | 3.2        | Hardware Platforms           | 27        |

|   | 3.3        | Metrics                      | 28        |

| 4 | Mul        | ti-channel Back-Projection   | 29        |

| - | 4.1        | <b>v</b>                     | <br>29    |

|   | 4.2        | $\varepsilon$                | 30        |

|   | 4.3        |                              | 32        |

|   |            |                              | 32        |

|   |            | 1 1                          | 33        |

|   | 4.4        | 1 1                          | 33        |

|   |            | ·                            | 33        |

|   |            |                              | 35        |

|   | 4.5        | 1                            | 37        |

|   | 1.0        | -                            | 37        |

|   |            |                              | 38        |

|   |            | 1                            | 46        |

|   | 4.6        | 1                            | 47        |

|   | 1.0        |                              | . ,<br>47 |

|   |            | <b>5</b>                     | 17<br>47  |

|   |            |                              | - ,<br>48 |

|   | 4.7        |                              | 49        |

| _ |            |                              |           |

| 5 |            | 9                            | 51        |

|   | 5.1        |                              | 51        |

|   |            | I I                          | 52<br>52  |

|   | <i>-</i> - | 1 1                          | 52        |

|   | 5.2        |                              | 52<br>52  |

|   |            |                              | 52<br>52  |

|   |            |                              | 53        |

|   |            |                              | 54        |

|   | <b>7</b> 0 | 11 1                         | 56        |

|   | 5.3        | •                            | 56        |

|   | 5.4        | 1                            | 56<br>    |

|   | 5.5        |                              | 57        |

|   |            |                              | 57        |

|   |            |                              | 58        |

|   | 5.6        | Related Work                 | 51        |

| 6 | Deci       | mation and Channel Reduction | 63        |

|   | 6.1        | Decimation                   | 63        |

|   |            | 6.1.1 Requirements           | 63        |

|   |            | 6.1.2 Evaluation             | 54        |

| 6.  | 2 Channel Reduction                |

|-----|------------------------------------|

|     | 6.2.1 Requirements                 |

|     | 6.2.2 Evaluation                   |

| 7 M | ap Drift Autofocus                 |

| 7.  | 1 Algorithm                        |

| 7.  | 2 Implementation                   |

| 7.  | 3 Evaluation                       |

| 7.  | 4 Related Work                     |

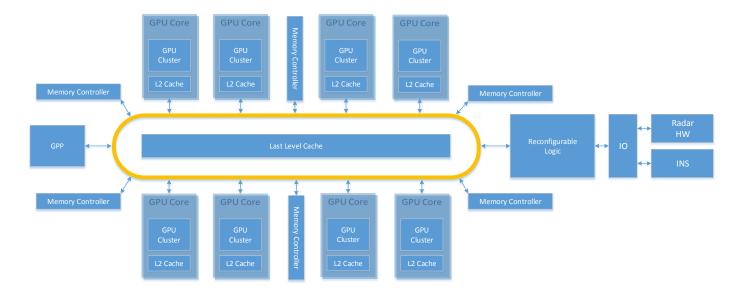

| 8 P | roposed System Architecture        |

| 8.  | 1 System Design                    |

|     | 8.1.1 Hardware Mapping             |

|     | 8.1.2 Custom Hardware Architecture |

| 8.  | 2 Scenarios                        |

|     | 8.2.1 Off-line High-end Processing |

|     | 8.2.2 Off-line Mobile Processing   |

|     | 8.2.3 On-line processing           |

| 9 C | onclusions and Future Work         |

| 9.  | 1 Conclusions                      |

| 9.  |                                    |

# **List of Figures**

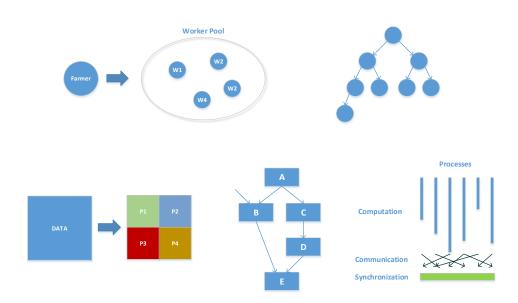

| 2.1  | Parallel Computation Models [38, 66]                               | 7  |

|------|--------------------------------------------------------------------|----|

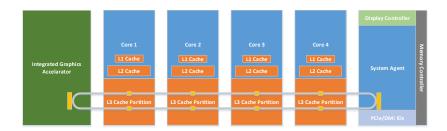

| 2.2  | Haswell system architecture                                        | 8  |

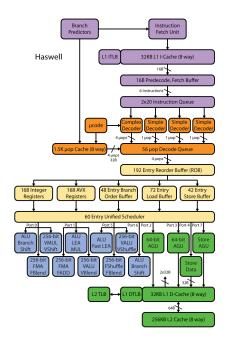

| 2.3  | The Haswell micro-architecture [12] (Courtesy of Real World Tech)  | 9  |

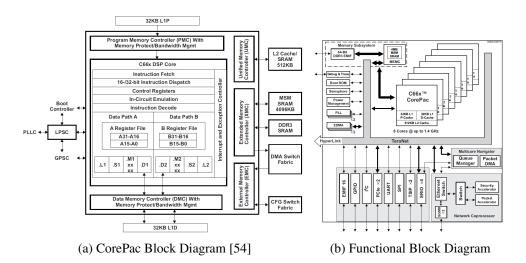

| 2.4  | DSP C66x [54] (Courtesy of Texas Instruments <sup>®</sup> )        | 10 |

| 2.5  | GK110 architecture [50] (Courtesy of NVIDIA ®)                     | 12 |

| 2.6  | SMX architecture [50] (Courtesy of NVIDIA ®)                       | 12 |

| 2.7  | FPGA architecture                                                  | 13 |

| 2.8  | OpenCL Architecture Model (Courtesy of Khronos Group)              | 14 |

| 2.9  | CUDA Thread and Memory Model                                       | 15 |

| 2.10 | OpenMP Example [67] (Courtesy of Wikipedia Commons)                | 16 |

| 2.11 | MQ-9 Reaper UAV equipped with SAR (Courtesy of U.S. Air Force)     | 19 |

| 2.12 | Radar Principle                                                    | 19 |

| 2.13 | SAR Principle [70] (Courtesy of Radartutorial.eu)                  | 21 |

| 2.14 | SAR Resolution                                                     | 21 |

| 2.15 | SAR Modes [70] (Courtesy of Radartutorial.eu)                      | 22 |

| 3.1  | SAR Software Architecture                                          | 25 |

| 4.1  | SAR back-projection                                                | 29 |

| 4.2  | Data flow diagram                                                  | 31 |

| 4.3  | Data Layout                                                        | 34 |

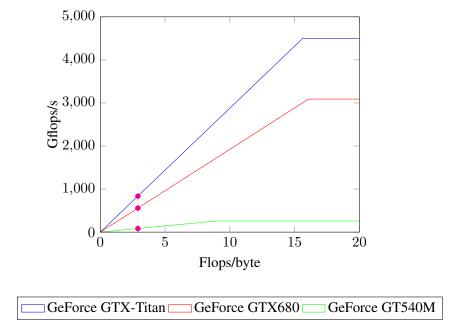

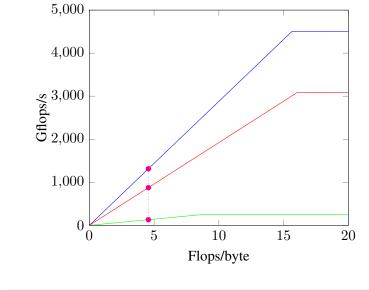

| 4.4  | Roofline model before applying any optimizations                   | 37 |

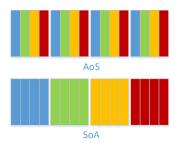

| 4.5  | Array-of-Structures (AoS) vs Structure-of-Arrays (SoA)             | 40 |

| 4.6  | Phase history                                                      | 41 |

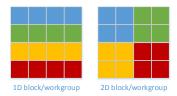

| 4.7  | Thread block/workgroup dimensionality                              | 42 |

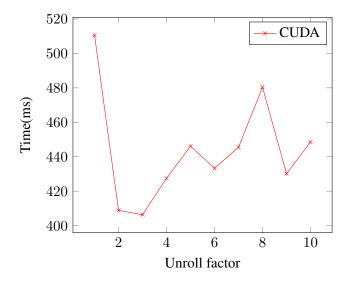

| 4.8  | Execution time with varying unrolling factor                       | 43 |

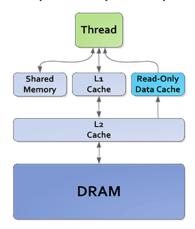

| 4.9  | Kepler cache hierarchy                                             | 44 |

| 4.10 | Roofline model after applying optimizations                        | 45 |

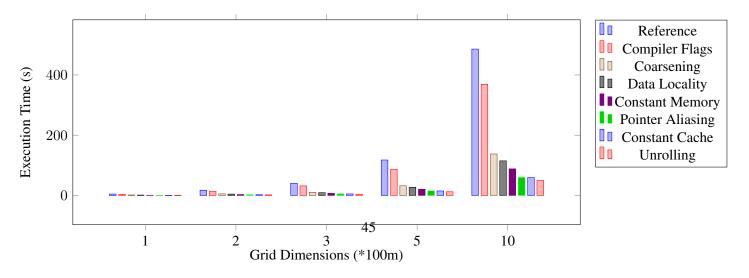

| 4.12 | Optimization impact on execution time                              | 45 |

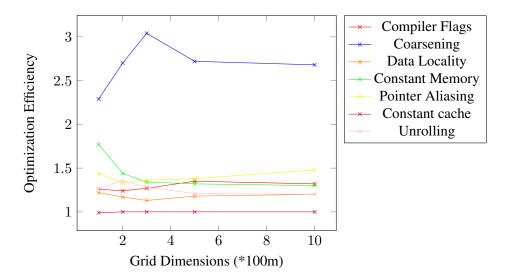

| 4.11 | Optimizations efficiency                                           | 46 |

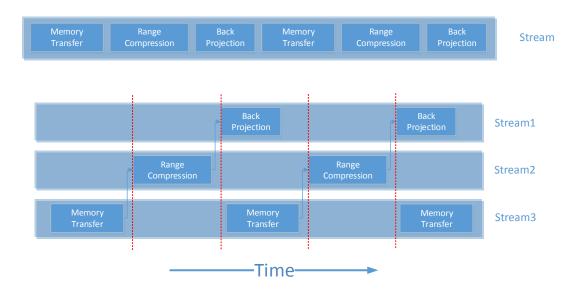

| 4.13 | Task parallelism on multi-channel back-projection                  | 47 |

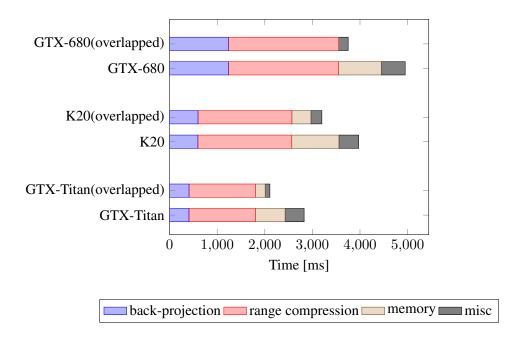

| 4.14 | Overlap impact for different devices (grid size of 100 by 100 m) . | 48 |

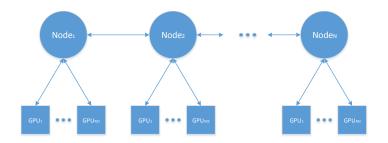

| 5.1  | Multi-node Multi-GPU implementation                                | 51 |

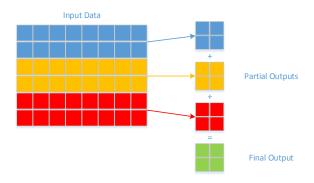

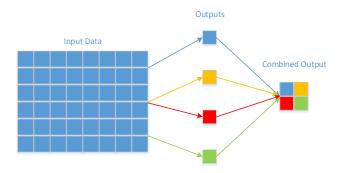

| 5.2 | Input-based parallelization                                    | 53 |

|-----|----------------------------------------------------------------|----|

| 5.3 | Output-based parallelization                                   | 55 |

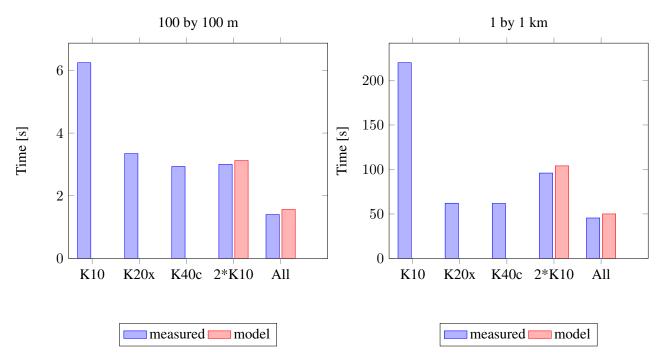

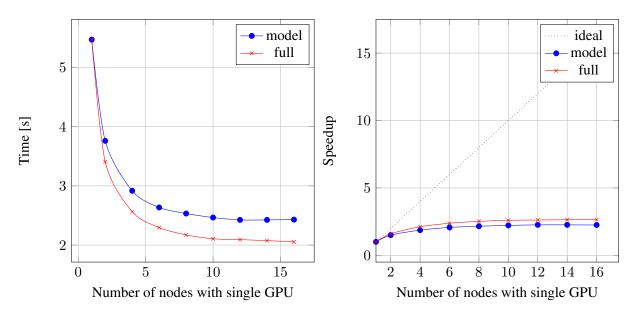

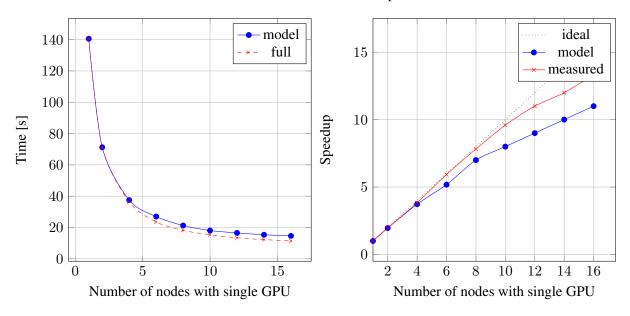

| 5.4 | Expiremental Results for the input-based multi-GPU approach    | 58 |

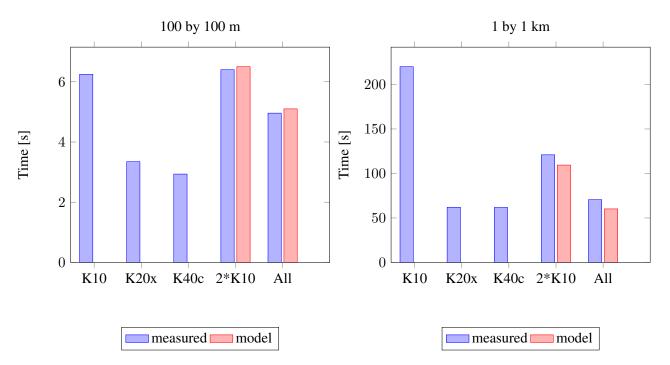

| 5.5 | Expiremental Results for the output-based multi-GPU approach . | 59 |

| 5.6 | Expiremental Results for a 100 by 100 meter voxel grid         | 60 |

| 5.7 | Expiremental Results for a 1 by 1 km voxel grid                | 60 |

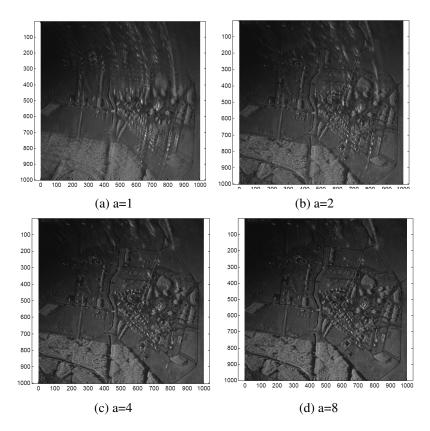

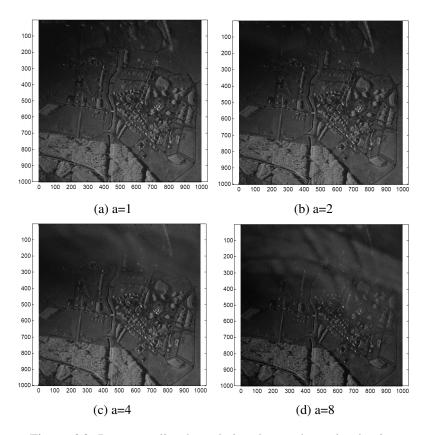

| 5.1 | Image quality with varying upsampling factor                   | 65 |

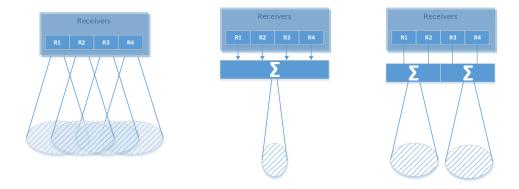

| 5.2 | Channel Reduction                                              | 66 |

| 5.3 | Image quality degradation due to channel reduction             | 67 |

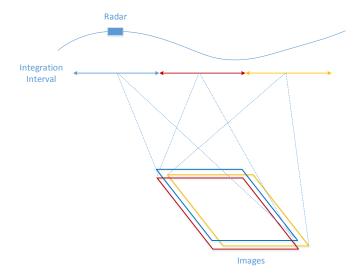

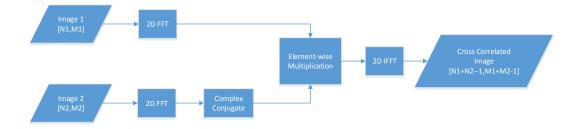

| 7.1 | Map Drift                                                      | 69 |

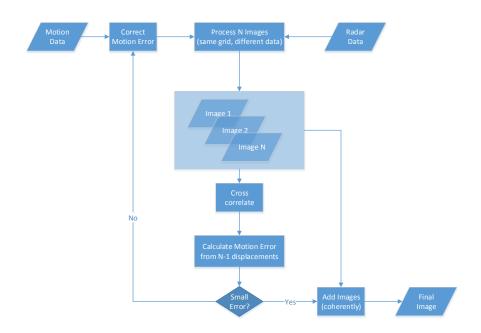

| 7.2 | Map Drift autofocus process chain                              | 70 |

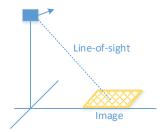

| 7.3 | Line-of-sight displacement                                     | 71 |

| 7.4 | Cross-correlation using FFTs                                   | 72 |

| 8.1 | Proposed Module Mapping                                        | 76 |

| 8.2 | Custom Architecture                                            | 77 |

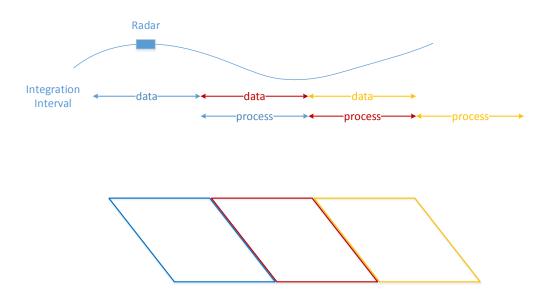

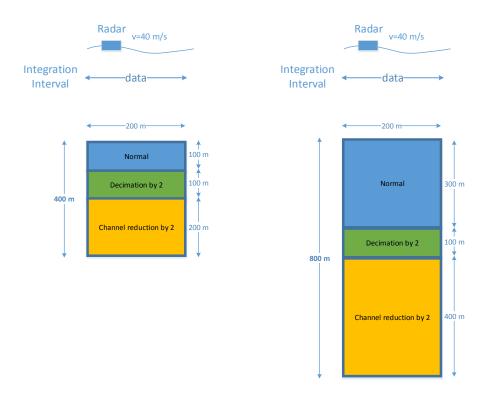

| 8.3 | Real-time Processing                                           | 81 |

| 8.4 | Real-time Grid Dimensions (left NVIDIA Geforce GTX680, right   |    |

|     | NVIDIA Titan)                                                  | 82 |

### Acronyms

QoS Quality of System

HDL Hardware Description Language

SIMD Single Instruction Multiple Data

**SPMD** Single Program Multiple Data

**CPU** Central Processing Unit

**GPP** General Purpose Processors

**DSP** Digital Signal Processor

ISA Instruction Set Architecture

MAC Multiply-accumulate

FFT Fast Fourier Transform

**GPU** Graphics Processing Unit

GPGPU General-purpose computing on Graphics Processing Unit

**GPC** Graphics Processor Cluster

**FPGA** Field-programmable Gate Array

**ASIC** Application Specific Integrated Circuit

API Application Programming Interface

**OpenCL** Open Computing Language

**CUDA** Compute Unified Device Architecture

**OpenMP** Open Multi-Processing

MPI Message Passing Interface

SAR Synthetic Aperture Radar

**UAV** Unmanned Aerial Vehicle

**TDC** Time-Domain Correlation

**GMTI** Ground Moving Target Indication

**INS** Inertial Navigation System

**DBF** Digital Beamforming

**GPS** Ground Positioning System

**PGA** Phase Gradient Algorithm

FMCW Frequency-Modulated Continuous-Wave

**SRF** Signal Repetition Frequency

AoS Array-of-Structures

SoA Structure-of-Arrays

**PSNR** Peak signal-to-noise ratio

## **Chapter 1**

### Introduction

### 1.1 Context

For many years, CPU designers used to achieve higher performance by mainly focusing on increasing the frequency of a system. Exploitation of frequency scaling became harder over the years due to physical limitations like the dramatical increase in power consumption and thermal dissipation. In order to fulfil the needs for higher performance out of a system, designers turned into exploiting the small transistor size by deploying multiple cores with lower frequencies on a single chip. This led to both an increase in performance but also a relative smaller and more controllable power consumption.

Applications also used to drive the design of hardware architectures in order to increase their performance; a glaring example are DSPs and Application Specific Integrated Circuits (ASICs). But the mutlicore trend gave birth to even more. The type of parallelism an application could express led to the design of hardware architectures with varying core complexity and core number.

Many practical problems emerged by multicore and specialized computing. The most important one was the dramatic shift that had to take place in the programming area. This led into renovating existing or creating new programming languages capable of expressing parallelism and as a result exploiting the benefits multicores have to offer.

Radars are widely used nowadays for a variety of reasons. Their ability to operate in almost every weather condition, day and night, makes them an attractive solution. SAR is a form of radar deployed on moving platforms like satellites and aircrafts and is capable of creating high resolution spatial images. The computational demands of such a radar system are high, thus achieving real-time performance, at first glance at least, seems impossible.

In this thesis, we focus on analysing the processing steps of a SAR system and investigating the possibility of achieving real-time performance under multiple processing scenarios. Our main interest lies in achieving real-time performance for UAVs and airborne solutions in general, that operate under computational and

power constraints.

### 1.2 Research Questions

This section presents the research questions that this thesis aims to answer. The main research addressed is:

Can the proposed SAR processing chain achieve real-time performance under computational and power constraints?

More research questions that this thesis addresses are:

- What are the current hardware and software trends in heterogeneous computing?

- What are the main processing modules of a SAR systems and what are their requirements in terms of computational power?

- How can multi-channel back-projection be efficiently parallelized and what are its bottlenecks and limitations?

- Is the performance of different optimisations affected by problem size and input data variability?

- Can the computational needs of the application be reduced and still retain an acceptable high QoS?

- Is there an efficient hardware mapping and a custom architecture for the processing modules of the system?

### 1.3 Contributions

The main contributions of this thesis are the following:

- We survey current trends in terms of hardware and software.

- We analyse the processing chain of a state of the art SAR system, investigating in detail all the processing steps and proposing efficient implementations of each one separately.

- We investigate how the optimisations effect change with problem scalability and input data variability.

- We propose a module mapping along with a custom hardware architecture where each module of the processing chain is deployed on the appropriate hardware architecture to achieve higher performance and lower power consumption.

### 1.4 Thesis Organization

This thesis is organized as follows. Chapter 2 provides all the background information required for further understanding the contents of the thesis. It presents the concept of parallelism along with the models used for expressing parallel computations. Moreover, a thorough analysis of the current hardware diversity takes place, along with the parallel programming language trends that exist nowadays. Finally, an introduction in SAR and radar systems in general takes place.

Chapter 3 lists the distinct processing modules that a SAR system requires nowadays. In addition, the specifications of the experimental setup that was used are presented.

Chapters 4 and 5 present and analyse the multi-channel back-projection algorithm, the most compute intensive component of the the SAR system. Different parallel implementations are shown along with the optimization steps. In addition, a multi-node multi-GPU implementation is analysed and a model is proposed.

In Chapter 6 two techniques are analysed specialized in reducing the data rate of the radar system and as a result the computational requirements of compute intensive processing steps of the processing chain.

Chapter 7 describes the autofocus algorithm that we used for correcting large motion errors.

In Chapter 8 we propose a custom architecture, specialized for the presented software architecture. Moreover, three different possible processing scenarios are analysed along with their performance and limitations.

Finally, our concluding remarks and future work directions are gathered in Chapter 9

## **Chapter 2**

# **Background**

In this chapter we present the basic concepts required to ease the understanding of the more complex material in this thesis. Specifically, we discuss parallelism models, hardware trends, programming models and the basic principles behind SAR.

### 2.1 Parallelism

Due to the explosive trend of multi-core architectures, the urge of exploration and exploitation of the benefits that they have to offer is inevitable. Clearly, exploiting hidden or evident *parallelism* is one way to do so.

Programs or tasks may have computational workloads that can inherently run in parallel with one another or be remodelled to do so. The fundamental argument of parallelism is to run compute intensive tasks, that need rather a long amount of time, in parallel. More and more legacy application are being ported or remodelled in order to exploit such a possibility. But still, limitations exist to the level of parallelism that can be exploited.

### 2.1.1 Amdhal's Law

Blindly parallelizing sequential applications may lead to very limited performance gain. In 1967, G. Amdahl [1] stated that the performance gain of a parallel application over its sequential version is limited. This statement is widely known as *Amdahl's Law*.

In more detail, Amdahl's Law specifies that if s is the sequential part of the program and 1-s the part of program that can be parallelized, then the maximum expected improvement S using P number of processors is:

$$S(P) = \frac{1}{s + \frac{1-s}{P}} \tag{2.1}$$

As a consequence, when  $P \to \infty$ , then the maximum possible speedup is bounded by the portion of the sequential part of the program. For this reason,

best candidates for parallelization tend to be portions of a program that account for a significant amount of the total execution time.

Finally, we have to point out that *Amdahl's Law* is a generalized argument, which over the years has been re-evaluated or complemented to adapt to the current multicore era [23, 39]. Multiple models have been introduced based on scalable computing where an increase in computing power can lead to an increase in the problem size as well.

### 2.1.2 Models of Parallel Computation

Implementing a parallel version of an algorithm is considered, for many, the "trivial" part of the whole paralellization process. The most important part tends to be the deep understanding of the underlying algorithm along with the modelling of parallelism that can be exposed. For this reason, conceptually at least, we can classify the way a parallel program can be modelled in one the following categories [38]:

- Farmer-Worker/Master-Slave: In this model the workload can be distributed among algorithmically identical processes, each one taking different input arguments than the other. Usually, a Farmer thread or process is responsible into splitting and assigning work among the Worker threads/processes. The idle Worker threads are usually part of a thread pool, where the Farmer thread checks for available threads to assign work. When a Worker thread finishes its work, it becomes again part of the thread pool waiting for further assignments.

- **Divide and Conquer:** In this model, the problem can be divided recursively in smaller problems until they become small enough to be fast to solve. Finally, all the partial solutions are combined to solve the initial problem. It is important to point out that each sub-problem is theoretically independent of the others, which makes concurrent or parallel execution feasible.

- Data Parallelism: In this model, computation follows the data. The data are distributed in different computing nodes each one performing the same task (executing the same code) on its own data. When finished, the data are usually gathered on a single node forming the final solution.

- Task Parallelism: In this model the basic tasks/function can be isolated, each one being responsible for solving a specific sub-problem. Each task acts on specific arguments providing specific outputs. The dependency between these tasks can be represented using an acyclic directed graph. The way these tasks can be mapped onto a structure of processors is not trivial, thus two types of execution models can be concluded: data-driven and demand-driven. In the data-driven execution model, a task proceeds to execution when the input arguments are available, while in the demand-driven, execution of a task occurs when the provided data are required further in the pipeline.

- Bulk-synchronous [59]: In this model, the problem can be solved though an iterative process, until solution convergence. Every iteration consists of three distinct steps: a computation step, a communication step and finally a synchronisation step. Each process performs the computation steps asynchronously with respect to the other processes. When computations end, processes can exchange data if required. Finally, for consistency, a synchronisation step follows where all individual processes reach a certain point before proceeding further.

- **Hybdid:** Every possible combination of the above models falls in this category.

Figure 2.1: Parallel Computation Models [38, 66]

### 2.2 Heterogeneous Computing: A Hardware Approach

The need for specialized computing has led to the hardware diversity we experience nowadays. The fundamental premise of specialized or, as it is widely known, heterogeneous computing is having a task or a specialized workload to run on the most appropriate hardware platform in order to achieve the best performance and the lowest power consumption.

In this section, we describe the most important hardware categories that can be found nowadays in computing infrastructures.

### 2.2.1 General Purpose Processors (GPP)

All the conventional, general purpose, computer architectures which consist of one (rarely) or several homogeneous cores fall in this category.

They are shared-memory architectures with a multi-layer cache hierarchy and usually facilitate complex performance oriented hardware level optimisations (e.g. branch prediction, dynamic execution). They are mostly used as stand-alone processors, but newer designs, with significantly improved performance capabilities, have been created to be used as high performance coprocessors, like Knights Corner and Knights Landing (brand name Xeon Phi) [21, 13].

They target almost the whole market spectrum, from mobile devices to servers, and are offered by many industrial vendors like Intel, AMD, IBM and ARM.

**Intel Haswell** is the latest generation of Intel's GPPs [12, 46] <sup>1</sup>.

A large of variety of models based on Haswell architecture are released or planned to be released soon, depending on the target market (e.g. High Performance, Low Power).

Most high performance designs come with four *physical cores*. Each one, due to Hyper-Threading Technology, can be seen as consisting of two individual cores, usually called *logical cores*. Hyper-Threading tries to exploit the fact that not all execution resources are being used during the execution of an instruction. By duplicating some resources, for example resources that keep the state of the program, gives the illusion of two distinct cores and the ability to run two independent processes or tasks in parallel.

Figure 2.2: Haswell system architecture

Cores have private L1 and L2 8-way associative caches with sizes of 32 KB and 256 KB respectively. A L3 cache, shared between the processors, and has varying size depending on the model.

Haswell also supports out-of-order execution, being enhanced with multiple resources required for dynamic scheduling.

Both vector and integer registers are present in Haswell. In addition, multiple execution and address generation units exist. There is support for both scalar and

<sup>&</sup>lt;sup>1</sup>At the time of writing, May 2014

#### SIMD operations.

Interesting is the fact Haswell contains an *Integrated Graphics Accelerator* connected to the bus ring, giving the ability to run graphics (and not only) tasks. The Graphics Accelerator was updated with compute capabilities. Different versions exist across the GPP models. The latest one is the Iris Pro 5200 version.

The L3 cache, along with the ring bus, run at a higher frequency than the cores in order to ensure GPU's high performance while keeping the cores in a low power state.

An example model of Haswell architecture is *i7-4770K* with and integrated Haswell GT2 graphics card is presented in Figure 2.3. The CPU itself has a peak performance of 448 Gflops (AVX with FMA) while the GPU 400 GFlops. The power consumption is close to 85 W [19].

Figure 2.3: The Haswell micro-architecture [12] (Courtesy of Real World Tech)

### 2.2.2 Digital Signal Processor (DSP)

A significant number of applications are signal processing oriented. Typical examples are sound or image applications. The need to accelerate such an application and the power constraints of mobile devices led to the design of DSPs. DSPs are processors designed for the efficient manipulation of digital signals.

A DSP's architecture differs in many ways from other processors. First of all, they have a signal processing oriented Instruction Set Architecture (ISA), which enables easier and faster implementation of digital signal processing applications. As required from these algorithms they perform a significant amount of operations

in parallel per work cycle. Such operations may be Multiply-accumulate (MAC) operations or even Fast Fourier Transform (FFT) loops. Moreover, in order to provide multiple operations per cycle and low power at the same time, they operate in lower frequencies.

Example companies designing DSP architectures are Texas Instruments, NXP and Freescale.

**Keystone multicore DSP** is one state-of-the-art multicore DSP architecture (see Figure 2.4) [53, 54] <sup>1</sup>. It consists of 8 DSP core packs each one running up to a frequency of 1GHz (see Figure 2.4b). Each DSP pack has a two-layer cache, L1 and L2 with 32KB and 512 KB respectively, and they all share a third one with a size of 4096 KB. Additionally, a memory interface exists for fast access to a DDR3 external memory. A large amount of standard interface is supported, some of the are PCIe2, Ethernet, UART and many more.

Each core has two datapaths with one register file and 4 functional units each (see Figure 2.4a). There are four kinds of functional units, .L and .S which perform general arithmetic and logical operations, .M for multiply operations and finally .D for transactions between the memory and the register file. Each functional unit can perform multiple operations per clock cycle depending on the operands' lengths.

Finally, the *SM320C6678 DSP* based on Keystone architecture has a performance of *16Gflops/32GMACs* per core when cores operate at full frequency, which sums up to a total performance of *128Gflops/256GMACs*.

Figure 2.4: DSP C66x [54] (Courtesy of Texas Instruments®)

### 2.2.3 General-purpose computing on Graphics Processing Unit (GPGPU)

In the beginning of the 21st century an interesting twist took place in the field of Graphics Processing Unit (GPU). These previously graphics dedicated architectures were enhanced with compute capabilities by deploying multiple simple cores. Nowadays, GPGPU is constantly attracting more and more people from both academia and industry.

GPUs are ALU-heavy, which means they contain multiple small and simple cores with compute capabilities and limited control logic. For this reason, suitable GPGPU applications mostly have high arithmetic intensity (arithmetic intensity is defined as the ratio between the number of operations and the data transfers needed for those operations), large input data sets and minimal dependencies between data elements. Evidently, GPUs target data parallel applications.

Furthermore, they have a complex memory-hierarchy which consist of on-chip memories, with multiple cache layers, and off-chip memories.

GPUs are mostly used as accelerators, but integrated graphics solutions also exist. Examples are Intel's new processor designs (Sandy Bridge, Ivy Bridge, Haswell) and ARM's Mali T60x architecture where GPUs and GPPs share the same physical memory space.

Example companies that provide GPUs are NVIDIA, AMD, Intel, ARM, Imagination Technologies and Qualcomm.

### **NVIDIA GK110** is a state-of-the-art NVIDIA Kepler based architecture [50].

*GK110* architecture consists of five Graphics Processor Cluster (GPC), where each containing three "next-generation Streaming Multiprocessors", which are widely known as *SMX* (see Figure 2.5). Most designs utilize 13 or 14 out of the total 15 SMXs, probably to increase yield during manufacturing. Moreover, across the edges there are six 64-bit memory controllers, summing up to a 384-bit path to the off-chip memory.

Each SMX unit accompanies 192 single-precision CUDA cores, 64 double-precision units, 32 special function units and finally 32 load-store units (see Figure 2.6). Four Warp Schedulers and eight Instruction Dispatch units are present, giving the ability to execute eight instructions from four selected warps (each warp contains 32 threads) per clock cycle.

Each SMX comes with a 64 KB on chip memory which can be configured as 16/48 or 48/16 or 32/32 between the L1 cache and the shared memory. One more addition to the GK110 architecture is the 48KB read-only data cache, which targets unaligned access patterns for data that are meant to be read-only during the execution of the program.

In conclusion, *GK110* leads to extreme raw computational power. For example *GeForce GTX Titan* based on *GK110* architecture offers up to *4 TFlops* of raw performance, *288 GB/s* memory bandwidth with a maximum power consumption of *250 W* [49].

Figure 2.5: GK110 architecture [50] (Courtesy of NVIDIA <sup>®</sup>)

Figure 2.6: SMX architecture [50] (Courtesy of NVIDIA <sup>®</sup>)

### 2.2.4 Field-programmable Gate Array (FPGA)

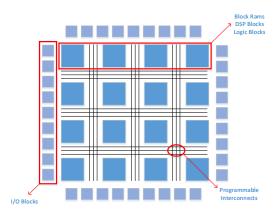

The inherent high performance of hardware based solutions is tempting for everyone. Unfortunately, designing ASIC for every possible application is both time consuming and not flexible. FPGAs are ASICs which consist of a matrix of reconfigurable logic blocks connected with each other with programmable interconnects (see Figure 2.7) [55]. Thus, they can be reprogrammed to facilitate any desired algorithm. Of course, their performance is lower compared to a custom made ASIC solution but this is compensated by the flexibility that they offer through re-programmability. It's important to mention that FPGAs offer high speed I/Os and data buses which make them appropriate for real-time or high volume applications. Xilinx and Altera are the two biggest FPGA providers worldwide.

Figure 2.7: FPGA architecture

### 2.3 Parallel Programming Languages

Nowadays, a variety of parallel programming languages exist, giving everyone the ability to utilise and benefit of the advantages that multicore systems have to offer at a level of abstraction that suits their competency.

We will briefly describe OpenCL and CUDA, the state-of-the-art languages we extensively used, along with OpenMP and MPI which exist for decades now but still have a dominant position.

### 2.3.1 OpenCL

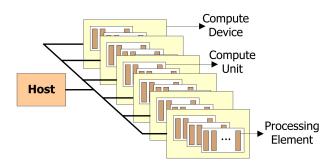

OpenCL is a royalty-free industrial standard designed for programming heterogeneous architectures which consist of collections of Central Processing Units (CPUs), GPUs, DSPs, FPGAs or other hardware accelerators in a single platform [57]. OpenCL was initially an Apple Inc. project, but from 2008 on it is managed by the non-profit Kronos Group which has the immediate support of vendors like Intel, NVIDIA, ARM, AMD and Qualcomm. Each of these providers release their own OpenCL implementation targeted for their own hardware platform.

The OpenCL platform model considers a single host connected to one or more OpenCL Compute Devices. Each Compute Device consists of one or more Com-

pute Units where each Compute Unit is made of one or more Processing Elements. Finally, each Processing Element executes code as SIMD or SPMD.

Figure 2.8: OpenCL Architecture Model (Courtesy of Khronos Group)

An OpenCL program consists of two distinct parts [25], the host and the device code. The device code is actually a kernel, or a collection of kernels, which run on the Compute Devices; they are written in a data/task parallel manner (see Figure 2.8). The host code is responsible for orchestrating the initialization, communication, and execution of the kernels among the Compute Devices.

The data are processed over an index space which can have varying dimensionality from one to three. Each element of this index space is a work-item and a collection of work-items is called work-group. Each work-group is independent of any other one and multiple work-groups can run in parallel. Thus, work-groups should not directly share data. However, work-items of a work-group can communicate and synchronize.

Finally, the OpenCL memory model, which is a relaxed memory model, is divided in four different memory spaces: the global memory, the constant memory, the local memory and the private memory. Each one has its own limitations and regulations concerning consistency between processing elements.

The greatest advantage of OpenCL is the code portability that it offers, but this does not mean that it will run optimally across different OpenCL devices without hardware or vendor specific optimizations [26, 37, 61].

### 2.3.2 CUDA

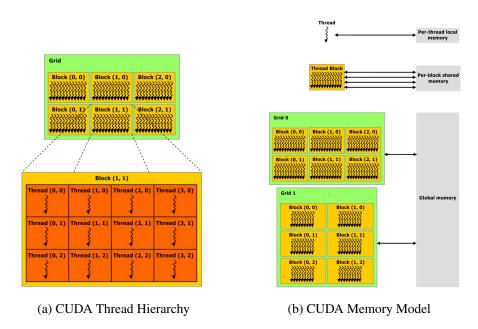

CUDA is the parallel programming model and platform developed by NVIDIA in order to harness the power of the NVIDIA GPUs [56]. The first public version was released in early 2007 while the latest stable version is 5.5 and was released in 2013. CUDA is quite popular in both academia and industry, leading to a variety of compute intensive applications to be ported on GPUs.

CUDA and OpenCL programming models are quite similar. Just like OpenCL, CUDA assumes a single host with one or more CUDA capable devices. The host is responsible for both the communication and synchronisation between the processor

and the CUDA devices, and for the invocation of compute intensive parts also called kernels to be executed on the GPUs. As the host code used to bare all the coordination burden of the application, NVIDIA ultimately tackled this problem by supporting in their new architectures (from Kepler on) a level of autonomous and dynamic parallelism, where a CUDA capable device has the ability to generate work for itself.

CUDA utilizes the GPUs through a hierarchy of threads [25, 69]. Threads are grouped into blocks called threadblocks and threadblocks are further grouped creating what is known as grid. The grid may have dimensionality up to three (see Figure 2.9a).

Two distinct physical address spaces are part of the CUDA memory system, an off-chip DRAM and an on-chip memory. From CUDA's perspective four different spaces are available, the global memory, the constant memory, the local memory and finally the shared memory (see Figure 2.9b).

Overall, CUDA is a major solution when targeting NVIDIA GPUs. CUDA its quite friendly as a language, making the implementation of parallel applications simple for someone that has a clear understanding of the programming model. The implementation of optimised versions may require deep understanding of both the target application and the underlying hardware, and lies on the capabilities of each programmer. Moreover, CUDA comes with a significant number of pre-optimized libraries for different scientific domains, like linear algebra (CUBLAS) and signal processing (CUFFT) which decrease programmer's effort.

Figure 2.9: CUDA Thread and Memory Model

### 2.3.3 OpenMP

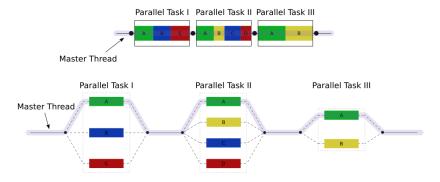

OpenMP is an Application Programming Interface (API) [58] that extends different programming languages in order to express shared memory parallelism. It is a collection of compiler directives, environmental variables and routines that hide the implementation details from the programmers. OpenMP is used to parallelize a sequential application. Although OpenMP can be considered a productive solution due to its abstraction level, parallelizing a legacy or inherently sequential application may limit the performance gain. OpenMP was first released in 1997 for Fortran from the OpenMP Architecture Review Board. Many specification updates have followed this up with the last one being Version 4.0.

In more detail, OpenMP is based on the fork-join [67] parallization model, where a master thread is split in a pre-specified number of work or slave threads which share the tasks among them (see Figure 2.10). Once the threads are forked, they run concurrently or in parallel. Depending on the nature of the parallelized application synchronization or communication between threads may be important for this reason appropriate pragmas exist.

Figure 2.10: OpenMP Example [67] (Courtesy of Wikipedia Commons)

### 2.3.4 MPI

MPI is a parallel programming model that enables the message passing paradigm for programming of parallel applications on distributed machines with separate memory spaces. The MPI specification standard was introduced in 1992 with the release of MPI 1.0 taking place in 1994. The latest version of MPI is MPI 3.0 and was released in 2012 [17]. After so many years, MPI is still the main solution when developing distributed applications. MPI, initially targeted only distributed memory architectures, but as multi-core processors trend took place and were connected over network, hybrid architectures were born. For this reason MPI was extended to support all kinds of memory models including hybrid (distributed and shared). Different implementations of MPI exist (e.g MPICH, LAM-MPI).

A generic MPI program consists of the environment initialization step, where the

communication world between the distributed machines is created, then the parallel execution starts where each machine performs its work and, finally, in the end the MPI environment is terminated [4]. During the parallel work step, machines can communicate using different message passing calls depending on the nature of the needed communication. Different communication types are being supported like broadcast, gather/scatter, reduce.

### 2.4 Real-time Systems

Real-time systems are computing systems that have to react to external stimuli within some timing constraints. As a result, the correctness of such a system is not specified only by the correctness of the calculated output, as in conventional systems, but also by meeting the imposed deadlines [5].

### 2.4.1 What Real-time Means

The term "real-time" is falsely interpreted by many [5]. Some assume a system to be real-time when it produces results really fast, but as the meaning of "time" is relative such is the meaning of "fast".

To characterize a system as real-time we have to have a clear understanding of the environment that it operates in and, as a result, of its timing characteristics. We have to make sure that the system operates in the same time scale with the environment, and guarantee that it will respond fast with respect to the environment's evolution. Sometimes, such systems may be compromised when external, "non-natural", events disrupt the timing characteristics of the environment it operates in.

Many real-time systems have been reported to malfunction due to false modelling of the environment timing characteristics, which may lead to incorrect correlation between the system's "time" and the environment's "time".

### 2.4.2 Types of Real-time Tasks

At conceptual level, a real-time task differs from a non-real-time one on the timing constraints that it has to meet. These constraints come in a form of deadlines. Imposing deadlines to a task introduces the probability of missing one of them as well, which means that the task is unable to produce the required data before the deadline. As a consequence, the criticality of a deadline miss to the system's behaviour helps to distribute real-time tasks in three distinct categories [5]:

Hard: A real-time task is characterised as hard when the miss of a deadline causes catastrophic consequences to the system or the environment. Example of such task is a task that controls an aeroplane's motors and/or sensors, where a deadline miss may lead to a catastrophic result from the control feedback loop.

- **Firm:** A real-time task is characterised as firm when a deadline miss produces useless data for the system but do not damage the system or the environment. Most of the times, a deadline miss in such tasks may lead to quality degradation. Examples of such tasks can be found in the signal processing domain, like video encoding/decoding or video streaming.

- **Soft:** A real-time task is characterised as soft when the data produced after a deadline are still useful but lead to a degradation to the system's performance. Example is a graphic user interface of an application.

### 2.4.3 Features of Real-time Systems

It is important for a real-time system to support six fundamental properties [5] in order to be able to host a critical application. These properties are:

- **Timeliness:** Such a system has to be able to guarantee that all the imposed deadlines are going to be met.

- **Predictability:** It is important for real-time systems to have been developed in a way where extensive analysis schemes can be applied to them, and varying behaviour over different scheduling techniques can be predicted.

- Efficiency: Usually, real-time systems come with not only timing constraints but also with power, area and computational power constraints. Thus, such a system has to operate correctly given all this constraints.

- **Robustness:** Aperiodic events may have a varying pattern depending on the evolution of the environment. Consequently, when event burst occur the response of such a system may be compromised. For this reason, we have to guarantee the correct behaviour in extreme workload cases.

- Fault tolerance: Due to either materials' physical properties and limitations or software errors, faults may introduced to a system. As a consequence, the system should be able to tolerate such permanent or transient faults and continue working in order not to compromise the system's operation.

- Maintainability: The system has to be developed in such a way that possible

extensions and/or modifications can take place without much integration effort.

### 2.5 Synthetic Aperture Radar (SAR)

SAR is a form of radar imaging methodology where a large antenna is emulated by moving a smaller antenna over a specific region. SAR creates finer spatial resolution images than any other conventional beam scanning techniques. SAR technology is usually deployed on satellites, aircraft and more recently also on Unmanned Aerial Vehicles (UAVs).

Figure 2.11: MQ-9 Reaper UAV equipped with SAR (Courtesy of U.S. Air Force)

### 2.5.1 Radar Principles

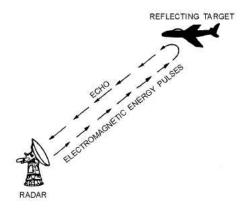

Radar stands for *Radio Detection and Ranging* and is an electrical system the main purpose of which is to detect objects and define their distance [36]. The fact that radar systems operate in almost every weather condition, day and night, makes them a really attractive solution compared to others.

In more detail, radars transmit electromagnetic waves over a target area and receive reflections of these waves from objects that may lie in this area of interest (see Figure 2.12). The angle the electromagnetic waves are received and the time difference between the transmission and reception of these waves reveal information about the position and the range of the objects in this transmission area.

Figure 2.12: Radar Principle

Identifying an object sometimes is not that straight-forward, as multiple sources of both external and internal interference exist. Examples are the noise of the electronic circuitry (e.g. thermal noise) and reflected electromagnetic waves from areas outside the area of interest.

Radars operate in frequencies between 300MHz and 110GHz, and limitations exist in both low and high frequencies. Achieving high resolution in low frequencies require large antennas while high frequencies increase the effect of atmospheric attenuation [36].

The transmitter along with the receiver are the main components of a radar system. The antenna is the part of the system which transfers the electromagnetic waves from/to system to/from the medium. Multiple transmitter/receiver configurations exist. They may share the same antenna (monostatic) or be separated, each one having its own antenna (bistatic). The main reason of bistatic radar systems is to provide physical isolation of the transmitting and the receiving subsystems. This is due to the fact that transmitters usually transmit high-power electromagnetic waves (KW or MW) which may affect the sensitive subsystem of the receiver, which receives signals with orders of magnitude less power (mW or nW).

Two distinct categories of radar waveforms exist: continuous wave and pulsed. In continuous wave waveform, transmitters and receivers operate at all times with the transmitter continuously transmitting a signal. On the other hand, in pulsed waveforms, short signals are being transmitted with a short period, while the receiver receives in between transmissions.

When relative motion between the target and the radar exist, the frequency of the received signal will be different from the frequency of the transmitted one. This commonly known as the Doppler effect. Proper utilisation of the Doppler effect helps to identify moving targets along with their direction and speed.

### 2.5.2 SAR Principles

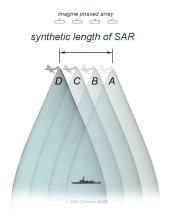

The fundamental premise of a SAR radar is to be able to emulate a rather large antenna, which would require a large amount of power and area, by moving a smaller antenna over a target area. The longer this synthetic antenna is, the higher the spatial resolution we can achieve.

The length of the synthetic antenna is determined by the distance between the start and the end of the data collection process (see Figure 2.13). Finally, by coherently integrating the collected data we can construct high resolution spatial images of the illuminated area.

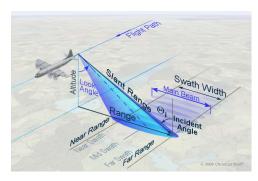

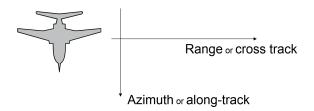

The resolution of a SAR system can be expressed in two terms along two perpendicular axes: the *range resolution* and the *azimuth resolution* (see Figure 2.14).

The range resolution takes place along the range axis which is perpendicular to the antenna moving path. Calculation of range resolution does not differ of that of a conventional radar.

The azimuth resolution is the resolution along the moving track. Multiple observations take place along the track, which in the end are coherently integrated to form high resolution images.

(a) Length of Synthetic Antenna

(b) SAR Geometry

Figure 2.13: SAR Principle [70] (Courtesy of Radartutorial.eu)

Figure 2.14: SAR Resolution

#### **SAR Operation Modes**

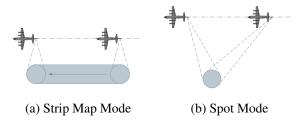

SAR systems support different illumination modes depending on the needs of the application. Figure 2.15 illustrates the most common SAR modes .

In *strip map mode* (see Figure 2.15a) the antenna has a fixed direction resulting in successive high resolution images along the illumination path of the antenna.

On the other hand, in *spot mode* (see Figure 2.15b) the antenna is steered to point to a desired target in the ground which leads to longer integration time and therefore very high resolution images. With digital beam forming, as mentioned later, multiple beams can be formed so that Strip and Spot can be performed simultaneously. This puts heavy demands on the processor.

Figure 2.15: SAR Modes [70] (Courtesy of Radartutorial.eu)

#### **SAR Processing**

As we previously mentioned, the main purpose of a SAR system is to transform the sampled raw data into a spatial image. This image formation procedure consists of multiple processing steps, with the most important being *pulse compression* and *azimuth compression*. Other steps include motion compensation, autofocus and contrast scaling which improve image's focussing and sharpness.

Over the years multiple ways of performing these important SAR processing steps have been proposed. We distinguish three distinct types of SAR processing techniques, each one having different weight distribution between accuracy and performance [34].

- Frequency domain algorithms like Spatial Matched Filter Interpolation, Range-Doppler, ω-K and Chirp Scaling perform both range and azimuth compression in the frequency domain. The utilization of FFTs to do that decreases considerably the required computational time but may lead to defocused images, wrap-around errors or even spread artifacts all over the processed image. This mainly happens because assumptions for the data layout are being made which may lead to formulation problems and approximations especially for wide-angle processing. Further, spatial based processing techniques are sensitive to motion errors, which are most of the times present in airborne SAR.

- Back-Projection is an alternative that offers accurate results in exchange of

higher computation requirements as it operates on the time-domain. BackProjection stems from tomographic imaging, where one-dimensional line

projections taken from a two or three dimensional target scene from different angles, are used to create a spatial image of the target scene. Being a

time-domain approach, makes back-projection able to deal with non-linear

motion paths. Back-Projection was not possible years ago, but has become

feasible thanks to fast computing.

#### **SAR** applications

The ability of radar systems to operate independent of the weather conditions, along with the flexibility and high resolution output of the SAR processing scheme makes SAR have numerous applications from military to environmental based ones [36].

Some example applications are:

- Target Surveillance: Used mainly for military purposes for the surveillance of specific target areas. Surveillance reasons may be treaty preservation between countries.

- Ground Moving Target Indication (GMTI): Moving targets are being monitored. Informations like the direction and the speed of moving targets can be extracted and utilized in a variety of ways.

- Navigation: The ability of radar systems to work in every weather condition, day or night, can be used in navigation systems. Cross-correlation of images with reference images that were previously obtained may reveal location and/or direction information.

- Environmental Monitoring: Environmental changes can be monitored with the use of SAR technology. Such changes may be deforestation, ice level or even oil spills as different materials have different backscatter characteristics

- Foliage and Ground Penetration: Interesting is the fact that low frequency radar system can penetrate foliage and sometimes decades of meters beyond ground surface. Such an important attribute can reveal information about underground targets.

- Interferometry: When two or more SAR images (or data from 2 or more antennas) are combined, generation of 3-D surface images is feasible.

# **Chapter 3**

# **Software Architecture**

# 3.1 Processing Requirements

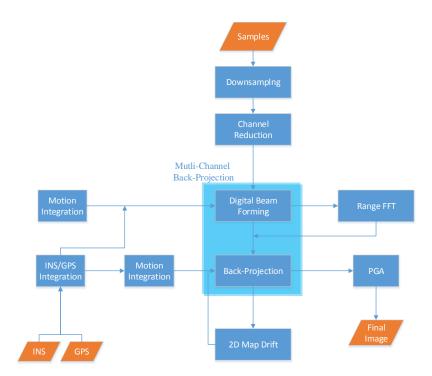

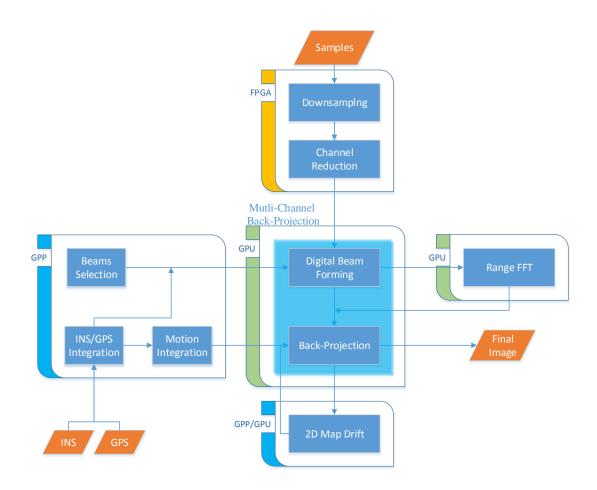

As we mentioned in the previous chapter multiple processing steps are required in order to produce high quality two-dimensional spatial images. Figure 3.1 illustrates the processing chain of a multi-channel SAR[62].

Figure 3.1: SAR Software Architecture

Initially, after the sampling phase a Decimation step takes place. Decimation [33] filters and down-samples the input data in order to reduce the input data rate.

This could be helpful for two main reasons. First of all, the sampling rate may be high enough leading to a high data rate, which may not be able to be supported by the underlying communication interface. Second, the amount of gathered samples may be more than enough to reconstruct high quality images, so a down-sampling step will reduce the processing requirements of the following steps of the chain and still provide high-resolution images.

Having multiple channels in the azimuth direction increases the active sampling rate which leads to higher resolution images or to wider swath width [65]. Channel reduction, tries to reduce the input data rate by adding pairs of channels together. Adding all the channels in this level of the processing chain leads to a conventional SAR configuration with one transmitter and a single channel receiver.

Multi-channel Back-Projection is the heart of the SAR system. It operates over three sampling domains: the channels, the fast time (cross-track) and the slow time (along-track). Back-projection constructs the spatial image of a target area by coherently summing the appropriate reflections of each voxel on the grid. In addition, Digital Beamforming (DBF) [20] helps improve the final image by focusing the receiver in the required direction. Moreover, DBF gives the ability to point different beams in multiple direction, thus multiple images can be constructed. In back-projection we perform explicitly an ultimate form of beamforming by focusing and steering beams to each voxel independently. Range resolution is achieved using FFTs while azimuth resolution by coherent integration along the flight path.

Information about the flight track are obtained through the Inertial Navigation System (INS) and the Ground Positioning System (GPS). By combining these information we can have a clear view about the radar positioning and motion.

Unfortunately, high accuracy INS and GPS systems are expensive and power hungry. Moreover, the accuracy required by a SAR systems strongly depends on the operating frequency of the SAR which for example when is in a magnitude of GHz, millimetre resolution is required by the INS and GPS sensors. In order to compensate potential motion errors multiple steps of iterative autofocus are performed [7]. With *Map Drift*[6] we can compensate large motion error while residual motion errors can be compensated using the *Phase Gradient Algorithm (PGA)* [64].

It is important to mention that this processing chain is just an example. More steps can be added or changed in order to support different functionality or meet specific power or time requirements. An example could be a step for identifying moving targets.

Finally, our main goal is to identify the requirements of each step of the processing chain and investigate possible real-time solutions under area, power and computational power constraints. We will provide this analysis in two phases. First we will discuss each module (Chapters 4-7). Next, we integrate and analyze these modules (Chapter 8).

#### 3.2 Hardware Platforms

A variety of hardware architectures were used to evaluate empirically our SAR implementation.

To start with, Table 3.1 summarizes the specifications of the used GPPs: Intel®  $Core^{TM}$  i7-2670QM[42], Intel®  $Core^{TM}$  i7-3612QM[43] and Intel®  $Core^{TM}$  i7-4960X Extreme Edition[45].

| Model                    | Intel Core<br>i7-2670QM | Intel Core<br>i7-3612QM | Intel Core<br>i7-4960X Extreme |

|--------------------------|-------------------------|-------------------------|--------------------------------|

|                          |                         |                         |                                |

| Cores/Threads            | 4/8                     | 4/8                     | 6/12                           |

| Core Frequency (GHz)     | 2.2                     | 2.1                     | 3.6                            |

| Last Level Cache (MB)    | 6                       | 6                       | 15                             |

| Throughput (GFlops)      | 70.4                    | 67.2                    | 130                            |

| Memory Bandwidth (GB/s)  | 21.3                    | 25.6                    | 59.7                           |

| Memory Channels          | 2                       | 2                       | 4                              |

| Thermal Design Power (W) | 45                      | 35                      | 130                            |

Table 3.1: GPPs' Specifications

Further, multiple GPUs were used: a mobile GPU, NVIDIA® GeForce<sup>TM</sup> GT540M[48], a mid-range GPU, NVIDIA® GeForce<sup>TM</sup> GTX650 Ti[48] and finally two highend GPUs, NVIDIA® Tesla<sup>TM</sup> K20[52] and NVIDIA® GeForce<sup>TM</sup> GTX Titan[49]. Table 3.2 presents the most important specifications of the previously mentioned architectures.

| Model                    | NVIDIA | NVIDIA  | NVIDIA    |

|--------------------------|--------|---------|-----------|

| Model                    | GT540M | GTX680  | GTX Titan |

| Cores/Threads            | 2/96   | 32/1536 | 14/2688   |

| Core Frequency (Hz)      | 1344   | 1006    | 837       |

| Off-chip Memory (GB)     | 1      | 2       | 6         |

| Throughput (GFlops)      | 258    | 3090    | 4500      |

| Memory Bandwidth (GB/s)  | 28.8   | 192     | 288       |

| Memory Frequency (Hz)    | 900    | 6000    | 6000      |

| Memory Interface         | GDDR3  | GDDR5   | GDDR5     |

| Memory Width (bits)      | 128    | 256     | 384       |

| Compute Capability       | 2.1    | 3       | 3.5       |

| Thermal Design Power (W) | 35     | 195     | 250       |

Table 3.2: GPUs' Specifications

The experimental data that we used come from AMBER [60], a *X-band Digital Array SAR* which targets UAVs. AMBER has a maximum bandwidth of 1 GHz and thus a maximum resolution of 15 cm. Moreover, it is equipped with a 24 element receiver array with a sampling frequency of 20 MHz.

#### 3.3 Metrics

Throughout this thesis multiple implementations of the all the algorithms will be presented. In order to compare those and be able to evaluate their performance on different hardware platforms we use the following metrics:

- Execution Time (T) is the main decisive metric when comparing different implementations. The execution time is obtained using the *wall timer* or using profiling tools like *NVIDIA's nvprof* [51] and *Intel's VTune Amplifier* [44].

- **Speedup** (S) represents the absolute performance gain between two different implementations with execution times  $T_1$  and  $T_2$  respectively:

$$S = \frac{T_1}{T_2} \tag{3.1}$$

#### • Throughput

Computational Throughput, is a measure of the amount of work that a computational system can perform in a given time period, and is calculated as the number of floating point operations that are being performed per second:

$$FLOPS = \frac{FLOPs_{total}}{T}$$

(3.2)

Memory Bandwidth, is a measure of the rate that data can be stored and read from a memory subsystem, and is calculated as the number of bytes transferred through memory transactions from and to the main memory (read and writes) per second:

$$MBw = \frac{bytes_{read} + bytes_{written}}{T}$$

(3.3)

• Back-projections per second (BPs), the number of back-projections that can be performed per second:

$$BPs = \frac{Back - projections_{total}}{T}$$

(3.4)

# **Chapter 4**

# **Multi-channel Back-Projection**

## 4.1 Algorithm

Back-Projection is one of the most used processing techniques in SAR systems. We focus on the time-domain "brute-force" approach presented in [63].

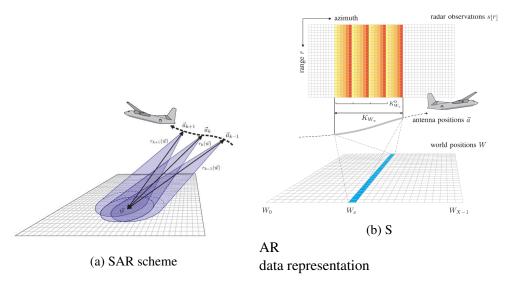

Along a flight path each radar observation s[r] is associated with a three-dimensional antenna position  $\vec{a_k}$ . Each radar observation is a collection of range compressed, complex data indexed by range r (see Figure 4.1b).

Figure 4.1: SAR back-projection

Range can be specified by calculating *the euclidean distance* between the position of the voxel  $\vec{w}$  where we need to measure the radar reflectivity and the k-th position of the antenna  $\vec{a_k}$  (see Figure 4.1a).

$$r_n(\vec{w}) = |\vec{w} - \vec{a_k}| \tag{4.1}$$

Having calculated the range between these two points, we can calculate the oneway phase shift  $\phi_k(\vec{w})$  and consequently the two-way phasor  $\theta_k(\vec{w})$ .

$$\phi_k(\vec{w}) = 2\pi \frac{r_k(\vec{w})}{\lambda}$$

$$\theta_k(\vec{w}) = e^{2j\phi_k(\vec{w})}$$

(4.2)

$$(4.3)$$

$$\theta_k(\vec{w}) = e^{2j\phi_k(\vec{w})} \tag{4.3}$$

where  $\lambda$  is the wavelength of the transmitted wave.

Further, the partial reflectivity of this voxel from a single observation can be reconstructed as follows:

$$u_k \left[ \vec{w} \right] = s_k \left[ r_k(\vec{w}) \right] \cdot \theta'_k(\vec{w}) \tag{4.4}$$

Finally, the total reflectivity of a voxel can be calculated by coherently summing all the partial contributions to the voxel's reflectivity from all the relevant radar observation.

$$u_k\left[\vec{w}\right] = \sum_{k \in K_{\vec{w}}} u_k\left[\vec{w}\right] \tag{4.5}$$

Clearly, in order to compute the reflectivity of a collection of voxels representing the grid of interest, this procedure has to be performed for each voxel independently, leading to high computational demands for high resolution wide grids.

For multi-channel receive antennas the number of radar observations is increased by a factor equal to the number of the receive channels. To be more specific, for mchannels, the total reflectivity of a voxel is:

$$u_k\left[\vec{w}\right] = \sum_{k \in K_{\vec{w}}} \sum_{m} u_{k,m}\left[\vec{w}\right] \tag{4.6}$$

#### 4.2 **Sequential Implementation**

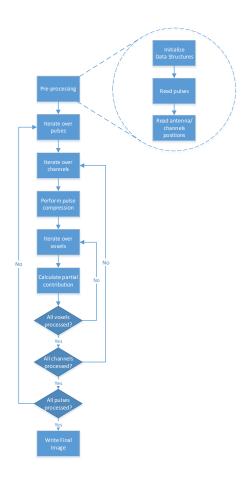

Initially, we implemented a sequential version of the multi-channel back-projection to reveal any computational bottlenecks and identify potential candidates for parallelization.

Figure 4.2 illustrates the processing steps of the presented algorithm. In the initialization step, the required data structures are initialized and the observations along with the position of the antenna are read. Having the antenna positions helps us calculate the position of each channel respectively.

Next, the main processing routine follows, where for each pulse and for each channel we calculate the reflectivity of each voxel in the target grid.

Overall, the whole process to calculate each voxel's reflectivity is an independent summation over three distinct domains: fast-time (across range), slow-time(across

track) and channels. As time-domain processing in the fast-time domain (across-range) lead to no significant improvements in output's quality, frequency-domain processing is preferred (Range Compression box). The order these summations occur does not change the final result.

Figure 4.2: Data flow diagram

**Profiling** this application will help measure the execution time of each individual part along with its contribution to the overall execution time of the program. We reconstructed voxel grids of varying sizes by integrating over 5 seconds of samples which is approximately 1506 sweeps.

Table 4.1 presents the execution time of the most important functions along with their contribution to the total execution. As we can see, the contribution calculation function and the range compression account together for the most part of the total time. When reconstructing voxel grids of larger sizes, we observe that the execution time of the contribution function is increasing while range compression

remains constant.

Evidently, we conclude that the contribution function along with the range compression one are the two main processing steps that urge parallelization as they account for approximately the 95% of the total execution time.

| Size      | Functions     | T[s] | %  |

|-----------|---------------|------|----|

|           | contribution  | 1276 | 74 |

| 100mx100m | rangeCompress | 301  | 17 |

|           | others        | 154  | 9  |

| 200mx200m | contribution  | 5320 | 92 |

|           | rangeCompress | 304  | 5  |

|           | others        | 162  | 3  |

Table 4.1: Profiler Results on GPP (single-threaded)

### 4.3 Parallel Approaches

Typically, applications use either input-based parallelization or output-based parallelization.

In input-based parallelization, the input elements are processed concurrently or in parallel. This can be advantageous when the number of the input elements is significantly larger than the output elements, but on the other hand can also lead to synchronization problems when multiple input items affect the same output element.

In output-based parallelization, the output elements are processed in parallel. While this can lead to redundant reads of input elements, and less parallelism in case the output is much smaller than the input, it resolves the synchronization problem.

Below we describe how these approaches can be applied to the given backprojection algorithm along with arguments of which one is friendly for a GPU implementation.

#### 4.3.1 Input-based parallelization

In this parallelization approach, each thread takes care of one or several input element(s). Thus, our main goal is to calculate which output voxels this input element/s affects and, as a result, coherently add its contribution to these voxels.

The number of elements of the input data is orders of magnitude larger than the output elements, a factor suitable for a gpu-level parallelism. Moreover, threads will read consecutive memory elements (coalesced accesses) which will lead to better utilisation of the memory hierarchy.

In order to follow this approach, each input element has to iterate over all the output elements and check which ones it affects. In [10] the authors mathematically

prove that the voxels that have to be checked can be limited to a certain amount, but still depending on the size of the grid and radar specific parameters their number could vary. Moreover, iterating over output elements may lead to a computational explosion and also increases dramatically the lifetime of each individual thread. Another way is to use a mathematical way to specify, with an acceptable accuracy, the elements that each input item affects. This may of course introduce more complex control logic and highly depends on many radar and sampling specific factors which are explained further during the data analysis step. Finally, due to the fact that multiple threads may access similar output voxels, atomic access to the output voxels is required.

#### 4.3.2 Output-based parallelization

The output-based parallelization can be implemented by making each individual parallel task responsible for calculating the contribution to a specific voxel of the output voxel grid. Such an approach may initially imply a lower level of parallelism as the number of the voxels is orders of magnitude less than the input data, but in reality the computational part is much more parallel-efficient and straightforward.

The main problem of this approach is that, as mentioned in the algorithm presentation, for each voxel we have to calculate the distance from the antenna for each aperture. Depending on this distance we have to access the appropriate range bin. These accesses to the corresponding range bins for the voxels may not be consecutive between voxels which may lead to lower utilization of the memory hierarchy or restrictions for further optimisations. Further analysis on the access patterns take place later in this chapter.

We chose to proceed with this approach as it turns out to be more parallel efficient and has less drawbacks and limitations compared to the input-based approach.

## 4.4 Analysis

Before proceeding to the parallelization process is important to have a deep understanding of the computational and memory requirements of the algorithm.

We start with a basic setup where we assume a single antenna consisting of  ${\cal M}$  channels in the azimuth direction and a Frequency-Modulated Continuous-Wave (FMCW) radar.

#### 4.4.1 Complexity Analysis

#### Input

In SAR processing, an image is reconstructed using a start-stop approximation, where a synthetic aperture is created consisting of multiple individual radar observations. The number of the individual apertures, P, depends on the start and stop

time of the integration process and the Signal Repetition Frequency (SRF), which is the frequency a pulse is transmitted (see Equation 4.7).

$$P = |t_{start} - t_{ston}| \cdot SRF \tag{4.7}$$

During consecutive apertures there are M channels sampling over the fast-time domain. The number of the collected samples across range per channel, R, depends on the hardware's sampling frequency  $(f_{sample})$  and the upsweep's time  $(T_{upsweep})$  (see Equation 4.8)

$$R = f_{sample} \cdot T_{upsweep} \tag{4.8}$$

For back-projection to achieve better resolution, an *interpolation* or *upsampling* takes place in the fast-time domain. This leads to an increased number of range bins,  $\tilde{R}$ , and depends on the upsampling factor  $(n_{upsample})$  (see Equation 4.9).

$$\tilde{R} = R \cdot n_{upsample} \tag{4.9}$$

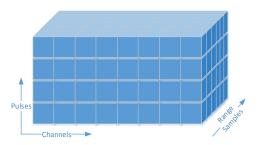

Figure 4.3 illustrates the structure of the observations in the three distinct domains.

Figure 4.3: Data Layout

As a result, the number of input observations equals to the number of apertures, times the number of channels, times the number of observation of each channel at each aperture:

$$input = obs = P \cdot M \cdot \tilde{R}$$

(4.10)

#### Output

The number of the output voxels in each dimension depends on the size of this dimension and the resolution we want to achieve in this dimension (see Equation 4.11).

$$N_d = \frac{Size_d}{res_d} \tag{4.11}$$

where  $Size_d$  is the length of the voxel grid in this dimension in meters and  $res_d$  is the resolution in this dimension.

The total number of voxels or output out is the product of the voxels in each dimension (see Equation 4.12).

$$out = N_{total} = \prod_{i}^{d} N_{i}$$

(4.12)

Overall, the complexity of the algorithm is  $O(PM(N_xN_y+(\tilde{R}log_2\tilde{R})))$ . This comes from the fact that for every pulse P and for every channel M we perform range compression over the interpolated range  $\tilde{R}$  samples using FFTs<sup>1</sup> and we calculate the contribution for each pixel (where  $N_xN_y$  is the total amount of pixels of a 2D voxel grid). Dominating factors are the number of channels, the number of pulses and the number of voxels.

#### 4.4.2 Operational Intensity Calculation

It is important to calculate the needs of our application in terms of computational intensity and memory bandwidth. This will provide us insight in our application's bounds and will guide our optimization strategy.

First of all, we focus on the contribution function requirements. Let's assume we operate on range compressed data. Moreover, we do not account the requirements for the pre-processing step as they are negligible compared to the main processing procedure.