#### Modular High Voltage Pulse Converter for Short Rise and Decay Times

Mao, Saijun

10.4233/uuid:0cd2c394-adc0-490d-9f4e-ba611d3f14c2

**Publication date**

**Document Version** Final published version

Citation (APA)

Mao, S. (2018). Modular High Voltage Pulse Converter for Short Rise and Decay Times. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:0cd2c394-adc0-490d-9f4e-ba611d3f14c2

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# Modular High Voltage Pulse Converter for Short Rise and Decay Times

Saijun Mao

毛赛君

# Modular High Voltage Pulse Converter for Short Rise and Decay Times

#### **Proefschrift**

ter verkrijging van de graad van doctor

aan de Technische Universiteit Delft,

op gezag van de Rector Magnificus Prof.dr.ir. T.H.J.J. van der Hagen;

voorzitter van het College voor Promoties,

in het openbaar te verdedigen op

dinsdag 30 januari 2018 om 15:00 uur

Door

Saijun MAO

Master of Engineering, Power Electronics, Nanjing University of Aeronautics and Astronautics, China

geboren te Jiangsu, China

This dissertation has been approved by the:

Promotor: Prof. dr. J. A. Ferreira

Copromotor: Dr. J. Popovic

#### Composition of the doctoral committee:

Rector Magnificus, Chairman

Prof. dr. J. A. Ferreira, Delft University of Technology, promotor

Dr. J. Popovic, Delft University of Technology, copromotor

#### Independent members:

Prof. dr. R. Ross, Delft University of Technology

Prof. dr. L. Empringham, University of Nottingham, England

Prof. dr. J. Böcker, Paderborn University, Germany

Prof. dr. G.Q. Zhang, Delft University of Technology

To my family

### Acknowledgements

The research presented in this thesis was performed in the Department of Electrical Sustainable Energy at Delft University of Technology (TU Delft). Many people have been involved in my Ph.D. research and this thesis would not be completed without their valuable company, help, encouragement, and support. I would like to take this opportunity to express my gratitude and appreciation to them.

First of all, I would like to thank my promotor Professor Braham Ferreira, for giving me the opportunity to pursue my Ph.D. degree. It is my great honor and fortune to have him as my promoter. His insightful guidance, broad horizon, brilliant ideas, profound knowledge support and encourage me to be able to continue and finish my Ph.D.

I would like to thank my co-promotor and daily supervisor Dr. Jelena Popovic for her continuous guidance and support. I learned a lot from her about research methodology, and critical thinking. I am very grateful for all the time and efforts she spent for providing great suggestions and comments for my papers and thesis chapters.

Thanks to staff members in the EPP group, Professor Paul Bauer, Dr. Zian Qin and Dr. Jianning Dong, for sharing their support and help. I would like to acknowledge Bart Roodenburg for his efforts on my Ph.D. thesis summary and propositions translation from English to Dutch.

I would like to acknowledge my doctoral examination committee, Professor R. Ross, Professor L. Empringham, Professor J. Böcker and Professor G.Q. Zhang for the valuable time they spent on reading my draft thesis and giving valuable comments and suggestions.

I am grateful for the Ph.D. colleagues in our research group. Thanks to all the colleagues for their help, accompany and sharing of knowledge. I would also like to thank Wenbo Wang, Liu Dong, Xuezhou Wang, Ilija Pecelj, Udai Shipurkar, Malden Gagic, Nils van der Blij, Tianzhu Tang, Fengze Hou, Donghao Wu. I would like to express my appreciation to group secretaries Sharmila Rattansingh and Ellen Schwencke-Karlas for helping me with all kinds of matters.

I would like to express my acknowledgement for GE Global Research Center to sponsor my Ph.D. study and and provide an excellent research environment. I would like to thank all the collesgues in GE Global Research Center for their support and help. Special thanks to Jie Shen, Zhihui Yuan, Xu Chu, Pengcheng Zhu, Pengju Kang, Yu Zhang, Asokan T. for their great help.

In particular, I would like to thank Professor Wuhua Li for his great support and help. I would like to acknowledge Chengmin Li and Yu Chen for their help and assistance of my experiments.

Last but not least, I would like to thank my family: my parents Heqin Yao and Guoping Mao, my parents-in-law Ruiyin Gu and Zhihua Zhu, for their great support and encouragement. I would like to thank especially my beloved wife, Ying Zhu. Thanks a lot for her understanding, support and sacrifice in so many weekends that I have to spend on my thesis. Thanks to my son, Yanzhen Mao, for bringing so much happiness to my life.

### **Abbreviations and symbols**

3D Three dimensional

AC Alternating current

$A_e$  Effective core area

AP Area product

$B_{max}$  Maximum flux density

C Capacitance

$C_{eq}$  Equivalent capacitance of the HV transformer loaded by the rectifier

$C_{eq}$  Equivalent capacitor of the sub-divided cell

$C_p$  Parallel resonant capacitance

$C_p'$  Parallel capacitor of the sub-divided cell

$C_r$  Resonant capacitor

$C_{\text{rec}}$  Capacitor of rectifier or voltage multiplier

$C_{tot}$  Total capacitance of the equivalent RC network

$C_{w,p}$  Capacitance of the transformer primary winding

$C_{w,s}$  Capacitance of the transformer secondary winding

$C_{\rm wp}$  Parasitic winding capacitance of the HV transformer

$C_{vm}$  Capacitance for the voltage multiplier

CCM Continuous conduction mode

CT Computed Tomography

CW Cockcroft-Walton

Duty cycle

DC Direct current

ESP Electrostatic precipitation

$f_s/\omega_s$  Frequency/Angular frequency of the resonant tank input voltage

$f_{\min}$  Minim frequency

FHA First Harmonic Approximation

$F_r$  Ratio of ac resistance to dc resistance of transformer windings

FW Full-wave

$G_{\theta}$  Product of  $\omega_s$ ,  $C_{tot}$ ,  $R_{eq}$

GaN Gallium nitride

GND Ground

*h* Height of the transformer windings

H Gain of the LCC resonant converter

HV High voltage

HW Half-wave

$I_{\text{crec-rms}}$  RMS value of the AC current flowing through the capacitor of the rectifier

or multiplier

$I_{\rm d\ Fav}$  Average current flowing through the diode

$I_{d\_Fav}$  RMS current flowing through the diode

*I<sub>rm</sub>* Maximum resonant current

$i_r(t)$  Instantaneous resonant current

$i_s$  Instantaneous current of the transformer secondary side

*I*<sub>o</sub> Output current

$I_{\rm p}$  RMS value of the transformer primary current

$I_{\rm s}$  RMS value of transformer secondary current

$I_{s,avg}$  Average current of the transformer secondary side

$I_{s,RMS}$  Root Mean Square (RMS) current of the transformer secondary side

*I<sub>in.RMS</sub>* Input RMS current

IGBT Insulated gate bipolar transistor

$J_w$  Current density

k Turns ratio of the high voltage transformer

$k_c$  Coefficients between  $C_p$  and  $C_{eq}$

$k_{core}$  Coefficients of magnetic core material

$k_i$  Coefficients of the Fourier transformation of the parallel capacitor current

$k_{VM}$  Voltage gain of the rectifier

$k_v$  Coefficients of the Fourier transformation of the parallel capacitor voltage

$K_u$  Core geometry factor

$K_w$  Window utilization factor

kV kilovolt

$L_m$  Magnetizing inductance

$L_r$  Resonant inductance

$L_{lk}$  Leakage inductance of the HV transformer

$L_{plk}$  Primary side leakage inductance of the HV transformer

$L_{slk}$  Secondary side leakage inductance of the HV transformer

$L_{r\_tot}$  Total resonant inductance of the resonant tank

LCC Series parallel

*m* Number of elemental HV transformers

mA Milliampere

MOSFET Metal oxide semiconductor field-effect transistor

*n* Stage number for the voltage multiplier

$n_1$  Turns number of the HV transformer primary winding

$n_2$  Turns number of the HV transformer secondary winding

P Polarities of the voltage multiplier

$P_{core}$  Magnetic core loss

$P_{cap\_rec}$  Power loss of the capacitors in the rectifier or multiplier circuit

$P_{diode\_rec}$  Power loss of the diode in the rectifier or multiplier circuit

$P_{diode\_rec\_con}$  Conduction power loss of the diode in the rectifier or multiplier circuit

$P_{diode\_rec\_rr}$  Switching power loss of the diode in the rectifier or multiplier circuit

$P_{HV tank}$  Total loss of the HV tank

*P<sub>o</sub>* Output power

$P_{winding\_con}$  Transformer winding conduction loss

$P_{winding\_die}$  Dielectric loss of winding in the HV transformer

$P_{winding}$  Total transformer winding loss

PCB Printed circuit board

*PF* Power factor of the resonant tank

PWM Pulse-wide-modulation

PRC Parallel resonant converter

Q Quality factor of the resonant tank

$Q_o$  Charge flowing through diodes

$Q_{rr}$  Reverse recovery charge

$R_{AC}$  AC resistance of the winding

$R_{DC}$  DC resistance of the winding

$R_{eq}$  Equivalent resistance of the high voltage transformer loaded by the rectifier

$R_{eq}$  Equivalent resistor of the sub-divided cell

$R_o$  Output resistor

$R_o'$  Output resistor of the sub-divided cell

$R_p$  Resistance of the transformer primary winding

$R_s$  Resistance of the transformer secondary winding

$R_{pw\_AC}$  AC resistance for the transformer primary winding,

$R_{\text{sw\_AC}}$  AC resistance for the transformer secondary winding

RMS Root mean square

SF6 Sulfur fluoride

Si Silicon

SiC Silicon carbide

SRC Series resonant converter

*t* Time

$t_r$  Rise times of the HV pulse

*t<sub>f</sub>* Decay times of the HV pulse

TR Transformer rectifier sets

UPS Uninterruptible power supply

$V_{\text{CWP}}$  Voltage applied to parasitic winding capacitance

$v_p$  Instantaneous voltage across the parallel capacitor

$V_{HV-tank\_elementary}$  Output voltage for the each elemental HV tank

*V<sub>HV-tank\_posotive\_total</sub>* Total output voltage for the positive polarity HV tank

$V_{HV-tank\_negtive\_total}$  Total output voltage for the negative polarity HV tank

$V_{in}$  Input DC voltage

$V_{\rm core}$  Volume of the magnetic core

$V_{Cr}$  Maximum voltage across the resonant capacitor

$V_{cp,max}$  Maximum voltage of the parallel capacitor

$V_o$  Output voltage

$V_{\rm r}$  Reverse voltage of the diode

$V_{sec}$  Voltage of transformer secondary winding

$V_{tr\_AC\_insulation}$  AC insulation stress for the HV transformer

$V_{tr\_DC\_insulation}$  DC insulation stress of the HV transformer

$V_{tr\_s}$  Secondary voltage of the HV transformer

$V_{tr\_s\_pk}$  Peak AC voltage of elemental HV transformer secondary winding

VF Voltage frequency

ZCS Zero-current switching

ZVS Zero-voltage switching

Z<sub>in</sub> Resonant tank input impedance

$\delta$  Skin depth

$\varepsilon$  Permittivity

$\varepsilon_r$  Relative permittivity

$\varepsilon_o$  Permittivity in vacuum

$\lambda$  Wavelength

*μ* Permeability

$\mu_r$  Relative permeability

Permeability in vacuum  $\mu_o$ Magnetic flux φ  $\theta$ Conduction angle Efficiency of the HV pulse converter η Phase lag between inverter output voltage and resonant current Ψ Conductor resistivity ρ Normalized conductor height related to skin depth Dissipation factor of the insulation materials  $tan\delta$ Magnetic flux density  $\Delta B$

### **Table of Contents**

| Chapter 1                                                             | 1  |

|-----------------------------------------------------------------------|----|

| Introduction                                                          | 1  |

| 1.1 Background                                                        | 1  |

| 1.1.1 Overview of HV pulse converters                                 | 1  |

| 1.1.2 HV pulse converters in CT and X-ray machine applications        | 2  |

| 1.1.3 HV pulse converters in electrostatic precipitator applications  | 4  |

| 1.1.4 Research needs for HV pulse converter performance improvement   | 7  |

| 1.2 Research questions                                                | 11 |

| 1.3 Approach                                                          | 12 |

| 1.4 Thesis layout                                                     | 12 |

| 1.5 References                                                        | 14 |

| Chapter 2                                                             | 17 |

| Overview of the state-of-art HV pulse converter technologies          | 17 |

| 2.1 Introduction                                                      | 17 |

| 2.2 HV pulse converters architectures                                 | 17 |

| 2.2.1 Architectures with single power building block sub-component    | 18 |

| 2.2.2 Architectures with multiple power building block sub-components | 19 |

| 2.3 Topologies, modeling and control                                  | 20 |

| 2.3.1 Topologies for the HV pulse converter                           |    |

| 2.3.2 Modeling and Control                                            |    |

| 2.4 HV transformers                                                   |    |

| 2.4.1 Transformer structures                                          |    |

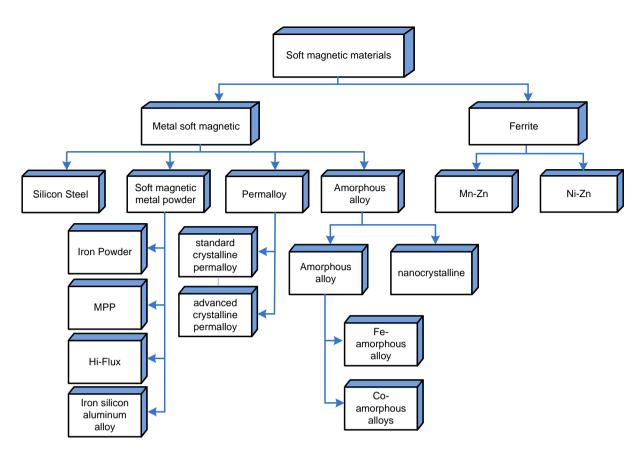

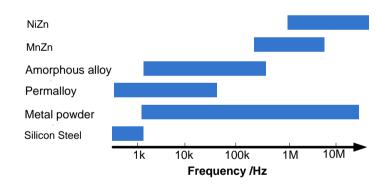

| 2.4.2 Magnetic core materials                                         |    |

| 2.4.3 Insulation materials                                            |    |

| 2.4.4 Equivalent circuit model                                        |    |

| 2.4.5 Design procedure of the HV transformer                          |    |

| 2.5 HV rectifiers                                                     |    |

| 2.5.1 Topologies                                                      |    |

| 2.5.2 Characteristics of a voltage multiplier                         |    |

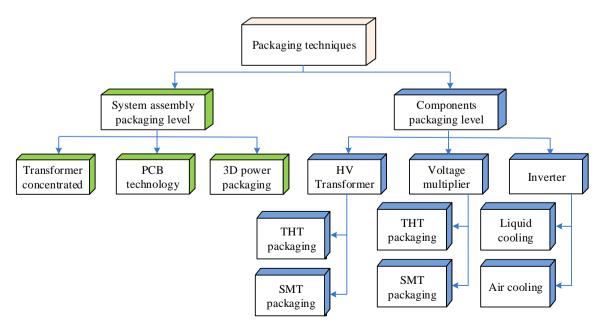

| 2.6 Packaging                                                         |    |

| 2.6.1 Packaging technology for the HV pulse converter                 |    |

| 2.6.2 Components packaging level                                      | 31 |

| 2.6.3 Assembly packaging level                                                  | 32          |

|---------------------------------------------------------------------------------|-------------|

| 2.6.4 Cooling                                                                   | 33          |

| 2. 7 Summary                                                                    | 36          |

| 2.8 References                                                                  | 37          |

| Chapter 3                                                                       | 45          |

| HV pulse converter architectures evaluation and comparison                      | 45          |

| 3.1 Introduction                                                                | 45          |

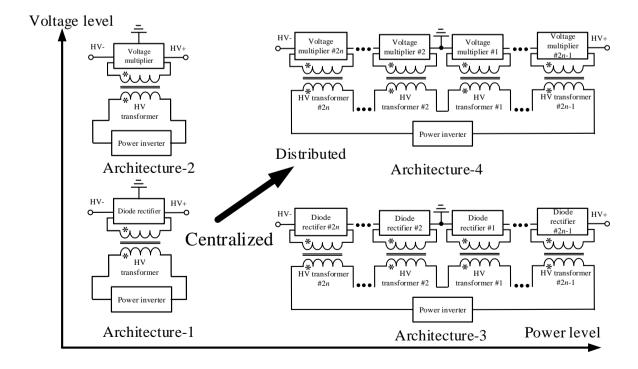

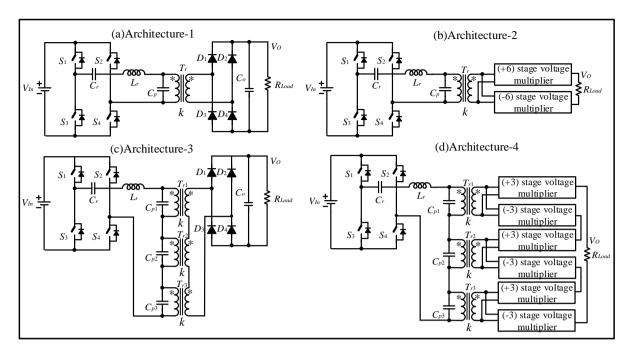

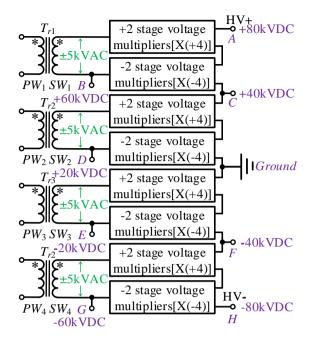

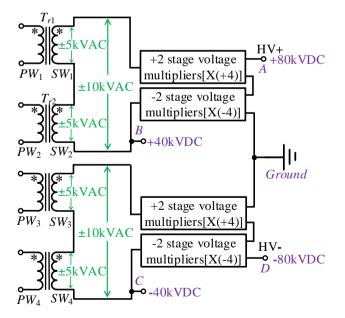

| 3.2 HV pulse converter architectures derivation and classifications             | 46          |

| 3.2.1 HV pulse converter architectures derivation methodology                   | 46          |

| 3.2.2 HV pulse converter architectures classifications                          | 47          |

| 3.2.3 Discussions                                                               | 53          |

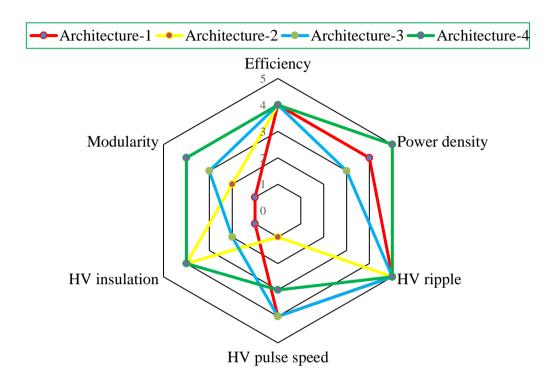

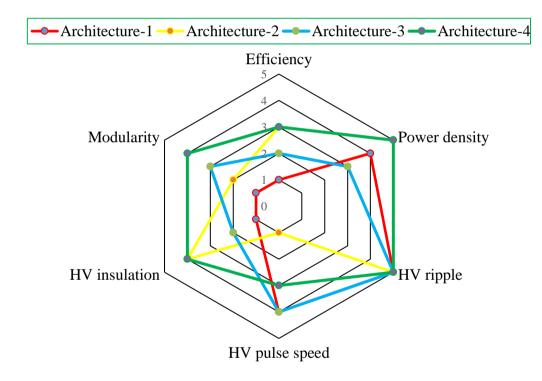

| 3.3 Evaluation of HV pulse converter architectures                              | 54          |

| 3.3.1 Performance requirements                                                  | 54          |

| 3.3.2 Evaluation specifications                                                 | 58          |

| 3.3.3 Evaluation assumptions                                                    | 58          |

| 3.3.4 Evaluation criteria                                                       | 59          |

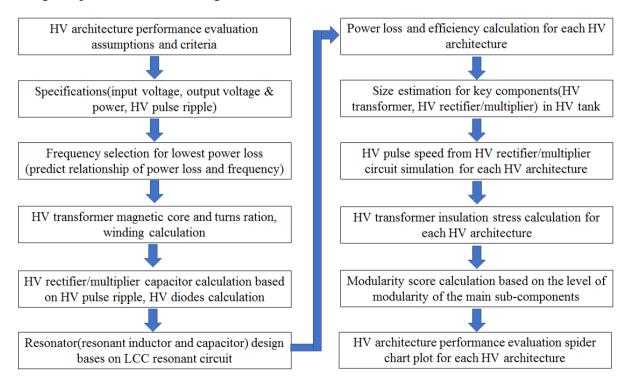

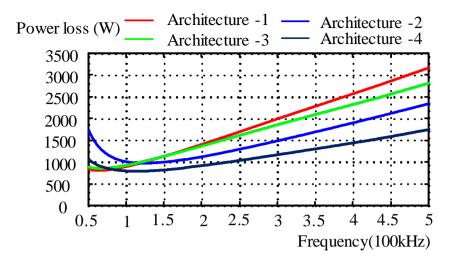

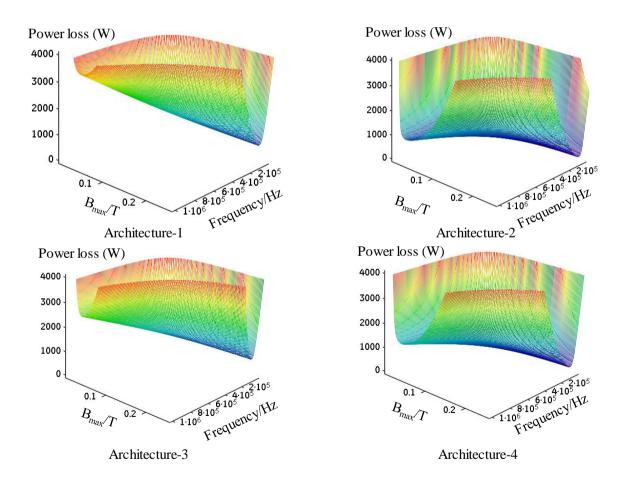

| 3.3.5 Evaluation methodology and first-order evaluation flow chart              | 60          |

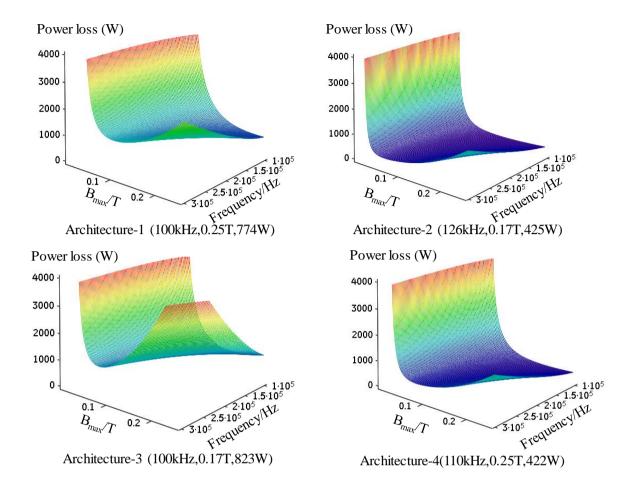

| 3.3.6 Evaluation results                                                        | 65          |

| 3.3.7 Discussions                                                               | 72          |

| 3.4 Summary                                                                     | 73          |

| 3.5 References                                                                  | 74          |

| Chapter 4                                                                       | 81          |

| Analysis of the HV transformer for the modular high frequency HV pulse con-     | verter81    |

| 4.1 Introduction                                                                | 81          |

| 4.2 The modularization of the HV transformer                                    | 81          |

| 4.2.1 The advantage of the modularization of the HV transformer                 | 81          |

| 4.2.2 Interconnection of the modular HV transformers and the converter          | 83          |

| 4.2.3 Equivalent circuit                                                        | 86          |

| 4.2.4 Challenges of the modularization of the HV transformer                    | 90          |

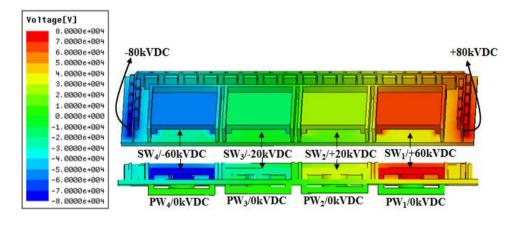

| 4.3 Packaging and insulation of the HV transformer                              | 90          |

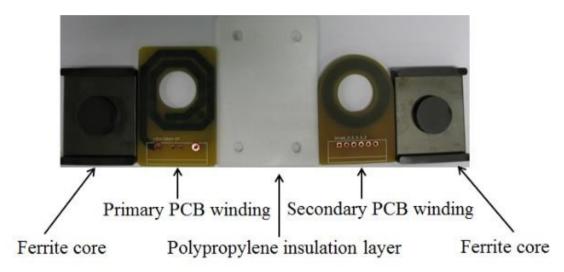

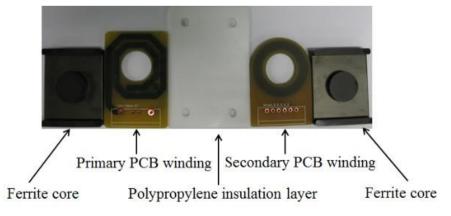

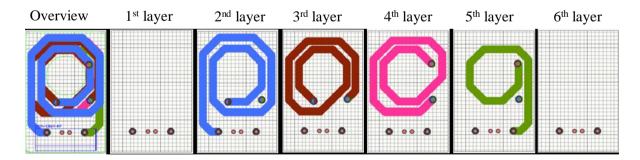

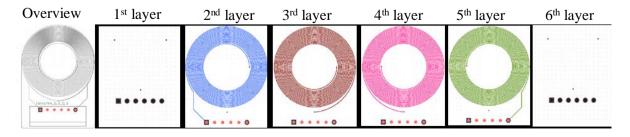

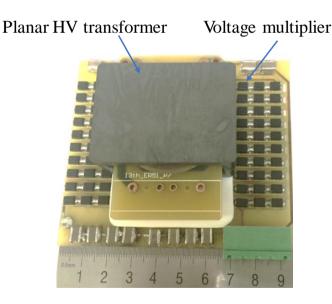

| 4.3.1 Planar HV transformer structure                                           | 90          |

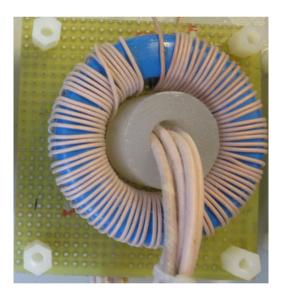

| 4.3.2 Wire-wound HV transformer structure                                       | 93          |

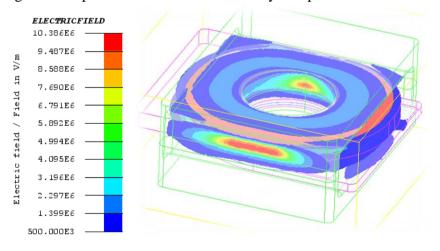

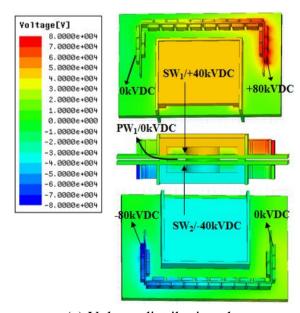

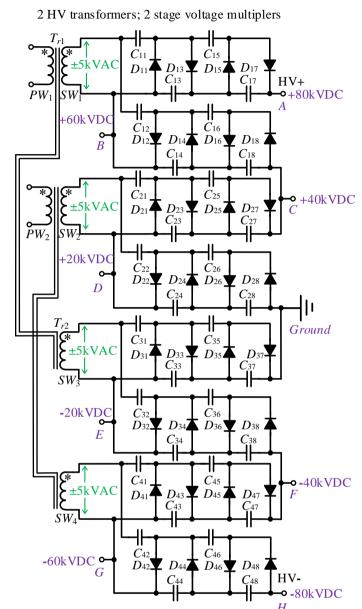

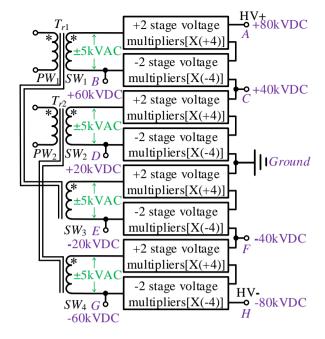

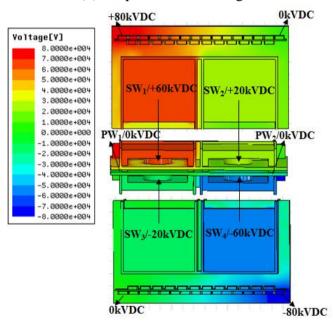

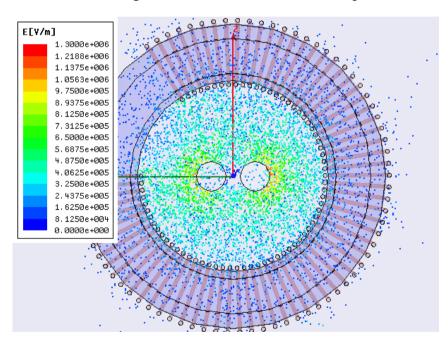

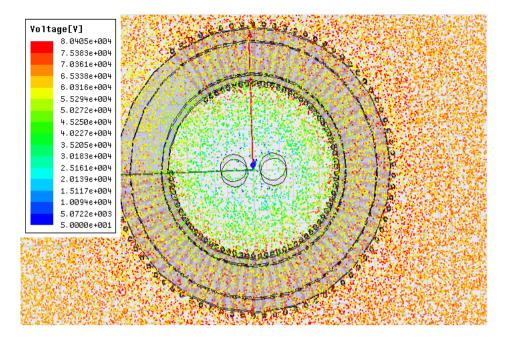

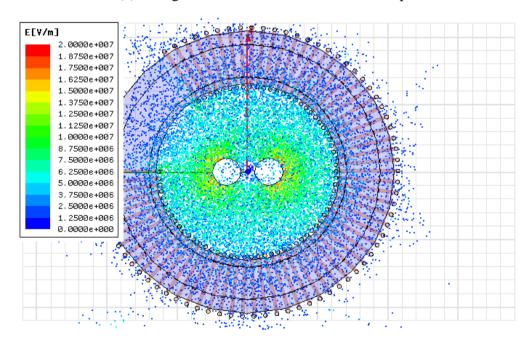

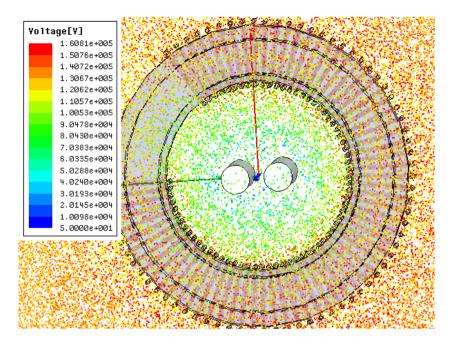

| 4.3.3 Insulation stress analysis of the HV transformer for the modular HV pulse | e converter |

|                                                                                 | 96          |

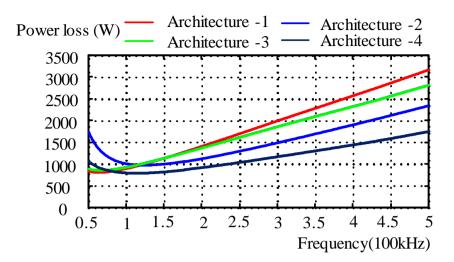

| 4.4 The influence of increasing switching frequency on a modular HV transformer        | 115   |

|----------------------------------------------------------------------------------------|-------|

| 4.4.1 The advantages of increasing switching frequency                                 | 115   |

| 4.4.2 The challenges of increasing the switching frequency for the HV transformer.     | 118   |

| 4.5 Design considerations and experimental results                                     | 118   |

| 4.5.1 Specifications                                                                   | 118   |

| 4.5.2 Insulation design                                                                | 122   |

| 4.5.3 Electrical design                                                                | 119   |

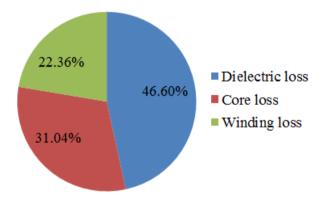

| 4.5.4 Power loss anlysis                                                               | 121   |

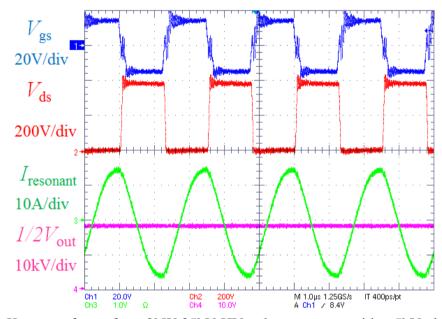

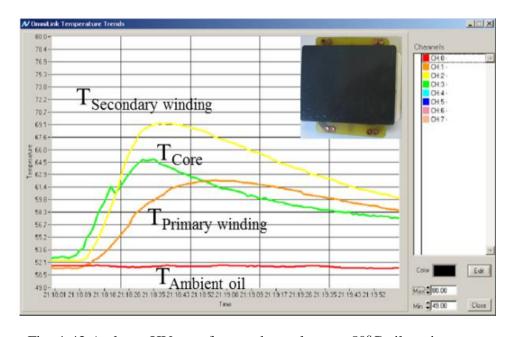

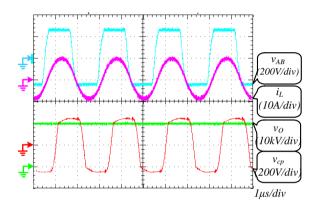

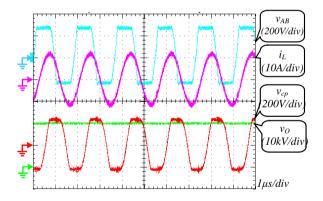

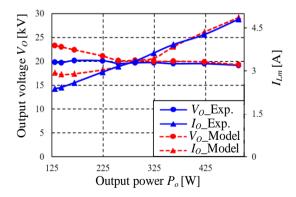

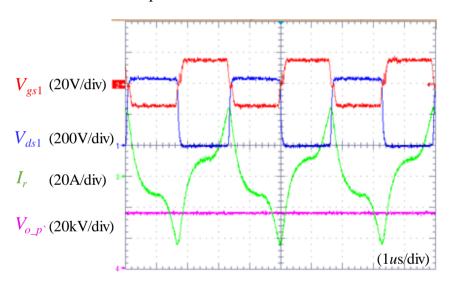

| 4.5.5 Experimental results                                                             | 122   |

| 4.6 Summary                                                                            | 125   |

| 4.7 References                                                                         | 125   |

| Chapter 5                                                                              | 129   |

| Steady state and dynamic analysis of the volatge multiplier for the modular HV pu      | ılse  |

| converter                                                                              | 129   |

| 5.1 Introduction                                                                       | 129   |

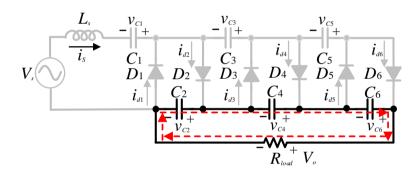

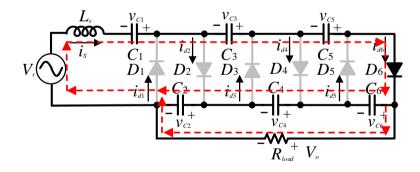

| 5.2 Steady state circuit analysis of the voltage multiplier                            | 129   |

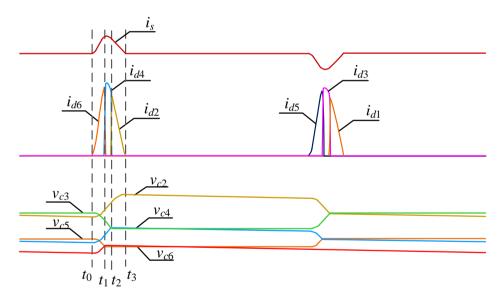

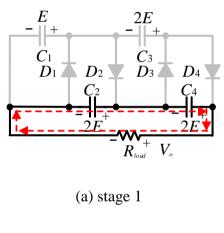

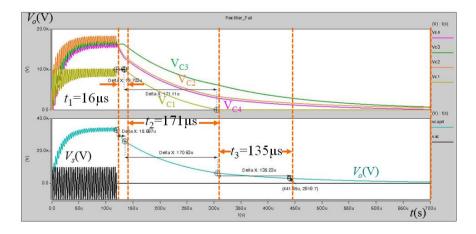

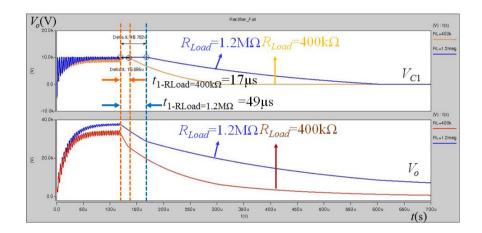

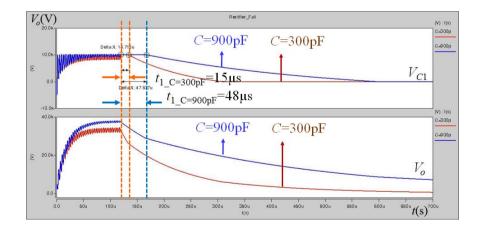

| 5.3 HV pulse rise and decay times analysis                                             | 134   |

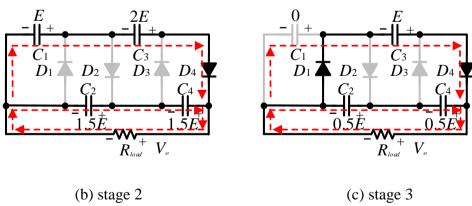

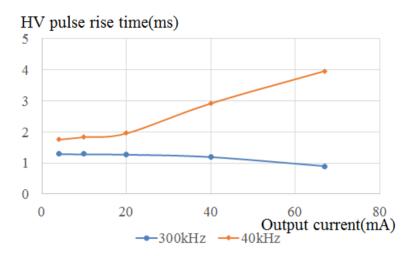

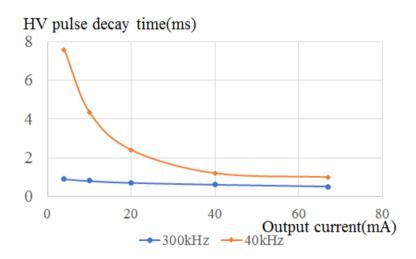

| 5.3.1 HV pulse rise times analysis                                                     | 134   |

| 5.3.2 HV pulse decay times analysis                                                    | 141   |

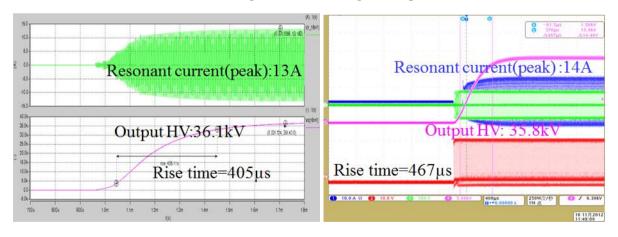

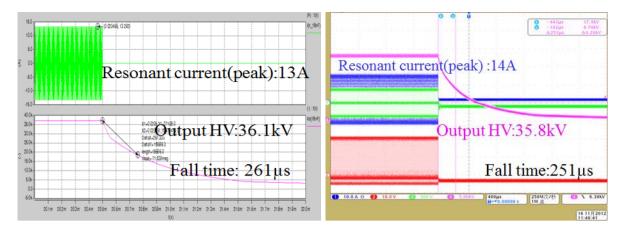

| 5.3.3 Experimental verifications                                                       | 143   |

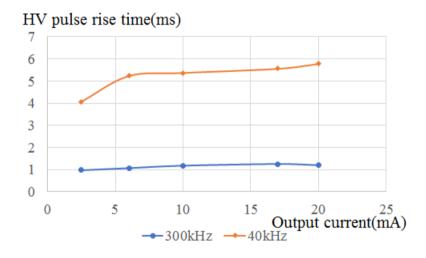

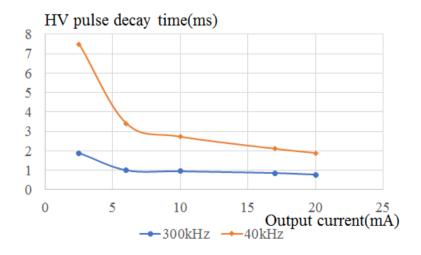

| 5.3.4 HV pulse rise and decay times experimental results from technology demonstrators | 144   |

| 5.3.5 Practical design guidelines                                                      | 146   |

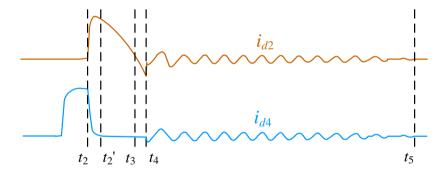

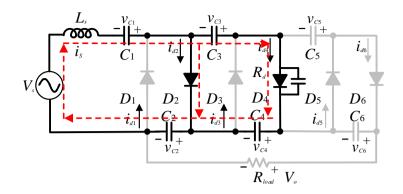

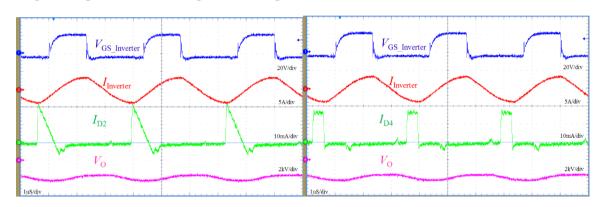

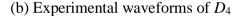

| 5.4 Diode reverse recovery process analysis for the voltage multiplier                 | 147   |

| 5.4.1 Diode reverse recovery in voltage multiplier circuit                             | 147   |

| 5.4.2 Experimental results                                                             | 149   |

| 5.5 Power loss for the voltage multiplier                                              | 150   |

| 5.6 Summary                                                                            | 152   |

| 5.7 References                                                                         | 152   |

| Chapter 6                                                                              | 155   |

| The unified steady-state circuit model and the comprehensive design of the modul       | ar HV |

| pulse converter                                                                        | 155   |

| 6.1 Introduction                                                                       | 155   |

| 6.2 Unified equivalent steady-state circuit modeling                                   | 158   |

| 6.2     | 2.1 Modelling assumptions                                                                                                 | 158 |

|---------|---------------------------------------------------------------------------------------------------------------------------|-----|

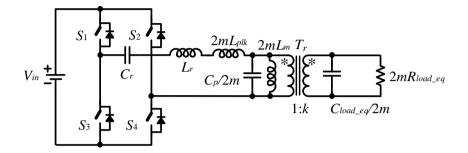

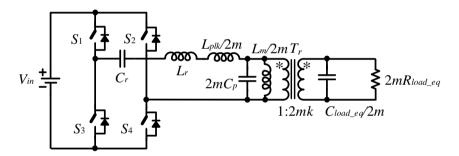

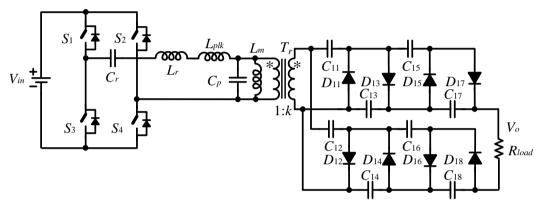

|         | 2.2. Modeling of the LCC resonant HV pulse converter with the single polarity hal ave Cockcroft-Walton voltage multiplier |     |

| 6.2     | 2.3 Generic steady-state circuit model of four HV pulse converter architectures                                           | 164 |

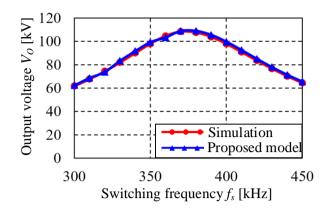

| 6.2     | 2.4 Simulation verifications of the steady-state circuit model                                                            | 167 |

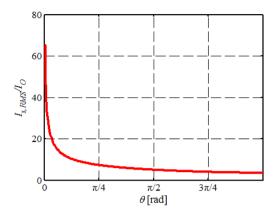

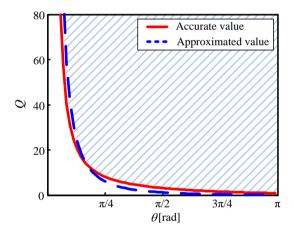

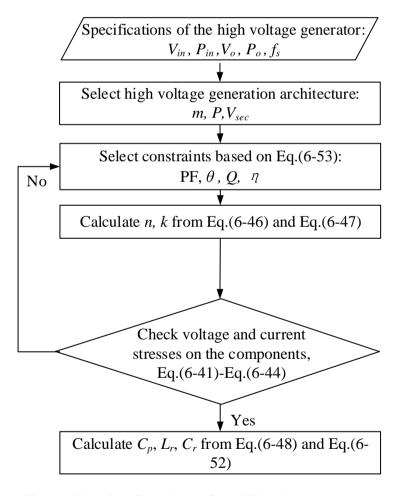

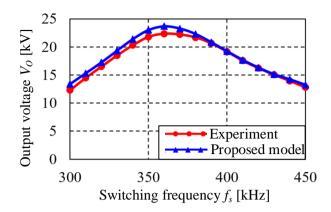

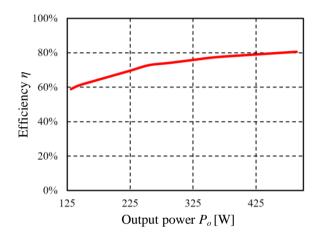

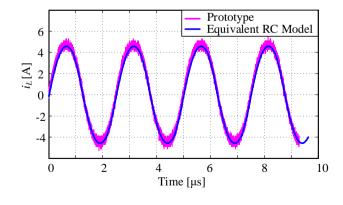

| 6.3     | Comprehensive analysis and design of the modular HV pulse converter                                                       | 169 |

| 6.3     | 3.1 Power factor                                                                                                          | 169 |

| 6.3     | 3.2 Voltage gain                                                                                                          | 170 |

| 6.3     | 3.3 Electrical stress                                                                                                     | 171 |

| 6.3     | 3.4 Design method                                                                                                         | 174 |

| 6.4     | Experimental results                                                                                                      | 175 |

| 6.5     | Summary                                                                                                                   | 179 |

| 6.6     | References                                                                                                                | 180 |

| Chapt   | ter 7                                                                                                                     | 183 |

| Concl   | usions and recommendations                                                                                                | 183 |

| 7.1     | Conclusions                                                                                                               | 183 |

| 7.2     | Thesis contributions.                                                                                                     | 185 |

| 7.2     | Recommendations for future research                                                                                       | 185 |

| Apper   | ndix                                                                                                                      | 187 |

| Techn   | nology demonstrators of the modular HV pulse converter                                                                    | 187 |

| Summ    | nary                                                                                                                      | 199 |

| List of | f Publications                                                                                                            | 205 |

| Curri   | culum Vitae                                                                                                               | 209 |

### Chapter 1

### Introduction

The main objective of this thesis is to investigate a modular high voltage (HV) pulse converter technology with fast rise and decay times, high efficiency, high power density. The focus of this thesis is to derive a systematic approach to classify and identify the optimal architecture, investigate the key subcomponent's technologies and derive a generic equivalent steady-state circuit modeling method and comprehensive design procedure for a HV pulse converter. More specifically, the research will concentrate on the effect of modularization, increased switching frequency for a HV transformer, and the key influence factors for HV pulse rise and decay times, as well as the method used to mitigate diode reverse recovery effect for multi-stage voltage multiplier. This chapter introduces the related research background, problem statement, research objectives and thesis layout.

#### 1.1 Background

#### 1.1.1 Overview of HV pulse converters

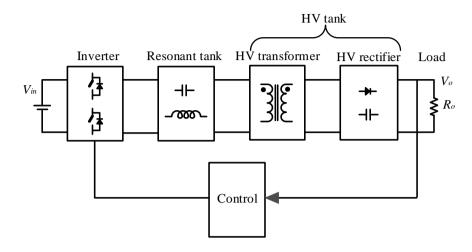

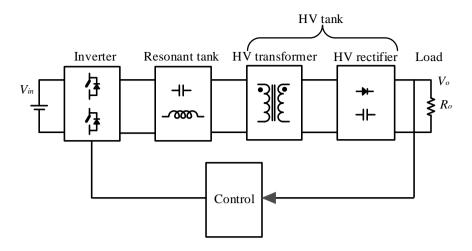

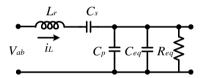

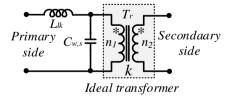

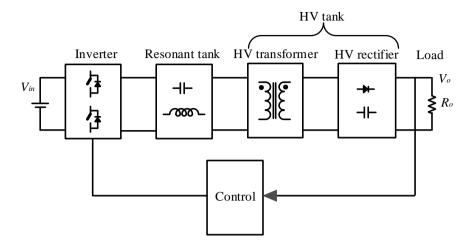

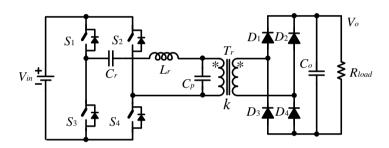

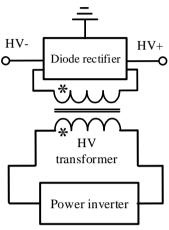

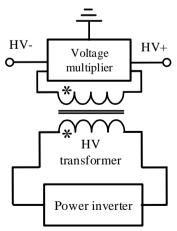

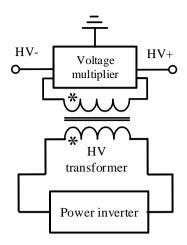

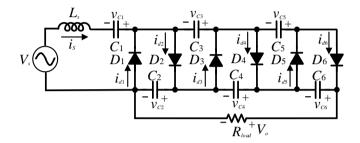

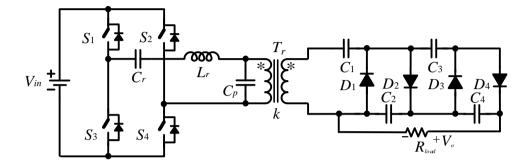

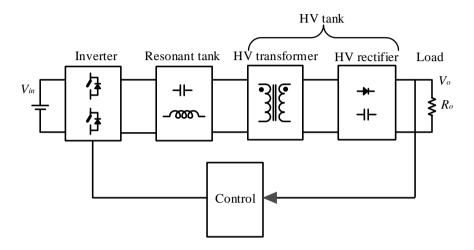

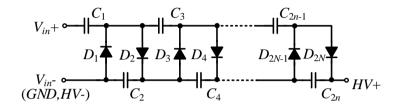

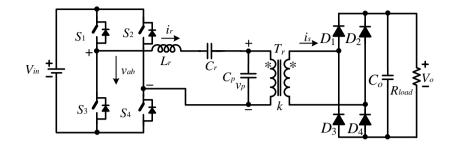

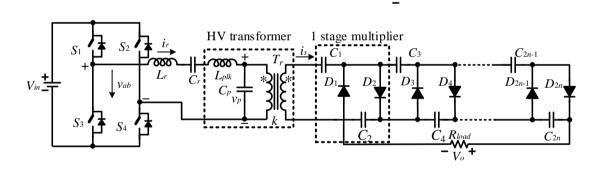

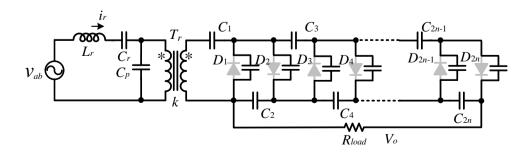

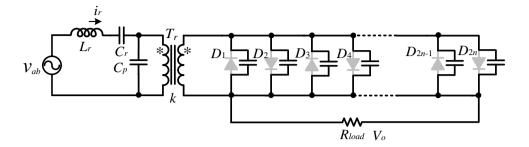

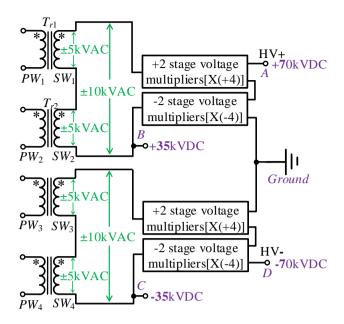

HV pulse converters are widely used in applications such as X-ray generation [1-1]-[1-5], electrostatic precipitation (ESP)[1-6]-[1-9], HV capacitor charger amongst other areas[1-10]-[1-12]. Generally, HV pulse converters convert low voltage DC voltage to high DC voltage, which typically is as high as tens to hundreds of kilovolts according to different applications. A HV pulse converter is also known as a HV pulse generator, HV generator, HV power supply or HV DC-DC converter in many applications. The HV pulse converter is the term used in this thesis. Compared to traditional low frequency HV pulse converters, switching mode high frequency HV pulse converters provide higher power density, higher efficiency and better steady and dynamic performance. During decades of research, high frequency HV generation technologies have been successfully industrialized and have accumulated abundant solutions for different applications. Generally, a HV pulse converter is composed of a DC-AC inverter, a resonant tank, a HV transformer and a HV rectifier, as illustrated in Fig.1-1. The seriesparallel (LCC) resonant type converter is the common topology of choice in high frequency HV pulse converter systems due to its ability to utilize the parasitic components of a HV transformer and achieve soft switching for a wide operating range. The inverter converts low input DC voltage into high frequency low AC voltage. The basic topology for an inverter is half bridge or full bridge. In relatively high input voltage applications, multi-level inverters or cascaded inverters are alternative options. Resonant capacitors and inductors are often combined to form a resonant tank, where resonant current or voltage is used to ensure softswitching of power semiconductor devices. The function of a HV transformer is to provide the voltage step-up with galvanic isolation by converting the high frequency low AC voltage to high frequency high AC voltage. The HV rectifier converts the high frequency high AC output voltage from the secondary winding of the HV transformer to even higher DC output voltage. A full bridge rectifier is the basic topology for a HV rectifier. However, in some cases, the multi-stage multiplier circuit is adopted to acquire higher output voltage. Besides, the aforementioned components can be connected in series or parallel flexibly to achieve better performance depending on the applications.

Fig. 1-1 HV pulse converter circuit diagram

#### 1.1.2 HV pulse converter in CT and X-ray machine applications

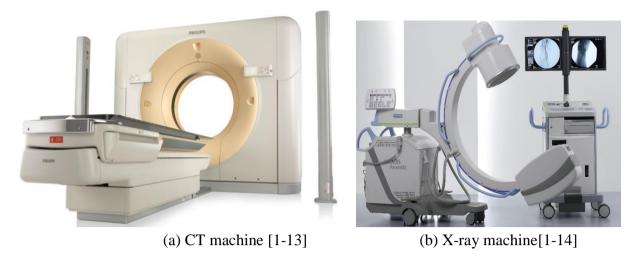

Fig. 1-2 introduces HV pulse converter application examples of medical computed tomography (CT) machines and X-ray machines. Being one of the most useful tools in the medical field, Radiologists use X-Ray Generators to produce pictures of a patient's internal structures, allowing them to diagnose broken bones, locate tumors, and even see the digestive tract. The HV pulse converter is the key component for CT and X-ray machines to generate required high voltage, ranging from 20 kilovolt(kV) to 160kV across the X-ray tube anode and cathode in order to establish an intense electric field to accelerate the electrons. The X-ray will be generated when the electrons gain sufficient energy through the acceleration and collide with the anode of the X-ray tube. The required high voltage can be as high as 450kV for industrial non-destructive inspection application which requires high intensity high resolution X-ray from the x-ray tubes with focal spot sizes of 1µm or less. The flow of electrons from the current of a HV pulse converter is in the range of 1 to 1000 milliampere(mA).

The HV pulse converter circuit for CT and X-ray machine radiographic applications has been developing for almost a century with the continuous improvement of power semiconductor devices, magnetic materials, insulation materials and dielectric materials technology. The X-ray HV pulse converter was developed in the early 20th century by using mechanical switches at low frequency (50/60Hz) operation. Then the power semiconductor device such as a thyristor was introduced for X-ray HV pulse converters in the middle of the 20 century. Since the 1980s, the power semiconductor devices such as silicon IGBT and MOSFET were used for X-ray HV pulse converters at several tens of kHz to few hundreds of kHz switching frequency. The typical switching frequency for a HV pulse converter in existing CT and X-ray machines is around 20 to 80kHz. A photo of a HV pulse converter for the medical X-ray machine is shown in Fig. 1-3 as an example [1-15]. The size of X-ray HV pulse converter can be reduced significantly by high switching frequency operation compared with low switching frequency in early stage.

Fig. 1-2 The HV pulse converter applications examples: medical CT and X-ray machine

Fig. 1-3 Photo of a HV pulse converter for the X-ray machine [1-15]

Along with the development of medical CT and X-ray machines, HV pulse converter technology will also evolve for improved performance or advanced function requirements for CT and X-ray machines in the future. Some of the requirements for medical CT and X-ray machine development are listed below:

- a) Better imaging quality, and image artefact mitigation due to motion

- b) Radiation dose reduction

- c) Dual energy, fast HV pulse switching between one HV to another HV within short time

- d) Low energy consumption

- e) Compactness, portable, light weight

- f) Flexible, scalable

- g) Reliable, easy maintenance

- h) Cost effective

The development requirements of medical CT and X-ray machine raise the research needs for a HV pulse converter to meet the medical instruments system performance and function target. The research needs will be elaborated later.

#### 1.1.3 HV pulse converter in electrostatic precipitator applications

The electrostatic precipitator is another industrial application example for the HV pulse converter illustrated in Fig. 1-4. Due to growing concerns about environmental pollution, the reduction of particle emissions by electrostatic precipitator is a highly important issue for coal fired power plants [1-6]. An ESP consists of parallel electrodes that use electrostatic charges to separate particles in the entering gas. Power converters are used to supply energy to the ESP electrodes at a high voltage level. These power supplies have a typical output power range of 10 to 250 kW and a high output DC voltage range of 30 to 150 kV [1-7].

(a) an electrostatic precipitator machine [1-16]

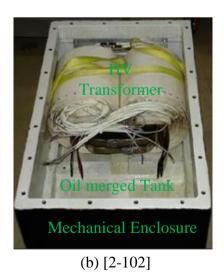

(b) a HV pulse converter [1-17]

Fig. 1-4. HV pulse converter applications examples: an electrostatic precipitator and photo of a HV pulse converter for an electrostatic precipitator

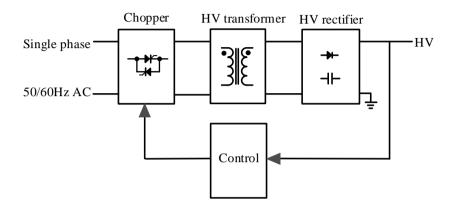

The conventional electrostatic precipitator was driven by mains frequency transformer-rectifier based HV pulse converter technology which is commonly referred to "transformer rectifier sets" (TR). The mains frequency HV pulse converters are still the most commonly used for ESP. Fig. 1-5 provides the diagram of a mains frequency HV pulse converter for an electrostatic precipitator [1-7]. It comprises a single-phase mains frequency (50/60Hz) voltage step-up transformer with high turns ratio and high insulation capability followed by a rectifier which connects to the electrostatic precipitator. The HV pulse converter is controlled by changing the firing angles of an anti-parallel pair of thyristors in the transformer primary side [1-8].

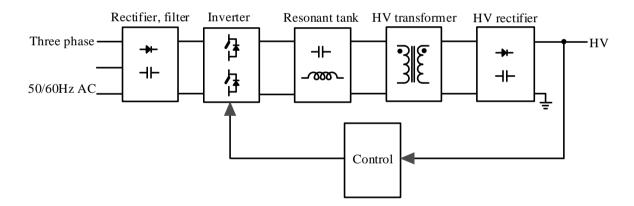

Modern high frequency HV pulse converter technologies have been being developed for the electrostatic precipitator in power plants and industrial processes since the early 1990s. For the high frequency HV pulse converter technology, the mains are rectified by three-phase input rectification and the resulting smooth DC voltage is chopped by using a transistor bridge to a high frequency AC voltage, connected to the HV transformer with a high turn ratio and with sufficient insulation. The secondary winding of the HV transformer is connected to the output diode rectifier that supplies the required voltage and current to the electrostatic precipitator. Typical operation switching frequency for a HV pulse converter is 20 to 50kHz. An example

of a high frequency HV pulse converter diagram is depicted in Fig. 1-6 [1-9]. A power factor close to unity, and a better form factor of the input current over the entire operation range, can be achieved. The series parallel(LCC) resonant converters are an attractive choice for a high frequency HV pulse converter for an electrostatic precipitator because they can operate in soft-switching modes, reducing the switching losses and with the possibility to incorporate the HV transformer non-idealities. If a conventional hard-switching PWM converter were to be used, the leakage inductance and the winding parasitic capacitance of the HV transformer, would cause parasitic resonances that affect the HV pulse converter's behaviour.

Fig. 1-5 Block diagram of a mains frequency HV pulse converter for an electrostatic precipitator [1-7]

Fig. 1-6 Block diagram of a high frequency HV pulse converter for the electrostatic precipitator [1-9]

High frequency HV pulse converter technology provides significant advantages over conventional mains frequency HV pulse converter to improve electrostatic precipitator overall performance and reduce the dust emission level. The advantages of high frequency HV pulse converter technology are summarized below:

- a) Comparatively overall size and weight reduction.

The weight of the high frequency type is around 1/3 to 1/5 of the conventional mains frequency HV pulse converter since the HV transformer size and weight can be greatly reduced at high switching frequency.

- b) Low output voltage ripple.

Very smooth high DC output voltage with negligible output voltage ripple can be achieved for a high frequency HV pulse converter. It will also increase the efficiency of the electrostatic precipitator.

c) Much faster control response, faster sparkover handling, low stress on the electrostatic precipitator electrodes.

There is a delay between detection of a sparkover and the reaction of the HV pulse converter in the range of few ten ms because the thyristor is operated at mains frequency for the conventional mains frequency HV pulse converter. This delay drops down into the µs range. The power flow to the arc is much faster than a mains frequency HV pulse converter, resulting in shorter arcing time due to much faster control response. The duration of the precipitation outage, and thus average emissions can be reduced. Additionally, shorter arcing durations mean less stress on components of the electrostatic precipitator.

d) Ease for transportation, installation.

The installation and commissioning time is reduced to half a day compared to several days for the conventional mains frequency HV pulse converter. The transportation and installation and commissioning cost can be also saved.

e) Low impact for the mains.

High frequency HV pulse converter technology loads the 3-phase mains symmetrically, and the load is shared symmetrically between the three mains phases. The conventional mains frequency HV pulse converter has unbalanced conditions between the mains phases, with a higher apparent power. So, it suffers higher losses and thus increasing the size and cost of devices. The input currents per phase are significantly lower for a high frequency HV pulse converter compared with the single-phase connected mains frequency HV pulse converter.

The main differences between the conventional thyristor-based mains-frequency HV pulse converter technology and the high frequency HV pulse converter technology are summarized in Table 1-1.

Due to the stricter requirement for emissions reduction and electrostatic precipitator system operation cost saving, the performance of high frequency HV pulse converters needs to be further improved. Some of the requirements for high frequency HV pulse converters used in electrostatic precipitator development are listed below:

- a) Better capability for emission reduction: faster response and sparkover handling capability, lower stress on the electrostatic precipitator electrodes.

- b) System operation cost saving: low energy consumption

- c) Reliable and easy maintenance

- d) Cost effective

The development requirements of an electrostatic precipitator raise the research needs for HV pulse converters to meet the system performance and function target.

Table 1-1 Summary of the main differences between conventional mains frequency and high frequency HV pulse converter technology

| Features              | Mains frequency HV generator     | High frequency HV generator |  |

|-----------------------|----------------------------------|-----------------------------|--|

| Input phase           | Single phase                     | Single phase                |  |

| Mains impact          | Power factor < 0.7               | Power factor>0.9            |  |

|                       | 3 phase unbalance for mains      | 3 phase balance for mains   |  |

|                       | High current stress              | Relative low current stress |  |

| Frequency             | 50/60Hz                          | 20~50kHz                    |  |

| Switching power       | Thyristor                        | Transistor: IGBT, MOSFET    |  |

| device                |                                  |                             |  |

| Output voltage ripple | ~30%                             | <1%                         |  |

| Power conversion      | 80~85%                           | 90~95%                      |  |

| efficiency            |                                  |                             |  |

| Dynamic performance   | Slower control (10 ms), downtime | Very fast (10-50 μs),       |  |

|                       | due to sparkover up to 100 ms    | downtime due to sparkover   |  |

|                       |                                  | below 10 ms                 |  |

| Weight                | 1000~3000kg                      | 200~500kg                   |  |

#### 1.1.4 Research needs for HV pulse converter performance improvement

According to the above introductions about the development requirements of medical CT and X-ray machines, the research needs for a HV pulse converter can be concluded to meet the medical instrument's system performance and function target. High switching frequency, modular HV architecture, new emerging Silicon Carbide(SiC) power semiconductor device and high power density integration are four key aspects to achieve HV pulse converter performance improvement. The relationship of four key aspects and development requirements of a HV pulse converter for medical CT/X-ray machines are summarized in Table 1-2. The green stars illustrate that the four key aspects impact on the development requirements.

Table 1-2 Relationship of four key aspects and development requirements of the HV pulse converter for medical CT / X-ray machine

|                            | High<br>switching<br>frequency | Modular architecture | SiC power<br>semiconductor<br>technology | High density integration |

|----------------------------|--------------------------------|----------------------|------------------------------------------|--------------------------|

| Imaging quality            | *                              |                      | 3,                                       |                          |

| Radiation dose reduction   | *                              |                      |                                          |                          |

| Low energy consumption     |                                | *                    | *                                        |                          |

| Dual energy                | *                              |                      |                                          |                          |

| Compact, light weight      | *                              | *                    | *                                        | *                        |

| Flexible, scalable         |                                | *                    |                                          |                          |

| Reliable, easy maintenance |                                | *                    |                                          |                          |

| Cost effective             | *                              | *                    |                                          | *                        |

**High switching frequency**

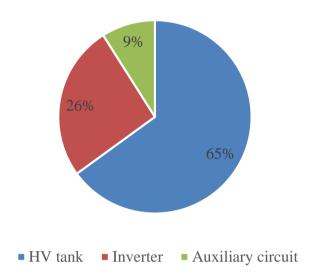

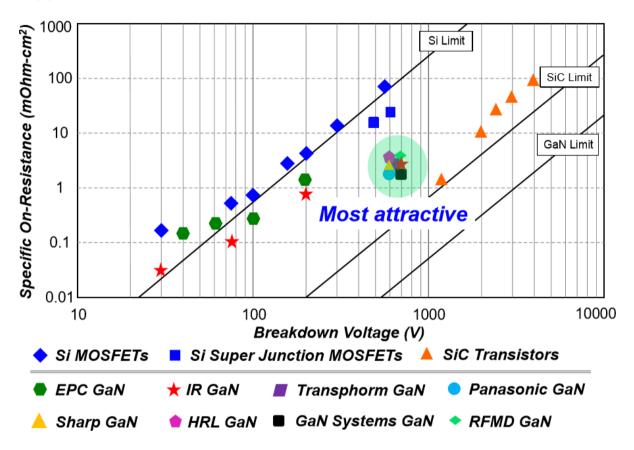

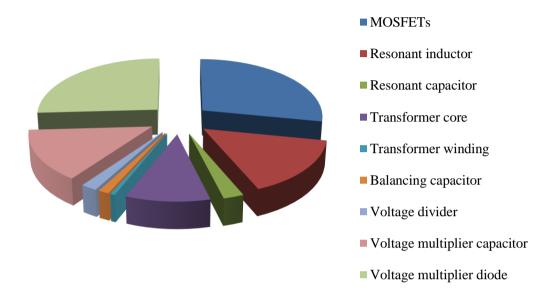

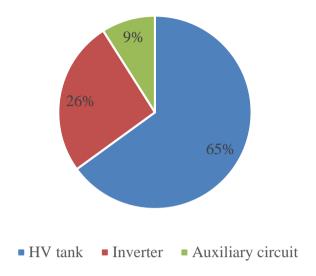

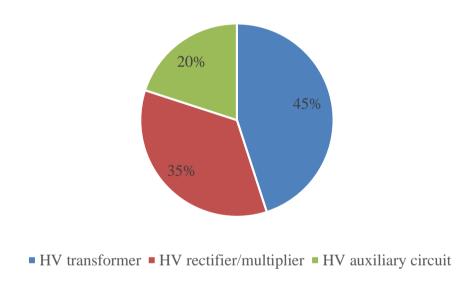

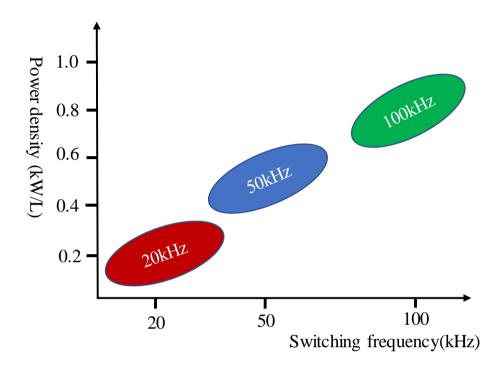

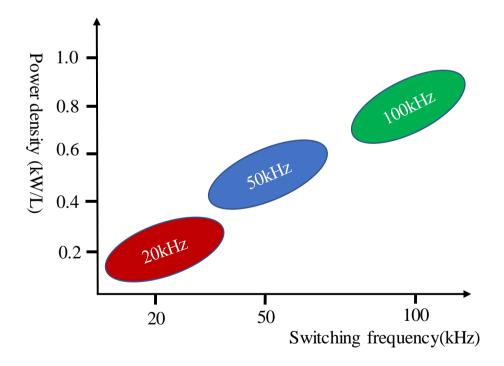

Regarding the development requirements of medical CT/X-ray machine: high switching frequency plays a critical role for HV pulse converter development. The switching frequency for state-of-the art HV pulse converter products in medical CT/X-ray machines is below 100 kHz to limit the HV transformer insulation stress at high frequencies and HV transformer and voltage multiplier power losses challenges at high frequency. At these frequencies, the power density of a HV pulse converter is limited to around 1kW/L. Fig. 1-7 shows the volume distribution of a HV pulse converter [1-18].

Fig. 1-7 Volume distribution for the HV pulse converter [1-18]

Fig. 1-8 Volume distribution for the HV tank [1-18]

The HV tank dominates the volume of a HV pulse converter. The volume distribution of a HV pulse converter is given in Fig. 1-8. HV transformers and HV rectifier/multipliers contribute to the majority of the volume. High switching frequencies can help to shrink the size of a HV pulse converter to achieve high power density and light weight performance, especially the

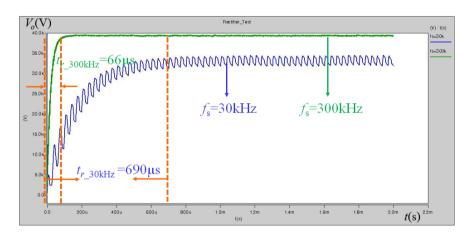

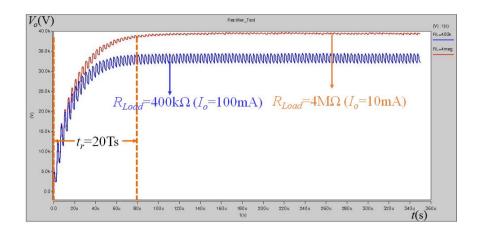

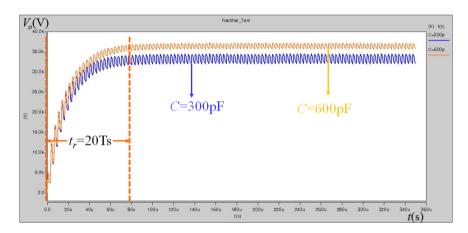

passive components such as the HV transformer, resonant inductor, resonant capacitor and voltage multiplier capacitors. With higher switching frequency, faster HV pulses can be realized since the HV tank capacitance can be significantly reduced. The image artefact can be mitigated due to the motion and better imaging quality can be achieved. Fast HV pulse will also help to reduce the radiation dose. Furthermore, a high switching frequency is the approach to achieve fast HV pulse switching between 80kV and 140kV with 100µs for dual energy CT. The mechanical enclosure size and required insulation oil volume can be reduced since the size and volume of the HV pulse converter can be shrunk at high frequency. The total HV pulse converter system cost can be reduced at high frequency operation.

#### **Modular HV architectures**

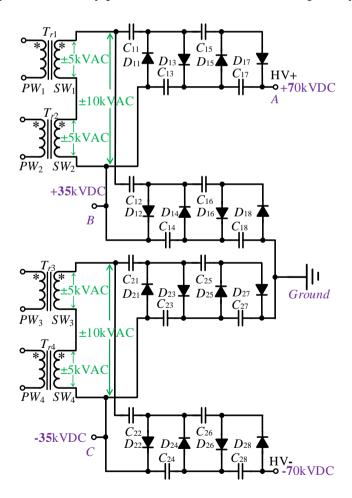

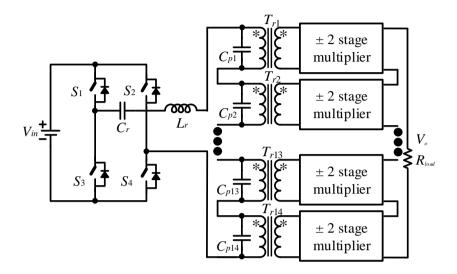

The conventional high voltage generator with a single HV transformer and rectifier or multiplier to achieve the high voltage generation suffers high insulation stress for the HV transformer and large size and low efficiency due to large parasitic-capacitance of HV transformer. High switching frequency can help to shrink the size of the HV pulse converter, especially the HV transformer and voltage multiplier capacitors. But the power loss will increase for the HV transformer due to high conduction loss and high frequency AC dielectric loss at high switching frequency. The modular HV generation architecture with a distributed HV transformer and multiplier will reduce the electrical and insulation stress for the key components in a HV pulse converter. Additionally, the power loss of a HV pulse converter can be reduced. With reduced HV insulation stress, lower voltage/power stress for the distributed HV transformer, the size of the HV tank can be reduced. In addition, the operation frequency can be further increased due to the lower parasitics from the HV transformer, reduced insulation stress, and lower winding dielectric loss. The modular architecture also helps to achieve compact size and high power density performance. Furthermore, the scalability for a HV generation system with modular HV architecture is important for mass production, and ease of manufacturing to save cost since smaller and lower voltage/power rating modules can be implemented in a cheaper technology platform, such as printed circuit board(PCB).

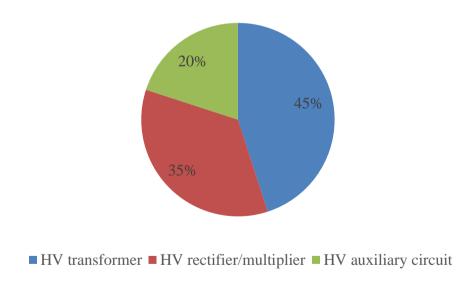

#### SiC power semiconductor technology

The new emerging wide band-gap materials such as Silicon Carbide (SiC) and Gallium Nitride (GaN) offer improved performance capabilities for power electronic devices compared to traditional Silicon (Si) power semiconductor devices due to the advantages of the wide band gap materials. SiC MOSFET power semiconductor devices are expected to displace silicon IGBTs and silicon MOSFETs in higher voltage and power applications wherein improved efficiency, power density and/or higher temperature operation are required. A comparison of power semiconductor device performance figures for various device technologies is shown in Fig. 1-9 [1-19]. From the device performance figure, SiC transistors are mostly targeted at high voltages beyond 1000V. SiC MOSFET power semiconductor devices provide potential loss reduction of 60 - 90% with low switching and conduction loss [1-19], [1-20]. Higher efficiency, reduced operational cost can be realized. The power density and HV pulse quality can be greatly improved since the SiC device is capable of operating at higher switching frequency (>100 kHz) due to inherent fast switching capability. It can also work at higher junction

temperature compared with existing Silicon devices and simplify the cooling requirement to enable a less expensive cooling system. The main challenge is the cost for high power SiC MOSFET module (around 5-10 times more expensive than a silicon IGBT module at current stage). The new emerging 6 inch fab will alleviate the challenge of high cost for the SiC MOSFET module.

Fig. 1-9 Power semiconductor device figures of merits [1-19]

#### **High density integration**

Recent trends in the power electronics industry pursue higher levels of integration and better packaging techniques in order to meet the power electronics system requirements such as cost, size and power density, [1-12], [1-13]. The development trend toward increased miniaturisation of components and packages with high density integration is continuing in the electrostatic precipitator and medical CT/X-ray machine industries. High power density integration as well as packaging technologies can improve the interconnection, shrink the size of the HV pulse converter and reduce the cost of the HV pulse converter system. High density integration technologies can achieve structural, functional and processing integration to reduce component volume and labour cost. An extremely careful balance of electromagnetic, physical, thermal and spatial aspects is required for high density integration for a HV pulse converter.

There is synergy of the HV pulse converter research needed for electrostatic precipitators and medical CT/X-ray machines. The requirement of a better capability for emission reduction, faster response, sparkover handling capability and lower stress on the electrostatic precipitator electrodes request sharp pulse and higher switching frequency operation. A sharp HV pulse

and higher switching frequency operation is the enabling technology to improve the imaging quality, radiation doze reduction, and dual energy function for medical CT/X-ray machines. Low energy consumption, reliability and easy maintenance, as well as cost effectiveness are common requirements for electrostatic precipitators and medical CT/X-ray machines. So the research needs for HV pulse converter development are similar and the four key aspects are common for electrostatic precipitator and medical CT/X-ray machine applications. Low energy consumption will help to reduce the operation cost for hospital and power plants. In summary, high efficiency, a sharp HV pulse and high power density are the most critical requirements for future HV pulse converters.

#### 1.2 Research questions

To meet the above requirement for further performance improvements such as efficiency, HV pulse quality and power density for HV pulse converters, the main research questions of this thesis are listed below:

# Identify the optimal HV architecture for a multi-kW 100kV HV pulse converter system supplying pulses with fast rise and decay times

The different HV pulse converter architectures to generate high output voltages for different industrial applications with different high output voltage rating and output power rating are reported. However, state-of-the-art works do not give a systematic approach to the modularisation of architectures of a HV pulse converter. A systematic approach to derive and classify HV pulse converter architectures is required to provide a clear picture of existing or potential solutions for HV generation architectures. Furthermore, the comparative evaluation of different HV pulse converter architectures have not yet been completed in literature. It is expected that different architectures will be optimal for low power and high power applications. Therefore, it is necessary to perform an evaluation of different HV pulse converter architectures in order to select promising architectures for good performance such as high efficiency, fast HV pulse and high power density at different voltage and power levels.

# How does modularization, increasing switching frequency, packaging and insulation structures affect the HV transformer in a HV pulse converter system?

High switching frequency operation can not only reduce the size of a HV pulse converter, especially the transformer and voltage multiplier capacitors, but it can also improve the HV pulse rise and decay times. However, the power loss will increase for the HV transformer due to high conduction loss and high frequency AC dielectric loss at high switching frequency. The modular HV pulse converter architecture with the modular HV transformer and modular multiplier is an enabler technology to reduce the stress and loss for the key components in a

HV pulse converter. However, the advantage and challenges of modularization for HV transformer has not yet been well discussed. The investigation and analysis of a HV transformer with planar and wire-wound packaging structure, as well as the HV insulation structure have not been mentioned for modular HV pulse converters.

## What are the key influence factors for multi-stage half-wave (HW) Cockcroft-Walton (CW) multiplier circuit output HV pulse waveforms?

The HV pulse rise and decay times play a critical part for the performance of modular HV pulse converter system. But the HV pulse rise and decay times of the multi-stage voltage multiplier based HV pulse converter has not been well investigated and key influence factors of HV pulse rise and decay times have not been studied in detail. Furthermore, the diode reverse recovery process of the high frequency HV multiplier circuit has not been addressed in literature. It's important to investigate the diode reverse recovery process at a high switching frequency and to study the diode reverse recovery mitigation method in order to achieve good performance for a voltage multiplier based HV pulse converter.

### Find a generic steady state circuit model and design methodology for modular architectures

The varying high voltage generation architectures offer greater alternatives to generate high output voltages. Simultaneously, more challenges are added in modeling and analysis due to various high voltage generation architectures. A unified steady-state model is essential and helpful to investigate the performance of modular HV pulse converter system with common architectures. This could offer effective guidelines in HV generation topology selection and find general parameter design strategies. Unfortunately, most state-of-the-art steady-state models are deduced only for the simple full-bridge rectifier and only for a specified architecture. For the voltage multiplier fed by the LCC resonant tank, the operation of the voltage multiplier is far more complex than that of the full bridge rectifier. In general, the modeling of the voltage multiplier fed by the LCC resonant tank and the various HV generation architectures are two remaining challenges to be solved. Furthermore, the design of the HV pulse converter is also challenging due to the lack of accurate models and the high degree of design freedom. The comprehensive design approach of a HV pulse converter based on power factor, quality factor and conduction angle to achieve the design of high efficiency and low components electrical stresses has not yet been mentioned.

### 1.3 Approach

Based on the aforementioned research questions, the following is the approach for this thesis:

- i. Develop a systematic approach to derive and classify the HV pulse converter architectures, evaluate different HV generation architectures and identify the most promising architectures in terms of output voltage and output power ratings.

- ii. Analyse the effects of modularization, packaging and the insulation solution for the transformer which can be used in modular HV pulse converter architecture.

- iii. Investigate the key factors that influence the HV pulse rise, decay times, and voltage multiplier diode reverse recovery mitigation solution.

- iv. Develop a generic equivalent steady-state circuit model and comprehensive design procedure for modular HV pulse converter architectures.

#### 1.4 Thesis layout

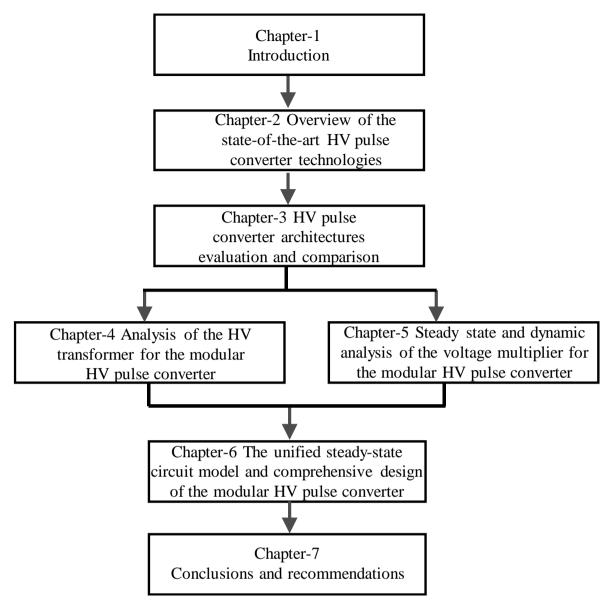

A map showing the layout of this thesis is shown in Fig. 1-10, and a summary of each chapter is described below.

In Chapter 2, the state-of-the-art HV pulse converter technologies are reviewed. Firstly, the overview of existing HV pulse converter architectures are provided. Then the topology, the key power building blocks of HV pulse converter such as inverter, HV transformer and HV rectifier/multiplier are reviewed separately. Then the HV insulation and packaging for a HV pulse converter are reviewed. Finally, the research gap and thesis focus are identified from the review of HV pulse converter technologies.

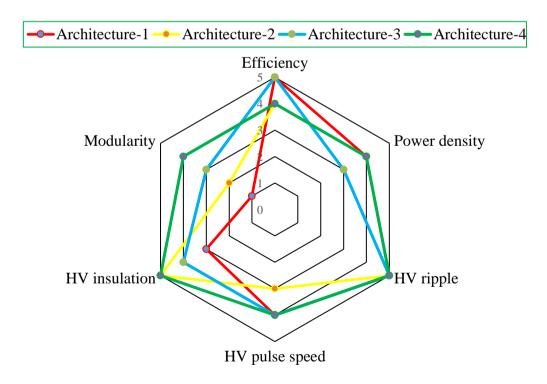

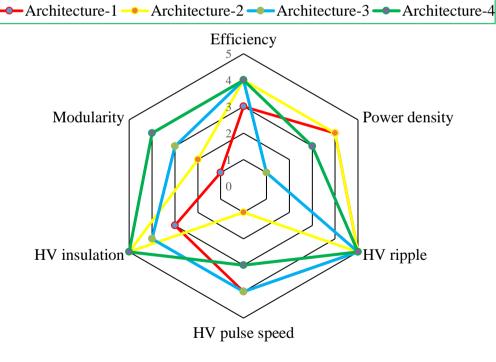

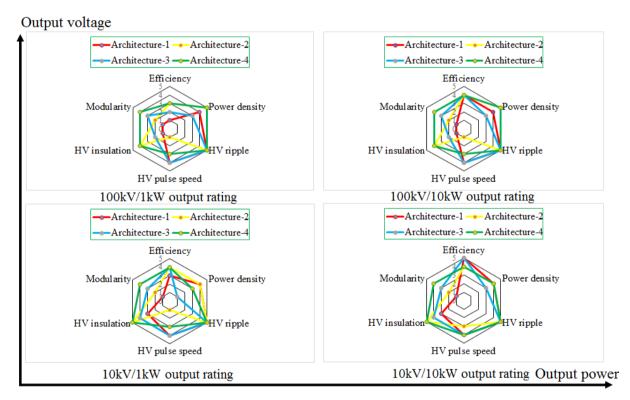

In Chapter 3, the methodology of HV generation architecture derivation is developed to derive and classify HV pulse converter architectures based on modularization levels of key subcomponents of a HV pulse converter. Then the comparative analysis of efficiency, power density, HV pulse quality, HV insulation stress, as well as modularity and evaluation of different HV pulse converter architectures are performed to compare the architecture's performance at different output voltage and output power ratings. Based on this, the optimal architecture is identified, and guidelines for architecture selections are recommended.

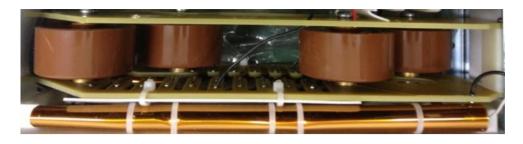

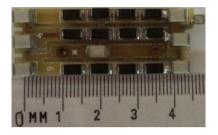

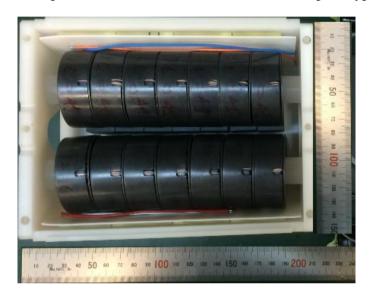

In Chapter 4, the advantages of modularization for a high frequency HV transformer are introduced firstly. Then the planar and wire-wound packaging structures, as well as HV insulation structures of a transformer in a modular HV pulse converter are presented. The detailed design considerations and technology demonstrator of a high frequency HV transformer for the modular HV pulse converter architecture are provided.

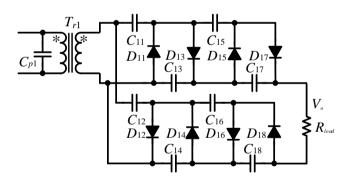

In Chapter 5, the steady state circuit analysis of the voltage multiplier is introduced to firstly provide the HV pulse drop and ripple characteristics. The key influence factors for HV pulse rise and decay times are investigated for a HV pulse converter with multi-stage voltage multiplier circuit. The diode reverse recovery process and mitigation method by using silicon carbide Schottky diodes for a high frequency multi-stage voltage multiplier circuit are addressed. Based on the analysis results performed, the hardware prototype experimental results are provided to validate the concept. The power loss analysis of high frequency voltage multiplier circuits is introduced.

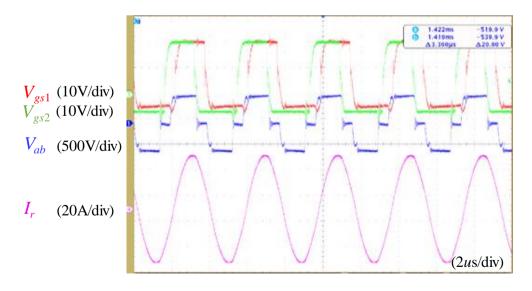

In Chapter 6, the generic equivalent circuit model which can simplify the design and analysis of LCC resonant converter based HV pulse converter architectures is proposed to provide effective guidelines for analysis and design of the HV pulse converter with different architectures. The comprehensive design method by utilizing conduction angle, power factor and quality factor for the modular HV pulse converter is developed and verified by prototype experimental results.

In Chapter 7, the conclusions of the thesis and recommendations for the future research are given.

Fig. 1-10 Map of the thesis layout

#### 1.5 References

- [1-1] J. Bushberg, "The essential physics of medical imaging," ISBN 0-683-30118-7, 2nd edition, 2002

- [1-2] J. A. Martin-Ramos, A. M. Pernia, J. Diaz, F. Nuno and J. A. Martinez, "Power Supply for a High-Voltage Application," IEEE Transaction Power Electron., vol. 23, no. 4, pp. 1608-1619, July 2008

- [1-3] H. Hino, T. Hatakeyama, M. Nakaoka, "Resonant PWM inverter linked DC-DC convertor using parasitic impedances of high-voltage transformer and its applications to X-ray generator," in Proc. IEEE PESC 1988, pp. 1212-1219

- [1-4] J. Sun, X. Ding, M. Nakaoka, H. Takano, "Series resonant ZCS-PFM DC-DC converter with multistage rectified voltage multiplier and dual-mode PFM control scheme for

- medical-use high-voltage X-ray power generator", IEE Proceedings Electric Power Applications, 2000, vol. 147, Issue.6, pp.527-534

- [1-5] S. Iqbal, G. K. Singh, R. Besar, "A dual-mode input voltage modulation control scheme for voltage multiplier based X-ray power supply," IEEE Transaction on Power Electron., vol. 23, no. 2, 2008, 1003-1008

- [1-6] P. Ranstad, C. Mauritzson, M. Kirsten, and R. Ridgeway, "On experiences of the application of high-frequency power converters for ESP energization," in Proc. ICESP, 2004, pp. 1-16

- [1-7] T. Soeiro, J. Biela, J. Nuhlethaler, J. Linner, P. Ranstad, and J. W. Kolar, "Optimal design of resonant dc-dc converter for electrostatic precipitators," in Proc. IPEC, 2010, pp. 2294-2301

- [1-8] T. B. Soeiro, J. Mühlethaler, J. Linnér, P. Ranstad and J. W. Kolar, "Automated design of a high-power high-frequency LCC resonant converter for electrostatic precipitators," IEEE Transaction Ind. Electron., vol. 60, no. 11, pp. 4805-4819, Nov. 2013

- [1-9] T. Soeiro, "High efficiency electrostatic precipitator systems with low effects on the mains," ETH PhD thesis, 2012

- [1-10] H.J. Ryoo, S.R. Jang, Y.S. Jin, J.S. Kim, Y.B. Kim, S.H. Ahn, J.W. Gong, B.H. Lee and D.H. Kim, "Design of high voltage capacitor charger with improved efficiency, power density and reliability," IEEE Transaction on Dielectrics and Electrical Insulation, Vol. 20, No. 4, pp. 1076-1084, 2013.

- [1-11] S. H. Ahn, H. J. Ryoo, J. W. Gong, and S. R. Jang, "Design and test of a 35-kJ/s high-voltage capacitor charger based on a delta-connected three phase resonant converter," IEEE Transaction Power Electron., vol. 29, no. 8, pp. 4039-4048, Aug. 2014.

- [1-12] M. Jaritz and J. Biela, "Optimal design of a modular series parallel resonant converter for a solid state 2.88 MW/115-kV long pulse modulator," IEEE Transaction Plasma Sci., vol. 42, no. 10, pp. 3014-3022, Oct. 2014.

- [1-13] Philips, <a href="http://www.usa.philips.com/healthcare/product/HCNCTB107/ct-big-bore-ct-simulator">http://www.usa.philips.com/healthcare/product/HCNCTB107/ct-big-bore-ct-simulator</a>

- [1-14] Siemens, https://w5.siemens.com/web/ua/ru/medecine/detection\_diagnosis/surgery-c-arm-systems / Mobile-C-arm-systems/ARCADIS-Avantic/Documents/348\_xp\_arcadis avantic\_final\_26129945\_5-00667284.pdf

- [1-15] Spellman, https://www.spellmanhv.com/en/Products/HFe

- [1-16] Alstom, http://img.saom.net.cn/pic/z114ede8-0x0-1/electrostatic\_precipitator.jpg

- [1-17] Alstom, the product brochure of high frequency power supplies for electrostatic precipitators (ESPs)

- [1-18] S. Mao, C. Li; W. Li; J. Popovic, J. Ferreira, "A Review of High Frequency High Voltage Generation Architecture," in Proc. IEEE ECCE-Asia 2017, pp. 1-7

- [1-19] S. Linder, "Power semiconductors in the electronics roadmap," in proc. International Seminar on Power Semiconductors Conference, 2008, pp. 1-29

- [1-20] A. Hefner, R. Sei-Hyung, B. Hull, D. Berning, C. Hood, J. M. Ortiz-Rodriguez, A. Rivera-Lopez, D. Tam, A. Adwoa, and M. Hernandez-Mora, "Recent advances in high voltage, high-frequency silicon-carbide power devices," in Proc. IEEE IAS 2006, pp. 330-337

- [1-21] J. Popović, J.A. Ferreira, "Concepts for high packaging and integration efficiency", in Proc. IEEE PESC 2004, pp. 4188-4194

- [1-22] J.A. Ferreira, J. Popović, "Packaging, Integration, Thermal management-From the State of the art to future trends", in Proc. PCIM 2003, pp. 20-22

# Chapter 2

# Overview of the state-of-art HV pulse converter technologies

### 2.1 Introduction

HV pulse converter systems being compact in size, lightweight and with sharp pulse features are required in various industrial applications, such as X-ray generators and electrostatic precipitators. HV pulse converter technologies have been developed in past three decades. In order to choose the correct technologies to achieve good HV pulse converter performance and identify the bottlenecks against further improvements, it is important to understand HV pulse converter technologies which have already been developed. This chapter examines these HV pulse converter technologies to provide an overall picture. First, an overview of a series of architectures of HV pulse converter topologies are introduced. Then a review of HV pulse converter circuit topologies and control, key subcomponents such inverter, HV transformers, and HV rectification, as well as packaging technologies are discussed. Finally, a summary is drawn based on the review. Recommendations for HV pulse converter technologies are also given.

# 2.2 HV pulse converters architectures

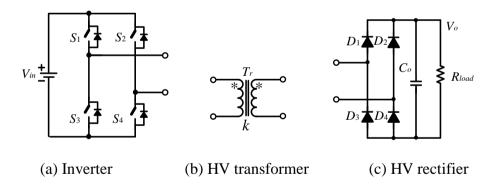

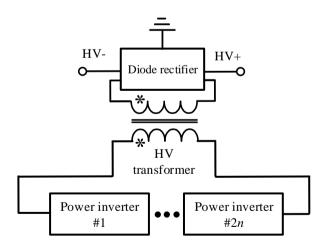

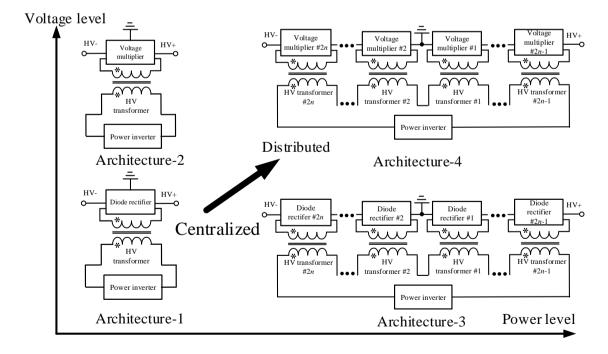

Different HV pulse converter architectures have been investigated to generate HV output from low voltage input for various applications. As introduced in Chapter-1, the typical HV pulse converter circuit includes a high-frequency DC-AC inverter, a HV transformer and a HV rectifier/multiplier. The HV pulse converter circuit diagram is drawn in Fig. 2-1. The inverter, HV transformer and HV rectifier are the three key power building blocks for a HV pulse converter main circuit. In general, there are two kinds of HV pulse converter architectures according to whether the sub-components of the HV pulse converter main circuit are of single or multiple configuration. For example, a multi-level inverter or multi-phase inverter can be regarded as a multiple type inverter configuration. A combination of HV transformers in a HV pulse converter circuit can be treated as multiple transformer configurations. A rectifier or doubler is considered as a single type rectification circuit and a multi-stage voltage multiplier is considered a multiple rectification circuit. It is easier to achieve high power rating, and reduce the electric, as well as insulation stress of single sub-component for a multiple configuration HV pulse converter.

Fig. 2-1 HV pulse converter circuit diagram

## 2.2.1 Architectures with a single power building block sub-component

The HV pulse converter architecture with a single inverter, a single HV transformer and a single rectifier, shown in Fig. 2-2, is widely used for existing industrial applications [2-1]-[2-24]. The main pros and cons of HV pulse converter architectures with a single power building block are listed as follows:

#### Advantages

- a) Simple structure.

- b) Fast HV pulse speed, low output voltage ripple with diode rectifications.

#### Disadvantages

- a) Insulation stress for the HV transformer is very large since it relies on a single HV transformer to achieve HV step up. The insulation design is complex and the size of HV transformer is large.

- b) The switching frequency is limited due to large parasitic capacitance and high leakage inductance of HV transformer.

- c) Not scalable for different output voltage and power rating

- d) The power density and efficiency improvement are challenged due to high insulation stress and large parasitic components for the HV transformer when the switching frequency is further increased.

Fig. 2-2 Circuit diagram of HV pulse converter architecture with a single inverter, a single HV transformer and a single rectifier

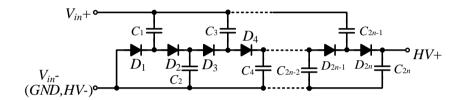

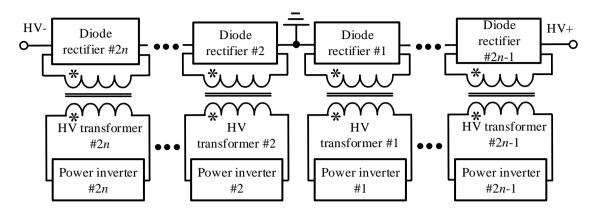

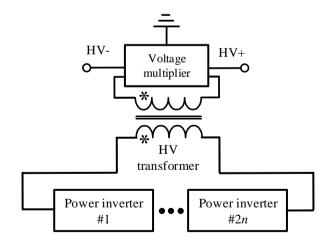

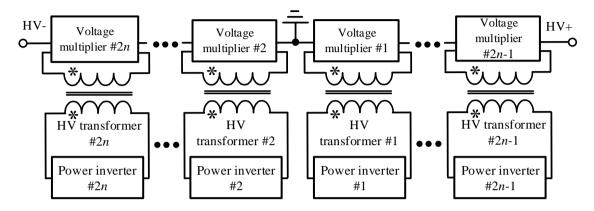

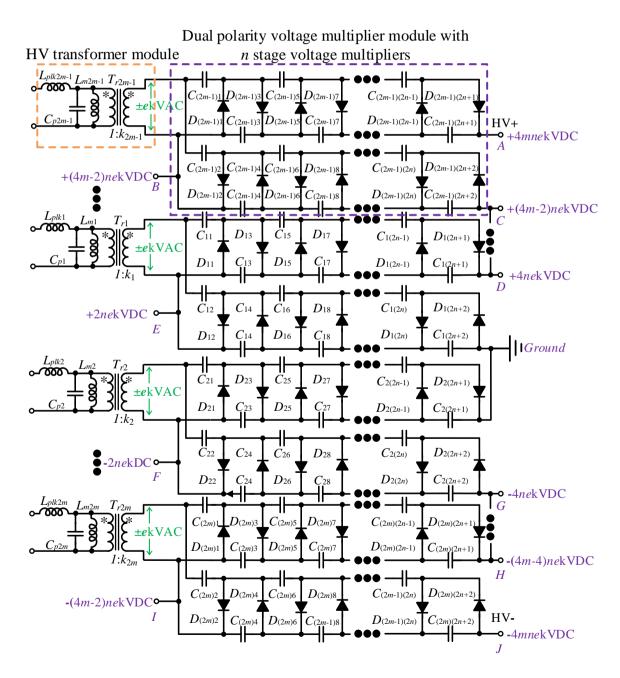

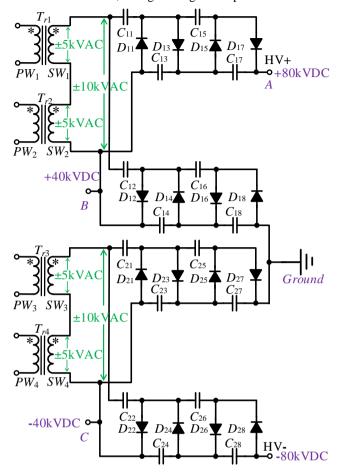

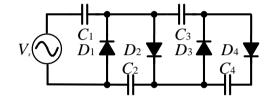

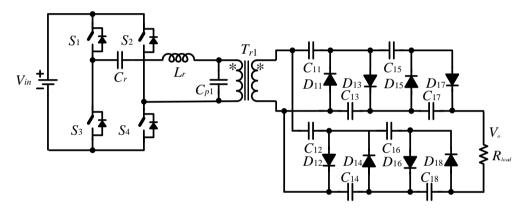

#### 2.2.2 Architectures with multiple power building block sub-components

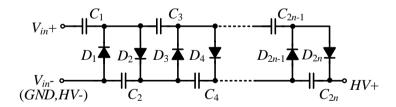

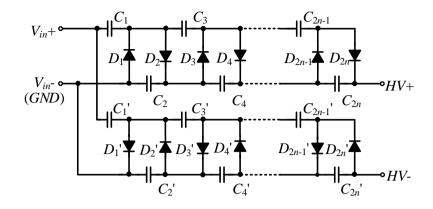

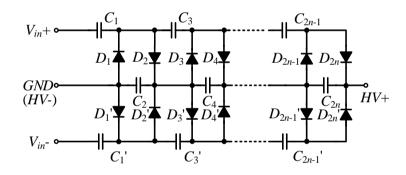

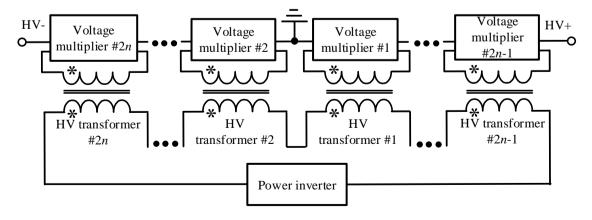

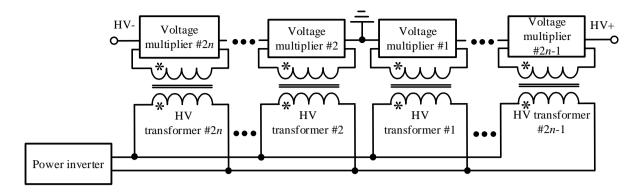

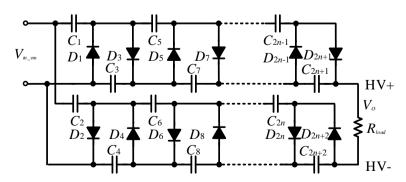

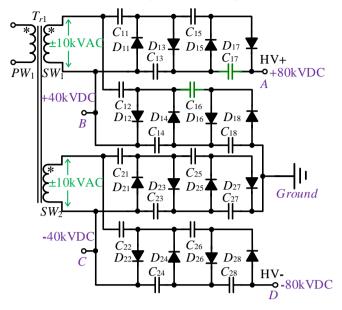

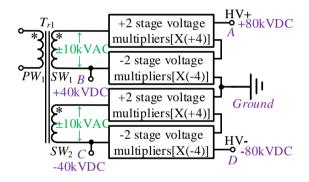

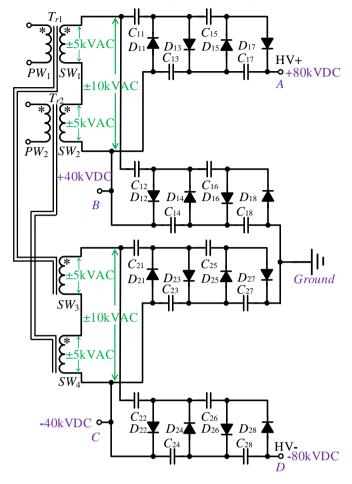

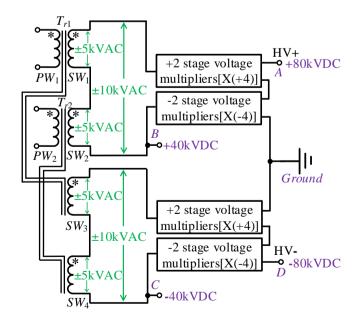

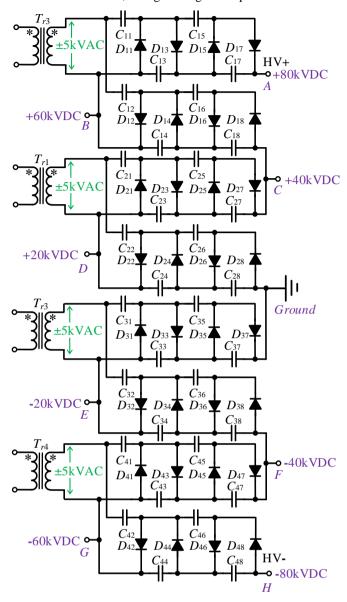

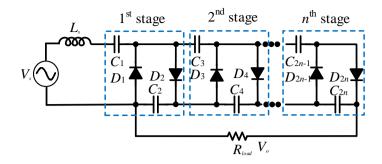

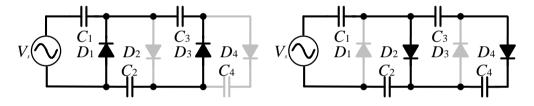

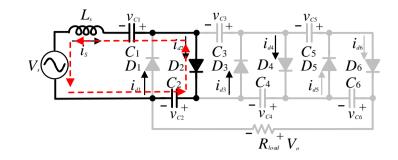

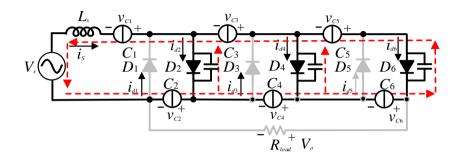

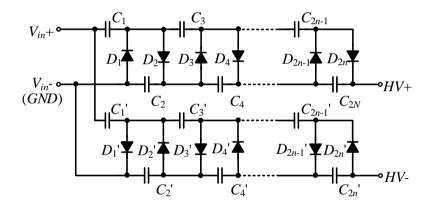

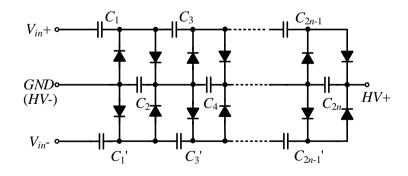

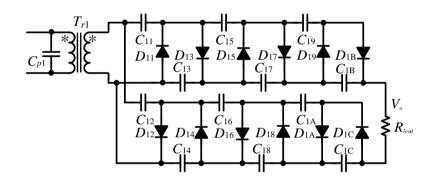

The Cockcroft-Walton voltage multiplier was introduced for the HV pulse converter to achieve the required high output DC voltage [2-25]-[2-39]. With the voltage multiplier, the insulation stress for a HV transformer can be largely reduced, unlike with the single rectifier configuration architecture, and this leads to a reduction of insulation stress for a HV transformer.

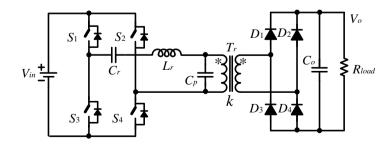

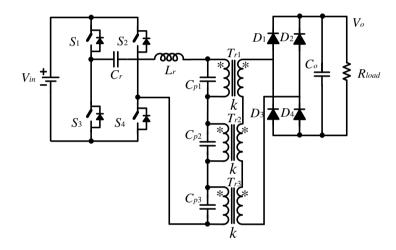

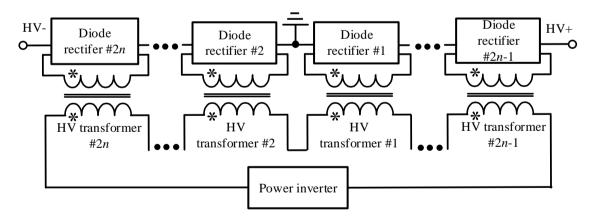

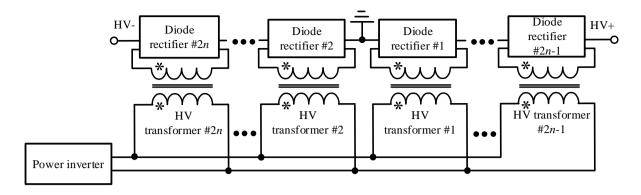

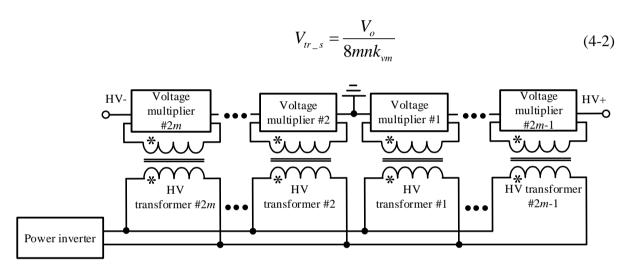

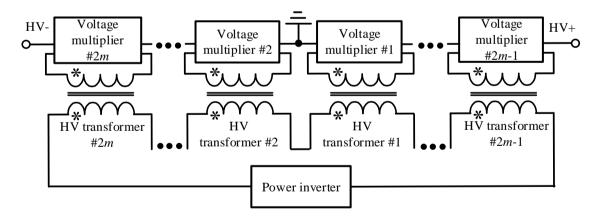

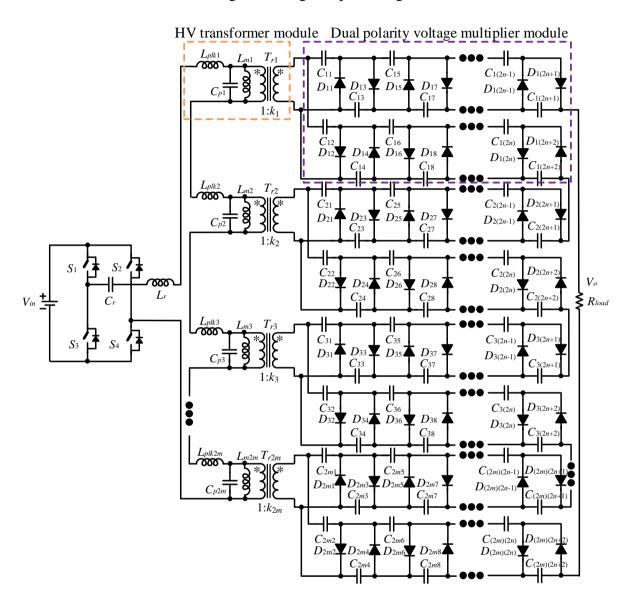

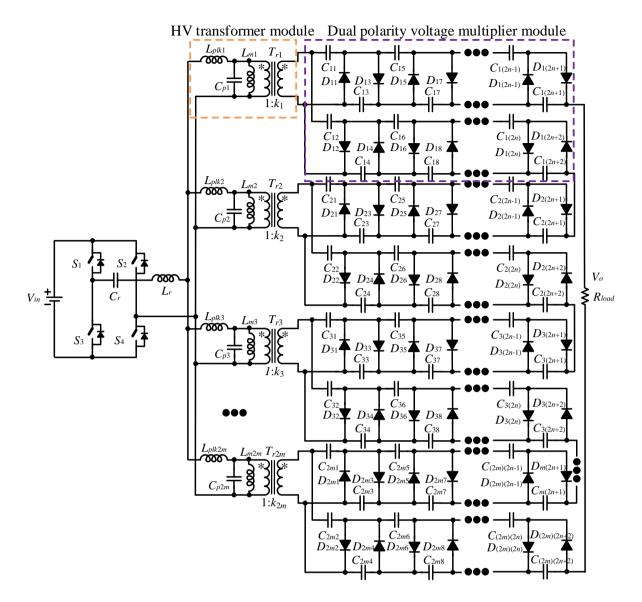

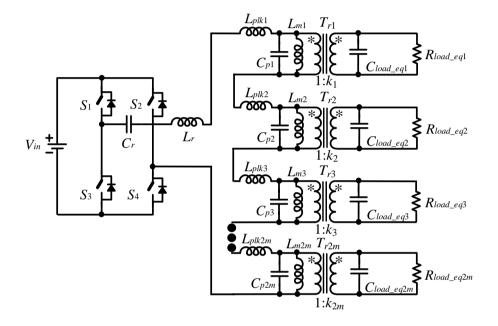

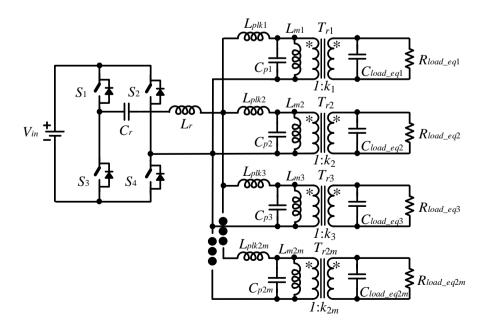

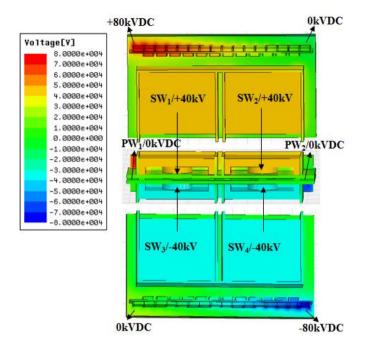

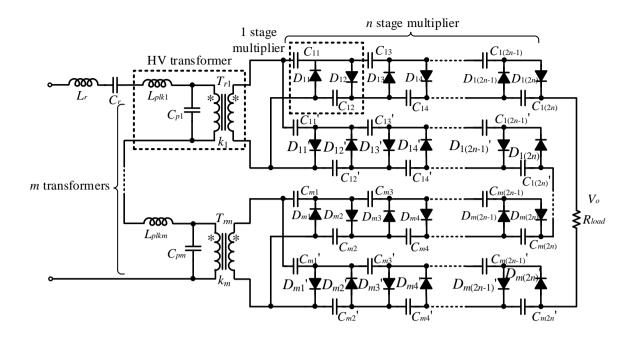

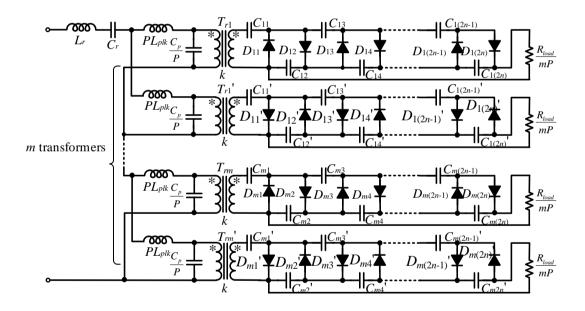

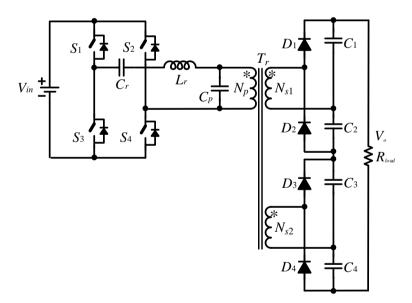

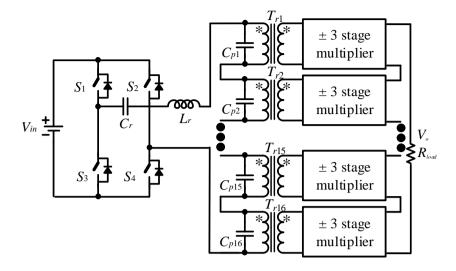

The multiple transformers configurations based HV pulse converter architectures are used together with a rectifier and connected in series so that the insulation stress of each transformer can be greatly decreased. Fig. 2-3 illustrates the circuit diagram of an example of the modular HV pulse converter architecture with a single inverter, multiple HV transformers and single rectifier. The connection of the transformer's primary sides can be either series or parallel. The series connection is suitable for a higher input AC voltage, and parallel connection is suitable for a large current application [2-40]-[2-49].

Fig. 2-3 Circuit diagram of a single inverter, multiple HV transformers and single rectifier based modular HV pulse converter architecture

Multi-level inverter or multi-phase inverter configurations will reduce the voltage stress or current stress for inverter power semiconductor devices at high power rating [2-50]-[2-56]. Furthermore, the most complex HV pulse converter architecture combines multiple inverters, multiple HV transformers, and multiple rectifiers provide full modularity for a power building block for HV pulse converter main circuit subcomponents [2-57]-[2-81]. The main pros and cons of HV pulse converter architectures with multiple power building blocks are listed as follows:

#### Advantages

- a) Modular structure.

- b) Scalable for different output voltage and power rating.

- c) Insulation stress and parasitic components can be smaller due to reduced turns ratio for a HV transformer with multi-stage multiplier rectifications.

- d) Power density and efficiency improvement with high switching frequency operation.

#### Disadvantages

- a) Power sharing between multiple power building blocks.

- b) The variance of HV transformer parasitics including magnetizing inductance, leakage inductance, winding capacitance due to the magnetic core characteristics difference and inconsistent manufacture process will lead to the voltage and current sharing challenges for modular HV pulse converter architectures. Furthermore, the variance of multiplier capacitor and the parasitic capacitance and inductance of the HV multi-stage multiplier circuits will also impact on the voltage and current sharing for modular HV pulse converter architectures.

- c) HV pulse rise and decay time, low output voltage ripple challenges due to multi-stage multiplier rectifications

- d) The HV pulse speed is related to the stage number of multi-stage multiplier rectifications. The HV pulse speed slows when the stage number of multi-stage multiplier are larger.

## 2.3 Topologies, model and control

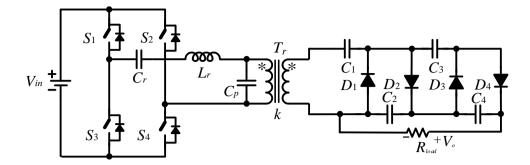

#### 2.3.1 Topologies for HV pulse converter

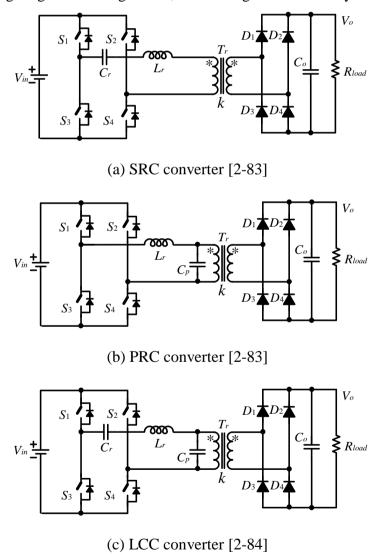

Due to the required high output voltage level of a HV pulse converter, a high turns-ratio transformer is usually adopted to boost voltage and a large insulation distance is needed. As a result, the leakage inductance and parasitic capacitance of the transformer cannot be ignored when it comes to choose the appropriate topology for a HV pulse converter, especially in high frequency conditions. The resonant converters, which can utilize the transformer parasitic capacitance, provide obvious advantages compared with pulse width modulation (PWM) converters. Large leakage inductance and parasitic capacitance of HV transformers can be utilized as part of the resonant tank in resonant converters, while in PWM converters they are harmful to efficiency improvement. In resonant converters, resonant current in the primary side of transformer is approximately sinusoidal under all load conditions, which enables the zero-current switching (ZCS) or zero-voltage switching (ZVS) of devices including switches of the inverter and diodes of the rectifier. As a result, high efficiency operation can be ensured.

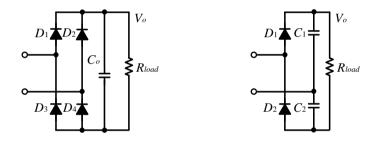

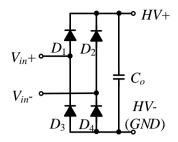

Series resonant converters (SRC) and parallel resonant converters (PRC) are two basic topologies of resonant converters [2-82], as depicted in Fig. 2-4(a) and (b). The capacitive output filter is preferred since HV filter inductor is not required. The advantage of SRC is the reduction in the current stress of power device with a decrease in load. This will lead to the conduction loss reduction for the power switching device as the load decreases, consequently preserving high part load efficiency. The parasitic capacitance of a HV transformer cannot be utilized by the SRC and will deteriorate circuit behaviour. Another drawback of the SRC is that the frequency band to achieve output voltage regulation over an entire range of loads will be very large. Therefore, the optimization of the SRC is very difficult from light load to full load. The maximum voltage gain of the SRC is only one. The limited voltage gain of SRC introduces the burden for the transformer and rectification circuit. A large turns ratio of the HV

transformer, and multi-stage multiplier circuit, can realize the required voltage gain lead to large leakage inductance and parasitic capacitance for the HV transformer as well as HV pulse speed decrease [2-83].

PRC makes use of the parasitic capacitance parameters of a HV transformer. Meanwhile, the transformer leakage inductance appears in series with the resonant inductor. Consequently, the PRC topology can integrate the HV transformer parasitics very well and then the transformer nonidealities do not degrade operation of the converter. The voltage gain of PRC can be larger than one, which can help to reduce the turns ratio of the HV transformer, or stage number of the voltage multiplier circuit. The main disadvantage of PRC is high device current stress which is relatively independent of load. The PRC will suffer poor efficiency at light load conditions. It's difficult for PRC to manage the good voltage regulation at the entire load range since PRC provides good voltage regulation at light load, but bad regulation at heavy load [2-83].

Fig. 2-4 Resonant converter topologies for the HV pulse converter

To combine the advantages of SRC and PRC, the Series-Parallel (LCC) resonant converter is widely adopted for HV pulse converter applications [2-84], as depicted in Fig. 2-4(c). The LCC converter can fully absorb the transformer parasitic components. The current in the inverter switches and resonant tank decreases as the load decreases, which ensures good efficiency at light load and no load. Furthermore, the LCC converter exhibits better control characteristics over the entire load range than the conventional two elements resonant converters with an additional resonant element.

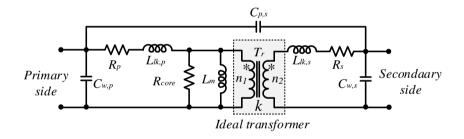

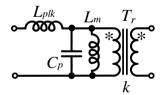

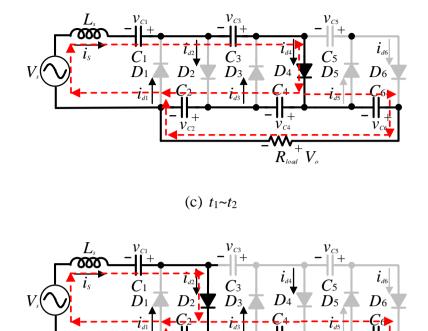

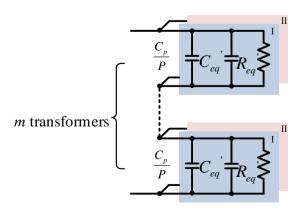

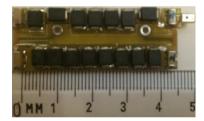

#### 2.3.2 Modeling and Control

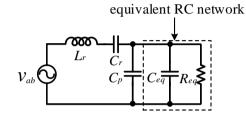

It is complex to acquire the accurate model of a LCC converter due to coupling of different resonant frequencies. Some simplified analysis methods are proposed to acquire a mathematical model with acceptable accuracy. Since a resonant current in the primary side of the transformer is approximately sinusoidal, the most widely used method in modeling of an LCC converter is based on First Harmonic Approximation (FHA), which utilizes the fundamental components of current and voltage in analysis [2-21]. In [2-85], the secondary part of the transformer is replaced by an equivalent RC network, as depicted in Fig. 2-5.  $R_{eq}$ ,  $C_{eq}$  are equivalent models of rectifiers, capacitor and load network. Based on the FHA model, further analysis and design are achieved with satisfactory results. [2-5], [2-34] give a dynamic and steady-state model of LCC converter. The step by step design procedure for a LCC converter is provided in [2-6], [2-17].

Fig. 2-5 Equivalent RC network of secondary side [2-85]

It can be demonstrated from Fig. 2-5 that the fundamental component of transformer voltage is decided by the impedance of the resonant tank and equivalent RC network, hence

$$\frac{V_{T(1)}(s)}{V_{ab(1)}(s)} = H(s) \tag{1}$$

To a given LCC converter,  $H_{(s)}$  is influenced by an operating point including frequency and load resistance. Ignoring harmonics,  $V_{T(I)}$  is proportional to output voltage. Thus, it is concluded that output voltage is controlled by switching frequency and duty cycle. The main control objective of a LCC converter is to regulate output voltage and enable soft switching at the entire load range. The output voltage can be controlled by frequency and duty cycle. The soft switching condition is deeply affected by impedance of the resonant tank. The simplest control schedule of the converter is 50% duty cycle with variable frequency, known as the voltage frequency (VF) method [2-6]. In this method, if impedance of the resonant tank is capacitive, it means that the fundamental component of input voltage has a phase lag behind the current. It is possible to turn off switches when the phase current reaches zero, however, hard turn-on occurs in this mode if the converter works in continuous conduction mode (CCM).

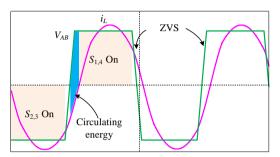

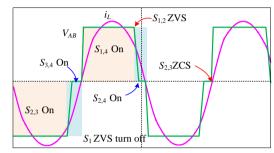

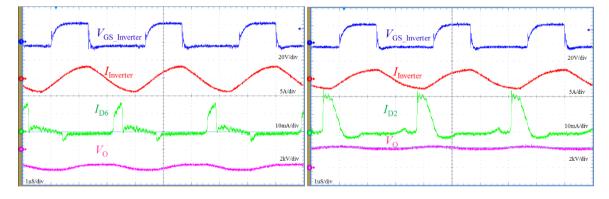

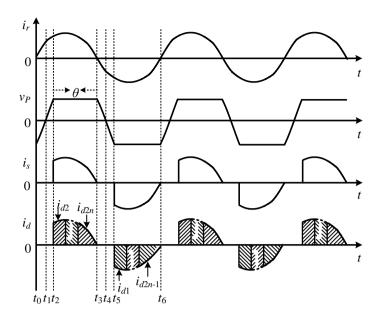

If the impedance of the resonant tank is inductive, ZVS can be achieved for all switches. However, VF control has reactive power in a resonant tank, as shown in the shaded area in Fig.2-6(a), the conducting loss increases especially under light load conditions. To solve this problem dual control, which regulates switching frequency to ensure ZCS of one phase leg of inverter and ZVS for the other and uses duty cycle to regulate output voltage, is proposed as an improvement of VF control in in Fig.2-6(b) [2-6]. In this control scheme, circuiting energy disappears and improved efficiency can be acquired. The drawback of this strategy is addition of a current polar detection circuit. The key waveform comparison of VF control and dual control strategy is depicted in Fig. 2-4.

Fig. 2-6 Key waveform of LCC (a) VF control; (b) Dual control

#### 2.4 HV transformers

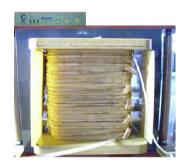

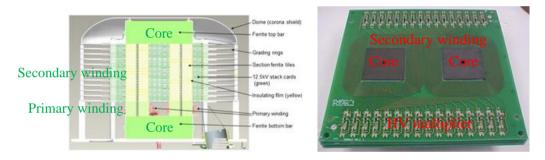

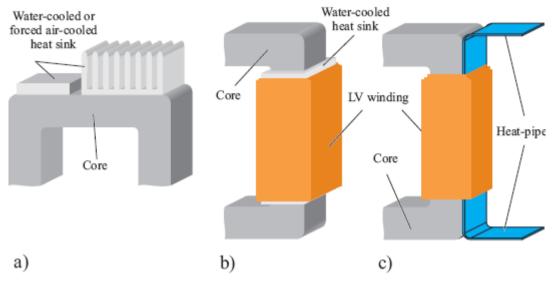

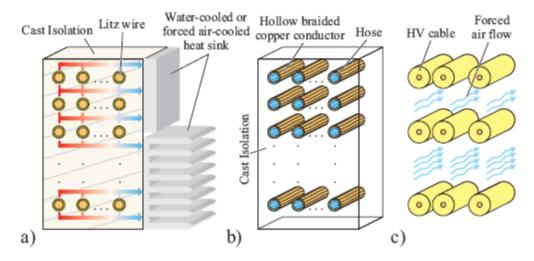

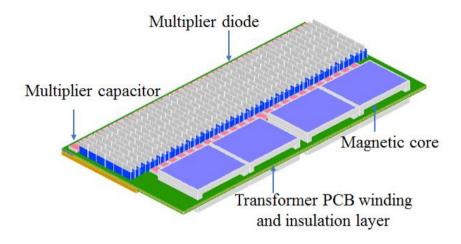

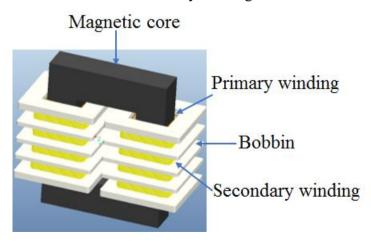

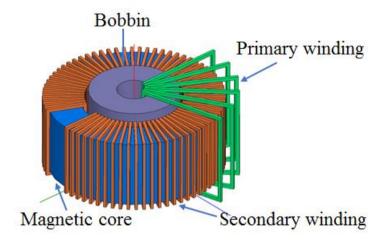

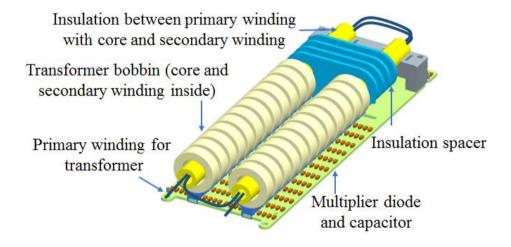

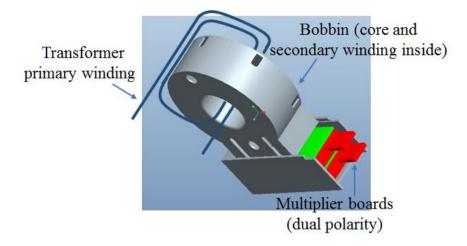

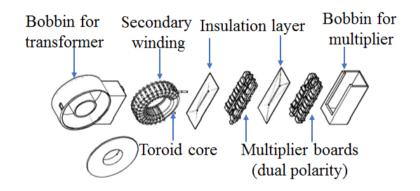

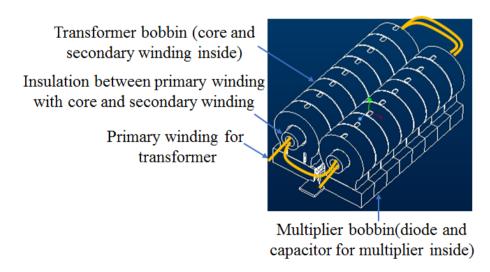

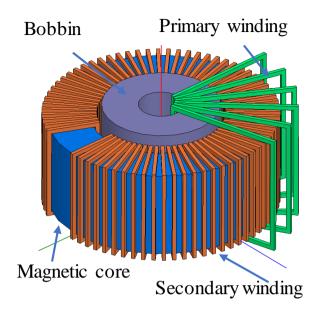

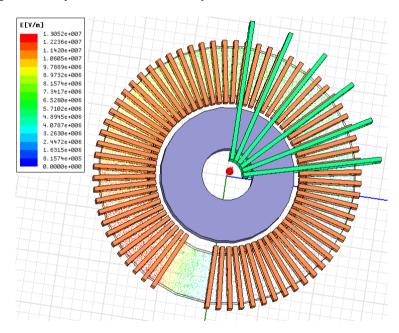

#### 2.4.1 Transformer structure

- (a) non-planar barrel structure

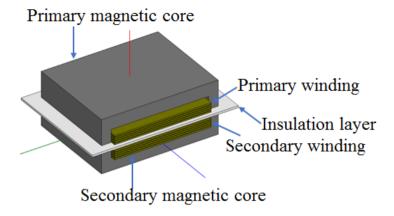

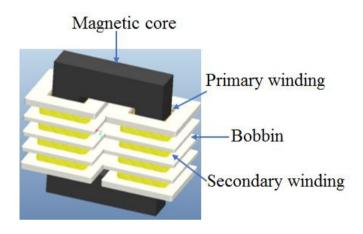

- (b) planar structure

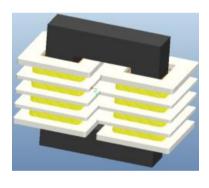

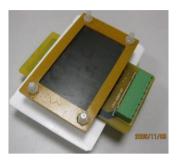

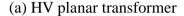

Fig. 2-7 Non-planar barrel and non-planar barrel HV transformer structures

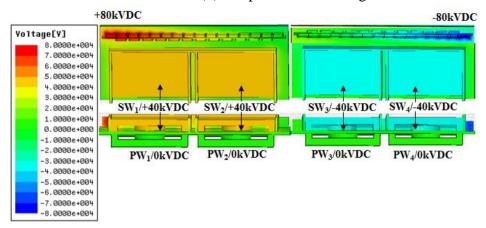

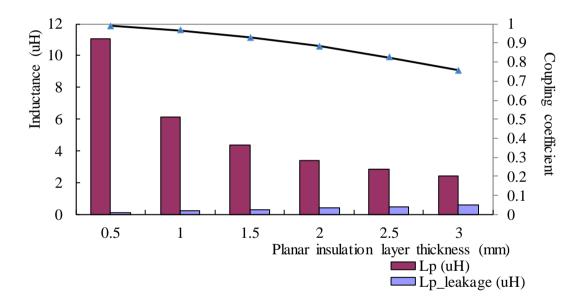

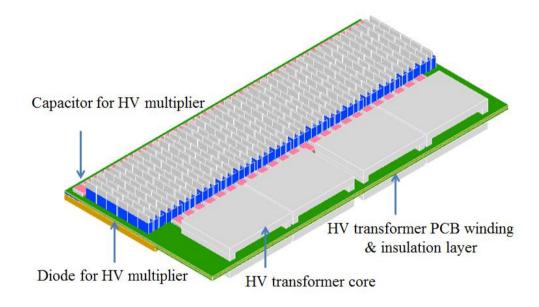

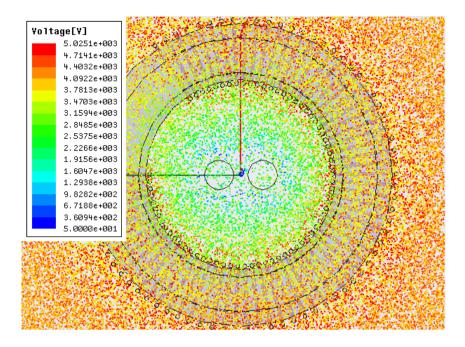

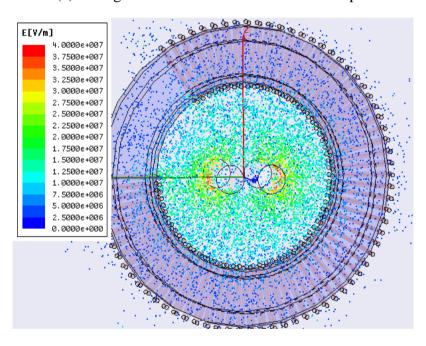

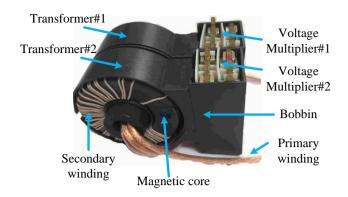

Compared with a low voltage transformer, large turns ratio and insulation requirements are the main differences of a HV transformer. The transformer is implemented using magnetic cores of different shapes and various magnetic materials. The windings of the transformer can be implemented in different manners such as wire-wound, planar printed circuit board (PCB), copper foil and helical winding technologies. Regardless of the magnetic core shapes and winding technologies utilized, the transformer can be constructed using two packaging structures: planar and non-planar barrel type [2-87]. The non-planar barrel and planar HV transformer are illustrated in Fig. 2-7(a) and Fig. 2-7(b) respectively [2-15], [2-26], [2-88]. The non-planar barrel HV transformer is implemented using various core shapes, such as ringshaped and E- and I-shaped cores. The primary and secondary windings which are composed of solid and litz wire or copper foil are wound on a bobbin. The bobbin provides the essential